**TPS274C65** SLVSFZ2C - APRIL 2023 - REVISED FEBRUARY 2024

# TPS274C65xS 72mΩ, Quad-Channel Smart High-Side Switch With SPI Interface and **Diagnostics**

#### 1 Features

- Quad-channel 72mΩ R<sub>ON</sub> SPI-controlled smart high-side switch

- Low R<sub>ON</sub> ensures low power dissipation for 500mA to 2A DC loads

- SPI control allows for simple isolation of control from output

- Adjustable current limiting enables improved system level reliability

- TPS274C65AS, TPS274C65BS: Current limit set-point from 250mA to 2.2A

- TPS274C65ASH: Current limit set-point from 290mA to 2.45A

- Capable of driving inductive, capacitive, and resistive loads

- Dual current limit threshold for inrush current management

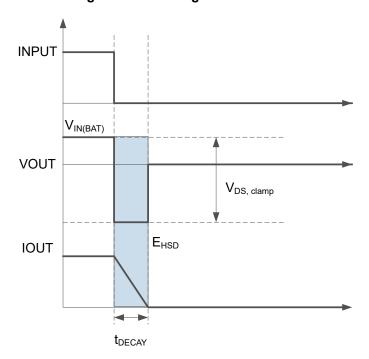

- Integrated output clamp to demagnetize inductive loads

- Robust output protection

- Integrated thermal shutdown

- Protection against short to ground events

- Configurable fault handling

- Diagnostic features enable improved module intelligence

- Output load current measurements

- Wire-break and short-to-supply detection

- Small 6mm × 6mm leadless package

# 2 Applications

- Industrial PLC system

- Digital output module

- IOLink master port

- Sensor supply

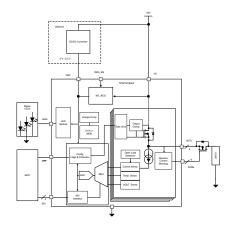

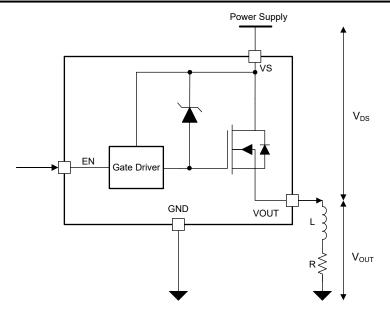

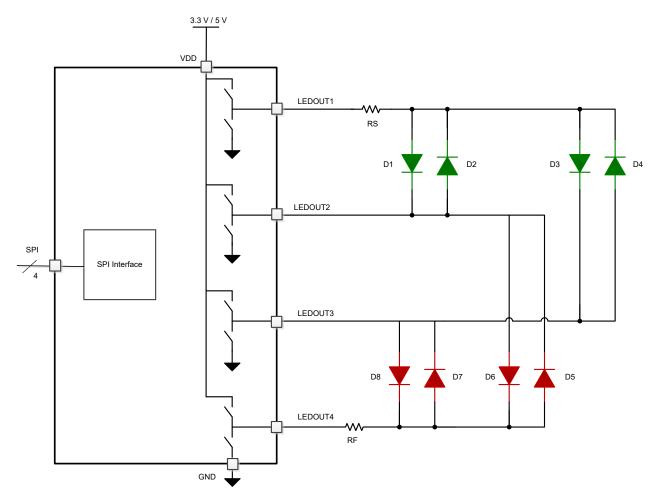

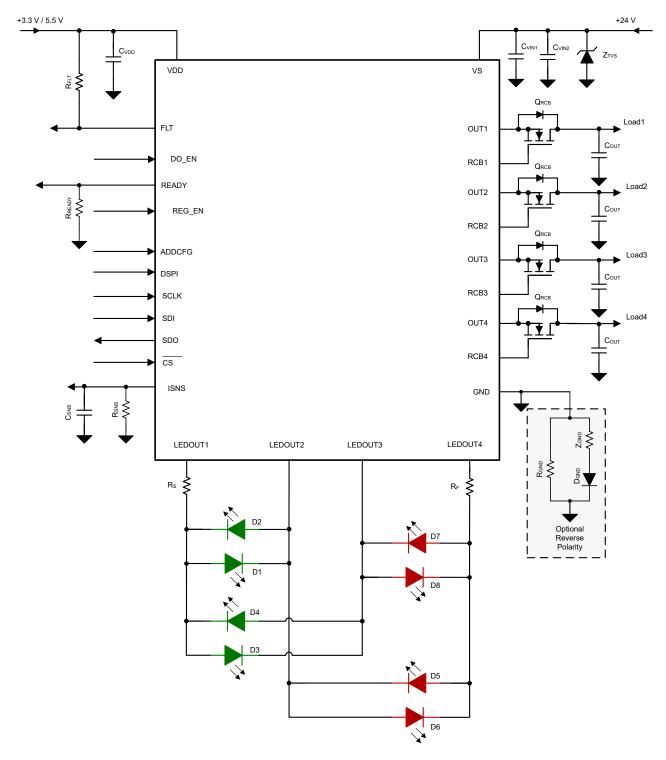

**Typical Application Schematic**

# 3 Description

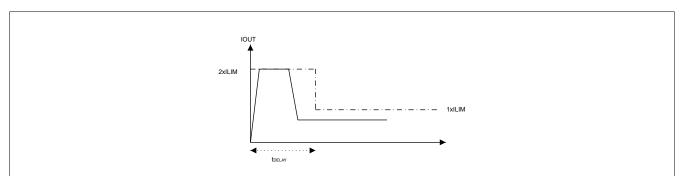

The TPS274C65xS device is a quad-channel smart high-side switch with a serial interface (SPI) control and is designed to meet the requirements of industrial control systems. The low  $72m\Omega$   $R_{DSON}$  minimizes device power dissipation even when providing large output load current. The device integrates protection and diagnostic features to ensure system protection even during harmful events like short circuits or load failures. The device protects against faults through a reliable current limit which is adjustable from 250mA to 2.45A to provide protection regardless of output load current. The TPS274C65xS has a configurable inrush current period which sets a higher current limit during turn-on for high inrush current loads, charging capacitive loads faster, or driving incandescent bulbs.

The TPS274C65xS also provides accurate current sense and an integrated analog to digital converter (AS) that allows for improved load diagnostics. By reporting load current digitally, the device allows for communication over any isolation barrier while enabling predictive maintenance and load diagnostics to improve system lifetime. Additional diagnostic features are integrated, such as on-state or off-state open load detection and short-to-supply detection.

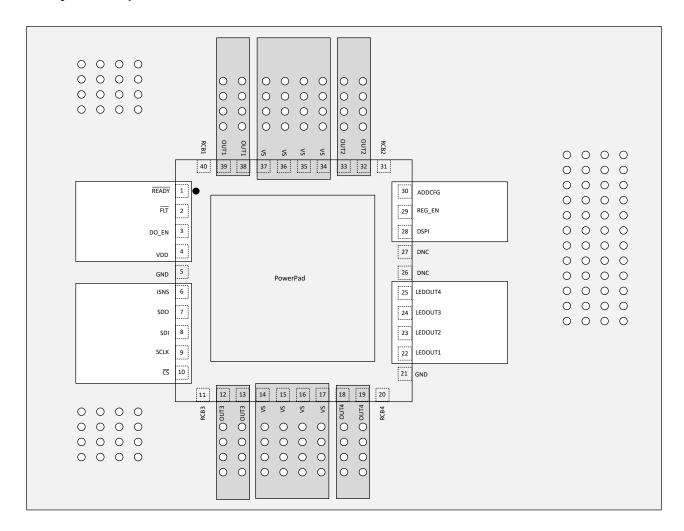

The TPS274C65xS is available in a small 6mm × 6mm VQFN package with 0.5mm pin pitch, which minimizes design PCB footprint.

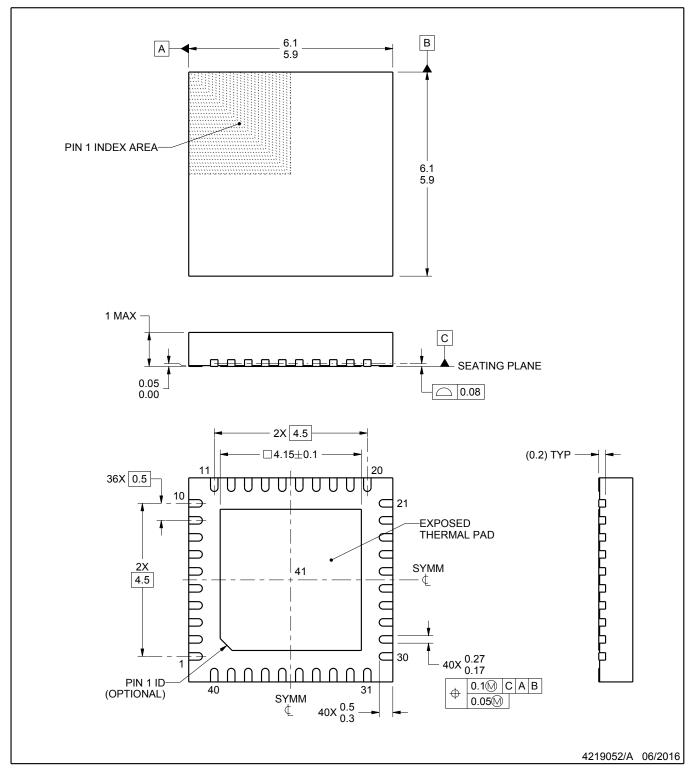

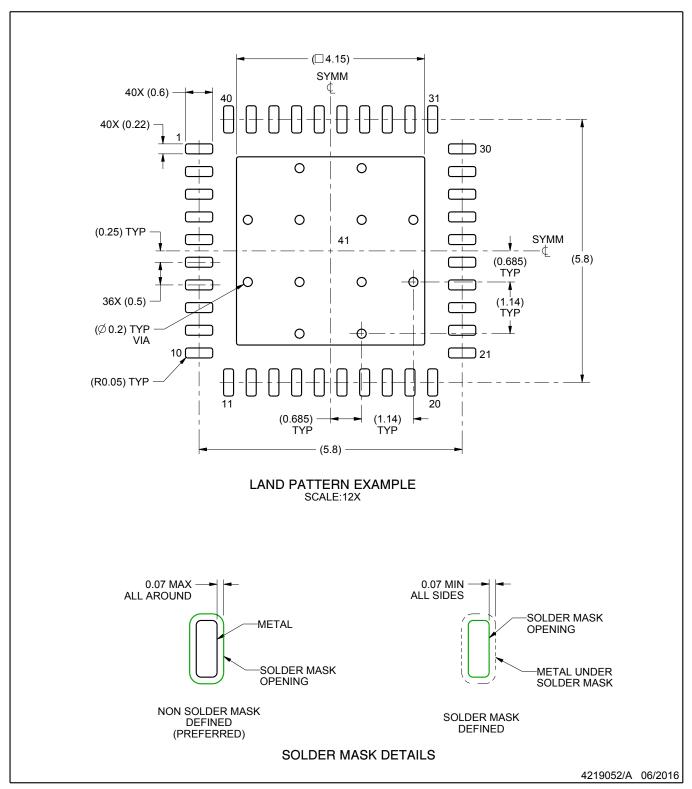

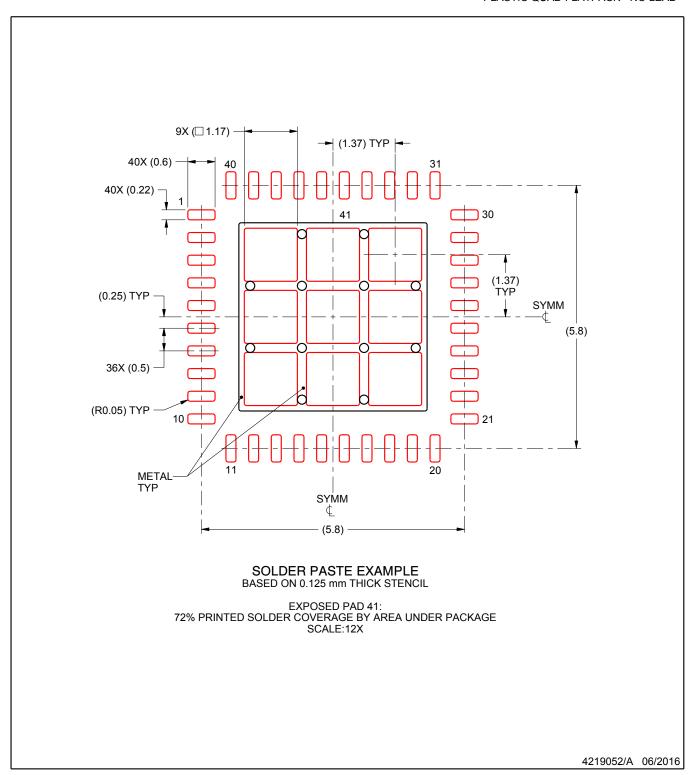

**Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TPS274C65xS | RHA (VQFN, 40)         | 6.00mm × 6.00mm             |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

# **Table of Contents**

| 1 Features                           | 1              | 8.3 Feature Description                              | 18                |

|--------------------------------------|----------------|------------------------------------------------------|-------------------|

| 2 Applications                       |                | 8.4 Device Functional Modes                          |                   |

| 3 Description                        |                | 8.5 TPS274C65BS Available Registers List             | 48                |

| 4 Device Comparison Table            |                | 8.6 TPS274C65 Registers                              |                   |

| 5 Pin Configuration and Functions    | 4              | 9 Application and Implementation                     |                   |

| 6 Specifications                     | <mark>7</mark> | 9.1 Application Information                          | 75                |

| 6.1 Absolute Maximum Ratings         | <mark>7</mark> | 9.2 Typical Application                              | 75                |

| 6.2 ESD Ratings                      | <mark>7</mark> | 9.3 Power Supply Recommendations                     |                   |

| 6.3 Recommended Operating Conditions | 7              | 9.4 Layout                                           | 78                |

| 6.4 Thermal Information              | 8              | 10 Device and Documentation Support                  | 80                |

| 6.5 Electrical Characteristics       | 8              | 10.1 Receiving Notification of Documentation Updates | s <mark>80</mark> |

| 6.6 Switching Characteristics        | 13             | 10.2 Support Resources                               | 80                |

| 6.7 SPI Timing Requirements          | 14             | 10.3 Trademarks                                      | 80                |

| 6.8 Typical Characteristics          | 15             | 10.4 Electrostatic Discharge Caution                 | 80                |

| 7 Parameter Measurement Information  | 16             | 10.5 Glossary                                        | 80                |

| 8 Detailed Description               | 17             | 11 Revision History                                  |                   |

| 8.1 Overview                         |                | 12 Mechanical, Packaging, and Orderable              |                   |

| 8.2 Functional Block Diagram         | 17             | Information                                          | 81                |

# **4 Device Comparison Table**

# **Table 4-1. Functionality Comparison**

| Part Number          | Interface | Reverse<br>Current<br>Blocking<br>(RCB) | Integrated<br>LED<br>Driver |     | Current<br>Limit<br>Settings<br>Allow for<br>2A<br>Operation | Current Sense                    | Available Registers                         |

|----------------------|-----------|-----------------------------------------|-----------------------------|-----|--------------------------------------------------------------|----------------------------------|---------------------------------------------|

| TPS274C65 <b>AS</b>  | SPI       | Yes                                     | Yes                         | Yes | No                                                           | Digital via SPI or analog output | See TPS274C65<br>Registers                  |

| TPS274C65 <b>ASH</b> | SPI       | Yes                                     | Yes                         | Yes | Yes                                                          | Digital via SPI or analog output | See TPS274C65<br>Registers                  |

| TPS274C65 <b>BS</b>  | SPI       | No                                      | No                          | No  | No                                                           | No current sense                 | See TPS274C65BS<br>Available Registers List |

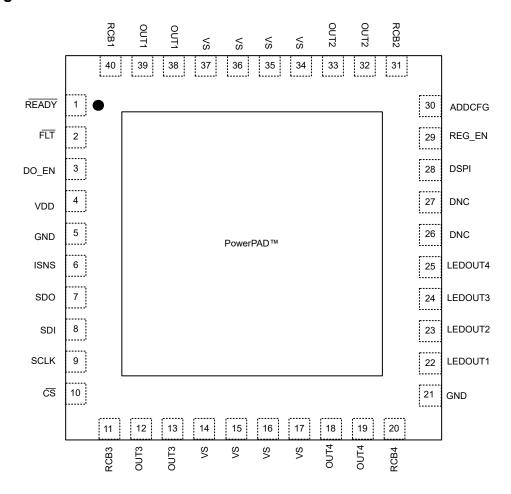

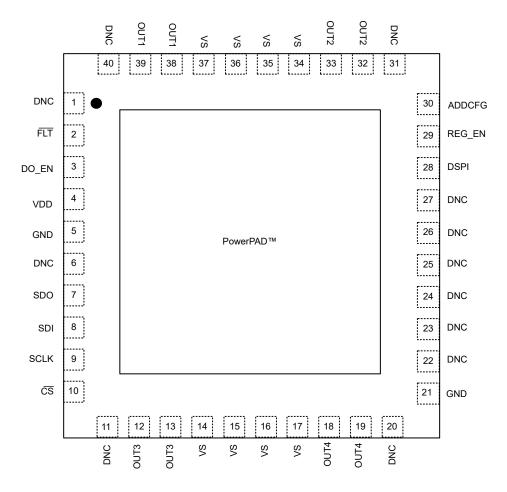

# **5 Pin Configuration and Functions**

Figure 5-1. RHA Package, 40-Pin VQFN – AS and ASH Version (Top View)

Figure 5-2. RHA Package, 40-Pin VQFN - BS Version (Top View)

Table 5-1. Pin Functions - Version AS and BS

Do not connect for pins labeled DNC

|        | PIN                          |                    |                     |                                                                                                                     |

|--------|------------------------------|--------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|

| NO.    | TPS274C65AS,<br>TPS274C65ASH | TPS274C65BS        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                         |

| 1      | READY                        | DNC <sup>(3)</sup> | 0                   | Logic low output indicating the IC is ready for SPI data transmission (connect to GND pin of the IC with resistor). |

| 2      | FLT                          | FLT                | 0                   | Fault output – on any (one or more) channel - open drain, needs to be pulled up to VDD pin.                         |

| 3      | DO_EN                        | DO_EN              | 1                   | Setting this pin low would disable all of the outputs. Set high to enable SPI based output Internal pull-down.      |

| 4      | VDD <sup>(2)</sup>           | VDD <sup>(2)</sup> | Р                   | Logic Supply Input <sup>(2)</sup> .                                                                                 |

| 5, 21  | GND                          | GND                | _                   | Device ground.                                                                                                      |

| 6      | ISNS                         | DNC <sup>(3)</sup> | 0                   | SNS current output – use a parallel RC network to the GND pin of the IC.                                            |

| 7      | SDO                          | SDO                | 0                   | SPI Data Output from the device.                                                                                    |

| 8      | SDI                          | SDI                | I                   | SPI device (secondary) data input.                                                                                  |

| 9      | SCLK                         | SCLK               | 0                   | SPI Clock Input.                                                                                                    |

| 10     | CS                           | CS                 | ı                   | SPI Chip select.                                                                                                    |

| 11     | RCB3                         | DNC <sup>(3)</sup> | 0                   | Gate connection for reverse current blocking FET Ch3.                                                               |

| 12, 13 | OUT3                         | OUT3               | 0                   | Output voltage for channel 3.                                                                                       |

### Table 5-1. Pin Functions – Version AS and BS (continued)

Do not connect for pins labeled DNC

|                | PIN                          |                    |                     |                                                                                                                                                                            |

|----------------|------------------------------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.            | TPS274C65AS,<br>TPS274C65ASH | TPS274C65BS        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                |

| 14–17          | VS                           | VS                 | Р                   | 24V Switch Supply input to the IC.                                                                                                                                         |

| 18, 19         | OUT4                         | OUT4               | 0                   | Output voltage for channel 4.                                                                                                                                              |

| 20             | RCB4                         | DNC <sup>(3)</sup> | 0                   | Gate connection for reverse current blocking FET Ch4.                                                                                                                      |

| 22             | LEDOUT1                      | DNC <sup>(3)</sup> | 0                   | LED matrix select driver.                                                                                                                                                  |

| 23             | LEDOUT2                      | DNC <sup>(3)</sup> | 0                   | LED matrix select driver.                                                                                                                                                  |

| 24             | LEDOUT3                      | DNC <sup>(3)</sup> | 0                   | LED matrix select driver.                                                                                                                                                  |

| 25             | LEDOUT4                      | DNC <sup>(3)</sup> | 0                   | LED matrix select driver.                                                                                                                                                  |

| 26             | DNC <sup>(3)</sup>           | DNC <sup>(3)</sup> | _                   | Do not connect.                                                                                                                                                            |

| 27             | DNC <sup>(3)</sup>           | DNC <sup>(3)</sup> | _                   | Do not connect.                                                                                                                                                            |

| 28             | DSPI                         | DSPI               | ı                   | Configure the device in daisy chain SPI mode when the pin is pulled HI.                                                                                                    |

| 29             | REG_EN                       | REG_EN             | ı                   | Internal Regulator Enable pin, float to enable. Tie to GND to disable and use an external supply input to VDD.                                                             |

| 30             | ADDCFG                       | ADDCFG             | 1                   | SPI IC Address Configuration pin – set the 3-bit address of each IC (up to 8 on one board) with a resistor to GND pin of the IC. Leave floating if using Daisy Chain mode. |

| 31             | RCB2                         | DNC <sup>(3)</sup> | 0                   | Gate connection for reverse current blocking FET Ch2.                                                                                                                      |

| 32, 33         | OUT2                         | OUT2               | 0                   | Output voltage for channel 2.                                                                                                                                              |

| 34–37          | VS                           | VS                 | Р                   | 24V Switch Supply input to the IC.                                                                                                                                         |

| 38, 39         | OUT1                         | OUT1               | 0                   | Output voltage for channel 1.                                                                                                                                              |

| 40             | RCB1                         | DNC <sup>(3)</sup> | 0                   | Gate connection for reverse current blocking FET Ch1.                                                                                                                      |

| Exposed<br>Pad | GND                          | GND                | I                   | Connected to GND pin of the IC.                                                                                                                                            |

- (1) I = input, O = output, P = power.

- (2) When the device is configured to support an external regulator connected to VDD, it is required that the supply input for the external regulator is derived from the same VS supply of TPS274C65 as shown in the Typical Application Schematic.

- (3) Do not connect for pins labeled DNC.

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

Over operating free-air temperature range (unless otherwise noted)(1)

|                                                      |                                                                      | MIN           | MAX                   | UNIT |

|------------------------------------------------------|----------------------------------------------------------------------|---------------|-----------------------|------|

| Continuous supply voltage, V <sub>VS</sub> to IC_GND |                                                                      | -0.3          | 40                    | V    |

| Maximum transient (< 1 ms) voltage at the sup        | oply pin (with respect to IC GND), V <sub>VS</sub> , during ON state | -0.3          | 60                    | V    |

| VOUT voltage to IC_GND                               |                                                                      | -30           | V <sub>VS</sub> + 0.3 | V    |

| V <sub>DS</sub> voltage                              | V <sub>DS</sub> voltage                                              | -0.7          | 39                    | V    |

| Low voltage supply pin voltage, V <sub>DD</sub>      | Low voltage supply pin voltage, V <sub>DD</sub>                      | -0.3          | 7.0                   | V    |

| Digital Input pin voltages, V <sub>DIG</sub>         |                                                                      | -0.3          | 7.0                   | V    |

| ED drive pin voltage, V <sub>LED_OUT</sub>           |                                                                      | -0.3          | 7.0                   | V    |

| Analog pin voltage REG_EN                            |                                                                      | -0.3          | 7.0                   | V    |

| RCBx pin voltage, V <sub>RCBx</sub>                  | RCBx pin voltage, V <sub>RCBx</sub>                                  | VOUT –<br>0.7 | VOUT - VOUT + 6       |      |

| Sense pin voltage, V <sub>SNS</sub>                  |                                                                      | -0.3          | 7.0                   | V    |

| FLT pin voltage, V <sub>FLT</sub>                    | FLT pin voltage, V <sub>FLT</sub>                                    | -0.3          | 7.0                   | V    |

| Reverse ground current, I <sub>GND</sub>             | V <sub>S</sub> < 0 V                                                 |               | -50                   | mA   |

| Maximum junction temperature, T <sub>J</sub>         |                                                                      |               | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>                |                                                                      | -65           | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |                         |                                                                                     |                                  | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|----------------------------------|-------|------|

| V <sub>ESD1</sub>  | Electrostatic discharge | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                | All pins except VS and VOUTx     | ±2000 | ٧    |

| V <sub>ESD2</sub>  | Electrostatic discharge | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                | VS and VOUTx with respect to GND | ±4000 | V    |

| V <sub>ESD3</sub>  | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | All pins                         | ±500  | V    |

| V <sub>surge</sub> | Electrostatic discharge | Surge protection with 42 $\Omega$ , per IEC 61000-4-5; 1.2/50 $\mu s$               | VS, OUTx                         | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                       |                                | MIN  | MAX | UNIT |

|-----------------------|--------------------------------|------|-----|------|

| V <sub>S_OPMAX</sub>  | Nominal supply voltage         | 12   | 36  | V    |

| $V_{DD}$              | Low voltage supply voltages    | 3.0  | 5.5 | V    |

| $V_{DIG}$             | All digital input pin voltage  | -0.3 | 5.5 | V    |

| V <sub>FLT</sub>      | FLT pin voltage                | -0.3 | 5.5 | V    |

| V <sub>LED_OUTx</sub> | LED_OUTx pin voltage           | -0.3 | 5.5 | V    |

| V <sub>ANA</sub>      | REG_EN pin voltage             | -0.3 | 5.0 | V    |

| V <sub>ANA</sub>      | SNS, ADDCFG pin voltage        | -0.3 | 5.0 | V    |

| T <sub>A</sub>        | Operating free-air temperature | -40  | 125 | °C   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.4 Thermal Information**

|                       |                                              | TPS274C65X RHA (VQFN) 40 PINS 25.4 15.8 7.6 0.2 |      |

|-----------------------|----------------------------------------------|-------------------------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup> (2)            | RHA (VQFN)                                      | UNIT |

|                       |                                              | 40 PINS                                         |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 25.4                                            | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 15.8                                            | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 7.6                                             | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2                                             | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 7.6                                             | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.6                                             | °C/W |

- (1) For more information about traditional and new thermal metrics, see the SPRA953 application report.

- (2) The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

#### 6.5 Electrical Characteristics

$V_{VS}$  = 11 V to 36 V,  $V_{VDD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 125°C (unless otherwise noted)

| 7/3                          | PARAMETER                                              | TEST CO                                                                   | INDITIONS                                                                  | MIN  | TYP  | MAX  | UNIT |

|------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| INPUT VOL                    | TAGE AND CURRENT                                       |                                                                           |                                                                            |      |      |      |      |

| V <sub>DS_Clamp</sub><br>CHx | V <sub>DS</sub> clamp voltage                          | FET current = 10 mA, V <sub>S</sub>                                       | = 24 V                                                                     | 40   | 44   | 50   | V    |

| V <sub>DS_Clamp</sub><br>CHx | V <sub>DS</sub> clamp voltage                          | FET current = 10 mA, V <sub>S</sub>                                       | = 19 V                                                                     | 40   | 44   | 50   | V    |

| V <sub>DS_Clamp</sub><br>CHx | V <sub>DS</sub> clamp voltage                          | FET current = 10 mA, V <sub>S</sub>                                       | = 10 V                                                                     | 33   | 37   | 41   | V    |

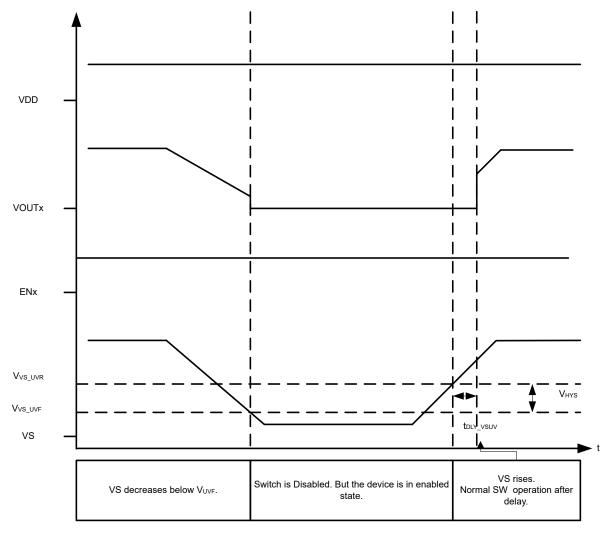

| V <sub>S_UVPF</sub>          | V <sub>S</sub> undervoltage protection falling         | Measured with respect<br>to the GND pin of the<br>device, All channels ON | Output FETs turned off at VS less than this threshold.                     | 8.6  | 9    | 9.3  | V    |

| V <sub>S_UVPR</sub>          | V <sub>S</sub> undervoltage protection recovery rising | Measured with respect<br>to the GND pin of the<br>device, All channels ON | Output FETs turned ON at VS more than this threshold.                      | 9.5  | 10   | 10.3 | V    |

| V <sub>S_UVPRH</sub>         | V <sub>S</sub> undervoltage protection deglitch time   | Time from triggering the U                                                | JVP fault to FET turn-off                                                  | 15   | 20   | 25   | μs   |

| V <sub>S_UVWF</sub>          | V <sub>S</sub> undervoltage warning falling            | Measured with respect to the GND pin of the device,                       | Reported in VS_UV_WRN register bit when below this threshold               | 12   | 12.5 | 13.5 | V    |

| V <sub>S_UVWR</sub>          | V <sub>S</sub> undervoltage warning recovery rising    | Measured with respect to the GND pin of the device,                       | VS_UV_WRN register bit cleared when below this threshold and register read | 11.2 | 13.5 | 15.8 | V    |

| V <sub>S_UVLOF</sub>         | V <sub>S</sub> undervoltage lockout falling            | Measured with respect to the GND pin of the device                        | Device will hit POR and READY pin will be pulled low                       |      | 3.0  |      | V    |

| V <sub>S,UVLOR</sub>         | V <sub>S</sub> undervoltage lockout rising             | Measured with respect to the GND pin of the device                        | READY pin will go high                                                     | 2.7  | 3    | 3.3  | V    |

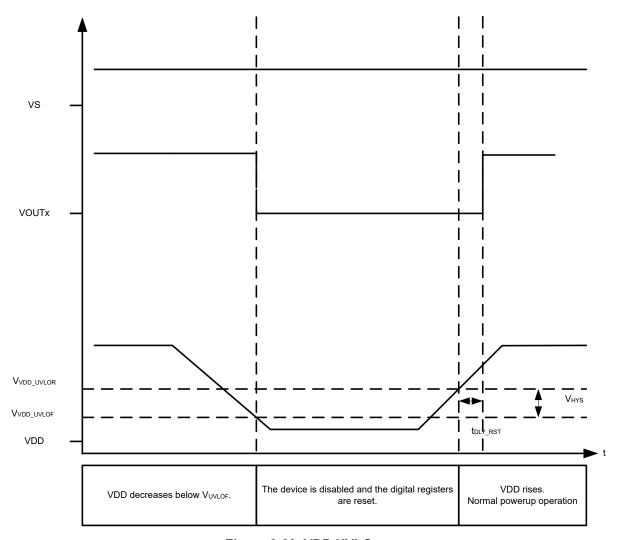

| V <sub>DD,UVLOF</sub>        | V <sub>DD</sub> undervoltage lockout falling           | Measured with respect to                                                  | the GND pin of the device                                                  | 2.7  | 2.8  | 2.9  | V    |

| V <sub>DD,UVLOR</sub>        | V <sub>DD</sub> undervoltage lockout rising            | Measured with respect to                                                  | the GND pin of the device                                                  | 2.8  | 2.88 | 2.98 | V    |

| 11                           | Continuous load current,                               | All channels enabled, T <sub>AN</sub>                                     | <sub>1B</sub> = 85°C                                                       |      | 1.6  |      | Α    |

| IL <sub>NOM</sub>            | per channel                                            | Two channels enabled, T                                                   | <sub>AMB</sub> = 85°C                                                      |      | 2.5  |      | Α    |

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

$V_{VS}$  = 11 V to 36 V,  $V_{VDD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 125°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                                    | TEST CO                                                                                                                                                                                                               | NDITIONS                                            | MIN | TYP | MAX  | UNIT |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|------|------|

| I <sub>OUT,LEAKX</sub> | Leakage current from OUT to GND in OFF state                                                                                                 | Vs = VOUT < 36 V, Switch<br>disabled, measured into the                                                                                                                                                               | 3                                                   |     |     | 40   | μА   |

| I <sub>OUT(OFF)</sub>  | Output leakage current (per channel)                                                                                                         | VS <= 36 V, V <sub>OUT</sub> = 0<br>Channel disabled, diagnos                                                                                                                                                         | stics disabled Tj <= 125°C                          | 0   | 0.8 | 10   | μΑ   |

| VDD I <sub>Q</sub>     | V <sub>DD</sub> quiescent current,<br>SCLK ON, all<br>diagnostics disabled,<br>(WB_OFF, WB_ON,<br>SHRT_VS, ADC)<br>external VDD              | $V_S \le 36 \text{ V}, V_{DD} = 5.5 \text{ V}$<br>All channels enabled, $I_{OU}$                                                                                                                                      | <sub>Tx</sub> = 0 A                                 |     | 1.3 | 1.6  | mA   |

| VDD I <sub>Q</sub>     | V <sub>DD</sub> quiescent current,<br>SCLK ON, all<br>diagnostics disabled,<br>(WB_OFF, WB_ON,<br>SHRT_VS, ADC)<br>external VDD              | $V_S \le 36 \text{ V}, V_{DD} = 3.0 \text{ V}$<br>All channels enabled, $I_{OU}$                                                                                                                                      | <sub>Tx</sub> = 0 A                                 |     | 1   | 1.2  | mA   |

| VDD I <sub>Q</sub>     | VDD quiescent current,<br>SCLK off, all diagnostics<br>disabled ((WB_OFF,<br>WB_ON, SHRT_VS),<br>ADC enabled and<br>converting, external VDD | $V_S \le 36 \text{ V}, V_{DD} = 5.5 \text{ V}$<br>All channels enabled, $I_{OU}$                                                                                                                                      | <sub>Tx</sub> = 0 A                                 |     | 1.2 | 1.6  | mA   |

| VS I <sub>Q</sub>      | V <sub>S</sub> quiescent current,<br>SCLK off, all<br>diagnostics disabled,<br>(WB_OFF, WB_ON,<br>SHRT_VS, ADC) internal<br>VDD              | V <sub>S</sub> ≤ 36 V,<br>All channels enabled, I <sub>OUTx</sub> = 0 A                                                                                                                                               |                                                     |     | 2.8 | 3.2  | mA   |

| VS I <sub>Q</sub>      | V <sub>S</sub> quiescent current,<br>SCLK off, all diagnostics<br>(WB_OFF, WB_ON,<br>SHRT_VS, ADC)<br>enabled, external VDD                  | $V_{\rm S} \le 36$ V, $V_{\rm DD} = 3.0$ V<br>All channels enabled, $I_{\rm OU}$                                                                                                                                      | <sub>Tx</sub> = 0 A                                 |     | 1.7 | 2.5  | mA   |

| VS I <sub>Q</sub>      | V <sub>S</sub> quiescent current,<br>SCLK off, all diagnostics<br>(WB_OFF, WB_ON,<br>SHRT_VS, ADC)<br>disabled, RCB enabled,<br>external VDD | $V_S \le 36 \text{ V}, V_{DD} = 3.0 \text{ V}$<br>All channels enabled, $I_{OU}$                                                                                                                                      | <sub>Tx</sub> = 0 A                                 |     | 1.4 | 2.45 | mA   |

| I <sub>leak_LG</sub>   | Leakage current out of<br>the output pins with the<br>GND of IC disconnected,<br>Load ground connected<br>to supply ground                   | V <sub>S</sub> ≤ 30 V, V <sub>DD</sub> = 5.5 V, RL<br>All channels enabled                                                                                                                                            | = 24 Ω                                              |     | 0.8 | 0.9  | mA   |

| RON CHAP               | RACTERISTICS                                                                                                                                 |                                                                                                                                                                                                                       |                                                     |     |     |      |      |

|                        | On-resistance<br>(Includes MOSFET and                                                                                                        | 10 V ≤ V <sub>S</sub> ≤ 36 V, I <sub>OUT1</sub> = I <sub>OUT2</sub> = 200 mA                                                                                                                                          | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 125°C     |     | 72  | 110  | mΩ   |

| R <sub>ON</sub>        | package)                                                                                                                                     | -0012 -00 ////                                                                                                                                                                                                        |                                                     |     |     | 110  | mΩ   |

| ···ON                  | On-resistance when 2 channels are paralleled (Includes MOSFET and package)                                                                   | $ \begin{aligned} &10 \text{ V} \leq \text{V}_{\text{S}} \leq 36 \text{ V, I}_{\text{OUT1}} = \\ &\text{I}_{\text{OUT2}} > 200 \text{ mA.} \\ &\text{V}_{\text{OUT1}} \text{ tied to V}_{\text{OUT2}} \end{aligned} $ | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 125°C     |     | 33  | 55   | mΩ   |

| VDD_REG                | CHARACTERISTICS                                                                                                                              |                                                                                                                                                                                                                       |                                                     |     |     |      |      |

| $V_{VDD}$              | VDD Output voltage<br>(Internal regulator<br>enabled)                                                                                        | 6 V ≤ V <sub>S</sub> ≤ 36 V, I <sub>VDD</sub> < 20 mA                                                                                                                                                                 | Includes load and line regulation across the range. | 3.1 | 3.3 | 3.6  | V    |

|                        | 1                                                                                                                                            | 1                                                                                                                                                                                                                     | 1                                                   | l   |     |      |      |

$V_{VS}$  = 11 V to 36 V,  $V_{VDD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 125°C (unless otherwise noted)

|                        | PARAMETER                                                        | TEST CO                                                                                                                                                                                                  | NDITIONS                   | MIN   | TYP   | MAX   | UNIT |

|------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|-------|-------|------|

| LR <sub>VDD</sub>      | Load regulation of internal VDD regulator when enabled           | 6 V ≤ V <sub>S</sub> ≤ 36 V, I <sub>VDD</sub> < 20                                                                                                                                                       | mA                         |       |       | 0.95  | V/A  |

| LR <sub>tran_VDD</sub> | Load transient regulation of internal VDD regulator when enabled | $6 \text{ V} \le \text{V}_{\text{S}} \le 36 \text{ V}, \text{I}_{\text{VDD}}$ <step 10="" 15="" 5="" from="" in="" ma="" td="" to="" μs<=""><td>1 uF</td><td></td><td></td><td>10</td><td>mV</td></step> | 1 uF                       |       |       | 10    | mV   |

| CL_VDD                 | Current Limit of internal regulator                              | 6 V ≤ V <sub>S</sub> ≤ 36 V                                                                                                                                                                              |                            | 25    |       | 50    | mA   |

| CURRENT                | SENSE CHARACTERISTIC                                             | CS                                                                                                                                                                                                       |                            | '     |       | '     |      |

| I <sub>SNSI</sub> CHx  | Current sense ratio I <sub>OUTx</sub> / I <sub>SNS</sub>         | I <sub>OUTX</sub> = 1 A, Range = 2.4<br>A                                                                                                                                                                | I <sub>OUTX</sub> = 1 A    |       | 1160  |       |      |

|                        |                                                                  |                                                                                                                                                                                                          | I <sub>OUTx</sub> = 2 A    | 1.69  | 1.73  | 0.95  | mA   |

| <sub>SNSI</sub> CHx    | CHx Current sense current                                        |                                                                                                                                                                                                          | I <sub>OUT1</sub> = 1 A    | 0.834 | 0.862 | 0.890 | mA   |

| lawa CHy               |                                                                  | Current Sense Diagnostic Enabled, $R_{SNS}$ = 1k $\Omega$                                                                                                                                                | I <sub>OUT1</sub> = 500 mA | 0.410 | 0.424 | 0.45  | mA   |

| ISNSI CI IX            |                                                                  |                                                                                                                                                                                                          | I <sub>OUT1</sub> = 200 mA | 0.151 | 0.168 | 0.184 | mA   |

|                        |                                                                  |                                                                                                                                                                                                          | I <sub>OUT1</sub> = 100 mA | 0.068 | 0.081 | 0.092 | mA   |

|                        |                                                                  |                                                                                                                                                                                                          | I <sub>OUT1</sub> = 50 mA  | 0.02  | 0.037 | 0.054 | mA   |

| I <sub>SNSI</sub> CHx  | CHx Current sense current                                        | Current Sense Diagnostic Enabled, $R_{SNS}$ = 1k $\Omega$                                                                                                                                                | I <sub>OUT1</sub> = 20 mA  | 0.005 | 0.010 | 0.028 | mA   |

| I <sub>SNSI</sub> CHx  | CHx Current sense current                                        | Current Sense Diagnostic Enabled, $R_{SNS} = 1k\Omega$                                                                                                                                                   | I <sub>OUT1</sub> = 10 mA  | 0.002 | 0.005 | 0.008 | mA   |

| I <sub>SNSI</sub> CHx  | CHx Current sense current                                        | Current Sense Diagnostic Enabled, $R_{SNS} = 1k\Omega$                                                                                                                                                   | I <sub>OUT1</sub> = 5 mA   | 0.000 | 0.002 | 0.004 | mA   |

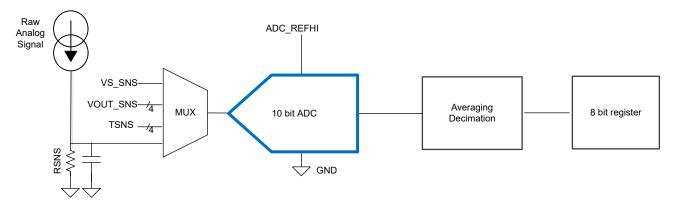

| ADC Perfo              | mance Characteristics                                            |                                                                                                                                                                                                          |                            |       |       |       |      |

| V <sub>ADCEFfHI</sub>  | ADC refernce voltage                                             |                                                                                                                                                                                                          |                            | 2.72  | 2.8   | 2.85  | V    |

| Tconv1                 | ADC sample update time in each measurement                       |                                                                                                                                                                                                          |                            |       |       | 128   | μs   |

| SNS CHAR               | ACTERISTICS                                                      |                                                                                                                                                                                                          |                            |       |       |       |      |

| T <sub>SNSout1</sub>   | T <sub>SNS</sub> output                                          | T <sub>J</sub> = -40°C                                                                                                                                                                                   |                            |       | 2.57  |       | V    |

| T <sub>SNSout2</sub>   | T <sub>SNS</sub> output                                          | T <sub>J</sub> = 25°C                                                                                                                                                                                    |                            |       | 2.17  |       | V    |

| T <sub>SNSout3</sub>   | T <sub>SNS</sub> output                                          | T <sub>J</sub> = 125°C                                                                                                                                                                                   |                            |       | 1.55  |       | V    |

| VOUT <sub>SNS</sub> _  | VOUT <sub>SNS</sub> output                                       | VOUT_CHx = 20 V                                                                                                                                                                                          |                            |       | 1.87  |       | V    |

| CURRENT                | LIMIT CHARACTERISTICS                                            | 3                                                                                                                                                                                                        |                            | •     |       | '     |      |

Product Folder Links: TPS274C65

$V_{VS}$  = 11 V to 36 V,  $V_{VDD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 125°C (unless otherwise noted)

|          | PARAMETER                                                               | TEST CO                                                                      | NDITIONS                                                     | MIN  | TYP  | MAX  | UNIT |

|----------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

|          |                                                                         |                                                                              | Setting = 2.45 A                                             | 2.06 | 2.45 | 2.84 | Α    |

|          |                                                                         |                                                                              | Setting = 2.26 A                                             | 2.01 | 2.26 | 2.88 | Α    |

|          |                                                                         |                                                                              | Setting = 2.07 A                                             | 1.74 | 2.07 | 2.4  | Α    |

|          |                                                                         |                                                                              | Setting = 1.9 A                                              | 1.6  | 1.9  | 2.3  | Α    |

|          |                                                                         |                                                                              | Setting =1.71 A                                              | 1.42 | 1.71 | 1.94 | Α    |

|          |                                                                         |                                                                              | Setting = 1.52 A                                             | 1.2  | 1.52 | 1.78 | Α    |

|          |                                                                         | Demillate designment et                                                      | Setting = 1.33 A                                             | 1.06 | 1.33 | 1.6  | Α    |

|          | CHx I <sub>CL</sub> current limitation                                  | Regulated current at short circuit RL <                                      | Setting = 1.15 A                                             | 0.94 | 1.15 | 1.36 | Α    |

| CLx      | level, H version                                                        | 200 mohms when                                                               | Setting = 0.96 A                                             | 0.78 | 0.96 | 1.1  | Α    |

|          |                                                                         | Enabled. VDD = 3.3 V.                                                        | Setting = 0.86 A                                             | 0.72 | 0.86 | 1.02 | Α    |

|          |                                                                         |                                                                              | Setting = 0.76 A                                             | 0.64 | 0.76 | 0.88 | Α    |

|          |                                                                         |                                                                              | Setting = 0.67 A                                             | 0.53 | 0.67 | 0.78 | Α    |

|          |                                                                         |                                                                              | Setting = 0.57 A                                             | 0.47 | 0.57 | 0.65 | Α    |

|          |                                                                         |                                                                              | Setting = 0.48 A                                             | 0.4  | 0.48 | 0.55 | Α    |

|          |                                                                         |                                                                              | Setting = 0.38 A                                             | 0.3  | 0.38 | 0.45 | Α    |

|          |                                                                         |                                                                              | Setting = 0.29 A                                             | 0.22 | 0.29 | 0.39 | Α    |

|          |                                                                         | Regulated current at                                                         | Setting = 2.2 A                                              | 1.85 | 2.2  | 2.55 | Α    |

|          |                                                                         |                                                                              | Setting = 1.9 A                                              | 1.6  | 1.9  | 2.3  | Α    |

|          |                                                                         |                                                                              | Setting = 1.75 A                                             | 1.5  | 1.75 | 2.05 | Α    |

|          |                                                                         |                                                                              | Setting = 1.6 A                                              | 1.35 | 1.6  | 1.85 | A    |

|          |                                                                         |                                                                              | Setting =1.5 A                                               | 1.19 | 1.5  | 1.75 | Α    |

|          |                                                                         |                                                                              | Setting = 1.25 A                                             | 1    | 1.25 | 1.5  | Α    |

|          |                                                                         |                                                                              | Setting = 1.1 A                                              | 0.9  | 1.1  | 1.3  | A    |

|          |                                                                         |                                                                              | Setting = 1 A                                                | 0.85 | 1    | 1.15 | A    |

| CLx      | level                                                                   | 200 mohms when                                                               | Setting = 0.85 A                                             | 0.72 | 0.85 | 1    | Α    |

|          |                                                                         | Enabled. VDD = 3.3 V.                                                        | Setting = 0.72 A                                             | 0.62 | 0.72 | 0.82 | A    |

|          |                                                                         |                                                                              | Setting = 0.67 A                                             | 0.53 | 0.67 | 0.78 | Α    |

|          |                                                                         |                                                                              | Setting = 0.56 A                                             | 0.47 | 0.56 | 0.63 | Α    |

|          |                                                                         |                                                                              | Setting = 0.48 A                                             | 0.4  | 0.48 | 0.55 | A    |

|          |                                                                         |                                                                              | Setting = 0.4 A                                              | 0.32 | 0.4  | 0.47 | Α    |

|          |                                                                         |                                                                              | Setting = 0.33 A                                             | 0.26 | 0.33 | 0.39 | Α    |

|          |                                                                         |                                                                              | Setting = 0.25 A                                             | 0.19 | 0.25 | 0.33 | A    |

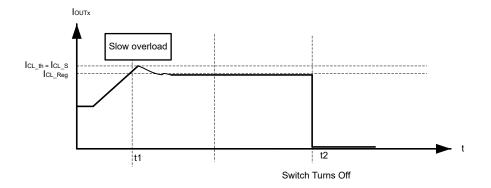

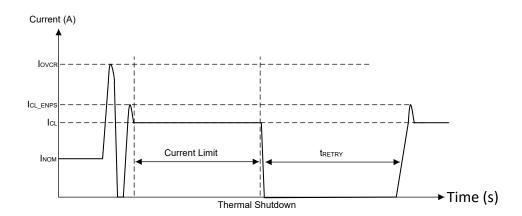

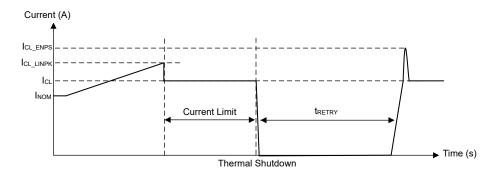

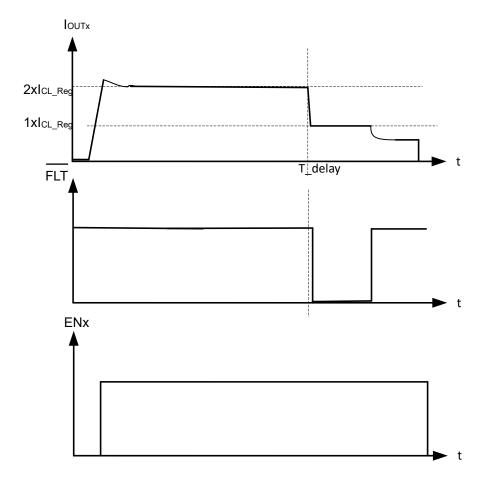

| CL_LINPK | Overcurrent limit threshold                                             | Threshold before current limiting - Overload condition                       | Setting = 2.2 A V <sub>VS</sub> – V <sub>VOUT</sub> < 1 V    |      |      | 2.75 | Α    |

| CL_LINPK | Overcurrent limit threshold                                             | Threshold before current limiting - Overload Conditions                      | Setting = 0.85 A V <sub>VS</sub> -<br>V <sub>VOUT</sub> < 1V |      |      | 1.1  | Α    |

| CL_PK1   | Peak current before regulation while enabling switch into 100 mohm load | T <sub>J</sub> = -40°C to 125°C<br>VS = 24 V, Minimum<br>inductance = 2.2 μH | Settting = 2.2 A                                             |      |      | 10   | А    |

| CL_PK2   | Peak current threshold<br>when short is applied<br>while switch enabled | T <sub>J</sub> = -40°C to 125°C<br>VS = 24 V, Minimum<br>inductance = 2.2 μH | Settting = 2.2 A                                             |      |      | 9.4  | Α    |

$V_{VS}$  = 11 V to 36 V,  $V_{VDD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 125°C (unless otherwise noted)

|                              | PARAMETER                                                                                    | TEST CO                                                                               | NDITIONS                   | MIN                       | TYP  | MAX  | UNIT |

|------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------|---------------------------|------|------|------|

| I <sub>CL_P</sub>            | Parallel I <sub>CL</sub> Current<br>Limitation Level                                         | Regulated current at<br>short circuit RL < 200<br>mohms when Enabled                  | Settting = 2.2 A           |                           | 4.3  |      | Α    |

| I <sub>CL_PK1_P</sub>        | Paralled Peak current enabling into permanent short                                          | $T_J = -40^{\circ}\text{C}$ to 125°C<br>VS = 24V, Minimum<br>inductance = 2.2 $\mu$ H | Settting = 2.2 A           |                           |      | 6.4  | Α    |

| I <sub>CL,PARALLE</sub><br>L | Paralled Channels<br>Current Limit Accuracy<br>Multiplier                                    | V <sub>OUT1</sub> tied to V <sub>OUT2</sub> ,<br>parallel channel mode<br>enabled     | Settting = 2.2 A           | 0.9                       |      | 1.1  |      |

| FAULT CHA                    | RACTERISTICS                                                                                 |                                                                                       |                            | ·                         |      |      |      |

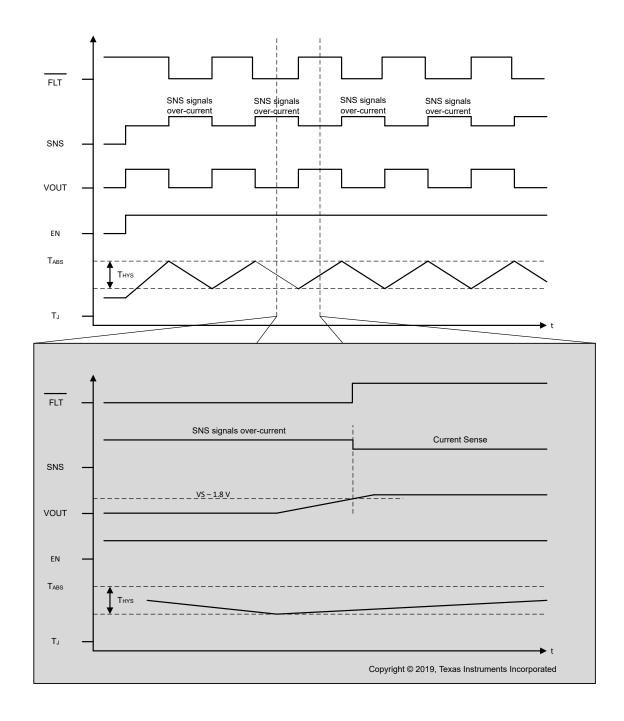

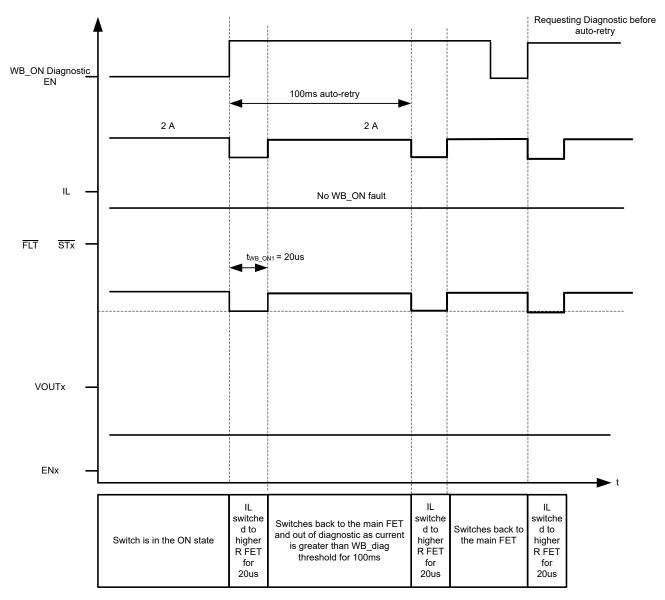

| I <sub>WB_ON_TH</sub>        | Wire-break (WB) or<br>Open-load (OL) detection<br>on-state threshold                         | Switch enabled, WB_ON_<br>WB_ON_TH_= 000                                              | CHx = enabled              | 0.38                      | 0.49 | 0.61 | mA   |

| $I_{WB\_OFF}$                | Off State Wirebreak or<br>Open-load (OL) detection<br>internal pullup current                | Switch disabled, WB_OFF<br>WB_PU=00                                                   | CHx = enabled              | 38                        | 51   | 64   | μΑ   |

| V <sub>SHRT_VS_T</sub><br>H  | Off state short to VS detection voltage                                                      | Channel Disabled, off-statenabled                                                     | e short_VS diagnostics     |                           | 12.0 |      | V    |

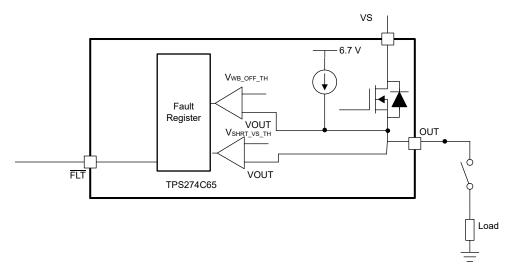

| V <sub>WB_OFF_P</sub><br>U   | Off state WireBreak<br>(WB) or Open-load (OL)<br>detection pull up current<br>source voltage | Channel Disabled, off-state wire-break diagnostics enabled                            |                            |                           | 6.7  |      | ٧    |

| V <sub>WB_OFF_T</sub><br>H   | Off state WireBreak<br>(WB) or Open-load (OL)<br>detection voltage                           | Channel Disabled, off-state wire-break diagnostics enabled                            |                            | 5.6                       | 6    | 6.5  | V    |

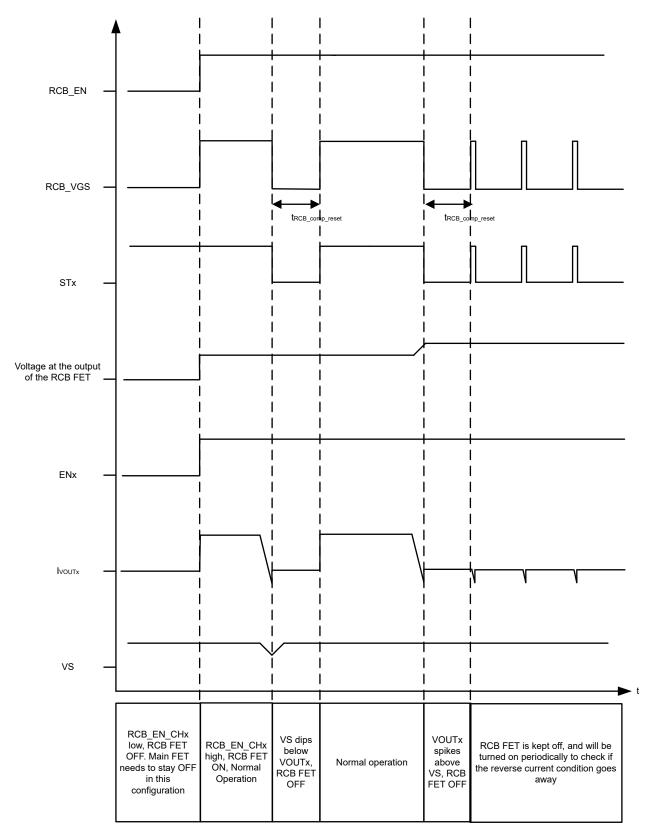

| t <sub>RCB_DGL</sub>         | CHx RCB Fault Deglitch time                                                                  | Channel Enabled, RCB enabled                                                          |                            |                           | 1.2  |      | ms   |

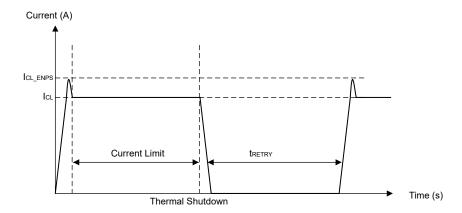

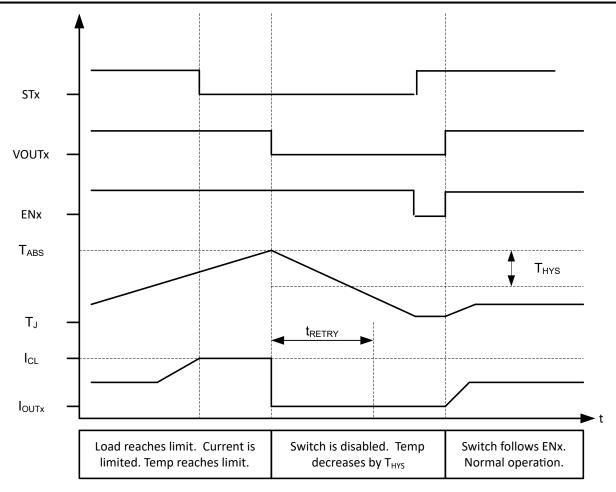

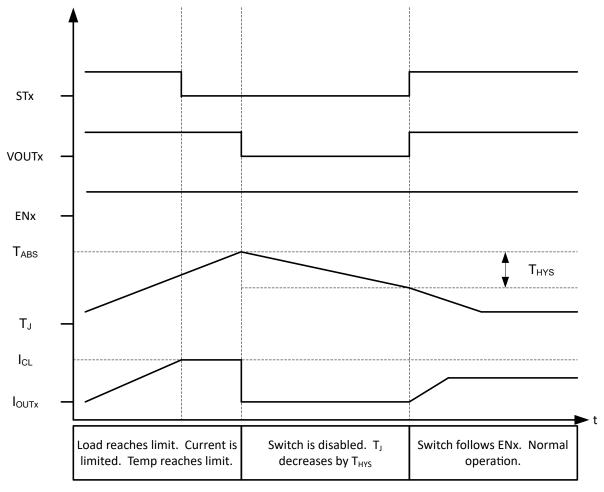

| T <sub>ABS</sub>             | Thermal shutdown                                                                             |                                                                                       |                            | 160                       | 185  | 210  | °C   |

| T <sub>OTW</sub>             | Thermal shutdown warning                                                                     |                                                                                       |                            | 110                       | 130  | 150  | °C   |

| T <sub>HYS</sub>             | Thermal shutdown hysteresis                                                                  |                                                                                       |                            | 20                        | 27   | 35   | °C   |

| V <sub>ol_FLT</sub>          | Fault low-output voltage                                                                     | I <sub>FLT</sub> = 2 mA, sink current ir                                              | nto the pin                |                           |      | 0.4  | V    |

| t <sub>RETRY</sub>           | Retry time                                                                                   | Time from thermal shutdo                                                              | wn until switch re-enable. |                           | 0.6  |      | ms   |

| t <sub>RCB_F</sub>           | Reverse current protection comparator delay                                                  | Time from VS – VOUT < 5 gate off                                                      | 0 mV overdrive to FET      | 1.6                       | 2    | 2.4  | μs   |

| $V_{RCB_{F}}$                | V(VS) – V(OUT)<br>threshold for<br>reverse protection<br>comparator,<br>falling              |                                                                                       |                            | -104                      | -64  | -23  | mV   |

| t <sub>RCB_comp_r</sub>      | RCB internal comparator reset interval                                                       |                                                                                       |                            |                           | 100  |      | ms   |

| V <sub>RCB_pu</sub>          | RCBx FET gate voltage                                                                        |                                                                                       |                            |                           | 6    | 7    | V    |

| V <sub>RCB_R</sub>           | V(VS) – V(OUT)<br>threshold for<br>reverse protection<br>comparator,<br>rising               |                                                                                       |                            | 28                        | 45   | 58   | mV   |

| DIGITAL IN                   | PUT PIN CHARACTERIST                                                                         | IC                                                                                    |                            |                           |      |      |      |

| V <sub>IH, DIG</sub>         | DIG pin Input voltage<br>high-level                                                          | 3.0 V ≤ VDD ≤ 5.5 V                                                                   |                            | 0.7 ×<br>V <sub>VDD</sub> |      |      | V    |

$V_{VS}$  = 11 V to 36 V,  $V_{VDD}$  = 3.0 V to 5.5 V,  $T_{J}$  = -40°C to 125°C (unless otherwise noted)

|                        | PARAMETER                                      | TEST CONDITIONS                                                          | MIN  | TYP  | MAX                       | UNIT |

|------------------------|------------------------------------------------|--------------------------------------------------------------------------|------|------|---------------------------|------|

| V <sub>IL, DIG</sub>   | DIG pin Input voltage low-level                | 3.0 V ≤ VDD ≤ 5.5 V                                                      |      |      | 0.3 ×<br>V <sub>VDD</sub> | V    |

| R <sub>REG_EN</sub>    | Internal pullup resistance for REG_EN pin      |                                                                          |      | 1    |                           | ΜΩ   |

| R <sub>DIGx</sub>      | Internal pulldown resistor                     |                                                                          | 0.7  | 1    | 2.0                       | МΩ   |

| I <sub>IH, DIG</sub>   | Input current high-level                       | V <sub>DIG</sub> = 5 V                                                   |      | 5    |                           | μA   |

| DIGITAL O              | UTPUT PIN CHARACTERI                           | STICS                                                                    |      |      |                           |      |

| V <sub>OH</sub>        | Output Logic High<br>Voltage Drop              | READY Pin current = -4 mA                                                | -0.5 |      |                           | V    |

| V <sub>OL_SDO</sub>    | Output Logic Low Voltage                       | SDO Pin current = -4 mA                                                  |      |      | 0.2                       | V    |

| V <sub>OL_FLT</sub>    | Output Logic Low Voltage                       | FLT Pin current = -4 mA                                                  |      |      | 0.4                       | V    |

| LED DRIVE              | R CHARACTERISTICS                              |                                                                          |      |      |                           |      |

| V <sub>drop_HL14</sub> | LED High Side / Low side drop Channels 1 and 4 | I_LED (average current over 4 phases) = 4 mA, LED switch current = 16 mA |      |      | 0.2                       | V    |

| V <sub>drop_HL23</sub> | LED High Side / Low side drop Channels 2 and 3 | I_LED (average current over 4 phases) = 4 mA, LED switch current = 32 mA |      |      | 0.2                       | V    |

| f <sub>PWM_LED</sub>   | LED driver PWM frequency                       |                                                                          |      | 1000 |                           | Hz   |

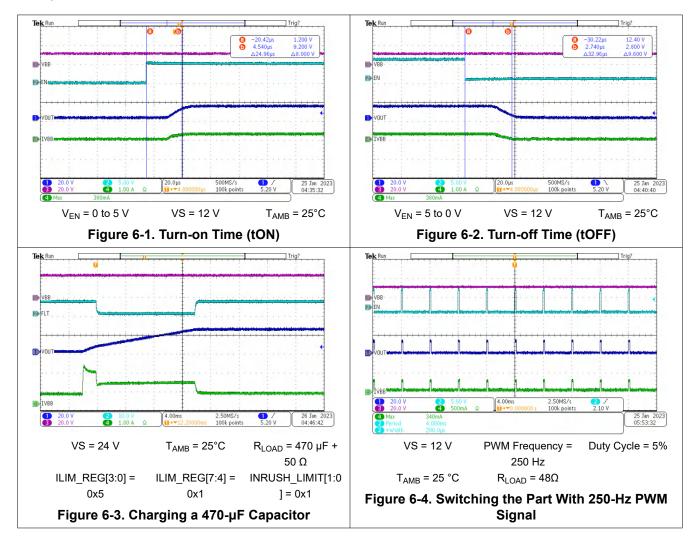

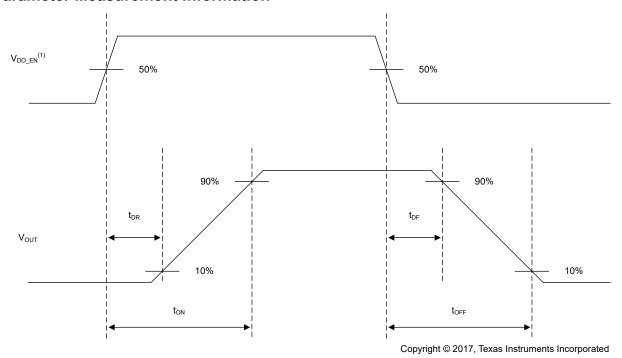

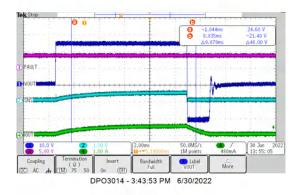

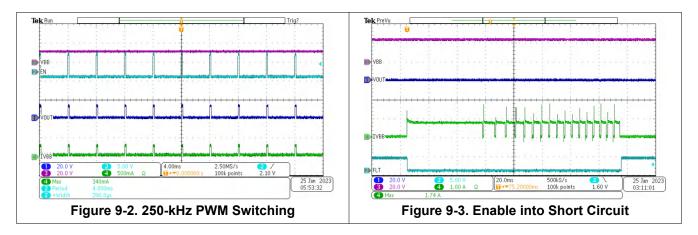

# **6.6 Switching Characteristics**

$V_S = 6 \text{ V to } 36 \text{ V}, T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C (unless otherwise noted)}$

|                                    | DADAMETED                               | TEST COMPITIONS                                                                          | MAINI | TVD       | MAY |      |

|------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|-------|-----------|-----|------|

|                                    | PARAMETER                               | TEST CONDITIONS                                                                          | MIN   | TYP       | MAX | UNIT |

| t <sub>DR</sub>                    | CHx Turnon delay time                   | $V_S$ = 24 V, $R_L$ = 48 $\Omega$ 50% of EN to 10% of VOUT                               | 5     | 18        | 25  | μs   |

| t <sub>DF</sub>                    | CHx Turnoff delay time                  | $V_S$ = 24 V, $R_L$ = 48 $\Omega$ 50% of EN to 90% of VOUT                               | 16    | 24        | 33  | μs   |

| SR2 <sub>R</sub>                   | VOUTx rising slew rate                  | $V_S$ = 24 V, 25% to 75% of $V_{OUT}$ , $R_L$ = 48 $\Omega$ ,                            | 1     | 1.6       | 2.2 | V/µs |

| SR2 <sub>F</sub>                   | VOUTx falling slew rate                 | $V_S$ = 24 V, 75% to 25% of $V_{OUT}$ , $R_L$ = 48 $\Omega$ ,                            | 1     | 1.4       | 1.8 | V/µs |

| f <sub>max</sub>                   | Maximum PWM frequency                   |                                                                                          |       |           | 1   | kHz  |

| t <sub>ON</sub>                    | CHx Turnon time                         | $V_S$ = 24 V, $R_L$ = 48 $\Omega$ 50% of EN to 90% of VOUT                               |       | 33        | 42  | μs   |

| t <sub>OFF</sub>                   | CHx Turnoff time                        | $V_S$ = 24 V, $R_L$ = 48 $\Omega$ 50% of EN to 10% of VOUT                               |       | 46        | 57  | μs   |

| t <sub>ON</sub> - t <sub>OFF</sub> | CHx Turnon and off matching             | 1ms ON time switch enable pulse $V_{BB}$ = 24 V, $R_{L}$ = 48 $\Omega$                   | -41   | <b>-7</b> | 23  | μs   |

| t <sub>ON</sub> - t <sub>OFF</sub> | CHx Turnon and off matching             | 100-μs OFF time switch enable pulse, $V_S$ = 24 V, $R_L$ = 48 $\Omega$ , $F$ = $f_{max}$ | -41   | <b>-7</b> | 23  | μs   |

| t <sub>ON</sub> - t <sub>OFF</sub> | CHxTurnon and off matching              | 100-μs ON time switch enable pulse, $V_S$ = 24 V, $R_L$ = 48 Ω, $F$ = $f_{max}$          | -41   | -7        | 23  | μs   |

| $\Delta_{PWM}$                     | CHx PWM accuracy - average load current | 200-μs enable pulse, $V_S$ = 24 V, $R_L$ = 48 $\Omega$ F = $f_{max}$                     | -20   |           | 20  | %    |

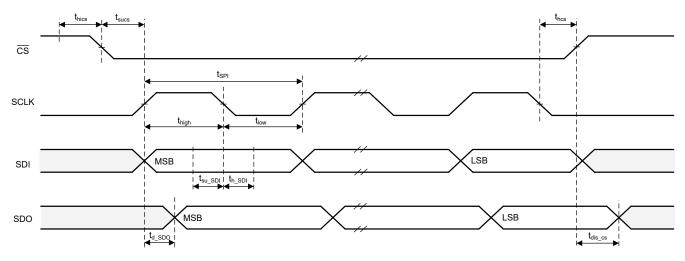

# **6.7 SPI Timing Requirements**

Over operating junction temperature  $T_J$  = -40°C to 125°C and operating  $V_{VS}$  = 2.3 to 36 V (unless otherwise noted).

|                     |                                                                                |                           | MIN | NOM | MAX | UNIT |

|---------------------|--------------------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| t <sub>SPI</sub>    | SPI clock (SCLK) period                                                        | C <sub>SDO</sub> = 30 pF; | 100 |     |     | ns   |

| t <sub>high</sub>   | High time: SCLK logic high-time duration                                       |                           |     |     |     | ns   |

| t <sub>low</sub>    | Low time: SCLK logic low-time duration                                         |                           |     |     |     | ns   |

| t <sub>sucs</sub>   | NCS setup time: Time delay between falling edge of NCS and rising edge of SCLK |                           |     |     |     | ns   |

| t <sub>su_SDI</sub> | SDI setup time: Setup time of SDI before the falling edge of SCLK              |                           |     |     |     | ns   |

| t <sub>h_SDI</sub>  | SDI hold time: Hold time of SDI before the falling edge of SCLK                |                           |     |     |     | ns   |

| t <sub>d_SDO</sub>  | Delay time: Time delay from rising edge of SCLK to data valid at SDO           |                           |     |     | 30  | ns   |

| t <sub>hcs</sub>    | Hold time: Time between the falling edge of SCLK and rising edge of NCS        |                           |     |     |     | ns   |

| t <sub>dis_cs</sub> | nCS disable time, nCS high to SDO high impedance                               |                           |     | 10  |     | ns   |

| t <sub>hics</sub>   | SPI transfer inactive time (time between two transfers) high                   | 500                       |     |     | ns  |      |

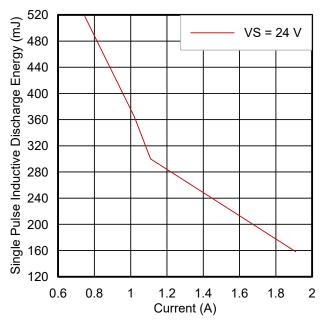

# **6.8 Typical Characteristics**

### 7 Parameter Measurement Information

(1) Rise and fall time of  $V_{\text{DO\_EN}}$  is 100 ns.

Figure 7-1. Switching Characteristics Definitions

Figure 7-2. SPI Timing

# 8 Detailed Description

#### 8.1 Overview

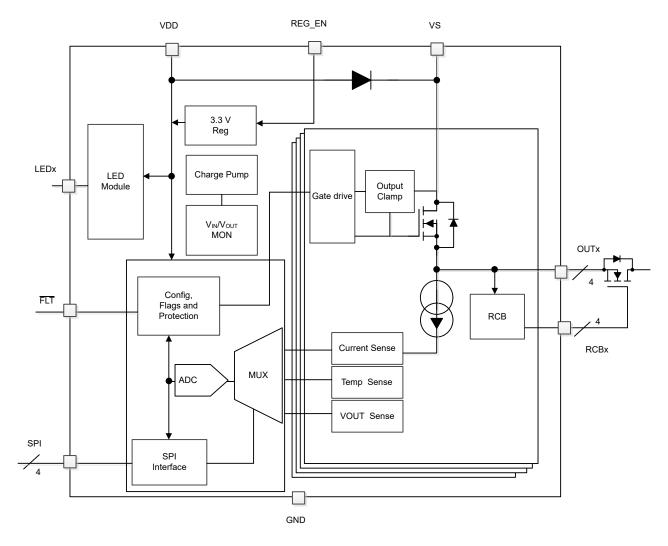

The TPS274C65 device is a quad channel 72-mΩ smart high-side switch intended for use for output ports with protection for 24-V industrial systems. The device is designed to drive a variety of resistive, inductive and capacitive loads. The device integrates various protection features including overload protection through current limiting, thermal protection, short-circuit protection, and reverse current protection. For more details on the protection features, refer to the *Feature Description* and *Application Information* sections of the document.

In addition, the device diagnostics features include a digital per-channel readout of output current, output voltage and FET temperature. The high-accuracy load current sense allows for integration of load measurement features that can enable predictive maintenance for the system by watching for leading indicators of load failures. The device also integrates open load detection in on and off states to enable protection against wire breaks. In addition, the device includes an open drain FLT pin output that indicates device fault states such as short to GND, short to supply, overtemperature, and the other fault states discussed.

# 8.2 Functional Block Diagram

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

#### 8.3 Feature Description

#### 8.3.1 Pin Diagrams

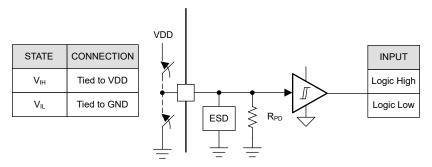

This section presents the I/O structure of all digital input and output pins.

Figure 8-1. Logic Level Input Pin

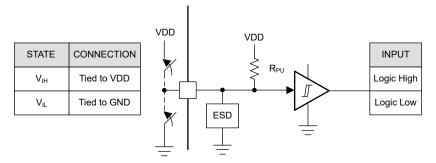

Figure 8-2 shows the input structure for the logic levels pin,  $\overline{\text{CS}}$ . The input can be with a voltage or external resistor.

Figure 8-2. Logic Level Input Pin (CS)

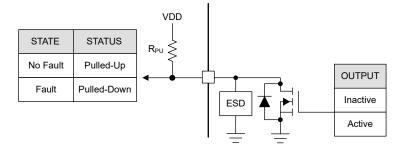

Figure 8-3 shows the structure of the open-drain output pin, FAULT. The open-drain output requires an external pullup resistor to function properly.

Figure 8-3. Open Drain Output Pin (FAULT)

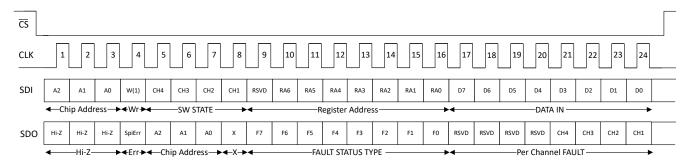

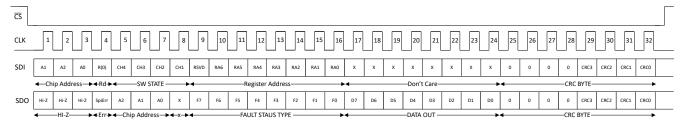

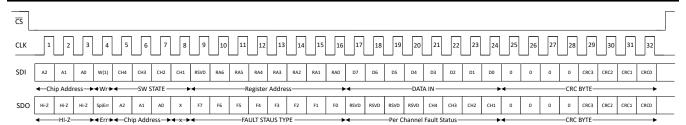

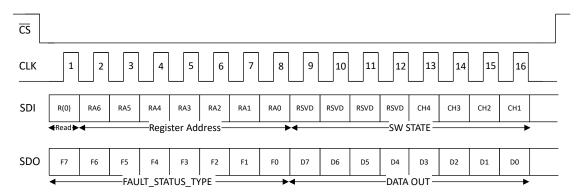

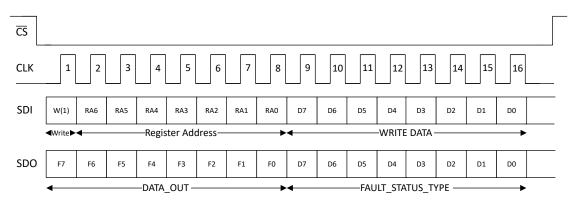

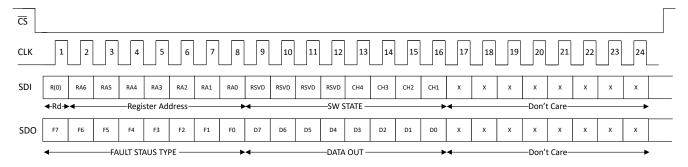

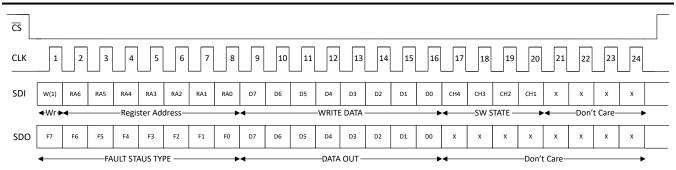

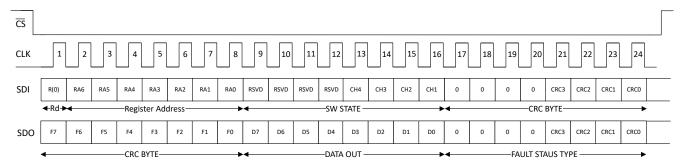

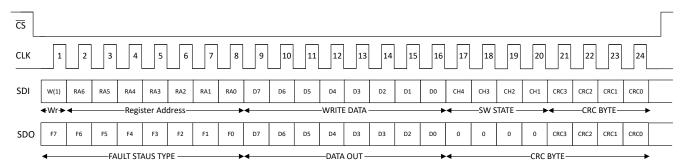

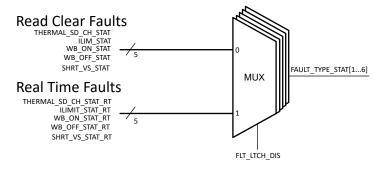

#### 8.3.2 SPI Mode Operation

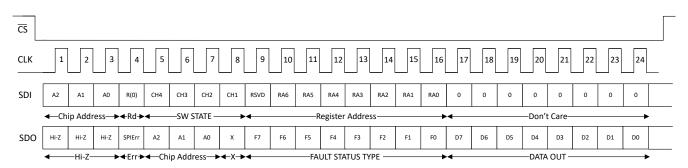

The TPS274C65xS communicates with the host controller through a high-speed SPI serial interface. The interface has three logic inputs: clock (CLK), chip select (CS), serial data in (SDI), and one data out (SDO). The SDO is three-stated when CS is high. The maximum SPI clock rate is 10 MHz. The capacitance at SPI communication pins (CLK, CS, SDI, SDO) needs to be minimized to achieve high SPI communication frequencies.

The device supports both simple daisy chain1 and addressable SPI; the selection of mode is from the DSPI pin. The main advantage of the addressable SPI mode is that diagnostics and configuration is easier. The two

Product Folder Links: TPS274C65

different modes of SPI that is fixed for a given system implementation and cannot be changed dynamically or on the fly. The two modes can be used with or without CRC.

The two modes are described in detail:

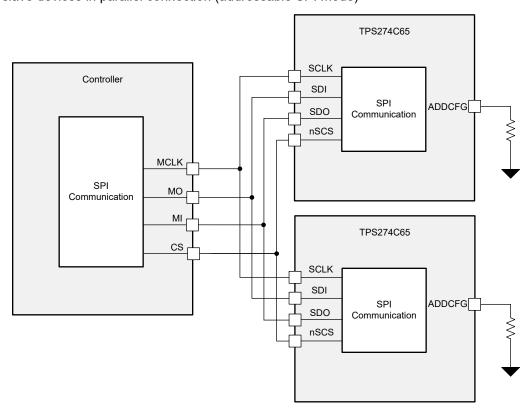

- 1. Addressable SPI mode non-daisy-chained SPI bus with one single/shared CS through chip addressing. Each chip on the shared SPI is assigned an individual chip address with the address set through a resistor (three-bit address for the chip). Addressed SPI (DSPI pin pulled low) allows direct communication with up to eight TPS274C65xS on a shared SPI using a single shared CS signal. The three-bit address of each IC (up to eight on one board) is set with a resistor to GND on this pin Addressed SPI offers the advantage of direct chip access. CRC check is enabled when CRCEN=1. The SPI main device addresses a specific chip by sending the appropriate A2, A1, A0 logic in the first three bits of the SPI read/write command. The TPS274C65xS monitors the SPI address in each SPI read or write cycle and responds appropriately when the address matches the programmed address for that IC. The added advantage is that it is possible to update the SW state register and read the data in the various read only fault and data registers in every read as well as write command frame. The transmission speed will be faster for addressable SPI compared to the daisy chain SPI as the direct data transmission will happen immediately once the address is transmitted.

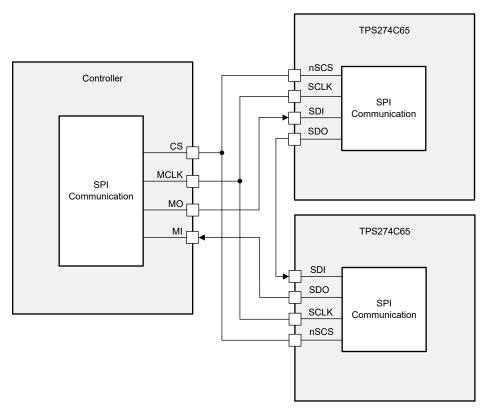

- 2. Daisy chain SPI mode is enabled by setting DSPI pin high. In this mode, multiple TPS274C65xS devices are configured in a serial fashion. In the 16-bit daisy-chain mode, only a minimum read capability and Switch state ON/OFF write is possible- the FAULT status can be read out on each write to the switch ON-OFF register. It is not possible to write to the LED registers or re-configure the device and at the same time update the switch state. However, it is possible to update the SW state register and read the data in the various read only fault and data registers. The 24-bit SPI format allows the write to the SW\_STATE register in every read as well as write command frame as well enable CRC. The speed of the transmission for daisy chain will be depending on the CLK frequency as well as the number of devices connected in series.

The communication between the TPS274C65 IC and the controller or MCU is through a SPI bus in a master-slave configuration. The external MCU is always an SPI master that sends command requests on the SDI pin of the TPS274C65 IC and receives device responses on the SDO pin of the IC. The TPS274C65 device is always an SPI slave device that receives command requests and sends responses (such as status and measured values) to the external MCU over the SDO line. The following lists the characteristics of the SPI:

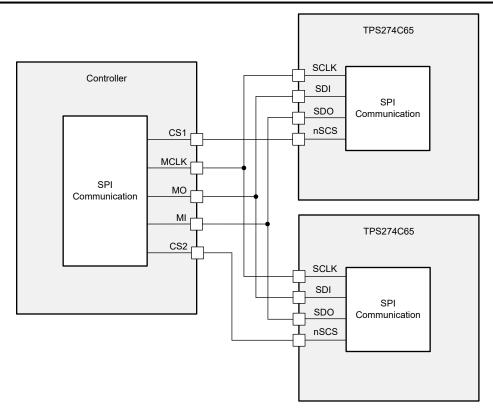

The TPS274C65 device can be connected to the master MCU in the following formats.

One slave device

Figure 8-4. Independent Slave Configuration

Multiple slave devices in parallel connection (addressable SPI mode)

Figure 8-5. Addressable SPI Configuration

www.ti.com

Multiple slave devices in series (daisy chain) connection limited only by the SPI write frame speed requirements.

Figure 8-6. Daisy Chain Configuration

SPI mode controls the following functions.

- ON/OFF control of the switches.

- Disable the diagnostics to reduce the quiescent current consumption.

- Select the channel(s) and measurements for VOUT, IOUT and TEMP.

- Fault management (clearing faults and action/response on fault).

- Watchdog timer the device will generate an error if the SW STATE register has not been successfully written into within the watchdog timeout period. The customer can disable the watchdog feature using the WD EN bit (default is off).

- The current limit protection threshold

Table 8-1. SPI IC Address Configuration

| Resistor Value(kΩ) | ADDCFG Code |

|--------------------|-------------|

| 13.3               | 000         |

| 17.8               | 001         |

| 23.7               | 010         |

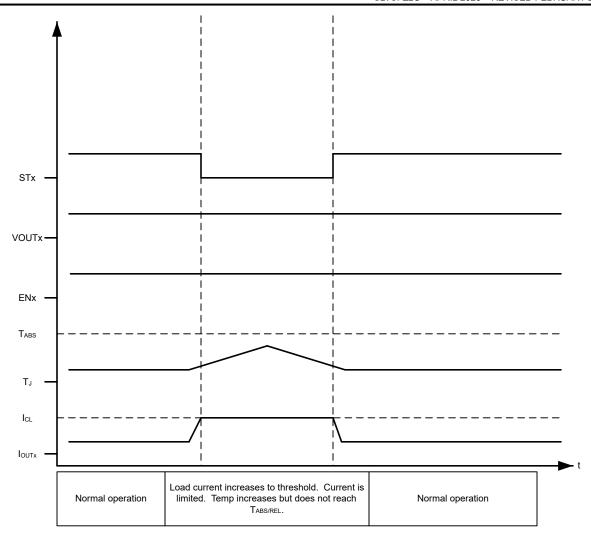

| 31.6               | 011         |