**TPS7H3014-SP** SNVSCE7 - JANUARY 2024

# TPS7H3014-SP Radiation-Hardness-Assured, 14V, 4-Channel Sequencer

## 1 Features

- Radiation performance:

- Radiation hardness assurance (RHA) up to a total ionizing dose (TID) of 100krad(Si)

- Single-event latchup (SEL), single-event burnout (SEB), and single-event gate rupture (SEGR) immune up to linear energy transfer  $(LET) = 75MeV-cm^2/mg$

- Single-event functional interrupt (SEFI) and single-event transient (SET) characterized up to  $LET = 75MeV-cm^2/mg$

- Wide supply IN voltage range (V<sub>IN</sub>): 3V to 14V

- Sequence and monitor up to 4 voltage rails with a single device

- Daisy chain capability for extended channel

- Single resistor programmable global timers for:

- Sequence up and down delay

- Sequence up time to regulation

- Reverse order sequence down

- Precision threshold voltage and hysteresis current

- V<sub>TH SENSEx</sub> of 599mV ±1% across: voltage, temperature, and radiation (TID)

- $I_{HYS\ SENSEx}$  of 24 $\mu A$  ±3% across: voltage, temperature, and radiation (TID)

- Push-Pull outputs with programmable pull-up voltage between 1.6V to 7V

- Global ENx pull-up domain (V<sub>PULL UP1</sub>)

- Common SEQ DONE and PWRGD pull-up domain (V<sub>PULL UP2</sub>)

- FAULT open drain output for monitoring of state machine induced faults

- Available in military (–55°C to 125°C) temperature range

## 2 Applications

- Satellite electrical power system (EPS)

- Control sequence and monitoring for complex digital processors such as: FPGAs, SoCs, AFEs, and power systems for space applications

## 3 Description

The TPS7H3014 is an integrated, 3V to 14V, fourchannel radiation-hardness-assured power-supply sequencer. Channel count can be expanded by connecting multiple devices in a daisy-chain configuration. The device provides sequence up and down control signals for integrated circuits (IC) with active high ("on") inputs. In addition SEQ DONE and PWRGD flags are provided to monitor the sequence and power status of the monitored power tree.

An accurate 599mV ±1% threshold voltage and a 24µA ±3% hysteresis current provide programmable rise and fall monitoring voltages. The rise and fall delay time is globally programmed via a single resistor. Also, a time-to-regulation timer is provided to track the rising voltage on SENSEx. In addition to these features, a FAULT detection pin is incorporated to monitor internally generated faults and provide increased system level reliability for power sequencing space applications. A standard microcircuit drawing (SMD) is available for the QML variant, 5962R23201VXC.

#### **Device Information**

| PART NUMBER (1) | GRADE (2)          | PACKAGE (3)                       |

|-----------------|--------------------|-----------------------------------|

| 5962R23201VXC   | QMLV-RHA           | 22-pin Ceramic (CFP)              |

| TPS7H3014HFT/EM | Engineering sample | 6.21mm x 7.69mm<br>Mass = 415.6mg |

- (1) For additional information view the Section 5 table.

- For additional information about part grade, view SLYB235. (2)

- Dimensions and mass are nominal values.

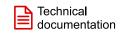

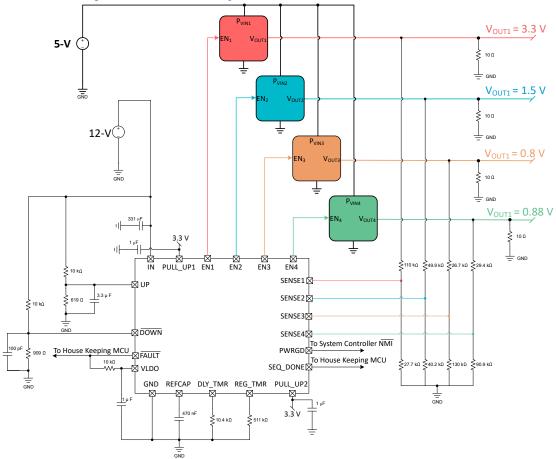

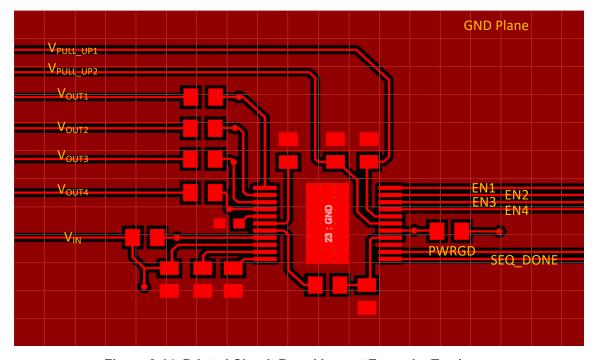

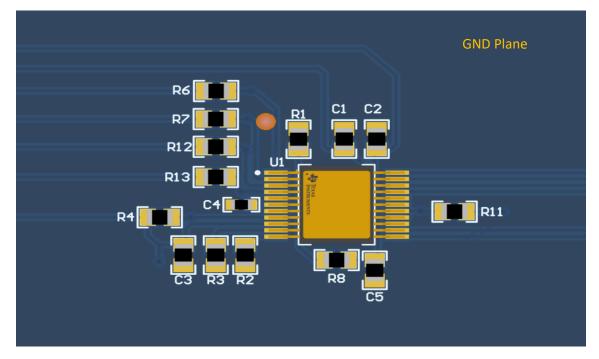

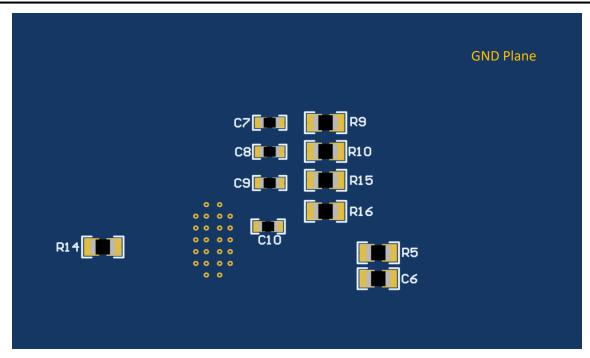

Typical Application

# **Table of Contents**

| 1 Features                           | 1  | 7.3 Feature Description                              | 19 |

|--------------------------------------|----|------------------------------------------------------|----|

| 2 Applications                       | 1  | 7.4 Daisy Chain                                      |    |

| 3 Description                        |    | 8 Application and Implementation                     |    |

| 4 Device Options                     | 3  | 8.1 Application Information                          |    |

| 5 Pin Configuration and Functions    | 4  | 8.2 Typical Application                              |    |

| 6 Specifications                     | 6  | 8.3 Power Supply Recommendations                     |    |

| 6.1 Absolute Maximum Ratings         |    | 8.4 Layout                                           | 43 |

| 6.2 ESD Ratings                      |    | 9 Device and Documentation Support                   |    |

| 6.3 Recommended Operating Conditions | 7  | 9.1 Documentation Support                            | 46 |

| 6.4 Thermal Information              | 7  | 9.2 Receiving Notification of Documentation Updates. | 46 |

| 6.5 Electrical Characteristics       | 8  | 9.3 Support Resources                                | 46 |

| 6.6 Timing Requirements              |    | 9.4 Trademarks                                       | 46 |

| 6.7 Quality Conformance Inspection   | 11 | 9.5 Electrostatic Discharge Caution                  | 46 |

| 6.8 Typical Characteristics          |    | 9.6 Glossary                                         |    |

| 7 Detailed Description               | 17 | 10 Revision History                                  | 46 |

| 7.1 Overview                         |    | 11 Mechanical, Packaging, and Orderable              |    |

| 7.2 Functional Block Diagram         |    | Information                                          | 46 |

| •                                    |    |                                                      |    |

# **4 Device Options**

| GENERIC PART<br>NUMBER | RADIATION RATING <sup>(1)</sup>                                     | GRADE <sup>(2)</sup> | PACKAGE        | ORDERABLE PART<br>NUMBER     |  |  |

|------------------------|---------------------------------------------------------------------|----------------------|----------------|------------------------------|--|--|

| TPS7H3014-SP           | TID of 100krad(Si) RLAT,<br>DSEE free to 75 MeV-cm <sup>2</sup> /mg | QMLV-RHA             | 22-pin CFP HFT | 5962R23201VXC <sup>(3)</sup> |  |  |

|                        | None                                                                | Engineering model    | 22-pin CFP HFT | TPS7H3014HFT/EM              |  |  |

<sup>(1)</sup> TID is total ionizing dose and DSEE is destructive single event effects. Additional information is available in the associated TID reports and SEE reports for each product.

<sup>(2)</sup> For additional information about part grade, view SLYB235.

<sup>(3)</sup> Product preview.

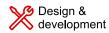

# **5 Pin Configuration and Functions**

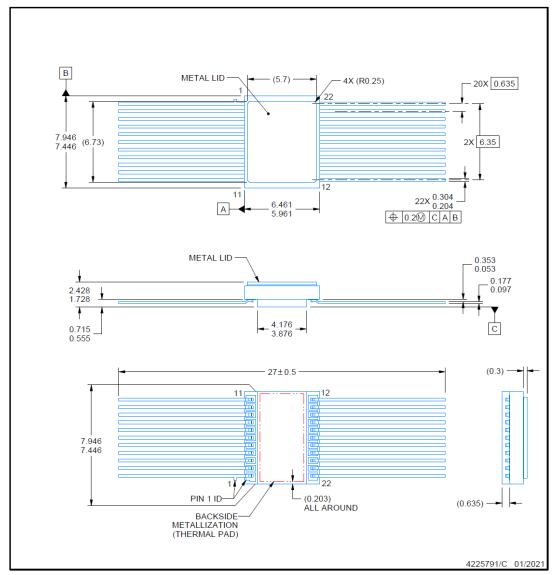

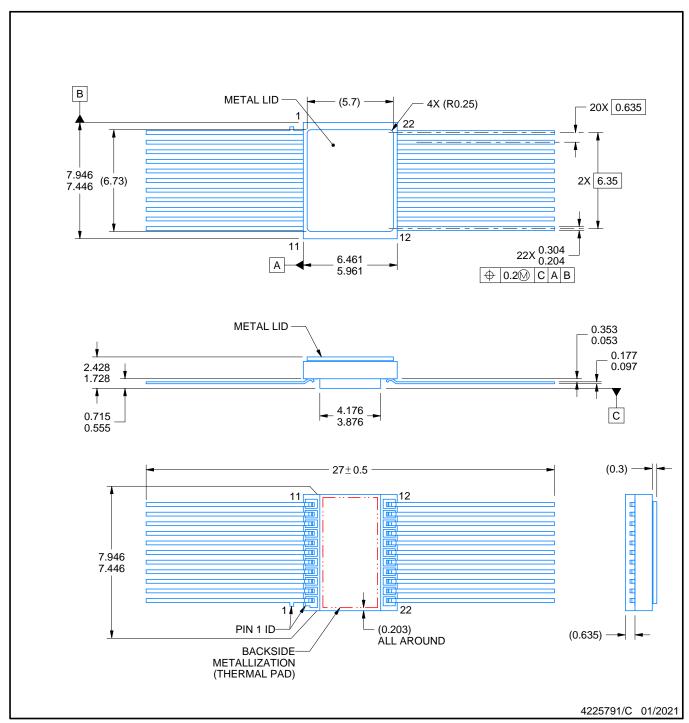

Figure 5-1. HFT Package, 22-Pin CFP (Top View)

**Table 5-1. Pin Functions**

| PIN    |     | I/O <sup>(1)</sup> | DECORPORTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 1/0(1/             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SENSE1 | 1   | ı                  | Non-inverting input of the comparator used to monitor the first rail to be sequenced up/down. To set the $V_{ON}$ and $V_{OFF}$ voltages, connect an external resistive divider between the rail to be monitored and GND with the middle point tied to SENSE1. A voltage greater than 599mV (typ) on this pin is considered as a regulated voltage rail ( $V_{ON}$ ). The $V_{OFF}$ is set by the $I_{HYS}$ current and the top resistor from the resistive divider. Refer to Top and Bottom Resistive Divider Design Equations.  |

| SENSE2 | 2   | ı                  | Non-inverting input of the comparator used to monitor the second rail to be sequenced up/down. To set the $V_{ON}$ and $V_{OFF}$ voltages, connect an external resistive divider between the rail to be monitored and GND with the middle point tied to SENSE2. A voltage greater than 599mV (typ) on this pin is considered as a regulated voltage rail ( $V_{ON}$ ). The $V_{OFF}$ is set by the $I_{HYS}$ current and the top resistor from the resistive divider. Refer to Top and Bottom Resistive Divider Design Equations. |

| SENSE3 | 3   | 1                  | Non-inverting input of the comparator used to monitor the third rail to be sequenced up/down. To set the $V_{ON}$ and $V_{OFF}$ voltages, connect an external resistive divider between the rail to be monitored and GND with the middle point tied to SENSE3. A voltage greater than 599mV (typ) on this pin is considered as a regulated voltage rail ( $V_{ON}$ ). The $V_{OFF}$ is set by the $I_{HYS}$ current and the top resistor from the resistive divider. Refer to Top and Bottom Resistive Divider Design Equations.  |

| SENSE4 | 4   | ı                  | Non-inverting input of the comparator used to monitor the fourth rail to be sequenced up/down. To set the $V_{ON}$ and $V_{OFF}$ voltages, connect an external resistive divider between the rail to be monitored and GND with the middle point tied to SENSE4. A voltage greater than 599mV (typ) on this pin is considered as a regulated voltage rail ( $V_{ON}$ ). The $V_{OFF}$ is set by the $I_{HYS}$ current and the top resistor from the resistive divider. Refer to Top and Bottom Resistive Divider Design Equations. |

| REFCAP | 5   | 0                  | 1.2V internal reference. Requires a 470nF external capacitor to GND. Do not load this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HYS    | 6   | 0                  | Hysteresis. Connect a $50k\Omega$ resistor between this pin and GND, to program the hysteresis current (typically $24\mu A$ ) at SENSE1 to SENSE4. Is recommended using a resistor with a $0.1\%$ or better tolerance for hysteresis current accuracy.                                                                                                                                                                                                                                                                            |

| FAULT  | 7   | 0                  | FAULT. Open drain output which is forced low by the state machine to indicate an internally generated fault. Is recommended to pull-up this pin to VLDO with a $10 \text{k}\Omega$ resistor. However, a different external voltage source can be used as the pull-up as long as it is stable before commanding the sequence up and never drops below 1V during the operation of the device.                                                                                                                                       |

Submit Document Feedback

## **Table 5-1. Pin Functions (continued)**

| PIN         | I   | 40                 | lable 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

| UP          | 8   | I                  | Non-inverting input of a comparator. A rising voltage greater than 599mV (typ) will induce a rising edge and will start a sequence up. This pin can be driven by an external controller, or connected to a main rail trough an external resistive divider with the middle point connected to the UP pin to start the sequence up automatically. This threshold has a fixed hysteresis of 100mV (typ).        |

| IN          | 9   | I                  | Input supply to the device. Input voltage range is from 3V to 14V. Connect at least a 0.1µF ceramic capacitor as close as possible to the pin.                                                                                                                                                                                                                                                               |

| REG_TMR     | 10  | I/O                | Time to regulation timer. Connect a resistor to GND between $10.5k\Omega$ and $1.18M\Omega$ to set the allowed time for a SENSE <sub>x</sub> rail to reach the regulation threshold (V <sub>ON</sub> ). The delay can be adjusted from 0.25ms to 25ms. Leave this pin floating to deactivate this feature.                                                                                                   |

| DLY_TMR     | 11  | I/O                | Delay timer. Connect a resistor to GND between $10.5 k\Omega$ and $1.18 M\Omega$ to set the sequence up and down delay. The delay can be adjusted from $0.25 ms$ to $25 ms$ . Leave this pin floating for no delay.                                                                                                                                                                                          |

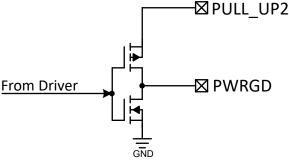

| SEQ_DONE    | 12  | 0                  | Sequence done. Push-pull output with V <sub>OH</sub> level set by PULL_UP2 input supply voltage. Indicates when the sequence up or down is completed.                                                                                                                                                                                                                                                        |

| PWRGD       | 13  | 0                  | Power Good. Push-pull output with $V_{OH}$ level set by PULL_UP2 input supply voltage. Indicates when all rails (SENSE1 to SENSE4) are in regulation (greater than $V_{ONx}$ ).                                                                                                                                                                                                                              |

| GND         | 14  | _                  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                      |

| VLDO        | 15  | 0                  | Output of internal regulator. Requires at least $1\mu F$ external ceramic capacitor to GND. Allowed loading of this regulator are: FAULT pull-up using a $10k\Omega$ resistor or to turn-off unused channels by connecting directly to SENSE2 to SENSE4 as needed.                                                                                                                                           |

| DOWN        | 16  | I                  | Non-inverting input of a comparator. A falling voltage lower than 498mV (typ) will induce a falling edge and will start a sequence down. This pin can be driven by an external controller, or connected to a main rail through an external resistive divider with the middle point connected to the DOWN pin to start the sequence down automatically. This threshold has a fixed hysteresis of 100mV (typ). |

| PULL_UP2    | 17  | I                  | Input supply voltage to program the pull-up voltage for the push-pull output stage on SEQ_DONE and PWRGD. Connect at least a 1µF ceramic capacitor as close as possible to the pin.                                                                                                                                                                                                                          |

| PULL_UP1    | 18  | I                  | Input supply voltage to program the global pull-up voltage for the push-pull output stages on EN1 to EN4. Connect at least a 1µF ceramic capacitor as close as possible to the pin.                                                                                                                                                                                                                          |

| EN4         | 19  | 0                  | Enable 4. Push pull output with V <sub>OH</sub> level set by the PULL_UP1 input supply voltage. Connect to the logic enable signal of the device to control and to be monitored by SENSE4.                                                                                                                                                                                                                   |

| EN3         | 20  | 0                  | Enable 3. Push pull output with $V_{\text{OH}}$ level set by the PULL_UP1 input supply voltage. Connect to the logic enable signal of the device to control and to be monitored by SENSE3.                                                                                                                                                                                                                   |

| EN2         | 21  | 0                  | Enable 2. Push pull output with $V_{OH}$ level set by the PULL_UP1 input supply voltage. Connect to the logic enable signal of the device to control and to be monitored by SENSE2.                                                                                                                                                                                                                          |

| EN1         | 22  | 0                  | Enable 1. Push pull output with $V_{OH}$ level set by the PULL_UP1 input supply voltage. Connect to the logic enable signal of the device to control and to be monitored by SENSE1.                                                                                                                                                                                                                          |

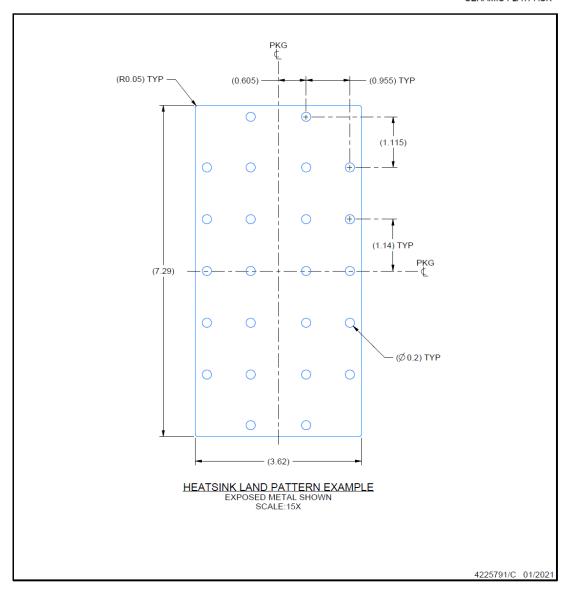

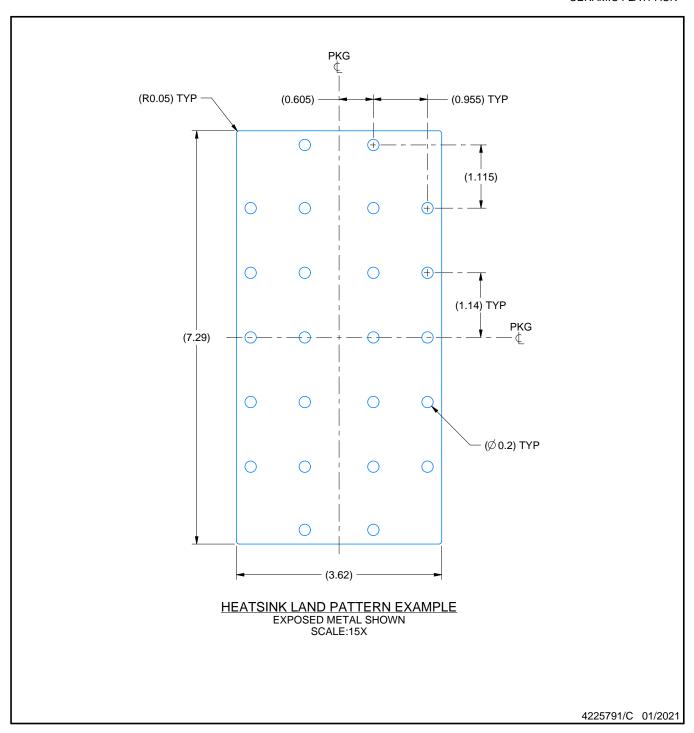

| Thermal pad |     | _                  | Internally grounded. It is recommended to connect this metal thermal pad to a large ground plane for effective heat dissipation.                                                                                                                                                                                                                                                                             |

| Metal lid   | Lid | _                  | The lid is internally connected to the thermal pad and GND through the seal ring.                                                                                                                                                                                                                                                                                                                            |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, — = Other

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                      |                                | MIN  | MAX | UNIT       |

|----------------------|--------------------------------|------|-----|------------|

|                      | IN                             | -0.3 | 16  |            |

|                      | UP, DOWN                       | -0.3 | 7.5 |            |

| Input voltage        | SENSE1, SENSE2, SENSE3, SENSE4 | -0.3 | 3.6 | V          |

|                      | PULL_UP1, PULL_UP2             | -0.3 | 7.5 | V          |

|                      | FAULT                          | -0.3 | 7.5 |            |

|                      | DLY_TMR, REG_TMR               | -0.3 | 3.6 |            |

|                      | VLDO                           | -0.3 | 3.6 |            |

|                      | EN1, EN2, EN3, EN4             | -0.3 | 7.5 |            |

| Output voltage       | REFCAP                         | -0.3 | 2   | V          |

|                      | HYS                            | -0.3 | 3.6 |            |

|                      | SEQ_DONE, PWRGD                | -0.3 | 7.5 |            |

| Output ourrant       | EN1, EN2, EN3, EN4             | -20  | 20  | <b>™</b> V |

| Output current       | SEQ_DONE, PWRGD                | -20  | 20  | mA         |

| Junction temperature | T <sub>J</sub>                 | -65  | 150 | °C         |

| Storage temperature  | T <sub>stg</sub>               | -65  | 150 | °C         |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                                          |                         |                                                                                     | VALUE | UNIT                                  |

|------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|-------|---------------------------------------|

| V                                        |                         | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | V                                     |

| V <sub>ESD</sub> Electrostatic discharge | Electiostatic discharge | Charged-device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±500  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

Product Folder Links: TPS7H3014-SP

- 1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

<sup>(2)</sup> All voltages values are with respect to GND.

# **6.3 Recommended Operating Conditions**

over operating temperature range,  $T_A = -55^{\circ}C$  to 125°C (unless otherwise noted) (1)

|                         |                                | MIN   | NOM MAX | UNIT |

|-------------------------|--------------------------------|-------|---------|------|

|                         | IN                             | 3     | 14      |      |

|                         | UP, DOWN                       | 0     | 7       |      |

| Input voltage           | SENSE1, SENSE2, SENSE3, SENSE4 | 0     | 3.5     | V    |

|                         | PULL_UP1, PULL_UP2             | 1.6   | 7       |      |

|                         | FAULT                          | 0     | 7       |      |

| Output voltage          | EN1, EN2, EN3, EN4             | 0     | 7       | V    |

| Output voltage          | SEQ_DONE, PWRGD                | 0     | 7       | V    |

|                         | EN1, EN2, EN3, EN4             | -10   | 10      |      |

| Output current          | SEQ_DONE,PWRGD                 | -10   | 10      | mA   |

|                         | FAULT                          | -2    |         |      |

| Junction temperature    | T <sub>J</sub>                 | -55   | 125     | °C   |

| Input voltage slew rate | SR <sub>IN</sub>               | 0.001 | 10      | V/µs |

<sup>(1)</sup> All voltages values are with respect to GND.

## **6.4 Thermal Information**

|                       |                                              | TPS7H3014-SP |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC(1)                            | HFT (CFP)    | UNIT |

|                       |                                              | 22 pins      |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 34.2         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 7.7          | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 17.2         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16.9         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 8.6          | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 17           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

Over  $3V \le V_{IN} \le 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{REG\_TMR} = 10k\Omega$ ,  $C_{REFCAP} = 470nF$ ,  $C_{VLDO} = 1\mu F$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ ,  $C_{PULL\_UP1} = 1\mu F$ ,  $C_{PULL\_UP2} = 1\mu F$ , over temperature range ( $T_{A} = -55^{\circ}C$  to  $125^{\circ}C$ ), unless otherwise noted; includes group E radiation testing at  $T_{A} = 25^{\circ}C$  for QML RHA devices  $T_{A} = 25^{\circ}C$  for QML RHA devices  $T_{A} = 25^{\circ}C$

| P                         | ARAMETER                                    | TEST CON                                           | DITIONS                                                                                | SUB-<br>GROUP (3) | MIN   | TYP  | MAX   | UNIT                  |

|---------------------------|---------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------|-------------------|-------|------|-------|-----------------------|

| SUPPLY VOLTAG             | GES AND CURRENTS                            |                                                    |                                                                                        |                   |       |      |       |                       |

| I <sub>Q_IN</sub>         | V <sub>IN</sub> quiescent current           | ŭ .                                                | In Waiting to sequence up and down states with all outputs floating. See State Diagram |                   |       | 2.5  | 4     | mA                    |

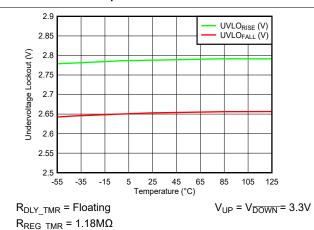

| UVLO <sub>RISE</sub>      | V <sub>IN</sub> rising undervoltage lockout |                                                    |                                                                                        | 1, 2, 3           | 2.72  | 2.79 | 2.84  | V                     |

| UVLO <sub>FALL</sub>      | V <sub>IN</sub> falling udervoltage lockout |                                                    |                                                                                        | 1, 2, 3           | 2.59  | 2.64 | 2.69  | V                     |

| \/                        | Internal linear regulator                   | 5V ≤ V <sub>IN</sub> ≤ 14V                         |                                                                                        | 1, 2, 3           | 3.19  | 3.29 | 3.38  | V                     |

| $V_{LDO}$                 | output voltage                              | V <sub>IN</sub> < 3.24V                            |                                                                                        | 1, 2, 3           | 97%   | 99%  |       | × V <sub>IN</sub>     |

| REFCAP                    | Internal bandgap voltage                    |                                                    |                                                                                        | 1, 2, 3           | 1.188 | 1.2  | 1.212 |                       |

| V <sub>POR_IN</sub>       | Power on reset voltage                      | $1.6V \le V_{PULL\_UPx} \le 7V$ , $I_{ENx} = -2mA$ | V <sub>OL</sub> ≤ 320mV with                                                           | 1, 2, 3           |       | 1.41 | 2     | V                     |

| V <sub>POR_PULL_UPx</sub> | Power on reset voltage (5)                  | V <sub>IN</sub> = 0V, V <sub>OL</sub> ≤ 320mV      | with I <sub>ENx</sub> = -100µA                                                         | 1, 2, 3           |       | 0.89 | 1.4   |                       |

| SENSE1 TO SEN             | SE4, UP AND DOWN COMP                       | PARATOR INPUTS                                     |                                                                                        |                   |       |      |       |                       |

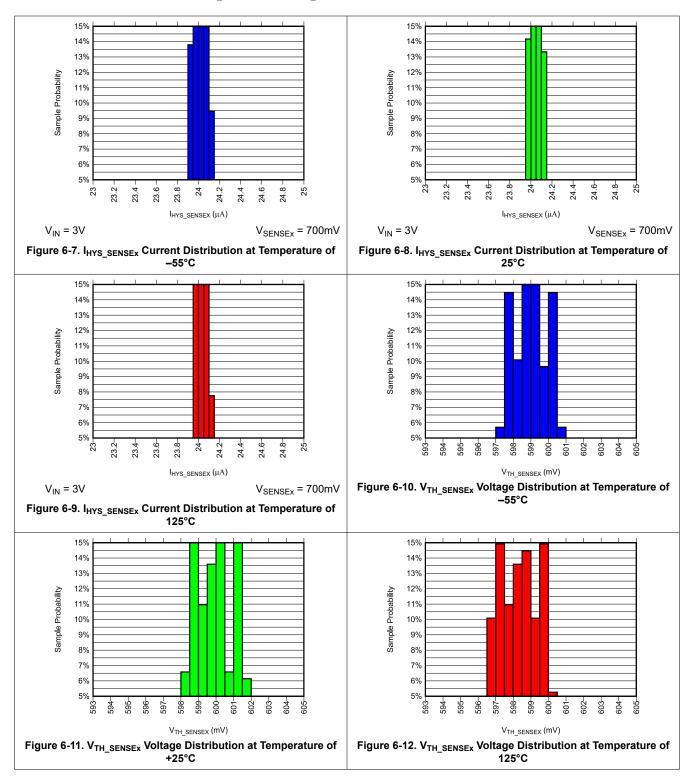

| V <sub>TH_SENSEx</sub>    | Threshold voltage at SENSEx                 |                                                    |                                                                                        | 1, 2, 3           | 593   | 599  | 605   | mV                    |

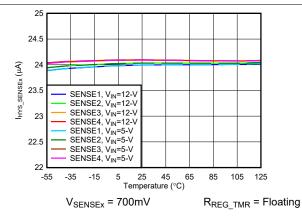

| I <sub>HYS_SENSEx</sub>   | SENSEx hysteresis current                   | V <sub>SENSEx</sub> = 700mV                        |                                                                                        | 1, 2, 3           | 23.28 | 24   | 24.72 | μΑ                    |

| I <sub>LKG_SENSEx</sub>   | Input leakage current at SENSEx             | V <sub>SENSEx</sub> = 500mV                        |                                                                                        | 1, 2, 3           |       | 2    | 100   | nA                    |

| V <sub>TH_UP</sub>        | Rising threshold voltage at UP              | V <sub>UP</sub> rising to 1V                       |                                                                                        | 1, 2, 3           | 580   | 598  | 615   | mV                    |

| V <sub>TH_DOWN</sub>      | Falling threshold voltage at DOWN           | V <sub>DOWN</sub> falling from 1V                  | V <sub>DOWN</sub> falling from 1V                                                      |                   | 483   | 498  | 512   | mV                    |

| V <sub>HYS_UP_DOWN</sub>  | UP and DOWN hysteresis voltage              |                                                    |                                                                                        | 1, 2, 3           |       | 100  |       | mV                    |

| I <sub>LKG_UP_DOWN</sub>  | Input leakage current at UP and DOWN        | $V_{UP} = V_{\overline{DOWN}} = 500 \text{mV}$     |                                                                                        | 1, 2, 3           |       | 2    | 100   | nA                    |

| V <sub>TURN_OFF</sub>     | Channel 2, 3, 4 turn off voltage            |                                                    |                                                                                        | 1, 2, 3           | 87%   | 89%  | 91%   | × VLDO                |

| EN1 TO EN4, SE            | Q_DONE AND PWRGD PUS                        | H PULL OUTPUTS                                     |                                                                                        |                   |       |      |       |                       |

| V                         | Low-level ENx output                        | 16\/<\/<7\/                                        | $I_{LOAD} = -2mA$                                                                      | 1, 2, 3           |       |      | 10%   |                       |

| $V_{OL\_ENx}$             | voltage                                     | $1.6V \le V_{PULL\_UP1} \le 7V$                    | $I_{LOAD} = -10mA$                                                                     | 1, 2, 3           |       |      | 25%   | х                     |

| V                         | High-level ENx output                       | 1.6V ≤ V <sub>PULL UP1</sub> ≤ 7V                  | $I_{LOAD} = 2mA$                                                                       | 1, 2, 3           | 90%   |      |       | V <sub>PULL_UP1</sub> |

| V <sub>OH_ENx</sub>       | voltage                                     | 1.0V = VPULL_UP1 = 7 V                             | $I_{LOAD} = 10mA$                                                                      | 1, 2, 3           | 70%   |      |       |                       |

| Vol. 050 2015             | Low-level SEQ_DONE                          | 1.6V ≤ V <sub>PULL UP2</sub> ≤ 7V                  | $I_{LOAD} = -2mA$                                                                      | 1, 2, 3           |       |      | 10%   |                       |

| V <sub>OL_SEQ_DONE</sub>  | output voltage                              | 1.0 v = v PULL_UP2 = 1 v                           | $I_{LOAD} = -10mA$                                                                     | 1, 2, 3           |       |      | 25%   |                       |

| V <sub>OH_SEQ_DONE</sub>  | High-level SEQ_DONE                         | 1.6V ≤ V <sub>PULL UP2</sub> ≤ 7V                  | I <sub>LOAD</sub> = 2mA                                                                | 1, 2, 3           | 90%   |      |       |                       |

|                           | output voltage                              |                                                    | I <sub>LOAD</sub> = 10mA                                                               | 1, 2, 3           | 70%   |      |       | X                     |

| V <sub>OL_PWRGD</sub>     | Low-level PWRGD                             | 1.6V ≤ V <sub>PULL UP2</sub> ≤ 7V                  | I <sub>LOAD</sub> = –2mA                                                               | 1, 2, 3           |       |      | 10%   | V <sub>PULL_UP2</sub> |

| 5 <u>-</u> ,0             | output voltage                              | v - v PULL_UP2 - 1 v                               | $I_{LOAD} = -10mA$                                                                     | 1, 2, 3           |       |      | 25%   |                       |

| V <sub>OH_PWRGD</sub>     | High-level PWRGD                            | 1.6V ≤ V <sub>PULL UP2</sub> ≤ 7V                  | I <sub>LOAD</sub> = 2mA                                                                | 1, 2, 3           | 90%   |      |       |                       |

| 511_1 W. (OD              | output voltage                              | 1 022_012                                          | $I_{LOAD} = 10mA$                                                                      | 1, 2, 3           | 70%   |      |       |                       |

## **6.5 Electrical Characteristics (continued)**

Over  $3V \le V_{IN} \le 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{REG\_TMR} = 10k\Omega$ ,  $C_{REFCAP} = 470nF$ ,  $C_{VLDO} = 1\mu F$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ ,  $C_{PULL\_UP1} = 1\mu F$ ,  $C_{PULL\_UP2} = 1\mu F$ , over temperature range ( $T_A = -55^{\circ}C$  to  $125^{\circ}C$ ), unless otherwise noted; includes group E radiation testing at  $T_A = 25^{\circ}C$  for QML RHA devices  $^{(1)}$   $^{(2)}$

| PARAMETER                     |                                           | TEST CON                                                               | DITIONS                             | SUB-<br>GROUP (3) | MIN | TYP | MAX | UNIT |

|-------------------------------|-------------------------------------------|------------------------------------------------------------------------|-------------------------------------|-------------------|-----|-----|-----|------|

| PULL_UPx <sub>LKG</sub>       | PULL_UPx leakage current                  | V <sub>PULL_UPx</sub> = 7V                                             |                                     | 1, 2, 3           |     | 48  | 121 | μΑ   |

| SR <sub>ENX_RISE</sub>        | Enable rising output voltage slew rate    | 10% to 90% of $V_{PULL\_UP1}$ , $R_{LOAD} = 50kΩ$ , $C_{LOAD} = 100pF$ | 1.6V ≤ V <sub>PULL_UP1</sub> ≤ 7V   | 9, 10, 11         | 17  | 125 |     |      |

| SR <sub>SEQ_DONE_RISE</sub>   | SEQ_DONE rising output voltage slew rate  | 10% to 90% of V <sub>PULL UP2</sub> ,                                  | 1.6V ≤ V <sub>PULL_UP2</sub>        | 9, 10, 11         | 17  | 125 |     |      |

| SR <sub>PWRGD_RISE</sub>      | PWRGD rising output voltage slew rate     | $R_{LOAD} = 50k\Omega$ ,<br>$C_{LOAD} = 100pF$                         | ≤ 7V                                | 9, 10, 11         | 17  | 125 |     | V/µs |

| SR <sub>ENx_FALL</sub>        | Enable falling output voltage slew rate   | 90% to 10% of                                                          | 1.6V ≤ V <sub>PULL_UP1</sub> ≤ 7V   | 9, 10, 11         | 44  | 126 |     |      |

| SR <sub>SEQ_DONE_FALL</sub>   | SEQ_DONE falling output voltage slew rate | $V_{PULL\_UP1}$ , $R_{LOAD} = 50k\Omega$ ,                             | 1.6V ≤ V <sub>PULL_UP2</sub>        | 9, 10, 11         | 44  | 126 |     |      |

| SR <sub>PWRGD_FALL</sub>      | PWRGD falling output voltage slew rate    | C <sub>LOAD</sub> = 100pF                                              | ≤ 7V                                | 9, 10, 11         | 44  | 126 |     |      |

| D                             | EN PMOS source output                     | - Om A                                                                 | $_{AD} = 2mA$ $\leq 3.3V$           | 1, 2, 3           |     | 18  | 40  |      |

| R <sub>ENx_PULL_UP</sub>      | resistance                                | I <sub>LOAD</sub> = 2mA                                                |                                     | 1, 2, 3           |     | 7   | 20  |      |

| D.                            | SEQ DONE PMOS                             | e I <sub>LOAD</sub> = 2mA                                              | 1.6V ≤ V <sub>PULL_UP2</sub> ≤ 3.3V | 1, 2, 3           |     | 18  | 40  |      |

| R <sub>SEQ_DONE_PULL_UP</sub> | source output resistance                  |                                                                        | 3.3V ≤ V <sub>PULL UP2</sub> ≤ 7V   | 1, 2, 3           |     | 7   | 20  |      |

| R <sub>PWRGD_PULL_UP</sub>    | PWRGD PMOS source                         | I <sub>LOAD</sub> = 2mA                                                | 1.6V ≤ V <sub>PULL_UP2</sub> ≤ 3.3V | 1, 2, 3           |     | 18  | 40  | Ω    |

| **PWRGD_PULL_UP               | output resistance                         | LOAD ZIIV                                                              | $3.3V \le V_{PULL\_UP2} \le 7V$     | 1, 2, 3           |     | 7   | 20  |      |

| R <sub>ENx_PULL_DOWN</sub>    | EN NMOS sink output resistance            | I <sub>LOAD</sub> = -2mA, 1.6V ≤ \                                     | V <sub>PULL_UP1</sub> ≤ 7V          | 1, 2, 3           |     | 7   | 28  |      |

| R <sub>SEQ_DONE_PULL_DO</sub> | SEQ_DONE NMOS sink output resistance      | I <sub>LOAD</sub> = -2mA, 1.6V ≤ \                                     | V <sub>PULL_UP1</sub> ≤ 7V          | 1, 2, 3           |     | 7   | 28  |      |

| R <sub>PWRGD_PULL_DOWN</sub>  | PWRGD NMOS sink output resistance         | I <sub>LOAD</sub> = -2mA, 1.6V ≤ V <sub>PULL_UP1</sub> ≤ 7V            |                                     | 1, 2, 3           |     | 7   | 28  |      |

| FAULT OUTPUT                  |                                           |                                                                        |                                     |                   |     |     |     |      |

| R <sub>FAULT_PULL_DOWN</sub>  | FAULT pull down resistance                | I <sub>FAULT</sub> = 100μA                                             |                                     | 1, 2, 3           |     | 131 | 512 | Ω    |

| I <sub>LKG_FAULT</sub>        | FAULT leakage current                     | V <sub>FAULT</sub> = 7V                                                |                                     | 1, 2, 3           |     | 23  | 600 | nA   |

| THERMAL PROTEC                | CTION                                     | 1                                                                      |                                     | 1                 |     |     |     |      |

| T <sub>SD_ENTER</sub>         | Thermal shutdown enter temperature        |                                                                        |                                     |                   |     | 177 |     | •••  |

| T <sub>SD_EXIT</sub>          | Thermal shutdown exit temperature         |                                                                        |                                     |                   |     | 164 |     | °C   |

## 6.5 Electrical Characteristics (continued)

Over  $3V \le V_{IN} \le 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{REG\_TMR} = 10k\Omega$ ,  $C_{REFCAP} = 470nF$ ,  $C_{VLDO} = 1\mu F$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ ,  $C_{PULL\_UP1} = 1\mu F$ ,  $C_{PULL\_UP2} = 1\mu F$ , over temperature range ( $T_A = -55^{\circ}C$  to  $125^{\circ}C$ ), unless otherwise noted; includes group E radiation testing at  $T_A = 25^{\circ}C$  for QML RHA devices  $^{(1)}$   $^{(2)}$

| PARAMETER                           |                    | TEST CONDITIONS              | SUB-<br>GROUP (3) | MIN   | TYP   | MAX   | UNIT |  |  |

|-------------------------------------|--------------------|------------------------------|-------------------|-------|-------|-------|------|--|--|

| DELAY AND TIME TO REGULATION TIMERS |                    |                              |                   |       |       |       |      |  |  |

| t <sub>DLY_TMR</sub>                |                    | $R_{DLY\_TMR} = 10.5k\Omega$ | 1, 2, 3           | 0.205 | 0.268 | 0.342 |      |  |  |

|                                     | Delay time         | $R_{DLY\_TMR} = 619k\Omega$  | 1, 2, 3           | 10.77 | 12.5  | 14.14 |      |  |  |

|                                     |                    | $R_{DLY\_TMR} = 1.18M\Omega$ | 1, 2, 3           | 20    | 23.37 | 27.2  | ms   |  |  |

| t <sub>REG_TMR</sub>                |                    | $R_{REG\_TMR} = 10.5k\Omega$ | 1, 2, 3           | 0.197 | 0.264 | 0.34  | 1115 |  |  |

|                                     | Time to regulation | $R_{REG\_TMR} = 619k\Omega$  | 1, 2, 3           | 10.8  | 12.4  | 14.1  |      |  |  |

|                                     |                    | $R_{REG\_TMR} = 1.18M\Omega$ | 1, 2, 3           | 20.3  | 23.63 | 27.2  |      |  |  |

- (1) See the 5962R23201VXC SMD (standard microcircuit drawing) for additional information on the RHA devices.

- (2) All voltage values are with respect to GND.

- (3) For subgroup definitions, see Quality Conformance Inspection table.

- (4) V<sub>POR\_IN</sub> is the minimum V<sub>IN</sub> voltage for a controlled output state, when 1.6V ≤ V<sub>PULL\_UPX</sub> ≤ 7V. Below V<sub>POR\_IN</sub>, the output cannot be determined.

- (5) V<sub>POR\_PULL\_UPx</sub> is the minimum V<sub>PULL\_UPx</sub> voltage for a controlled output state, when V<sub>IN</sub> ≤ 3V. Below V<sub>POR\_PULL\_UPx</sub> the output cannot be determined.

## 6.6 Timing Requirements

Over  $3V \le V_{IN} \le 14V$ ,  $R_{DLY\_TMR} = 10k\Omega$ ,  $R_{REG\_TMR} = 10k\Omega$ ,  $C_{REFCAP} = 470nF$ ,  $C_{VLDO} = 1\mu F$ ,  $V_{PULL\_UP1} = 3.3V$ ,  $V_{PULL\_UP2} = 3.3V$ ,  $C_{PULL\_UP1} = 1\mu F$ ,  $C_{PULL\_UP2} = 1\mu F$ , over temperature range ( $T_A = -55^{\circ}C$  to  $125^{\circ}C$ ) unless otherwise noted; includes group E radiation testing at  $T_A = 25^{\circ}C$  for RHA devices (1)

|                             | PARAMETER                                            | TEST CONDITIONS                                                                                                | SUB-<br>GROUP (2) | MIN TYF | MAX | UNIT |

|-----------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------|---------|-----|------|

| t <sub>Start_up_delay</sub> | Start-up delay time (3)                              | V <sub>REFCAP</sub> ≥ 1.1V                                                                                     | 1, 2, 3           |         | 2.8 | ms   |

| t <sub>pd_ENx</sub>         | ENx propagation delay                                | DLY_TMR = Open,<br>V <sub>OVERDRIVE</sub> = 10mV,<br>V <sub>PULL_UPy</sub> =1.6V,<br>from 50% of IN to 50% OUT | 1, 2, 3           | 3.4     | 6.5 |      |

| t <sub>pd_SEQ_DONE</sub>    | SEQ_DONE propagation delay                           | DLY_TMR = Open, V <sub>OVERDRIVE</sub> = 10mV                                                                  | 1, 2, 3           | 3.4     | 6.5 | μs   |

| t <sub>pd_PWRGD</sub>       | PWRGD propagation delay                              | DLY_TMR = Open, V <sub>OVERDRIVE</sub> = 10mV                                                                  | 1, 2, 3           | 3.4     | 6.5 |      |

| t <sub>pd_SM_FAULT</sub>    | State machine fault propagation delay                | Out of order fault                                                                                             | 1, 2, 3           | 3.4     | 4.3 |      |

| t <sub>MIN_UP</sub>         | V <sub>UP</sub> rising minimum time for valid UP     |                                                                                                                | 4, 5, 6           | 0.27    | 0.7 |      |

| t <sub>MIN_DOWN</sub>       | V <sub>DOWN</sub> rising minimum time for valid DOWN |                                                                                                                | 4, 5, 6           | 0.42    | 0.9 | μs   |

| t <sub>h_VTH_RISE</sub>     | Rising theshold on VSENSEx hold time                 |                                                                                                                | 4, 5, 6           | 0.84    | 1.6 | μs   |

| t <sub>h_VTH_FALL</sub>     | Falling theshold on VSENSEx hold time                |                                                                                                                | 4, 5, 6           | 0.35    | 1   | μs   |

- (1) See the 5962R23201VXC SMD (standard microcircuit drawing) for additional information on the RHA devices (coming later)

- (2) For subgroup definitions, see Quality Conformance Inspection table.

- (3) During the power-on, V<sub>IN</sub> must be at or above V<sub>IN</sub> (MIN) for at least t<sub>Start up delay</sub> for all internal references to be within specification.

# **6.7 Quality Conformance Inspection**

MIL-STD-883, Method 5005 - Group A

| SUBGROUP | DESCRIPTION         | TEMP (°C)   |

|----------|---------------------|-------------|

| 1        | Static tests at     | 25          |

| 2        | Static tests at     | 125         |

| 3        | Static tests at     | <b>–</b> 55 |

| 4        | Dynamic tests at    | 25          |

| 5        | Dynamic tests at    | 125         |

| 6        | Dynamic tests at    | <b>-</b> 55 |

| 7        | Functional tests at | 25          |

| 8A       | Functional tests at | 125         |

| 8B       | Functional tests at | <b>–</b> 55 |

| 9        | Switching tests at  | 25          |

| 10       | Switching tests at  | 125         |

| 11       | Switching tests at  | <b>–</b> 55 |

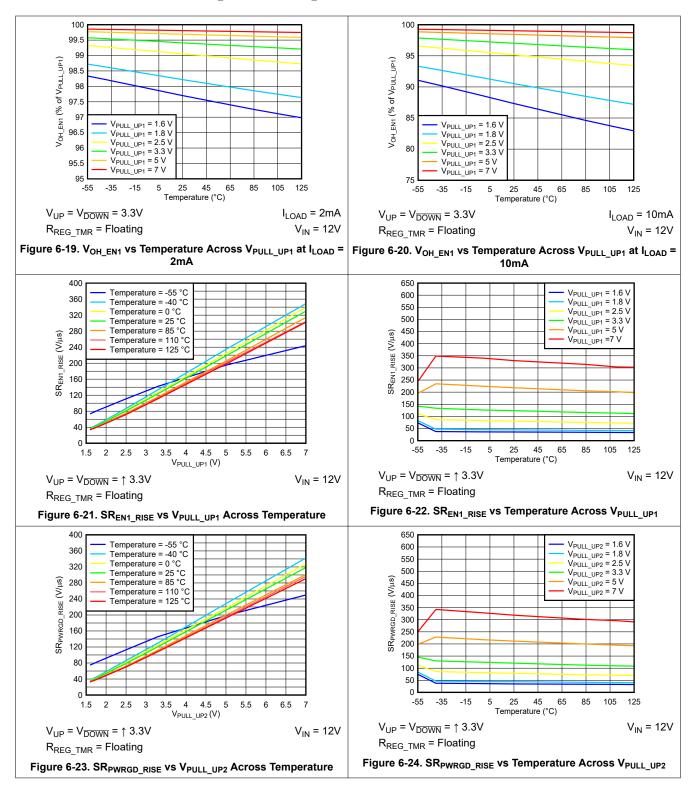

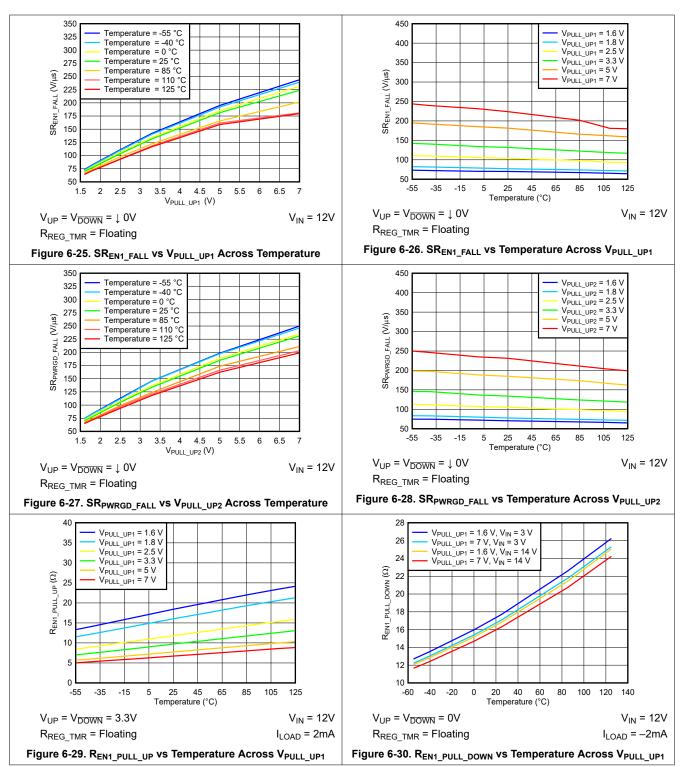

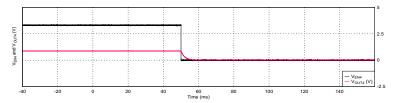

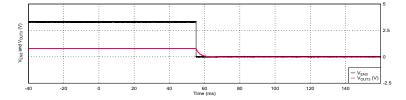

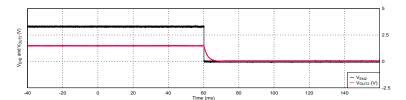

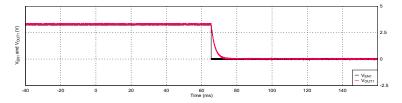

## 6.8 Typical Characteristics

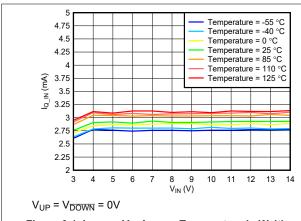

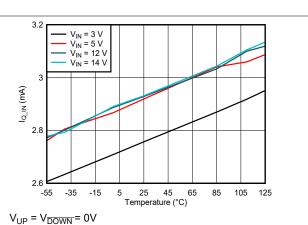

$R_{DLY\_TMR} = 10k\Omega, \ R_{REG\_TMR} = 10k\Omega, \ V_{PULL\_UP1} = 3.3V, \ V_{PULL\_UP2} = 3.3V, \ V_{\overline{FAULT}} = 10k\Omega \ pull-up \ to \ VLDO, \ R_{HYS} = 50k\Omega, \ C_{REFCAP} = 470nF, \ C_{VLDO} = 1\mu F, \ C_{PULL\_UP1} = 1\mu F, \ C_{PULL\_UP2} = 1\mu F, \ unless \ otherwise \ noted.$

Figure 6-1.  $I_{Q\_IN}$  vs  $V_{IN}$  Across Temperature in Waiting to Sequence UP State

Figure 6-2. I<sub>Q\_IN</sub> vs Temperature Across V<sub>IN</sub> in Waiting to Sequence UP State

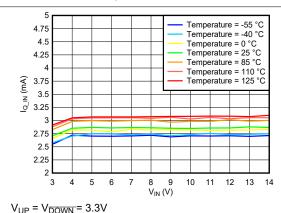

Figure 6-3. I<sub>Q\_IN</sub> vs V<sub>IN</sub> Across Temperature in Waiting to Sequence DOWN State

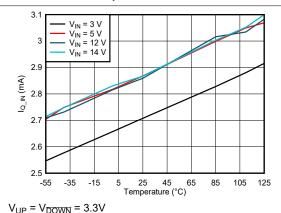

Figure 6-4. I<sub>Q\_IN</sub> vs Temperature Across V<sub>IN</sub> in Waiting to Sequence DOWN State

Figure 6-5. Undervoltage Lockout vs Temperature

Figure 6-6.  $I_{\text{HYS\_SENSEx}}$  vs Temperature Across  $V_{\text{IN}}$  and SENSEx Channel

Submit Document Feedback

$R_{DLY\_TMR} = 10k\Omega, \ R_{REG\_TMR} = 10k\Omega, \ V_{PULL\_UP1} = 3.3V, \ V_{PULL\_UP2} = 3.3V, \ V_{\overline{FAULT}} = 10k\Omega \ pull-up \ to \ VLDO, \ R_{HYS} = 50k\Omega, \ C_{REFCAP} = 470nF, \ C_{VLDO} = 1\mu F, \ C_{PULL\_UP1} = 1\mu F, \ C_{PULL\_UP2} = 1\mu F, \ unless \ otherwise \ noted.$

$R_{DLY\_TMR} = 10k\Omega, \ R_{REG\_TMR} = 10k\Omega, \ V_{PULL\_UP1} = 3.3V, \ V_{PULL\_UP2} = 3.3V, \ V_{\overline{FAULT}} = 10k\Omega \ pull-up \ to \ VLDO, \ R_{HYS} = 50k\Omega, \ C_{REFCAP} = 470nF, \ C_{VLDO} = 1\mu F, \ C_{PULL\_UP1} = 1\mu F, \ C_{PULL\_UP2} = 1\mu F, \ unless \ otherwise \ noted.$

Submit Document Feedback

$R_{DLY\_TMR} = 10k\Omega, \ R_{REG\_TMR} = 10k\Omega, \ V_{PULL\_UP1} = 3.3V, \ V_{PULL\_UP2} = 3.3V, \ V_{\overline{FAULT}} = 10k\Omega \ pull-up \ to \ VLDO, \ R_{HYS} = 50k\Omega, \ C_{REFCAP} = 470nF, \ C_{VLDO} = 1\mu F, \ C_{PULL\_UP1} = 1\mu F, \ C_{PULL\_UP2} = 1\mu F, \ unless \ otherwise \ noted.$

$R_{DLY\_TMR} = 10k\Omega, \ R_{REG\_TMR} = 10k\Omega, \ V_{PULL\_UP1} = 3.3V, \ V_{PULL\_UP2} = 3.3V, \ V_{\overline{FAULT}} = 10k\Omega \ pull-up \ to \ VLDO, \ R_{HYS} = 50k\Omega, \ C_{REFCAP} = 470nF, \ C_{VLDO} = 1\mu F, \ C_{PULL\_UP1} = 1\mu F, \ C_{PULL\_UP2} = 1\mu F, \ unless \ otherwise \ noted.$

Submit Document Feedback

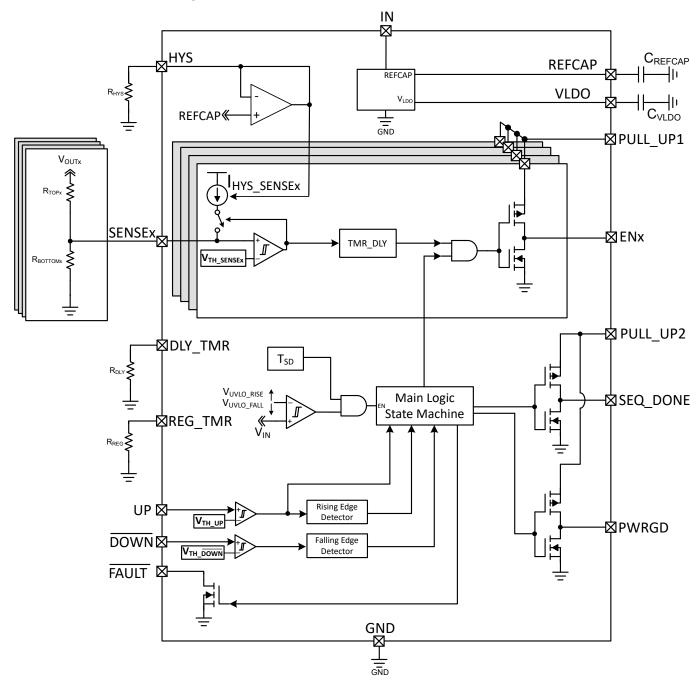

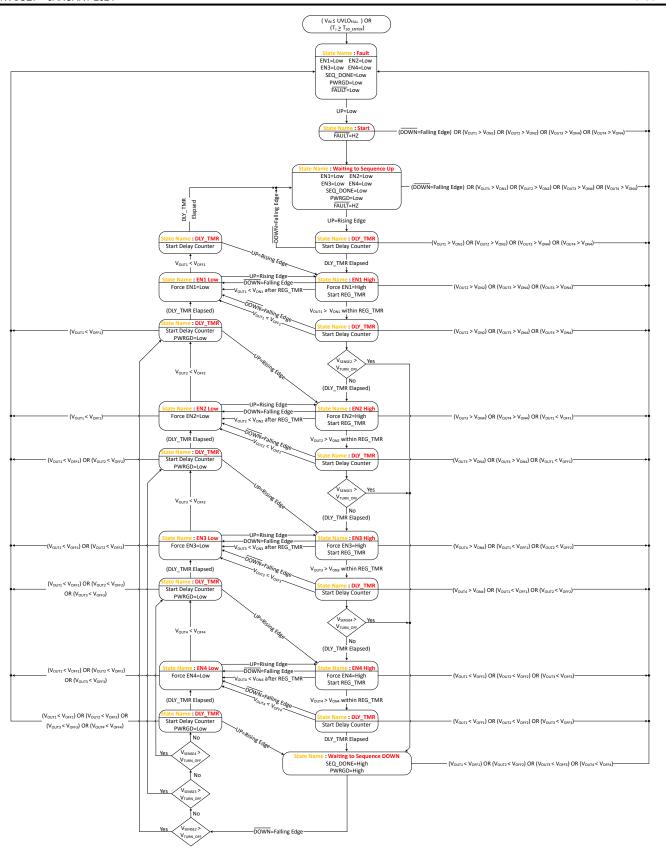

## 7 Detailed Description

## 7.1 Overview

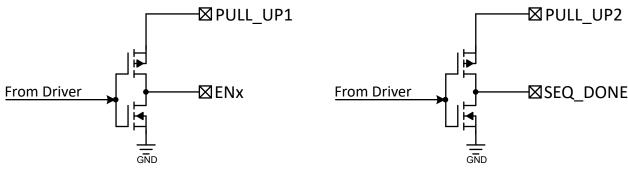

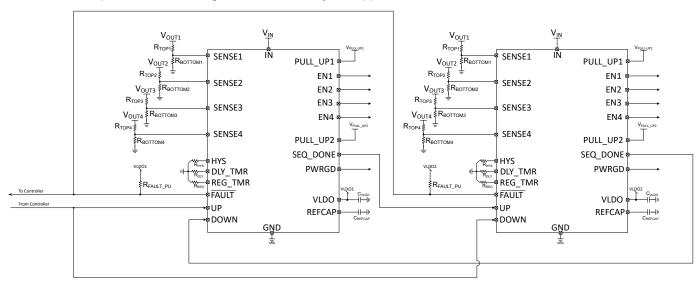

The TPS7H3014 is a four-Channel, 3V to 14V, sequencer and supervisor for space applications. The device is intended to drive devices with enable high logic inputs. The channel count can be incremented as needed for the application by connecting multiple ICs. in a daisy-chain configuration. Each output incorporates a push-pull architecture. The logic high of these outputs are externally provided by the user by supplying a voltage to the PULL-UPx inputs. All ENx push-pull outputs are tied to the PULL\_UP1 domain while SEQ\_DONE and PWRGD are tied to the PULL UP2 domain.

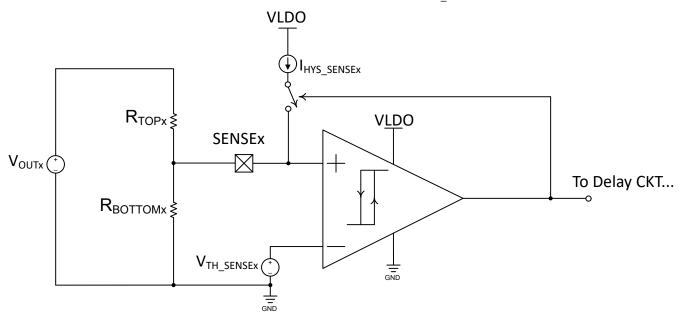

The SENSEx inputs are connected to the non-inverting input (undervoltage) of a comparator which is used to determine the on (in regulation) and off (not in regulation) voltage level of the monitored power supply  $(V_{OUTx})$ . Each of these inputs feature a threshold level of 599mV (typ) with an accuracy of  $\pm 1\%$  across: voltage, temperature, and radiation (TID). The hysteresis voltage threshold level can be adjusted by the user and determined by the  $R_{TOPx}$  resistance and the hysteresis current ( $I_{HYS}$ ). The  $I_{HYS}$  becomes active once the rising voltage at SENSEx exceeds the threshold (599mV typ), indicating the monitored voltage rail is in regulation.  $I_{HYS}$  is 24 $\mu$ A with an accuracy of  $\pm 3\%$  across: voltage, temperature, and radiation (TID).

The device incorporates two timers:

- 1. **DLY\_TMR**: Set the rising and falling ENx delay. Once the SENSE<sub>x-1</sub> is above the on voltage during a sequence up, the EN<sub>x</sub> will be asserted high once the delay set by the user using the DLY\_TMR input is expired. The same is true during sequence down, this means that once SENSE<sub>x</sub> is below the off voltage the EN<sub>x-1</sub> will be asserted low once the timer is expired. This timer can be set from 0.25ms to 25ms, by using a 10.5k $\Omega$  to a 1.18M $\Omega$ , respectively.

- 2. **REG\_TMR**: Set the allowed time that a sensed voltage rail has to be above the on threshold (in regulation). Once the  $EN_x$  is asserted high, the  $SENSE_x$  has up to the time set by the user, using REG\_TMR, to be above 599mV (typ). Otherwise a reverse sequence down from  $EN_{x-1}$  is started.

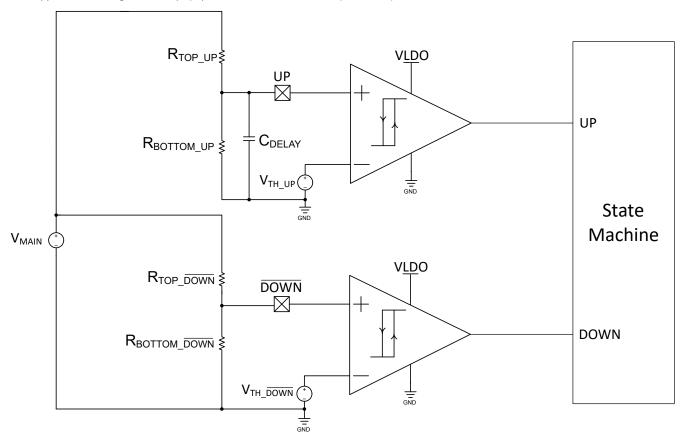

Separate UP and  $\overline{DOWN}$  pins are provided by the device in order to enable daisy-chain configurations. The UP pin has a threshold (V<sub>TH\_DOWN</sub>) of 599mV (typ), while the  $\overline{DOWN}$  pin has an threshold (V<sub>TH\_DOWN</sub>) of 498mV. A fixed hysteresis of 100mV is incorporated in both input comparators for noise stability. These pins are edge sensitive, a rising edge in UP starts the sequence up, while a falling edge in  $\overline{DOWN}$  will start the sequence down.

When using a single device and driven externally, both pins (UP and DOWN) are typically tied together. Since UP and  $\overline{\text{DOWN}}$  inputs have an accurate threshold, they can be used to initiate the sequence up and down by accurately sensing another rail (using a resistive divider), or they can be externally driven by a controller. Once UP is driven above V<sub>TH\_UP</sub>, the device will start a sequence up by asserting EN1 high after the programmed delay time (DLY\_TMR), at which point the SENSE1 will start rising up. If SENSE1 crosses the on voltage before the REG\_TMR is expired, then EN2 will be asserted high after the programmed delay. This process continues until the SEQ\_DONE and PWRGD are asserted high indicating a complete sequence up and system power good, respectively.

Once the  $\overline{\text{DOWN}}$  pin is driven below  $V_{\text{TH\_DOWN}}$ , the device will start a sequence down by forcing EN4 low after the programmed delay. At this point, the  $\overline{\text{SENSE4}}$  voltage will start falling until is lower than the set off voltage. Once this happens, EN3 will be asserted low after the programmed delay. This will continue until EN1 is forced low. As the discharge time of the sequenced devices is unknown, the REG\_TMR is not active during power down.

During sequence up, SEQ\_DONE and PWRGD are asserted high after the last used channel crosses the on voltage threshold and the programmed DLY\_TMR is expired (assuming it is active). During sequence down, SEQ\_DONE is forced low once V<sub>OUT1</sub> is below the off voltage and the DLY\_TMR is expired. However PWRGD is forced low immediately after the commanded sequence down.

The TPS7H3014 also incorporates a comprehensive FAULT management system described in the State Machine section.

# 7.2 Functional Block Diagram

## 7.3 Feature Description

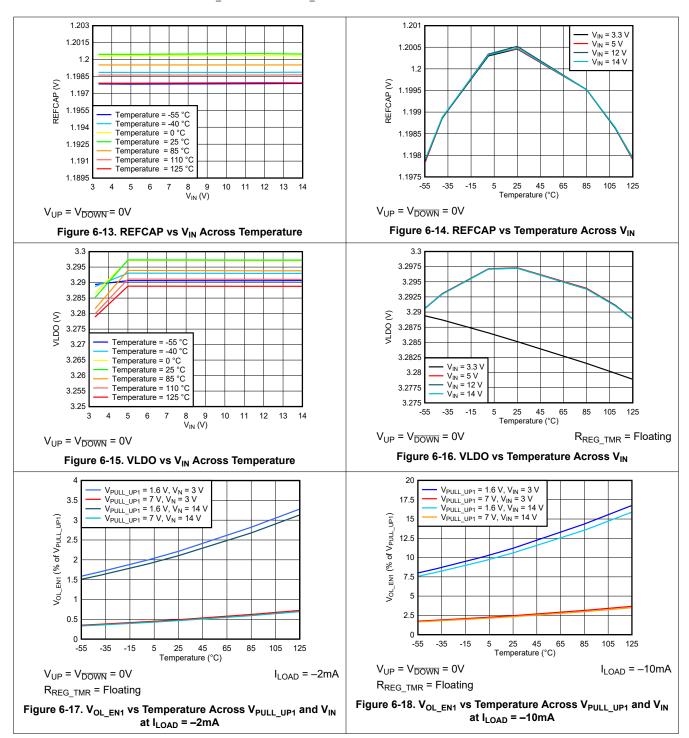

## 7.3.1 Input Voltage (IN), VLDO and REFCAP

During steady state operation, the input voltage of the TPS7H3014 must be between 3V and 14V. A minimum bypass capacitance of at least  $0.1\mu F$  is needed between  $V_{IN}$  and GND. The input bypass capacitors should be placed as close to the sequencer IC as possible. Is recommended that  $V_{IN}$  slew rate is controlled between  $10V/\mu s$  to  $1mV/\mu s$  for proper IC operation.

The voltage applied at  $V_{IN}$  serves as the input for the internal regulator that generates the VLDO voltage, typically 3.29V. At input voltages less the 3.29V (typ), the VLDO voltage will follow the voltage at  $V_{IN}$ . Recommended capacitance for VLDO is 1µF. Unused SENSE2 to SENSE4 can be tied to VLDO to by-pass the channel delay during sequence up and down. It is recommended to pull-up the  $\overline{FAULT}$  pin to VLDO via a  $10k\Omega$  resistor, but otherwise it is recommended not to externally load this pin due to limited output current capability. During power up, the user should wait at least the 2.8ms ( $t_{Start\_up\_delay}$ ) after  $V_{IN}$  > UVLO<sub>RISE</sub> before attempting to start a sequence up, this is due to internal time constants in the device.

Each device generates an internal 1.2V bandgap reference that is utilized throughout the various internal control logic blocks. This is the voltage present on the REFCAP pin during steady state operation. This voltage is divided down to produce the reference for the comparator inputs SENSE<sub>x</sub> (599mV typ), UP (598mV typ) and  $\overline{\text{DOWN}}$  (498mV typ). The V<sub>TH\_SENSEx</sub> reference is measured at the EN<sub>x</sub> outputs to account for offsets in the error amplifier and maintains regulation within  $\pm 1\%$  across: voltage, temperature, and radiation TID (up to 100krad in Silicon). This tight reference tolerance allows the user to monitor voltage rails with high accuracy. A 470nF capacitor to GND is required at the REFCAP pin for proper electrical operation as well as to ensure robust SET performance of the device.

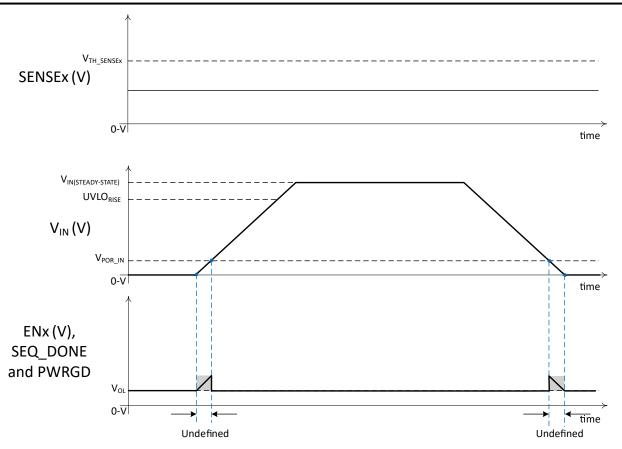

## 7.3.1.1 Undervoltage Lockout ( $V_{POR\ IN} < V_{IN} < UVLO$ )

When the voltage on  $V_{IN}$  is less than the UVLO (2.79V typ) voltage, but greater than the power-on reset voltage ( $V_{POR\_IN}$ , 1.41V typ), the output pins (ENx, SEQ\_DONE and PWRGD) will be in a logic low state, regardless of the voltage at the inputs of the device, named as:

- SENSE<sub>x</sub>

- UP

- DOWN

#### 7.3.1.2 Power-On Reset ( $V_{IN} < V_{POR \ IN}$ )

When the voltage on  $V_{IN}$  is lower than the power on reset voltage ( $V_{POR\_IN}$ ), the output signal is undefined and is not to be relied upon for proper device function.

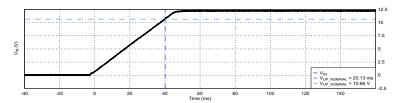

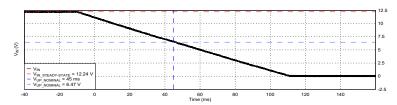

Figure 7-1 shows the ENx outputs relationship to a rising input voltage ( $V_{IN}$ ). As can be observed, the ENx are undefined when  $V_{IN}$  is lower than  $V_{POR\_IN}$  (typically 1.41V). During this time the outputs can be any value from 0V to  $V_{IN}$ . In this case, the input voltages to all undervoltage (UV) input comparators (SENSEx) are below the  $V_{TH\_SENSEx}$  (599mV). For this reason (in conjunction with waiting for a rising edge on UP), the ENx, SEQ\_DONE and PWRGD stays low after  $V_{IN}$  rises above UVLO<sub>RISE</sub> (typically 2.79V).

Figure 7-1. Outputs in a Valid Low State After V<sub>IN</sub> > V<sub>IN-MIN</sub>

## A. This figures assumes:

- 1. A valid external pull-up voltage is connected to the PULL\_UPx inputs (1.6V  $\leq$  V<sub>PULL\_UPx</sub>  $\leq$  7V).

- 2.  $V_{IN(STEADY-SATE)}$  is a valid  $V_{IN}$  voltage between 3V to 14V.

- 3.  $V_{\overline{FAULT}}$  pull up to VLDO.

- 4. Device is in the: Waiting to Sequence UP State (Refer to State Machine for more details).

- $5. \quad V_{OL} \, represents: V_{OL\_SEQ\_DONE}, \, and \, V_{OL\_PWRGD}, \, or \, the \, low \, logic \, output \, voltage \, for \, all \, outputs.$

Submit Document Feedback

## 7.3.2 SENSEx Inputs

## 7.3.2.1 $V_{TH}$ SENSEX and $V_{ONx}$

The TPS7H3014 sequencer integrates four under-voltage (UV) comparators, with an accurate ( $\pm 1\%$ ) threshold voltage ( $V_{TH\_SENSEx}$ ) of 599mV nominal.  $V_{TH\_SENSEx}$  is measured at the ENx outputs to account for comparator offsets in the threshold. Maximum flexibility is provided as external resistive dividers can be adjusted to sense any voltage rail ( $V_{OUTx}$ ). Figure 7-2 shows a conceptual diagram of the comparators connected to the SENSEx inputs. As can be observed, the sensed voltage rail ( $V_{OUTx}$ ) is attenuated (using an external resistive divider,  $R_{TOPx}$  and  $R_{BOTTOMx}$ ) and compared against the  $V_{TH\_SENSEx}$  voltage. Is recommended to maintain the steady-state SENSEx voltage below 1.6V, in order to maintain the threshold ( $V_{TH\_SENSEx}$ ) accuracy.

Figure 7-2. SENSEx Comparators Inputs

When the voltage at the monitored rail  $(V_{OUTx})$  is rising, the hysteresis current  $(I_{HYS})$  is not connected to SENSEx input. At this time the SENSEx (attenuated  $V_{OUTx}$ ) voltage is compared against the SENSEx threshold  $(V_{TH\_SENSEx})$ . When  $V_{SENSEx} > V_{TH\_SENSEx}$  the voltage is considered within regulation limits. We can calculate the on (within regulation) voltage by doing a simple voltage divider as:

$$V_{ONx\_NOMINAL}$$

$\left(V\right) = \left(1 + \frac{R_{TOPx}}{R_{BOTTOMx}}\right) \times V_{TH\_SENSEx}$  (1)

Where:

V<sub>TH SENSEx</sub> is the nominal sense threshold voltage of 599mV.

As with any system, there is some variation (or errors) of the design variables, in this case the top and bottom resistors and the SENSEx threshold voltage. Using the derivative method to calculate the total error (and assuming these variables are uncorrelated) with both resistors having the same tolerance value, the  $V_{ONx}$  error can be calculated as:

$$V_{\text{ONx\_ERROR}} \left( V \right) = \pm \sqrt{\frac{V_{\text{TH\_SENSEx}}^2 \times \left[ \left( 2 \times R_{\text{TOL}}^2 \times R_{\text{TOPx}}^2 \right) + \left( V_{\text{TH\_SENSEx\_ACC}}^2 \times \left( R_{\text{TOPx}} + R_{\text{BOTTOMx}} \right)^2 \right) \right]}{R_{\text{BOTTOMx}}^2}$$

(2)

#### Where:

- R<sub>TOL</sub> is the resistors tolerance (same for top and bottom resistors) as numeric value. For example, for 0.1% tolerance resistors, we use 0.001.

- V<sub>TH\_SENSEx\_ACC</sub> is the SENSEx threshold accuracy as numeric value (in this case 0.01).

- $R_{TOPx}$  and  $R_{BOTTOMx}$  are in Ohms ( $\Omega$ ).

- V<sub>TH</sub> SENSEx is 0.599 Volts.

Using Equation 1 and Equation 2 we can calculate the on voltage range as:

$$V_{ONx} = V_{ONx\_NOMINAL} \pm V_{ONx\_ERROR}$$

(3)

#### Note

Remember  $V_{TH\_SENSEx}$  is the reference voltage when accounting for the comparator offsets  $V_{TH\_SENSEx} = V_{REF} + V_{OFFSETx}$ .

As this device is intended for sequencing of multirail systems, the ENx to SENSEx order is defined in ascending channel number (EN1 to EN4) for sequence up, and descending (EN4 to EN1) for sequence down. When a channel of the sequencer is not needed (unused) the channel can be connected to VLDO to skip the channel during sequence up/down. Is recommended to connect all disabled channels to VLDO, but an external voltage greater than 91% of VLDO (max) will disabled the channel (the voltage at SENSEx cannot exceed 3.5V). Only channels 2 through 4 can be disabled. It is recommended to disabled channels starting from high (channel #4) to low (channel #2). The channels are disabled starting from the lowest channel count and higher. This means that if channel #2 is disabled, by definition channels #3 and #4 will also be disabled.

#### Note

The channels to be disabled must be valid at power up and not be dynamically changed during the sequence up and down.

Any voltage at SENSE 2 to SENSE4 >  $V_{TURN\_OFF}$  [91% of VLDO(max)] will disable (or turn-off) the channel. This will disable the delay (set by TMR DLY) for those channels during sequence up and down.

Although it is not required, in noisy applications it is good analog design practice to place a small bypass capacitor at the SENSEx inputs in order to reduce sensitivity to transient voltages on the monitored signal.

## 7.3.2.2 I<sub>HYS SENSEx</sub> and V<sub>OFFx</sub>

The TPS7H3014 has a built-in hysteresis current of  $24\mu A$  with an accuracy of  $\pm 3\%$  (with  $R_{HYS} = 50k\Omega$ ). The hysteresis current is equivalent to REFCAP/ $R_{HYS}$ . A tolerance of 0.1% for the  $R_{HYS}$  is recommended as it ultimately affects the hysteresis current accuracy. This current is mirrored internally across all SENSEx inputs. This hysteresis current becomes active when the SENSEx voltage is greater than the threshold voltage (599mV  $\pm 1\%$ ), same as  $V_{OUTx} > V_{ONx}$  (Refer to Equation 3 and Figure 7-2). This current ( $I_{HYS}$ ) multiplied by the  $R_{TOPx}$  resistance induces a voltage ( $V_{HYSx}$ ) that is added to the SENSEx node, effectively boosting (incrementing) the node voltage. During sequence down, or an undervoltage event when the  $V_{OUTx}$  is decrementing, it will need to drop below the  $V_{OFF}$  voltage in order to be considered as an out of regulation (or fault). The hysteresis voltage is defined as:

$$V_{HYSX \ NOMINAL} \ (V) = I_{HYS \ SENSEX} \times R_{TOPX}$$

(4)

#### Where:

- $I_{HYS SENSEx} = 24 \times 10^{-6}$  Amps (or  $24\mu$ A)

- R<sub>TOPx</sub> units are in Ohms (Ω)

The "off" voltage (or out of regulation) voltage can be calculated as:

$$V_{OFFx \ NOMINAL} \ (V) = V_{ONx \ NOMINAL} - V_{HYSx \ NOMINAL}$$

(5)

Submit Document Feedback

### Using Equation 1 and Equation 5

$$V_{OFFx\_NOMINAL}\left(V\right) = \left[\left(1 + \frac{R_{TOPx}}{R_{BOTTOMx}}\right) \times V_{TH\_SENSEx}\right] - \left(I_{HYS\_SENSEx} \times R_{TOPx}\right)$$

(6)

#### Where:

- V<sub>TH SENSEx</sub> is the nominal sense threshold voltage of 0.599V

- $I_{HYS} = 24 \times 10^{-6} \text{ Amps (or } 24\mu\text{A)}$

- R<sub>TOPx</sub> and R<sub>BOTTOMx</sub> units are in Ohms (Ω)

The V<sub>OFF</sub> error (using the derivative method and assuming all variables are uncorrelated) can be calculated as:

$$V_{OFFx\_ERROR}\left(V\right) = \pm \sqrt{\frac{A+B+C+D}{R_{BOTTOMx}^2}}$$

(7)

Where the equation terms are:

$$A = I_{HYS\_SENSEx}^{2} \times I_{HYS\_SENSEx\_ACC}^{2} \times R_{TOPx}^{2} \times R_{BOTTOMx}^{2}$$

(8)

$$B = R_{TOL}^2 \times R_{TOPx}^2 \times V_{TH SENSEx}^2$$

(9)

$$C = R_{TOL}^{2} \times R_{TOPx}^{2} \times \left[ \left( I_{HYS \ SENSEx} \times R_{BOTTOMx} \right) - V_{TH \ SENSEx} \right]^{2}$$

(10)

$$D = V_{TH SENSEx}^{2} \times V_{TH SENSEx ACC}^{2} \times (R_{TOPx} + R_{BOTTOMx})^{2}$$

(11)

#### Where:

- R<sub>TOL</sub> is the resistors tolerance (same for top and bottom resistors) as numeric value. For example, for 0.1% tolerance resistors, we use 0.001.

- V<sub>TH SENSEx ACC</sub> is the SENSEx threshold accuracy as numeric value (in this case 0.01).

- I<sub>HYS SENSEx ACC</sub> is the hysteresis current accuracy as numeric value (in this case 0.03)

- V<sub>TH</sub> SENSEx is the nominal sense threshold voltage of 0.599V

- $I_{HYS} = 24 \times 10^{-6} \text{ Amps (or } 24\mu\text{A)}$

- $R_{TOPx}$  and  $R_{BOTTOMx}$  units are in Ohms ( $\Omega$ )

$$V_{OFFx} = V_{OFFx\_NOMINAL} \pm V_{OFFx\_ERROR}$$

(12)

Using Equation 6 and Equation 7 we can calculate the off voltage range as:

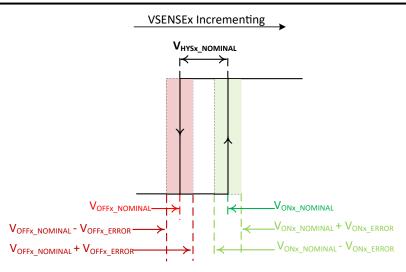

Figure 7-3, shows a conceptual diagram of the rising and falling voltage, it also shows the errors on this voltage due to  $V_{TH}$  accuracy,  $I_{HYS}$  accuracy, and the resistive divider tolerances. At the system level, these errors have to be taken into account for a robust design.

Figure 7-3. Rising and Falling Thresholds Voltages for the SENSE<sub>x</sub> Comparators

## 7.3.2.3 Top and Bottom Resistive Divider Design Equations

At the system level the designer knows (or selects) the  $V_{ONx}$  and  $V_{OFFx}$  levels. Usually these voltages are selected as percentages of the nominal rail voltage ( $V_{OUTx}$ ) being monitored. Knowing this information, we can calculate the resistive divider components values ( $R_{TOPx}$  and  $R_{BOTTOMx}$ ) for the desired target levels. Using Equation 4 and Equation 5 we can calculate the top resistor as:

$$R_{TOPx} = \frac{V_{ONx} - V_{OFFx}}{I_{HYS SENSEx}}$$

(13)

From Equation 1 we can calculate the bottom resistor as:

$$R_{BOTTOMx} = \frac{R_{TOPx} \times V_{TH\_SENSEx}}{V_{ONx} - V_{TH\_SENSEx}}$$

(14)

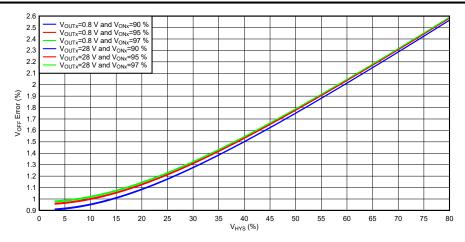

It's important to notice that the larger the separation between  $V_{ONx}$  and  $V_{OFFx}$  (referred as  $V_{HYSx}$ ), the bigger the error in the off voltage. Figure 7-4 shows a plot of the error in the  $V_{OFFx}$  for different hysteresis voltages ( $V_{HYSx} = V_{ONx} - V_{OFFx}$ ). The plot is created for three different  $V_{ON}$  voltages (or percentages of the nominal output voltage: 90, 95, and 97%) and two different output voltages (0.8V and 28V). As can be observed, the output voltage has very little impact on the off voltage error (differences cannot be appreciated on the plot). The error (in percent) can go from approximately 1% (at  $V_{HYS} = 3\%$ ) to around 2.6% (at  $V_{HYS} = 80\%$ ).

Submit Document Feedback

Figure 7-4. V<sub>OFFx</sub> Error vs V<sub>HYS</sub>

- A. This plot does not includes the error on the V<sub>OFFx</sub> due to the difference between the calculated top and bottom resistors using Equation 13 and Equation 14 and the actual resistance values that a designer can procure.

- B. The resistor tolerance used for the calculation is 0.1%,  $V_{TH\_SENSEx}$  accuracy is 1%, and the  $I_{HYS\_SENSEx}$  accuracy is 3%.

- C. In this plot the V<sub>HYS</sub> (%) represents the separation as percentages of the nominal output voltage (V<sub>OUTx</sub>).

- D. In this plot, the V<sub>OFF</sub> error in % is normalized with respect to the full-scale voltage (or V<sub>OUTx</sub>).

## 7.3.3 Output Stages (ENx,SEQ\_DONE,PWRGD,PULL\_UP1 and PULL\_UP2)

The output stage's (EN1 to EN4), SEQ\_DONE and PWRGD are of push-pull, active high type. The pull-up voltage for the push-pull outputs is externally provided by the user. PULL\_UP1 (input) is the pull-up voltage domain for all ENx outputs (EN1 to EN4), while PULL\_UP2 (input) is the pull-up voltage domain for the SEQ DONE and PWRGD outputs.

#### Note

There are no sequencing requirements for IN, PULL\_UP1, and PULL\_UP2, however, both must be biased before commanding a sequence up and down.

#### Note

TI recommends to decouple PULL\_UPx inputs with a 1μF ceramic capacitor as close to the pins as possible. This is to ensure clean voltages signals at the outputs (ENx, PWRGD, and SEQ\_DONE).

Each output stage consists of a PMOS/NMOS (CMOS) pair. Each leg has an output resistance of typically  $7\Omega$  for  $V_{PULL\_UPX} > 3.3V$ . PULL\_UP1 and PULL\_UP2, have a voltage range of 1.6V to 7V, and can be independently biased or tied to the same voltage rail, however both most be biased. The output resistance of the PMOS leg has a PULL\_UPx voltage dependency. The lower the PULL\_UPx voltage, the higher the PMOS resistance.

When  $V_{IN} < V_{POR\_IN}$  and  $V_{PULL\_UPx} > V_{POR\_PULL\_UPx}$  (1.4V maximum) the output will be in a known pull-down state. At this condition the outputs have reduced sinking capabilities with  $V_{OL} \le 320$ mV when the device is sinking 100µA of current into the outputs:

- ENx

- PWRGD

- SEQ\_DONE

Once the input voltage range is withing the recommended input voltage range of 3V to 14 V, the output will have the full strength capabilities of  $\pm 10$ mA, per output.

Figure 7-5. ENx Push-Pull Output Stages

Figure 7-6. SEQ\_DONE Push-Pull Output Stage

Figure 7-7. PWRGD Push-Pull Output Stage

Submit Document Feedback

## 7.3.4 User-Programmable TIMERS

The TPS7H3014 has two global (or common to all SENSEx channels) adjustable timers:

- DLY\_TMR

- REG\_TMR

Both timers are programmed via a single resistor from the DLY\_TMR and REG\_TMR pin to GND. The resistors are used to program the internal oscillator frequency of the timers. Leaving the DLY\_TMR or the REG\_TMR pin floating will disable the timer, respectively. The range for both timers is 250µs to 25ms.

# Note Timers conditions must be valid at power up and must not be dynamically changed.

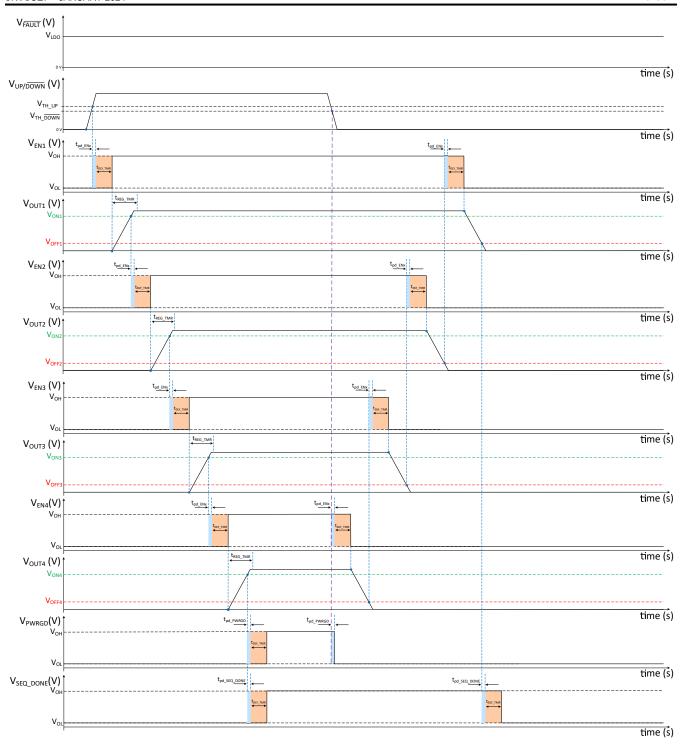

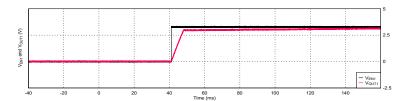

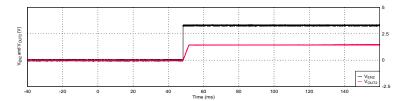

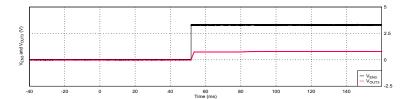

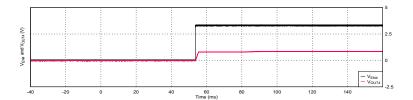

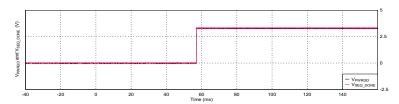

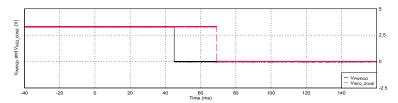

Figure 7-8 shows a sequence up and down assuming no faults and UP/DOWN pins tied together. The DLY\_TMR is shown in orange and the REG\_TMR time is shown with arrows (starting from ENx going high).

Figure 7-8. Sequence UP and DOWN

- A. It's important to notice the t<sub>pd\_ENx</sub>, t<sub>pd\_PWRGD</sub>, and t<sub>pD\_SEQ\_DONE</sub> in blue. This is a propagation delay in the outputs (ENx,PWRGD and SEQ\_DONE). If no DLY\_TMR (floating) is used, the output signals will change to the valid state after this delay. When using the DLY\_TMR, then this time has to be added to the programmed timer time.

- B. The REG\_TMR is only valid during sequence up.

## 7.3.4.1 DLY\_TMR

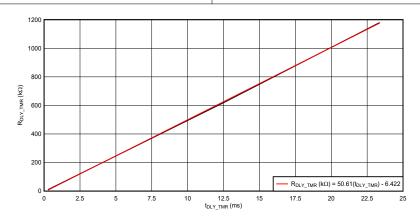

The TPS7H3014 includes an adjustable time delay. A single resistor connected between the DLY\_TMR pin and GND will program the delay. Possible resistor ( $R_{DLY}$ ) values are between 10.5k $\Omega$  and 1.18M $\Omega$  for a 268µs to 23.63ms delay, respectively. During sequence up, this delay holds the EN<sub>x+1</sub>, SEQ\_DONE, and PWRGD low after the monitored voltage crosses the "on" voltage ( $V_{OUTx} > V_{ONx}$ ) for the user programmed time. During sequence down, the EN<sub>x-1</sub> and SEQ\_DONE are held high for the programmed delay time after the monitored voltage crosses the "off" voltage ( $V_{OUTx} < V_{OFFx}$ ).

#### Note

During sequence down, PWRGD goes low immediately after the  $V_{\overline{DOWN}} < V_{TH}$   $\overline{DOWN}$ .

If no delay is preferred for the system, the pin (DLY\_TMR) can be left floating. When no delay is preferred, an inherent propagation delay of 6.5 $\mu$ s (max) will be observed during sequence up, between V<sub>OUTx</sub> crossing the V<sub>ONx</sub> and EN<sub>x+1</sub> going high. The propagation delay is also observed during sequence down when V<sub>OUTx</sub> cross the V<sub>OFFx</sub> and the EN<sub>x-1</sub> is forced low. SEQ\_DONE and PWRGD also have this propagation delay during V<sub>OUT4</sub> > V<sub>ON4</sub> during sequence up. During sequence down, SEQ\_DONE will go low after the propagation delay when V<sub>OUT1</sub> < V<sub>OFF1</sub> and PWRGD will go low after the propagation delay when the sequence down is commanded. Figure 7-8 shows the propagation delay in blue ( $t_{pd\_ENx}$ ,  $t_{pd\_SEQ\_DONE}$ ,  $t_{pd\_PWRGD}$ ) and the programmed delay ( $t_{DLY\_TMR}$ ) in orange. The DLY\_TMR resistor can be selected using Equation 15. Figure 7-9 shows the linear trend between the DLY\_TMR resistor and the delay time.

$$R_{\text{DLY\_TMR}}(k\Omega) = \left[50.61 \times t_{\text{DLY\_TMR}}(ms)\right] - 6.422 \tag{15}$$

Table 7-1 shows nominal resistors value for different delay times.

Table 7-1. Typical DLY TMR Resistors

| Delay (ms) | $R_{DLY\_TMR}$ (k $\Omega$ ) |  |  |  |

|------------|------------------------------|--|--|--|

| 0.268      | 10.5                         |  |  |  |

| 12.5       | 619                          |  |  |  |

| 23.37      | 1180                         |  |  |  |

Figure 7-9. R<sub>DLY TMR</sub> vs t<sub>DLY TMR</sub> Across Full Oscillator Range

## 7.3.4.2 REG\_TMR

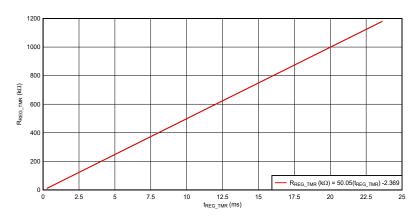

The REG\_TMR (for regulation timer) is an adjustable time monitor that monitors the time it takes to V<sub>OUTx</sub> > V<sub>ONx</sub>. The user can program the REG\_TMR using a single resistor between REG\_TMR and GND. The range of the resistor ( $R_{REG}$ ) is between 10.5k $\Omega$  to 1.18M $\Omega$ , for a 264 $\mu$ s to 23.63ms, respectively. If the user does not want the REG\_TMR to be active, the pin can be left floating. In this case,  $V_{OUTx}$  has infinite time to cross the  $V_{ONx}$ voltage. The REG\_TMR is only active during the sequence up.

#### Note

If the REG\_TMR is left floating and the V<sub>ONx</sub> voltage is never crossed, the state machine will stay waiting indefinitely.

If active, the REG\_TMR will monitor the time a V<sub>OUTx</sub> takes to cross the V<sub>ONx</sub> voltage once the ENx signal is forced high. In the case the REG\_TMR is expired and V<sub>OUTx</sub> has not crossed the V<sub>ONx</sub> voltage, a reverse sequence down from the previously sequenced rail will be started as described in the State Machine section. Figure 7-8 shows the REG\_TMR active during sequence up, from the time ENx is forced high (V<sub>OUTx</sub> starts rising). In this case, V<sub>OUTx</sub> always crosses V<sub>ON</sub> before the timer is expired. The REG\_TMR resistor can be selected using Equation 16. Figure 7-10 shows the linear trend between the REG\_TMR resistor and the regulation time allowed for the rail to be in regulation ( $V_{OUTx} > V_{ONx}$ ).

$$R_{\text{DLY\_TMR}}(k\Omega) = \left[50.05 \times t_{\text{DLY\_TMR}}(ms)\right] - 2.369 \tag{16}$$

Table 7-2 shows typical resistor values for different allowed regulation times.

Table 7-2. Typical REG TMR Resistors

| Allowed Regulation Time (ms) | R <sub>REG_TMR</sub> (kΩ) |

|------------------------------|---------------------------|

| 0.264                        | 10.5                      |

| 12.4                         | 619                       |