# **TPS99000S-Q1 System Management and Illumination Controller**

#### 1 Features

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Temperature grade 2: –40°C to 105°C ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- **Functional Safety Quality-Managed**

- Documentation available to aid ISO 26262 functional safety system design up to ASIL-B

- Automotive system management device for TI DLP® Products:

- Advanced power monitoring, sequencing, and protection circuits

- Two die temperature monitors, MCU external watchdog timer, clock frequency monitor

- System over-brightness detection

- SPI port with parity, checksum, and password register protection

- Second SPI port for independent system monitoring

- On-chip DMD mirror voltage regulators

- Generates +16-V, +8.5-V and -10-V DMD control voltages

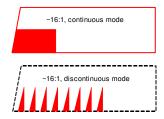

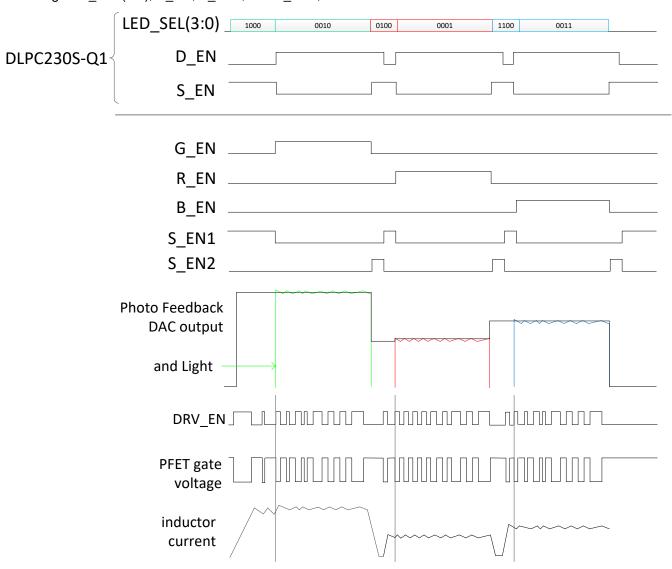

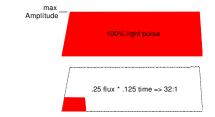

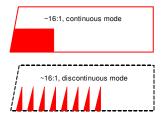

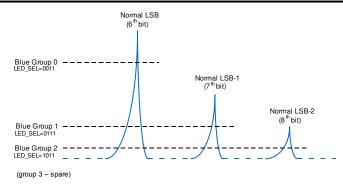

- High dynamic range dimming and color control, enabling > 5000:1 dimming range with high bit depth and white color balance:

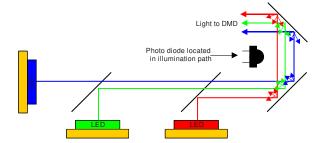

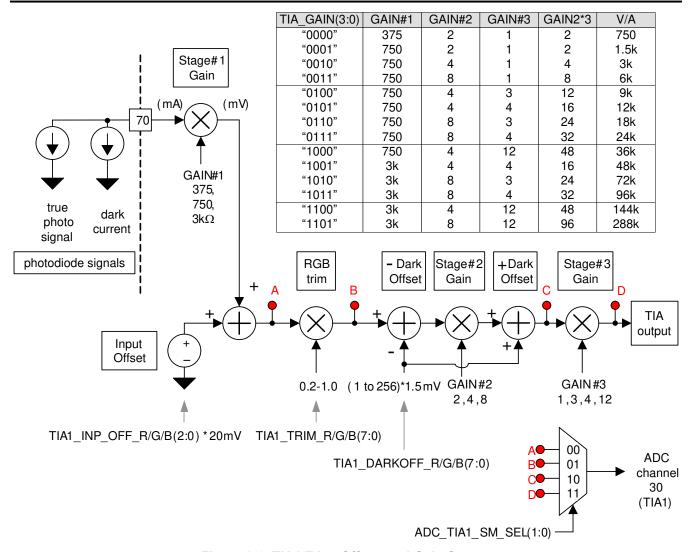

- Two transimpedance amplifiers (TIA) with wide dynamic range supporting numerous optical designs

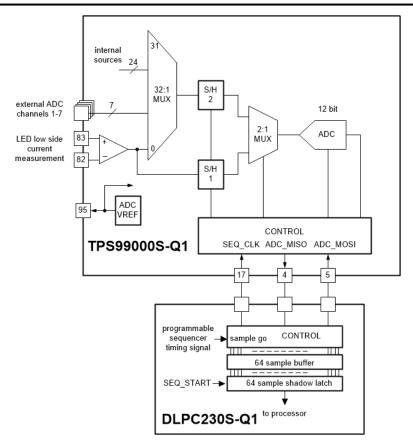

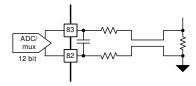

- 12-bit ADC with up to 63 time sequence samples per frame

- DAC and comparator functions for color and pulse control

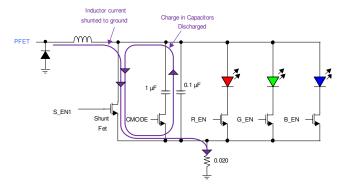

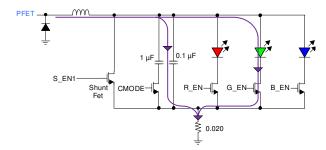

- FET drivers for LED and shunt control

### 2 Applications

- Wide field of view and augmented reality head-up display (HUD) systems

- Digital cluster, navigation, and infotainment windshield displays

#### 3 Description

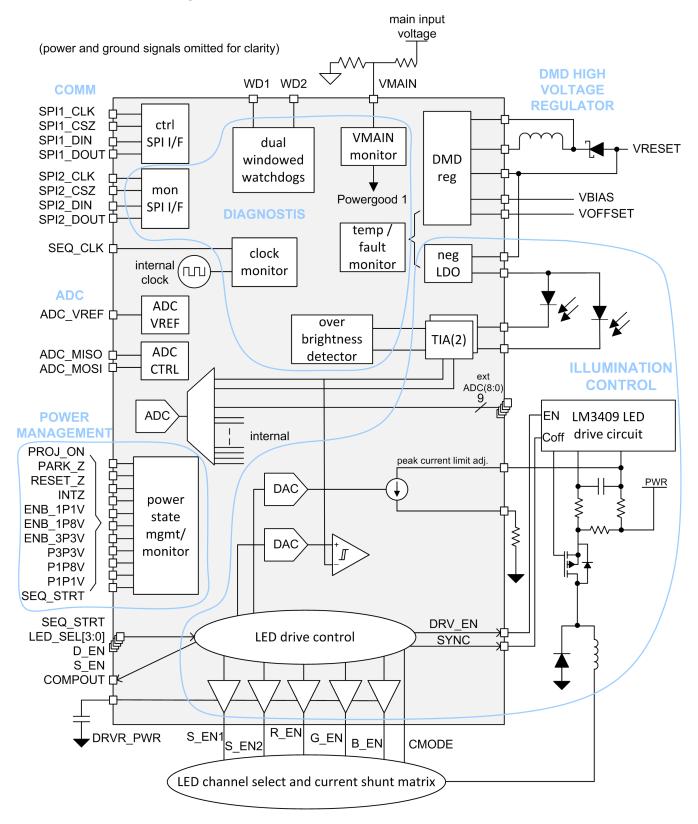

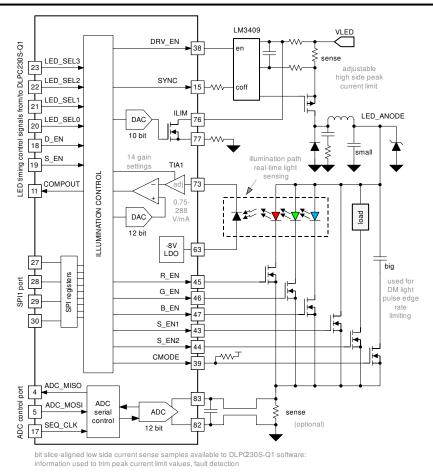

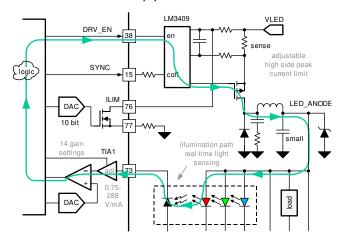

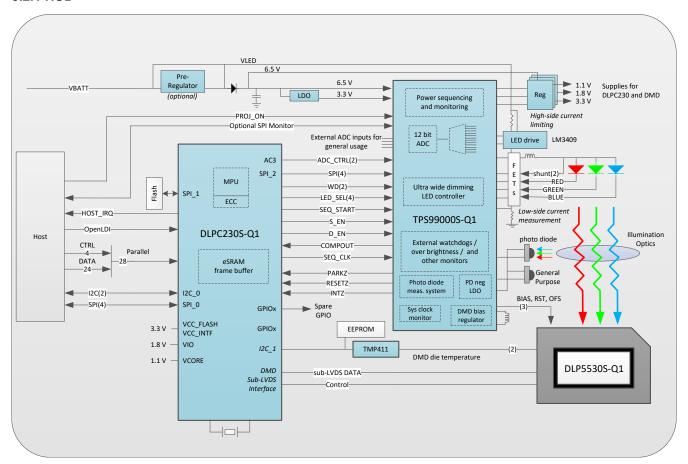

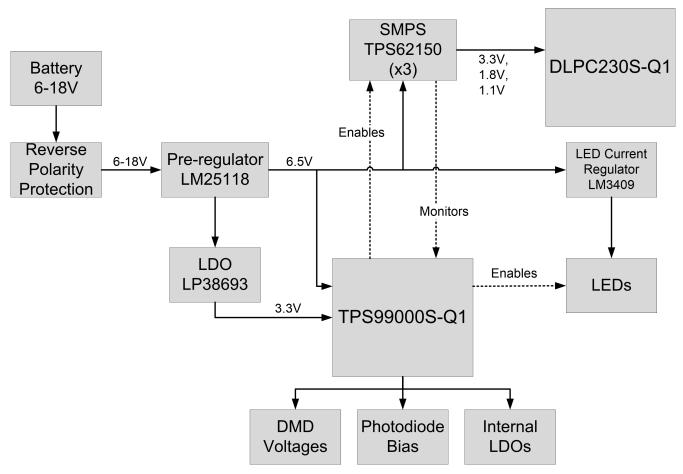

TPS99000S-Q1 system management and illumination controller is part of the DLP553x-Q1 chipset, which also includes the DLPC230S-Q1 DMD display controller. The chipset provides all functions needed to support and exceed typical 5000:1 display dimming requirements for Head-Up Display (HUD) applications, with typical requirements of 3 to 15,000 nits brightness range and tight color point control.

An integrated DMD high-voltage regulator supplies DMD mirror reference voltages, meeting the required tight tolerances. The power supply sequencer and monitor provide robust coordination of power-up and power-down events for the entire chipset.

The TPS99000S-Q1 illumination controller integrates a 12-bit ADC, two DACs (12-bit and 10-bit), and two high-performance photodiode signal conditioning transimpedance amplifiers (TIAs) as the core components of the illumination control system. The ADC is capable of automatic sampling up to 63 events per video frame.

Advanced system status monitoring circuits provide real-time visibility into display sub-system operational condition, including two processor watchdog circuits, two die temperature monitors, comprehensive supply for overvoltage and detection, checksum and password register protection with byte-level parity on SPI bus transactions, an excessive brightness monitor circuit, and other built-in test functions.

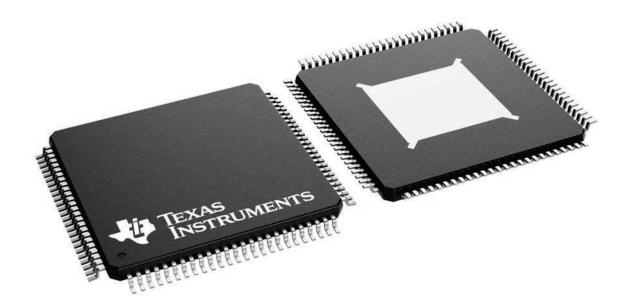

#### **Device Information**

| PART NUMBER  | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)     |

|--------------|------------------------|---------------------|

| TPS99000S-Q1 | HTQFP (100)            | 14.00 mm × 14.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

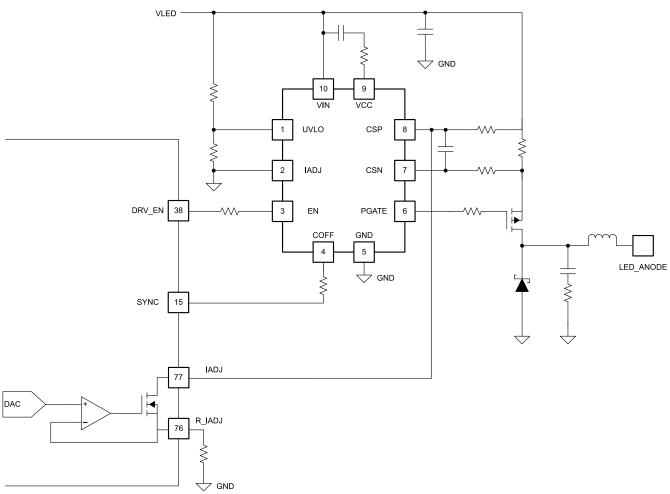

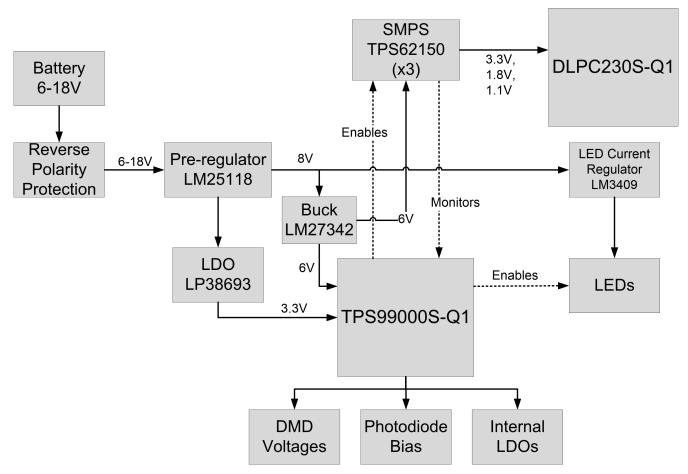

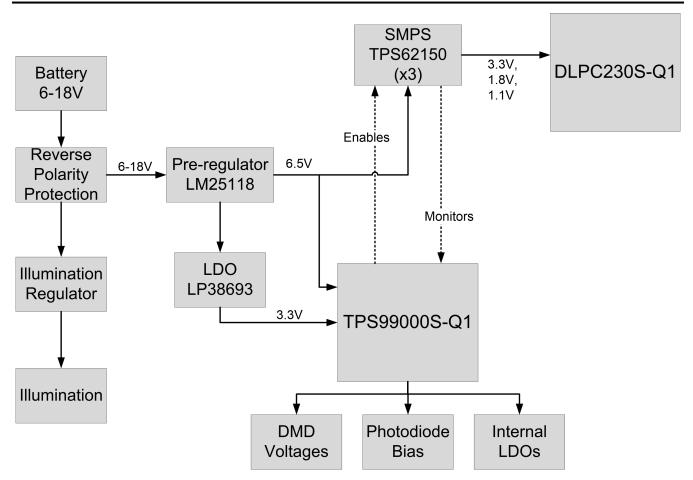

**Typical Standalone System**

## **Table of Contents**

| 1 Features1                                              | 6.15 Timing Requirements - Sequencer Clock           | 24 |

|----------------------------------------------------------|------------------------------------------------------|----|

| 2 Applications1                                          | 6.16 Timing Requirements - Host / Diagnostic Port    |    |

| 3 Description1                                           | SPI Interface                                        | 25 |

| 4 Revision History2                                      | 6.17 Timing Requirements - ADC Interface             | 25 |

| 5 Pin Configuration and Functions3                       | 6.18 Switching Characteristics                       | 25 |

| Pin Functions - Initialization, Clock, and Diagnostics4  | 7 Detailed Description                               | 27 |

| Pin Functions - Power and Ground5                        | 7.1 Overview                                         | 27 |

| Pin Functions - Power Supply Management6                 | 7.2 Functional Block Diagram                         | 28 |

| Pin Functions - Illumination Control7                    | 7.3 Feature Description                              | 29 |

| Pin Functions - Serial Peripheral Interfaces8            | 7.4 Device Functional Modes                          | 54 |

| Pin Functions - Analog to Digital Converter9             | 7.5 Register Maps                                    | 56 |

| 6 Specifications10                                       | 8 Application and Implementation                     | 59 |

| 6.1 Absolute Maximum Ratings10                           | 8.1 Application Information                          | 59 |

| 6.2 ESD Ratings10                                        | 8.2 Typical Applications                             | 59 |

| 6.3 Recommended Operating Conditions10                   | 9 Power Supply Recommendations                       |    |

| 6.4 Thermal Information11                                | 9.1 TPS99000S-Q1 Power Supply Architecture           | 69 |

| 6.5 Electrical Characteristics - Transimpedance          | 9.2 TPS99000S-Q1 Power Outputs                       | 69 |

| Amplifier Parameters12                                   | 9.3 Power Supply Architecture                        | 69 |

| 6.6 Electrical Characteristics - Digital to Analog       | 10 Layout                                            |    |

| Converters14                                             | 10.1 Layout Guidelines                               | 73 |

| 6.7 Electrical Characteristics - Analog to Digital       | 11 Device and Documentation Support                  | 78 |

| Converter15                                              | 11.1 Device Support                                  |    |

| 6.8 Electrical Characteristics - FET Gate Drivers 16     | 11.2 Receiving Notification of Documentation Updates | 78 |

| 6.9 Electrical Characteristics - Photo Comparator 16     | 11.3 Support Resources                               | 78 |

| 6.10 Electrical Characteristics - Voltage Regulators 17  | 11.4 Trademarks                                      |    |

| 6.11 Electrical Characteristics - Temperature and        | 11.5 Electrostatic Discharge Caution                 |    |

| Voltage Monitors18                                       | 11.6 Glossary                                        | 78 |

| 6.12 Electrical Characteristics - Current Consumption 19 | 12 Mechanical, Packaging, and Orderable              |    |

| 6.13 Power-Up Timing Requirements20                      | Information                                          | 79 |

| 6.14 Power-Down Timing Requirements22                    |                                                      |    |

# **4 Revision History**

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| October 2020 | *        | Initial Release |

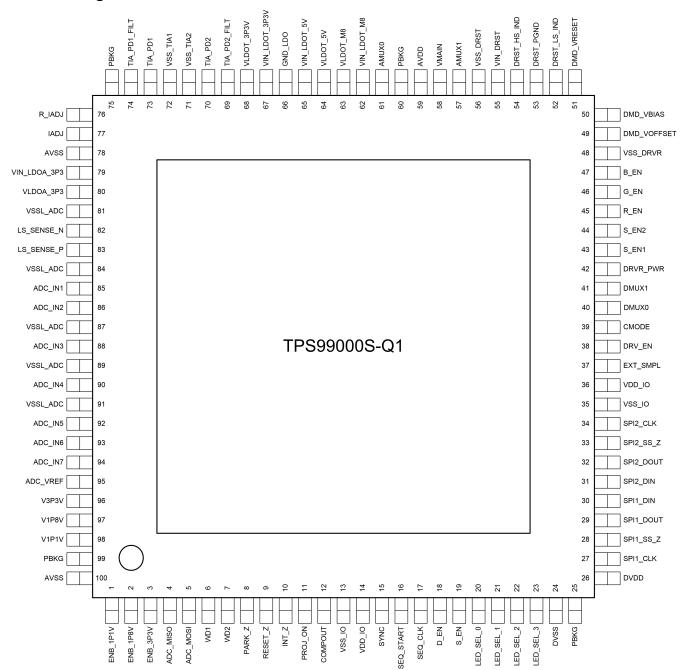

## **5 Pin Configuration and Functions**

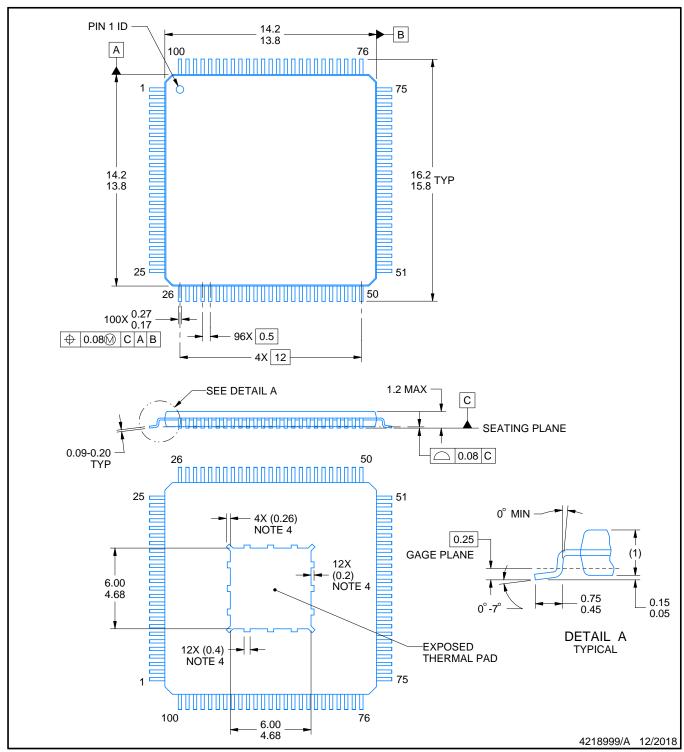

Figure 5-1. PZP Package 100-Pin HTQFP Top View

# Pin Functions - Initialization, Clock, and Diagnostics

| PIN |           | TYPE | DESCRIPTION                                                                                                                                                  |

|-----|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      | ITPE | DESCRIPTION                                                                                                                                                  |

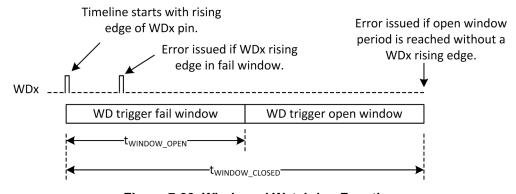

| 6   | WD1       | I    | Watch Dog Interrupt Channel 1                                                                                                                                |

| 7   | WD2       | I    | Watch Dog Interrupt Channel 2                                                                                                                                |

| 8   | PARK_Z    | 0    | DMD Mirror Parking Signal (active low)                                                                                                                       |

| 9   | RESET_Z   | 0    | Reset output to the DLPC230S-Q1. TPS99000S-Q1 controlled.                                                                                                    |

| 10  | INT_Z     | 0    | Interrupt output signal to DLPC230S-Q1 (open drain). Recommended to pull up to the DLPC230S-Q1 3.3 V rail controlled by the TPS99000S-Q1 's ENB_3P3V signal. |

| 11  | PROJ_ON   | I    | Input signal to enable/disable the IC and DLP projector                                                                                                      |

| 16  | SEQ_START | I    | PWM Shadow Latch Control; indicates a Start of Sequence                                                                                                      |

| 17  | SEQ_CLK   | I    | Sequencer Clock                                                                                                                                              |

| 40  | DMUX0     | 0    | Digital test point output                                                                                                                                    |

| 41  | DMUX1     | 0    | Digital test point output                                                                                                                                    |

| 57  | AMUX1     | 0    | Analog Test Mux Output 1                                                                                                                                     |

| 61  | AMUX0     | 0    | Analog Test Mux Output 0                                                                                                                                     |

## **Pin Functions - Power and Ground**

| PIN                |               | T)/DE | PERCEIPTION                                                                                                                                         |  |  |

|--------------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.                | NAME          | TYPE  | DESCRIPTION                                                                                                                                         |  |  |

| 13, 35             | VSS_IO        | GND   | Ground Connection for Digital IO Interface                                                                                                          |  |  |

| 14, 36             | VDD_IO        | POWER | 3.3 V power input for IO rail supply                                                                                                                |  |  |

| 24                 | DVSS          | GND   | Digital Core Ground Return                                                                                                                          |  |  |

| 25, 60, 75, 99     | PBKG          | GND   | Substrate Tie and ESD Ground Return                                                                                                                 |  |  |

| 26                 | DVDD          | POWER | 3.3 V power input for digital core supply                                                                                                           |  |  |

| 42                 | DRVR_PWR      | POWER | 6 V or 3.3 V power input for FET driver power. Supply for S_EN1, S_EN2, R_EN, G_EN, & B_EN outputs                                                  |  |  |

| 48                 | VSS_DRVR      | GND   | Ground Connection for FET driver power                                                                                                              |  |  |

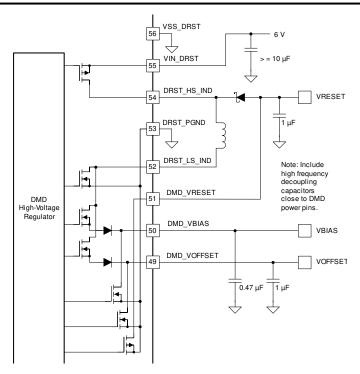

| 49                 | DMD_VOFFSET   | POWER | VOFFSET output rail. Connect a 1µF ceramic capacitor to ground                                                                                      |  |  |

| 50                 | DMD_VBIAS     | POWER | VBIAS output rail. Connect a 0.47µF ceramic capacitor to ground                                                                                     |  |  |

| 51                 | DMD_VRESET    | POWER | VRESET output rail. Connect a 1µF ceramic capacitor to ground. Connect to DRST_HS_IND through external diode. Connect anode of diode to DMD_VRESET. |  |  |

| 53                 | DRST_PGND     | GND   | Power ground for DMD power supply. Connect to ground plane                                                                                          |  |  |

| 55                 | VIN_DRST      | POWER | 6 V input for DMD power supply                                                                                                                      |  |  |

| 56                 | VSS_DRST      | GND   | Ground Supply for DMD power supply                                                                                                                  |  |  |

| 59                 | AVDD          | POWER | 3.3 V power supply input for analog circuit                                                                                                         |  |  |

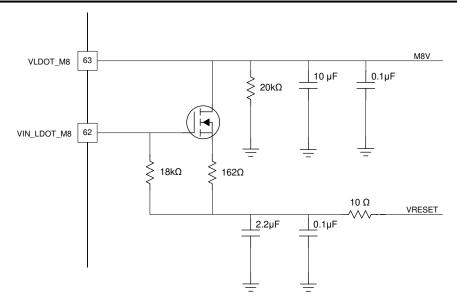

| 63                 | VLDOT_M8      | POWER | Dedicated TIA Interface –8 V LDO output                                                                                                             |  |  |

| 64                 | VLDOT_5V      | POWER | Filter Cap Interface for 5 V TIA LDO                                                                                                                |  |  |

| 65                 | VIN_LDOT_5V   | POWER | 6 V power input for 5 V TIA LDO                                                                                                                     |  |  |

| 66                 | GND_LDO       | GND   | Power ground return for LDO                                                                                                                         |  |  |

| 67                 | VIN_LDOT_3P3V | POWER | 6 V power input for 3.3 V TIA LDO                                                                                                                   |  |  |

| 68                 | VLDOT_3P3V    | POWER | Filter Cap Interface for 3.3 V TIA LDO                                                                                                              |  |  |

| 71                 | VSS_TIA2      | GND   | TIA2 Dedicated Ground                                                                                                                               |  |  |

| 72                 | VSS_TIA1      | GND   | TIA1 Dedicated Ground                                                                                                                               |  |  |

| 78, 100            | AVSS          | GND   | Analog Ground                                                                                                                                       |  |  |

| 79                 | VIN_LDOA_3P3  | POWER | 6 V power input for dedicated ADC interface 3.3 V LDO supply                                                                                        |  |  |

| 80                 | VLDOA_3P3     | POWER | Dedicated ADC Interface 3.3 V LDO Filter Cap Output                                                                                                 |  |  |

| 81, 84, 87, 89, 91 | VSSL_ADC      | GND   | External ADC Channel Bondwire and Lead Frame Isolation Ground                                                                                       |  |  |

| 95                 | ADC_VREF      | POWER | ADC Reference voltage output                                                                                                                        |  |  |

# **Pin Functions - Power Supply Management**

| PIN |             | TYPE | DESCRIPTION                                                                                                         |

|-----|-------------|------|---------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | ITPE | DESCRIPTION                                                                                                         |

| 1   | ENB_1P1V    | 0    | External 1.1 V Buck Enable. 3.3 V Output                                                                            |

| 2   | ENB_1P8V    | 0    | External 1.8 V Buck Enable. 3.3 V Output                                                                            |

| 3   | ENB_3P3V    | 0    | External 3.3 V Buck Enable. 3.3 V Output                                                                            |

| 52  | DRST_LS_IND | ANA  | Connection for the DMD power supply inductor (10µH). Connect a 330pF 50 V capacitor to ground. X7R recommended      |

| 54  | DRST_HS_IND | ANA  | Connection for the DMD power supply inductor (10µH)                                                                 |

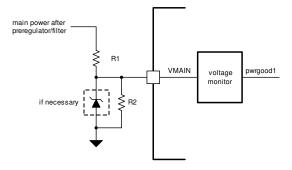

| 58  | VMAIN       | I    | Main intermediate voltage monitor input. Use external resistor divider to set voltage input for brownout monitoring |

| 62  | VIN_LDOT_M8 | 0    | Dedicated TIA Interface –8 V LDO external regulation FET drive signal                                               |

| 96  | V3P3V       | I    | External 3.3 V Buck Voltage Monitor Input                                                                           |

| 97  | V1P8V       | I    | External 1.8 V Buck Voltage Monitor Input                                                                           |

| 98  | V1P1V       | ı    | External 1.1 V Buck Voltage Monitor Input                                                                           |

## **Pin Functions - Illumination Control**

| PIN | PIN          |      | PERMITTION                                                                                                                |  |

|-----|--------------|------|---------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME         | TYPE | DESCRIPTION                                                                                                               |  |

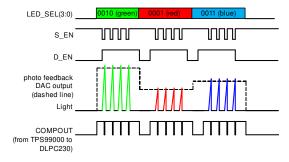

| 12  | COMPOUT      | 0    | Photodiode (PD) Interface High-speed comparator output                                                                    |  |

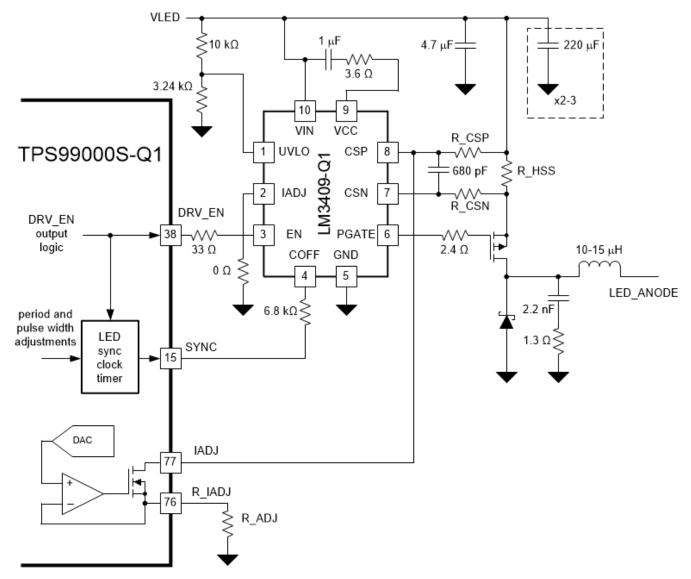

| 15  | SYNC         | 0    | External LED buck driver sync strobe output                                                                               |  |

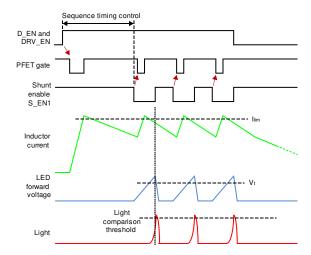

| 18  | D_EN         | I    | LED Interface; Buck High-Side FET Drive Enable                                                                            |  |

| 19  | S_EN         | I    | LED Bypass Shunt Strobe Input                                                                                             |  |

| 20  | LED_SEL_0    | I    | LED Enable Strobe 0 Input                                                                                                 |  |

| 21  | LED_SEL_1    | I    | LED Enable Strobe 1 Input                                                                                                 |  |

| 22  | LED_SEL_2    | I    | LED Enable Strobe 2 Input                                                                                                 |  |

| 23  | LED_SEL_3    | I    | LED Enable Strobe 3 Input                                                                                                 |  |

| 37  | EXT_SMPL     | I    | Reserved. Connect to ground                                                                                               |  |

| 38  | DRV_EN       | 0    | Drive enable for LM3409                                                                                                   |  |

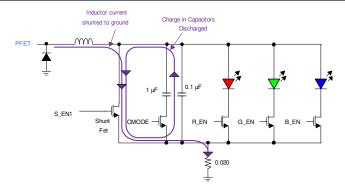

| 39  | CMODE        | 0    | Capacitor selection output (allows for a smaller capacitance to be used in CM mode for less over/under shoot). Open drain |  |

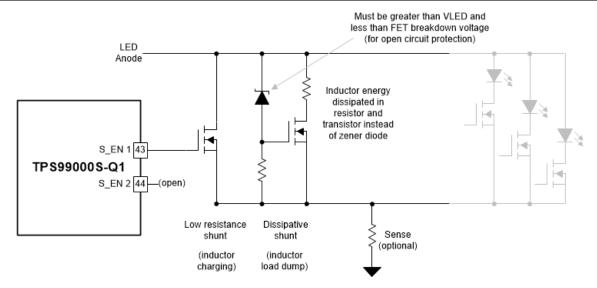

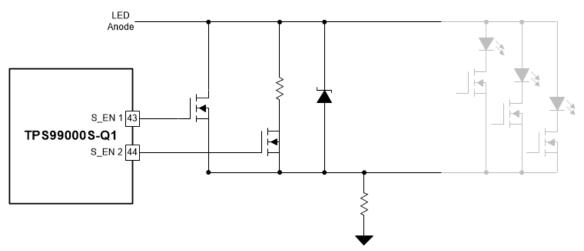

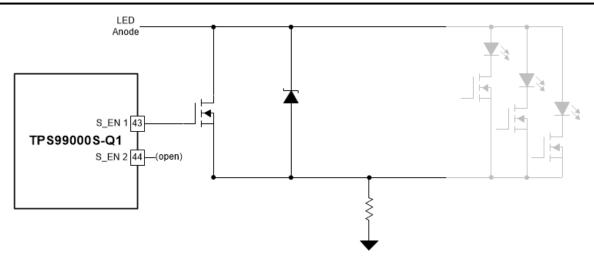

| 43  | S_EN1        | 0    | Low resistance shunt NFET drive enable [High means shunt active]                                                          |  |

| 44  | S_EN2        | 0    | High resistance shunt NFET drive enable [High means shunt active]                                                         |  |

| 45  | R_EN         | 0    | Red channel select. Drive for low side NFET                                                                               |  |

| 46  | G_EN         | 0    | Green channel select. Drive for low side NFET                                                                             |  |

| 47  | B_EN         | 0    | Blue channel select. Drive for low side NFET                                                                              |  |

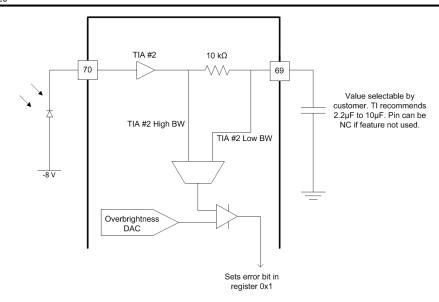

| 69  | TIA_PD2_FILT | 0    | TIA2 External Filter Cap - Low Bandwidth Sampling                                                                         |  |

| 70  | TIA_PD2      | I    | TIA2 Photodiode Cathode Driver                                                                                            |  |

| 73  | TIA_PD1      | I    | TIA1 Photodiode Cathode Driver                                                                                            |  |

| 74  | TIA_PD1_FILT | 0    | TIA1 External Filter Cap - Low Bandwidth Sampling                                                                         |  |

| 76  | R_IADJ       | ANA  | External resistance for IADJ voltage to current transformation                                                            |  |

| 77  | IADJ         | ANA  | Current output used to adjust external LED controller drive current set point                                             |  |

# **Pin Functions - Serial Peripheral Interfaces**

| PIN |           | TYPE | DESCRIPTION                                                                              |

|-----|-----------|------|------------------------------------------------------------------------------------------|

| NO. | NAME      | ITPE | DESCRIPTION                                                                              |

| 27  | SPI1_CLK  | I    | SPI Control interface (DLPC230S-Q1 Master, TPS99000S-Q1 slave), clock input              |

| 28  | SPI1_SS_Z | I    | SPI Control interface (DLPC230S-Q1 Master, TPS99000S-Q1 slave), chip select (active low) |

| 29  | SPI1_DOUT | 0    | SPI Control interface (DLPC230S-Q1 Master, TPS99000S-Q1 slave),<br>Transmit data output  |

| 30  | SPI1_DIN  | I    | SPI Control interface (DLPC230S-Q1 Master, TPS99000S-Q1 slave), Receive data input       |

| 31  | SPI2_DIN  | ı    | SPI Diagnostic Port (slave), Receive data input. For read-only monitoring                |

| 32  | SPI2_DOUT | 0    | SPI Diagnostic Port (slave), Transmit data output. For read-only monitoring              |

| 33  | SPI2_SS_Z | ı    | SPI Diagnostic Port (slave), chip select (active low). For read-only monitoring          |

| 34  | SPI2_CLK  | ı    | SPI Diagnostic Port (slave), clock input. For read-only monitoring                       |

Submit Document Feedback

# Pin Functions - Analog to Digital Converter

| PIN |            | TYPE | DESCRIPTION                                                                 |

|-----|------------|------|-----------------------------------------------------------------------------|

| NO. | NAME       | TYPE | DESCRIPTION                                                                 |

| 4   | ADC_MISO   | 0    | ADC 2-wire Interface - data Output. DLPC230S-Q1 master, TPS99000S-Q1 slave. |

| 5   | ADC_MOSI   | I    | ADC 2-wire Interface - data Input. DLPC230S-Q1 master, TPS99000S-Q1 slave.  |

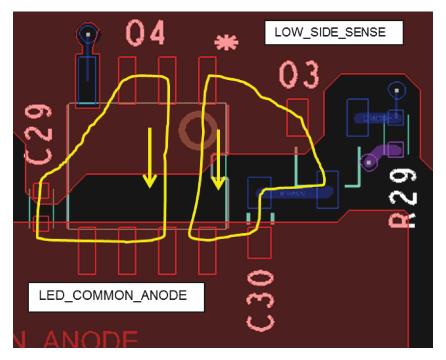

| 82  | LS_SENSE_N | I    | Low side current sense ADC negative input, see Table 7-2                    |

| 83  | LS_SENSE_P | I    | Low side current sense ADC positive input, see Table 7-2                    |

| 85  | ADC_IN1    | I    | External ADC Channel 1, see Table 7-2                                       |

| 86  | ADC_IN2    | ı    | External ADC Channel 2, see Table 7-2                                       |

| 88  | ADC_IN3    | ı    | External ADC Channel 3, see Table 7-2                                       |

| 90  | ADC_IN4    | I    | External ADC Channel 4, see Table 7-2                                       |

| 92  | ADC_IN5    | I    | External ADC Channel 5, see Table 7-2                                       |

| 93  | ADC_IN6    | ı    | External ADC Channel 6, see Table 7-2                                       |

| 94  | ADC_IN7    | I    | External ADC Channel 7, see Table 7-2                                       |

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

| ·          | ,                                                                                                                                                         | MIN  | MAX | UNIT |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

|            | VDD_IO to VSS_IO                                                                                                                                          | -0.3 | 4   |      |

|            | DVDD to DVSS                                                                                                                                              | -0.3 | 4   |      |

|            | AVDD to DVSS                                                                                                                                              | -0.3 | 4   |      |

|            | All "VSS" to other "VSS" (grounds)                                                                                                                        | -0.1 | 0.1 |      |

|            | All digital input signals to ground (WD1, WD2, ADC_MOSI, PROJ_ON, SEQ_START, SEQ_CLK, SPI1_CLK, SPI1_DIN, SPI1_SS, SPI2_DIN, SPI2_CLK, SPI2_SS, EXT_SMPL) | -0.3 | 3.6 |      |

|            | DRVR_PWR to ground                                                                                                                                        | -0.3 | 7.5 |      |

|            | VIN_LDO_5V                                                                                                                                                | -0.3 | 7.5 |      |

|            | V3P3V to ground                                                                                                                                           | -0.3 | 5   |      |

| Input      | V1P8V to ground                                                                                                                                           | -0.3 | 5   |      |

| voltage    | V1P1V to ground                                                                                                                                           | -0.3 | 5   | V    |

|            | VIN_LDOA_3P3 to ground                                                                                                                                    | -0.3 | 7.5 |      |

|            | VIN_LDOT_3P3 to ground                                                                                                                                    | -0.3 | 7.5 |      |

|            | ADC_IN(7:1) to ground                                                                                                                                     | -0.3 | 3.6 |      |

|            | LS_SENSE_N and LS_SENSE_P to ground                                                                                                                       | -0.3 | 3.6 |      |

|            | IADJ to ground                                                                                                                                            | -0.3 | 18  |      |

|            | R_IADJ to ground                                                                                                                                          | -0.3 | 5   |      |

|            | VIN_LDOT_M8 to ground                                                                                                                                     | -18  | 0.3 |      |

|            | DRST_LS_IND to DRST_PGND                                                                                                                                  | -0.3 | 27  |      |

|            | VIN_DRST to ground                                                                                                                                        | -0.3 | 7.5 |      |

|            | VMAIN                                                                                                                                                     | -0.3 | 7.5 |      |

| Outputs    | INT_Z                                                                                                                                                     | -0.3 | 7.5 | V    |

| Operating  | junction temperature, T <sub>J</sub>                                                                                                                      | -40  | 130 | °C   |

| Storage te | mperature, T <sub>stg</sub>                                                                                                                               | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                            |                                          |             | VALUE | UNIT |

|--------------------|----------------------------|------------------------------------------|-------------|-------|------|

|                    |                            | Human-body model (HBM), per AEC Q100-002 | 0(1)        | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged-device model (CDM), per AEC      | All pins    | ±500  | V    |

|                    | a.55a.g5                   | Q100-011                                 | Corner pins | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                              | MIN | NOM MAX | UNIT |

|----------------|----------------------------------------------|-----|---------|------|

| TEMPERATUR     | RE                                           |     |         |      |

| T <sub>A</sub> | Operating ambient temperature <sup>(1)</sup> | -40 | 105     | °C   |

| T <sub>J</sub> | Operating junction temperature               | -40 | 125     | °C   |

| VOLTAGE        |                                              |     |         |      |

Submit Document Feedback

over operating free-air temperature range (unless otherwise noted)

|               |                                     | MIN | NOM | MAX | UNIT |

|---------------|-------------------------------------|-----|-----|-----|------|

| VDD_IO        | IO 3.3 V Voltage Supply             | 3   | 3.3 | 3.6 | V    |

| DVDD          | Digital 3.3 V Supply                | 3   | 3.3 | 3.6 | V    |

| AVDD          | Analog 3.3 V Supply                 | 3   | 3.3 | 3.6 | V    |

| ADC           | ADC(7:1) Inputs                     | 0.1 |     | 1.6 | V    |

| VIN_DRST      | DMD Reset Regulator Input           | 5.5 | 6   | 7   | V    |

| VIN_LDOT_5V   | Power supply input to 5 V TIA LDO   | 5.5 | 6   | 7   | V    |

| VIN_LDOA_3P3V | Power supply input to 3.3 V ADC LDO | 5.5 | 6   | 7   | V    |

| VIN_LDOT_3P3V | Power supply input to 3.3 V TIA LDO | 5.5 | 6   | 7   | V    |

| DRVR_PWR      | Gate driver power supply            | 3   | 6   | 7   | V    |

<sup>(1) -40°</sup>C to 105°C ambient, free air convection, AEC Q100 grade 2.

#### **6.4 Thermal Information**

|                       |                                              | TPS99000S-Q1 |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup> (2)            | PZP (HTQFP)  | UNIT |

|                       |                                              | 100 PINS     |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 6.9          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.3          | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.1          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 8.2          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.4          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

<sup>(2)</sup> Operating ambient temperature is dependent on system thermal design. Operating junction temperature may not exceed its specified range across ambient temperature conditions.

# **6.5 Electrical Characteristics - Transimpedance Amplifier Parameters**

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                             | TEST CONDITIONS                                                              | MIN   | TYP  | MAX              | UNIT |

|------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|-------|------|------------------|------|

| TIA1 AND TIA2          |                                                       |                                                                              |       |      |                  |      |

| I <sub>IN_TOT</sub>    | TIA1 and TIA2 Combined Input<br>Current               |                                                                              | 0     |      | 7 <sup>(3)</sup> | mA   |

| TRANSIMPEDAN           | CE AMPLIFIER #1 (TIA1)                                |                                                                              |       |      |                  |      |

| I <sub>IN</sub>        | TIA Input Current                                     | RGB trim <= 0.5x <sup>(1)</sup>                                              | 0     | 0.6  | 4.8              | mA   |

| C <sub>IN</sub>        | Total Input Capacitance <sup>(2)</sup>                | Allowable input capacitances from board, connectors, photo diode, and cables | 10    | 50   | 140              | pF   |

| TRIM <sub>RGB</sub>    | RGB Trim, normal flux system                          |                                                                              | 0.2   | 0.5  | 1                | V/V  |

| GAINTOL <sub>ABS</sub> | TIA Gain Tolerance (absolute)                         | Tolerance to specified gain target per setting                               | -20%  |      | 20%              |      |

| GAINTOL <sub>REL</sub> | TIA Gain Tolerance (relative)                         | Tolerance as a ratio to other settings                                       |       | 3%   |                  |      |

| TIA1 SLEW RATE         |                                                       |                                                                              |       |      |                  |      |

| TIA <sub>SLEW1</sub>   | Low Gain Slew Rate, Output<br>Referred                | <= 96 kV/A gain                                                              | 12    |      |                  | V/µs |

| TIA <sub>SLEW2</sub>   | High Gain Slew Rate, Output<br>Referred               | > 96 kV/A gain                                                               | 5     |      |                  | V/µs |

| TIA <sub>DELAY</sub>   | TIA Pad to COMPOUT Pad Delay,<br>DM min, Falling Edge | max slew rate input, 20 pF load, 100 mV minimum over trip point              |       | 40   | 64               | ns   |

| TIA <sub>DELAYCM</sub> | TIA Pad to COMPOUT Delay. CM                          | CM max current                                                               |       |      | 100              | ns   |

| TIA1 EFFECTIVE         | GAIN                                                  |                                                                              |       |      |                  |      |

|                        | Gain Setting 0                                        | Trim set to 1.0                                                              | 0.6   | 0.75 | 0.9              | kV/A |

|                        | Gain Setting 1                                        | Trim set to 1.0                                                              | 1.2   | 1.5  | 1.8              | kV/A |

|                        | Gain Setting 2                                        | Trim set to 1.0                                                              | 2.4   | 3    | 3.6              | kV/A |

|                        | Gain Setting 3                                        | Trim set to 1.0                                                              | 4.8   | 6    | 7.2              | kV/A |

|                        | Gain Setting 4                                        | Trim set to 1.0                                                              | 7.2   | 9    | 10.8             | kV/A |

|                        | Gain Setting 5                                        | Trim set to 1.0                                                              | 9.6   | 12   | 14.4             | kV/A |

|                        | Gain Setting 6                                        | Trim set to 1.0                                                              | 14.4  | 18   | 21.6             | kV/A |

|                        | Gain Setting 7                                        | Trim set to 1.0                                                              | 19.2  | 24   | 28.8             | kV/A |

|                        | Gain Setting 8                                        | Trim set to 1.0                                                              | 28.8  | 36   | 43.2             | kV/A |

|                        | Gain Setting 9                                        | Trim set to 1.0                                                              | 38.4  | 48   | 57.6             | kV/A |

|                        | Gain Setting 10                                       | Trim set to 1.0                                                              | 57.6  | 72   | 86.4             | kV/A |

|                        | Gain Setting 11                                       | Trim set to 1.0                                                              | 76.8  | 96   | 115.2            | kV/A |

|                        | Gain Setting 12                                       | Trim set to 1.0                                                              | 115.2 | 144  | 172.8            | kV/A |

|                        | Gain Setting 13                                       | Trim set to 1.0                                                              | 230.4 | 288  | 345.6            | kV/A |

Product Folder Links: TPS99000S-Q1

bmit Document Feedback

|                      | PARAMETER                    | TEST CONDITIONS                 | MIN   | TYP  | MAX   | UNIT |

|----------------------|------------------------------|---------------------------------|-------|------|-------|------|

| TRANSIMPEDA          | NCE AMPLIFIER #2 (TIA2)      |                                 |       |      |       |      |

| I <sub>IN</sub>      | TIA Input Current            | RGB trim <= 0.5x <sup>(1)</sup> | 0     |      | 4.8   | mA   |

| TRIM <sub>RGB</sub>  | RGB Trim, normal flux system |                                 | 0.2   |      | 1     | V/V  |

| TIA2 SLEW RAT        | E                            | <u>'</u>                        |       |      |       |      |

| TIA2 <sub>SLEW</sub> | Slew Rate, Output Referred   | All gains                       | 1     |      |       | V/µs |

| TIA2 EFFECTIV        | E GAIN                       |                                 |       |      |       |      |

|                      | Gain Setting 0               | Trim set to 1.0                 | 0.6   | 0.75 | 0.9   | kV/A |

|                      | Gain Setting 1               | Trim set to 1.0                 | 1.2   | 1.5  | 1.8   | kV/A |

|                      | Gain Setting 2               | Trim set to 1.0                 | 2.4   | 3    | 3.6   | kV/A |

|                      | Gain Setting 3               | Trim set to 1.0                 | 4.8   | 6    | 7.2   | kV/A |

|                      | Gain Setting 4               | Trim set to 1.0                 | 7.2   | 9    | 10.8  | kV/A |

|                      | Gain Setting 5               | Trim set to 1.0                 | 9.6   | 12   | 14.4  | kV/A |

|                      | Gain Setting 6               | Trim set to 1.0                 | 14.4  | 18   | 21.6  | kV/A |

|                      | Gain Setting 7               | Trim set to 1.0                 | 19.2  | 24   | 28.8  | kV/A |

|                      | Gain Setting 8               | Trim set to 1.0                 | 28.8  | 36   | 43.2  | kV/A |

|                      | Gain Setting 9               | Trim set to 1.0                 | 38.4  | 48   | 57.6  | kV/A |

|                      | Gain Setting 10              | Trim set to 1.0                 | 57.6  | 72   | 86.4  | kV/A |

|                      | Gain Setting 11              | Trim set to 1.0                 | 76.8  | 96   | 115.2 | kV/A |

|                      | Gain Setting 12              | Trim set to 1.0                 | 115.2 | 144  | 172.8 | kV/A |

|                      | Gain Setting 13              | Trim set to 1.0                 | 230.4 | 288  | 345.6 | kV/A |

<sup>(1)</sup> Maximum input current decreases linearly in proportion to the selected trim value, with a lower maximum value of 2.4 mA occurring when the trim is 1.0×.

<sup>(2)</sup> Large capacitive loads could impact system performance.

<sup>(3)</sup> For applications requiring greater than 7 mA combined TIA current, contact TI for details.

# 6.6 Electrical Characteristics - Digital to Analog Converters

|                         | PARAMETER                           | TEST CONDITIONS                                                     | MIN         | TYP | MAX  | UNIT          |

|-------------------------|-------------------------------------|---------------------------------------------------------------------|-------------|-----|------|---------------|

| PHOTO FEEDBA            | CK 12 BIT DAC                       |                                                                     |             |     |      |               |

| V <sub>OUTDAC Max</sub> | Output Range max                    |                                                                     | 1.96        | 2   | 2.04 | V             |

| V <sub>OUTDAC Min</sub> | Output Range min                    |                                                                     | -0.1        | 0   | 0.1  | V             |

| t <sub>SET</sub>        | Settling Time                       | Full-range step response, To within ±2%                             | 0           |     | 500  | ns            |

| INL                     | Integral Non-Linearity              |                                                                     | -3.5        |     | 3.5  | LSB           |

| DNL                     | Differential Non-Linearity          |                                                                     | -3.5        |     | 3.5  | LSB           |

| VOFF                    | Offset Error                        |                                                                     | -100        |     | 100  | mV            |

| ZERO <sub>ERR</sub>     | Zero-scale Error                    |                                                                     | -100        |     | 100  | mV            |

| GAIN <sub>ERR</sub>     | Gain Error                          |                                                                     | -5          |     | 5    | %V/code       |

| FS <sub>ERR</sub>       | Full-scale Error                    |                                                                     | -2          |     | 2    | %FSR          |

| ZERO <sub>ERRDFT</sub>  | Zero-scale Error Drift              |                                                                     | -50         | 20  | 50   | μV/°C         |

| GAIN <sub>TEMP</sub>    | Gain Temperature Coefficient        |                                                                     | <b>–</b> 52 | 0   | 52   | ppm<br>FSR/°C |

| CURRENT CONT            | ROL 10 BIT DAC                      |                                                                     |             |     | '    |               |

| V <sub>OUTDAC Max</sub> | Output Range max                    |                                                                     | 1.96        | 2   | 2.04 | V             |

| V <sub>OUTDAC Min</sub> | Output Range min                    |                                                                     | -0.1        | 0   | 0.1  | V             |

| t <sub>SET</sub>        | Settling Time                       | Full-range step response to within ±2%                              | 0           |     | 1000 | ns            |

| INL                     | Integral Non-Linearity              |                                                                     | -2          |     | 2    | LSB           |

| DNL                     | Differential Non-Linearity          |                                                                     | -2          |     | 2    | LSB           |

| V <sub>OFF</sub>        | Offset Error                        |                                                                     | -100        |     | 100  | mV            |

| ZERO <sub>ERR</sub>     | Zero-scale Error                    |                                                                     | -100        |     | 100  | mV            |

| GAIN <sub>ERR</sub>     | Gain Error                          |                                                                     | -5          |     | 5    | %V/code       |

| FS <sub>ERR</sub>       | Full-scale Error                    |                                                                     | -2          |     | 2    | %FSR          |

| ZERO <sub>ERRDFT</sub>  | Zero-scale Error Drift              |                                                                     | -50         | 20  | 50   | μV/°C         |

| GAIN <sub>TEMP</sub>    | Gain Temperature Coefficient        |                                                                     | 52          | 0   | 52   | ppm<br>FSR/°C |

| OVERBRIGHTNE            | SS DETECTOR 8 BIT DAC               |                                                                     |             |     |      |               |

| V <sub>OUTDAC max</sub> | Output Range max                    |                                                                     | 1.95        | 2   | 2.05 | V             |

| V <sub>OUTDAC min</sub> | Output Range min                    |                                                                     | -0.1        | 0   | 0.1  | V             |

| t <sub>OBDAC</sub>      | Over-brightness DAC Adjustment Time | From input code mux input change to 90/10 settling at analog output |             |     | 1000 | μs            |

| INL                     | Integral Non-Linearity              |                                                                     | -1          |     | 1    | LSB           |

| DNL                     | Differential Non-Linearity          |                                                                     | -0.5        |     | 0.5  | LSB           |

| V <sub>OFF</sub>        | Offset Error                        |                                                                     | -100        |     | 100  | mV            |

| ZERO <sub>ERR</sub>     | Zero-scale Error                    |                                                                     | -100        |     | 100  | mV            |

| GAIN <sub>ERR</sub>     | Gain Error                          |                                                                     | <b>–</b> 5  |     | 5    | %V/code       |

| FS <sub>ERR</sub>       | Full-scale Error                    |                                                                     | -3          |     | 3    | %FSR          |

| ZERO <sub>ERRDFT</sub>  | Zero-scale Error Drift              |                                                                     | -50         | 20  | 50   | μV/°C         |

| GAIN <sub>TEMP</sub>    | Gain Temperature Coefficient        |                                                                     | -52         | 0   | 52   | ppm<br>FSR/°C |

# 6.7 Electrical Characteristics - Analog to Digital Converter

|                           | PARAMETER                          | TEST CONDITIONS                           | MIN   | TYP   | MAX   | UNIT |

|---------------------------|------------------------------------|-------------------------------------------|-------|-------|-------|------|

| 12 BIT ADC <sup>(1)</sup> |                                    |                                           |       |       | '     |      |

| V <sub>INPUT</sub>        | Input Range <sup>(2)</sup>         |                                           | 0.1   |       | 1.6   | V    |

| INL                       | Integral Non-Linearity             | Over valid input range VINPUT             | -4    |       | 4     | LSB  |

| DNL                       | Differential Non-Linearity         |                                           | -2.5  |       | 2.5   | LSB  |

| ENOB                      | Effective Number Of Bits           |                                           | 10    | 12    |       | bits |

| t <sub>SAMPLE</sub>       | S/H Sampling Period                |                                           | 0.4   | 5.2   | 12.8  | μs   |

| t <sub>DELAY</sub>        | S/H Delay before conversion starts |                                           | 0.4   |       | 2.8   | μs   |

| t <sub>SHOLD</sub>        | S/H Holding Period                 |                                           |       | 102.4 | 245   | μs   |

| t <sub>CONV</sub>         | Conversion Period                  |                                           |       | 102.4 |       | μs   |

| $V_{REF}$                 | Measurement Reference              | ADC reference voltage is doubled to 1.6 V | 0.784 | 0.8   | 0.816 | V    |

| V <sub>OFFS</sub>         | Offset                             |                                           | -20   |       | 20    | LSB  |

|                           | Gain Error                         | "ADC_IN(7:1) Inputs                       | 2     |       | 2     | %FSR |

<sup>(1)</sup> ADC specifications refer to ADC core behavior, presume ideal clocks and IC input power conditions, unless otherwise noted.

<sup>(2)</sup> Results in invalid ADC codes below 256.

#### 6.8 Electrical Characteristics - FET Gate Drivers

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                   | TEST CONDITIONS                                                        | MIN    | TYP  | MAX    | UNIT |

|------------------|---------------------------------------------|------------------------------------------------------------------------|--------|------|--------|------|

| LED CC           | NTROL SIGNAL FET GATE DRIVERS               |                                                                        |        |      |        |      |

| Q <sub>SEN</sub> | S_EN1/2 Load Gate Charge                    |                                                                        |        | 12   | 16.5   | nC   |

| Z <sub>SEN</sub> | S_EN1/2 Pull-up Gate Drive Output           | 3.3 V domain <sup>(1)</sup>                                            |        | 12.3 |        | Ω    |

|                  | Impedance                                   | 6 V domain <sup>(2)</sup>                                              |        | 10.7 |        | Ω    |

| Z <sub>SEN</sub> | S_EN1/2 Pull-down Gate Drive Output         | 3.3 V domain <sup>(1)</sup>                                            |        | 4.85 |        | Ω    |

|                  | Impedance                                   | 6 V domain <sup>(2)</sup>                                              |        | 4.6  |        | Ω    |

| T <sub>SEN</sub> | S_EN1/2 Pull-up Transition Time             | 3.3 V domain, with max total gate charge load of 2.5 nF <sup>(1)</sup> | 49.5   | 66   | 82.5   | ns   |

|                  |                                             | 6 V domain, with max total gate charge load of 2.5 nF <sup>(2)</sup>   | 45     | 60   | 75     | ns   |

| T <sub>SEN</sub> | S_EN1/2 Pull-down Transition Time           | 3.3 V domain, with max total gate charge load of 2.5 nF <sup>(1)</sup> | 20.25  | 27   | 33.75  | ns   |

|                  |                                             | 6 V domain, with max total gate charge load of 2.5 nF <sup>(2)</sup>   | 18.75  | 25   | 31.25  | ns   |

| Z <sub>RGB</sub> | RGB_EN Pull-up Output Impedance             | 3.3 V domain <sup>(1)</sup>                                            |        | 50.8 |        | Ω    |

|                  |                                             | 6 V domain <sup>(2)</sup>                                              |        | 43.6 |        | Ω    |

| Z <sub>RGB</sub> | RGB_EN Pull-down Output Impedance           | 3.3 V domain <sup>(1)</sup>                                            |        | 4.85 |        | Ω    |

|                  |                                             | 6 V domain <sup>(2)</sup>                                              |        | 4.6  |        | Ω    |

| T <sub>RGB</sub> | RGB_EN Pull-up Falling Transition Time      | 3.3 V domain, with max total gate charge load of 2.5 nF <sup>(1)</sup> | 198.75 | 265  | 331.25 | ns   |

|                  |                                             | 6 V domain, with max total gate charge load of 2.5 nF <sup>(2)</sup>   | 180    | 240  | 300    | ns   |

| T <sub>RGB</sub> | RGB_EN Pull-down Falling Transition<br>Time | 3.3 V domain, with max total gate charge load of 2.5 nF <sup>(1)</sup> | 20.25  | 27   | 33.75  | ns   |

|                  |                                             | 6 V domain, with max total gate charge load of 2.5 nF <sup>(2)</sup>   | 18.75  | 25   | 31.25  | ns   |

- (1) DRVR\_PWR Supply Voltage is between 3 V and 3.6 V.

- (2) DRVR\_PWR Supply Voltage is between 5.5 V and 7.5 V.

## **6.9 Electrical Characteristics - Photo Comparator**

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------|----------------|-----------------|-----|-----|-----|------|

| PHOTO FEEDBACK    | COMPARATOR     |                 |     |     |     |      |

| V <sub>OFF</sub>  | Offset Voltage |                 | -10 |     | 10  | mV   |

| T <sub>HYST</sub> | Hysteresis     |                 | 10  | 20  |     | mV   |

#### www.ti.com

## 6.10 Electrical Characteristics - Voltage Regulators

| PARAMETER              |                                   | TEST CONDITIONS            | MIN    | TYP  | MAX                 | UNIT |

|------------------------|-----------------------------------|----------------------------|--------|------|---------------------|------|

| VOFFSET REGU           | ILATOR                            |                            |        |      |                     |      |

| V <sub>OUT</sub>       | Output Voltage                    | Across load conditions     | 8.25   | 8.5  | 8.75                | V    |

| I <sub>OUT</sub>       | Output Current <sup>(2)</sup>     |                            | 0.1(4) |      | 16.3                | mA   |

| V <sub>PGTHRESHR</sub> | Powergood Threshold, VOUT Rising  |                            |        | 86%  |                     |      |

| V <sub>PGTHRESHF</sub> | Powergood Threshold, VOUT Falling |                            |        | 66%  |                     |      |

| C <sub>OUT</sub>       | Output Capacitor <sup>(3)</sup>   |                            |        | 1    |                     | μF   |

| T <sub>DISC</sub>      | Discharge Time                    | C <sub>OUT</sub> = 1 µF    |        |      | 260                 | μs   |

| VBIAS REGULAT          | ror .                             |                            |        |      |                     |      |

| V <sub>OUT</sub>       | Output Voltage                    |                            | 15.5   | 16   | 16.5                | V    |

| I <sub>OUT</sub>       | Output Current <sup>(2)</sup>     |                            | 0.1(4) |      | 1.5                 | mA   |

| V <sub>PGTHRESHR</sub> | Powergood Threshold, VOUT Rising  |                            |        | 86%  |                     |      |

| V <sub>PGTHRESHF</sub> | Powergood Threshold, VOUT Falling |                            |        | 66%  |                     |      |

| C <sub>OUT</sub>       | Output Capacitor <sup>(3)</sup>   |                            |        | 0.47 |                     | μF   |

| T <sub>DISC</sub>      | Discharge Time                    | C <sub>OUT</sub> = 0.47 μF |        |      | 260                 | μs   |

| VRESET REGUL           | ATOR                              |                            |        |      |                     |      |

| V <sub>OUT</sub>       | Output Voltage                    |                            | -10.5  | -10  | -9.5                | V    |

| I <sub>OUT</sub>       | Output Current <sup>(1)</sup> (2) |                            | -17.6  |      | -0.1 <sup>(4)</sup> | mA   |

| V <sub>PGTHRESHR</sub> | Powergood Threshold               |                            |        | 80%  |                     |      |

| C <sub>OUT</sub>       | Output Capacitor <sup>(3)</sup>   |                            |        | 1    |                     | μF   |

| T <sub>DISC</sub>      | Discharge Time                    | C <sub>OUT</sub> = 1 μF    |        |      | 260                 | μs   |

| NEGATIVE 8 V P         | PHOTO DIODE LDO                   |                            |        |      |                     |      |

| V <sub>IN</sub>        | Input Voltage                     |                            |        | -10  |                     | V    |

| V <sub>OUT</sub>       | Output Voltage                    | Unloaded                   | -8.5   | -8   | -7.5                | V    |

| I <sub>OUT</sub>       | Output Current                    |                            | -6     |      |                     | mA   |

| V <sub>IRIPPLE</sub>   | Input Ripple                      |                            |        |      | 100                 | mVpp |

- (1) VRESET current supplies both DMD and Negative 8-V LDO.

- VOFFSET, VBIAS, and VRESET are designed to supply the DMD and Negative 8 V LDO only, and should not be connected to (2) additional loads.

- The capacitance value of some ceramic capacitor types can diminish drastically depending on the applied DC voltage and temperature. TI recommends X7R dielectric capacitors to minimize capacitance loss over voltage bias and temperatures. Using a higher voltage rated part and/or a larger package size also helps minimize the capacitance reduction at the applied DC voltage. Refer to the DLP5531Q1EVM for suggested components.

- (4) Pull down resistors required to meet minimum current requirement.

## **6.11 Electrical Characteristics - Temperature and Voltage Monitors**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER               |                             | TEST CONDITIONS                                                          | MIN    | TYP  | MAX    | UNIT     |

|-------------------------|-----------------------------|--------------------------------------------------------------------------|--------|------|--------|----------|

| TEMPERATURE             | MONITOR                     |                                                                          |        |      |        |          |

| TEMP <sub>WARN</sub>    | Thermal Warning Threshold   | Junction Temperature                                                     |        | 135  |        | °C       |

| TEMP <sub>EMRG</sub>    | Thermal Emergency Threshold | Junction Temperature                                                     |        | 150  |        | °C       |

| 1.1 V SUPPLY M          | ONITOR                      |                                                                          |        |      |        | l        |

| V <sub>TRIPN</sub>      | Negative Trip Threshold     | Negative going only                                                      | 0.95   | 0.98 | 1.01   | V        |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold, amount higher than negative trip voltage       |        | 2%   |        |          |

| t <sub>GLITCH</sub>     | Glitch Suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000   | μs       |

| 1.8 V SUPPLY M          | ONITOR                      |                                                                          |        |      |        | <b>'</b> |

| V <sub>TRIPN</sub>      | Negative Trip Threshold     | Negative going only                                                      | 1.552  | 1.6  | 1.648  | V        |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold, amount higher than negative trip voltage       |        | 2%   |        |          |

| t <sub>GLITCH</sub>     | Glitch Suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000   | μs       |

| 3.3 V SUPPLY M          | ONITOR                      |                                                                          |        |      |        |          |

| V <sub>TRIPN</sub>      | Negative Trip Threshold     | Negative going only                                                      | 2.852  | 2.93 | 3.03   | V        |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold, amount higher than negative trip voltage       |        | 2%   |        |          |

| t <sub>GLITCH</sub>     | Glitch Suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000   | μs       |

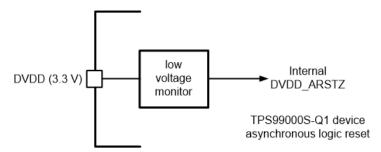

| AVDD, DVDD, V           | DDIO SUPPLY MONITORS        |                                                                          |        |      |        |          |

| V <sub>TRIPN</sub>      | Negative Trip Threshold     | Negative going only                                                      | 2.74   | 2.86 | 2.98   | V        |

| V <sub>TRIPHYST</sub>   | Hysteresis                  | Positive going threshold,<br>amount higher than negative trip<br>voltage |        | 2%   |        |          |

| t <sub>GLITCH</sub>     | Glitch Suppression          | Size of glitch ignored (no reset) with 2% overdrive                      | 20     |      | 1000   | μs       |

| VMAIN SYSTEM            | INPUT SUPPLY MONITOR        | · '                                                                      |        |      |        |          |

| V <sub>MAINTHRSH</sub>  | VMAIN Threshold             | External resistor divider used to translate VMAIN                        | 1.2125 | 1.25 | 1.2875 | V        |

| t <sub>MAINGLITCH</sub> | VMAIN Glitch Suppression    | At 2% overdrive                                                          | 20     |      | 1000   | μs       |

### 6.12 Electrical Characteristics - Current Consumption

| PARAMETER                    | TEST CONDITIONS                         | MIN          | TYP <sup>(1)</sup> | MAX <sup>(2)</sup> | UNIT |

|------------------------------|-----------------------------------------|--------------|--------------------|--------------------|------|

| SUM OF 3.3 V SUPPLY PINS: DV | /DD, VDD_IO, AND AVDD                   |              |                    |                    |      |

| System off                   | PROJ_ON Low                             |              | 1.5                | 2                  | mA   |

| System on                    | Display On state, no TIAs enabled       |              | 3.5                | 4                  | mA   |

| TIA #1                       | Additional current from enabling TIA #1 |              | 1                  | 1                  | mA   |

| TIA #2                       | Additional current from enabling TIA #2 |              | 1                  | 1                  | mA   |

| SUM OF 6 V SUPPLY PINS: DRV  | R_PWR, VIN_DRST, VIN_LDOT_5V, VIN_LDOT  | _3P3V, AND V | IN_LDOA_3P3        | BV                 |      |

| System off                   | PROJ_ON Low                             |              | 1                  | 2                  | mA   |

| System on <sup>(3)</sup>     | Display On state, no TIAs enabled       |              | 98                 | 119                | mA   |

| TIA #1                       | Additional current from enabling TIA #1 |              | 20                 | 25                 | mA   |

| TIA #2                       | Additional current from enabling TIA #2 |              | 20                 | 25                 | mA   |

- (1) Typical measurements performed at 25°C and nominal voltage.

- (2) Measurements taken at -40°C, 25°C, and 105°C. 3.3 V inputs measured at 3 V, 3.3 V, 3.6 V. 6 V inputs measured at 5.5 V, 6 V, and 7 V. The maximum current draw of all these conditions is shown.

- (3) This number represents the current at the input to the TPS99000S-Q1 when the DMD voltage rails output the maximum current as listed in the respective sections of this datasheet. This number is the combination of the measured current when the DMD voltage regulator is unloaded (35 mA typical, 56 mA max) and the estimated current draw on the 6 V supply when the DMD voltage regulator outputs the maximum current (63 mA). The estimated current draw is calculated by the equation I<sub>6V</sub>=[(16/6)\*I<sub>VBIAS</sub>+(8.5/6)\*I<sub>VOFFSET</sub>+ (-10/6)\*I<sub>VRESET</sub>]/η where η = 0.9. In order to calculate the power dissipation of the TPS99000S-Q1 in this condition, multiply the current from the unloaded condition by the input voltage, and add the current from the DMD voltage regulator multiplied by the input voltage multiplied by (1-η).

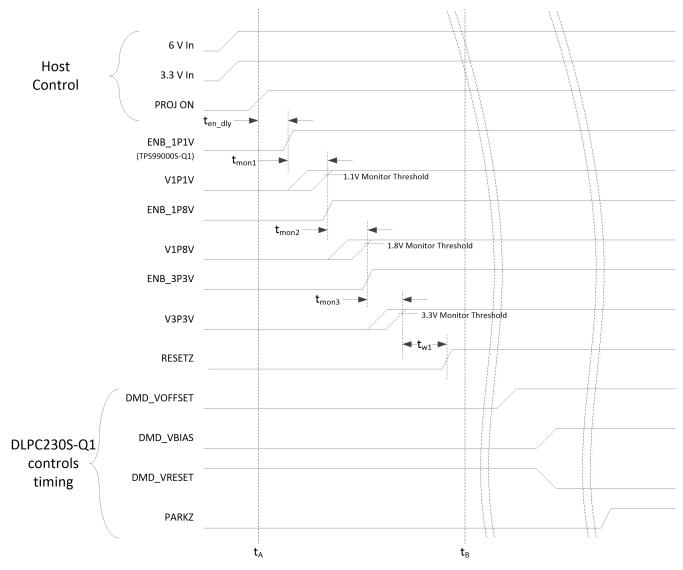

## **6.13 Power-Up Timing Requirements**

|                           |                                                                                                                                                            |                                                         | TYP | UNIT |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|------|

| t <sub>en_dly</sub>       | PROJ_ON to 1.1 V enable. This includes PROJ_ON $t_{\mbox{\scriptsize glitch}}$ time.                                                                       | Rising edge of PROJ_ON to rising edge of 1.1 V enable.  | 11  | ms   |

| t <sub>mon1</sub> (1) (2) | Maximum time for 1.1 V rail to reach voltage threshold after enable has been asserted. This delay length will occur even if 1.1 V meets threshold earlier. | Rising edge of ENB_1P1V to internal 1.1 V monitor test. | 10  | ms   |

| t <sub>mon2</sub> (1) (2) | Maximum time for 1.8 V rail to reach voltage threshold after enable has been asserted. This delay length will occur even if 1.8 V meets threshold earlier. | Rising edge of ENB_1P8V to internal 1.8 V monitor test. | 10  | ms   |

| t <sub>mon3</sub> (1) (2) | Maximum time for 3.3 V rail to reach voltage threshold after enable has been asserted. This delay length will occur even if 3.3 V meets threshold earlier. | Rising edge of ENB_3P3V to internal 3.3 V monitor test. | 10  | ms   |

| t <sub>w1</sub>           | RESETZ delay after voltage testing completion.                                                                                                             | Completion of 3.3 V monitor test to RESETZ rising edge. | 10  | ms   |

<sup>(1)</sup> V1P1V, V1P8V, and V3P3V rails can be enabled prior to the TPS99000S-Q1 assertion of their respective enable signal if required for system power design. If necessary, ENB\_1P1V may be connected to the 1.1 V, 1.8 V, and 3.3 V external supply enables.

<sup>(2)</sup> If any voltage threshold is not met within the specified time, the TPS99000S-Q1 will not de-assert RESETZ. The power-up procedure must be fully restarted in this situation.

Figure 6-1. Power Up Timing

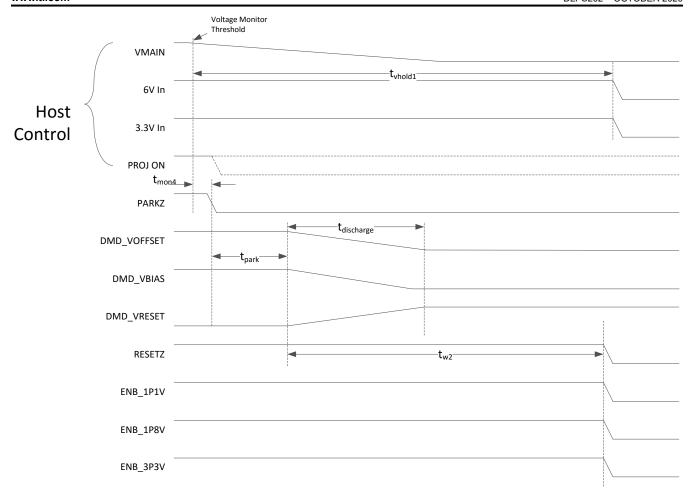

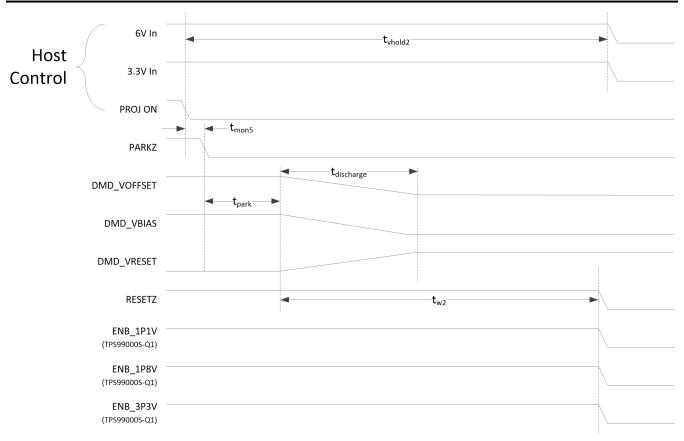

### **6.14 Power-Down Timing Requirements**

#### See (1)

|                            |                                                                                                             |                                                                                                       | MIN  | MAX | UNIT |

|----------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----|------|

| t <sub>vhold1</sub>        | Host voltage hold time after VMAIN minimum threshold reached. $t_{mon4}(max) + t_{park}(max) + t_{w2}(max)$ | VMAIN threshold to 6 V and 3.3 V power loss. <sup>(2) (3)</sup>                                       | 900  |     | μs   |

| t <sub>vhold2</sub>        | Host voltage hold time after PROJ_ON deasserted. $t_{mon5}(max) + t_{park}(max) + t_{w2}(max)$              | VMAIN threshold to 6 V and 3.3 V power loss. <sup>(2) (3)</sup>                                       | 1.78 |     | ms   |

| t <sub>mon4</sub>          | VMAIN monitoring time.                                                                                      | Minimum voltage trip threshold to PARKZ falling edge.                                                 | 52   | 120 | μs   |

| t <sub>mon5</sub>          | PROJ_ON de-assertion reaction time.                                                                         | Falling edge of PROJ_ON to PARKZ falling edge.                                                        |      | 1   | ms   |

| t <sub>park</sub>          | DMD Park time.                                                                                              | PARKZ falling edge to start DMD_VOFFSET discharge.                                                    |      | 280 | μs   |

| t <sub>discharge</sub> (4) | DMD voltage rail discharge time.                                                                            | VOFFSET C <sub>out</sub> = 1 μF<br>VRESET C <sub>out</sub> = 1 μF<br>VBIAS C <sub>out</sub> = 0.47 μF |      | 260 | μs   |

| t <sub>w2</sub>            | DMD voltage disable to RESETZ de-assertion.                                                                 | Start of DMD voltage rail discharge to RESETZ falling edge.                                           |      | 500 | μs   |

- (1) There are two methods for initiating the power down sequence:

- a. VMAIN voltage decreases below its minimum threshold. This is typical if the TPS99000S-Q1 is expected to initiate the power down sequence when main power is removed from the system. Note that the 6 V and 3.3 V input rails must remain within operating range for a specified period of time after the power-down sequence begins.

- b. PROJ\_ON low. This is allows a host controller to initiate power down through a digital input to the TPS99000S-Q1.

- (2) 6 V input rails include DRVR\_PWR, VIN\_DRST, VIN\_LDOT\_5V, VIN\_LDOA\_3P3V, VIN\_LDOT3P3V.

- (3) 3.3 V input rails include VDD\_IO, DVDD, AVDD.

- (4) The DMD specifies a maximum absolute voltage difference between VBIAS and VOFFSET. In order to remain below this maximum voltage difference, VBIAS must discharge faster than VOFFSET. This is accomplished by using a smaller C<sub>out</sub> capacitance for VBIAS in order to allow it to discharge quicker than VOFFSET.

Figure 6-2. Power Down Timing - VMAIN Trigger

Figure 6-3. Power Down Timing - PROJ\_ON Trigger

## 6.15 Timing Requirements - Sequencer Clock

|                    |                                                    | MIN | NOM MAX | UNIT  |

|--------------------|----------------------------------------------------|-----|---------|-------|

| $f_{\sf SEQ\_CLK}$ | SEQ_CLK Frequency                                  |     | 30.00   | MHz   |

| t <sub>JPP</sub>   | SEQ_CLK Jitter (peak to peak)                      | -3% | 3%      | ó     |

| $f_{SS}$           | SEQ_CLK allowable spread spectrum                  | -2% | 0%      | ó     |

| fssmod             | SEQ_CLK Spread Spectrum Modulation Frequency       | 25  | 10      | ) kHz |

| $f_{\sf SSSTEPS}$  | SEQ_CLK Spread Spectrum Modulation Frequency Steps |     | 50      | steps |

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

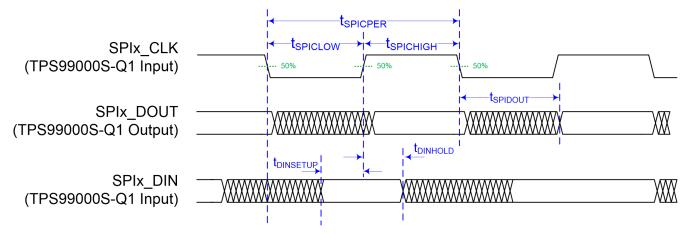

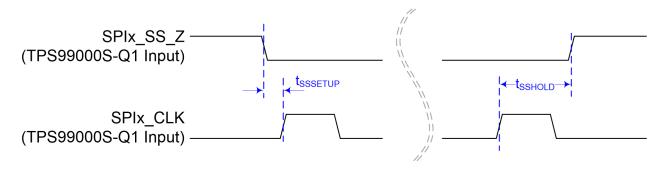

## 6.16 Timing Requirements - Host / Diagnostic Port SPI Interface

|                       |                                   | MIN | NOM | MAX | UNIT |

|-----------------------|-----------------------------------|-----|-----|-----|------|

| t <sub>SPICPER</sub>  | SPI CLK Cycle Time                | 31  | 33  |     | ns   |

| t <sub>SPICHIGH</sub> | SPI CLK High Time                 | 10  |     |     | ns   |

| t <sub>SPICLOW</sub>  | SPI CLK Low Time                  | 10  |     |     | ns   |

| t <sub>SPIDOUT</sub>  | CLK Falling to DOUT               | 0   |     | 15  | ns   |

| t <sub>SSSETUP</sub>  | SPI SS_Z to CLK Rising Setup Time | 5   |     |     | ns   |

| t <sub>SSHOLD</sub>   | SPI CLK Rising to SS_Z Hold Time  | 5   |     |     | ns   |

| t <sub>DINSETUP</sub> | SPI DIN to CLK Rising Setup Time  | 5   |     |     | ns   |

| t <sub>DINHOLD</sub>  | SPI CLK Rising to DIN Hold Time   | 5   |     |     | ns   |

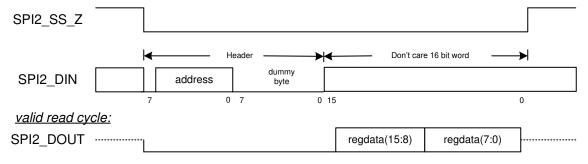

Figure 6-4. DLPC230S-Q1 Diagnostic Interface Timing

Figure 6-5. Chip Select Setup and Hold Timing

## 6.17 Timing Requirements - ADC Interface

|                          |                                  | MIN | NOM MAX | UNIT |

|--------------------------|----------------------------------|-----|---------|------|

| t <sub>ADCDINSETUP</sub> | ADC DIN to CLK Rising Setup Time | 5   |         | ns   |

| t <sub>ADCDINHOLD</sub>  | ADC CLK Rising to DIN Hold Time  | 5   |         | ns   |

| t <sub>ADCDOUT</sub>     | CLK Rising to DOUT               | 0   | 15      | ns   |

## 6.18 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------|-----------------|-----|-----|-----|------|

| INTERNAL CLOCK |                 |     |     |     |      |

Copyright © 2020 Texas Instruments Incorporated

Submit Document Feedback

## TPS99000S-Q1

DLPS202 - OCTOBER 2020

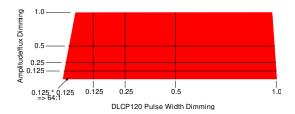

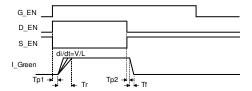

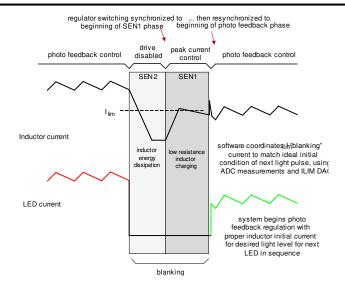

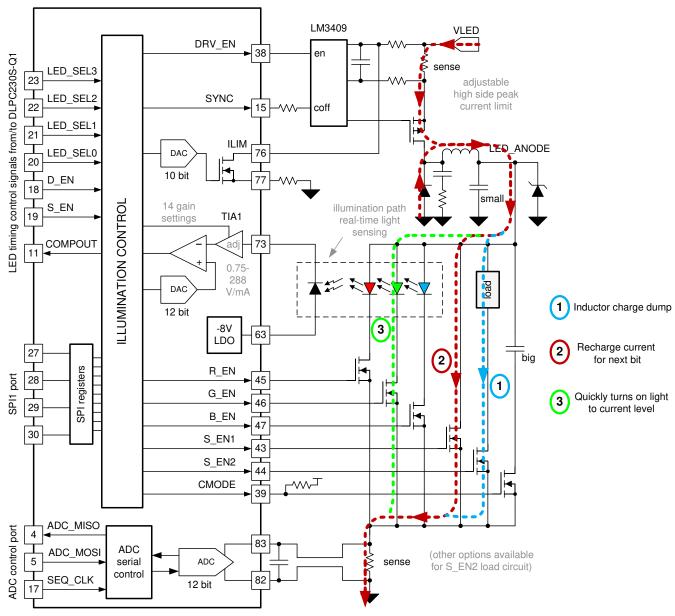

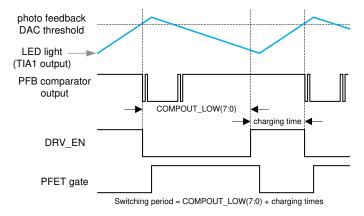

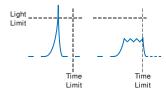

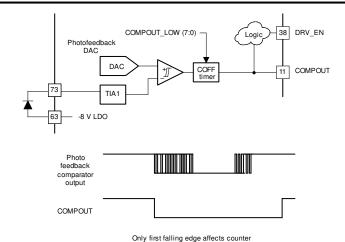

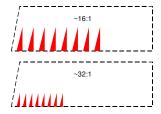

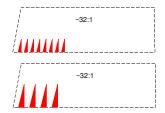

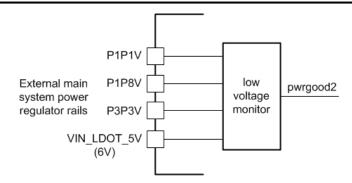

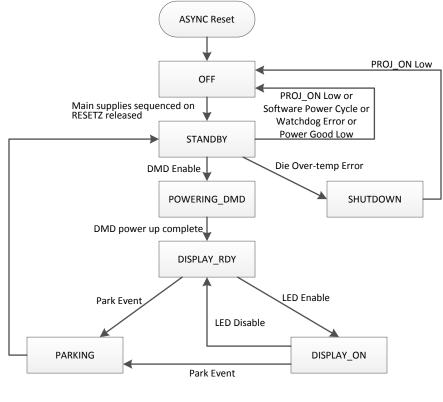

over operating free-air temperature range (unless otherwise noted)