# TUSB2E11 USB 2.0-eUSB2 Repeater

#### 1 Features

- USB 2.0 and eUSB2 (rev 1.2) compliant

- Low-speed, full-speed, high-speed signaling

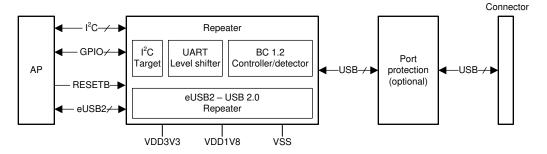

- Best-in-class high-speed total jitter of 20ps

- Register access protocol receptor capable

- Host and device mode (dual-role device) support

- Auto detection for I<sup>2</sup>C or strap-pin options

- Three strap-pins for USB 2.0 high-speed channel compensation settings

- I<sup>2</sup>C device interface for more configurations

- Device variants

- eUSB2 1.0V or 1.2V signaling interface

- eUSB2 trace loss compensation levels for different product form-factors

- 1.2V or 1.8V I<sup>2</sup>C interface

- Optional battery charging and detection support

- BC 1.2 CDP or DCP divider mode advertising

- Data-aware USB Type-C<sup>™</sup> compatible BC 1.2 SDP, CDP, and DCP divider mode detection

- Dual-role auto switching between charger advertising or detection

- CTA-936 USB Carkit UART support

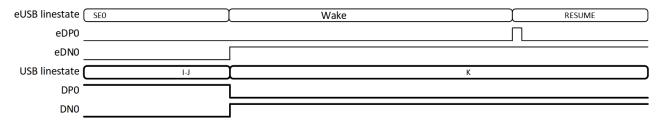

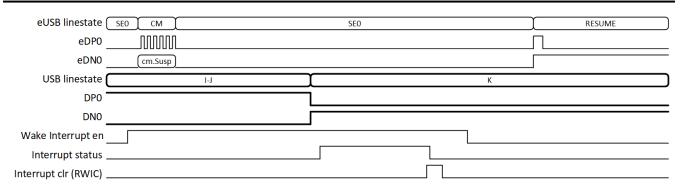

- Supports auto-resume ECR as well as L2 interrupt resume mode

- Optional GPIOs: interrupt GPIO2, debug, I<sup>2</sup>C ↔ GPIO0/1

- I<sup>2</sup>C accessible debug capabilities for manufacturing tests

## 2 Applications

- Notebooks and desktops

- Cell phones

- **Tablets**

- Wearables

- Portable electronics

# 3 Description

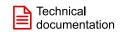

The TUSB2E11 is a USB compliant eUSB2 to USB 2.0 repeater supporting both device and host modes.

The device supports USB low-speed (LS), full-speed (FS) signals, and high-speed (HS) signals.

The device has multiple patented designs to provide robust interoperability, optimum performance, and power.

For systems without an I<sup>2</sup>C interface, the device offers eight individual settings with three strap-pins for USB 2.0 channel Equivalent Series Resistance (ESR) up to 20Ω. Device variants are available for different levels of eUSB2 trace length compensation up to 10 inches.

The I<sup>2</sup>C interface permits additional flexibility for fine tuning of device RX equalization and TX amplitude, slew rate and pre-emphasis to pass electrical compliance tests and compensate for channel loss.

Various debug options are available through the three GPIO pins that can be configured to monitor various USB bus states or interrupt as well as CTA-936 UART mode that can provide SoC debug capabilities. GPIO0 and GPIO1 can be used as general purpose I<sup>2</sup>C to GPIOs bridge.

### **Package Information**

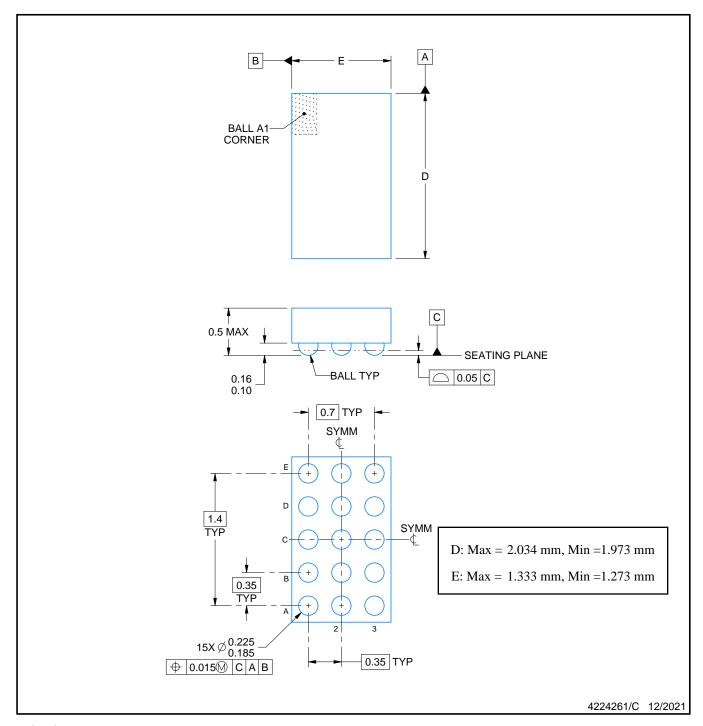

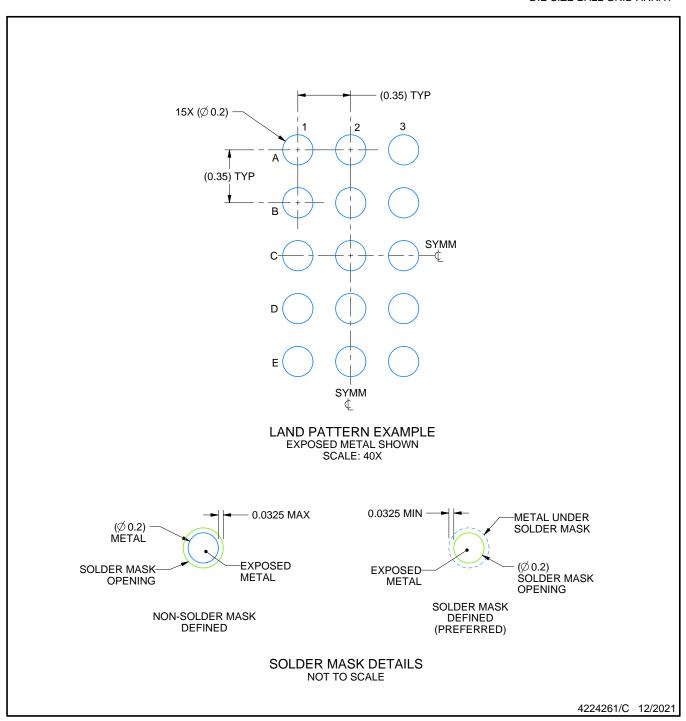

| PART NUMBER(1) | PACKAGE <sup>(2)</sup> | PACKAGE SIZE(3) |

|----------------|------------------------|-----------------|

| TUSB2E11       | YCG (DSBGA, 15)        | 1.75mm × 1.05mm |

- (1) See the Device Comparison table.

- (2) For more information, see Section 14.

- (3)The package size (length × width) is a nominal value and includes pins, where applicable.

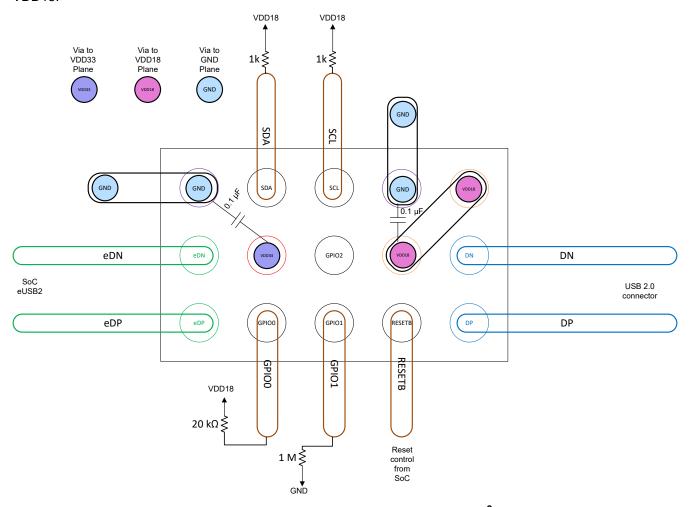

**Simplified Application**

# **Table of Contents**

| 1 Features                           | 1               | 8.5 Manufacturing Test Modes                        | 31                 |

|--------------------------------------|-----------------|-----------------------------------------------------|--------------------|

| 2 Applications                       | 1               | 8.6 I <sup>2</sup> C Target Interface               | 33                 |

| 3 Description                        | 1               | 9 Register Access Protocol (RAP)                    | 35                 |

| 4 Device Version Comparison          | <mark>2</mark>  | 10 Register Map                                     | 36                 |

| 4.1 Device Variants                  | 3               | 10.1 TUSB2E11 Registers                             | 36                 |

| 5 Pin Configuration and Functions    | 4               | 11 Application and Implementation                   | 49                 |

| 6 Specifications                     | 9               | 11.1 Application Information                        | 49                 |

| 6.1 Absolute Maximum Ratings         | 9               | 11.2 Typical Application                            | 49                 |

| 6.2 ESD Ratings                      | 9               | 11.3 Power Supply Recommendations                   |                    |

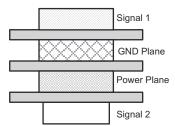

| 6.3 Recommended Operating Conditions | 9               | 11.4 Layout                                         | 53                 |

| 6.4 Thermal Information              | 11              | 12 Device and Documentation Support                 | 55                 |

| 6.5 Electrical Characteristics       | 11              | 12.1 Device Support                                 | 55                 |

| 6.6 Switching Characteristics        | 18              | 12.2 Documentation Support                          | 55                 |

| 6.7 Timing Requirements              | <mark>20</mark> | 12.3 Receiving Notification of Documentation Update | es <mark>55</mark> |

| 6.8 Typical Characteristics          | <mark>22</mark> | 12.4 Support Resources                              | 55                 |

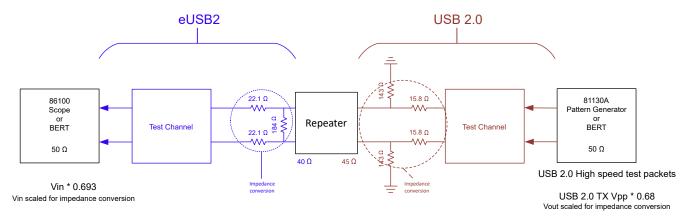

| 7 Parameter Measurement Information  | <mark>23</mark> | 12.5 Trademarks                                     |                    |

| 8 Detailed Description               | <mark>24</mark> | 12.6 Electrostatic Discharge Caution                | <mark>55</mark>    |

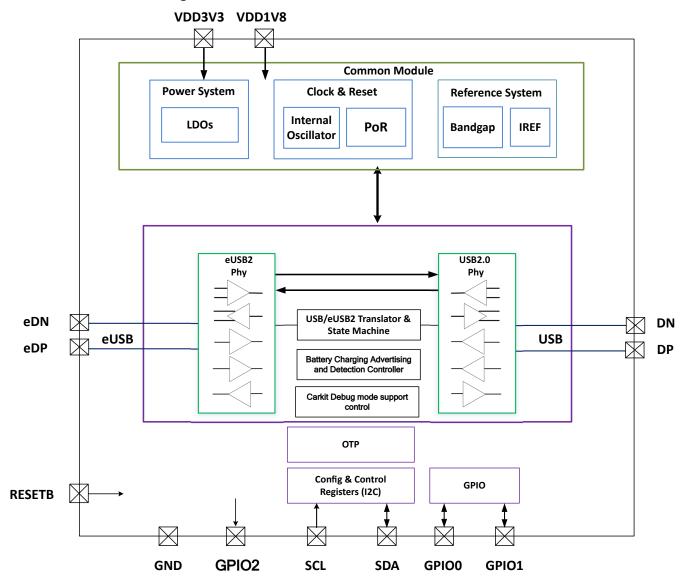

| 8.1 Overview                         | <mark>24</mark> | 12.7 Glossary                                       | 55                 |

| 8.2 Functional Block Diagram         | 24              | 13 Revision History                                 | 55                 |

| 8.3 Feature Description              | <mark>25</mark> | 14 Mechanical, Packaging, and Orderable             |                    |

| 8.4 Device Functional Modes          | <mark>25</mark> | Information                                         | 56                 |

|                                      |                 |                                                     |                    |

# **4 Device Version Comparison**

# **Table 4-1. Device Register Comparison Table**

|             | Register Address | B0 default | B1 default |

|-------------|------------------|------------|------------|

| Table 10-5  | 0x70h            | 0x73h      | 0x7Ch      |

| Table 10-6  | 0x71h            | 0x38h      | 0x3Ch      |

| Table 10-7  | 0x72h            | 0x90h      | 0x92h      |

| Table 10-8  | 0x73h            | 0x04h      | 0x83h      |

| Table 10-9  | 0x77h            | 0x00h      | 0x00h      |

| Table 10-10 | 0x78h            | 0x0Bh      | 0x0Bh      |

| Table 10-11 | 0x79h            | 0x40h      | 0x60h      |

| Table 10-12 | 0x50h            | 0x02h      | 0x02h      |

| Table 10-13 | 0xB0h            | 0x02h      | 0x03h      |

| Table 10-14 | 0xB2h            | 0x00h      | 0x00h      |

| Table 10-15 | 0xB3h            | 0x00h      | 0x00h      |

| Table 10-16 | 0xB4h            | 0x00h      | 0x00h      |

| Table 10-18 | 0xB6h            | 0xC0h      | 0xC0h      |

| Table 10-22 | 0x60h            | 0x00h      | 0x00h      |

| Table 10-23 | 0xF5h            | 0x32h      | 0x32h      |

### **Table 4-2. Device Feature Comparison Table**

| Features                      | В0            | B1                                                  |

|-------------------------------|---------------|-----------------------------------------------------|

| Low Power Mode (RESETB = low) | not supported | supported (9 μW)                                    |

| Auto-resume ECR               |               | supported (enabled by default) [see register 0x78h] |

| L2 State Interrupt Resume     | supported     | supported                                           |

### **4.1 Device Variants**

The following table describes the key differences between TUSB2E11x device variants.

**Table 4-3. Device Variant Information**

| Orderable Device | Package Type | Package Drawing | Pins | Version | I/O Voltage <sup>(1)</sup> | Device Marking |

|------------------|--------------|-----------------|------|---------|----------------------------|----------------|

| TUSB2E111YCGR    | WCSP         | YCG             | 15   | B1      | 1.8V                       | T2E111A        |

| TUSB2E112YCGR    | WCSP         | YCG             | 15   | B1      | 1.2V                       | T2E112         |

(1) I/O Voltage: I2C Bus voltage and GPIO voltage

For more information and availability of device variants such as eUSB2 1.0 signaling interface, 1.2V I<sup>2</sup>C interface, and 1.2V GPIO interface please contact support.

# **5 Pin Configuration and Functions**

Figure 5-1. TUSB2E11 YCG Package, 15-Pin DSBGA (Top View)

Table 5-1. Pin Functions

| PIN    |        | TYPE <sup>(2)</sup> | REST  | ASSOCIATED ESD | DESCRIPTION                                                                                                                                                                                                                                                               |  |  |

|--------|--------|---------------------|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO.    |                     | STATE | SUPPLY         |                                                                                                                                                                                                                                                                           |  |  |

| VDD3V3 | B2     | PWR                 | N/A   | N/A            | 3.3V Supply Voltage                                                                                                                                                                                                                                                       |  |  |

| VDD1V8 | D2, E3 | PWR                 | N/A   | N/A            | 1.8V Supply Voltage                                                                                                                                                                                                                                                       |  |  |

| VSS    | A3, D3 | GND                 | N/A   | N/A            | GND                                                                                                                                                                                                                                                                       |  |  |

| RESETB | D1     | I                   | N/A   | VDD1V8         | <ul> <li>Active Low Reset</li> <li>Upon de-assertion of RESETB, the repeater is enabled and be in eUSB2 default mode awaiting configuration from eDSPr or eUSPr.</li> <li>If RESETB is not actively controlled, a pullup resistor 100kΩ to VDD1V8 is required.</li> </ul> |  |  |

|       |     |                                                  |                                                                     | ble 5-1. Pin Func        | tions (cont                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | inued)         |             |                                |                                                                             |

|-------|-----|--------------------------------------------------|---------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|--------------------------------|-----------------------------------------------------------------------------|

| PI    | 1   | TYPE <sup>(2)</sup>                              | REST<br>STATE                                                       | ASSOCIATED ESD<br>SUPPLY |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | DESCRIPTION |                                |                                                                             |

| NAME  | NO. |                                                  |                                                                     | 001121                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Г              |             | _                              |                                                                             |

| SCL   | C3  | I                                                | Internal pulldown 1MΩ typical (disabled after reset) <sup>(1)</sup> | VDD1V8                   | I <sup>2</sup> C Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Device         | Low         | See Table 5-4 for more details | Mode<br>Non-I <sup>2</sup> C<br>USB<br>Repeater                             |

| SDA   | В3  | I/O                                              | Hi-Z <sup>(1)</sup>                                                 | VDD1V8                   | Bidirectional<br>1 <sup>2</sup> C data<br>Open drain<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Mode<br>Matrix | High        | Low                            | Non-I <sup>2</sup> C<br>UART<br>mode<br>Repeate                             |

|       |     |                                                  |                                                                     |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | High        | High                           | I <sup>2</sup> C<br>Enabled                                                 |

| GPIO2 | C2  | I/O                                              | Internal<br>pulldown<br>1MΩ typical<br>(disabled<br>after reset)    | VDD1V8                   | <ul> <li>In I<sup>2</sup>C mode GPIO2 is an open-drain active low level interrupt output. Connect GPIO2 to input of APU and a pullup resistor to use interrupt features</li> <li>In non I<sup>2</sup>C mode GPIO2 defaults to USB configuration input at power up reset.</li> <li>When a pullup resistor is used to set high input, ensure VIH is met accounting for internal pulldown as small as 500kΩ</li> <li>GPIO2 is an open-drain output after reset and can be left floating when not used.</li> </ul>                                                                                  |                |             |                                | ip resistor to tion input at sure VIH is $00k\Omega$                        |

| GPIO0 | B1  | I/O                                              | Internal pulldown 1MΩ typical (disabled after reset) <sup>(1)</sup> | VDD1V8                   | <ul> <li>Defaults to an input mode at power up reset. RESETB assertion and de-assertion or soft reset reverts GPIO0 to input mode</li> <li>In I²C mode GPIO0 defaults to control Carkit UART mode: active low to enable Carkit UART mode. Default Carkit UART direction is DP → eDP (RX) and eDN → DN (TX). GPIO0 mus be pulled up to be in USB repeater mode.</li> <li>In non I²C mode GPIO0 defaults to USB configuration input at power up reset.</li> <li>When a pullup resistor is used to set high input, ensure VIH is met accounting for internal pulldown as small as 500kΩ</li> </ul> |                |             |                                | node<br>I mode:<br>arkit UART<br>GPIO0 must<br>tion input at<br>sure VIH is |

| GPIO1 | C1  | I/O                                              | Internal pulldown 1MΩ typical (disabled after reset) <sup>(1)</sup> | VDD1V8                   | <ul> <li>Defaults to an input mode at power up reset. RESETB assertion and de-assertion or soft reset reverts GPIO1 to input mode</li> <li>In I<sup>2</sup>C mode GPIO1 defaults to debug input</li> <li>In non I<sup>2</sup>C mode GPIO1 defaults to USB Configuration input at power up reset.</li> <li>When a pullup resistor is used to set high input, ensure VIH is met accounting for internal pulldown as small as 500kΩ</li> </ul>                                                                                                                                                     |                |             |                                |                                                                             |

| eDN   | A2  | I/O                                              | Hi-Z                                                                | VDD1V8                   | eUSB2 port D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )-             |             |                                |                                                                             |

| eDP   | A1  | I/O                                              | Hi-Z                                                                | VDD1V8                   | eUSB2 port D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )+             |             |                                |                                                                             |

|       | +   | <del>                                     </del> | +                                                                   | +                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |             |                                |                                                                             |

When configured as an input but not actively driven, use  $1M\Omega$  external pulldown to strap low. I = input, I/O = input or output, PWR= power, GND = ground (1) (2)

VDD3V3

VDD3V3

Hi-Z

Hi-Z

I/O

I/O

E2

E1

DN

DP

USB port D-

USB port D+

# Table 5-2. Pin Configuration for Device Mode

| Device Mode                            | SCL (C3)                                                | SDA (B3)                               | GPIO0 (B1)                                                                                                 | GPIO1 (C1)                                                              | GPIO2 (C2)                                                                                                                        |  |  |

|----------------------------------------|---------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| I <sup>2</sup> C Mode                  | Pull-up<br>Input sampled at<br>reset                    | Pull-up<br>Input sampled at<br>reset   | Default to Input  Low = UART Mode  High = USB repeater mode  Function can be reconfigured through register | Default to Input<br>Function can be<br>reconfigured through<br>register | Default to Open drain<br>output (can be left<br>floating when not<br>used)<br>Function can be<br>reconfigured through<br>register |  |  |

| Non I <sup>2</sup> C UART mode         | Pull-up<br>Input sampled at<br>reset                    | Pull-down<br>Input sampled at<br>reset | Default to Input  Low = UART transfer enabled  High = UART transfer disabled                               | High-Z (can be left floating)                                           | High-Z (can be left floating)                                                                                                     |  |  |

| Non I <sup>2</sup> C USB repeater mode | Pull-down<br>Input sampled at<br>reset<br>See Table 5-4 | See Table 5-4                          | Def                                                                                                        | fault input sampled at reset.<br>See Table 5-3                          |                                                                                                                                   |  |  |

Table 5-3. Pin Configuration for USB PHY Tuning without I<sup>2</sup>C

| GPIO2    | GPIO1        | GPIO0         | Equivalent<br>series<br>resistance<br>(ESR)<br>between<br>repeater<br>and USB<br>connector | U_EQ_P1<br>setting | U_HS_TX_<br>AMPLITUD<br>E_P1<br>setting | U_HS_TX_<br>PRE_EMPH<br>ASIS_P1<br>setting | U_SQUELC<br>H_THRESH<br>OLD_P1<br>setting | U_DISCON<br>NECT_THR<br>ESHOLD_P<br>1 setting | HS Term |    |

|----------|--------------|---------------|--------------------------------------------------------------------------------------------|--------------------|-----------------------------------------|--------------------------------------------|-------------------------------------------|-----------------------------------------------|---------|----|

|          |              |               | Ω                                                                                          | dB                 | mV                                      | dB                                         | mV                                        | mV                                            | Ω       |    |

| Float    | Float        | Float         | 2.5                                                                                        | 0.06               | 840                                     | 0.5                                        | 104                                       | 625                                           | 45      |    |

| Fluat    | Float        | Float         | 2.5                                                                                        | (3'b000)           | (4'b0101)                               | (3'b000)                                   | (3'b100)                                  | (4'b0101)                                     | 43      |    |

| Fla.a4   | Float        | <b>5</b> 14   | Floor Double                                                                               | _                  | 0.06                                    | 880                                        | 0.9                                       | 98                                            | 645     | 45 |

| Float    |              | Pull-Up       | 5                                                                                          | (3'b000)           | (4'b0111)                               | (3'b001)                                   | (3'b101)                                  | (4'b0110)                                     | 45      |    |

| t        | D. II I I in | Pull-Up Float | + 7.5                                                                                      | 0.58               | 900                                     | 0.9                                        | 98                                        | 645                                           | 45      |    |

| Float    | Pull-Op      |               | 7.5                                                                                        | (3'b001)           | (4'b1000)                               | (3'b001)                                   | (3'b101)                                  | (4'b0110)                                     | 45      |    |

| Floot    | Dull I In    | II-Up Pull-Up | 10                                                                                         | 1.09               | 920                                     | 0.9                                        | 98                                        | 685                                           | 45      |    |

| Float    | Pull-Up      |               | 10                                                                                         | (3'b010)           | (4'b1001)                               | (3'b001)                                   | (3'b101)                                  | (4'b1000)                                     | 45      |    |

| Pull-Up  | Floot        | Float Float   | Floot                                                                                      | 12.5               | 1.56                                    | 940                                        | 1.2                                       | 91                                            | 685     | 45 |

| Pull-Up  | Float        |               | 12.5                                                                                       | (3'b011)           | (4'b1010)                               | (3'b010)                                   | (3'b110)                                  | (4'b1000)                                     | 45      |    |

| Pull-Up  | Float        | Pull-Up       | 15                                                                                         | 2.26               | 980                                     | 1.2                                        | 91                                        | 685                                           | 45      |    |

| Pull-Op  | Float        | Full-Op       | 15                                                                                         | (3'b100)           | (4'b1100)                               | (3'b010)                                   | (3'b110)                                  | (4'b1000)                                     | 43      |    |

| Dull Lle | Pull-Up      | Floot         | 17.5                                                                                       | 2.67               | 1000                                    | 1.7                                        | 91                                        | 685                                           | 45      |    |

| Pull-Up  | Pull-Op      | Float         | 17.5                                                                                       | (3'b101)           | (4'b1101)                               | (3'b011)                                   | (3'b110)                                  | (4'b1000)                                     | 40      |    |

| Pull-Up  | Pull-Up      | Dull Lie      | 111- 20                                                                                    | 2.67               | 1020                                    | 1.7                                        | 85                                        | 705                                           | 40.75   |    |

| ruii-Op  | Full-Op      | Pull-Up       | 20                                                                                         | (3'b101)           | (4'b1110)                               | (3'b011)                                   | (3'b111)                                  | (4'b1001)                                     | 42.75   |    |

Table 5-4. Pin Configuration for Battery Charging in non I<sup>2</sup>C Mode

| Table 5-4. Pin Configuration for Battery Charging in non I <sup>2</sup> C Mode |                                                       |                                                                                                                    |                                                                                                                  |                |                                    |                                                                                                                        |                                                               |                                               |  |  |

|--------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------|--|--|

| Device Mode                                                                    |                                                       |                                                                                                                    |                                                                                                                  | Repeater State | Charger<br>Detection<br>Status     | VBUS Control<br>Output                                                                                                 |                                                               |                                               |  |  |

|                                                                                | SCL (C3)                                              | SDA (B3)                                                                                                           | Unconfigured                                                                                                     | Host Repeater  | Peripheral<br>Repeater             | {GPIO2,<br>GPIO1}                                                                                                      | GPIO0                                                         |                                               |  |  |

| Non I <sup>2</sup> C USB repeater mode                                         | Pull-down<br>resistor to<br>ground<br>0 to 160Ω       | Input Low = BC 1.2 disabled High = BC 1.2 enabled                                                                  | When BC 1.2 is<br>enabled,<br>charger<br>detection                                                               | N/A            | N/A                                | or DCP                                                                                                                 | charger<br>detected<br>• 2'b01: CDP                           | charger<br>detected<br>• 2'b01: CDP<br>or DCP |  |  |

| Non I <sup>2</sup> C USB repeater mode                                         | Pull-down<br>resistor to<br>ground<br>1.5kΩ to 2kΩ    | Input VBUS_Valid input: use a voltage divider to reduce VBUS voltage to appropriate VIH for 1.8V or 1.2V I/O mode. | When<br>VBUS_valid is<br>high enable<br>charger<br>detection                                                     | N/A            | Charger<br>detection is<br>enabled | charger detected 2'b10: DCP (1.5A) or Divider Mode (2.1A) charger detected 2'b11: Divider Mode (2.4A) charger detected | N/A                                                           |                                               |  |  |

| Non I <sup>2</sup> C USB repeater mode                                         | Pull-down<br>resistor to<br>ground<br>3.4kΩ to 3.96kΩ | Input Low = BC 1.2 disabled High = BC 1.2 enabled                                                                  | When BC 1.2 is<br>enabled,<br>advertise<br>charging BC 1.2<br>DCP                                                | Advertise CDP  | N/A                                | N/A                                                                                                                    | Active High<br>Push-Pull<br>output for VBUS<br>switch Control |                                               |  |  |

| Non I <sup>2</sup> C USB repeater mode                                         | Pull-down<br>resistor to<br>ground<br>7.5kΩ to 11kΩ   | Input Low = BC 1.2 disabled High = BC 1.2 enabled                                                                  | When BC 1.2 is<br>enabled,<br>advertise<br>charging (auto<br>cycle between<br>BC 1.2 DCP<br>and Divider<br>mode) | Advertise CDP  | N/A                                | N/A                                                                                                                    | High =     VBUS ON     Low =     VBUS OFF                     |                                               |  |  |

## **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                             |                                                                                                    | MIN  | MAX  | UNIT |

|-----------------------------|----------------------------------------------------------------------------------------------------|------|------|------|

| Supply voltage range        | V <sub>DD3V3</sub>                                                                                 | -0.3 | 4.32 | V    |

| Analog Supply voltage range | V <sub>DD1V8</sub>                                                                                 | -0.3 | 2.1  | V    |

| Voltage range               | DP, DN, (with OVP enabled), 1000 total number of short events and cumulative duration of 1000 hrs. | -0.3 | 6    | V    |

| Voltage range               | eDP, eDN                                                                                           | -0.3 | 1.6  | V    |

| Voltage range               | RESETB, GPIO0, GPIO1, GPIO2, SCL, SDA                                                              | -0.3 | 2.1  | V    |

| Junction temperature        | T <sub>J(max)</sub>                                                                                |      | 125  | °C   |

| Storage temperature         | T <sub>stg</sub>                                                                                   | -65  | 150  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |     |                                                                                     | VALUE | UNIT |

|--------------------|-----|-------------------------------------------------------------------------------------|-------|------|

| V                  |     | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>         | ±1500 | V    |

| V <sub>(ESD)</sub> | _ I | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

| ,                  | 3 1 3 ( )                                           | MIN  | NOM | MAX  | UNIT |

|--------------------|-----------------------------------------------------|------|-----|------|------|

| V <sub>DD3V3</sub> | Supply voltage (VDD3V3)                             | 3.0  | 3.3 | 3.6  | V    |

| V <sub>DD1V8</sub> | Analog Supply voltage (VDD1V8)                      | 1.62 | 1.8 | 1.98 | V    |

| V_I2C_Pullup       | I2C and GPIO open drain Bus Voltage (1.2 V Variant) | 1.08 | 1.2 | 1.32 | V    |

| V_I2C_Pullup       | I2C and GPIO open drain Bus Voltage (1.8 V Variant) | 1.62 | 1.8 | 1.98 | V    |

| USB<br>Voltage     | DP, DN                                              | 0    |     | 3.6  | V    |

| eUSB2<br>voltage   | eDP, eDN                                            | 0    |     | 1.32 | V    |

| Digital<br>voltage | GPIO0, GPIO1, GPIO2, SCL, SDA (1.8 V Variant)       | 0    |     | 1.98 | V    |

| Digital<br>voltage | GPIO0, GPIO1, GPIO2, SCL, SDA (1.2 V Variant)       | 0    |     | 1.32 | V    |

| RESETB             | RESETB (1.2 V or 1.8 V Variant)                     | 0    |     | 1.98 | V    |

| T <sub>A</sub>     | Operating free-air temperature                      | -20  |     | 85   | °C   |

| TJ                 | Junction temperature                                | -20  |     | 105  | °C   |

| T <sub>CASE</sub>  | Case temperature                                    | -20  |     | 105  | °C   |

Copyright © 2024 Texas Instruments Incorporated

Product Folder Links: *TUSB2E11*

### TUSB2E11

SLLSFI4D – NOVEMBER 2021 – REVISED APRIL 2024

over operating free-air temperature range (unless otherwise noted)

|                  |                                             | MIN | NOM | MAX | UNIT |

|------------------|---------------------------------------------|-----|-----|-----|------|

| T <sub>PCB</sub> | PCB temperature (1 mm away from the device) | -20 |     | 92  | °C   |

### **6.4 Thermal Information**

|                       |                                              | TUSB2E11                                   |      |

|-----------------------|----------------------------------------------|--------------------------------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YCG (DSBGA)  15 PINS  90.5  0.6  22.9  0.4 | UNIT |

|                       |                                              | 15 PINS                                    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 90.5                                       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.6                                        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 22.9                                       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.4                                        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 22.9                                       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                           | TEST CONDITIONS                                                                                                                                                                                                            | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| POWER                 |                                                                                     |                                                                                                                                                                                                                            |     |     | •   |      |

| P <sub>WC_1V8</sub>   | Absolute worst case peak power consumption (VDD1V8 only) for power supply budgeting | I2C interface active, GPIOs in output mode, repeater in HS mode with USB transmitting, maximum RX EQ, max TX VOD and PE settings, maximum transition density. T <sub>A</sub> = -20°C to 85°C.                              |     |     | 280 | mW   |

| P <sub>WC_3V3</sub>   | Absolute worst case peak power consumption (VDD3V3 only) for power supply budgeting | I2C interface active, GPIOs in output mode, repeater in HS mode with USB transmitting, maximum RX EQ, max TX VOD and PE settings, maximum transition density. T <sub>A</sub> = -20°C to 85°C.                              |     |     | 30  | mW   |

| P <sub>WCFS_3V3</sub> | Absolute worst case peak power consumption (VDD3V3 only) for power supply budgeting | I2C interface active, GPIOs in output mode, repeater in FS mode with USB Asynchronous traffic. T <sub>A</sub> = -20°C to 85°C.                                                                                             |     |     | 75  | mW   |

| P <sub>HS_IOC</sub>   | USB Audio ISOC High-speed                                                           | Maximum TX Vod/Maximum TX PE for both USB and eUSB2. Averaged over 8 ms and only 1 uFrame with data packet. Toff threshold = 1/32. Host Peripheral Mode.                                                                   |     | 35  |     | mW   |

| P <sub>PD</sub>       | Powered down                                                                        | Device powered, RESETB=Low,<br>T <sub>A</sub> =25°C, (DP/DN Voltage ≤ VDD3V3).                                                                                                                                             |     |     | 9   | μW   |

| P <sub>Disabled</sub> | Disabled                                                                            | Device powered, I2C/GPIO interfaces functional but idle, repeater is disabled and put into the lowest power state and non-functional. T <sub>A</sub> =25°C, (DP/DN Voltage ≤ VDD3V3).                                      |     | 43  | 95  | μW   |

| P <sub>Detach</sub>   | USB unconnected                                                                     | I2C/GPIO interfaces idle, repeater is connected to a eUSB2 PHY and waiting for a USB attach event. T <sub>A</sub> = 25°C, (DP/DN Voltage ≤ VDD3V3)                                                                         |     | 43  | 85  | μW   |

| P <sub>Suspend</sub>  | L2 Suspend (host mode)                                                              | I2C/GPIO interfaces idle, USB link is in L2, repeater is monitoring for a resume/ remote wake event. T <sub>A</sub> = 25°C, (DP/DN Voltage ≤ VDD3V3). In peripheral mode additional current is present due the DP pull up. |     | 45  | 85  | μW   |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

over operating free-air temperature range (unless otherwise noted)

|                             | PARAMETER                                   | TEST CONDITIONS                                                                                                                                                                                                  | MIN   | TYP | MAX   | UNIT |

|-----------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| P <sub>Sleep</sub>          | L1 Sleep                                    | I2C/GPIO interfaces idle, repeater is supporting a USB connection, USB link is in L1 (host exists L1 every 1 ms) and repeater is monitoring for a L1 exit event. T <sub>A</sub> = 25°C, (DP/DN Voltage ≤ VDD3V3) |       | 2.3 | 5     | mW   |

| P <sub>LS_Active</sub>      | Low Speed Active                            | I2C/GPIO interfaces idle, repeater in LS mode, maximum transition density. T <sub>A</sub> = 85°C.                                                                                                                |       | 7.2 | 24    | mW   |

| P <sub>FS1_Active</sub>     | Full Speed Active (ASYNC Traffic)           | I2C/GPIO interfaces idle, repeater in FS mode, maximum transition density. T <sub>A</sub> = 85°C.                                                                                                                |       | 45  | 80    | mW   |

| P <sub>FS2_Active</sub>     | Full Speed Active (ISO Traffic)             | I2C/GPIO interfaces idle, repeater in FS mode, maximum transition density. T <sub>A</sub> = 85°C.                                                                                                                |       | 9   | 24    | mW   |

| P <sub>HS_Idle_Host</sub>   | High Speed Idle (Host mode)                 | L0.Idle. TA = 85°C. (Typical at 25°C).                                                                                                                                                                           |       | 26  | 70    | mW   |

| P <sub>HS_Idle_Periph</sub> | High Speed Idle (Peripheral mode)           | L0.Idle. TA = 85°C. (Typical at 25°C).                                                                                                                                                                           |       | 108 | 200   | mW   |

| DIGITAL INPU                | UTS                                         |                                                                                                                                                                                                                  |       |     | 1     |      |

| V <sub>IH</sub>             | High level input voltage                    | GPIO0, GPIO1, GPIO2 (1.2 V Variant)                                                                                                                                                                              | 0.702 |     |       | V    |

| V <sub>IH</sub>             | High level input voltage                    | GPIO0, GPIO1, GPIO2 (1.8 V Variant)                                                                                                                                                                              | 1.053 |     |       | V    |

| V <sub>IL</sub>             | Low-level input voltage                     | GPIO0, GPIO1, GPIO2 (1.2 V Variant)                                                                                                                                                                              |       |     | 0.462 | V    |

| $V_{IL}$                    | Low-level input voltage                     | GPIO0, GPIO1, GPIO2 (1.8 V Variant)                                                                                                                                                                              |       |     | 0.693 | V    |

| V <sub>IL</sub>             | Low-level input voltage                     | RESETB                                                                                                                                                                                                           |       |     | 0.35  | V    |

| V <sub>IH</sub>             | High level input voltage                    | RESETB                                                                                                                                                                                                           | 0.75  |     |       | V    |

| I <sub>IH</sub>             | High level input current                    | V <sub>IH</sub> = 1.98 V, VDD3V3=3.0 V or 0 V,<br>VDD1V8=1.62 V or 0 V<br>RESETB, GPIO0, GPIO1                                                                                                                   |       |     | 0.5   | μA   |

| I <sub>IL</sub>             | Low level input current                     | V <sub>IL</sub> = 0 V, VDD3V3=3.0 V or 0 V,<br>VDD1V8=1.62 V or 0 V<br>RESETB, GPIO0, GPIO1                                                                                                                      |       |     | 0.5   | μΑ   |

| DIGITAL OUT                 | PUTS                                        |                                                                                                                                                                                                                  |       |     | '     |      |

| V <sub>OH</sub>             | High level output voltage                   | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OH</sub> = 20 μA and maximum 3 pF C <sub>load)</sub> (1.2 V Variant)                                                                                             | 0.81  |     |       | V    |

| V <sub>OH</sub>             | High level output voltage                   | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OH</sub> = 20 μA and maximum 3 pF C <sub>load)</sub> (1.8 V Variant)                                                                                             | 1.21  |     |       | V    |

| V <sub>OL</sub>             | Low level output voltage                    | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OL</sub> = 1 mA) (1.2 V Variant)                                                                                                                                 |       |     | 0.25  | V    |

| V <sub>OL</sub>             | Low level output voltage                    | GPIO0, GPIO1, GPIO2, push-pull I/O mode (I <sub>OL</sub> = 1 mA) (1.8 V Variant)                                                                                                                                 |       |     | 0.35  | V    |

| I <sub>OL_PP</sub>          | Low level output current in push-pull mode  | GPIO0, GPIO1, GPIO2 (1.2 V Variant),<br>VOL=0.4 V                                                                                                                                                                | 2.5   | 4   | 5.6   | mA   |

| I <sub>OL_PP</sub>          | Low level output current in push-pull mode  | GPIO0, GPIO1, GPIO2 (1.8 V Variant),<br>VOL=0.4 V                                                                                                                                                                | 4     | 6   | 8     | mA   |

| I <sub>OH_PP</sub>          | High level output current in push-pull mode | GPIO0, GPIO1, GPIO2, push-pull I/O mode, VOH=0.9 V (1.2 V Variant)                                                                                                                                               | 22    |     |       | μA   |

| I <sub>OH_PP</sub>          | High level output current in push-pull mode | GPIO0, GPIO1, GPIO2, push-pull I/O mode, VOH=0.9 V (1.8 V Variant)                                                                                                                                               | 50    |     |       | μA   |

| I2C (SDA, SC                | EL)                                         | 1                                                                                                                                                                                                                |       | -   |       |      |

| V <sub>IL</sub>             | Low level input voltage, 1.2 V variant      | SDA, SCL, V <sub>I2C Pullup</sub> = 1.08 V                                                                                                                                                                       |       |     | 0.387 | V    |

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                              | TEST CONDITIONS                                                                                                       | MIN   | TYP | MAX   | UNIT           |

|------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|-----|-------|----------------|

| V <sub>IL</sub>        | Low level input voltage, 1.8 V variant                                 | SDA, SCL, V_I2C_Pullup = 1.96 V                                                                                       |       |     | 0.588 | V              |

| V <sub>IH</sub>        | High level input voltage, 1.2 V variant                                | SDA, SCL, V <sub>I2C Pullup</sub> = 1.08 V                                                                            | 0.833 |     |       | V              |

| V <sub>IH</sub>        | High level input voltage, 1.8 V variant                                | SDA, SCL, V <sub>I2C_Pullup</sub> = 1.96 V                                                                            | 1.372 |     |       | V              |

| √ <sub>HYS</sub>       | Input hysteresis, 1.2 V variant                                        | V_I2C_Pullup = 1.08 V                                                                                                 | 0.020 |     |       | V              |

| V <sub>HYS</sub>       | Input hysteresis, 1.8 V variant                                        | V <sub>I2C Pullup</sub> = 1.96 V                                                                                      | 0.098 |     |       | V              |

| IH                     | High level input leakage current                                       | V <sub>IH</sub> = 1.98 V                                                                                              |       |     | 0.5   | μA             |

| <br>IIL                | Low level input leakage current                                        | V <sub>IL</sub> = 0 V                                                                                                 |       |     | 0.5   | <u>'</u><br>μΑ |

| V <sub>OL</sub>        | Low level output voltage (1 kΩ pull up), 1.2 V variant                 | I <sub>OL</sub> = 2.5 mA, V_I2C_Pullup = 1.08 V                                                                       |       |     | 0.2   |                |

| V <sub>OL</sub>        | Low level output voltage (1 k $\Omega$ pull up), 1.8V variant          | I <sub>OL</sub> = 2.5 mA, V_I2C_Pullup = 1.96 V                                                                       |       |     | 0.3   | V              |

| I <sub>OL</sub>        | Open drain drive strength, 1.2 V Variant                               | VOL = 0.4 V                                                                                                           | 1.6   | 2.4 | 3.0   | mA             |

| I <sub>OL</sub>        | Open drain drive strength, 1.8 V Variant                               | VOL = 0.4 V                                                                                                           | 8     | 10  | 12.6  | mA             |

| UART I/O               | <u> </u>                                                               |                                                                                                                       |       | ,   |       |                |

| V <sub>OLI</sub>       | Internal output low                                                    | Internal UART output (eDP/eDN) 1.2 V signaling                                                                        |       |     | 0.1   | V              |

| V <sub>OHI</sub>       | Internal output high                                                   | Internal UART output (eDP/eDN) 1.2 V signaling                                                                        | 0.918 |     | 1.32  | V              |

| V <sub>ILI</sub>       | Internal input low                                                     | Internal UART input (eDP/eDN) 1.2 V signaling                                                                         | -0.1  |     | 0.399 | V              |

| V <sub>IHI</sub>       | Internal input high                                                    | Internal UART input (eDP/eDN) 1.2 V signaling                                                                         | 0.819 |     | 1.386 | V              |

| $V_{OLE}$              | External output low                                                    | External UART output (DP/DN) 3.3 V signaling                                                                          | 0     |     | 0.3   | V              |

| V <sub>OHE</sub>       | External output high                                                   | External UART output (DP/DN) 3.3 V signaling                                                                          | 2.8   |     | 3.6   | V              |

| V <sub>ILE</sub>       | External input low                                                     | External UART input (DP/DN) 3.3 V signaling                                                                           |       |     | 0.8   | V              |

| V <sub>IHE</sub>       | External input high                                                    | External UART input (DP/DN) 3.3 V signaling                                                                           | 2     |     |       | V              |

| USB (DP, DI            | N)                                                                     |                                                                                                                       |       |     |       |                |

| Z <sub>inp_Dx</sub>    | Impedance to GND, no pull up or pull down                              | Vin=3.6 V, V <sub>DD3V3</sub> =3.0 V, <i>Input</i> Characteristics                                                    | 390   |     |       | kΩ             |

| C <sub>IO_Dx</sub>     | Capacitance to GND                                                     | Measured with VNA at 240 MHz, Driver Hi-Z                                                                             |       |     | 10    | pF             |

| R <sub>PUI</sub>       | Bus pull-up resistor on upstream facing port (idle)                    | High-speed Device Speed Identification <sup>(1)</sup>                                                                 | 0.92  | 1.1 | 1.475 | kΩ             |

| R <sub>PUR</sub>       | Bus pull-up resistor on upstream facing port (receiving)               | High-speed Device Speed Identification <sup>(1)</sup>                                                                 | 1.525 | 2.2 | 2.99  | kΩ             |

| R <sub>PD</sub>        | Bus pull-down resistor on downstream facing port                       | High-speed Device Speed Identification <sup>(1)</sup>                                                                 | 14.35 | 19  | 24.6  | kΩ             |

| V <sub>HSTERM</sub>    | Termination voltage in high speed                                      | The output voltage in the high-<br>speed idle state, <i>High-speed Input</i><br><i>Characteristics</i> <sup>(1)</sup> | -10   |     | 10    | mV             |

| USB TERMI              | NATION                                                                 |                                                                                                                       |       | ,   |       |                |

| Z <sub>HSTERM_</sub> P | Driver Output Resistance (which also serves as high speed termination) | (VOH= 0 to 600 mV) Full-speed (12 Mb/s) Driver Characteristics <sup>(1)</sup> , Default, U_HS_TERM_Px setting 01      | 40.6  | 45  | 49.4  | Ω              |

| Z <sub>HSTERM_</sub> N | Driver Output Resistance (which also serves as high speed termination) | (VOH= 0 to 600 mV) Full-speed (12 Mb/s) Driver Characteristics <sup>(1)</sup> , Default, U_HS_TERM_Px setting 01      | 40.6  | 45  | 49.4  | Ω              |

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                       | TEST CONDITIONS                                                                                                                                                                                                                        | MIN   | TYP  | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| USB INPU            | T LEVELS LS/FS                                                                  |                                                                                                                                                                                                                                        |       |      |      |      |

| V <sub>IH</sub>     | High (driven)                                                                   | Receiver Characteristics <sup>(1)</sup> (measured at the connector)                                                                                                                                                                    | 2     |      |      | V    |

| $V_{IHZ}$           | High (floating)                                                                 | Receiver Characteristics <sup>(1)</sup> (HOST downstream port pull-down resistor enabled and external device pull up 1.5 $k\Omega \pm 5\%$ to 3.0-3.6 V)                                                                               | 2.7   |      | 3.6  | V    |

| V <sub>IL</sub>     | Low                                                                             | Receiver Characteristics <sup>(1)</sup>                                                                                                                                                                                                |       |      | 8.0  | V    |

| $V_{DI}$            | Differential Input Sensitivity (hysteresis is off)                              | (D+)-(D-) ; Differential Input Sensitivity<br>Range for Low-/full-speed <sup>(7)</sup> ; (measured<br>at connector) V <sub>CM</sub> =0.8 V to 2.0 V                                                                                    |       |      | 0.2  | V    |

| USB OUTP            | PUT LEVELS LS/FS                                                                |                                                                                                                                                                                                                                        |       |      | '    |      |

| V <sub>OL</sub>     | Low                                                                             | USB Driver Characteristics <sup>(1)</sup> , (measured at connector with RL of 1.425 kΩ to 3.6 V.)                                                                                                                                      | 0     |      | 0.3  | V    |

| V <sub>OH</sub>     | High (Driven)                                                                   | USB Driver Characteristics $^{(1)}$ , (measured at the connector with RL of 14.25 k $\Omega$ to GND. )                                                                                                                                 | 2.8   |      | 3.6  | V    |

| Z <sub>FSTERM</sub> | Driver Series Output Resistance                                                 | USB Driver Characteristics <sup>(1)</sup> , measured it during VOL or VOH                                                                                                                                                              | 28    |      | 44   | Ω    |

| V <sub>CRS2</sub>   | Output Signal Crossover Voltage                                                 | Measured as in <i>Data Signal Rise and</i> Fall Time <sup>(1)</sup> , excluding the first transition from the Idle state. With external 1.5 $k\Omega$ pull up on DP to 3.0 V                                                           | 1.3   |      | 2    | V    |

| V <sub>CRS</sub>    | Output Signal Crossover Voltage                                                 | Measured as in <i>Data Signal Rise and</i> Fall Time <sup>(1)</sup> , excluding the first transition from the Idle state                                                                                                               | 1.3   |      | 2    | V    |

| USB INPU            | T LEVELS HS                                                                     |                                                                                                                                                                                                                                        |       |      |      |      |

| $V_{HSSQ}$          | High-speed squelch/no-squelch detection threshold                               | Full-/High-speed Signaling Level <sup>(1)</sup> , specification refers to peak differential signal amplitude), measured at 240 MHz with increasing amplitude, U_SQUELCH_THRESHOLD_Px setting 011, V <sub>CM</sub> = -50 mV to 500 mV   | 111   | 128  | 161  | mV   |

| $V_{HSSQ}$          | High-speed squelch/no-squelch detection threshold                               | Full-/High-speed Signaling Levels <sup>(1)</sup> , (specification refers to peak differential signal amplitude), measured at 240 MHz with increasing amplitude, U_SQUELCH_THRESHOLD_Px setting 100, V <sub>CM</sub> = -50 mV to 500 mV | 104   | 125  | 150  | mV   |

| $V_{HSDSC}$         | High-speed disconnect detection threshold                                       | Full-/High-speed Signaling Levels <sup>(i)</sup> , (specification refers to differential signal amplitude). (HW Default), U_DISCONNECT_THRESHOLD_Px setting 0000, V <sub>CM</sub> =200 mV to 600 mV                                    | 525   | 575  | 625  | mV   |

| V <sub>HSDSC</sub>  | High-speed disconnect detection threshold                                       | Full-/High-speed Signaling Levels <sup>(1)</sup> (specification refers to differential signal amplitude). (+25.6%), U_DISCONNECT_THRESHOLD_Px setting 1000, V <sub>CM</sub> =280 mV to 680 mV                                          | 685   | 757  | 846  | mV   |

| EQ_ <sub>UHS</sub>  | USB high-speed data receiver equalization, (measured indirectly through jitter) | 240 MHz, U_EQ_Px setting 000                                                                                                                                                                                                           | -0.37 | 0.06 | 0.57 | dB   |

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                                              | TEST CONDITIONS                                                                                                                                                                                                         | MIN  | TYP  | MAX  | UNIT |

|------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| EQ_ <sub>UHS</sub>     | USB High-speed data receiver equalization, (measured indirectly through jitter)        | 240 MHz, U_EQ_Px setting 010                                                                                                                                                                                            | 0.62 | 1.09 | 1.57 | dB   |

| USB OUTP               | UT LEVELS HS                                                                           |                                                                                                                                                                                                                         |      |      |      |      |

| V <sub>HSOH</sub>      | High-speed data signaling high                                                         | Full-/High-speed Signaling Levels <sup>(1)</sup> , measured single-ended peak voltage per USB 2.0 test measurement spec, U_HS_TX_AMPLITUDE_Px setting 0011, PE disabled, Test load is an ideal 45 Ω to GND on DP and DN | 360  | 400  | 440  | mV   |

| Vнsон                  | High-speed data signaling high                                                         | Full-/High-speed Signaling Levels <sup>(1)</sup> , measured single ended peak voltage per USB 2.0 test measurement spec, U_HS_TX_AMPLITUDE_Px setting 1100, PE disabled, Test load is an ideal 45 Ω to GND on DP and DN | 441  | 490  | 539  | mV   |

| $V_{HSOD}$             | High-speed data signaling swing                                                        | Measured p-p, 0%, U_HS_TX_AMPLITUDE_Px setting 0011, PE disabled, Test load is an ideal 45 Ω to GND on DP and DN.                                                                                                       | 720  | 800  | 880  | mV   |

| $V_{HSOD}$             | High-speed data signaling swing                                                        | Measured p-p, 22.5%, U_HS_TX_AMPLITUDE_Px setting 1100, PE disabled,Test load is an ideal 45 Ω to GND on DP and DN.                                                                                                     | 882  | 980  | 1078 | mV   |

| V <sub>HSOL</sub>      | High-speed data signaling low, driver is off termination is on (measured single ended) | Full-/High-speed Signaling Levels <sup>(1)</sup> , PE disabled, test load is an ideal 45 $\Omega$ to GND on DP and DN.                                                                                                  | -10  |      | 10   | mV   |

| V <sub>CHIRPJ</sub>    | Host or hub chirp J level (differential voltage)                                       | Full-/High-speed Signaling Levels <sup>(1)</sup> , (PE is disabled. swing setting has no impact but slew rate control has impact), Test load is an ideal 1.5 k $\Omega$ pull up on DP.                                  | 700  | 900  | 1100 | mV   |

| V <sub>CHIRPK</sub>    | Device chirp K level (differential voltage)                                            | Full-/High-speed Signaling Levels <sup>(1)</sup> , (PE is disabled. swing setting has no impact but slew rate control has impact), Test load is an ideal 45 $\Omega$ to GND on DP and DN.                               | -900 | -760 | -500 | mV   |

| V <sub>CHIRPK</sub>    | Host or hub Chirp K level (differential voltage)                                       | Full-/High-speed Signaling Levels <sup>(1)</sup> , (PE is disabled. swing setting has no impact but slew rate control has impact), Test load is an ideal 1.5 kΩ pull up on DP.                                          | -900 | -700 | -500 | mV   |

| U2_TX <sub>PE</sub>    | High-speed TX pre-emphasis                                                             | U_HS_TX_PRE_EMPHASIS_Px setting 000, test load is an ideal 45 Ω to GND on DP and DN.                                                                                                                                    | 0.25 | 0.5  | 0.75 | dB   |

| U2_TX <sub>PE</sub>    | High-speed TX pre-emphasis                                                             | U_HS_TX_PRE_EMPHASIS_Px setting 100, test load is an ideal 45 Ω to GND on DP and DN.                                                                                                                                    | 1.7  | 2.1  | 2.5  | dB   |

| U2_TX <sub>PE_UI</sub> | High-speed TX pre-emphasis width                                                       | U_HS_TX_PE_WIDTH_Px setting 11 (measured with PE=2.5 dB setting of 101), Test load is an ideal 45 $\Omega$ to GND on DP and DN.                                                                                         | 0.54 | 0.65 | 0.77 | UI   |

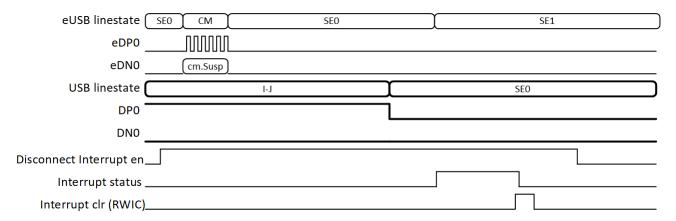

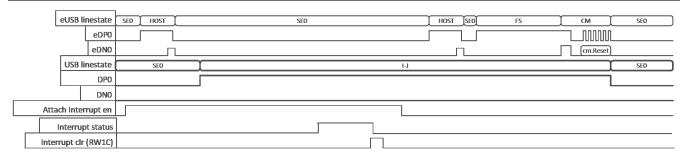

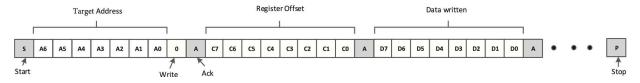

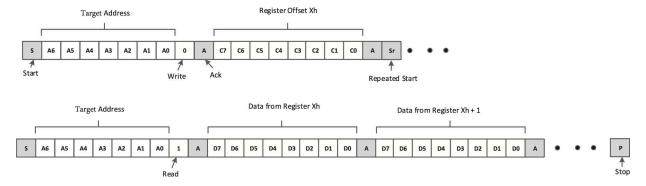

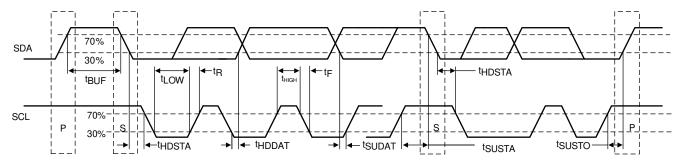

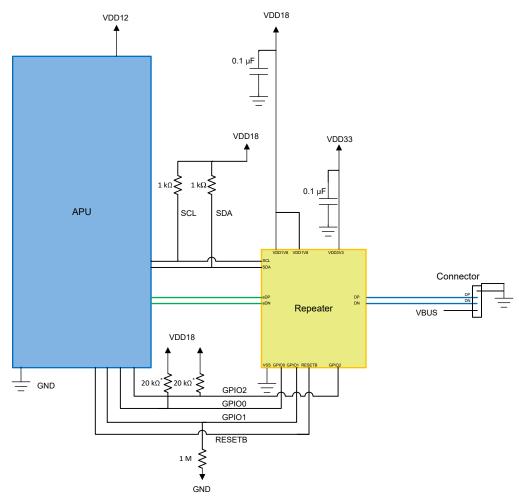

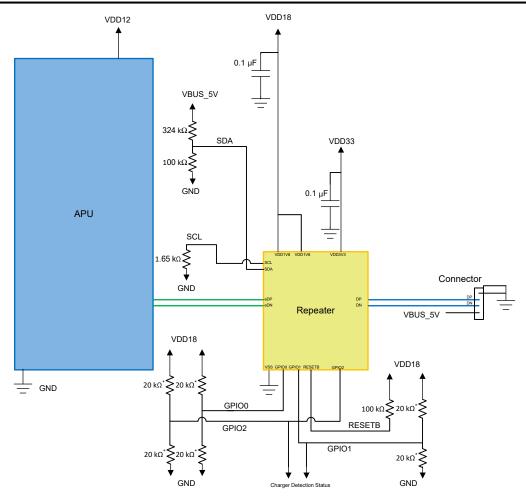

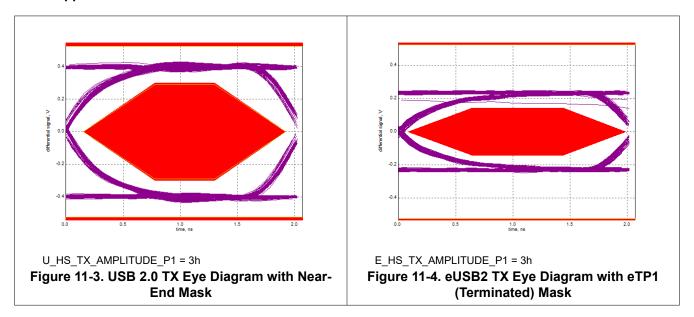

| eUSB2 TER              | RMINATION                                                                              |                                                                                                                                                                                                                         |      |      |      |      |