# Digital Control Compatible Synchronous-Buck Gate Driver With Current Sense and Fault Protection

Check for Samples: UCD7232

#### **FEATURES**

- · Dual High Current Drivers.

- Full Compatibility with TI Fusion Digital Power Supply Controllers, such as UCD91xx and UCD92xx Families

- Operational to 2 MHz Switching Frequency

- High-Side FET and Output Current Limit Protection with Independently Adjustable Thresholds

- Fast High-Side Overcurrent Sense Circuit with Fault Flag Output – Prevents Catastrophic Current Levels on a Cycle-by-Cycle Basis

- Differential High-Gain Current Sense Amplifier

- Voltage Proportional to Load Current Monitor Output

- Wide Input Voltage Range: 4.7 V to 15 V

Operation to 2.2 V Input Supported with an External 4.5-6.5 V Bias Supply

- Onboard Regulated Supplies for Gate Drive and Internal Circuits

- · Integrated Thermal Shutdown

- Selectable Operation Modes:

- PWM plus Synchronous Rectifier Enable (SRE) with Automatic Dead-Time Control

- Direct High-Gate and Low-Gate Inputs for Direct FET Control

- 3-State PWM Input for Power Stage Shutdown

- · UVLO Housekeeping Circuit

- Rated from –40°C to +125°C Junction Temperature

# **APPLICATIONS**

- Digitally-Controlled Synchronous-Buck Power Stages for Single- and Multi-Phase Applications

- Digitally-Controlled Power Modules

# **DESCRIPTION**

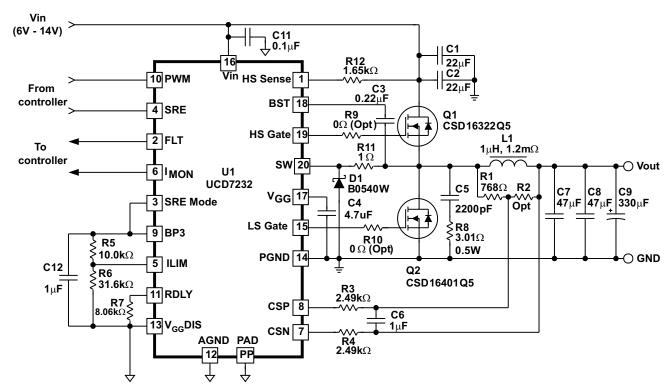

The UCD7232 high current driver is specifically designed digitally-controlled, point-of-load. for synchronous buck switching power supplies. Two driver circuits provide high charge and discharge current for the high-side NMOS switch and the low-side NMOS synchronous rectifier synchronous buck circuit. The MOSFET gates are driven by an internally regulated V<sub>GG</sub> supply. The internal V<sub>GG</sub> regulator can be disabled to permit the user to supply their own gate drive voltage. This flexibility allows a wide power conversion input voltage range of 2.2 to 15 V. Internal under voltage lockout (UVLO) logic insures V<sub>GG</sub> is good before allowing chip operation.

A drive logic block allows operation in one of two modes selected by the SRE Mode pin. In Synchronous Mode, the logic block uses the PWM signal to control both the high-side and low-side gate drive signals. Dead time is automatically adjusted to prevent cross conduction. The Synchronous Rectifier Enable (SRE) pin controls whether or not the low-side FET is turned on when the PWM signal is low. In Independent Mode, the PWM and SRE pins control the high-side and low-side gates directly. No anti-cross-conduction logic is used in this mode.

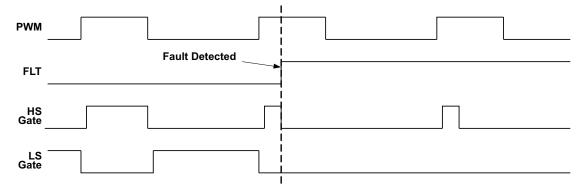

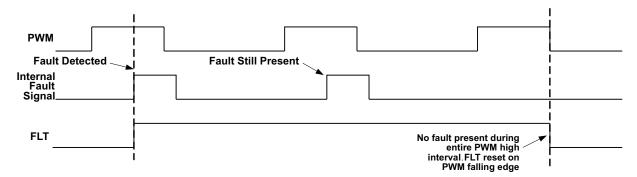

On-board comparators monitor the voltage across the high side switch and the voltage across an external current sense element to safeguard the power stage from sudden high current loads. Blanking delay is set for the high side comparator by a single resistor in order to avoid false reports coincident with switching edge noise. In the event of a high-side fault or an over-current fault, the high-side FET turned off and the Fault Flag (FLT) is asserted to alert the digital controller. The fault thresholds are independently set by the HS Sense and ILIM pins.

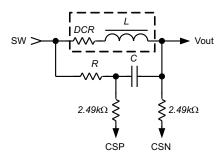

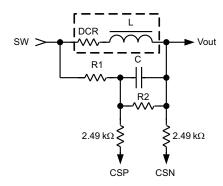

Output current is measured and monitored by a precision, high gain, switched capacitor differential amplifier that processes the voltage present across an external current sense element. The amplified signal is available for use by the digital controller on the  $I_{MON}$  pin. The current sense amplifier has output offset of 0.5 V so that both positive (sourcing) and negative (sinking) current can be sensed.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION (CONTINUED)**

An on-chip temperature sense monitors the die temperature. If it exceeds approximately 165°C, the temperature sensor will initiate a thermal shutdown that halts output switching and sets the FLT flag. The temperature fault automatically clears when the die temperatures falls by approximately 20°.

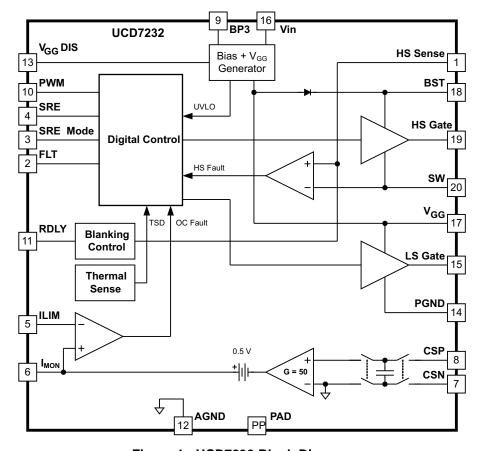

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. UCD7232 Block Diagram

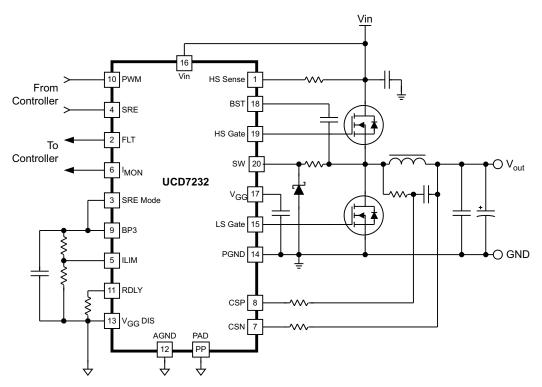

## SIMPLIFIED APPLICATION DIAGRAM

Figure 2. Typical Synchronous Buck Power Stage

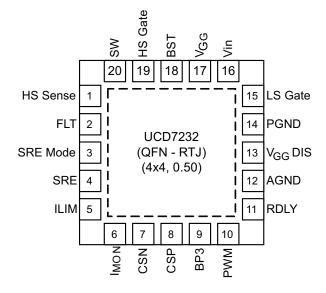

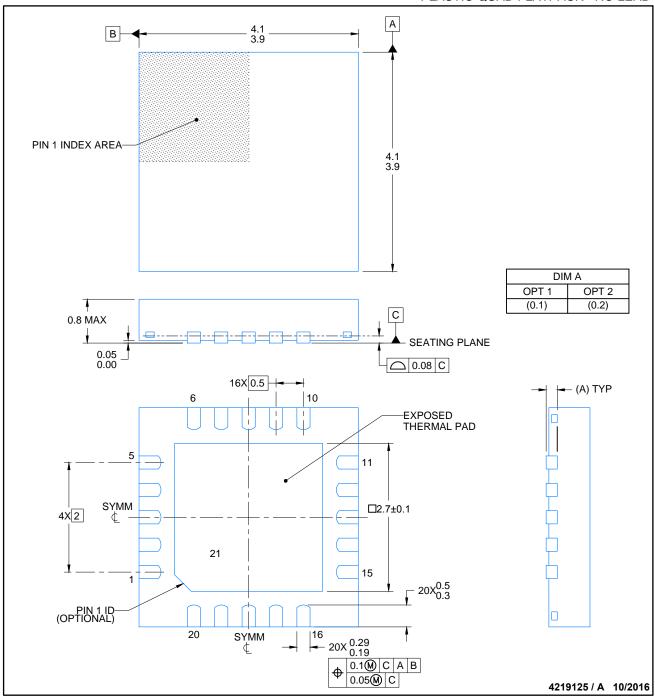

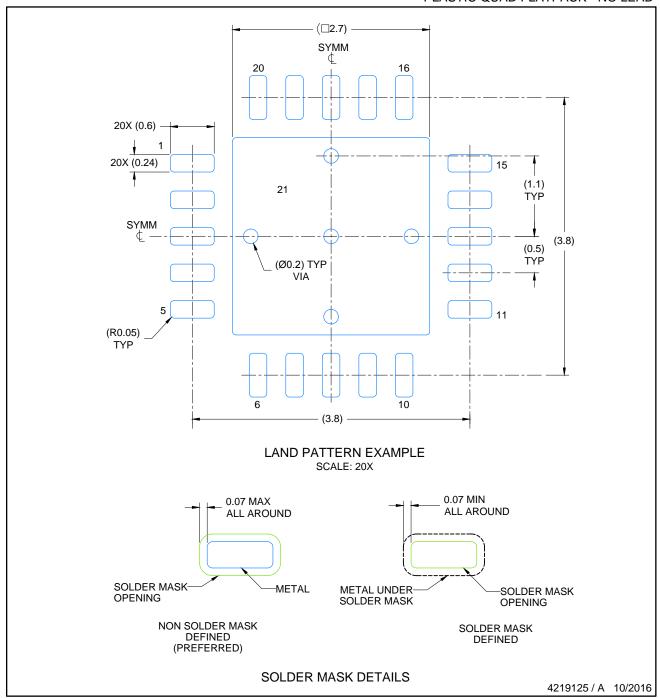

# **CONNECTION DIAGRAM**

#### **ORDERING INFORMATION**

| TEMPERATURE RANGE | PACKAGE               | TAPE AND REEL QTY | PART NUMBER |

|-------------------|-----------------------|-------------------|-------------|

| –40°C to +125°C   | Diagric OFN 20 (DT I) | 250               | UCD7232RTJT |

|                   | Plastic QFN-20 (RTJ)  | 2500              | UCD7232RTJR |

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

| <b>n</b>                                       | VALU                                                    | LINUT      |                      |    |  |  |

|------------------------------------------------|---------------------------------------------------------|------------|----------------------|----|--|--|

| P                                              | MIN                                                     | MAX        | UNIT                 |    |  |  |

| Supply voltage, V <sub>IN</sub>                |                                                         | -0.3       | 16                   | V  |  |  |

|                                                | V <sub>BST</sub> DC                                     | -0.3       | 23                   |    |  |  |

| Do estatuara constanta                         | V <sub>BST</sub> Pulse (V <sub>SW</sub> at 20V < 400ns) | -0.3       | 27                   | V  |  |  |

| Bootstrap voltage                              | V <sub>BST</sub> Pulse (V <sub>SW</sub> at 22V < 64ns)  | -0.3       | 29                   | V  |  |  |

|                                                | V <sub>BST</sub> Pulse (V <sub>SW</sub> at 30V < 16ns)  | -0.3       | 37                   |    |  |  |

| Gate drive supply voltage                      | V <sub>GG</sub> (Externally supplied)                   | -0.3       | 7                    | V  |  |  |

| Output acts drive valtage                      | HS Gate – SW                                            | 5 11 /     |                      |    |  |  |

| Output gate drive voltage                      | LS Gate                                                 | PGND - 0.3 | V <sub>GG</sub> +0.3 | V  |  |  |

|                                                | V <sub>SW</sub> DC                                      | -1         | 16                   |    |  |  |

| Cuitab nada valtaga                            | V <sub>SW</sub> Pulse < 400 ns, E = 20 μJ               | -2         | 20                   | V  |  |  |

| Switch node voltage                            | V <sub>SW</sub> Pulse < 64 ns                           | -5         | 22                   |    |  |  |

|                                                | V <sub>SW</sub> Pulse < 16 ns                           | -10        | 30                   | =  |  |  |

|                                                | CSP, CSN, RDLY                                          | -0.3       | 5.6                  |    |  |  |

| Analog inputs                                  | ILIM                                                    | -0.3       | 3.6                  | V  |  |  |

|                                                | HS Sense                                                | -0.3       | 16                   | 1  |  |  |

| Digital inputs                                 | PWM, SRE, SRE Mode                                      | -0.3       | 5.6                  |    |  |  |

| Digital inputs                                 | V <sub>GG</sub> DIS                                     | -0.3       | 3.6                  | V  |  |  |

| Analog outputs                                 | I <sub>MON</sub>                                        | -0.3       | 3.6                  | V  |  |  |

| Digital outputs                                | FLT                                                     | -0.3       | 3.6                  | V  |  |  |

| ECD Detine                                     | Human body model                                        |            | 2000                 | V  |  |  |

| ESD Rating                                     | Charged device model                                    |            | 500                  | V  |  |  |

| Operating ambient temperature, T <sub>A</sub>  |                                                         | -40        | 125                  | °C |  |  |

| Operating junction temperature, T <sub>J</sub> |                                                         | -40        | 150                  | °C |  |  |

| Storage temperature, T <sub>STG</sub>          |                                                         | -65        | 150                  | °C |  |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to AGND. Currents are positive into, negative out of the specified terminal. Consult company packaging information for thermal limitations and considerations of packages.

## THERMAL INFORMATION

|                         | THEDMAN METRIC(1)                            | UCD7232       | LINUTO |

|-------------------------|----------------------------------------------|---------------|--------|

|                         | THERMAL METRIC <sup>(1)</sup>                | RTJ (20 PINS) | UNITS  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 38.2          |        |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 34.4          |        |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 15.7          | °C/W   |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.4           | C/VV   |

| ΨЈВ                     | Junction-to-board characterization parameter | 15.7          |        |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 5.9           |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|          |                                                             | MIN | TYP | MAX | UNIT |

|----------|-------------------------------------------------------------|-----|-----|-----|------|

| $V_{IN}$ | Power Input Voltage (Internally generated V <sub>GG</sub> ) | 4.7 | 12  | 15  | V    |

| $V_{IN}$ | Power Input Voltage (Externally supplied V <sub>GG</sub> )  | 2.2 | -   | 15  | V    |

| $V_{GG}$ | Externally supplied gate drive voltage                      | 4.6 | 6   | 6.5 | V    |

| $T_{J}$  | Operating junction temperature range                        | -40 | _   | 125 | °C   |

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V, 4.7  $\mu F$  from  $V_{GG}$  to PGND, 1  $\mu F$  from BP3 to AGND, 0.22  $\mu F$  from BST to SW,  $T_A = T_J = -40^{\circ} C$  to 125°C, RDLY = 8.06k $\Omega$ , SRE Mode = 3.3V,  $V_{GG}$  DIS tied to AGND (unless otherwise noted)

|                       | PARAMETER                                                         | TEST CONDITIONS                                                                                             | MIN  | TYP  | MAX | UNIT |

|-----------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| SUPPLY SE             | CTION                                                             |                                                                                                             |      |      |     |      |

|                       | Supply current                                                    | Outputs not switching, V <sub>IN</sub> = 5 V, PWM = LOW                                                     |      | 8    | 10  | mA   |

|                       | Supply current                                                    | Outputs not switching, V <sub>IN</sub> = 15 V, PWM = LOW                                                    |      | 8    | 10  | mA   |

| GATE DRIV             | E UNDER-VOLTAGE LOCKOUT                                           |                                                                                                             |      |      |     |      |

| $V_{GG}$              | UVLO OFF                                                          | V <sub>GG</sub> rising                                                                                      |      | 4.4  | 4.6 | V    |

| $V_{GG}$              | UVLO ON                                                           | V <sub>GG</sub> falling                                                                                     | 4.1  | 4.3  |     | V    |

| $V_{GG}$              | UVLO hysteresis                                                   |                                                                                                             |      | 80   |     | mV   |

| V <sub>GG</sub> SUPPL | Y GENERATOR                                                       |                                                                                                             |      |      |     |      |

| \/                    |                                                                   | $V_{IN} \ge 7 \text{ V, I}_{GG} \le 100 \text{ mA}$                                                         | 5    |      |     | V    |

| $V_{GG}$              |                                                                   | V <sub>IN</sub> = 12 V, I_V <sub>GG</sub> ≤ 80 mA                                                           | 5.6  | 6.2  | 6.8 | V    |

|                       | Dropout                                                           | $V_{IN} = 4.75 \text{ V}, I_{QG} \le 100 \text{ mA}$                                                        |      |      | 350 | mV   |

| DIGITAL INI           | PUT SIGNALS (PWM, SRE)                                            |                                                                                                             |      |      |     |      |

| V <sub>IH_PWM</sub>   | Positive-going input threshold voltage                            |                                                                                                             |      | 1.8  | 2   | V    |

| $V_{IL\_PWM}$         | Negative-going input threshold voltage                            |                                                                                                             | 0.80 | 0.90 |     | V    |

| PWM                   | Input voltage hysteresis, $(V_{IH} - V_{IL})$                     |                                                                                                             |      | 0.90 |     | V    |

| V <sub>IH_SRE</sub>   | Positive-going input threshold voltage                            |                                                                                                             |      | 1.5  | 1.7 | V    |

| $V_{IL\_SRE}$         | Negative-going input threshold voltage                            |                                                                                                             | 0.9  | 1.00 |     | V    |

| SRE                   | Input voltage hysteresis, (V <sub>IH</sub> – V <sub>IL</sub> )    |                                                                                                             |      | 0.45 |     | V    |

|                       |                                                                   | V <sub>PWM</sub> = 5 V                                                                                      | 140  |      |     |      |

| I <sub>PWM</sub>      | Input current                                                     | V <sub>PWM</sub> = 3.3 V                                                                                    | 70   |      |     | μΑ   |

|                       |                                                                   | V <sub>PWM</sub> = 0 V                                                                                      |      |      |     |      |

|                       |                                                                   | V <sub>SRE</sub> = 5 V                                                                                      |      | 190  |     |      |

| I <sub>SRE</sub>      | Input current                                                     | V <sub>SRE</sub> = 3.3 V                                                                                    |      | 12   |     | μΑ   |

|                       |                                                                   | V <sub>SRE</sub> = 0 V                                                                                      |      |      |     |      |

| t <sub>HLD_R</sub>    | 3-state hold-off time <sup>(1)</sup>                              | V <sub>PWM</sub> transition from 0 V to 1.65 V,<br>Time until V <sub>LS Gate</sub> falls to 0 V             | 450  | 600  | 750 | ns   |

| t <sub>HLD_R</sub>    | 3-state recovery time (1)                                         | V <sub>PWM</sub> transition from 1.65 V to 0 V,<br>Time until V <sub>LS Gate</sub> rises to V <sub>GG</sub> | 150  | 330  | 500 | ns   |

| t <sub>min</sub>      | PWM minimum pulse to force HS gate pulse <sup>(1)</sup>           | C <sub>L</sub> = 3 nF at HS gate, VPWM = 3.3 V                                                              | 50   |      |     | ns   |

|                       | PWM frequency <sup>(1)</sup>                                      | $Qg_{HS} + Qg_{LS} < 46 \text{ nC}, V_{GG} = 6.4 \text{ V}$                                                 |      |      | 2   | MHz  |

| OUTPUT CL             | JRRENT LIMIT (ILIM)                                               |                                                                                                             |      |      |     |      |

|                       | ILIM Input impedance <sup>(1)</sup>                               |                                                                                                             |      | 250  |     | kΩ   |

|                       | ILIM set point range <sup>(1)</sup>                               |                                                                                                             | 0.5  |      | 3   | V    |

|                       | FLT output high level                                             | I <sub>LOAD</sub> = -2 mA                                                                                   | 2.7  | 3.3  |     | V    |

|                       | FLT output low level <sup>(1)</sup>                               | I <sub>LOAD</sub> = 2 mA                                                                                    |      | 0.1  | 0.6 | V    |

| t <sub>FAULT_HS</sub> | Fault detection time. Delay until HS Gate falling. <sup>(1)</sup> | V <sub>(ILIM)</sub> = 1.50 V, (CSP – CSN) = 20 mV,<br>CSN = 1.80 V                                          |      | 100  | 150 | ns   |

| t <sub>FAULT_LS</sub> | Fault detection time. Delay until LS Gate rising. (1)             | V <sub>(ILIM)</sub> = 1.50 V, (CSP - CSN) = 20 mV,<br>CSN = 1.80 V                                          |      | 150  | 200 | ns   |

<sup>(1)</sup> As designed and characterized. Not 100% tested in production.

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12V, 4.7  $\mu F$  from  $V_{GG}$  to PGND, 1  $\mu F$  from BP3 to AGND, 0.22  $\mu F$  from BST to SW,  $T_A = T_J = -40^{\circ} C$  to 125°C,

RDLY =  $8.06k\Omega$ , SRE Mode = 3.3V,  $V_{GG}$  DIS tied to AGND (unless otherwise noted)

| NDL1 = 0.0                          | $6kΩ$ , SRE Mode = 3.3V, $V_{GG}$ DIS tied PARAMETER                                                                                         | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN      | TYP  | MAX  | UNIT |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|

| t <sub>FAULT_FLT</sub>              | Fault detection time. Delay until FLT asserted (2)                                                                                           | V <sub>(ILIM)</sub> = 1.50 V, (CSP – CSN) = 20 mV,<br>CSN = 1.80 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 85   | 170  | ns   |

|                                     | Propagation delay from PWM to reset FLT <sup>(2)</sup>                                                                                       | PWM falling to FLT falling after a current limit event is cleared. PWM pulse width ≥100 ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 85   | 200  | ns   |

| CURRENT SE                          | NSE BLANKING (RDLY, HS Sense)                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |      |      |      |

| I <sub>RDLY</sub>                   | RDLY source current                                                                                                                          | $8.06 \text{ k}\Omega$ resistor from RDLY to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80       | 90   | 100  | μΑ   |

|                                     | RDLY resistance range <sup>(2)</sup>                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.5      | 8.06 | 10   | kΩ   |

| t <sub>BLANK</sub>                  | HS blanking time                                                                                                                             | RDLY = 8.06 k $\Omega$ . From SW rising to HS fault comparator enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110      | 125  | 140  | ns   |

| I <sub>HS Sense</sub>               | HS Sense sink current                                                                                                                        | $R_{HS Sense} = 2. k\Omega$ to $V_{IN}$ , $V_{IN} = 12 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 100  |      | μΑ   |

| t <sub>HSFAULT_HS</sub>             | HS fault detection time. Delay after $t_{\rm BLANK}$ until HS Gate falling $^{(2)}$                                                          | RDLY = 8.06 k $\Omega$ , R <sub>HS Sense</sub> = 2 k $\Omega$ to V <sub>IN</sub> , V <sub>IN</sub> = 12 V, V <sub>IN</sub> - V <sub>SW</sub> = 220 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 20   |      | ns   |

| t <sub>HSFAULT_LS</sub>             | HS fault detection time. Delay after t <sub>BLANK</sub> until LS Gate falling <sup>(2)</sup>                                                 | RDLY = 8.06 k $\Omega$ , R <sub>HS Sense</sub> = 2 k $\Omega$ to V <sub>IN</sub> , V <sub>IN</sub> = 12 V, V <sub>IN</sub> - V <sub>SW</sub> = 220 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 30   |      | ns   |

| CURRENT SE                          | NSE AMPLIFER (I <sub>MON</sub> , CSP, CSN)                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |      | ,    |      |

|                                     | V(I <sub>MON</sub> ) at no load                                                                                                              | CSP = CSN = 1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 460      | 500  | 540  | mV   |

|                                     | Closed loop DC gain                                                                                                                          | CSP - CSN = 10 mV; 0.5 V ≤ CSN ≤ 3.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48       | 50.2 | 52.4 | V/V  |

|                                     |                                                                                                                                              | Gain with 2.49k resistors in series with CSP, CSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45.6     | 47.8 | 49.9 | V/V  |

|                                     | Input impedance <sup>(2)</sup>                                                                                                               | Differential, CSP – CSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 100  |      | kΩ   |

| V <sub>CM</sub>                     | Input common mode voltage range <sup>(2)</sup>                                                                                               | V <sub>CM</sub> (max) is limited to (V <sub>GG</sub> – 1.2 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.3     |      | 5.6  | V    |

| V(I <sub>MON</sub> ) <sub>MIN</sub> |                                                                                                                                              | CSP = 1.2 V; CSN = 1.3 V; I(I <sub>MON</sub> ) = -250 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 0.1  | 0.15 | V    |

| V(I <sub>MON</sub> ) <sub>MAX</sub> |                                                                                                                                              | CSP = 1.3 V; CSN = 1.2 V; I(I <sub>MON</sub> ) = 500 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3        | 3.2  | 3.3  | V    |

| ( WOIV/W/OC                         | Sampling Rate <sup>(2)</sup>                                                                                                                 | , and the second |          | 5    |      | Msps |

| LOW-SIDE OU                         | UTPUT DRIVER (LS Gate)                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1        |      |      |      |

|                                     | Peak Source Current <sup>(2)</sup>                                                                                                           | V <sub>GG</sub> = 6.2 V, PWM = Low, LS Gate = 3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 6    |      | Α    |

|                                     | Peak Sink Current (2)                                                                                                                        | V <sub>GG</sub> = 6.2 V, PWM = High, LS Gate = 3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 6    |      | Α    |

| t <sub>RL</sub>                     | Rise Time <sup>(2)</sup>                                                                                                                     | C <sub>L</sub> = 6 nF, V <sub>IN</sub> = 12 V, V <sub>GG</sub> = 6.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 30   |      | ns   |

| t <sub>FL</sub>                     | Fall Time <sup>(2)</sup>                                                                                                                     | C <sub>L</sub> = 6 nF, V <sub>IN</sub> = 12 V, V <sub>GG</sub> = 6.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 20   |      | ns   |

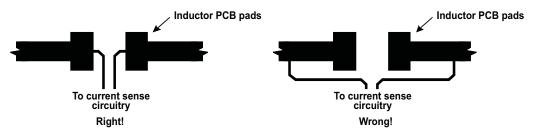

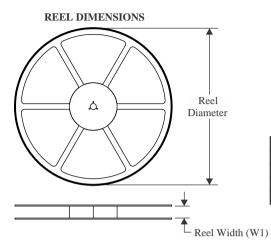

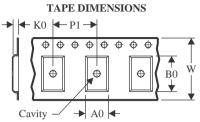

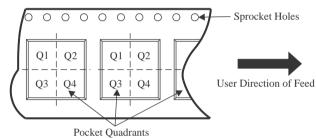

| 16                                  | Output with V <sub>GG</sub> <uvlo (2)<="" td=""><td>V<sub>GG</sub> = 1 V, Isink = 10 mA</td><td></td><td>0</td><td>0.5</td><td>V</td></uvlo> | V <sub>GG</sub> = 1 V, Isink = 10 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 0    | 0.5  | V    |