# Errata TMS320F2833x, TMS320F2823x Real-Time MCUs Silicon Errata (Silicon Revisions A, 0)

# **TEXAS INSTRUMENTS**

### ABSTRACT

This document describes the known exceptions to the functional specifications (advisories). This document may also contain usage notes. Usage notes describe situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness.

# **Table of Contents**

| 1 Usage Notes and Advisories Matrices                                          | <mark>2</mark> |

|--------------------------------------------------------------------------------|----------------|

| 1 Usage Notes and Advisories Matrices           1.1 Usage Notes Matrix         | 2              |

| 1.2 Advisories Matrix                                                          |                |

| 2 Nomenclature, Package Symbolization, and Revision Identification             | 3              |

| 2.1 Device and Development Support Tool Nomenclature                           | 3              |

| 2.2 Devices Supported                                                          | 3              |

| 2.2 Devices Supported<br>2.3 Package Symbolization and Revision Identification | 4              |

| 2.4 Silicon Change Overview                                                    | 6              |

| 3 Silicon Revision A Usage Notes and Advisories                                | 7              |

| 3.1 Silicon Revision A Usage Notes                                             | 7              |

| 3.2 Silicon Revision A Advisories                                              | 9              |

| 4 Silicon Revision 0 Usage Notes and Advisories                                | 19             |

| 4.1 Silicon Revision 0 Usage Notes                                             | 19             |

| 4.2 Silicon Revision 0 Advisories                                              | 19             |

| 5 Documentation Support                                                        | 22             |

| 6 Trademarks                                                                   | 22             |

| 7 Revision History                                                             |                |

|                                                                                |                |

# **List of Figures**

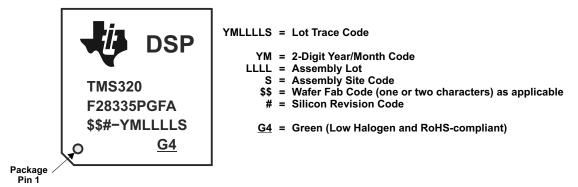

| Figure 2-1. Example of Device Markings (PGF)                                                       | 4  |

|----------------------------------------------------------------------------------------------------|----|

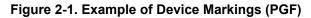

| Figure 2-2. Example of Device Markings (ZAY)                                                       |    |

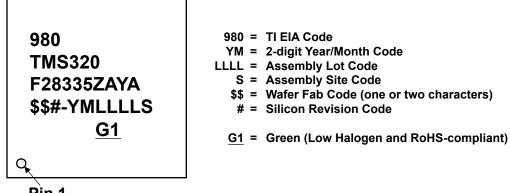

| Figure 2-3. Device Nomenclature                                                                    | 5  |

| Figure 3-1. Difference Between Expected and Erroneous Operation of START Bit                       | 9  |

| Figure 3-2. Pipeline Diagram of the Issue When There are no Stalls in the Pipeline                 |    |

| Figure 3-3. Pipeline Diagram of the Issue if There is a Stall in the E3 Slot of the Instruction I1 | 14 |

| Figure 3-4. Pipeline Diagram With Workaround in Place                                              | 15 |

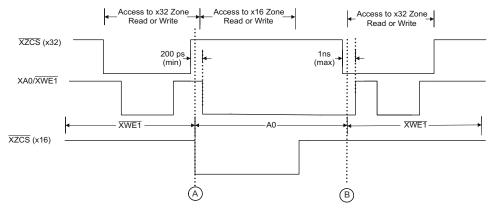

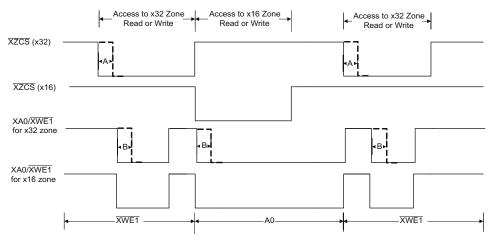

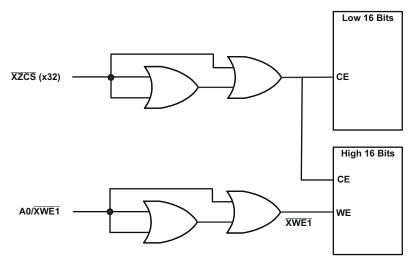

| Figure 4-1. Behavior of Zone Chip Select Signals and XA0/ XWE1                                     | 20 |

| Figure 4-2. Behavior After Application of Delay                                                    | 21 |

| Figure 4-3. Example Delay Line Circuit                                                             | 21 |

|                                                                                                    |    |

# List of Tables

| Table 1-1. Usage Notes Matrix                                                   | . 2 |

|---------------------------------------------------------------------------------|-----|

| Table 1-2. Advisories Matrix                                                    | .2  |

| Table 2-1. Determining Silicon Revision From Lot Trace Code (F2833x and F2823x) | .4  |

| Table 2-2. TMS320F2833x and TMS320F2823x Silicon Change Overview                | .6  |

1

# **1 Usage Notes and Advisories Matrices**

Table 1-1 lists all usage notes and the applicable silicon revision(s). Table 1-2 lists all advisories, modules affected, and the applicable silicon revision(s).

### 1.1 Usage Notes Matrix

| NUMBER        | TITLE                                                                                                                                                             | SILICON<br>REVISION(S)<br>AFFECTED |     |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|--|

|               |                                                                                                                                                                   | 0                                  | Α   |  |

| Section 3.1.1 | PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt Mask Clear                                                                | Yes                                | Yes |  |

| Section 3.1.2 | Caution While Using Nested Interrupts                                                                                                                             | Yes                                | Yes |  |

| Section 3.1.3 | Watchdog: Watchdog Issues Reset After Bad Key is Written                                                                                                          | Yes                                | Yes |  |

| Section 3.1.4 | McBSP: XRDY Bit can Hold the Not-Ready Status (0) if New Data is Written to the DX1<br>Register Without First Verifying if the XRDY Bit is in its Ready State (1) | Yes                                | Yes |  |

| Section 3.1.5 | Maximum Flash Program Time and Erase Time in Revision O of the <i>TMS320F2833x,</i><br><i>TMS320F2823x Real-Time Microcontrollers</i> Data Sheet                  |                                    | Yes |  |

### Table 1-1. Usage Notes Matrix

### **1.2 Advisories Matrix**

| MODULE | DESCRIPTION                                                                                     | SILICON<br>REVISION(S)<br>AFFECTED |     |  |

|--------|-------------------------------------------------------------------------------------------------|------------------------------------|-----|--|

|        |                                                                                                 | 0                                  | A   |  |

| SCI    | SCI: Incorrect Operation of SCI in Address Bit Mode                                             | Yes                                | Yes |  |

| ADC    | ADC: Simultaneous Sampling Latency                                                              | Yes                                | Yes |  |

| ADC    | ADC: ADC Inaccuracy at Low Frequencies                                                          | Yes                                | Yes |  |

| GPIO   | GPIO: GPIO Qualification                                                                        | Yes                                | Yes |  |

| eCAN   | eCAN: Abort Acknowledge Bit Not Set                                                             | Yes                                | Yes |  |

| eCAN   | eCAN: Unexpected Cessation of Transmit Operation                                                | Yes Yes                            |     |  |

| FPU    | FPU: CPU-to-FPU Register Move Operation Followed By F32TOUI32, FRACF32, or UI16TOF32 Operations | Yes                                | Yes |  |

| FPU    | FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation                        | Yes                                | Yes |  |

| eQEP   | eQEP: eQEP Inputs in GPIO Asynchronous Mode                                                     | Yes                                | Yes |  |

| eQEP   | eQEP: Position Counter Incorrectly Reset on Direction Change During Index                       | Yes                                | Yes |  |

| eQEP   | eQEP: Missed First Index Event                                                                  |                                    | Yes |  |

| Memory | Memory: Prefetching Beyond Valid Memory                                                         | Yes                                | Yes |  |

| Memory | Memory: Possible Incorrect Operation of XINTF Module After Power Up                             | Yes                                | Yes |  |

| Memory | Memory: M1 Memory Access Conflict                                                               | Yes                                |     |  |

|        | Boot to XINTF x16, x32 and Parallel Boot Setup Issue                                            | Yes                                |     |  |

| XINTF  | XINTF Rogue Write for Back-to-Back Accesses to x16/x32 Zones                                    | Yes                                |     |  |

### Table 1-2. Advisories Matrix

### 2 Nomenclature, Package Symbolization, and Revision Identification 2.1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all [TMS320] DSP devices and support tools. Each TMS320<sup>™</sup> DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (for example, **TMS**320F28335). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/ tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **TMP** Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications.

- TMS Production version of the silicon die that is fully qualified.

Support tool development evolutionary flow:

**TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

**TMDS** Fully-qualified development-support product.

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, ZJZ) and temperature range (for example, A).

### 2.2 Devices Supported

This document supports the following devices:

- TMS320F28335

- TMS320F28335-Q1

- TMS320F28334

- TMS320F28333

- TMS320F28332

- TMS320F28235

- TMS320F28235-Q1

- TMS320F28234

- TMS320F28234-Q1

- TMS320F28232

- TMS320F28232-Q1

# 2.3 Package Symbolization and Revision Identification

Figure 2-1 and Figure 2-2 provide examples of the F2833x and F2823x device markings and define each of the markings. The device revision can be determined by the symbols marked on the top of the package as shown in Figure 2-1 and Figure 2-2. Some prototype devices may have markings different from those illustrated. Figure 2-3 shows the device nomenclature.

Figure 2-2. Example of Device Markings (ZAY)

| SILICON REVISION CODE                 | SILICON REVISION     | REVISION ID<br>Address: 0x0883 | COMMENTS                                        |  |  |  |

|---------------------------------------|----------------------|--------------------------------|-------------------------------------------------|--|--|--|

| Blank<br>(no second letter in prefix) | Indicates Revision 0 | 0x0000                         | This silicon revision is available as TMX only. |  |  |  |

| A                                     | Indicates Revision A | 0x0001                         | This silicon revision is TMS.                   |  |  |  |

### 2.4 Silicon Change Overview

Table 2-2 lists the change(s) made to each silicon revision.

| Table 2-2. TMS320F2833x and TMS320F2823x Silicon Change Overview |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| REVISION                                                         | CHANGES MADE                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| 0                                                                | First silicon release                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| А                                                                | Changes<br>The following changes are implemented with Revision A:                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                                                                  | • Flash API version 2.00 is needed for Rev A silicon. This version is backward-compatible with Rev 0 silicon.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                                                                  | McBSP boot loader                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                                                                  | <ul><li>McBSP loader will now echo back the data received. This was not the case on Rev 0.</li><li>DMA connection to ePWM</li></ul>                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                                                                  | The ePWM/HRPWM modules can be re-mapped to peripheral frame 3 where they can be accessed by the DMA module.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                                                                  | In addition, the SOCA and SOCB of each EPWM module is connected to the DMA at the following peripheral interrupt select positions in each channel MODE register (MODE[PERINTSEL(4:0)] bits):                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|                                                                  | $\begin{array}{l} EPWM1\text{-}SOCA \to PERINTSEL(18) \\ EPWM1\text{-}SOCB \to PERINTSEL(20) \\ EPWM2\text{-}SOCA \to PERINTSEL(21) \\ EPWM3\text{-}SOCB \to PERINTSEL(22) \\ EPWM3\text{-}SOCB \to PERINTSEL(23) \\ EPWM4\text{-}SOCA \to PERINTSEL(24) \\ EPWM4\text{-}SOCB \to PERINTSEL(25) \\ EPWM4\text{-}SOCA \to PERINTSEL(26) \\ EPWM5\text{-}SOCA \to PERINTSEL(27) \\ EPWM6\text{-}SOCA \to PERINTSEL(28) \\ EPWM6\text{-}SOCB \to PERINTSEL(29) \end{array}$ |  |  |  |  |  |  |  |  |

|                                                                  | The PARTID register moved to address 0x380090. PARTID values changed. See the <i>TMS320F2833x</i> , <i>TMS320F2823</i><br><i>Real-Time Microcontrollers</i> data sheet for details.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                                                                  | The address 0x882 (formerly the PARTID register) is now called the CLASSID register. See the <i>TMS320F2833x</i> ,<br><i>TMS320F2823x Real-Time Microcontrollers</i> data sheet for details.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|                                                                  | Advisories Fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                                                                  | The following advisories are fixed in rev A :                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                                                                  | Boot to XINTF x16, x32 and Parallel Boot Setup Issue                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                                                                  | M1 memory access conflict                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|                                                                  | XINTF rogue write for back-to-back accesses to x16/x32 zones.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                                                                  | Behavior changed such that external delay logic is no longer required to avoid this issue on Rev A. The behavior                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                                                                  | of the XA0/ XWE1 signal has been modified such that it goes high during inactive cycles. Use the XBANK feature                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                                                                  | to force inactive cycles between back-to-back zone accesses. See the External Interface (XINTF) chapter of the                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                                                                  | TMS320x2833x, TMS320x2823x Real-Time Microcontrollers Technical Reference Manual for more information.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

## **3 Silicon Revision A Usage Notes and Advisories**

This section lists the usage notes and advisories for this silicon revision.

### 3.1 Silicon Revision A Usage Notes

This section lists all the usage notes that are applicable to silicon revision A [and earlier silicon revisions].

# 3.1.1 PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt Mask Clear Usage Note

### Revision(s) Affected: 0, A

Certain code sequences used for nested interrupts allow the CPU and PIE to enter an inconsistent state that can trigger an unwanted interrupt. The conditions required to enter this state are:

- 1. A PIEACK clear is followed immediately by a global interrupt enable (EINT or asm(" CLRC INTM")).

- 2. A nested interrupt clears one or more PIEIER bits for its group.

Whether the unwanted interrupt is triggered depends on the configuration and timing of the other interrupts in the system. This is expected to be a rare or nonexistent event in most applications. If it happens, the unwanted interrupt will be the first one in the nested interrupt's PIE group, and will be triggered after the nested interrupt re-enables CPU interrupts (EINT or asm(" CLRC INTM")).

**Workaround:** Add a NOP between the PIEACK write and the CPU interrupt enable. Example code is shown below.

```

//Bad interrupt nesting code

PieCtrlRegs.PIEACK.all = 0xFFFF; //Enable nesting in the PIE

EINT; //Enable nesting in the CPU

//Good interrupt nesting code

PieCtrlRegs.PIEACK.all = 0xFFFF; //Enable nesting in the PIE

asm(" NOP"); //Wait for PIEACK to exit the pipeline

EINT; //Enable nesting in the CPU

```

### 3.1.2 Caution While Using Nested Interrupts

### Revision(s) Affected: 0, A

If the user is enabling interrupts using the EINT instruction inside an interrupt service routine (ISR) in order to use the nesting feature, then the user must disable the interrupts before exiting the ISR. Failing to do so may cause undefined behavior of CPU execution.

### 3.1.3 Watchdog: Watchdog Issues Reset After Bad Key is Written

### Revision(s) Affected: 0, A

Whenever a bad key is written, the watchdog issues a reset. But if a good key is written after a bad key, the watchdog does not issue a reset.

7

# 3.1.4 McBSP: XRDY Bit can Hold the Not-Ready Status (0) if New Data is Written to the DX1 Register Without First Verifying if the XRDY Bit is in its Ready State (1)

### Revision(s) Affected: 0, A

If the XRDY bit is used to properly gate writes to the DX2/DX1 registers, this condition does not occur.

Per the operation of the McBSP, a write to the DX1 data transmit register automatically clears the XRDY bit, indicating a not-ready status. Once this data is transferred to the internal transmit shift register (XSR1), the McBSP HW sets the XRDY bit to indicate a ready status, and new data can be written to DX2/DX1 data transmit registers.

If the set and clear of XRDY occur on the same CPU clock cycle, the XRDY bit remains cleared and the new data in DX2/DX1 is not transmitted.

In this state of XRDY = 0, the McBSP will appear not-ready indefinitely.

Any subsequent writes to DX2/DX1 will behave normally and the XRDY bit will function normally.

**Workaround:** When transmitting multiple words of data using the McBSP module, the XRDY bit in the SPCR2 register should be polled before writing new data to the DX2/DX1 registers in order to prevent overwriting. For those modules that do not have access to the XRDY bit (such as the DMA controller), the XINT interrupt inside the McBSP module can be configured to reflect XRDY (through the XINTM bits in the SPCR2 register) and this can also be used to gate writes to the DX2/DX1 registers. This also ensures the XRDY bit is not set and cleared on the same CPU cycle, causing the above "indefinite not-ready" condition.

If the system allows multiple bus controllers (such as the C28x CPU and the DMA controller) to write to the DX2/DX1 registers, then the ready-state of the XRDY bit should be validated prior to passing control of the McBSP to a different bus controller. This ensures that the state of XRDY is accurate and the simultaneous set/clear action does not occur.

**3.1.5 Maximum Flash Program Time and Erase Time in Revision O of the** *TMS320F2833x, TMS320F2823x Real-Time Microcontrollers* **Data Sheet**

### Revision(s) Affected: A

The maximum flash "Program time" and "Erase time" that were added in revision O of the *TMS320F2833x*, *TMS320F2823x Real-Time Microcontrollers* data sheet are only applicable for devices manufactured after March 2019.

### 3.2 Silicon Revision A Advisories

This section lists all the advisories that are applicable to silicon revision A [and earlier silicon revisions].

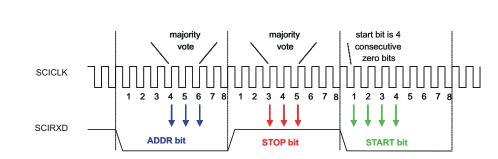

### Advisory SCI: Incorrect Operation of SCI in Address Bit Mode

### Revision(s) Affected 0, A

Details

SCI does not look for STOP bit after the ADDR bit. Instead, SCI starts looking for the start bit beginning on sub-sample 6 of the ADDR bit. Slow rise-time from ADDR to STOP bit can cause the false START bit to occur since the 4th sub-sample for the start bit may be sensed low.

Erroneous Operation:

Expected Operation:

**Workaround(s)** Program the baud rate of the SCI to be slightly slower than the actual. This will cause the 4th sub-sample of the false START bit to be delayed in time, and therefore occur more towards the middle of the STOP bit (away from the signal transition region). The amount of baud slowing needed depends on the rise-time of the signal in the system. Alternatively, IDLE mode of the SCI module may be used, if applicable.

9

| Advisory             | dvisory ADC: Simultaneous Sampling Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Revision(s) Affected | Revision(s) Affected 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Details              | When the ADC conversions are initiated in simultaneous mode, the first sample pair will not give correct conversion results.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Workaround(s)        | 1. If the ADC is used with a sampling window $\leq$ 160 nS, then the first sample pair must<br>be discarded and a second sample of the same pair must be taken. For instance, if<br>the sequencer is set to sample channel A0:B0/A1:B1/A2:B2 in that order, then load the<br>sequencer with A0:B0/A0:B0/A1:B1/A2:B2 and only use the last three conversions.                                                                                                                                   |  |  |  |  |  |  |  |

|                      | 2. If the ADC is used with a sampling window greater than 160 ns, there is no issue.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Advisory             | ADC: ADC Inaccuracy at Low Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Details              | At ADCCLK frequencies of less than 1 MHz, the ADC may give inaccurate results on some devices. The inaccuracy will be worse at cold temperature. Small ACQPS settings (less than 3) are more likely to show the inaccuracy.                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Workaround(s)        | Operate ADCCLK at 1 MHz or above.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                      | There is no performance improvement gained by operating the ADCCLK at low frequencies. It is recommended that ADCCLK be set at the maximum value specified in the data sheet or down to one-half the maximum value specified in the data sheet.                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Advisory             | GPIO: GPIO Qualification                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Details              | If a GPIO pin is configured for "n" SYSCLKOUT cycle qualification period (where $1 \le n \le 510$ ) with "m" qualification samples (m = 3 or 6), it is possible that an input pulse of [n * m - (n - 1)] width may get qualified (instead of n * m). This depends upon the alignment of the asynchronous GPIO input signal with respect to the phase of the internal prescaled clock, and hence, is not deterministic. The probability of this kind of wrong qualification occurring is "1/n". |  |  |  |  |  |  |  |

|                      | Worst-case example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                      | If n = 510, m = 6, a GPIO input width of (n * m) = 3060 SYSCLKOUT cycles is required to pass qualification. However, because of the issue described in this advisory, the minimum GPIO input width which may get qualified is $[n * m - (n - 1)] = 3060 - 509 = 2551$ SYSCLKOUT cycles.                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Workaround(s)        | None. Ensure a sufficient margin is in the design for input qualification.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Advisory             | eCAN: Abort Acknowledge Bit Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | I 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Details              | After setting a Transmission Request Reset (TRR) register bit to abort a message, there are some rare instances where the TRRn and TRSn bits will clear without setting the Abort Acknowledge (AAn) bit. The transmission itself is correctly aborted, but no interrupt is asserted and there is no indication of a pending operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | <ol> <li>In order for this rare condition to occur, all of the following conditions must happen:</li> <li>The previous message was not successful, either because of lost arbitration or because no node on the bus was able to acknowledge it or because an error frame resulted from the transmission. The previous message need not be from the same mailbox in which a transmit abort is currently being attempted.</li> <li>The TRRn bit of the mailbox should be set in a CPU cycle immediately following the cycle in which the TRSn bit was set. The TRSn bit remaining set due to incompletion of transmission satisfies this condition as well; that is, the TRSn bit could have been set in the past, but the transmission remains incomplete.</li> <li>The TRRn bit must be set in the exact SYSCLKOUT cycle where the CAN module is in idle state for one cycle. The CAN module is said to be in idle state when it is not in the process of receiving/transmitting data.</li> </ol> |

|                      | If these conditions occur, then the TRRn and TRSn bits for the mailbox will clear $t_{clr}$<br>SYSCLKOUT cycles after the TRR bit is set where:<br>$t_{clr} = [(mailbox_number) * 2] + 3$ SYSCLKOUT cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                      | The TAn and AAn bits will not be set if this condition occurs. Normally, either the TA or AA bit sets after the TRR bit goes to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Workaround(s)        | When this problem occurs, the TRRn and TRSn bits will clear within $t_{clr}$ SYSCLKOUT cycles. To check for this condition, first disable the interrupts. Check the TRRn bit $t_{clr}$ SYSCLKOUT cycles after setting the TRRn bit to make sure it is still set. A set TRRn bit indicates that the problem did not occur.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                      | If the TRRn bit is cleared, it could be because of the normal end of a message and the corresponding TAn or AAn bit is set. Check both the TAn and AAn bits. If either one of the bits is set, then the problem did not occur. If they are both zero, then the problem did occur. Handle the condition like the interrupt service routine would except that the AAn bit does not need clearing now.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | If the TAn or AAn bit is set, then the normal interrupt routine will happen when the interrupt is re-enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Advisory             | eCAN: Unexpected Cessation of Transmit Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Revision(s) Affected | Г <mark>О, А</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Details              | In rare instances, the cessation of message transmission from the eCAN module has been observed (while the receive operation continues normally). This anomalous state may occur without any error frames on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Workaround(s)        | The Time-out feature (MOTO) of the eCAN module may be employed to detect this condition. When this occurs, set and clear the CCR bit (using the CCE bit for verification) to remove the anomalous condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Advisory FPU: CPU-to-FPU Register Move Operation Followed By F32TOUI32, FRACF32, or UI16TOF32 Operations

### Revision(s) Affected 0, A

**Details**

This advisory applies when the write phase of a CPU-to-FPU register write coincides with the execution phase of the F32TOUI32, FRACF32, or UI16TOF32 instructions. If the F32TOUI32 instruction execution and CPU-to-FPU register write operation occur in the same cycle, the target register (of the CPU-to-FPU register write operation) gets overwritten with the output of the F32TOUI32 instruction instead of the data present on the C28x data write bus. This scenario also applies to the following instructions:

- F32TOUI32 RaH, RbH

- FRACF32 RaH , RbH

- UI16TOF32 RaH , mem16

- UI16TOF32 RaH , RbH

# **Workaround(s)** A CPU-to-FPU register write must be followed by a gap of five NOPs or non-conflicting instructions before F32TOUI32, FRACF32, or UI16TOF32 can be used.

The C28x code generation tools v6.0.5 (for the 6.0.x branch), v6.1.2 (for the 6.1.x branch), and later check for this scenario.

### **Example of Problem:**

```

SUBF32 R5H, R3H, R1H

|| MOV32 *--XAR4, R4H

EISQRTF32 R4H, R2H

UI16TOF32 R2H, R3H

MOV32 R0H, @XAR0 ; Write to R0H register

NOP ;

NOP ;

F32TOUI32 R1H, R1H ; R1H gets written to R0H

I16TOF32 R6H, R3H

```

Example of Workaround:

```

SUBF32 R5H, R3H, R1H

|| MOV32 *--XAR4, R4H

EISQRTF32 R4H, R2H

UI16TOF32 R2H, R3H

MOV32 R0H, @XAR0 ; Write to R0H register

NOP

NOP

NOP

NOP

NOP

F32TOUI32 R1H, R1H

I16TOF32 R6H, R3H

```

### Advisory FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

### Revision(s) Affected 0, A

#### Details

This advisory applies when a multi-cycle (2p) FPU instruction is followed by a FPU-to-CPU register transfer. If the FPU-to-CPU read instruction source register is the same as the 2p instruction destination, then the read may be of the value of the FPU register before the 2p instruction completes. This occurs because the 2p instructions rely on dataforwarding of the result during the E3 phase of the pipeline. If a pipeline stall happens to occur in the E3 phase, the result does not get forwarded in time for the read instruction.

The 2p instructions impacted by this advisory are MPYF32, ADDF32, SUBF32, and MACF32. The destination of the FPU register read must be a CPU register (ACC, P, T, XAR0...XAR7). This advisory does not apply if the register read is a FPU-to-FPU register transfer.

In the example below, the 2p instruction, MPYF32, uses R6H as its destination. The FPU register read, MOV32, uses the same register, R6H, as its source, and a CPU register as the destination. If a stall occurs in the E3 pipeline phase, then MOV32 will read the value of R6H before the MPYF32 instruction completes.

### **Example of Problem:**

| MPYF32 R6H, R5H, R0H                        | ; 2p FPU instruction that writes to R6H         |

|---------------------------------------------|-------------------------------------------------|

| F32TOUI16R R3H, R4H<br>ADDF32 R2H, R2H, R0H | ; delay slot                                    |

|                                             | ; alignment cycle<br>; FPU register read of R6H |

Figure 3-2 shows the pipeline diagram of the issue when there are no stalls in the pipeline.

|    | Instruction                                   | F1 | F2      | D1     | D2 | R1 | R2        | E  | w  |           |                                                                                                                                                                                                                                                                       |  |

|----|-----------------------------------------------|----|---------|--------|----|----|-----------|----|----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    |                                               |    | FPU pip | eline> | >  | R1 | R2        | E1 | E2 | E3        | Comments                                                                                                                                                                                                                                                              |  |

| I1 | MPYF32 R6H, R5H, R0H<br>   MOV32 *XAR7++, R4H | Il |         |        |    |    |           |    |    |           |                                                                                                                                                                                                                                                                       |  |

| I2 | F32TOUI16R R3H, R4H                           | I2 | I1      |        |    |    |           |    |    |           |                                                                                                                                                                                                                                                                       |  |

| I3 | ADDF32 R3H, R2H, R0H<br>   MOV32 *SP, R2H     | I3 | I2      | Il     |    |    |           |    |    |           |                                                                                                                                                                                                                                                                       |  |

| I4 | MOV32 @XAR3, R6H                              | I4 | I3      | I2     | I1 |    |           |    |    |           |                                                                                                                                                                                                                                                                       |  |

|    |                                               |    | I4      | I3     | I2 | I1 |           |    |    |           |                                                                                                                                                                                                                                                                       |  |

|    |                                               |    |         | I4     | I3 | I2 | I1        |    |    |           |                                                                                                                                                                                                                                                                       |  |

|    |                                               |    |         |        | I4 | I3 | I2        | I1 |    |           |                                                                                                                                                                                                                                                                       |  |

|    |                                               |    |         |        |    | I4 | I3        | I2 | I1 |           |                                                                                                                                                                                                                                                                       |  |

|    |                                               |    |         |        |    |    | <u>14</u> | 13 | 12 | <u>11</u> | 14 samples the result as it enters<br>the R2 phase. The product<br>R6H=R5H*R0H (II) finishes<br>computing in the E3 phase, but is<br>forwarded as an operand to I4.<br>This makes I4 appear to be a 2p<br>instruction, but I4 actually takes<br>3p cycles to compute. |  |

|    |                                               |    |         |        |    |    |           | I4 | I3 | I2        |                                                                                                                                                                                                                                                                       |  |

|    |                                               |    |         |        |    |    |           |    | I4 | I3        |                                                                                                                                                                                                                                                                       |  |

Figure 3-2. Pipeline Diagram of the Issue When There are no Stalls in the Pipeline

### Advisory (continued) FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

Figure 3-3 shows the pipeline diagram of the issue if there is a stall in the E3 slot of the instruction I1.

|    | Instruction                                   | F1            | F2 | D1 | D2 | R1 | R2        | E  | w  |               |                                                                                                                                                                                                                                              |

|----|-----------------------------------------------|---------------|----|----|----|----|-----------|----|----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                               | FPU pipeline> |    |    | R1 | R2 | E1        | E2 | E3 | Comments      |                                                                                                                                                                                                                                              |

| Il | MPYF32 R6H, R5H, R0H<br>   MOV32 *XAR7++, R4H | Il            |    |    |    |    |           |    |    |               |                                                                                                                                                                                                                                              |

| I2 | F32TOUI16R R3H, R4H                           | I2            | I1 |    |    |    |           |    |    |               |                                                                                                                                                                                                                                              |

| I3 | ADDF32 R3H, R2H, R0H<br>   MOV32 *SP, R2H     | I3            | I2 | Il |    |    |           |    |    |               |                                                                                                                                                                                                                                              |

| I4 | MOV32 @XAR3, R6H                              | I4            | I3 | I2 | I1 |    |           |    |    |               |                                                                                                                                                                                                                                              |

|    |                                               |               | I4 | I3 | I2 | I1 |           |    |    |               |                                                                                                                                                                                                                                              |

|    |                                               |               |    | I4 | I3 | I2 | I1        |    |    |               |                                                                                                                                                                                                                                              |

|    |                                               |               |    |    | I4 | I3 | I2        | I1 |    |               |                                                                                                                                                                                                                                              |

|    |                                               |               |    |    |    | I4 | I3        | I2 | I1 |               |                                                                                                                                                                                                                                              |

|    |                                               |               |    |    |    |    | <u>14</u> | 13 | I2 | I1<br>(STALL) | I4 samples the result as it enters<br>the R2 phase, but I1 is stalled in<br>E3 and is unable to forward the<br>product of R5H*R0H to I4 (R6H does<br>not have the product yet due to a<br>design bug). So, I4 reads the old<br>value of R6H. |

|    |                                               |               |    |    |    |    | I4        | I3 | I2 | 11            | There is no change in the pipeline<br>as it was stalled in the previous<br>cycle. I4 had already sampled the<br>old value of R6H in the previous<br>cycle.                                                                                   |

|    |                                               |               |    |    |    |    |           | Ι4 | IЗ | I2            | Stall over                                                                                                                                                                                                                                   |

# Figure 3-3. Pipeline Diagram of the Issue if There is a Stall in the E3 Slot of the Instruction I1

# **Workaround(s)** Treat MPYF32, ADDF32, SUBF32, and MACF32 in this scenario as 3p-cycle instructions. Three NOPs or non-conflicting instructions must be placed in the delay slot of the instruction.

The C28x Code Generation Tools v.6.2.0 and later will both generate the correct instruction sequence and detect the error in assembly code. In previous versions, v6.0.5 (for the 6.0.x branch) and v.6.1.2 (for the 6.1.x branch), the compiler will generate the correct instruction sequence but the assembler will not detect the error in assembly code.

### Example of Workaround:

| MPYF32 R6H, R5H, R0H<br>   MOV32 *XAR7++, R4H<br>F32TOUI16R R3H, R4H<br>ADDF32 R2H, R2H, R0H | ; 3p FPU instruction that writes to R6H<br>; delay slot |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------|

| MOV32 *SP, R2H                                                                               | ; delay slot                                            |

| NOP                                                                                          | ; alignment cycle                                       |

| MOV32 @XAR3, R6H                                                                             | ; FPU register read of R6H                              |

Figure 3-4 shows the pipeline diagram with the workaround in place.

### Advisory (continued) FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation

|    | Instruction                                   | F1            | F2 | D1 | D2 | R1 | R2 | E  | w  |               |                                                                                                                                                          |

|----|-----------------------------------------------|---------------|----|----|----|----|----|----|----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                               | FPU pipeline> |    |    | R1 | R2 | E1 | E2 | E3 | Comments      |                                                                                                                                                          |

| Il | MPYF32 R6H, R5H, R0H<br>   MOV32 *XAR7++, R4H | Il            |    |    |    |    |    |    |    |               |                                                                                                                                                          |

| I2 | F32TOUI16R R3H, R4H                           | I2            | I1 |    |    |    |    |    |    |               |                                                                                                                                                          |

| I3 | ADDF32 R3H, R2H, R0H<br>   MOV32 *SP, R2H     | I3            | I2 | Il |    |    |    |    |    |               |                                                                                                                                                          |

| I4 | NOP                                           | I4            | I3 | I2 | I1 |    |    |    |    |               |                                                                                                                                                          |

| 15 | MOV32 @XAR3, R6H                              | I5            | I4 | I3 | I2 | I1 |    |    |    |               |                                                                                                                                                          |

|    |                                               |               | I5 | I4 | I3 | I2 | I1 |    |    |               |                                                                                                                                                          |

|    |                                               |               |    | I5 | I4 | I3 | I2 | I1 |    |               |                                                                                                                                                          |

|    |                                               |               |    |    | 15 | I4 | I3 | I2 | I1 |               |                                                                                                                                                          |

|    |                                               |               |    |    |    | I5 | I4 | I3 | I2 | I1<br>(STALL) | Due to one extra NOP, I5 does not<br>reach R2 when I1 enters E3; thus,<br>forwarding is not needed.                                                      |

|    |                                               |               |    |    |    | I5 | I4 | I3 | I2 | Il            | There is no change due to the stall in the previous cycle.                                                                                               |

|    |                                               |               |    |    |    |    | 15 | I4 | 13 | I2            | Il moves out of E3 and I5 moves to<br>R2. R6H has the result of R5H*R0H<br>and is read by I5. There is no<br>need to forward the result in this<br>case. |

|    |                                               |               |    |    |    |    |    | I5 | I4 | I3            |                                                                                                                                                          |

Figure 3-4. Pipeline Diagram With Workaround in Place

| Advisory             | eQEP: eQEP Inputs in GPIO Asynchronous Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Revision(s) Affected | 0, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Details              | If any of the eQEP input pins are configured for GPIO asynchronous input mode via<br>the GPxQSELn registers, the eQEP module may not operate properly. For example,<br>QPOSCNT may not reset or latch properly, and pulses on the input pins may be missed.<br>This is because the eQEP peripheral assumes the presence of external synchronization<br>to SYSCLKOUT on inputs to the module.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                      | For proper operation of the eQEP module, input GPIO pins should be configured via<br>the GPxQSELn registers for synchronous input mode (with or without qualification). This<br>is the default state of the GPxQSEL registers at reset. All existing eQEP peripheral<br>examples supplied by TI also configure the GPIO inputs for synchronous input mode.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                      | The asynchronous mode should not be used for eQEP module input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |