## Errata IWR6843AOP Device Silicon Errata Silicon Revisions 1.0 and 2.0

# **TEXAS INSTRUMENTS**

## **Table of Contents**

| 1 Introduction                                         | 2  |

|--------------------------------------------------------|----|

| 2 Device Nomenclature                                  | 2  |

| 3 Device Markings                                      |    |

| 4 Usage Notes                                          |    |

| 4.1 MSS: SPI Speed in 3-Wire Mode Usage Note           |    |

| 5 Advisory to Silicon Variant / Revision Map           |    |

| 6 Known Design Exceptions to Functional Specifications | 7  |

| 7 Trademarks                                           | 58 |

| 8 Revision History                                     |    |

| ,                                                      |    |

## 1 Introduction

This document describes the known exceptions to the functional and performance specifications to TI CMOS Radar Devices (IWR6843AOP).

### 2 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of Radar / mmWave sensor devices. Each of the Radar devices has one of the two prefixes: XIx or IWRx (for example: **XI6843AOP**QAGALB). These prefixes represent evolutionary stages of product development from engineering prototypes (XI) through fully qualified production devices (IWR).

Device development evolutionary flow:

- XI Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **IWR** Production version of the silicon die that is fully qualified.

XI devices are shipped with the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Texas Instruments recommends that these devices not to be used in any production system as their expected end –use failure rate is still undefined.

## **3 Device Markings**

Figure 3-1 shows an example of the IWR6843AOP Radar Device's package symbolization.

Figure 3-1. Example of Device Part Markings

This identifying number contains the following information:

- Line 1: TI Logo

- Line 2: G1 = "Green" Package Build (must be underlined)

- Line 3:

- XIWR6843 = xIWR6843 Device Identifier (Pre-Production Industrial), IWR6843 ES2.0 Device Identifier (Production Industrial)

- BG ALP = Package Identifier

- YM = Year/Month Code

- Z = Assembly Site Code

- LLL = Assembly Lot Code

- 9 = Primary Site Code

## 4 Usage Notes

Usage notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These usage notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 4.1 MSS: SPI Speed in 3-Wire Mode Usage Note

The maximum SPI speed under 3-wire operation was only tested up to 33 MHz. This affects IWR6843AOP ES1.0.

## 5 Advisory to Silicon Variant / Revision Map

| Table 5-1. Advisor | to Silicon Variant | / Revision Map |

|--------------------|--------------------|----------------|

|--------------------|--------------------|----------------|

| ADVISORY              |                                                                                                                                                                                        | IWR6843AOP |       |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| NUMBER                | ADVISORY TITLE                                                                                                                                                                         | ES1.0      | ES2.0 |

|                       | Main Subsystem                                                                                                                                                                         |            |       |

| MSS#03                | Incorrect Handling of "Saturation" in FFT Hardware Accelerator's Statistics Block                                                                                                      | Х          |       |

| MSS#10                | Partial Write After a Full Data Width Write Fails to Mailbox Memory if ECC is Enabled                                                                                                  | Х          |       |

| MSS#11                | Clock Monitoring Logic Core Clock Comparator (CCCB) for CPU Clock Cannot be Used                                                                                                       | Х          |       |

| MSS#12                | MCAN Filter Event Interrupt not Connected to DMA                                                                                                                                       | Х          |       |

| MSS#13                | Incorrect Read from FFT Hardware Accelerator After Complex Multiplication Operation                                                                                                    | Х          |       |

| MSS#14                | Asynchronous Assertion of SoC Warm Reset may not Work Reliably When Device Operating on PLL Clock                                                                                      | Х          |       |

| MSS#16                | Delay Time, ETM Trace Clock to ETM Data Valid does not Meet Datasheet Specification                                                                                                    | Х          |       |

| MSS#17                | Invalid Pre-fetch from MSS CR4 Processor (due to Speculative Read Operation from Tightly Coupled Memory Instance) Leads to Generation of MSS_ESM Group 3 Channel 7: MSS_TCMA_FATAL_ERR | х          |       |

| MSS#18 <sup>(1)</sup> | Core Compare Module (CCM-R4F) may Cause nERROR Toggle After First Reset De-<br>assertion Subsequent to Power Application                                                               | Х          |       |

| MSS#19                | DMA Read from Unimplemented Address Space may Result in DMA Hang Scenario                                                                                                              | Х          |       |

| MSS#20                | Radar Frame Stuck due to Missing Synchronizer Logic in Hardware                                                                                                                        | Х          |       |

| MSS#21                | Issue with HWA Input Formatter 16 bit Real Signed Format                                                                                                                               | Х          |       |

| MSS#22                | CAN-FD: Message Transmitted With Wrong Arbitration and Control Fields                                                                                                                  | Х          |       |

| MSS#23                | HWA Read Registers Cannot be Read Reliably When the HWA is Executing a ParamSet Instruction                                                                                            | х          |       |

| MSS#24                | Limitation With Peak Grouping Feature in Hardware Accelerator                                                                                                                          | Х          |       |

| MSS#25                | Debugger May Display Unpredictable Data in the Memory Browser Window if a System Reset Occurs                                                                                          | х          | х     |

| MSS#26                | DMA Requests Lost During Suspend Mode                                                                                                                                                  | Х          | Х     |

| MSS#27                | MibSPI in Slave Mode in 3- or 4-Pin Communication Transmits Data Incorrectly for Slow<br>SPICLK Frequencies and for Clock Phase = 1                                                    | х          | х     |

| MSS#28                | A Data Length Error is Generated Repeatedly in Slave Mode When IO Loopback is Enabled                                                                                                  | Х          | Х     |

| MSS#29                | Spurious RX DMA REQ From a Peripheral Mode MibSPI                                                                                                                                      | Х          | Х     |

| MSS#30                | MibSPI RX RAM RXEMPTY Bit Does Not Get Cleared After Reading                                                                                                                           | Х          | х     |

| MSS#31                | CPU Abort Generated on a Write to Implemented CRC Space After a Write to Unimplemented CRC Space                                                                                       | Х          | х     |

| MSS#32                | DMMGLBCTRL BUSY Flag Not Set When DMM Starts Receiving A Packet                                                                                                                        | Х          | Х     |

| MSS#33                | MibSPI RAM ECC is Not Read Correctly in DIAG Mode                                                                                                                                      | Х          | Х     |

| MSS#34                | HS Device Does Not Reboot Successfully on Warm Reset Getting Triggered by Watchdog Expiry                                                                                              | х          | х     |

| MSS#35                | EDMA TPTC Generates an Incorrect Address on the Read Interface, Causing one or More Data Integrity Failures, Hangs, or Extra Reads                                                     | х          |       |

| MSS#36                | DMA Read From an Unimplemented Address Space is not Reported as a BUS Error                                                                                                            |            | Х     |

| MSS#37B               | DCC Module Frequency Comparison can Report Erroneous Results                                                                                                                           | Х          | х     |

| MSS#38A               | GPIO Glitch During Power-Up                                                                                                                                                            | Х          | х     |

| MSS#39                | The State of the MSS DMA is Left Pending and Uncleared on Any DMA MPU Fault                                                                                                            | Х          | х     |

| MSS#40                | Any EDMA Transfer That Spans ACCEL_MEM1 +ACCEL_MEM2 Memories of Hardware<br>Accelerator May Result In Data Corruption Without Any Notification Of Error From The SoC                   | Х          | Х     |

| MSS#41                | Issuing WARM_RESET can Cause Bootloader Failure Which Results in Failure to Load the Application From Serial Flash                                                                     | Х          | Х     |

| MSS#42A               | DSP L2 Memory Initialisation can Reoccur on Execution DSP Self Test (STC) OR DSP Power Cycling Execution by Application.                                                               | Х          | Х     |

| ADVISORY  | ADVISORY TITLE                                                                                                              | IWR6843AOP |       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|------------|-------|

| NUMBER    |                                                                                                                             | ES1.0      | ES2.0 |

| MSS#43A   | Read-Data from Internal Registers of PCR is Not Reliable. Shared PCS Region Protection is Also Not Supported                | Х          | Х     |

| MSS#44A   | SYNC IN Input Pulse Wider Than 4usec can Cause a FRC Lockstep Error                                                         | Х          | Х     |

| MSS#45    | Bootup Failure During the Serial Flash Busy State                                                                           | Х          | Х     |

| MSS#50    | Occasional EDMA self-test failures                                                                                          | Х          | Х     |

| MSS#51    | Spurious toggle on nERROR OUT signal during powerup due to undefined state in ESM block.                                    | Х          | Х     |

|           | Analog / Millimeter Wave                                                                                                    |            |       |

| ANA#11B   | TX, RX Gain Calibrations Sensitive to Large External Interference                                                           | Х          | Х     |

| ANA#12A   | Second Harmonic (HD2) is Present When Receiver is Tested Standalone Using CW Input                                          | Х          | Х     |

| ANA#13B   | Phase Mismatch Variation Across Temperature in TX3/TX1 and TX3/TX2 Combinations are higher than that of TX2/TX1 Combination | Х          | х     |

| ANA#14    | Doppler Spur Observed for Narrow Chirps Spanning 59.4 GHz and 62.1 GHz                                                      | Х          | Х     |

| ANA#16    | LVDS Coupling to Clock System                                                                                               | Х          | Х     |

| ANA#17A   | On-Board Supply Ringing Induced Spur                                                                                        | Х          | Х     |

| ANA#18B   | Spurs Caused due to Digital Activity Coupling to XTAL                                                                       | Х          | Х     |

| ANA#19    | Bandgap Decoupling Capacitor On-Board                                                                                       | Х          | Х     |

| ANA#20    | Occasional Failures Observed During Calibration of the Radar Subsystem                                                      | Х          | Х     |

| ANA#22A   | Overshoot and Undershoot During Inter-Chirp Idle Time                                                                       | Х          | Х     |

| ANA#27A   | Digital Temperature Sensor Readings Differ From Analog Temperature Sensors                                                  | Х          | Х     |

| ANA#30    | Inter-Channel Mismatch Variation Across Angle of Arrival                                                                    | Х          | Х     |

| ANA#31    | Increase in Rx Effective Isotropic Noise Figure when Tx Chains are Turned ON                                                | Х          | Х     |

|           | DSP Subsystem                                                                                                               |            |       |

| DSS#01    | Access to L3 Region Above Allocated Region may Result in Double Bit ECC Error if ECC is<br>Enabled                          | Х          |       |

| DSS#02    | L1P Parity Error not Connected to ESM                                                                                       | Х          |       |

| DSS#03    | Different Number of Chirps in ADC Buffer's Ping and Pong Memory is not Supported                                            | Х          |       |

| DSS#05    | Byte Writes not Supported to L3 If ECC is Enabled                                                                           | Х          |       |

| DSS#07    | Temperature Sensor Located Near DSP not Working                                                                             | Х          |       |

|           | PACKAGE                                                                                                                     |            |       |

| ACKAGE#01 | Mechanical Package Change from ES1.0 to ES2.0                                                                               | Х          |       |

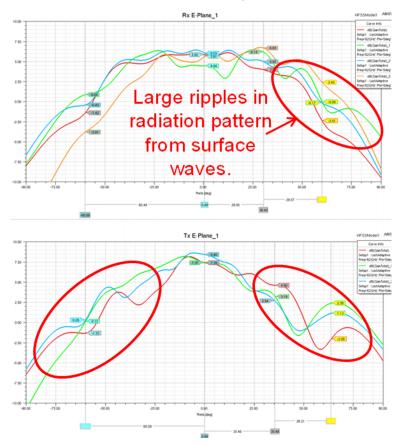

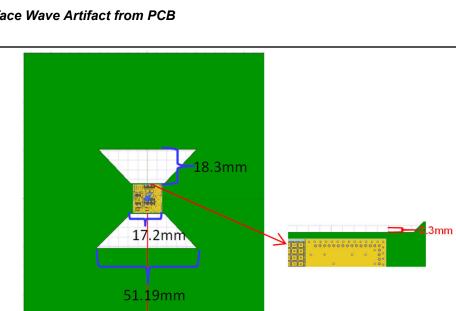

| ACKAGE#02 | Surface Wave Artefact from PCB                                                                                              | Х          | Х     |

#### Table 5-1. Advisory to Silicon Variant / Revision Map (continued)

(1) Applies to SIL Targeted devices.

| -                        |                                                                                                                                                                                                                                                                                         |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSS#03                   | Incorrect Handling of "Saturation" in FFT Hardware Accelerator's Statistics Block                                                                                                                                                                                                       |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                        |

| Description:             | Statistics block always assumes that input is signed when checking for saturation, but the input can be unsigned in some cases.                                                                                                                                                         |

| Workaround(s):           | None.                                                                                                                                                                                                                                                                                   |

| MSS#10                   | Partial Write After a Full Data Width Write Fails to Mailbox Memory if ECC is<br>Enabled                                                                                                                                                                                                |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                        |

| Description:             | Partial data write after a full data width write would result is wrong data being written into the Mailbox memory if ECC is enabled.                                                                                                                                                    |

| Workaround(s):           | None. Silicon update will be provided by TI.                                                                                                                                                                                                                                            |

| MSS#11                   | Clock Monitoring Logic Core Clock Comparator (CCCB) for CPU Clock Cannot be<br>Used                                                                                                                                                                                                     |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                        |

| Description:             | Clock used for the Watchdog Timer (WDT) is same as the CPU clock. CCCB can be dedicated to monitor CPU clock against a reference clock like XTAL/RCOSC to generate a WDT reset if CPU clock fails. However, CCCB does not consistently generate an error if the CPU clock stops ticking |

| Workaround(s):           | None. Silicon update will be provided by TI.                                                                                                                                                                                                                                            |

## **6 Known Design Exceptions to Functional Specifications**

| MSS#12                   | MCAN Filter Event Interrupt not Connected to DMA                                                                                                                                                  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                  |

| Description:             | MCAN filter event interrupt is only connected to MSS VIM and not connected to MSS DMA. If a DMA transfer operation is expected to happen on this interrupt , MSS CR4 will have to trigger the DMA |

| Workaround(s):           | None. Silicon update will be provided by TI.                                                                                                                                                      |

| MSS#13                   | Incorrect Read from FFT Hardware Accelerator After Complex Multiplication                                                                                                                         |

|                          | Operation                                                                                                                                                                                         |

| Revision(s)<br>Affected: | Operation<br>IWR6843AOP ES1.0                                                                                                                                                                     |

| • •                      | <u>.</u>                                                                                                                                                                                          |

| MSS#14                   | Asynchronous Assertion of SoC Warm Reset may no<br>Operating on PLL Clock                                                      | ot Work Re      | eliably Whe        | n Device              |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|-----------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                               |                 |                    |                       |

| Description:             | Asynchronous assertion of SoC warm reset through WA watchdog reset, or Debug reset may not reliably work ar hang scenario.     |                 |                    |                       |

| Workaround(s):           | MSS VCLK must be switched from PLL clock to REFCLI software sequence before a warm reset is issued.                            | K by followi    | ng the preso       | cribed                |

| MSS#16                   | <i>Delay Time, ETM Trace Clock to ETM Data Valid does</i><br>Specification                                                     | s not Meet      | Datasheet          |                       |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                               |                 |                    |                       |

| Description:             | Delay time, ETM trace clock to ETM data valid does not below:                                                                  | meet datas      | heet specifi       | cation                |

|                          | PARAMETER                                                                                                                      | MIN             | MAX                |                       |

|                          |                                                                                                                                |                 |                    | UNIT                  |

|                          | Delay time, ETM trace clock high to ETM data valid                                                                             | 1               | 7                  | ns                    |

|                          | Delay time, ETM trace clock high to ETM data valid<br>Delay time, ETM trace clock low to ETM data valid                        | 1<br>1          | 7<br>7             |                       |

|                          |                                                                                                                                | 1               | 7                  | ns<br>ns              |

|                          | Delay time, ETM trace clock low to ETM data valid<br>In IWR6843AOP ES1.0, Delay time, ETM trace clock to                       | 1               | 7                  | ns<br>ns              |

|                          | Delay time, ETM trace clock low to ETM data valid<br>In IWR6843AOP ES1.0, Delay time, ETM trace clock to<br>is as given below: | 1<br>ETM data t | 7<br>iming that is | ns<br>ns<br>being met |

Workaround(s): None. Silicon update will be provided by TI.

| MSS#17                   | Invalid Pre-fetch from MSS CR4 Processor (due to Speculative Read Operation<br>from Tightly Coupled Memory Instance) Leads to Generation of MSS_ESM Group 3<br>Channel 7: MSS_TCMA_FATAL_ERR                                                                                                                                                                                                              |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:             | The CR4 processor may perform an invalid pre-fetch access due to speculative TCM read leading to an invalid address access. This can result in a TCERROR and also a 2-bit ECC fatal error. The TCERROR is ignored by the processor since these correspond to instructions that are pre-fetched but never executed. However, the invalid MSS_TCMA_FATAL_ERR is generated on the ESM group3 channel-7.      |

|                          | Implication: In case of a genuine TCMA ECC fatal error, nERROR will not be generated<br>directly through ESM.                                                                                                                                                                                                                                                                                             |

| Workaround(s):           | Mask Group 3 channel 7: MSS_TCMA_FATAL_ERR to ESM can be masked by writing<br>into MSS_RCM:ESMGATE0 register. CR4F abort handler should handle the nERROR<br>generation                                                                                                                                                                                                                                   |

|                          | OR                                                                                                                                                                                                                                                                                                                                                                                                        |

|                          | Disable branch prediction for MSS-CR4F                                                                                                                                                                                                                                                                                                                                                                    |

| MSS#18                   | Core Compare Module (CCM-R4F) may Cause nERROR Toggle After First Reset<br>De-assertion Subsequent to Power Application                                                                                                                                                                                                                                                                                   |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:             | The CCM-R4F module compares the outputs of the two Cortex-R4F CPU cores and generates an error on any mis-compare. This ensures the lock-step operation of the two Cortex-R4F CPUs. The nERROR signal should only be set by the CCM-R4 module by a valid core mismatch. At power-on, some uninitialized circuits may cause the CCMR4-F to falsely detect a mis-compare.                                   |

| Workaround(s):           | The anomalous nERROR toggle would need to be ignored by the external monitoring circuit (if deployed).                                                                                                                                                                                                                                                                                                    |

| MSS#19                   | DMA Read from Unimplemented Address Space may Result in DMA Hang Scenario                                                                                                                                                                                                                                                                                                                                 |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:             | The MSS DMA generates a BER (Bus Error) interrupt when the DMA detects a bus<br>error due to a read from unimplemented address space. This interrupt is available on<br>VIM Interrupt Channel-70 for DMA1 and VIM Interrupt Channel-51 for DMA2 .This read<br>from unimplemented address space results in a hang condition in the DMA infrastructure<br>bridge that connects it to the main interconnect. |

|                          | Implication: A DMA read from an unimplemented address can result in a DMA hang condition. In the resulting state the DMA will not respond to any further DMA requests.                                                                                                                                                                                                                                    |

| Workaround(s):           | The MSS CR4F processor will have to invoke a warm reset or generate an nERROR, if it receives a DMA BER error.                                                                                                                                                                                                                                                                                            |

| MSS#20                   | Radar Frame Stuck due to Missing Synchronizer Logic in Hardware                                                                                                                                                                                                                                                                                                                                           |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                                                                                                                                                                                                          |

| MSS#20 (continued)       | Radar Frame Stuck due to Missing Synchronizer Logic in Hardware                                                                                                                                                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description:             | Radar Sub System Internal Frame Clock is triggered by rlSensorStart API which starts the Radar Frame. Occasionally the rlSensorStart API does not trigger the clock due to missing synchronizer logic in hardware. |

|                          | Implication: A DMA read from an unimplemented address can result in a DMA hang condition. In the resulting state the DMA will not respond to any further DMA requests.                                             |

| Workaround(s):           | The issue is frequent if FRC clock source is changed. Ensure that FRC Clock source is not changed.                                                                                                                 |

| MSS#21                   | Issue with HWA Input Formatter 16 bit Real Signed Format                                                                                                                                                           |

| Revision(s)<br>Affected: | IWR6843AOP ES1.0                                                                                                                                                                                                   |

| Description:             | Wrong sign extension is implemented for 16 bit signed format in real only mode operation.<br>Hence, signed 16-bit real format cannot be supported for input formatter.                                             |

| Workaround(s):           | None. Silicon update will be provided by TI.                                                                                                                                                                       |

| MSS#22                   | CAN-FD: Message Transmitted With Wrong Arbitration and Control Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Description:             | <ul> <li>Under the following conditions a message with wrong ID, format, and DLC is transmitted:</li> <li>M_CAN is in state "Receiver" (PSR.ACT = "10"), no pending transmission</li> <li>A new transmission is requested before the 3rd bit of Intermission is reached</li> <li>The CAN bus is sampled dominant at the third bit of Intermission which is treated as SoF (see ISO11898-1:2015 Section 10.4.2.2)</li> </ul>                                                                                            |

|                          | Under the conditions listed above it may happen, that:                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          | <ul> <li>The shift register is not loaded with ID, format, and DLC of the requested message</li> <li>The M_CAN will start arbitration with wrong ID, format, and DLC on the next bit</li> <li>In case the ID wins arbitration, a CAN message with valid CRC is transmitted</li> <li>In case this message is acknowledged, the ID stored in the Tx Event FIFO is the ID of the requested Tx message and not the ID of the message transmitted on the CAN bus, no error is detected by the transmitting M_CAN</li> </ul> |

|                          | The erratum is limited to the case when M_CAN is in state "Receiver" (PSR.ACT = "10") with no pending transmission and a new transmission is requested before the 3rd bit of Intermission is reached and this 3rd bit of intermission is seen dominant.                                                                                                                                                                                                                                                                |

|                          | When a transmission is requested by the CPU, the Tx Message Handler performs an internal arbitration and loads the pending transmit message with the highest priority into its output buffer and then sets the transmission request for the CAN Protocol Controller. The problem occurs only when the transmission request for the CAN Protocol Controller is activated between the sample points of the 2nd and 3rd bit of Intermission and if that 3rd bit of intermission is seen dominant.                         |

|                          | This dominant level at the 3rd bit of Intermission may result from an external disturbance or may be transmitted by another node with a significantly faster clock.                                                                                                                                                                                                                                                                                                                                                    |

|                          | In the described case it may happen that the shift register is not loaded with arbitration<br>and control field of the message to be transmitted. The frame is transmitted with wrong<br>ID, format, and DLC but with the data field of the requested message. The message is<br>transmitted in correct CAN (FD) frame format with a valid CRC.                                                                                                                                                                        |

|                          | If the message loses arbitration or is disturbed by an error, it is retransmitted with correct arbitration and control fields.                                                                                                                                                                                                                                                                                                                                                                                         |

| Workaround(s):           | Request a new transmission only if another transmission is already pending or when the M_CAN is not in state "Receiver" (when PSR.ACT $\neq$ "10").                                                                                                                                                                                                                                                                                                                                                                    |

|                          | Another option would be to add a checksum to the data field covering arbitration and control fields of the message to be transmitted.                                                                                                                                                                                                                                                                                                                                                                                  |

| MSS#23                   | HWA Read Registers Cannot be Read Reliably When the HWA is Executing a ParamSet Instruction                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Description:             | Any read from the HWA configuration or status registers can be corrupted, if the read access is performed when the HWA is active. Reads from the HWA registers can be performed correctly, only after the execution of the entire ParamSet (i.e., after the ACC_DONE_INTR interrupt) or when the HWA is in IDLE mode waiting for the trigger to the start the execution of the next ParamSet instruction.                                                                                                   |

| Workaround(s):           | <ul> <li>Perform the following:</li> <li>Read-back of signature registers: Software needs to maintain a soft copy of the one-hot encoded signature registers and use that copy location for the EDMA programming.</li> <li>Read-back of static registers on the HWA ParamSet interrupt. There is no reliable way to read the HWA static registers, if the HWA is active.</li> <li>Read-back of Debug/status registers: The User can only read these registers when the HWA is <i>not</i> active.</li> </ul> |

| MSS#24                   | Limitation With Peak Grouping Feature in Hardware Accelerator                                                                                                                                                                                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 only                                                                                                                                                                                                                                                              |

| Description:             | Peak is declared only if the cell under test is greater than its most immediate neighboring cells to its left and right. In the case where CFAR qualified peaks in the two adjacent cells happen to be equal in magnitude, enabling peak grouping can lead to the peak being lost. |

| Workaround(s):           | Do not enable the peak grouping feature in the hardware accelerator.                                                                                                                                                                                                               |

| MSS#25                   | Debugger May Display Unpredictable Data in the Memory Browser Window if a System Reset Occurs                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOPES1.0, ES2.0                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Description:             | If a system reset (nRST goes low) occurs while the debugger is performing an access on<br>the system resource using system view, a slave error should be replied to the debugger.<br>If the access was a read, instead the response might indicate that the access completed<br>successfully and return unpredictable data.                                                                                                                   |

|                          | This issue occurs under this condition: when a system reset is asserted (nRST low) on<br>a specific cycle, while the debugger is completing an access on the system, using the<br>system view. An example would be, when a debugger, like the CCS-IDE memory browser<br>window, is refreshing content using the system view. This is not an issue for a CPU only<br>reset and, this is not an issue during a power-on-reset (nPORRST) either. |

| Workaround(s):           | Avoid performing debug reads and writes while the device might be in reset.                                                                                                                                                                                                                                                                                                                                                                   |

| MSS#26                   | DMA Requests Lost During Suspend Mode                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 and IWR6843AOP ES2.0                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Description:             | While the device is halted in suspend mode by the debugger, the DMA is expected to complete the remaining transfers of a block, if the DEBUG MODE bit field of the GCTRL register is configured to '01'. Instead, the DMA does not complete the remaining transfers of a block but, rather stops after two more frames of data are transferred. Subsequent DMA requests from a peripheral to trigger the remaining frames of a block can be lost.                 |

|                          | <ul> <li>This issue occurs only in the following conditions:</li> <li>The device is suspended by a debugger</li> <li>A peripheral continues to generate requests while the device is suspended</li> <li>The DMA is setup to continue the current block transfer during suspend mode with the DEBUG MODE bit field of the GCTRL register set to '01'</li> <li>The request transfer type TTYPE bit in the CHCTRL registers is set to frame trigger ('0')</li> </ul> |

| Workaround(s):           | Workaround #1:                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | Use TTYPE = block transfer ('1'), when the DEBUG MODE bit field is '01' ( <i>finish current block transfer</i> )                                                                                                                                                                                                                                                                                                                                                  |

|                          | or                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | Workaround #2:                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Use the DMA DEBUG MODE = '00' (ignore suspend), when using TTYPE = frame transfer ('0') to complete the block transfer, even after suspend/halt is asserted.

| MSS#27                   | MibSPI in Peripheral Mode in 3- or 4-Pin Communication Transmits Data Incorrectly<br>for Slow SPICLK Frequencies and for Clock Phase = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s)<br>Affected: | IWR6843AOPES1.0, ES2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Description:             | <ul> <li>The MibSPI module, when configured in multibuffered peripheral mode with 3-functional pins (CLK, SIMO, SOMI) or 4-functional pins (CLK, SIMO, SOMI, nENA), could transmit incorrect data when all the following conditions are met:</li> <li>MibSPI module is configured in multibuffered mode,</li> <li>Module is configured to be a slave in the SPI communication,</li> <li>SPI communication is configured to be in 3-pin mode or 4-pin mode with nENA,</li> <li>Clock phase for SPICLK is 1, and</li> <li>SPICLK frequency is MSS_VCLK frequency / 12 or slower</li> </ul> |  |

| Workaround(s):           | The issue can be avoided by setting the CSHOLD bit in the control field of the TX RAM (Multi-Buffer RAM Transmit Data Register). The nCS is not used as a functional signal in this communication; hence, setting the CSHOLD bit does not cause any other effect on the SPI communication.                                                                                                                                                                                                                                                                                               |  |

| MSS#28                   | A Data Length Error is Generated Repeatedly in Peripheral Mode When IO<br>Loopback is Enabled                                                                                                                                                                                                                                                                                                             |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s)<br>Affected: | IWR6843AOPES1.0, ES2.0                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Description:             | When a DLEN error is created in Peripheral mode of the SPI using nSCS pins in IO Loopback Test mode, the SPI module re-transmits the data with the DLEN error instead of aborting the ongoing transfer and stopping. This is only an issue for an IOLPBK mode Peripheral in Analog Loopback configuration, when the intentional error generation feature is triggered using CTRLDLENERR (IOLPBKTSTCR.16). |  |

| Workaround(s):           | After the DLEN_ERR interrupt is detected in IOLPBK mode, disable the transfers by clearing the SPIEN (bit 24) in the SPIGCR1 register and then, re-enable the transfers by resetting the SPIEN bit.                                                                                                                                                                                                       |  |

| MSS#29                   | Spurious RX DMA REQ From a Peripheral Mode MibSPI                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s)<br>Affected: | IWR6843AOPES1.0, ES2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Description:             | <ul> <li>A spurious DMA request could be generated even when the SPI Peripheral is not transferring data in the following condition sequence:</li> <li>The MIBSPI is configured in standard (non-multibuffered) SPI mode, as a Peripheral</li> <li>The DMAREQEN bit (SPIINT0.16) is set to enable DMA requests</li> <li>The Chip Select (nSCS) pin is in an active state, but no transfers are active</li> <li>The SPI is disabled by clearing the SPIEN (SPIGCR1.24) bit from '1' to '0'</li> </ul> |  |

|                          | The above sequence triggers a false request pulse on the Receive DMA Request as soon as the SPIEN bit is cleared from '1' to '0'.                                                                                                                                                                                                                                                                                                                                                                    |  |

| Workaround(s):           | Whenever disabling the SPI, by clearing the SPIEN bit (SPIGCR1.24), first clear the DMAREQEN bit (SPIINT0.16) to '0', and then, clear the SPIEN bit.                                                                                                                                                                                                                                                                                                                                                 |  |

| MSS#30                   | MibSPI RX RAM RXEMPTY bit Does Not Get Cleared After Reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s)<br>Affected: | IWR6843AOPES1.0, ES2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Description:             | <ul> <li>The RXEMPTY flag may not be auto-cleared after a CPU or DMA read when the following conditions are met:</li> <li>The TXFULL flag of the latest buffer that the sequencer read out of transmit RAM for the currently active transfer group is 0,</li> <li>A higher-priority transfer group interrupts the current transfer group and the sequencer starts to read the first buffer of the new transfer group from the transmit RAM, and</li> <li>Simultaneously, the Host (CPU/DMA) is reading out a receive RAM location that contains valid received data from the previous transfers.</li> </ul> |  |  |

| Workaround(s):           | If at all possible, avoid transfer groups interrupting one another.<br>If dummy buffers are used in lower-priority transfer groups, select the appropriate                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                          | "BUFMODE" for them (like, SKIP/DISABLED) unless, there is a specific need to use the<br>"SUSPEND" mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| MSS#31                   | CPU Abort Generated on a Write to Implemented CRC Space After a Write to<br>Unimplemented CRC Space                                                                                                                                                                                                                                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 and IWR6843AOP ES2.0                                                                                                                                                                                                                                                                                              |

| Description:             | An abort could be generated on a write to a legal address in the address offset region (0x0000–0x01FF) of the CRC register space when a normal mode write to an unimplemented address region (0x0200–0xFFFF) of the CRC register space is followed by a write to a legal address region (0x0000–0x01FF) of the CRC register space. |

| Workaround(s):           | None.                                                                                                                                                                                                                                                                                                                              |

| MSS#32                   | DMMGLBCTRL BUSY Flag Not Set When DMM Starts Receiving A Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 and IWR6843AOP ES2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Description:             | <ul> <li>The BUSY flag in the DMMGLBCTRL register should be set when the DMM starts receiving a packet or has data in its internal buffers. However, the BUSY flag (DMMGLBCTRL.24) may not get set when the DMM starts receiving a packet under the following condition:</li> <li>The BUSY bit is set only after the packet has been received, de-serialized, and written to the internal buffers. It stays active while data is still in the DMM internal buffers. If the internal buffers are empty (meaning that no data needs to be written to the destination memory) then, the BUSY bit will be cleared.</li> </ul> |  |

| Workaround(s):           | Wait for a number of DMMCLK cycles (for example, 95 DMMCLK cycles) beyond the longest reception and deserialization time needed for a given packet size and DMM port configuration, before checking the status of the BUSY flag, and after the DMM ON/OFF bit field (DMMGLBCTRL.[3:0]) has been programmed to OFF.                                                                                                                                                                                                                                                                                                        |  |

| MSS#33                   | MibSPI RAM ECC is Not Read Correctly in DIAG Mode                                                                                                                                                                                                               |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s)<br>Affected: | IWR6843AOPES1.0, ES2.0                                                                                                                                                                                                                                          |  |

| Description:             | A Read operation to the ECC address space of the MibSPI RAM in DIAG mode, does not return the correct ECC value for the first 128 buffers, if the Extended Buffer support is implemented but, the Extended Mode is disabled for the particular MibSPI instance. |  |

| Workaround(s):           | None.                                                                                                                                                                                                                                                           |  |

| MSS#34                   | HS Device Does Not Reboot Successfully on Warm Reset Getting Triggered or With<br>Internal Software Reset                                                                                                                                 |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision(s)<br>Affected: | IWR6843AOP ES1.0 and IWR6843AOP ES2.0                                                                                                                                                                                                     |  |

| Description:             | A warm reset triggered by a watchdog expiry (MSS Wdog) , a software register write (SOFTSYSRST), or an external warm reset pin does not ensure a successful reboot of the device in a secure device (HS device).                          |  |

| Workaround(s):           | A warm reset should not be triggered externally or internally by a watchdog expiry, a software write, or other trigger mechanisms.                                                                                                        |  |

|                          | To initiate a reset cycle, external circuitry should be used on the sensor design. The external circuitry uses the watchdog, nERROR OUT monitoring, or other kinds of GPIO signaling to trigger a reset using the nRST pin of the device. |  |

Affected:

**Description:**

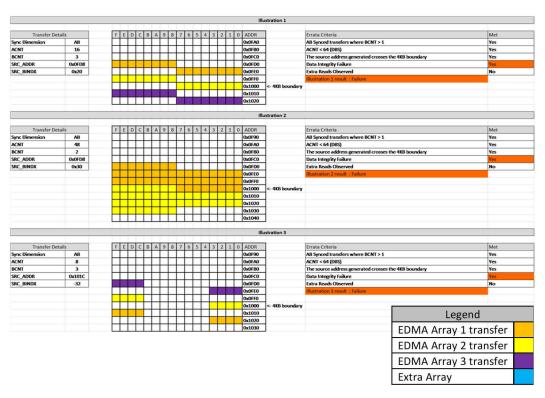

#### MSS#35 EDMA TPTC Generates an Incorrect Address on the Read Interface, Causing one or More Data Integrity Failures, Hangs, or Extra Reads

Revision(s) IWR6843AOP ES1.0 only

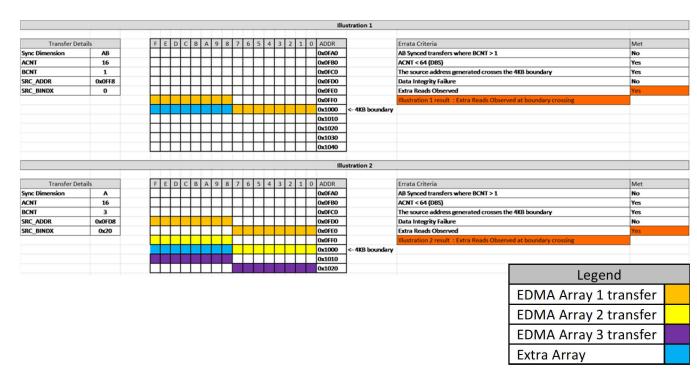

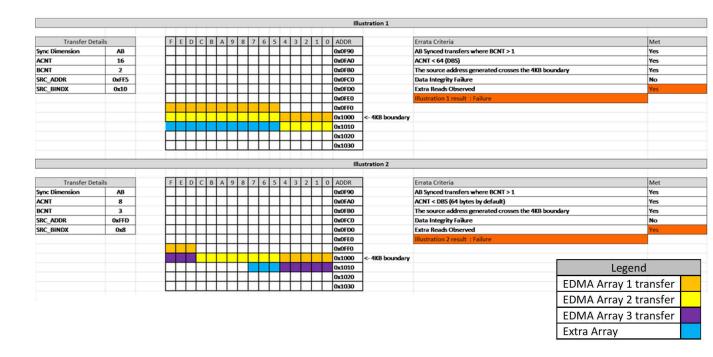

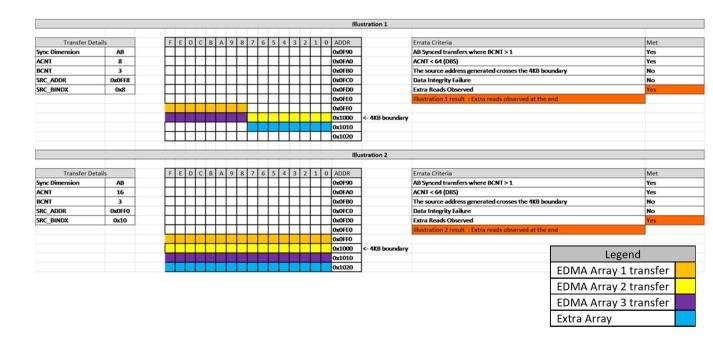

Certain scenarios could lead to an incorrect read, hang, or data integrity issues in the EDMA TPTC block. Table 6-1 shows the various scenarios and the resulting effects of each scenario.

A scenario happens, if *ALL* conditions listed for that scenario are satisfied (true); that is, "AND" of all conditions.

A "hang" outcome means that one or more attempts of the hang causing scenarios can progressively lead to not receiving a "transfer completion" indication from the TPTC. The last transfer attempt which does not receive the completion indication can be any transfer – any scenario transfer within this advisory or even outside of this advisory.

| SCENARIO<br>ID | CONDITIONS                                                                                                                                                                                                                                                                                              | DATA<br>INTEGRITY<br>FAILURES | HANGS    | EXTRA<br>READS             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------|----------------------------|

| 1              | AB-sync<br>BCNT > 1<br>ACNT not in [2,4,8,16,32]<br>(ACNT < 64) OR ((ACNT = 64) AND (SRCBIDX != ACNT))<br>Source Addressing crossing 4-KB boundary for any of the BCNT<br>number of ACNT transfers.                                                                                                     | Yes<br>(see Figure<br>6-4)    | Possible | Possible                   |

| 2              | AB-sync with BCNT=1 or A-sync<br>ACNT not in [224, 32]<br>ACNT <= 64<br>Source Addressing crossing 4-KB boundary for any of the BCNT<br>number of ACNT transfers.                                                                                                                                       | No                            | Possible | Yes                        |

| 3              | AB-sync with BCNT=1 or A-sync<br>ACNT in [224, 32]<br>Source Addressing crossing 4-KB boundary for any of the BCNT<br>number of ACNT transfers.                                                                                                                                                         | No                            | No       | Yes<br>(see Figure<br>6-1) |