SBAS042A - MARCH 1997 - REVISED SEPTEMBER 2003

ADS7812

# Low-Power, Serial 12-Bit Sampling ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

- 20µs max CONVERSION TIME

- SINGLE +5V SUPPLY OPERATION

- PIN-COMPATIBLE WITH 16-BIT ADS7813

- EASY-TO-USE SERIAL INTERFACE

- 0.3" DIP-16 AND SO-16

- ±0.5LSB max INL AND DNL

- 72dB min SINAD

- USES INTERNAL OR EXTERNAL REFERENCE

- MULTIPLE INPUT RANGES

- 35mW max POWER DISSIPATION

- NO MISSING CODES

- 50µW POWER DOWN MODE

# APPLICATIONS

- DATA ACQUISITION SYSTEMS

- INDUSTRIAL CONTROL

- TEST EQUIPMENT

- DIGITAL SIGNAL PROCESSING

## DESCRIPTION

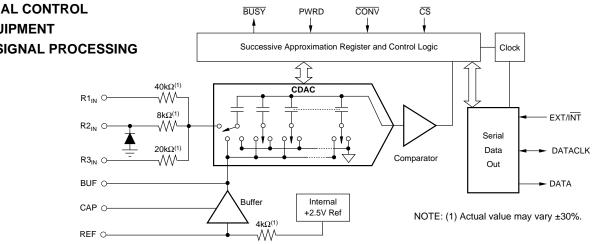

The ADS7812 is a low-power, single +5V supply, 12-bit sampling analog-to-digital converter. It contains a complete 12-bit capacitor-based SAR A/D with a sample/hold, clock, reference, and serial data interface.

The converter can be configured for a variety of input ranges including  $\pm 10V$ ,  $\pm 5V$ , 0V to 10V, and 0.5V to 4.5V. A high impedance 0.3V to 2.8V input range is also available (input impedance >  $10M\Omega$ ). For most input ranges, the input voltage can swing to +16.5V or -16.5V without damage to the converter.

A flexible SPI compatible serial interface allows data to be synchronized to an internal or external clock. The ADS7812 is specified at a 40kHz sampling rate over the -40°C to +85°C temperature range. It is available in a 0.3" DIP-16 or an SO-16 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| R2 <sub>IN</sub><br>R3 <sub>IN</sub><br>REF<br>CAP            | ±16.5V<br>GND - 0.3V to +16.5V<br>±16.5V<br>GND - 0.3V to V <sub>S</sub> + 0.3V<br>Indefinite Short to GND<br>Momentary Short to V <sub>S</sub><br>7V |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Inputs<br>Maximum Junction T<br>Internal Power Dissip | GND - 0.3V to V <sub>S</sub> + 0.3V<br>emperature                                                                                                     |

NOTE: (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability.

### PACKAGE/ORDERING INFORMATION

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT        | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>ERROR (LSB) | SPECIFIED<br>NO MISSING<br>CODE LEVEL<br>(LSB) | MINIMUM<br>SIGNAL-TO-<br>(NOISE +<br>DISTORTION)<br>RATIO (DB) | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER        | TRANSPORT<br>MEDIA, QUANTITY     |

|----------------|-------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|--------------|--------------------------------------|-----------------------------------|--------------------|---------------------------|----------------------------------|

| ADS7812P       | ±1                                              | 12                                             | 70                                                             | Dip-16       | N                                    | -40°C to +85°C                    | ADS7812P           | ADS7812P                  | Tubes, 25                        |

| ADS7812PB      | ±0.5                                            | 12                                             | 72                                                             | "            | "                                    | "                                 | ADS7812PB          | ADS7812PB                 | Tubes, 25                        |

| ADS7812U<br>"  | ±1<br>"                                         | 12<br>"                                        | 70<br>"                                                        | SO-16<br>"   | DW<br>"                              | –40°C to +85°C<br>"               | ADS7812U<br>"      | ADS7812U<br>ADS7812U/1K   | Tubes, 48<br>Tape and Reel, 1000 |

| ADS7812UB<br>" | ±0.5<br>"                                       | 12<br>"                                        | 72<br>"                                                        | SO-16<br>"   | DW<br>"                              | -40°C to +85°C<br>"               | ADS7812UB<br>"     | ADS7812UB<br>ADS7812UB/1K | Tubes, 48<br>Tape and Reel, 1000 |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

# **SPECIFICATIONS**

At  $T_A = -40^{\circ}C$  to +85°C,  $f_S = 40$ kHz,  $V_S = +5V \pm 5\%$ , using internal reference, unless otherwise specified.

|                                                                   |                                         |     | ADS7812P,   | U     | A   | DS7812PB, | UB    |                    |

|-------------------------------------------------------------------|-----------------------------------------|-----|-------------|-------|-----|-----------|-------|--------------------|

| PARAMETER                                                         | CONDITIONS                              | MIN | ТҮР         | МАХ   | MIN | ТҮР       | МАХ   | UNITS              |

| RESOLUTION                                                        |                                         |     |             | 12    |     |           | *     | Bits               |

| ANALOG INPUT                                                      |                                         |     |             |       |     |           |       |                    |

| Voltage Range                                                     |                                         |     | See Table I |       |     | *         |       |                    |

| Impedance                                                         |                                         |     | See Table I |       |     | *         |       |                    |

| Capacitance                                                       |                                         |     | 35          |       |     | *         |       | pF                 |

| THROUGHPUT SPEED                                                  |                                         |     |             |       |     |           |       |                    |

| Conversion Time                                                   |                                         |     |             | 20    |     |           | *     | μs                 |

| Complete Cycle                                                    | Acquire and Convert                     |     |             | 25    |     |           | *     | μs                 |

| Throughput Rate                                                   |                                         | 40  |             |       | *   |           |       | kHz                |

| DC ACCURACY                                                       |                                         |     |             |       |     |           |       |                    |

| Integral Linearity Error                                          |                                         |     | 0.1         | ±1    |     | *         | ±0.5  | LSB <sup>(1)</sup> |

| Differential Linearity Error                                      |                                         |     | 0.1         | ±1    |     | *         | ±0.5  | LSB                |

| No Missing Codes                                                  |                                         |     | Specified   |       |     | *         |       |                    |

| Transition Noise <sup>(2)</sup>                                   |                                         |     | 0.05        |       |     | *         |       | LSB                |

| Full Scale Error <sup>(3)</sup>                                   |                                         |     |             | ±0.5  |     |           | ±0.25 | %                  |

| Full Scale Error Drift                                            |                                         |     | ±14         |       |     | *         |       | ppm/°C             |

| Full Scale Error <sup>(3)</sup>                                   | Ext. 2.5000V Ref                        |     |             | ±0.5  |     |           | ±0.25 | %                  |

| Full Scale Error Drift                                            | Ext. 2.5000V Ref                        |     | ±5          |       |     | *         |       | ppm/°C             |

| Bipolar Zero Error                                                | Bipolar Ranges                          |     |             | ±10   |     |           | *     | mV                 |

| Bipolar Zero Error Drift                                          | Bipolar Ranges                          |     | ±3          |       |     | *         |       | ppm/°C             |

| Unipolar Zero Error                                               | Unipolar Ranges                         |     |             | ±6    |     |           | *     | mV                 |

| Unipolar Zero Error Drift                                         | Unipolar Ranges                         |     | ±3          |       |     | *         |       | ppm/°C             |

| Recovery Time to Rated Accuracy<br>from Power Down <sup>(4)</sup> | 1.0µF Capacitor to CAP                  |     | 300         |       |     | *         |       | μs                 |

| Power Supply Sensitivity                                          | +4.75V < (V <sub>S</sub> = +5V) < +5.25 |     |             | ±0.75 |     |           | *     | LSB                |

| AC ACCURACY                                                       |                                         |     |             |       |     |           |       |                    |

| Spurious-Free Dynamic Range                                       | f <sub>IN</sub> = 1kHz                  | 80  | 98          |       | *   | *         |       | dB <sup>(5)</sup>  |

| Total Harmonic Distortion                                         | $f_{IN} = 1 \text{ kHz}$                |     | -96         | -80   |     | *         | *     | dB                 |

| Signal-to-(Noise+Distortion)                                      | $f_{IN} = 1 \text{kHz}$                 | 70  | 74          |       | 72  | *         |       | dB                 |

| Signal-to-Noise                                                   | $f_{IN} = 1 \text{kHz}$                 | 70  | 74          |       | 72  | *         |       | dB                 |

| Useable Bandwidth <sup>(6)</sup>                                  | 111                                     |     | 130         |       |     | *         |       | kHz                |

| Full Power –3dB Bandwidth                                         |                                         |     | 600         |       |     | *         |       | kHz                |

# **SPECIFICATIONS** (Cont.)

At  $T_A = -40^{\circ}$ C to +85°C,  $f_S = 40$ kHz,  $V_S = +5V \pm 5\%$ , using internal reference, unless otherwise specified.

|                                     |                           |       | ADS7812P, | U                    | A         | DS7812PB, | UB  |        |

|-------------------------------------|---------------------------|-------|-----------|----------------------|-----------|-----------|-----|--------|

| PARAMETER                           | CONDITIONS                | MIN   | ТҮР       | MAX                  | MIN       | ТҮР       | MAX | UNITS  |

| SAMPLING DYNAMICS                   |                           |       |           |                      |           |           |     |        |

| Aperture Delay                      |                           |       | 40        |                      |           | *         |     | ns     |

| Aperture Jitter                     |                           |       | 20        |                      |           | *         |     | ps     |

| Transient Response                  | FS Step                   |       | 5         |                      |           | *         |     | μs     |

| Overvoltage Recovery <sup>(7)</sup> |                           |       | 750       |                      |           | *         |     | ns     |

| REFERENCE                           |                           |       |           |                      |           |           |     |        |

| Internal Reference Voltage          |                           | 2.48  | 2.5       | 2.52                 | *         | *         | *   | V      |

| Internal Reference Source Current   |                           |       | 100       |                      |           | *         |     | μΑ     |

| Internal Reference Drift            |                           |       | 8         |                      |           | *         |     | ppm/°C |

| External Reference Voltage Range    |                           | 2.3   | 2.5       | 2.7                  | *         | *         | *   | V      |

| External Reference Current Drain    | $V_{REF} = +2.5V$         |       |           | 100                  |           |           | *   | μΑ     |

| DIGITAL INPUTS                      |                           |       |           |                      |           |           |     |        |

| Logic Levels                        |                           |       |           |                      |           |           |     |        |

| V <sub>IL</sub>                     |                           | -0.3  |           | +0.8                 | *         |           | *   | V      |

| V <sub>IH</sub> <sup>(8)</sup>      |                           | +2.0  |           | V <sub>S</sub> +0.3V | *         |           | *   | V      |

| l <sub>iL</sub>                     |                           |       |           | ±10                  |           |           | *   | μΑ     |

| I <sub>IH</sub>                     |                           |       |           | ±10                  |           |           | *   | μΑ     |

| DIGITAL OUTPUTS                     |                           |       |           |                      |           |           |     |        |

| Data Format                         |                           |       |           | Se                   |           |           |     |        |

| Data Coding                         |                           |       | E         | Binary Two's         | Complemen | nt        |     |        |

| V <sub>OL</sub>                     | $I_{SINK} = 1.6mA$        |       |           | +0.4                 |           |           | *   | V      |

| V <sub>OH</sub>                     | $I_{SOURCE} = 500 \mu A$  | +4    |           |                      | *         |           |     | V      |

| Leakage Current                     | High-Z State,             |       |           | ±1                   |           |           | *   | μΑ     |

|                                     | $V_{OUT} = 0V$ to $V_{S}$ |       |           |                      |           |           |     | _      |

| Output Capacitance                  | High-Z State              |       |           | 15                   |           |           | 15  | pF     |

| POWER SUPPLY                        |                           |       |           |                      |           |           |     |        |

| Vs                                  |                           | +4.75 | +5        | +5.25                | *         | *         | *   | V      |

| Power Dissipation                   | $f_{S} = 40 \text{kHz}$   |       |           | 35                   |           |           | *   | mW     |

| TEMPERATURE RANGE                   |                           |       |           |                      |           |           |     |        |

| Specified Performance               |                           | -40   |           | +85                  | *         |           | *   | °C     |

| Derated Performance                 |                           | -55   |           | +125                 | *         |           | *   | °C     |

\* Same specification as grade to the left.

NOTES: (1) LSB means Least Significant Bit. For the ±10V input range, one LSB is 4.88mV. (2) Typical rms noise at worst case transitions and temperatures. (3) Full scale error is the worst case of –Full Scale or +Full Scale untrimmed deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and includes the effect of offset error. (4) After the ADS7812 is initially powered on and fully settles, this is the time delay after it is brought out of Power Down Mode until all internal settling occurs and the analog input is acquired to rated accuracy, and normal conversions can begin again. (5) All specifications in dB are referred to a full-scale input. (6) Useable Bandwidth defined as Full-Scale input frequency at which Signal-to-(Noise+Distortion) degrades to 60dB, or 10 bits of accuracy. (7) Recovers to specified performance after 2 x FS input overvoltage. (8) The minimum V<sub>IH</sub> level for the DATACLK signal is 3V.

### **PIN CONFIGURATION**

**PIN CONFIGURATION**

| PIN # | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | R1 <sub>IN</sub> | Analog Input. See Tables I and IV.                                                                                                                                                                                                                                                                                                                                                                            |

| 2     | GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3     | R2 <sub>IN</sub> | Analog Input. See Tables I and IV.                                                                                                                                                                                                                                                                                                                                                                            |

| 4     | R3 <sub>IN</sub> | Analog Input. See Tables I and IV.                                                                                                                                                                                                                                                                                                                                                                            |

| 5     | BUF              | Reference Buffer Output. Connect to $R1_{IN}$ , $R2_{IN}$ , or $R3_{IN}$ , as needed.                                                                                                                                                                                                                                                                                                                         |

| 6     | CAP              | Reference Buffer Compensation Node. Decouple to ground with a 1µF tantalum capacitor in parallel with a 0.01µF ceramic capacitor.                                                                                                                                                                                                                                                                             |

| 7     | REF              | Reference Input/Output. Outputs internal +2.5V reference via a series $4k\Omega$ resistor. Decouple this voltage with a 1µF to 2.2µF tantalum capacitor to ground. If an external reference voltage is applied to this pin, it will override the internal reference.                                                                                                                                          |

| 8     | GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9     | DATACLK          | Data Clock Pin. With EXT/INT LOW, this pin is an output and provides the synchronous clock for the serial data. The output is tri-stated when $\overline{CS}$ is HIGH. With EXT/INT HIGH, this pin is an input and the serial data clock must be provided externally.                                                                                                                                         |

| 10    | DATA             | Serial Data Output. The serial data is always the result of the last completed conversion and is synchronized to DATACLK. If DATACLK is from the internal clock (EXT/INT LOW), the serial data is valid on both the rising and falling edges of DATACLK. DATA is tri-stated when $\overline{CS}$ is HIGH.                                                                                                     |

| 11    | EXT/ĪNT          | External or Internal DATACLK Pin. Selects the source of the synchronous clock for serial data. If HIGH, the clock must be provided externally. If LOW, the clock is derived from the internal conversion clock. Note that the clock used to time the conversion is always internal regardless of the status of EXT/INT.                                                                                       |

| 12    | CONV             | Convert Input. A falling edge on this input puts the internal sample/hold into the hold state and starts a conversion regardless of the state of CS. If a conversion is already in progress, the falling edge is ignored. If EXT/INT is LOW, data from the previous conversion will be serially transmitted during the current conversion.                                                                    |

| 13    | CS               | Chip Select. This input tri-states all outputs when HIGH and enables all outputs when LOW. This includes DATA, BUSY, and DATACLK (when EXT/INT is LOW). Note that a falling edge on CONV will initiate a conversion even when CS is HIGH.                                                                                                                                                                     |

| 14    | BUSY             | Busy Output. When a conversion is started, $\overline{\text{BUSY}}$ goes LOW and remains LOW throughout the conversion. If EXT/ $\overline{\text{INT}}$ is LOW, data is serially transmitted while $\overline{\text{BUSY}}$ is LOW. $\overline{\text{BUSY}}$ is tri-stated when $\overline{\text{CS}}$ is HIGH.                                                                                               |

| 15    | PWRD             | Power Down Input. When HIGH, the majority of the ADS7812 is placed in a low power mode and power consumption is significantly reduced. CONV must be taken LOW prior to PWRD going LOW in order to achieve the lowest power consumption. The time required for the ADS7812 to return to normal operation after power down depends on a number of factors. Consult the Power Down section for more information. |

| 16    | Vs               | +5V Supply Input. For best performance, decouple to ground with a 0.1µF ceramic capacitor in parallel with a 10µF tantalum capacitor.                                                                                                                                                                                                                                                                         |

#### Top View DIP, SOIC 16 V<sub>S</sub> R1<sub>IN</sub> 1 GND 2 15 PWRD R2<sub>IN</sub> 14 BUSY 3 13 <u>CS</u> $R3_{IN}$ 4 ADS7812 12 CONV BUF 5 CAP 6 11 EXT/INT 10 DATA REF 7 9 DATACLK GND 8

| ANALOG<br>INPUT<br>RANGE (V) | CONNECT<br>R1 <sub>IN</sub><br>TO | R1 <sub>IN</sub> R2 <sub>IN</sub> |                 | R1 <sub>IN</sub> R2 <sub>IN</sub> R3 <sub>IN</sub> |  | INPUT<br>IMPEDANCE<br>(kΩ) |

|------------------------------|-----------------------------------|-----------------------------------|-----------------|----------------------------------------------------|--|----------------------------|

| ±10V                         | V <sub>IN</sub>                   | BUF                               | GND             | 45.7                                               |  |                            |

| 0.3125V to<br>2.8125V        | V <sub>IN</sub>                   | V <sub>IN</sub>                   | V <sub>IN</sub> | > 10,000                                           |  |                            |

| ±5V                          | GND                               | BUF                               | V <sub>IN</sub> | 26.7                                               |  |                            |

| 0V to 10V                    | BUF                               | GND                               | V <sub>IN</sub> | 26.7                                               |  |                            |

| 0V to 4V                     | BUF                               | V <sub>IN</sub>                   | GND             | 21.3                                               |  |                            |

| ±3.33V                       | V <sub>IN</sub>                   | BUF                               | V <sub>IN</sub> | 21.3                                               |  |                            |

| 0.5V to<br>4.5V              | GND                               | V <sub>IN</sub>                   | GND             | 21.3                                               |  |                            |

TABLE I. ADS7812 Input Ranges.

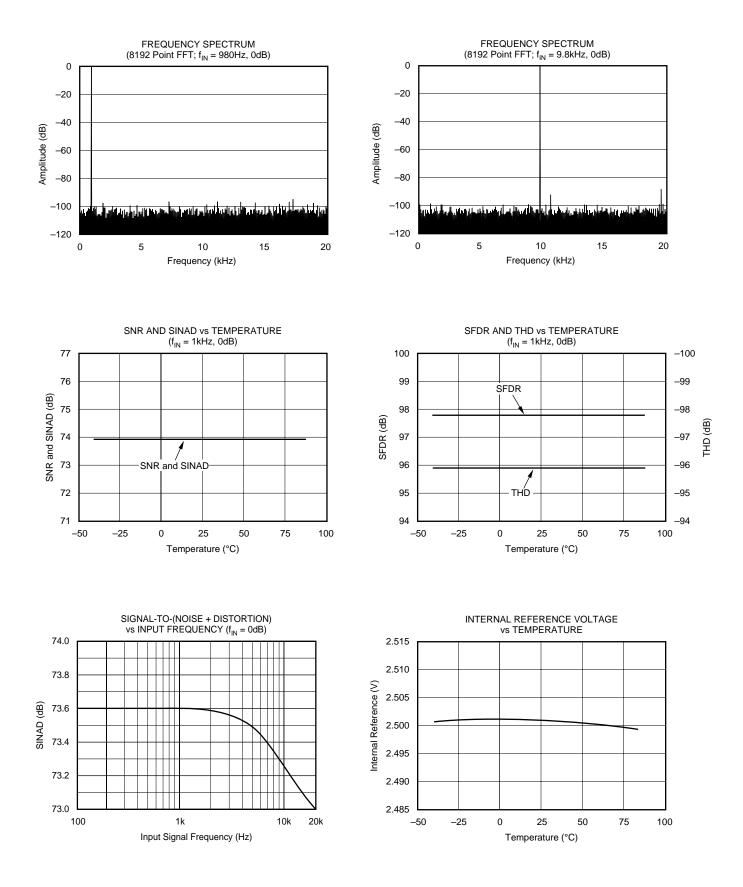

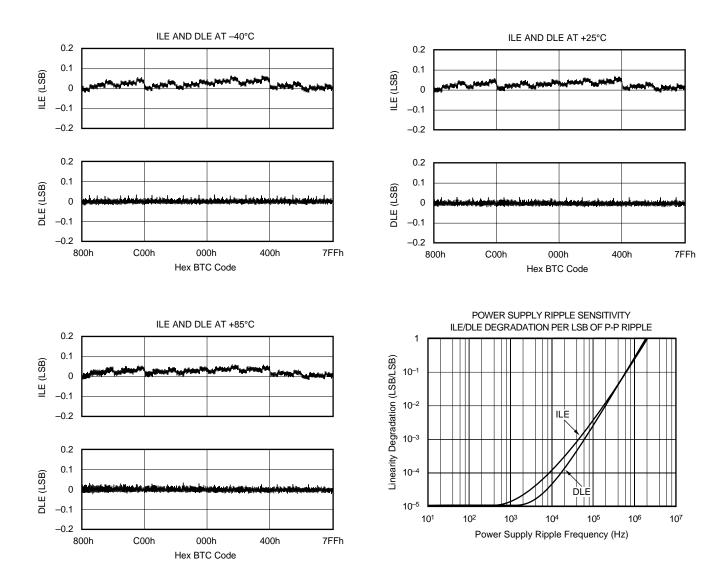

# **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25^{\circ}C$ ,  $f_S = 40kHz$ ,  $V_S = +5V$ ,  $\pm 10V$  input range, using internal reference, unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A = +25^{\circ}C$ ,  $f_S = 40kHz$ ,  $V_S = +5V$ ,  $\pm 10V$  input range, using internal reference, unless otherwise noted.

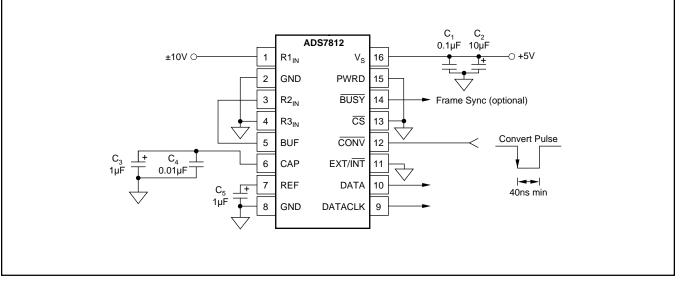

## **BASIC OPERATION**

### INTERNAL DATACLK

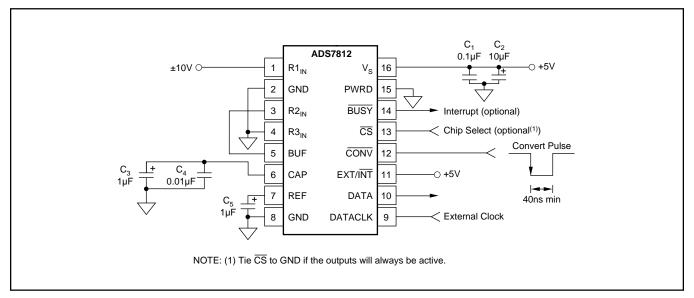

Figure 1a shows a basic circuit to operate the ADS7812 with a  $\pm 10V$  input range. To begin a conversion and serial transmission of the results from the previous conversion, a falling edge must be provided to the  $\overline{\text{CONV}}$  input. BUSY will go LOW indicating that a conversion has started and will stay LOW until the conversion is complete. During the conversion, the results of the previous conversion will be transmitted via DATA while DATACLK provides the synchronous clock for the serial data. The data format is 12-bit, Binary Two's Complement, and MSB first. Each data bit is valid on both the rising and falling edge of DATACLK. BUSY is LOW during the entire serial transmission and can be used as a frame synchronization signal.

#### EXTERNAL DATACLK

Figure 1b shows a basic circuit to operate the ADS7812 with a  $\pm 10V$  input range. To begin a conversion, a falling edge must be provided to the CONV input. BUSY will go LOW indicating that a conversion has started and will stay LOW until the conversion is complete. Just prior to BUSY rising near the end of the conversion, the internal working register holding the conversion result will be transferred to the internal shift register.

The internal shift register is clocked via the DATACLK input. The recommended method of reading the conversion result is to provide the serial clock after the conversion has completed. See External DATACLK under the Reading Data section of this data sheet for more information.

FIGURE 1a. Basic Operation, ±10V Input Range, Internal DATACLK.

FIGURE 1b. Basic Operation, ±10V Input Range, External DATACLK.

| SYMBOL          | DESCRIPTION                                       | MIN | ТҮР | МАХ | UNITS |

|-----------------|---------------------------------------------------|-----|-----|-----|-------|

| t <sub>1</sub>  | Conversion Plus Acquisition Time                  |     |     | 25  | μs    |

| t <sub>2</sub>  | CONV LOW to All Digital<br>Inputs Stable          |     |     | 8   | μs    |

| t <sub>3</sub>  | CONV LOW to Initiate a Conversion                 | 40  |     |     | ns    |

| t <sub>4</sub>  | BUSY Rising to Any Digital<br>Input Active        | 0   |     |     | ns    |

| t <sub>5</sub>  | CONV HIGH Prior to Start<br>of Conversion         | 2   |     |     | μs    |

| t <sub>6</sub>  | BUSY LOW                                          |     | 15  | 20  | μs    |

| t <sub>7</sub>  | CONV LOW to BUSY LOW                              |     | 85  | 120 | ns    |

| t <sub>8</sub>  | Aperture Delay                                    |     | 40  |     | ns    |

| t <sub>9</sub>  | Conversion Time                                   |     | 14  | 20  | μs    |

| t <sub>10</sub> | Conversion Complete to<br>BUSY Rising             |     | 1.1 | 2   | μs    |

| t <sub>11</sub> | Acquisition Time                                  |     |     | 5   | μs    |

| t <sub>12</sub> | CONV LOW to Rising Edge<br>of First DATACLK       |     | 1.4 |     | μs    |

| t <sub>13</sub> | Internal DATACLK HIGH                             | 250 | 350 | 500 | ns    |

| t <sub>14</sub> | Internal DATACLK LOW                              | 600 | 760 | 875 | ns    |

| t <sub>15</sub> | Internal DATACLK Period                           |     | 1.1 |     | μs    |

| t <sub>16</sub> | DATA Valid to Internal<br>DATACLK Rising          | 20  |     |     | ns    |

| t <sub>17</sub> | Internal DATACLK Falling<br>to DATA Not Valid     | 400 |     |     | ns    |

| t <sub>18</sub> | Falling Edge of Last DATACLK<br>to BUSY Rising    |     | 800 |     | ns    |

| t <sub>19</sub> | External DATACLK Rising<br>to DATA Not Valid      | 15  |     |     | ns    |

| t <sub>20</sub> | External DATACLK Rising<br>to DATA Valid          |     | 55  | 85  | ns    |

| t <sub>21</sub> | External DATACLK HIGH                             | 50  |     |     | ns    |

| t <sub>22</sub> | External DATACLK LOW                              | 50  |     |     | ns    |

| t <sub>23</sub> | External DATACLK Period                           | 100 |     |     | ns    |

| t <sub>24</sub> | CONV LOW to External<br>DATACLK Active            | 120 |     |     | ns    |

| t <sub>25</sub> | External DATACLK LOW<br>or CS HIGH to BUSY Rising | 2   |     |     | μs    |

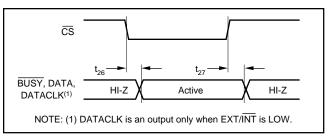

| t <sub>26</sub> | CS LOW to Digital Outputs Enabled                 | 85  |     |     | ns    |

| t <sub>27</sub> | CS HIGH to Digital Outputs Disabled               | 85  |     |     | ns    |

TABLE II. ADS7812 Timing.  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .

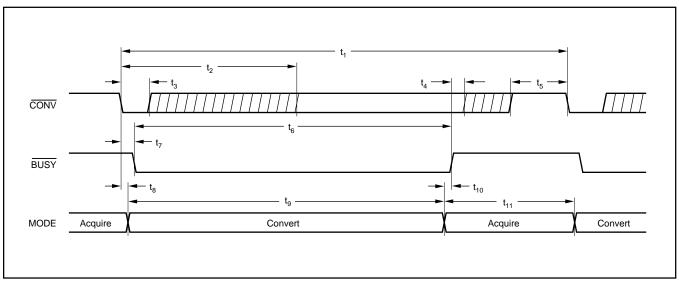

# **STARTING A CONVERSION**

If a conversion is not currently in progress, a falling edge on the  $\overrightarrow{\text{CONV}}$  input places the sample and hold into the hold mode and begins a conversion, as shown in Figure 2 and with the timing given in Table II. During the conversion, the  $\overrightarrow{\text{CONV}}$  input is ignored. Starting a conversion does not depend on the state of  $\overrightarrow{\text{CS}}$ . A conversion can be started once every 25µs (40kHz maximum conversion rate). There is no minimum conversion rate.

Even though the  $\overline{\text{CONV}}$  input is ignored while a conversion is in progress, this input should be held static during the conversion period. Transitions on this digital input can easily couple into sensitive analog portions of the converter, adversely affecting the conversion results (see the Sensitivity to External Digital Signals section of this data sheet for more information).

Ideally, the  $\overline{\text{CONV}}$  input should go LOW and remain LOW throughout the conversion. It should return HIGH sometime after  $\overline{\text{BUSY}}$  goes HIGH. In addition, it should be HIGH prior to the start of the next conversion for a minimum time period given by  $t_5$ . This will ensure that the digital transition on the  $\overline{\text{CONV}}$  input will not affect the signal that is acquired for the next conversion.

An acceptable alternative is to return the  $\overline{\text{CONV}}$  input HIGH as soon as possible after the start of the conversion. For example, a negative going pulse 100ns wide would make a good  $\overline{\text{CONV}}$  input signal. It is strongly recommended that from time t<sub>2</sub> after the start of a conversion until  $\overline{\text{BUSY}}$  rises, the  $\overline{\text{CONV}}$  input should be held static (either HIGH or LOW). During this time, the converter is more sensitive to external noise.

FIGURE 2. Basic Conversion Timing.

| DESCRIPTION                                     | ANALO          | G INPUT                | DIGITAL OUTPUT          |          |  |  |

|-------------------------------------------------|----------------|------------------------|-------------------------|----------|--|--|

|                                                 |                |                        | BINARY TWO'S COMPLEMENT |          |  |  |

| Full-Scale Range<br>Least Significant Bit (LSB) | ±10V<br>4.88mV | 0.5V to 4.5V<br>0.98mV | BINARY CODE             | HEX CODE |  |  |

| +Full Scale –1LSB                               | 9.99512V       | 4.49902V               | 0111 1111 1111          | 7FF      |  |  |

| Midscale                                        | 0V             | 2.5V                   | 0000 0000 0000          | 000      |  |  |

| Midscale –1LSB                                  | -4.88mV        | 2.49902 V              | 1111 1111 1111          | FFF      |  |  |

| -Full Scale                                     | -10V           | 0.5V                   | 1000 0000 0000          | 800      |  |  |

TABLE III. Ideal Input Voltage and Corresponding Digital Output for Two Common Input Ranges.

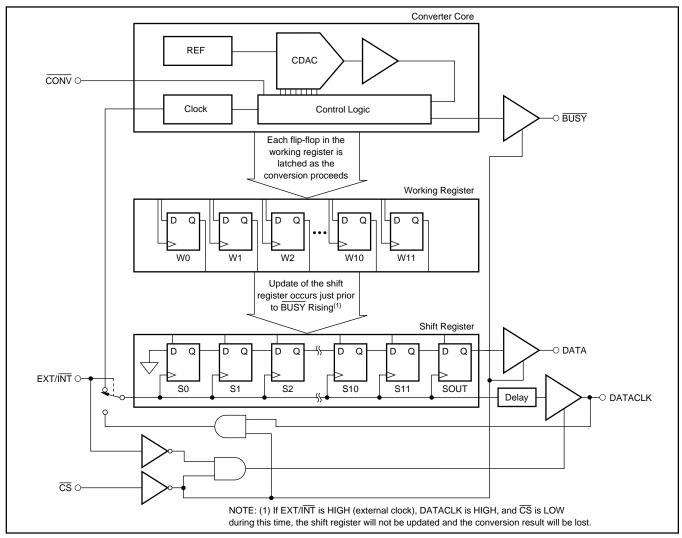

FIGURE 3. Block Diagram of the ADS7812's Digital Inputs and Outputs.

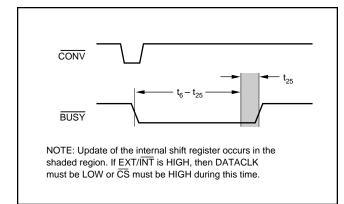

FIGURE 4. Timing of the Shift Register Update.

# **READING DATA**

The ADS7812's digital output is in Binary Two's Complement (BTC) format. Table III shows the relationship between the digital output word and the analog input voltage under ideal conditions.

Figure 3 shows the relationship between the various digital inputs, digital outputs, and internal logic of the ADS7812. Figure 4 shows when the internal shift register of the ADS7812 is updated and how this relates to a single conversion cycle. Together, these two figures point out a very important aspect of the ADS7812: the conversion result is not available until after the conversion is complete. The implications of this are discussed in the following sections.

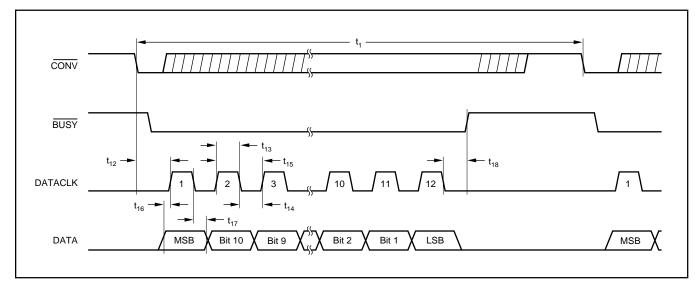

### INTERNAL DATACLK

With EXT/ $\overline{INT}$  tied LOW, the result from conversion 'n' is serially transmitted during conversion 'n+1', as shown in Figure 5 and with the timing given in Table II. Serial transmission of data occurs only during a conversion. When a transmission is not in progress, DATA and DATACLK are LOW.

During the conversion, the results of the previous conversion will be transmitted via DATA, while DATACLK provides the synchronous clock for the serial data. The data format is 12-bit, Binary Two's Complement, and MSB first. Each data bit is valid on both the rising and falling edges of DATACLK. BUSY is LOW during the entire serial transmission and can be used as a frame synchronization signal.

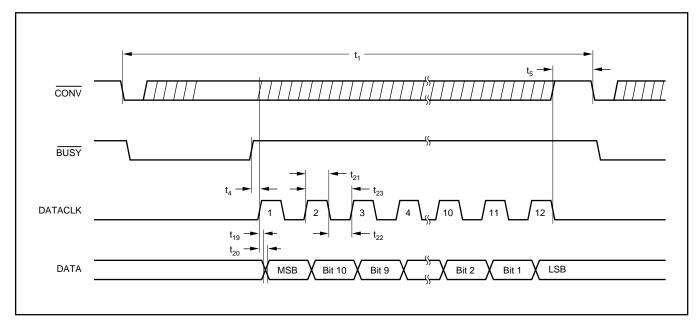

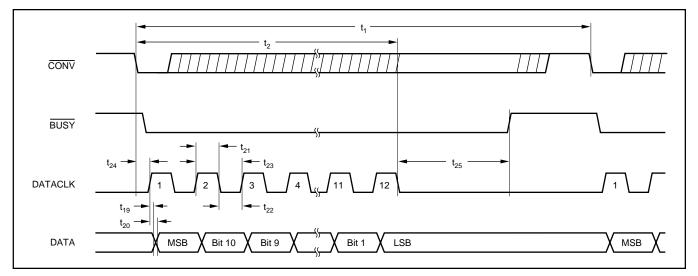

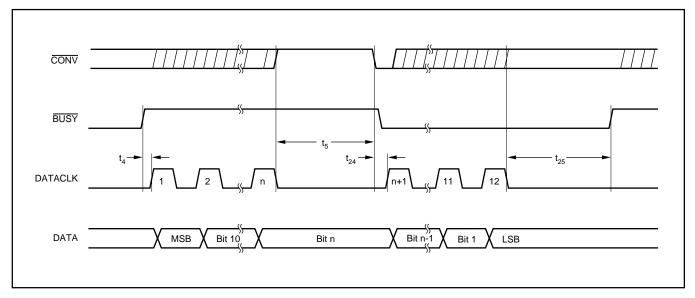

### EXTERNAL DATACLK

With EXT/INT tied HIGH, the result from conversion 'n' is clocked out after the conversion has completed, during the next conversion ('n+1'), or a combination of these two. Figure 6 shows the case of reading the conversion result after the conversion is complete. Figure 7 describes reading the result during the next conversion. Figure 8 combines the important aspects of Figures 6 and 7 as to reading part of the result after the conversion is complete and the remainder during the next conversion.

The serial transmission of the conversion result is initiated by a rising edge on DATACLK. The data format is 12-bit, Binary Two's Complement, and MSB first. Each data bit is valid on the falling edge of DATACLK. In some cases, it

FIGURE 5. Serial Data Timing, Internal Clock (EXT/ $\overline{INT}$  and  $\overline{CS}$  LOW).

FIGURE 6. Serial Data Timing, External Clock, Clocking After the Conversion Completes (EXT/INT HIGH, CS LOW).

might be possible to use the rising edge of the DATACLK signal. However, one extra clock period (not shown in Figures 6, 7, and 8) is needed for the final bit.

The external DATACLK signal must be LOW or  $\overline{CS}$  must be HIGH prior to  $\overline{BUSY}$  rising (see time  $t_{25}$  in Figures 7 and 8). If this is not observed, the output shift register of the ADS7812 will not be updated with the conversion result. Instead, the previous contents of the shift register will remain and the new result will be lost.

If more than 12 clock cycles are provided to the DATACLK input, the DATA output will go LOW after the rising edge of the 13th clock period. The operation of the ADS7812 will not be affected as long as the timing specifications are met.

Before reading the next three paragraphs, consult the Sensitivity to External Digital Signals section of this data sheet. This will explain many of the concerns regarding how and when to apply the external DATACLK signal.

### External DATACLK Active After the Conversion

The preferred method of obtaining the conversion result is to provide the DATACLK signal after the conversion has been completed and before the next conversion starts—as shown in Figure 6. Note that the DATACLK signal should be static before the start of the next conversion. If this is not observed, the DATACLK signal could affect the voltage that is acquired.

#### External DATACLK Active During the Next Conversion

Another method of obtaining the conversion result is shown in Figure 7. Since the output shift register is not updated until the end of the conversion, the previous result remains valid during the next conversion. If a fast clock ( $\geq$  2MHz) can be provided to the ADS7812, the result can be read during time t<sub>2</sub>. During this time, the noise from the DATACLK signal is less likely to affect the conversion result.

FIGURE 7. Serial Data Timing, External Clock, Clocking During the Next Conversion (EXT/INT HIGH, CS LOW).

FIGURE 8. Serial Data Timing, External Clock, Clocking After the Conversion Completes and During the Next Conversion (EXT/INT HIGH, CS LOW).

# External DATACLK Active After the Conversion and During the Next Conversion

Figure 8 shows a method that is a hybrid of the two previous approaches. This method works very well for microcontrollers that do serial transfers 8 bits at a time and for slower microcontrollers. For example, if the fastest serial clock that the microcontroller can produce is 1 $\mu$ s, and two 8-bit transfers must be used to obtain the serial data, the approach shown in Figure 6 would result in a diminished throughput (26kHz maximum conversion rate). The method described in Figure 7 could not be used because time t<sub>25</sub> would be violated. The approach in Figure 8 results in an improved throughput rate (33kHz maximum with a 1 $\mu$ s clock) and DATACLK is LOW during t<sub>25</sub>.

### COMPATIBILITY WITH THE ADS7813

The only difference between the ADS7812 and the ADS7813 is in the internal control logic and the digital interface. Since the ADS7813 is a 16-bit converter, the internal shift register is 16 bits wide. In addition, only 16-bit decisions are made during the conversion. Thus, the ADS7813's conversion time is approximately 133% of the ADS7812's.

The timing presented in this data sheet will allow as much compatibility as possible with the ADS7813. The main concern will be the different number of serial clocks. If a design must be compatible with both the ADS7812 and ADS7813, it is recommended to consider the ADS7813 first. If the design works with the ADS7813, it will certainly work with the ADS7812. This is also true in regards to layout (see the Layout section of this data sheet).

## CHIP SELECT (CS)

The  $\overline{CS}$  input allows the digital outputs of the ADS7812 to be disabled and gates the external DATACLK signal when EXT/ $\overline{INT}$  is HIGH. See Figure 9 for the enable and disable time associated with  $\overline{CS}$  and Figure 3 for a block diagram of the ADS7812's logic. The digital outputs can be disabled at any time.

Note that a conversion is initiated on the falling edge of  $\overline{\text{CONV}}$  even if  $\overline{\text{CS}}$  is HIGH. If the EXT/ $\overline{\text{INT}}$  input is LOW (internal DATACLK) and  $\overline{\text{CS}}$  is HIGH during the entire conversion, the previous conversion result will be lost (the serial transmission occurs but DATA and DATACLK are disabled).

FIGURE 9. Enable and Disable Timing for Digital Outputs.

## **ANALOG INPUT**

The ADS7812 offers a number of input ranges. This is accomplished by connecting the three input resistors to either the analog input ( $V_{IN}$ ), to ground (GND), or to the 2.5V reference buffer output (BUF). Table I shows the input ranges that are typically used in data acquisition applications. These ranges are all specified to meet the specifications given in the Specifications table. Table IV contains a complete list of ideal input ranges, associated input connections, and comments regarding the range.

| ANALOG<br>INPUT<br>RANGE (V) | CONNECT<br>R1 <sub>IN</sub><br>TO | CONNECT<br>R2 <sub>IN</sub><br>TO | CONNECT<br>R3 <sub>IN</sub><br>TO | INPUT<br>IMPEDANCE<br>(kΩ) | COMMENT                                    |

|------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|----------------------------|--------------------------------------------|

| 0.3125 to 2.8125             | V <sub>IN</sub>                   | V <sub>IN</sub>                   | V <sub>IN</sub>                   | > 10,000                   | Specified offset and gain                  |

| -0.417 to 2.916              | V <sub>IN</sub>                   | V <sub>IN</sub>                   | BUF                               | 26.7                       | V <sub>IN</sub> cannot go below GND – 0.3V |

| 0.417 to 3.750               | V <sub>IN</sub>                   | V <sub>IN</sub>                   | GND                               | 26.7                       | Offset and gain not specified              |

| ±3.333                       | V <sub>IN</sub>                   | BUF                               | V <sub>IN</sub>                   | 21.3                       | Specified offset and gain                  |

| –15 to 5                     | V <sub>IN</sub>                   | BUF                               | BUF                               | 45.7                       | Offset and gain not specified              |

| ±10                          | V <sub>IN</sub>                   | BUF                               | GND                               | 45.7                       | Specified offset and gain                  |

| 0.833 to 7.5                 | V <sub>IN</sub>                   | GND                               | V <sub>IN</sub>                   | 21.3                       | Offset and gain not specified              |

| -2.5 to 17.5                 | V <sub>IN</sub>                   | GND                               | BUF                               | 45.7                       | Exceeds absolute maximum V <sub>IN</sub>   |

| 2.5 to 22.5                  | V <sub>IN</sub>                   | GND                               | GND                               | 45.7                       | Exceeds absolute maximum V <sub>IN</sub>   |

| 0 to 2.857                   | BUF                               | V <sub>IN</sub>                   | V <sub>IN</sub>                   | 45.7                       | Offset and gain not specified              |

| -1 to 3                      | BUF                               | V <sub>IN</sub>                   | BUF                               | 21.3                       | V <sub>IN</sub> cannot go below GND – 0.3V |

| 0 to 4                       | BUF                               | V <sub>IN</sub>                   | GND                               | 21.3                       | Specified offset and gain                  |

| -6.25 to 3.75                | BUF                               | BUF                               | V <sub>IN</sub>                   | 26.7                       | Offset and gain not specified              |

| 0 to 10                      | BUF                               | GND                               | V <sub>IN</sub>                   | 26.7                       | Specified offset and gain                  |

| 0.357 to 3.214               | GND                               | V <sub>IN</sub>                   | V <sub>IN</sub>                   | 45.7                       | Offset and gain not specified              |

| -0.5 to 3.5                  | GND                               | V <sub>IN</sub>                   | BUF                               | 21.3                       | V <sub>IN</sub> cannot go below GND – 0.3V |

| 0.5 to 4.5                   | GND                               | V <sub>IN</sub>                   | GND                               | 21.3                       | Specified offset and gain                  |

| ±5                           | GND                               | BUF                               | V <sub>IN</sub>                   | 26.7                       | Specified offset and gain                  |

| 1.25 to 11.25                | GND                               | GND                               | V <sub>IN</sub>                   | 26.7                       | Offset and gain not specified              |

TABLE IV. Complete List of Ideal Input Ranges.

The input impedance results from the various connections and the internal resistor values (refer to the block diagram on the front page of this data sheet). The internal resistor values are typical and can change by  $\pm 30\%$ , due to process variations. However, the ratio matching of the resistors is considerably better than this. Thus, the input range will vary only a few tenths of a percent from part to part, while the input impedance may vary up to  $\pm 30\%$ .

The Specifications table contains the maximum limits for the variation of the analog input range, but only for those ranges where the comment field shows that the offset and gain are specified (this includes all the ranges listed in Table I). For the other ranges, the offset and gain are not tested and are not specified.

Five of the input ranges in Table IV are not recommended for general use. For two of the these, the input voltage exceeds the absolute maximum. These ranges can still be used as long as the input voltage remains under the absolute maximum, but this will moderately to significantly reduce the full-scale range of the converter.

The other three input ranges involve the connection at  $R2_{IN}$  being driven below GND – 0.3V. This input has a reversebiased ESD protection diode connection to ground. If  $R2_{IN}$  is taken below ground, this diode will be forward-biased and will clamp the negative input at –0.4V to –0.7V, depending on the temperature. Here again, these ranges can still be used at the cost of the full-scale range of the converter.

Note that Table IV assumes that the voltage at the REF pin is 2.5V. This is true if the internal reference is being used or if the external reference is 2.5V. Other reference voltages will change the values in Table IV.

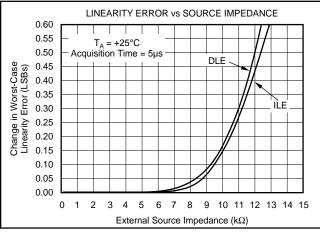

#### HIGH IMPEDANCE MODE

When  $R1_{IN}$ ,  $R2_{IN}$ , and  $R3_{IN}$  are connected to the analog input, the input range of the ADS7812 is 0.3125V to 2.8125V and the input impedance is greater than 10M $\Omega$ . This input range can be used to connect the ADS7812 directly to a wide variety of sensors. Figure 10 shows the impedance of the sensor versus the change in ILE and DLE of the ADS7812. The performance of the ADS7812 can be improved for higher sensor impedance by allowing more time for acquisition. For example, 10µs of acquisition time will approximately double sensor impedance for the same ILE/DLE performance.

The input impedance and capacitance of the ADS7812 are very stable with temperature. Assuming that this is true of the sensor as well, the graph shown in Figure 10 will vary less than a few percent over the specified temperature range of the ADS7812. If the sensor impedance varies significantly with temperature, the worst-case impedance should be used.

### DRIVING THE ADS7812 ANALOG INPUT

ADS7812

SBAS042A

In general, any "reasonably fast", high quality operational or instrumentation amplifier can be used to drive the ADS7812 input. When the converter enters the acquisition mode, there is some charge injection from the converter's input to the amplifier's output. This can result in inadequate settling time with slower amplifiers. Be very careful with singlesupply amplifiers, particularly if their output will be required to swing very close to the supply rails.

In addition, be careful in regards to the amplifier's linearity. The outputs of single-supply and "rail-to-rail" amplifiers can saturate as they approach the supply rails. Rather than the amplifier's transfer function being a straight line, the curve can become severely 'S' shaped. Also, watch for the point where the amplifier switches from sourcing current to sinking current. For some amplifiers, the transfer function can be noticeably discontinuous at this point, causing a significant change in the output voltage for a much smaller change on the input.

Texas Instruments manufactures a wide variety of operational and instrumentation amplifiers that can be used to drive the input of the ADS7812. These include the OPA627, OPA134, OPA132, and INA110.

## REFERENCE

The ADS7812 can be operated with its internal 2.5V reference or an external reference. By applying an external reference voltage to the REF pin, the internal reference voltage is overdriven. The voltage at the REF input is internally buffered by a unity gain buffer. The output of this buffer is present at the BUF and CAP pins.

### REF

The REF pin is the output of the internal 2.5V reference or the input for an external reference. A  $1\mu$ F to  $2.2\mu$ F tantalum capacitor should be connected between this pin and ground. The capacitor should be placed as close as possible to the ADS7812.

When using the internal reference, the REF pin should not be connected to any type of significant load. An external load will cause a voltage drop across the internal  $4k\Omega$ resistor that is in series with the internal reference. Even a  $4M\Omega$  external load to ground will cause a decrease in the full-scale range of the converter by 4 LSBs.

The range for the external reference is 2.3V to 2.7V. The voltage on REF determines the full-scale range of the converter and the corresponding LSB size. Increasing the reference voltage will increase the LSB size in relation to the internal noise sources which, in turn, can improve signal-to-noise ratio. Likewise, decreasing the reference voltage will reduce the LSB size and signal-to-noise ratio.

### CAP

The CAP pin is used to compensate the internal reference buffer. A 1 $\mu$ F tantalum capacitor in parallel with a 0.01 $\mu$ F ceramic capacitor should be connected between this pin and ground, with the ceramic capacitor placed as close as possible to the ADS7812. The total value of the capacitance on the CAP pin is critical to optimum performance of the ADS7812. A value larger than 2.0 $\mu$ F could overcompensate the buffer while a value lower than 0.5 $\mu$ F may not provide adequate compensation.

### BUF

The voltage on the BUF pin is the output of the internal reference buffer. This pin is used to provide +2.5V to the analog input or inputs for the various input configurations. The BUF output can provide up to 1mA of current to an external load. The load should be constant as a variable load could affect the conversion result by modulating the BUF voltage. Also note that the BUF output will show significant glitches as each bit decision is made during a conversion. Between conversions, the BUF output is quiet.

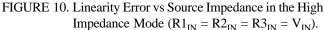

## **POWER DOWN**

The ADS7812 has a power-down mode that is activated by taking  $\overline{\text{CONV}}$  LOW and then PWRD HIGH. This will power down all of the analog circuitry including the reference, reducing power dissipation to under 50µW. To exit the power-down mode,  $\overline{\text{CONV}}$  is taken HIGH and then PWRD is taken LOW. Note that a conversion will be initiated if PWRD is taken HIGH while  $\overline{\text{CONV}}$  is LOW.

While in the power-down mode, the voltage on the capacitors connected to CAP and REF will begin to leak off. The voltage on the CAP capacitor leaks off much more rapidly than the REF capacitor (the REF input of the ADS7812 becomes high impedance when PWDN is HIGH—this is not true for the CAP input). When the power-down mode is exited, these capacitors must be allowed to recharge and settle to a 12-bit level. Figure 11 shows the amount of time typically required to obtain a valid 12-bit result based on the amount of time spent in power down (at room temperature). This figure assumes that the total capacitance on the CAP pin is  $1.01\mu$ F.

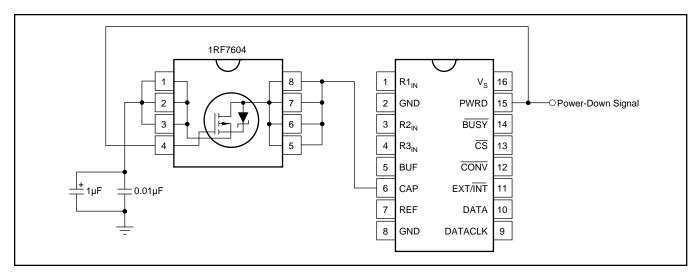

Figure 12 provides a circuit which can significantly reduce the power up time if the power down time will be fairly brief (a few seconds or less). A low on-resistance MOSFET is used to disconnect the capacitance on the CAP pin from the leakage paths internal to the ADS7812. This allows the capacitors to retain their charge for a much longer period of time, reducing the time required to recharge them at power up. With this circuit, the power down time can be extended to tens or hundreds of milliseconds with almost instantaneous power up.

FIGURE 11. Power-Down to Power-Up Response.

FIGURE 12. Improved Power-Up Response Circuit.

# LAYOUT

The ADS7812 should be treated as a precision analog component and should reside completely on the "analog" portion of the printed circuit board. Ideally, a ground plane should extend underneath the ADS7812 and under all other analog components. This plane should be separate from the digital ground until they are joined at the power supply connection. This will help prevent dynamic digital ground currents from modulating the analog ground through a common impedance to power ground.

The +5V power should be clean, well-regulated, and separate from the +5V power for the digital portion of the design. One possibility is to derive the +5V supply from a linear regulator located near the ADS7812. If derived from the digital +5V power, a 5 $\Omega$  to 10 $\Omega$  resistor should be placed in series with the power connection from the digital supply. It may also be necessary to increase the bypass capacitance near the V<sub>S</sub> pin (an additional 100µF or greater capacitor in parallel with the 10µF and 0.1µF capacitors). For designs with a large number of digital components or very high speed digital logic, this simple power supply filtering scheme may not be adequate.

# SENSITIVITY TO EXTERNAL DIGITAL SIGNALS

All successive approximation register-based A/D converters are sensitive to external sources of noise. The reason for this will be explained in the following paragraphs. For the ADS7812 and similar A/D converters, this noise most often originates due to the transition of external digital signals. While digital signals that run near the converter can be the source of the noise, the biggest problem occurs with the digital inputs to the converter itself.

In many cases, the system designer may not be aware that there is a problem or a potential for a problem. For a 12-bit system, these problems typically occur at the least significant bits and only at certain places in the converter's transfer function. For a 16-bit converter, the problem can be much easier to spot. For example, the timing diagram in Figure 2 shows that the  $\overline{\text{CONV}}$  signal should return HIGH sometime during time  $t_2$ . In fact, the  $\overline{\text{CONV}}$  signal can return HIGH at any time during the conversion. However, after time  $t_2$ , the transition of the  $\overline{\text{CONV}}$  signal has the potential of creating a good deal of noise on the ADS7812 die. If this transition occurs at just precisely the wrong time, the conversion results could be affected. In a similar manner, transitions on the DATACLK input could affect the conversion result.

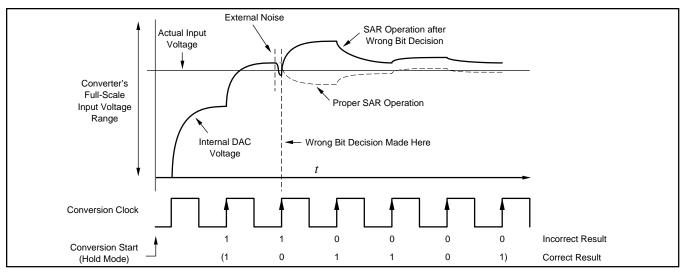

For the ADS7812, there are 12 separate bit decisions which are made during the conversion. The most significant bit decision is made first, proceeding to the least significant bit at the end of the conversion. Each bit decision involves the assumption that the bit being tested should be set. This is combined with the result that has been achieved so far. The converter compares this combined result with the actual input voltage. If the combined result is too high, the bit is cleared. If the result is equal to or lower than the actual input voltage, the bit remains HIGH. This is why the basic architecture is referred to as "successive approximation register."

If the result so far is getting very close to the actual input voltage, then the comparison involves two voltages which are very close together. The ADS7812 has been designed so that the internal noise sources are a minimum just prior to the comparator result being latched. However, if a external digital signal transitions at this time, a great deal of noise will be coupled into the sensitive analog section of the ADS7812. Even if this noise produces a difference between the two voltages of only 2mV, the conversion result will be off by 3 counts or least significant bits (LSBs). (The internal LSB size of the ADS7812 is  $610\mu V$  regardless of the input range.)

Once a digital transition has caused the comparator to make a wrong bit decision, the decision cannot be corrected. All subsequent bit decisions will then be wrong (unless some type of error correction is employed). Figure 13 shows a successive approximation process that has gone awry. The dashed line represents what the correct bit decisions should have been. The solid line represents the actual result of the conversion.

Texas

www.ti.com

STRUMENTS

٩I

FIGURE 13. SAR Operation When External Noise Affects the Conversion.

Keep in mind that the time period when the comparator is most sensitive to noise is fairly small. Also, the peak portion of the noise "event" produced by a digital transition is fairly brief as most digital signals transition in a few nanoseconds. The subsequent noise may last for a period of time longer than this and may induce further effects which require a longer settling time; however, in general, the event is over within a few tens of nanoseconds.

For the ADS7812, error correction is done when the tenth bit is decided. During this bit decision, it is possible to correct limited errors that may have occurred during previous bit decisions. However, after the tenth bit, no such correction is possible. Note that for the timing diagrams shown in Figures 2, 5, 6, 7, and 8, all external digital signals should remain static from 8 $\mu$ s after the start of a conversion until  $\overline{BUSY}$ rises. The tenth bit is decided approximately 10 $\mu$ s to 11 $\mu$ s into the conversion.

# **APPLICATIONS INFORMATION**

### **QSPI INTERFACING**

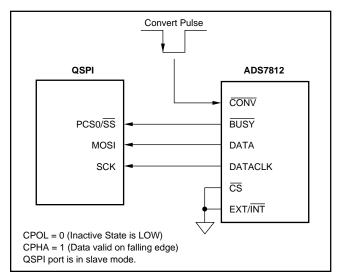

Figure 14 shows a simple interface between the ADS7812 and any queued serial peripheral interface (QSPI) equipped microcontroller (available on several Motorola devices). This interface assumes that the convert pulse does not originate from the microcontroller and that the ADS7812 is the only serial peripheral.

Before enabling the QSPI interface, the microcontroller must be configured to monitor the slave select  $(\overline{SS})$  line. When a LOW to HIGH transition occurs (indicating the end of a conversion), the port can be enabled. If this is not done, the microcontroller and A/D converter may not be properly synchronized. (The slave select line simply enables communication—it does not indicate the start or end of a serial transfer.)

FIGURE 14. QSPI Interface to the ADS7812.

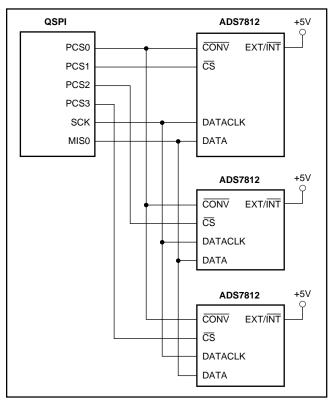

Figure 15 shows a QSPI-equipped microcontroller interfacing to three ADS7812s. There are many possible variations to this interface scheme. As shown, the QSPI port produces a common  $\overline{\text{CONV}}$  signal which initiates a conversion on all three converters. After the conversions are finished, each result is transferred, in turn. The QSPI port is completely programmable to handle the timing and transfers without processor intervention. If the CONV signal is generated in this way, it should be possible to make both AC and DC measurements with the ADS7812, as the CONV signal will have low jitter. Note that if the CONV signal is generated via software commands, it will have a good deal of jitter and only low frequency (DC) measurements can be made.

FIGURE 15. QSPI Interface to the Three ADS7812s.

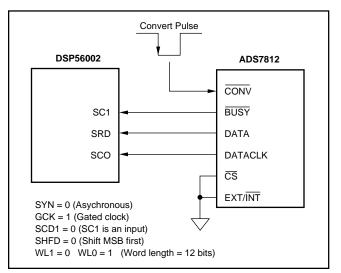

### **DSP56002 INTERFACING**

The DSP56002 serial interface has an serial peripheral interface (SPI) compatibility mode with some enhancements. Figure 16 shows an interface between the ADS7812 and the DSP56002. As with the QSPI interface of Figure 14,

FIGURE 16. DSP56002 Interface to the ADS7812.

the DSP56002 must be programmed to enable the serial interface when a LOW to HIGH transition on SCI occurs.

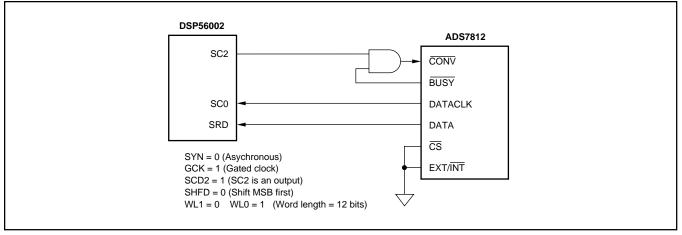

The DSP56002 can also provide the  $\overline{\text{CONV}}$  signal, as shown in Figure 17. The receive and transmit sections of the interface are decoupled (asynchronous mode) and the transmit section is set to generate a word length frame sync every other transmit frame (frame rate divider set to 2). The prescale modulus should be set to produce a transmit frame at twice the desired conversion rate.

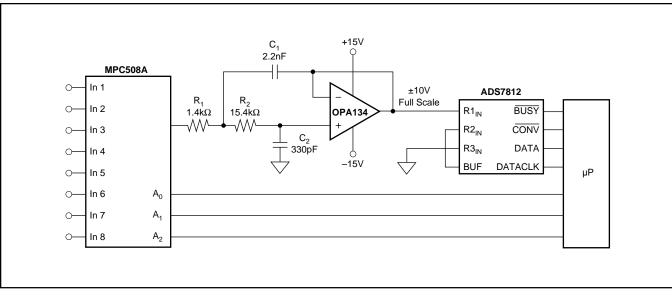

### **APPLICATIONS CIRCUIT**

Figure 18 shows a multiplexed data acquisition circuit using the ADS7812. The MPC508A provides the multiplexing function while the OPA134 is configured as a Sallen-Key, two-pole, unity gain lowpass filter.

FIGURE 17. DSP56002 Interface to the ADS7812. Processor Initiates Conversions.

FIGURE 18. Multiplexed Data Acquisition Circuit.

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                 |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                     |              |                |         |

| ADS7812PB        | ACTIVE | PDIP         | Ν       | 16   | 25      | RoHS & Green | Call TI       | N / A for Pkg Type  |              | ADS7812P       | Samples |

| ADS7812UB        | ACTIVE | SOIC         | DW      | 16   | 40      | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7812U<br>B  | Samples |

| ADS7812UB/1K     | ACTIVE | SOIC         | DW      | 16   | 1000    | RoHS & Green | Call TI       | Level-3-260C-168 HR | -40 to 85    | ADS7812U       | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

www.ti.com

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

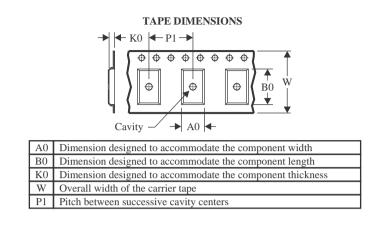

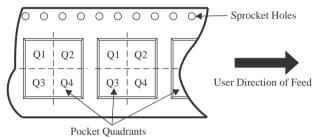

### TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All | dimensions | are | nominal |  |

|------|------------|-----|---------|--|

|      |            |     |         |  |

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADS7812UB/1K | SOIC            | DW                 | 16 | 1000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

www.ti.com

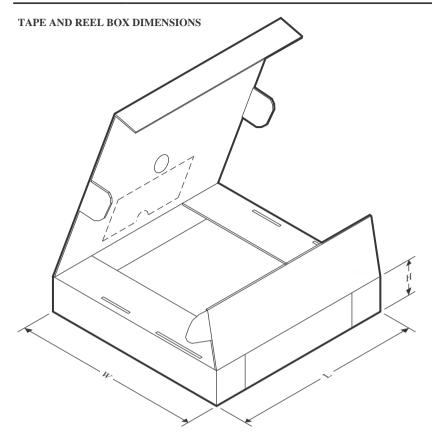

## PACKAGE MATERIALS INFORMATION

6-Apr-2024

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS7812UB/1K | SOIC         | DW              | 16   | 1000 | 356.0       | 356.0      | 35.0        |

### TEXAS INSTRUMENTS

www.ti.com

6-Apr-2024

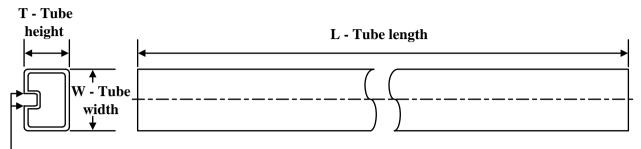

### TUBE

### - B - Alignment groove width

\*All dimensions are nominal

| Device    | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|-----------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ADS7812PB | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| ADS7812UB | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

## **DW 16**

## **GENERIC PACKAGE VIEW**

### SOIC - 2.65 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

7.5 x 10.3, 1.27 mm pitch

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

## **DW0016A**

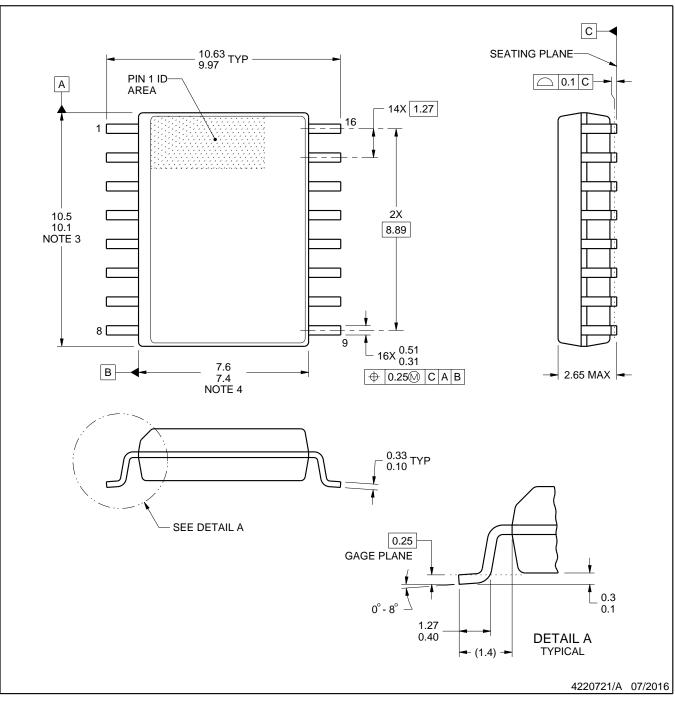

## **PACKAGE OUTLINE**

SOIC - 2.65 mm max height

SOIC

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

- 5. Reference JEDEC registration MS-013.

## DW0016A

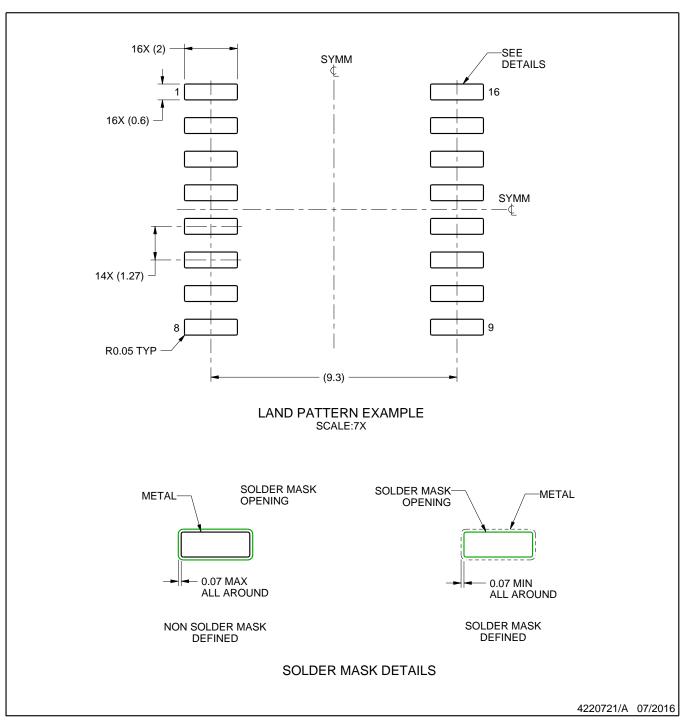

## **EXAMPLE BOARD LAYOUT**

### SOIC - 2.65 mm max height

SOIC

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

## DW0016A

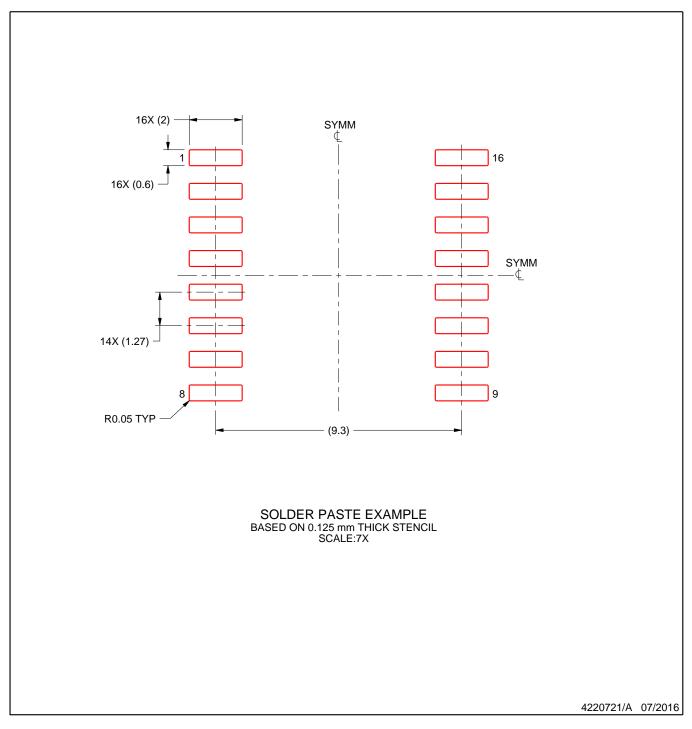

## **EXAMPLE STENCIL DESIGN**

## SOIC - 2.65 mm max height

SOIC

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

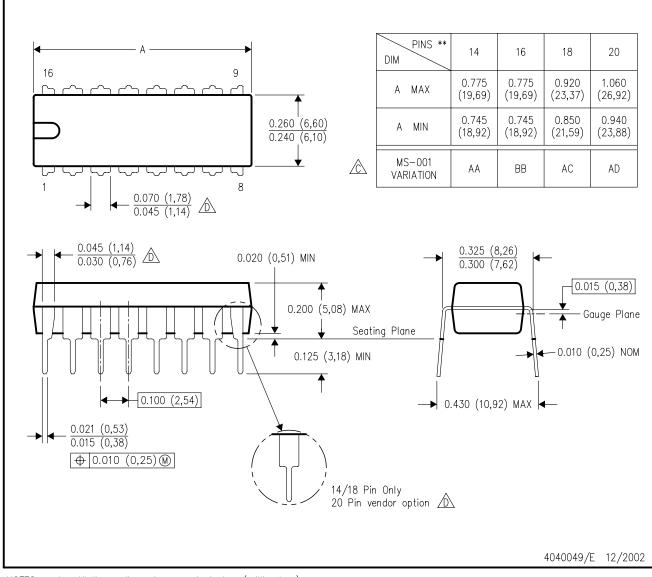

## N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated