LM3556

SNVS796D - AUGUST 2011 - REVISED OCTOBER 2015

# LM3556 1.5-A Synchronous Boost LED Flash Driver With High-Side Current Source

## **Features**

- Grounded Cathode LED Operation for Improved Thermal Management

- 1.5-A High-Side Current Source for Single LED

- Accurate and Programmable LED Current from 46.9 mA to 1.5 A

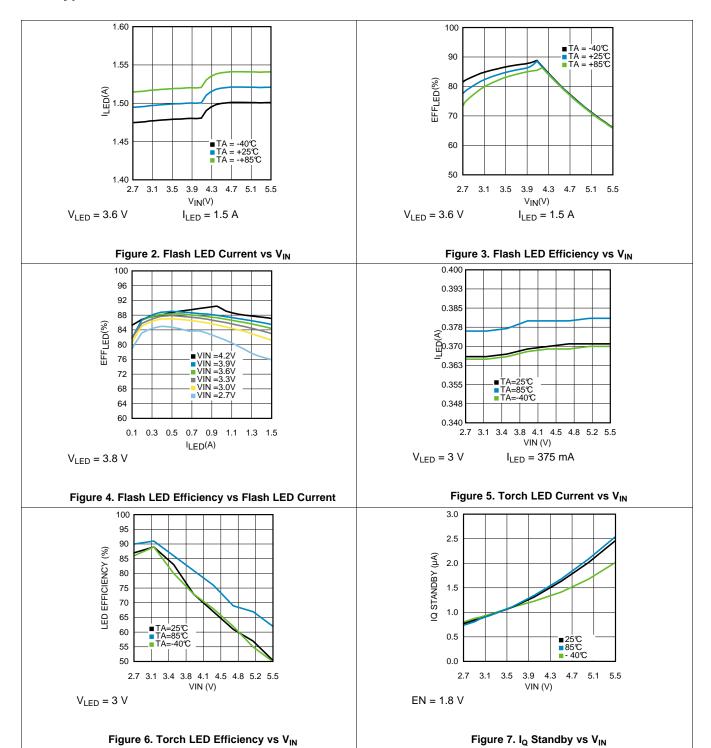

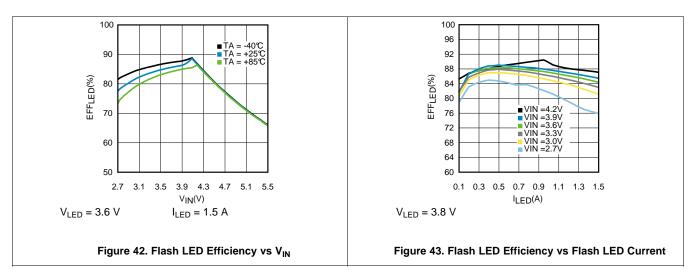

- > 85% Efficiency in Torch Mode (at 100 mA) and Flash Mode (at 1 A to 1.5 A)

- Small Solution Size: < 20 mm<sup>2</sup>

- LED Thermal Sensing and Current Scale-Back

- Soft-Start Operation for Battery Protection

- Hardware Enable Pin

- Hardware Torch Enable

- Hardware Strobe Enable

- Synchronization Input for RF Power Amplifier Pulse Events

- V<sub>IN</sub> Flash Monitor Optimization

- 400-kHz I<sup>2</sup>C-Compatible Interface

- I<sup>2</sup>C-Compatible Programmable NTC Trip Point

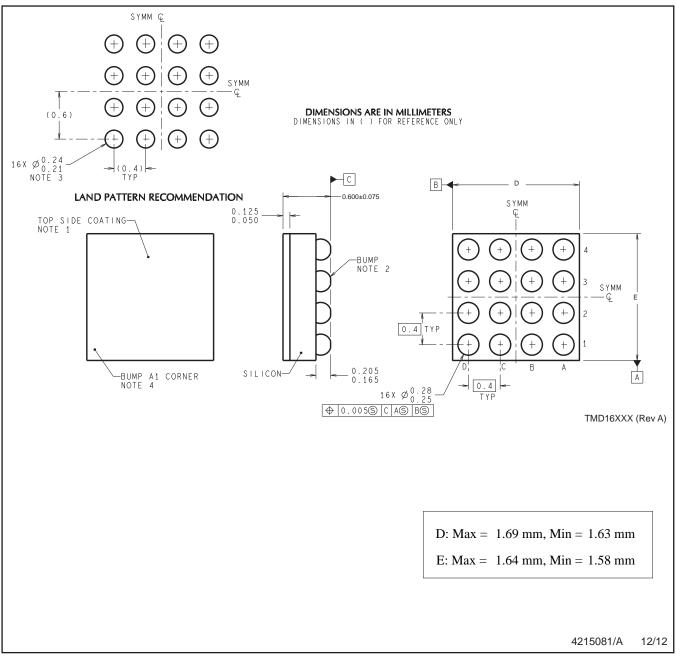

- 0.4-mm Pitch, 16-Pin DSBGA Package

# **Applications**

Camera Phone LED Flash

# 3 Description

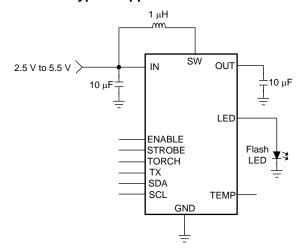

The LM3556 is a 4-MHz fixed-frequency synchronous boost converter plus 1.5-A constant current driver for a high-current white LED. The high-side current source allows for grounded cathode LED operation providing flash current up to 1.5 A. An adaptive regulation method ensures the current source remains in regulation and maximizes efficiency.

The LM3556 is controlled via an I<sup>2</sup>C-compatible interface. Features include: a hardware flash enable (STROBE) allowing a logic input to trigger the flash pulse, a hardware torch enable (TORCH) for Movie Mode or flashlight functions, a TX input which forces the flash pulse into a low-current Torch Mode allowing for synchronization to RF power amplifier events or other high-current conditions, and an integrated comparator designed to monitor an NTC thermistor and provide an interrupt to the LED current. With a fast 1-µs transition from 0 mA to 46.9 mA, the TORCH input pin can be used to develop custom LED current waveforms.

4-MHz switching frequency, overvoltage protection and adjustable current limit allow for the use of tiny, low-profile inductors and 10-µF ceramic capacitors. The device is operates over a -40°C to +85°C temperature range.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)   |  |

|-------------|------------|-------------------|--|

| LM3556      | DSBGA (16) | 1.69 mm × 1.64 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

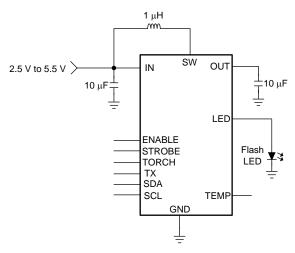

#### Typical Application Circuit

# **Table of Contents**

| 1 | Features 1                           |    | 7.5 Programming                      | 1              |

|---|--------------------------------------|----|--------------------------------------|----------------|

| 2 | Applications 1                       |    | 7.6 Register Maps                    | 19             |

| 3 | Description 1                        | 8  | Application and Implementation       | 27             |

| 4 | Revision History2                    |    | 8.1 Application Information          | 27             |

| 5 | Pin Configuration And Functions3     |    | 8.2 Typical Application              | 2              |

| 6 | Specifications4                      | 9  | Power Supply Recommendations         | 29             |

| • | 6.1 Absolute Maximum Ratings         | 10 | Layout                               | 30             |

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines               | 30             |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example                  | 3 <sup>,</sup> |

|   | 6.4 Thermal Information              | 11 | Device And Documentation Support     | 32             |

|   | 6.5 Electrical Characteristics5      |    | 11.1 Device Support                  | 32             |

|   | 6.6 Timing Requirements              |    | 11.2 Documentation Support           | 3              |

|   | 6.7 Typical Characteristics          |    | 11.3 Community Resources             | 3              |

| 7 | Detailed Description 12              |    | 11.4 Trademarks                      | 3              |

| - | 7.1 Overview                         |    | 11.5 Electrostatic Discharge Caution | 32             |

|   | 7.2 Functional Block Diagram         |    | 11.6 Glossary                        | 32             |

|   | 7.3 Feature Description              | 12 | Mechanical, Packaging, And Orderable | 01             |

|   | 7.4 Device Functional Modes 15       |    | Information                          | 3.             |

# 4 Revision History

# Changes from Revision C (April 2013) to Revision D

Page

Added Device Information and Pin Configuration and Functions sections, ESD Rating table, Feature Description,

Device Functional Modes, Application and Implementation, Power Supply Recommendations, Layout, Device and

Documentation Support, and Mechanical, Packaging, and Orderable Information sections

\_\_\_

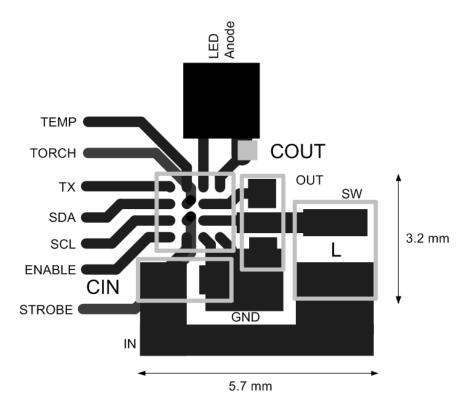

# 5 Pin Configuration And Functions

YFQ Package 16-Pin DSBGA Top View

## **Pin Functions**

|        | PIN    | TYPE   | DESCRIPTION                                                                                                                                                                                |  |  |

|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER | NAME   | ITPE   | DESCRIPTION                                                                                                                                                                                |  |  |

| A1, B1 | LED    | Power  | High-side current source output for flash LED. Both pins must be connected for proper operation.                                                                                           |  |  |

| B2, A2 | OUT    | Power  | Step-up DC-DC converter output. Connect a 10-µF ceramic capacitor between this pin and GND.                                                                                                |  |  |

| B3, A3 | SW     | Power  | Drain connection for internal NMOS and synchronous PMOS switches.                                                                                                                          |  |  |

| A4, B4 | GND    | Ground | Ground                                                                                                                                                                                     |  |  |

| C1     | TEMP   | Power  | Threshold detector for LED temperature sensing and current scale back.                                                                                                                     |  |  |

| C2     | TORCH  | Power  | Active high hardware torch enable. Drive TORCH high to turn on Torch or Movie mode. Used for external PWM Mode. Has an internal pulldown resistor of 300 k $\Omega$ between TORCH and GND. |  |  |

| С3     | STROBE | I/O    | Active high hardware flash enable. Drive STROBE high to turn on flash pulse. STROBE overrides TORCH. Has an internal pulldown resistor of 300 k $\Omega$ between STROBE and GND.           |  |  |

| C4     | IN     | Input  | Input voltage connection. Connect IN to the input supply, and bypass to GND with a 10-<br>µF or larger ceramic capacitor.                                                                  |  |  |

| D1     | TX     | I/O    | Configurable dual polarity power amplifier synchronization input. Has an internal pulldown resistor of 300 $k\Omega$ between TX and GND.                                                   |  |  |

| D2     | SDA    | I/O    | Serial data input/output.                                                                                                                                                                  |  |  |

| D3     | SCL    | Input  | Serial clock input.                                                                                                                                                                        |  |  |

| D4     | ENABLE | Power  | Active high enable pin. High = standby, low = shutdown/reset. There is no internal pulldown resistor on this pin.                                                                          |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                                                                           | MIN       | MAX                                                                 | UNIT |

|---------------------------------------------------------------------------|-----------|---------------------------------------------------------------------|------|

| $V_{IN}, V_{SW}, V_{OUT}$                                                 | -0.3      | 6                                                                   | V    |

| $V_{SCL},V_{SDA},V_{ENABLE},V_{STROBE},V_{TX},V_{TORCH},V_{LED},V_{TEMP}$ |           | -0.3 V to the lesser of (V <sub>IN</sub> + 0.3 V)<br>w/ 6 V maximum |      |

| Continuous power dissipation <sup>(3)</sup>                               | Internall | Internally limited                                                  |      |

| Junction temperature, T <sub>J-MAX</sub>                                  |           | 150                                                                 | °C   |

| Maximum lead temperature (soldering)                                      | Se        | See <sup>(4)</sup>                                                  |      |

| Storage temperature, T <sub>stg</sub>                                     | -65       | 150                                                                 | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages are with respect to the potential at the GND pin.

- (3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typical) and disengages at T<sub>J</sub> = 135°C (typical). Thermal shutdown is ensured by design.

- (4) For detailed soldering specifications and information, refer to Texas Instruments Application Note 1112: DSBGA Wafer Level chip Scale Package (SNVA009).

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Floatrootatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                    | MIN | NOM MAX | UNIT |

|----------------------------------------------------|-----|---------|------|

| V <sub>IN</sub>                                    | 2.5 | 5.5     | V    |

| Junction temperature, T <sub>J</sub>               | -40 | 125     | °C   |

| Ambient temperature, T <sub>A</sub> <sup>(2)</sup> | -40 | 85      | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (R<sub>θJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

#### 6.4 Thermal Information

|                                                                        | LM3556      |      |

|------------------------------------------------------------------------|-------------|------|

| THERMAL METRIC <sup>(1)</sup>                                          | YFQ (DSBGA) | UNIT |

|                                                                        | 16 PINS     |      |

| R <sub>θJA</sub> <sup>(2)</sup> Junction-to-ambient thermal resistance | 60          | °C/W |

- For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

- (2) Junction-to-ambient thermal resistance (R<sub>θJA</sub>) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 102 mm × 76 mm × 1.6 mm with a 2 × 1 array of thermal vias. The ground plane on the board is 50 mm × 50 mm. Thickness of copper layers are 36 μm/18 μm/36 μm (1.5 oz/1 oz/1.5 oz). Ambient temperature in simulation is 22°C, still air. Power dissipation is 1 W.

# 6.5 Electrical Characteristics

Unless otherwise specified,  $V_{IN}=3.6~V$ , typical limits apply for  $T_A=25^{\circ}C$ , and minimum (MIN) and maximum (MAX) limits apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_A \le +85^{\circ}C$ ). (1)(2)

|                   | PARAMETER                                             | TEST CONDITIONS                                                        | 3     | MIN            | TYP  | MAX             | UNIT       |  |

|-------------------|-------------------------------------------------------|------------------------------------------------------------------------|-------|----------------|------|-----------------|------------|--|

| CURREN            | IT SOURCE SPECIFICATIONS                              |                                                                        |       |                |      |                 |            |  |

| I <sub>LED</sub>  | Current source accuracy                               | 1.5-A Flash, V <sub>OUT</sub> = 4 V                                    |       | 1.425<br>(-5%) | 1.5  | 1.575<br>(+5%)  | Α          |  |

|                   | ·                                                     | 46.88-mA Torch, V <sub>OUT</sub> = 3.6                                 | V     | 42.3 (-10%)    | 47   | 51.7 (+10%)     | mA         |  |

| V                 | Current source regulation                             | I <sub>LED</sub> = 1.5 A                                               | Flash |                | 250  | 280 (+12%)      | mV         |  |

| $V_{HR}$          | voltage                                               | I <sub>LED</sub> = 46.88 mA                                            | Torch |                | 150  | 172.5 (+15%)    | IIIV       |  |

| \/                | Output overvoltage protection                         | ON Threshold                                                           |       | 4.86           | 5    | 5.1             | V          |  |

| V <sub>OVP</sub>  | trip point                                            | OFF Threshold                                                          |       | 4.75           | 4.88 | 4.99            | V          |  |

| STEP-UP           | DC-DC CONVERTER SPECIFIC                              | ATIONS                                                                 |       |                |      |                 |            |  |

| R <sub>PMOS</sub> | PMOS switch on-resistance                             | I <sub>PMOS</sub> = 1 A                                                |       |                | 85   |                 | <b>~</b> 0 |  |

| R <sub>NMOS</sub> | NMOS switch on-resistance                             | I <sub>NMOS</sub> = 1 A                                                |       |                | 65   |                 | mΩ         |  |

|                   |                                                       |                                                                        |       | -12%           | 1.7  | 12%             |            |  |

|                   | Outlieb surround Parit                                |                                                                        |       | -12%           | 1.9  | 12%             | •          |  |

| I <sub>CL</sub>   | Switch current limit                                  |                                                                        |       | -10%           | 2.5  | 10%             | Α          |  |

|                   |                                                       |                                                                        |       | -12%           | 3.1  | 12%             |            |  |

| $V_{TRIP}$        | NTC comparator trip threshold                         | Configuration Register, bit [1] = 1                                    |       | -6%            | 600  | 6%              | mV         |  |

| UVLO              | Undervoltage lockout threshold                        | Falling V <sub>IN</sub>                                                |       | 2.74           | 2.8  | 2.85            | V          |  |

| I <sub>NTC</sub>  | NTC current                                           |                                                                        |       |                | 75   | 6%              | μA         |  |

| $V_{IVFM}$        | Input voltage flash monitor trip threshold            |                                                                        |       | -3.2%          | 2.9  | 3.2%            | V          |  |

| $f_{\sf SW}$      | Switching frequency                                   | 2.5 V ≤ V <sub>IN</sub> ≤ 5.5 V                                        |       | 3.72           | 4    | 4.28            | MHz        |  |

| IQ                | Quiescent supply current                              | Device not switching Pass M                                            | ode   |                | 0.6  | 0.75            | mA         |  |

| I <sub>SD</sub>   | Shutdown supply current                               | Device disabled, EN = 0V<br>2.5 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V  |       |                | 0.1  | 1.3             | μΑ         |  |

| I <sub>SB</sub>   | Standby supply current                                | Device disabled, EN = 2 V<br>2.5 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V |       |                | 2.5  | 4               | μΑ         |  |

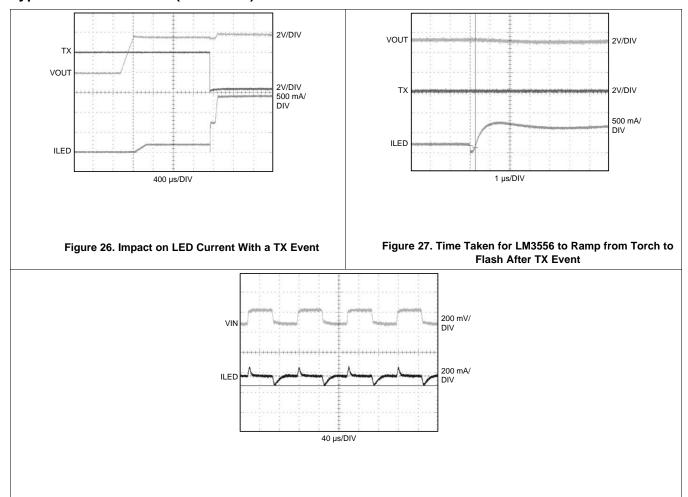

| t <sub>TX</sub>   | Flash-to-torch LED current settling time              | TX low to high,<br>I <sub>LED</sub> = 1.5 A to 46.88 mA                |       |                | 4    |                 | μs         |  |

| I <sub>OS</sub>   | I <sub>LED</sub> overshoot in external indicator mode | 0 mA to I <sub>TORCH</sub>                                             |       |                | 8%   |                 |            |  |

| ENABLE,           | , STROBE, TORCH, TX VOLTAG                            | E SPECIFICATIONS                                                       |       |                |      |                 |            |  |

| V <sub>IL</sub>   | Input logic low                                       |                                                                        |       | 0              |      | 0.4             | ,,,        |  |

| V <sub>IH</sub>   | Input logic high                                      | 2.5 V ≤ V <sub>IN</sub> ≤ 5.5 V                                        |       | 1.2            |      | V <sub>IN</sub> | V          |  |

|                   | PATIBLE INTERFACE SPECIFIC                            | ATIONS (SCL, SDA)                                                      |       | 1              |      | -               |            |  |

| V <sub>IL</sub>   | Input logic low                                       |                                                                        |       | 0              |      | 0.4             | .,         |  |

| V <sub>IH</sub>   | Input logic high                                      | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 4.2 \text{ V}$             |       | 1.2            |      | V <sub>IN</sub> | V          |  |

| V <sub>OL</sub>   | Output logic low                                      | I <sub>LOAD</sub> = 3 mA                                               |       |                |      | 400             | mV         |  |

|                   |                                                       |                                                                        |       | 1              |      |                 |            |  |

<sup>(1)</sup> Minimum and maximum limits are specified by design, test, or statistical analysis. Typical numbers are not verified, but do represent the most likely norm. Unless otherwise specified, conditions for typical specifications are:  $V_{IN} = 3.6 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ . All voltages are with respect to the potential at the GND pin.

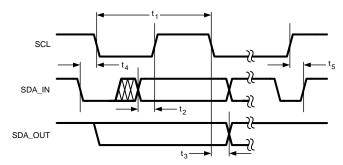

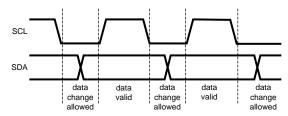

# 6.6 Timing Requirements

|                |                                          | MIN | NOM MAX | UNIT |

|----------------|------------------------------------------|-----|---------|------|

| t <sub>1</sub> | SCL clock frequency                      | 2.4 |         | μs   |

| t <sub>2</sub> | Data in setup time to SCL high           | 100 |         | ns   |

| t <sub>3</sub> | Data out stable after SCL low            | 0   |         | ns   |

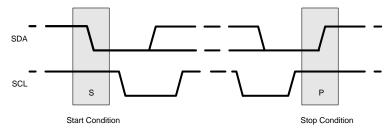

| t <sub>4</sub> | SDA low setup time to SCL low (start)    | 100 |         | ns   |

| t <sub>5</sub> | SDA high hold time after SCL high (stop) | 100 |         | ns   |

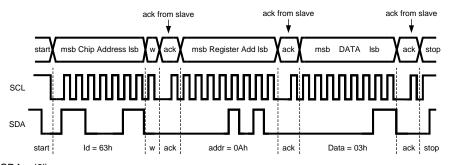

Figure 1. I<sup>2</sup>C-Compatible Timing Diagram

# 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

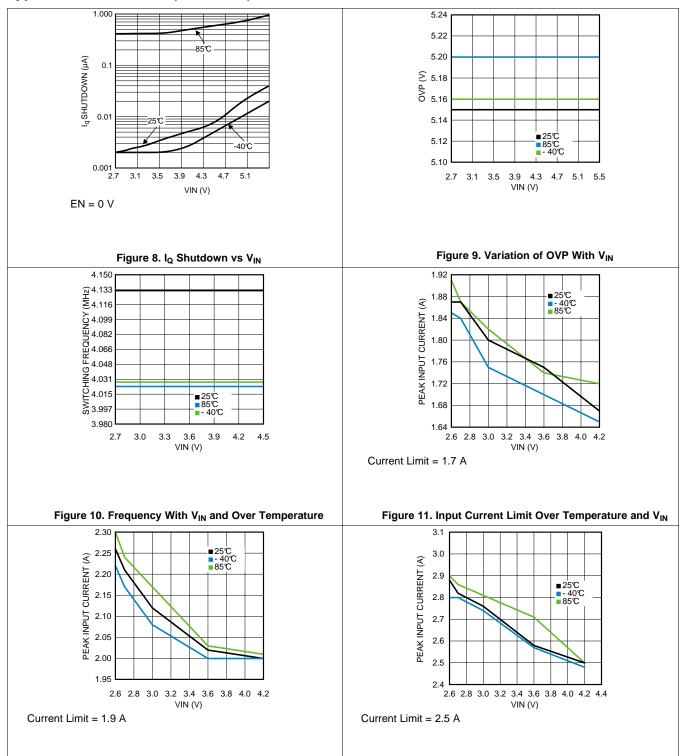

# **Typical Characteristics (continued)**

Submit Documentation Feedback

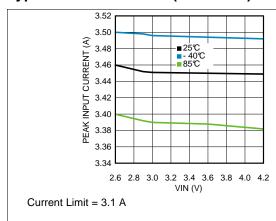

Figure 12. Input Current Limit Over Temperature and  $V_{\text{IN}}$

Figure 13. Input Current Limit Over Temperature and  $V_{\text{IN}}$

# **Typical Characteristics (continued)**

Figure 14. Input Current Limit Over Temperature and VIN

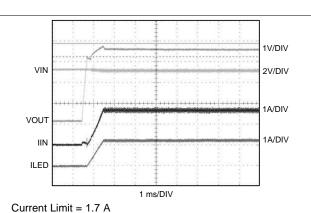

Odificial Ellille = 1.7 A

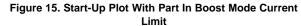

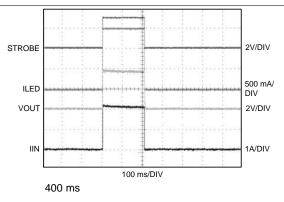

Figure 16. Strobe With Edge-Triggered Signal

Figure 17. Strobe With Level-Triggered Signal

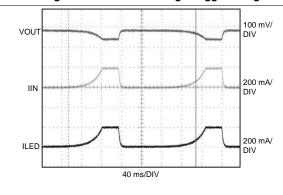

Figure 18. Internal Indicator Operation

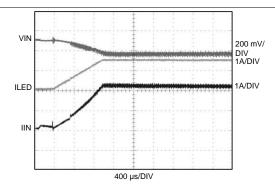

Figure 19. Input Voltage Flash Monitor Report Mode With Default Settings

Copyright © 2011–2015, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Submit Documentation Feedback

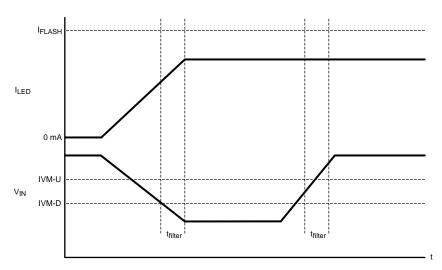

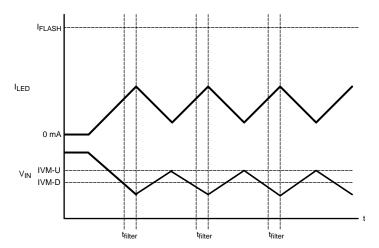

Figure 24. Input Voltage Flash Monitor, Up and Down Mode

Copyright © 2011–2015, Texas Instruments Incorporated

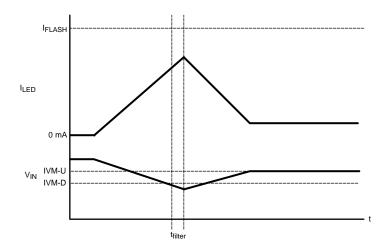

Figure 25. Input Voltage Flash Monitor, Up and Down Mode

# **Typical Characteristics (continued)**

Figure 28. Transient Plot When  $V_{IN}$  Stepped from 3  $\rightarrow$  2.9 V

# 7 Detailed Description

#### 7.1 Overview

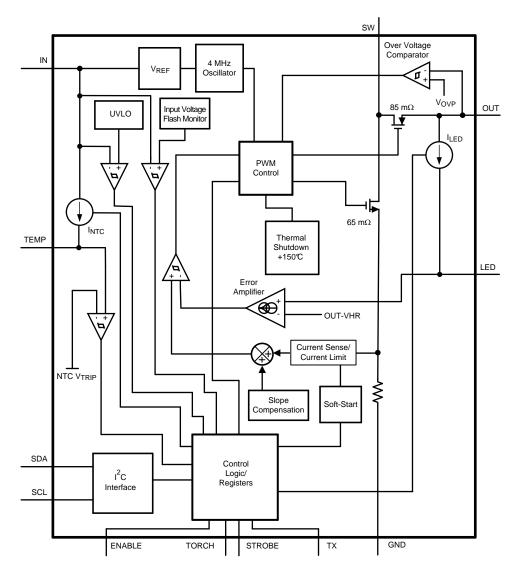

The LM3556 is a high-power white LED flash driver capable of delivering up to 1.5 A into a single high-powered LED. The device incorporates a 4-MHz constant-frequency synchronous current-mode PWM boost converter, and a single high-side current source to regulate the LED current over the 2.5-V to 5.5-V input voltage range.

The LM3556 PWM converter switches and maintains at least  $V_{HR}$  across the current source (LED). This minimum headroom voltage ensures that the current source remains in regulation. If the input voltage is above the LED voltage plus current source headroom voltage, the device does not switch, and turns the PFET on continuously (Pass Mode). In Pass Mode the difference between  $(V_{IN} - I_{LED} \times R_{PMOS})$  and the voltage across the LED is dropped across the current source.

The LM3556 has three logic inputs including a hardware flash enable (STROBE), a hardware torch enable (TORCH) used for external torch mode control and custom LED indication waveforms, and a flash interrupt input (TX) designed to interrupt the flash pulse during high battery-current conditions. All three logic inputs have internal  $300-k\Omega$  (typical) pulldown resistors to GND.

Additional features of the LM3556 include an internal comparator for LED thermal sensing via an external NTC thermistor and an input voltage monitor that can reduce the Flash current (during low V<sub>IN</sub> conditions).

Control of the LM3556 is done via an  $I^2C$ -compatible interface. This includes adjustment of the flash and torch current levels, changing the flash time-out duration, changing the switch current limit, and enabling the NTC block. Additionally, there are flag and status bits that indicate flash current time-out, LED overtemperature condition, LED failure (open or short), device thermal shutdown, TX interrupt, and  $V_{IN}$  undervoltage conditions.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Power-Amplifier Synchronization (TX)

The TX pin is a power-amplifier synchronization input. It is designed to reduce the flash LED current and thus limit the battery current during high battery-current conditions such as PA transmit events. When the LM3556 is engaged in a flash event, and the TX pin is pulled high, the LED current is forced into Torch Mode at the programmed torch current setting or shutdown. If the TX pin is then pulled low before the flash pulse terminates, the LED current returns to the previous flash current level. At the end of the flash time-out, whether the TX pin is high or low, the LED current turns off. The polarity of the TX input can be changed from active high to active low through the *Configuration Register (0x07)* and can be disabled/enabled by setting the TX Enable bit in the *Enable Register (0x0A)* to a '0'.

#### 7.3.2 Input Voltage Flash Monitor (IVFM)

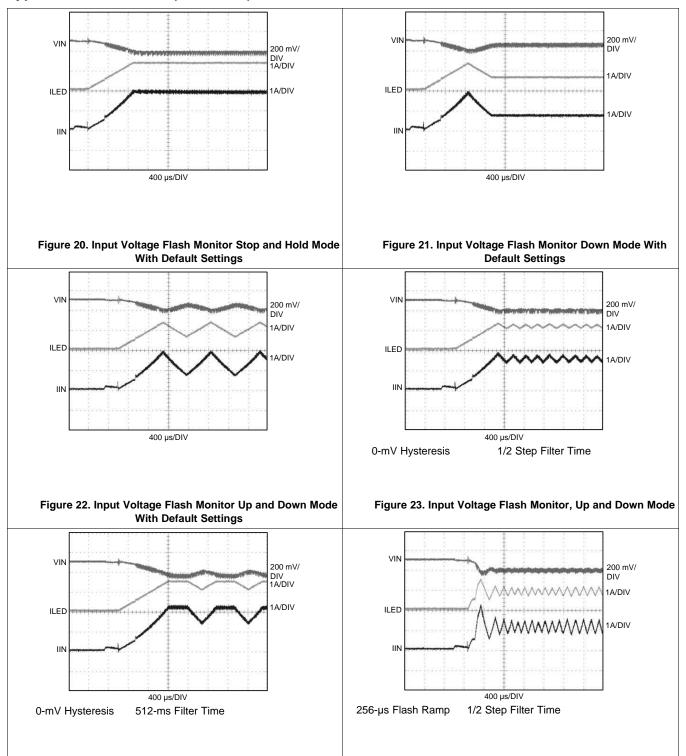

The LM3556 device can adjust the flash current based upon the voltage level present at the IN pin using an input voltage flash monitor. Two adjustable thresholds (IVM-D and IVM-U) ranging from 2.9 V to 3.6 V in 100-mV steps, and four different usage modes (Report Mode, Stop and Hold Mode, Adjust Down Only Mode, Adjust Up and Down Mode), are provided. The Flags Register has the fault flag set when the input voltage crosses the IVM-D value. In Report Mode, apart from the fault flag triggering, no action is taken on the LED current.

Copyright © 2011–2015, Texas Instruments Incorporated

## **Feature Description (continued)**

Additionally, the IVM-D threshold sets the input voltage boundary that forces the LM3556 to either stop ramping the flash current during start-up (Stop and Hold Mode) or to start decreasing the LED current during the flash (Adjust Down Only Mode and Adjust Down and Up Mode). The IVM-U threshold sets the input voltage boundary that forces the LM3556 to start ramping the flash current back up towards the target (Adjust Up and Down Mode). The IVM-U threshold is equal to the IVM-D value plus the programmed hysteresis value also stored in the Input Voltage Flash Monitor (IVFM) Mode Register (0x01).

To help prevent a premature current reduction, the LM3556 has four different filter timers that start once the input voltage decreases below the IVM-D line. These filter times are set in the Silicon Revision and Filter Time Register (0x00). For more information, refer to Input Voltage Flash Monitor (IVFM) Mode Register (0x01) and Configuration Register (0x07).

#### 7.3.3 Fault Protections

#### 7.3.3.1 Fault Operation

Upon entering a fault condition, the LM3556 sets the appropriate flag in the *Flags Register (0x0B)*, placing the part into standby by clearing and locking the Torch Enable bit (TEN), Pre-Charge bit, and Mode bits (M1, M0) in the *Enable Register (0x0A)*, until the *Flags Register (0x0B)* is read back via I<sup>2</sup>C.

#### 7.3.3.2 Flash Time-Out

The Flash time-out period sets the amount of time that the flash current is being sourced from the current source (LED). The LM3556 has 8 time-out levels ranging 100 ms to 800 ms in 100-ms steps. The flash time-out period is controlled in the *Flash Features Register* (0x08). Flash time-out only applies to the Flash Mode operation. The mode bits are cleared upon a flash time-out.

#### 7.3.3.3 Overvoltage Protection (OVP)

The output voltage is limited to typically 5 V (see  $V_{OVP}$  in *Electrical Characteristics*. In situations such as an open LED, the LM3556 device raises the output voltage in order to keep the LED current at its target value. When  $V_{OUT}$  reaches 5 V (typical), the overvoltage comparator trips and turns off the internal NFET. When  $V_{OUT}$  falls below the  $V_{OVP}$  off threshold, the LM3556 begins switching again. The mode bits in the *Enable Register (0x0A)* are not cleared upon an OVP.

#### 7.3.3.4 Current Limit

The LM3556 features selectable inductor-current limits that are programmable through the *Flash Features Register (0x08)* of the  $I^2C$ -compatible interface. When the inductor-current limit is reached, the LM3556 terminates the charging phase of the switching cycle.

Because the current limit is sensed in the NMOS switch, there is no mechanism to limit the current when the device operates in Pass Mode. In Boost Mode or Pass Mode, if  $V_{OUT}$  falls below 2.3 V, the device stops switching, and the PFET operates as a current source limiting the current to 200 mA. This prevents damage to the LM3556 and excessive current draw from the battery during output short-circuit conditions. The mode bits in the *Enable Register (0x0A)* are not cleared upon a current limit event.

Pulling additional current from the V<sub>OUT</sub> node during normal operation is not recommended.

# 7.3.3.5 NTC Thermistor Input (TEMP)

The TEMP pin serves as a threshold detector for negative temperature coefficient (NTC) thermistors. It interrupts the LED current when the voltage at TEMP goes below the programmed threshold. The NTC threshold voltage is adjustable from 200 mV to 900 mV in 100-mV steps. The NTC current is adjustable from 25 μA to 100 μA in 25-μA steps. When an overtemperature event is detected, the LM3556 can be set to force the LED current from Flash Mode into Torch Mode or into shutdown. These settings are adjusted via the *NTC Settings Register (0x02)*, and the NTC detection circuitry can be enabled or disabled via the *Enable Register (0x0A)*. If enabled, the NTC block turns on and off during the start and stop of a flash, torch, or indicator event. The NTC mode of operation is set by adjusting the NTC Mode bit in the *Configuration Register (0x07)*. See *NTC Settings Register (0x02)* for more details. The mode bits in the *Enable Register (0x0A)* are cleared upon an NTC event.

## Feature Description (continued)

#### 7.3.3.6 Undervoltage Lockout (UVLO)

The LM3556 has an internal comparator that monitors the voltage at IN and forces the LM3556 into shutdown if the input voltage drops to 2.8 V. If the UVLO monitor threshold is tripped, the UVLO flag bit is set in the Flags Register (0x0B). If the input voltage rises above 2.8 V, the device is available for operation until there is an I<sup>2</sup>C read command initiated for the Flags Register (0x0B). Upon a read, the Flags Register is cleared, and normal operation can resume. This feature can be disabled by writing a '0' to the UVLO EN bit in the Input Voltage Flash Monitor (IVFM) Mode Register (0x01). The mode bits in the Enable Register (0x0A) are cleared upon a UVLO event.

#### 7.3.3.7 Thermal Shutdown ( $T_{SD}$ )

When the LM3556 device's die temperature reaches 150°C, the boost converter shuts down, and the NFET and PFET turn off, as does the current source (LED). When the thermal shutdown threshold is tripped, a '1' gets written to the corresponding bit of the Flags Register (0x0B) (T<sub>SD</sub> bit), and the device goes into standby. The LM3556 can only restart after the Flags Register (0x0B) is read, clearing the fault flag. Upon restart, if the die temperature is still above 150°C, the device resets the fault flag and re-enters standby. The mode bits in the Enable Register (0x0A) are cleared upon a T<sub>SD</sub>.

# 7.3.3.8 LED and/or V<sub>OUT</sub> Fault

The LED fault flag in the Flags Register (0x0B) reads back a '1' if the part is active in Flash Mode or Torch Mode, and the LED output or the V<sub>OUT</sub> node experiences a short condition. The LM3556 determines an LED open condition if the OVP threshold is crossed at the OUT pin while the device is in Flash or Torch Mode. An LED short condition is determined if the voltage at LED goes below 500 mV (typical) while the device is in either Torch or Flash Mode. There is a delay of 256-µs deglitch time before the LED flag is valid, and 2.048 ms before the V<sub>OUT</sub> flag is valid. This delay is the time between when the flash or torch current is triggered and when the LED voltage and the output voltage are sampled. The LED flag can only be reset to '0' by removing power to the LM3556, or by reading back the Flags Register (0x0B). The mode bits in the Enable Register (0x0A) are cleared upon an LED and/or V<sub>OUT</sub> fault.

# 7.4 Device Functional Modes

#### 7.4.1 Start-Up (Enabling The Device)

Turnon of the LM3556 Torch and Flash Modes can be done through the *Enable Register (0x0A)*. On start-up, when V<sub>OUT</sub> is less than V<sub>IN</sub> the internal synchronous PFET turns on as a current source and delivers 200 mA (typical) to the output capacitor. During this time the current source (LED) is off. When the voltage across the output capacitor reaches 2.2 V (typical) the current source turns on. At turnon the current source steps through each FLASH or TORCH level until the target LED current is reached. This gives the device a controlled turnon and limits inrush current from the V<sub>IN</sub> supply.

#### 7.4.2 Pass Mode

The LM3556 starts up in Pass Mode and stays there until Boost Mode is needed to maintain regulation. If the voltage difference between V<sub>OUT</sub> and V<sub>LED</sub> falls below V<sub>HR</sub>, the device switches to Boost Mode. In Pass Mode the boost converter does not switch, and the synchronous PFET fully turns on bringing  $V_{OUT}$  up to  $(V_{IN} - I_{LED} \times I_{CED})$ R<sub>PMOS</sub>). In Pass Mode the inductor current is not limited by the peak current limit. In this situation the output current must be limited to 2 A.

#### 7.4.3 Flash Mode

In Flash Mode, the LED current source (LED) provides 16 target current levels from 93.75 mA to 1500 mA. The Flash currents are adjusted via the Current Control Register (0x09). Flash mode is activated by the Enable Register (0x0A), or by pulling the STROBE pin HIGH. Once the Flash sequence is activated the current source (LED) ramps up to the programmed Flash current by stepping through all current steps until the programmed current is reached.

When the device is enabled in Flash Mode through the Enable Register, all mode bits in the Enable Register are cleared after a flash time-out event.

Submit Documentation Feedback

## **Device Functional Modes (continued)**

Data can be written to the mode bits (bits[1:0]) in *Enable Register (0x0A)* only after the flash has ramped down to the desired value, and  $V_{OUT}$  has decayed.

Table 1 shows the I<sup>2</sup>C commands and the state of the mode bits, if the STROBE pin is used to enable the Flash Mode.

Table 1. I<sup>2</sup>C Commands and the State of the Mode Bits

| MODE CHANGE REQUIRED                                                                                       | ENABLE AND CONFIGURATION<br>REGISTER SETTING (0x0A=Enable<br>Register, 0x07=Configuration Register) | STATUS OF MODE BITS IN THE ENABLE REGISTER AFTER A FLASH                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Using edge-triggered STROBE to Flash                                                                       | 0x0A = 0x23; 0x07 = 0x78 (default setting)                                                          | Mode bits are cleared after a single flash. To reflash, 0x23 has to be written to 0x0A.                                                                                                                                                                                                  |

| Using level-triggered STROBE to Flash                                                                      | 0x0A = 0x23; 0x07 = 0xF8                                                                            | Mode bits are cleared after a single flash. To reflash, 0x23 has to be written to 0x0A.                                                                                                                                                                                                  |

| Part is required to go from external TORCH<br>Mode to external STROBE mode using<br>edge-triggered STROBE  | 0x0A = 0x33; 0x07 = 0x78 (default setting)                                                          | Mode bits are cleared after a single flash. To reflash, 0x33 has to be written to 0x0A.                                                                                                                                                                                                  |

| Part is required to go from external TORCH<br>Mode to external STROBE mode using<br>Level Triggered STROBE | 0x0A = 0x33; 0x0 7= 0xF8                                                                            | Mode bits are cleared only if the part has an internal flash time-<br>out event happening before the STROBE level goes low. To re-<br>flash, 0x33 has to be written to 0x0A. If the STROBE level goes<br>low before an internal flash time-out event, then mode bits are not<br>cleared. |

#### 7.4.4 Torch Mode

In Torch Mode, the current source (LED) is programmed via the *Current Control Register (0x09)*. Torch Mode is activated by the *Enable Register (0x0A)* or by the hardware TORCH input. Once the Torch Mode is enabled the current source ramps up to the programmed torch current level. The ramp-up and ramp-down times are independently adjustable via the *Torch Ramp Time Register (0x06)*. Torch Mode is not affected by flash timeout.

#### 7.4.5 Indicator Mode

This mode has two options: the Internal Indicator Mode and the External Indicator mode. Both these modes are activated by the Configuration Register (0x07) in addition to the *Enable Register (0x0A)*.

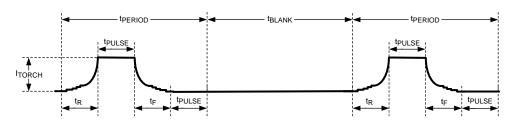

In the Internal Indicator Mode, the current source (LED) can be programmed to 8 different intensity levels, with current values being 1/8th the values in *Current Control Register (0x09)* bits [6:4]. The ramp-up, ramp-down, the pulse time, number of blanks and periods of the desired output current can be independently controlled via the *Indicator Ramp Time Indicator (0x03)*, *Indicator Blinking Register (0x04)* and the *Indicator Period Count Register (0x05)*.

In the External Indicator Mode, the current source (LED) is controlled via the TORCH pin. An external PWM signal can be input to the part via the TORCH pin to choose any one of the 8 available intensity settings (bits [6:4] of the *Current Control Register (0x09)*) for the current source (LED).

## 7.5 Programming

## 7.5.1 I<sup>2</sup>C-Compatible Interface

#### 7.5.1.1 Data Validity

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

Figure 29. Data Validity Diagram

A pullup resistor between the controller's VIO line and SDA must be greater than [(VIO –  $V_{OL}$ ) / 3mA] to meet the  $V_{OL}$  requirement on SDA. Using a larger pullup resistor results in lower switching current with slower edges, while using a smaller pullup results in higher switching currents with faster edges.

#### 7.5.1.2 Start and Stop Conditions

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as the SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 30. Start and Stop Conditions

# 7.5.1.3 Transferring Data

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LM3556 pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The LM3556 generates an acknowledge after each byte is received. There is no acknowledge created after data is read from the LM3556.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3556 7-bit address is 0x63. For the eighth bit, a '0' indicates a WRITE and a '1' indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

# **Programming (continued)**

W = Write (SDA = '0')

R = Read (SDA = '1')

Ack = Acknowledge (SDA Pulled Down By Either Master Or Slave)

ID= Chip Address, 63h For LM3556

Figure 31. Write Cycle

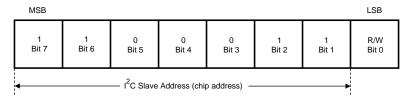

# 7.5.1.4 PC-Compatible Chip Address

The device address for the LM3556 is 1100011 (63). After the START condition, the  $I^2C$ -compatible master sends the 7-bit address followed by an eighth read or write bit (R/W). R/W = 0 indicates a WRITE and R/W = 1 indicates a READ. The second byte following the device address selects the register address to which the data will be written. The third byte contains the data for the selected register.

Figure 32. I<sup>2</sup>C-Compatible Device Address

#### 7.5.1.5 Transferring Data

Every byte on the SDA line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data must be followed by an acknowledge bit (ACK). The acknowledge related clock pulse (9th clock pulse) is generated by the master. The master releases SDA (HIGH) during the 9th clock pulse. The LM3556 pulls down SDA during the 9th clock pulse, signifying an acknowledge. An acknowledge is generated after each byte has been received.

#### 7.6 Register Maps

#### 7.6.1 Register Descriptions

| REGISTER NAME                             | INTERNAL HEX ADDRESS | POWER ON/RESET VALUE |

|-------------------------------------------|----------------------|----------------------|

| Silicon Revision and Filter Time Register | 0x00                 | 0x04                 |

| IVFM Mode Register                        | 0x01                 | 0x80                 |

| NTC Settings Register                     | 0x02                 | 0x12                 |

| Indicator Ramp Time Register              | 0x03                 | 0x00                 |

| Indicator Blinking Register               | 0x04                 | 0x00                 |

| Indicator Period Count Register           | 0x05                 | 0x00                 |

| Torch Ramp Time Register                  | 0x06                 | 0x00                 |

| Configuration Register                    | 0x07                 | 0x78                 |

| Flash Features Register                   | 0x08                 | 0xD2                 |

| Current Control Register                  | 0x09                 | 0x0F                 |

| Enable Register                           | 0x0A                 | 0x00                 |

| Flags Register                            | 0x0B                 | 0x00                 |

#### 7.6.1.1 Silicon Revision and Filter Time Register (0x00)

Table 2. Silicon Revision and Filter Time Register Description

| Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3                                                                             | Bit 2 | Bit 1                                   | Bit 0 |

|-------|-------|-------|--------------|-----------------------------------------------------------------------------------|-------|-----------------------------------------|-------|

| RFU   | RFU   | RFU   | '00' = 1/2 c | FM Filter Times of the Current Step Time '01' = 256 μs '10' =512 μs 11' = 1024 μs |       | ilable for Silicon<br>urrent Value = '′ |       |

## 7.6.1.2 Input Voltage Flash Monitor (IVFM) Mode Register (0x01)

Table 3. Input Voltage Flash Monitor (IVFM) Mode Register Description

| Bit 7                    | Bit 6                         | Bit 5 | Bit 4 | Bit 3                                                                                                                                            | Bit 2 | Bit 1                                    | Bit 0                                                                 |

|--------------------------|-------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------|-----------------------------------------------------------------------|

| 1 = UVLO EN<br>(default) | 00 = 50 m<br>01 = 1<br>10 = 1 | •     |       | M-D (Down) Thresh<br>000 = 2.9 V (default<br>001 = 3 V<br>010 = 3.1 V<br>011 = 3.2 V<br>100 = 3.3 V<br>101 = 3.4 V<br>110 = 3.5 V<br>111 = 3.6 V |       | 00 = Report I<br>01 = Stop ar<br>10 = Do | just Mode<br>Mode (default)<br>nd Hold Mode<br>wn Mode<br>d Down Mode |

- 00 = Report Mode Sets IVFM flag in Flags Register upon crossing IVM-D line Only. Does not adjust current.

- **01 = Stop and Hold Mode** Stops current ramp and holds the level for the remaining flash if V<sub>IN</sub> crosses IVM-D Line. Sets IVFM flag in Flags Register upon crossing IVM-D line.

- 10 = Down Mode Adjusts current down if V<sub>IN</sub> crosses IVM-D Line and stops decreasing once V<sub>IN</sub> rises above the IVM-D line plus the IVFM hystersis setting. The LM3556 decreases the current throughout the flash pulse anytime the input voltage falls below the IVM-D line, and not just once. The flash current does not increase again until the next flash. Sets IVFM flag in Flags Register upon crossing IVM-D Line.

- 11 = Up and Down Mode Adjusts current down if V<sub>IN</sub> crosses IVM-D Line and adjusts current up if V<sub>IN</sub> rises above the IVM-D line plus the IVFM hystersis setting. In this mode, the current continually adjusts with the rising and falling of the input voltage throughout the entire flash pulse. Sets IVFM flag in Flags Register upon crossing IVM-D Line.

- UVLO EN If enabled and V<sub>IN</sub> drops below 2.8 V, the LM3556 enters standby and sets the UVLO flag in the Flags Register. Enabled = '1', Disabled = '0' IVM-U = IVM-D + IVFM Hysteresis

Copyright © 2011–2015, Texas Instruments Incorporated

Figure 33. Stop and Hold Mode

Figure 34. Adjust Down-Only Mode

Figure 35. Adjust Up and Down Mode

# 7.6.1.3 NTC Settings Register (0x02)

**Table 4. NTC Settings Register Description**

| Bit 7 | Bit 6 | Bit 5                                                                           | Bit 4 | Bit 3                                                                                                                                                    | Bit 2 | Bit 1                          | Bit 0                                                   |

|-------|-------|---------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------|---------------------------------------------------------|

| RFU   | RFU   | NTC Event Level 0 = Go to standby (default) 1 = Reduce to minimum torch current |       | NTC Trip Threshold<br>000 = 200 mV<br>001 = 300 mV<br>010 = 400 mV<br>011 = 50 mV<br>00 = 600 mV (defaul<br>101 = 700 mV<br>110 = 800 mV<br>111 = 900 mV |       | 00 = 3<br>01 = 3<br>10 = 75 μ. | urrent Level<br>25 μΑ<br>50 μΑ<br>A (default)<br>100 μΑ |

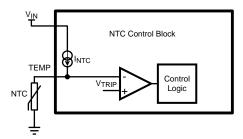

Figure 36. NTC Control Block

The TEMP node is connected to an NTC resistor as shown in Figure 36 above. A constant current source from the input is connected to this node. Any change in the voltage because of a change in the resistance of the NTC resistor is compared to a set  $V_{TRIP}$ . The trip thresholds are selected by Bits[4:2] of the NTC Register. The output of the Control Logic upon an NTC trip is selected through Bit[5].

# 7.6.1.4 Indicator Ramp Time Indicator (0x03)

**Table 5. Indicator Ramp Time Indicator Description**

| Bit 7 | Bit 6 | Bit 5                 | Bit 4          | Bit 3                 | Bit 2                                      | Bit 1          | Bit 0 |  |  |

|-------|-------|-----------------------|----------------|-----------------------|--------------------------------------------|----------------|-------|--|--|

| RFU   | RFU   | Indic                 | ator Ramp-Up T | ime (t <sub>R</sub> ) | Indicator Ramp-Down Time (t <sub>F</sub> ) |                |       |  |  |

|       |       | 000 = 16 ms (default) |                |                       | 000 = 16 ms (default)                      |                |       |  |  |

|       |       |                       | 001 = 32  ms   |                       | 001 = 32 ms                                |                |       |  |  |

|       |       |                       | 010 = 64  ms   |                       | 010 = 64  ms                               |                |       |  |  |

|       |       | 011 = 128 ms          |                |                       | 011 = 128 ms                               |                |       |  |  |

|       |       |                       | 100 = 256  ms  |                       | 100 = 256 ms                               |                |       |  |  |

|       |       |                       | 101 = 512 ms   |                       | 101 = 512 ms                               |                |       |  |  |

|       |       | 110 = 1.024 s         |                |                       | 110 = 1.024 s                              |                |       |  |  |

|       |       | 111 = 2.048 s         |                |                       |                                            | 111 = 2.048  s |       |  |  |

Product Folder Links: LM3556

# 7.6.1.5 Indicator Blinking Register (0x04)

# **Table 6. Indicator Blinking Register Description**

| Bit 7 | Bit 6           | Bit 5     | Bit 4 | Bit 3                            | Bit 2    | Bit 1     | Bit 0 |  |  |

|-------|-----------------|-----------|-------|----------------------------------|----------|-----------|-------|--|--|

|       | N <sub>BL</sub> | ANK       |       | Pulse Time (t <sub>PULSE</sub> ) |          |           |       |  |  |

|       | 0000 = 0        | (default) |       |                                  | 0000 = 0 | (default) |       |  |  |

|       | 0001            | = 1       |       |                                  | 0001 =   | 32 ms     |       |  |  |

|       | 0010            | ) = 2     |       |                                  | 0010 =   | 64 ms     |       |  |  |

|       | 0011            | = 3       |       |                                  | 0011 =   | 92 ms     |       |  |  |

|       | 0100            | ) = 4     |       |                                  | 0100 =   | 128 ms    |       |  |  |

|       | 0101            | = 5       |       | 0101 = 160 ms                    |          |           |       |  |  |

|       | 0110            | ) = 6     |       | 0110 = 196 ms                    |          |           |       |  |  |

|       | 0111            | = 7       |       | 0111 = 224 ms                    |          |           |       |  |  |

|       | 1000            | 8 = 0     |       | 1000 = 256 ms                    |          |           |       |  |  |

|       | 1001            | = 9       |       | 1001 = 288 ms                    |          |           |       |  |  |

|       | 1010            | = 10      |       | 1010 = 320 ms                    |          |           |       |  |  |

|       | 1011            | = 11      |       | 1011 = 352 ms                    |          |           |       |  |  |

|       | 1100            | = 12      |       | 1100 = 384 ms                    |          |           |       |  |  |

|       | 1101            | = 13      |       | 1101 = 416 ms                    |          |           |       |  |  |

|       | 1110            | = 14      |       | 1110 = 448 ms                    |          |           |       |  |  |

|       | 1111            | = 15      |       |                                  | 1111 =   | 480 ms    |       |  |  |

# 7.6.1.6 Indicator Period Count Register (0x05)

**Table 7. Indicator Period Count Register Description**

|       |       |       | 1     |       | 1     |                                                                                                           |       |

|-------|-------|-------|-------|-------|-------|-----------------------------------------------------------------------------------------------------------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                                                                                                     | Bit 0 |

| RFU   | RFU   | RFU   | RFU   | RFU   |       | NPERIOD<br>000 = 0 (default)<br>001 = 1<br>010 = 2<br>011 = 3<br>100 = 4<br>101 = 5<br>110 = 6<br>111 = 7 |       |

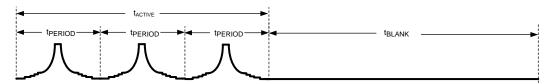

Figure 37. Indicator Usage

- 1. Number of periods  $(t_{PERIOD} = t_R + t_F + t_{PULSE} \times 2)$

- 2. Active Time  $(t_{ACTIVE} = t_{PERIOD} \times N_{PERIOD})$

- 3. Blank Time ( $t_{BLANK} = t_{ACTIVE} \times N_{BLANK}$ )

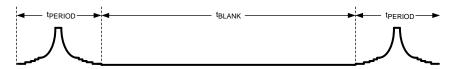

Figure 38. Single Pulse With Dead Time

Figure 39. Multiple Pulse With Dead Time

## 7.6.1.7 Torch Ramp Time Register (0x06)

**Table 8. Torch Ramp Time Register**

| Bit 7 | Bit 6 | Bit 5 | Bit 4                                                                                                                                               | Bit 3 | Bit 2 | Bit 1                                                                                                                       | Bit 0 |

|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------|-------|

| RFU   | RFU   |       | orch Ramp-Up T<br>000 = 16 ms (defa<br>001 = 32 ms<br>010 = 64 ms<br>011 = 128 ms<br>100 = 256 ms<br>101 = 512 ms<br>110 = 1.024 s<br>111 = 2.048 s | ault) |       | rch Ramp-Down 000 = 16 ms (defar 001 = 32 ms 010 = 64 ms 011 = 128 ms 100 = 256 ms 101 = 512 ms 110 = 1.024 s 111 = 2.048 s |       |

#### 7.6.1.8 Configuration Register (0x07)

**Table 9. Configuration Register Description**

| Bit 7                    | Bit 6                        | Bit 5                        | Bit 4                        | Bit 3                       | Bit 2                       | Bit 1                    | Bit 0                          |

|--------------------------|------------------------------|------------------------------|------------------------------|-----------------------------|-----------------------------|--------------------------|--------------------------------|

| Strobe Usage<br>0 = Edge | Strobe Pin<br>Polarity       | Torch Pin<br>Polarity        | TX Pin<br>Polarity           | TX Event Level<br>0 = Off   | IVFM Enable<br>0 = Disabled | NTC Mode<br>0 = Normal   | Indicator Mode<br>0 = Internal |

| (default)                | 0 = Active Low<br>1 = Active | 0 = Active Low<br>1 = Active | 0 = Active Low<br>1 = Active | 1 = Torch Current (default) | (default)<br>1 = Enabled    | (default)<br>1 = Monitor | (default)<br>1 = External      |

| 1 = Level                | High (default)               | High (default)               | High (default)               | ,                           |                             |                          |                                |

**Strobe Usage** Level or edge. Flash follows strobe timing if Level and internal timing if edge.

Strobe Polarity Active high or active low select.

Torch Polarity Active high or active low select.

**TX Polarity** Active high or active low select.

**TX Event Level** Transition to torch current level or off setting if TX event occurs.

The TX Event Level off setting is designed to force a shutdown only during a flash event. When Torch or Indicator Mode is enabled, and a TX event occurs with the TX event level set to Off , the LM3556 does not shut down. The TX flag bit (bit7 in the Table 14) is set, and the mode bits (bit0 and bit1 in Table 12) get locked out until the fault register is cleared via an I<sup>2</sup>C read. Because a TX event is periodic and frequently occurring, clearing the fault register becomes more difficult. Depending on the I<sup>2</sup>C read/write speed and TX event frequency, it may be necessary to set the TX enable bit (bit6 in the Table 12) to a '0' before clearing the fault register to prevent future flag sets.

**IVFM Enable** Enables input voltage flash monitoring.

Indicator Mode Externally generated via TORCH pin or internally generated PWM.

#### 7.6.1.9 Flash Features Register (0x08)

#### **Table 10. Flash Features Register Description**

| Bit 7      | Bit 6                              | Bit 5                        | Bit 4                            | Bit 3 | Bit 2                        | Bit 1                        | Bit 0 |  |  |

|------------|------------------------------------|------------------------------|----------------------------------|-------|------------------------------|------------------------------|-------|--|--|

|            | urrent Limit                       |                              | Flash Ramp Tin                   | ne    | Flash Time-Out Time          |                              |       |  |  |

|            | 1.7 A<br>1.9 A                     | 000 = 256 μs<br>001 = 512 μs |                                  |       | 000 = 100 ms<br>001 = 200 ms |                              |       |  |  |

|            | 2.5 A                              | 010 = 1.024 ms (default)     |                                  |       | 010 = 300 ms (default)       |                              |       |  |  |

| 11 = 3.1 / | A (default)                        |                              | 011 = 2.048 ms<br>100 = 4.096 ms |       |                              | 011 = 400 ms<br>100 = 500 ms |       |  |  |

|            |                                    |                              |                                  | 6     | 101 = 600 ms                 |                              |       |  |  |

|            | 110 = 16.384 ms<br>111 = 32.768 ms |                              |                                  |       | 110 = 700 ms<br>111 = 800 ms |                              |       |  |  |

# 7.6.1.10 Current Control Register (0x09)

**Table 11. Current Control Register Description**

| Bit 7 | Bit 6                             | Bit 5                                                                                                                                                    | Bit 4 | Bit 3 | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 1                                                                                                                                                                                                  | Bit 0 |

|-------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| RFU   | 000 = 0<br>0<br>0<br>1<br>1<br>10 | Torch Current<br>46.88 mA (defaul<br>001 =93.75 mA<br>10 =140.63 mA<br>11 = 187.5 mA<br>00 =234.38 mA<br>01 = 281.25 mA<br>10 = 328.13 mA<br>111 =375 mA | t)    |       | 0000 = 0001 = 0010 = 2 0011 = 0100 = 2 0110 = 2 0110 = 2 0111 = 1000 = 8 1001 = 1100 = 1 1100 = 1 1100 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 = 1 1101 | 93.75 mA<br>187.5 mA<br>281.25 mA<br>281.25 mA<br>368.75 mA<br>562.5mA<br>562.5mA<br>565.25 mA<br>343.75 mA<br>937.5 mA<br>031.25 mA<br>1125 mA<br>1125 mA<br>1312.5 mA<br>406.25 mA<br>0 mA (default) |       |

#### 7.6.1.11 Enable Register (0x0A)

**Table 12. Enable Register Description**

| Bit 7                                                  | Bit 6                                            | Bit 5                                                            | Bit 4                                                           | Bit 3                                                    | Bit 2                                                                | Bit 1                         | Bit 0                                                    |

|--------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|----------------------------------------------------------|

| NTC Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | TX Pin Enable 0 = Disabled (default) 1 = Enabled | STROBE Pin<br>Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | TORCH Pin<br>Enable<br>0 = Disabled<br>(default)<br>1 = Enabled | PreCharge Mode Enable 0 = Normal (default) 1 = PreCharge | Pass-Mode<br>Only Enable<br>0 = Normal<br>(default)<br>1 = Pass Only | 00 = Stand<br>01 = Ir<br>10 = | s: M1, M0<br>lby (default)<br>ndicator<br>Torch<br>Flash |

NTC EN Enables NTC block.

**TX EN** Allows TX events to change the current.

**Strobe EN** Enables STROBE pin to start a flash event.

**Torch EN** Enables TORCH pin to start a torch event.

PreCharge Mode EN Enables Pass Mode to pre-charge the output cap.

Pass-Only Mode EN Only allows Pass Mode and disallows Boost Mode.

If Pass-Only Mode is enabled during any LED mode (Indicator, Torch or Flash), it remains enabled until the LM3556 enters the standby state regardless of whether the Pass-Only Mode bit is reset or not during the following command.

#### 7.6.1.11.1 Enable Register Mode Bits

#### 00-Standby Off

**01–Indicator** Sets Indicator Mode. Default Indicator Mode uses external pattern on TORCH pin.

**10–Torch** Sets Torch Mode with ramping. If Torch EN = 0, Torch starts after  $I^2$ C-compatible command.

**11–Flash** Sets Flash Mode with ramping. If Strobe EN = 0, Flash starts after  $I^2$ C-compatible command.

#### 7.6.1.11.2 Control Logic Delays

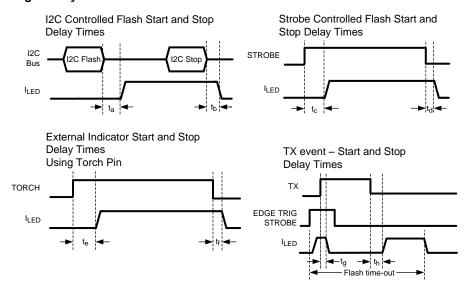

Figure 40. Control Logic Delays

**Table 13. Control Logic Delay Timing**

| DELAY          | EXPLANATION                                                                                                                    | TIME   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|--------|

| t <sub>a</sub> | Time for the LED current to start ramping up after an I <sup>2</sup> C Write command.                                          | 554 µs |

| t <sub>b</sub> | Time for the LED current to start ramping down after an I <sup>2</sup> C Stop command.                                         | 32 µs  |

| t <sub>c</sub> | Time for the LED current to start ramping up after the STROBE pin is raised high.                                              | 400 μs |

| t <sub>d</sub> | Time for the LED current to start ramping down after the STROBE pin is pulled low.                                             | 16 µs  |

| t <sub>e</sub> | Time for the LED current to start ramping up after the TORCH pin is raised high.                                               | 300 µs |

| t <sub>f</sub> | Time for the LED current to start ramping down after the TORCH pin is pulled low.                                              | 16 µs  |

| t <sub>g</sub> | Time for the LED current to start ramping down after the TX pin is pulled high.                                                | 3 µs   |

| t <sub>h</sub> | Time for the LED current to start ramping up after the TX pin is pulled low, provide the part has not timed out in Flash Mode. | 2 µs   |

Product Folder Links: LM3556

proprated Submit Documentation Feedback

#### 7.6.1.12 Flags Register (0x0B)

#### **Table 14. Flags Register Description**

| Bit 7                       | Bit 6                   | Bit 5               | Bit 4                      | Bit 3                     | Bit 2                                     | Bit 1                        | Bit 0                         |

|-----------------------------|-------------------------|---------------------|----------------------------|---------------------------|-------------------------------------------|------------------------------|-------------------------------|

| <b>TX Event</b> 0 = Default | NTC Trip<br>0 = Default | IVFM<br>0 = Default | <b>UVLO</b><br>0 = Default | <b>OVP</b><br>0 = Default | LED or VOUT<br>Short Fault<br>0 = Default | Thermal Shutdown 0 = Default | Flash Time-out<br>0 = Default |

TX Event Flag TX event occurred.

NTC Trip Flag NTC threshold crossed.

IVFM Flag IVFM block reported and/or adjusted LED current.

UVLO Fault UVLO threshold crossed.

**OVP Flag** Overvoltage Protection tripped. Open output capacitor or open LED.

LED Short Fault LED short detected.

Thermal Shutdown Fault LM3556 die temperature reached thermal shutdown value.

Time-Out Flag Flash Timer tripped.

#### **NOTE**

Faults require a read-back of the Flags Register to resume operation. Flags report an event occurred, but do not inhibit future functionality. A read-back of the Flags Register updates again if the fault or flags are still present upon a restart.

Copyright © 2011–2015, Texas Instruments Incorporated Product Folder Links: *LM3556*

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The LM3556 can drive one flash LED at currents up to 1.5 A. The 4-MHz DC-DC boost regulator allows for the use of small-value discrete external components.

## 8.2 Typical Application

Figure 41. LM3556 Typical Application

## 8.2.1 Design Requirements

Example requirements based on default register values are listed in Table 15:

DESIGN PARAMETER

EXAMPLE VALUE

Input Voltage Range

2.5 V to 5.5 V

Brightness Control

I2C Register

Output current

1.5 A

LED Configuration

1 Flash LED

Switching frequency

4 MHz (typical)

**Table 15. Design Parameters**

# 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Output Capacitor Selection

The LM3556 is designed to operate with a ceramic output capacitor of at least 10  $\mu$ F. When the boost converter is running, the output capacitor supplies the load current during the boost converter's on-time. When the NMOS switch turns off, the inductor energy is discharged through the internal PMOS switch, supplying power to the load and restoring charge to the output capacitor. This causes a sag in the output voltage during the on-time and a rise in the output voltage during the off-time. The output capacitor is therefore chosen to limit the output ripple to an acceptable level depending on load current and input/output voltage differentials and also to ensure the converter remains stable.

Larger capacitors (for example, a 22- $\mu$ F capacitor) or capacitors in parallel may be used if lower output voltage ripple is desired. To estimate the output voltage ripple, considering the ripple due to capacitor discharge ( $\Delta V_Q$ ) and the ripple due to the capacitors equivalent series resistance (ESR) ( $\Delta V_{ESR}$ ), use Equation 1 and Equation 2.

For continuous conduction mode, the output voltage ripple due to the capacitor discharge is:

$$\Delta V_{Q} = \frac{I_{LED} \times (V_{OUT} - V_{IN})}{f_{SW} \times V_{OUT} \times C_{OUT}}$$

(1)

The output voltage ripple due to the ESR of the output capacitor is found by:

$$\Delta V_{ESR} = R_{ESR} \times \left( \frac{I_{LED} \times V_{OUT}}{V_{IN}} \right) + \Delta I_{L}$$

where

$$\Delta I_{L} = \frac{V_{IN} \times \left( V_{OUT} - V_{IN} \right)}{2 \times f_{SW} \times L \times V_{OUT}}$$

(2)

In ceramic capacitors the ESR is very low so the assumption is that 80% of the output voltage ripple is due to capacitor discharge and 20% from ESR. Table 16 lists different manufacturers for various output capacitors and their case sizes suitable for use with the LM3556.

#### 8.2.2.2 Input Capacitor Selection