# LM8850 High-Performance, Step-Up DC-DC Converter for High-Power Applications in Mobile Devices

Check for Samples: LM8850

# FEATURES

- 6µA typ. Quiescent Current

- V<sub>OUT</sub> = 3.6V to 5.7V (max V<sub>O</sub> = 5.7V)

- Operates from a Single Lithium Ion Cell (2.3V to 5.5V)

- 8 User-selectable Output Voltages via I<sup>2</sup>C

- High-speed 3.4 MHz I<sup>2</sup>C-compatible Interface

- Up to 1.0A Maximum Load Current Capability

- 4 Levels of Current Limiting

- Auto-mode Operation and Forced PWM

- 2.5 MHz Switching Drequency (typ.)

- ±2.5% DC Output Voltage Precision

- 1.0 µH Inductor (2520 Case Size)

- 4.7 μF Input and Output Capacitors (0603 case size)

- PGOOD Signal

- True Shutdown Isolation

- Output Over-voltage Protection

- Internal Active Voltage Balancing for Supercapacitors

- DSBGA 9-bump Package

- (1.58 mm x 1.62 mm x 0.35 mm)(0.5 mm pitch)

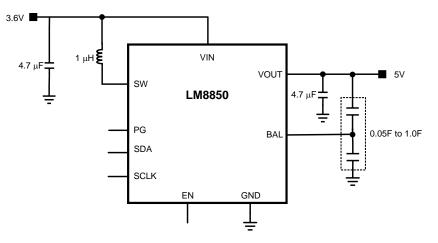

# **Typical Application Circuit**

# APPLICATIONS

- Flash LED

- Mobile Phones

- WiMAX

- USB

- Audio Amplifier

# DESCRIPTION

LM8850 is a step-up DC-DC converter optimized for use with a supercapacitor to protect a battery from power surges and enable new high power applications in mobile device architectures. The device creates an ideal rail from 3.6V to 5.7V boosting from a single Li-Ion cell with an input voltage range of 2.3V to 5.5V; Target V<sub>OUT</sub> must be at least 10% higher than V<sub>IN</sub>.

An I<sup>2</sup>C interface controlling multiple output voltage settings, input current limits, and load currents up to 1A provides superior user flexibility. The LM8850 operates in Auto mode, where the converter is in PFM mode at light loads and switches to PWM mode at heavy loads. Hysteretic PFM extends the battery life by reduction of the quiescent current to 6µA (typ.) light and standby during load conditions. Synchronous operation provides true shutdown isolation and improves its efficiency at medium-to-full load conditions.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# **DESCRIPTION (CONTINUED)**

High-switching frequency enables smaller passive components. Internal compensation is used for a broader range of inductor and output capacitor values to meet system demand and achieve small system solution size.

LM8850 is available in a 9-bump ultra-thin DSBGA package. Only four external surface-mount components, a 1.0  $\mu$ H inductor, a 4.7  $\mu$ F for input capacitor, 4.7  $\mu$ F for output capacitor and 0.05F-1.0F supercapacitor for energy storage are required.

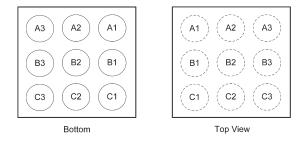

## **Connection Diagram**

#### **PIN DESCRIPTIONS**

| Pin # | Name | Description                                                                                                                     |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------|

| A1    | VIN  | Power Supply Input. Connect to input filter capacitor (See Typical Application Circuit)                                         |

| A2    | SW   | Switching node. Connection to the internal NFET switch and PFET synchronous rectifier                                           |

| A3    | GND  | Ground Pin                                                                                                                      |

| B1    | SDA  | $I^2$ C data (Use a 2kΩ pull-up resistor)                                                                                       |

| B2    | PG   | Power Good indicator                                                                                                            |

| B3    | VOUT | Output pin.                                                                                                                     |

| C1    | SCLK | I <sup>2</sup> C Clock (Use a 2kΩ pull-up resistor)                                                                             |

| C2    | EN   | Enable pin. The device is in shutdown when voltage to this pin is <0.4V and enabled when >1.2V. Do not leave this pin floating. |

| C3    | BAL  | Balancing pin for active voltage balancing of supercapacitor                                                                    |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

SNVS647C - AUGUST 2010 - REVISED MAY 2013

#### www.ti.com

## Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                                  | 5                         | 1                  |  |  |

|--------------------------------------------------|---------------------------|--------------------|--|--|

| VIN Pin to GND                                   |                           | -0.2V to 6.5V      |  |  |

| EN, PG, SDA, SCLK pins to GND                    | PG, SDA, SCLK pins to GND |                    |  |  |

| VOUT to GND                                      | (GND-0.2V) to<br>6.5V     |                    |  |  |

| SW pin to GND                                    | -0.2V to 6.5V             |                    |  |  |

| BAL to GND                                       | -0.2V to VOUT             |                    |  |  |

| Junction Temperature (T <sub>J-MAX</sub> )       | +150°C                    |                    |  |  |

| Storage Temperature Range                        | −65°C to +150°C           |                    |  |  |

| Continuous Power Dissipation <sup>(3)</sup>      |                           | Internally Limited |  |  |

| Maximum Lead Temperature<br>(Soldering, 10 sec.) |                           | 260°C              |  |  |

| ESD Rating <sup>(4)</sup>                        | Human Body Model          | 2kV                |  |  |

|                                                  | Machine Model             | 200V               |  |  |

|                                                  | Charged Device Model      | 500V               |  |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 150^{\circ}C$  (typ.) and disengages at  $T_J = 140^{\circ}C$  (typ.).

- (4) The Human Body Model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin. MIL-STD-883–3015.7.

### **Operating Ratings**<sup>(1)(2)</sup>

| Input Voltage Range                                        | 2.3V to 5.5V    |

|------------------------------------------------------------|-----------------|

| Recommended Load Current                                   | 0mA to 1.0A     |

| Junction Temperature (T <sub>J</sub> ) Range               | −40°C to +125°C |

| Ambient Temperature (T <sub>A</sub> ) Range <sup>(3)</sup> | −40°C to +85°C  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pin.

(3) In applications where high power dissipation and/or poor package resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>) and the junction-to-ambient thermal resistance of the part/package (θ<sub>JA</sub>) in the application, as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX</sub> – (θ<sub>JA</sub>x P<sub>D-MAX</sub>).

### **Thermal Properties**

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) (DSBGA) <sup>(1)</sup> | 70°C/W |

|---------------------------------------------------------------------------------|--------|

|                                                                                 |        |

(1) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high power dissipation exists, special care must be given to thermal dissipation issues in board design.

## Electrical Characteristics<sup>(1)(2)(3)(4)</sup>

Limits in standard typeface are for  $T_A = 25^{\circ}$ C. Limits in **boldface** type apply over the operating junction temperature range (-40°C  $\leq T_J = T_A \leq +85^{\circ}$ C). Unless otherwise noted, specifications apply to the LM8850 open loop Typical Application Circuit with  $V_{IN} = EN = 3.6$ V.

| Symbol                   | Parameter                           | Condition                                     | Min  | Тур  | Max  | Units |  |  |  |

|--------------------------|-------------------------------------|-----------------------------------------------|------|------|------|-------|--|--|--|

| V <sub>OUT</sub>         | Output Voltage                      | I <sub>OUT</sub> = 0mA, V <sub>OUT</sub> = 5V | -2.5 |      | +2.5 | %     |  |  |  |

|                          |                                     | VSEL bits = 0 0 0                             |      | 3.6  |      |       |  |  |  |

|                          | Output Voltage Range                | VSEL bits = 0 0 1                             |      | 3.9  |      |       |  |  |  |

|                          | Register 0                          | VSEL bits = 0 1 0                             |      | 4.2  |      |       |  |  |  |

|                          |                                     | VSEL bits = 0 1 1                             |      | 4.5  |      |       |  |  |  |

| V <sub>OUT</sub>         |                                     | VSEL bits = 1 0 0                             |      | 4.7  |      | V     |  |  |  |

|                          | Output Voltage Range                | VSEL bits = 1 0 1                             |      | 5.0  |      |       |  |  |  |

|                          | Register 1                          | VSEL bits = 1 1 0                             |      | 5.3  |      |       |  |  |  |

|                          |                                     | VSEL bits = 1 1 1                             |      | 5.7  |      | -     |  |  |  |

| I <sub>SHDN</sub>        | Shutdown Supply Current             |                                               |      | 0.4  | 3    |       |  |  |  |

| I <sub>Q_PFM</sub>       | Quiescent Current in PFM<br>Mode    |                                               |      | 6    | 10   | μA    |  |  |  |

| I <sub>Q_PWM</sub>       | Quiescent Current in PWM<br>Mode    |                                               |      | 330  | 500  |       |  |  |  |

| R <sub>DSON (NFET)</sub> | Pin-Pin Resistance for Sync<br>NFET | $V_{IN} = V_{GS} = 3.6V$                      |      | 200  |      |       |  |  |  |

| R <sub>DSON (PFET)</sub> | Pin-Pin Resistance for<br>PFET      | $V_{IN} = V_{GS} = 5.0V$                      |      | 215  |      | mΩ    |  |  |  |

|                          |                                     | ISEL bits = 111<br>VIN = 4.5V                 | 1350 | 1500 | 1650 |       |  |  |  |

|                          | Switch Peak Current Limit           | ISEL bits = 101<br>VIN = 4.5V                 | 923  | 1025 | 1128 | mA    |  |  |  |

| I <sub>LIM</sub>         |                                     | ISEL bits = 011<br>VIN = 4.5V                 | 666  | 740  | 814  |       |  |  |  |

|                          |                                     | ISEL bits = 001<br>VIN = 4.5V                 | 477  | 530  | 583  |       |  |  |  |

|                          |                                     | T <sub>ON</sub> = 00                          |      | 5    |      |       |  |  |  |

| -                        |                                     | T <sub>ON</sub> = 01                          |      | 7.5  |      |       |  |  |  |

| T <sub>ON</sub>          | Turn on Time                        | T <sub>ON</sub> = 10                          |      | 10   |      | secs. |  |  |  |

|                          |                                     | T <sub>ON</sub> = 11                          |      | 12.5 |      | 1     |  |  |  |

| I <sub>EN</sub>          | Pin Input current                   | EN                                            |      | 0.01 | 1    | μA    |  |  |  |

| F <sub>OSC</sub>         | Internal Oscillator<br>Frequency    |                                               | 2.25 | 2.5  | 2.75 | MHz   |  |  |  |

| VIH                      | Logic High Input 1.2                |                                               |      |      |      |       |  |  |  |

| V <sub>IL</sub>          | Logic Low Input                     |                                               |      |      | 0.4  | 1     |  |  |  |

| V <sub>OH</sub>          | Logic Output High                   |                                               | 1.2  |      |      | V     |  |  |  |

| V <sub>OL</sub>          | Logic Input High                    |                                               |      |      | 0.4  | 1     |  |  |  |

(1) All voltages are with respect to the potential at the GND pin.

(2) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

(3) The parameters in the electrical characteristic table are tested under open loop conditions at  $V_{IN} = 3.6V$  unless otherwise specified. For performance over the input voltage range and closed loop condition, refer to the datasheet curves.

(4) Open-loop Electrical Characteristics taken without supercapacitor.

### Table 1. Dissipation Rating Table

| θ <sub>JA</sub> | T <sub>A</sub> ≤ 25°C<br>Power Rating | T <sub>A</sub> ≤ 60°C<br>Power Rating | T <sub>A</sub> ≤ 85°C<br>Power Rating |  |  |

|-----------------|---------------------------------------|---------------------------------------|---------------------------------------|--|--|

| 70°C/W          | 1500 mW                               | 980 mW                                | 600 mW                                |  |  |

Texas Instruments

www.ti.com

SNVS647C - AUGUST 2010 - REVISED MAY 2013

Texas NSTRUMENTS

4.5 5.0 5.5

= 2.7\

1000

= 100 m\

RIPPLE

1000

SNVS647C - AUGUST 2010 - REVISED MAY 2013

www.ti.com

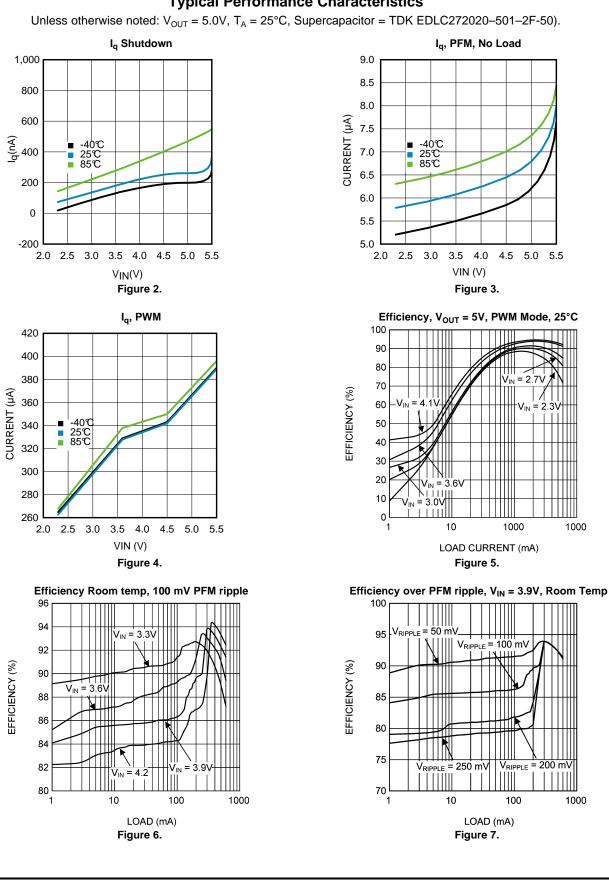

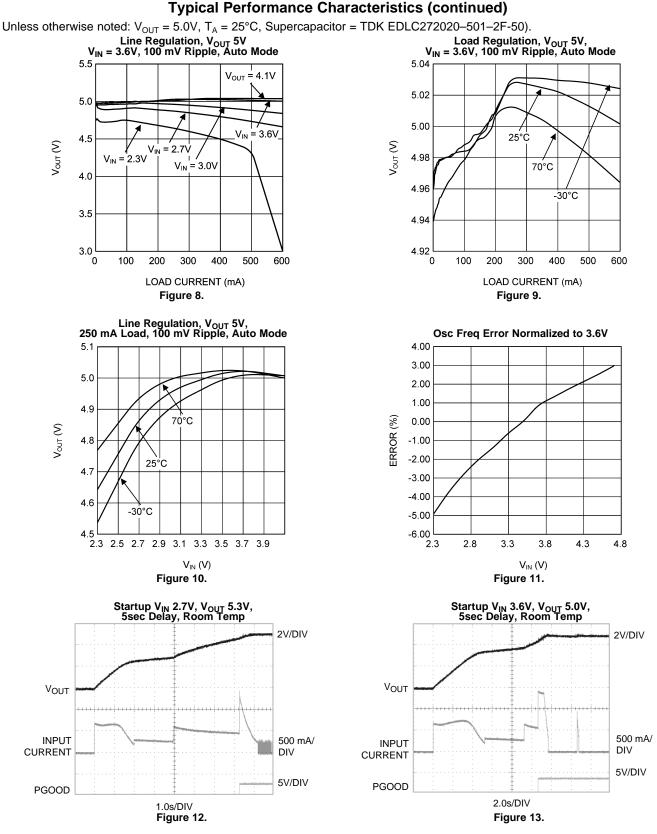

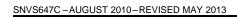

### **Typical Performance Characteristics**

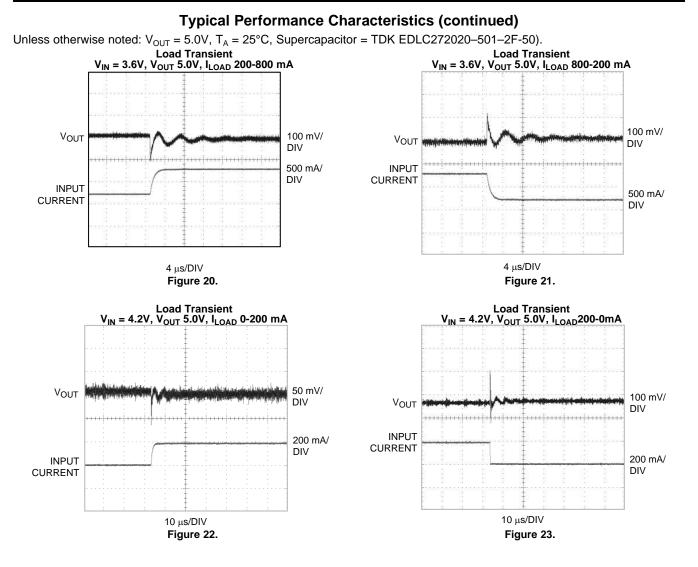

Unless otherwise noted: V<sub>OUT</sub> = 5.0V, T<sub>A</sub> = 25°C, Supercapacitor = TDK EDLC272020–501–2F-50).

6

VRIPPLE

100

= 200 mV

1000

SNVS647C - AUGUST 2010 - REVISED MAY 2013

#### www.ti.com

Texas Instruments

www.ti.com

#### SNVS647C - AUGUST 2010-REVISED MAY 2013

LM8850

SNVS647C - AUGUST 2010 - REVISED MAY 2013

www.ti.com

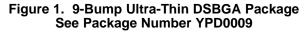

## **OPERATION DESCRIPTION**

#### LM8850 FUNCTIONALITY

The LM8850, a high-efficiency, step-up DC-DC switching boost converter, delivers a constant voltage from a stable DC input voltage source. Using a voltage mode architecture with synchronous rectification, the LM8850 has the ability to deliver up to 600 mA of load current, depending on the input voltage, output voltage, ambient temperature, and the inductor chosen.

There are three modes of operation depending on the current required - PWM (Pulse Width Modulation), PFM (Pulse Frequency Modulation), and shutdown. The device operates in PWM mode at load currents of approximately 200 mA or higher. Lighter output current loads cause the device to automatically switch into PFM for reduced current consumption ( $I_q = 6\mu A$  typ). Shutdown mode turns off the voltage regulation and offers the lowest current consumption ( $I_{SHUTDOWN} = 0.4 \mu A$  typ).

Once enabled, the LM8850 charges the supercapacitor utilizing all of the default settings in the registers. The  $I^2C$  must be used to change the default settings and this can only be done with the LM8850 enabled. Once a register is written to, the changes will transition immediately. Every time the EN pin transitions from VIL to VIH, registers 0 and 1 are reset to their defaults settings and any settings need to be rewritten into the appropriate registers.

### AUTO MODE

The LM8850 utilizes AUTO mode to reduce the amount of energy required to maintain the regulated output voltage under light load conditions. The transition from Auto mode to PWM mode varies depending on input voltage and output voltage. For an output voltage of 5.0V and an input voltage of 3.6V, the transition will occur around 225 mA.

Auto mode can only be used with a supercapacitor. If no supercapacitor is being used in the circuit, Auto-Mode must be disabled via I<sup>2</sup>C.

### V<sub>RIPPLE</sub>

The ripple voltage used in Auto-Mode is programmable via  $I^2C$ . The ripple voltage can be set to 50, 100, 200 and 250 mV. The larger the ripple voltage, the more constant energy will be supplied by the supercapacitor. The regulator will remain asleep until the effective energy to reduce the supercapacitor's voltage by the ripple value has been used by the load.

### POWER GOOD

The Power Good signal is both an output and a read only register bit. The Power Good signal will have a  $V_{OH}$  value if the  $V_{OUT}$  is greater than 85% of its programmed value. This is a typical value for 5.0V and 3.6V  $V_{IN}$ . The typical value will vary based on input and output voltage.

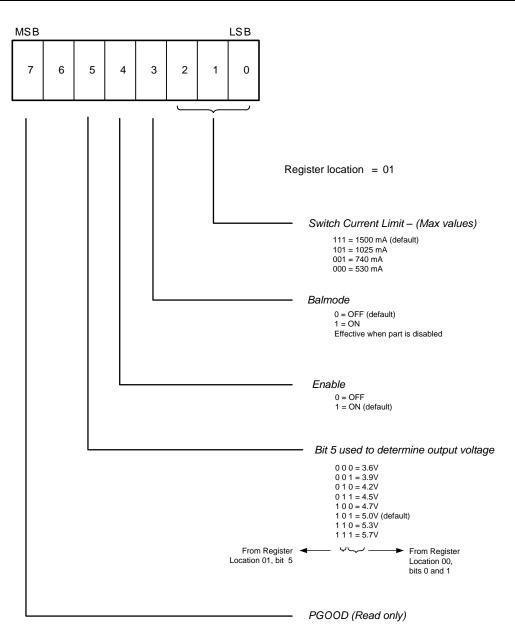

### PROGRAMMABLE V<sub>OUT</sub>

The output voltage of the LM8850 can be programmed via  $I^2C$  to any of 8 different values: 3.6, 3.9, 4.2, 4.5, 4.7, 5.0, 5.3, and 5.7V. The only requirement is that the input voltage must remain 10% below the desired output voltage for it to remain in regulation. The output voltage can be changed while the part is enabled and regulating. The transition time will depend on load conditions.

### TURN-ON TIME

The LM8850 has four programmable turn time values, 5, 7.5, 10, and 12.5 seconds. During the turn on time, the LM8850 is ramping to the output voltage while limiting the inrush current which charges the supercapacitor.

#### **BALANCING CIRCUIT**

The LM8850 has an internal balancing circuit that helps maintain voltage balance between the two capacitors within the super capacitor. The BAL pin regulates a voltage of VOUT/ 2 between the two capacitors. If one capacitor is overcharged or less charged, the LM8850 will use the balancing circuit to correct this charge inbalance. The balancing circuit can be turned off/on via the  $I^2C$  registers (BALMODE – Control Reg01, bit 3). The balancing circuit also has the ability to stay ON even after the LM8850 is shutting down (BAL – Control Reg00, bit 4).

### I<sup>2</sup>C Interface

Control of LM8850 is done via I<sup>2</sup>C compatible interface. This includes switch over from AUTO to PWM mode, adjustment of current limit, output voltage, PFM Hysteresis voltage, and start-up time. The I<sup>2</sup>C interface can also switch the active voltage balance circuit ON during shutdown. Additionally, there is a flag bit that reads back PGOOD condition.

## I<sup>2</sup>C SIGNALS

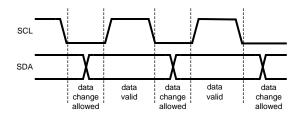

In I<sup>2</sup>C-compatible mode, the SCL pin is used for the I<sup>2</sup>C clock and the SDA pin is used for the I<sup>2</sup>C data. Both these signals need a pull-up resistor according to I<sup>2</sup>C specification. The values of the pull-up resistors are determined by the capacitance of the bus. See I<sup>2</sup>C specification from Philips for further details. Signal timing specifications are according to the I<sup>2</sup>C bus specification. Maximum frequency is 400 kHz or 3.4 MHz if in High-Speed Mode.

### I<sup>2</sup>C DATA VALIDITY

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

Figure 24. I<sup>2</sup>C Signals: Data Validity

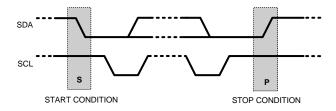

### I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 25. START and STOP Conditions

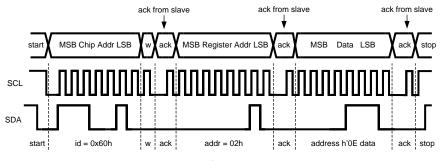

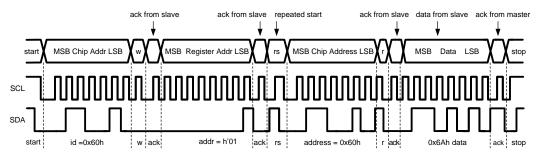

#### TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. All clock pulses are generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the ninth clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

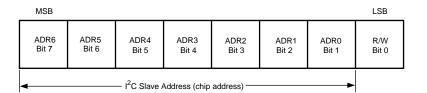

After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM8850 address is 0x60. the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Copyright © 2010–2013, Texas Instruments Incorporated

SNVS647C-AUGUST 2010-REVISED MAY 2013

#### www.ti.com

# Chip address: 60h

Figure 26. I<sup>2</sup>C Chip Address

Figure 27. I<sup>2</sup>C Write Cycle

- w = write (SDA = "0")

- r = read (SDA = "1)

- ack = acknowledge (SDA pulled down by either master or slave)

- rs = repeated start

- id = chip address

When a READ function is to be accomplished, a WRITE function must precede the READ function as shown in the Read Cycle waveform.

Figure 28. I<sup>2</sup>C Read Cycle

# HIGH-SPEED, 3.4 MHZ MODE

High-speed mode is entered by:

- 1. Start condition;

- 2. Chip Address: 0000 1XXXX (X = don't care);

- 3. Wait a clock for the acknowledge;

- 4. Now everything is in HS mode...do a repeated start (do NOT do a "stop" then a "start" because a "stop" kicks the part out of HS mode);

- 5. Send read or writes in HS mode. (Remember to use "repeated starts" between commands.); then

- 6. When you are done with the last command send a "stop" condition to put the part back into regular 400 kHz mode.

# www.ti.com I<sup>2</sup>C-COMPATIBLE CHIP ADDRESS

# The device address for LM8850 is 60 (HEX).

| CONTROL         0         RW         Control Register 1           CONTROL         1         RW         Control Register 2           MSB         LSB              7         6         5         4         3         2         1         0           Register location         00         -         Output Voltage Change         00         -         00         -         30%           01         -         30%         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | Re      | egister name |   |     | Locati | ion |        | Туре                                                                                                 | Register                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|---|-----|--------|-----|--------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSB       LSB         7       6       5       4       3       2       1       0         Register location       =       00       =       00       =       00         0       0       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =       00       =<                                                                            | CONTROL |              |   |     | 0      |     |        | R/W                                                                                                  | Control Register 1                                                                                                                                                                                                                                                                       |

| 7       6       5       4       3       2       1       0         Register location = 00         Output Voltage Change         00       00       3.0V         01       1.2.3V       01       1.2.3V         01       1.2.3V       01       1.2.3V         01       1.0.4.7V       101       5.0V         10       2.7.V       101       5.0V         11       5.3V       111       5.3V         Trom Register Location = 00         Voltage Ripple         01       5.0V       11         Description of Lots 0         and 1         Or OFF         Voltage Ripple         01       10       20 mV         US OFF         Mode         0         OFFMERYN11 default)         1         OFFMERYN12         OFFMERYN12         OFFMERYN12         OFFMERYN12         OFFMERYN12         OFFMERYN12         OFFMERYN12                                                                                                                                                                                                                                                             | CONTROL |              |   |     | 1      |     |        | R/W                                                                                                  | Control Register 2                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |              | 5 | 4 3 | 1      |     | D<br>J | R/W<br>R/W<br>Register locat<br>Output V<br>egister Location -<br>01, bit 5<br>PFM Volt<br>Balance C | ion = 00<br>ion = 00<br>/oltage Change<br>$\begin{array}{c} 0 & 0 & 0 & 3.6V\\ 0 & 0 & 1 & 3.9V\\ 0 & 1 & 0 & 3.9V\\ 0 & 1 & 0 & 4.2V\\ 0 & 1 & 1 & 4.5V\\ 1 & 0 & 0 & 4.7V\\ 1 & 0 & 1 & 5.3V\\ 1 & 1 & 1 & 5.3V\\ 1 & 1 & 1 & 5.7V\\ \hline & & & & & & \\ & & & & & & \\ & & & & & &$ |

| 0 0 = 5s (default)<br>0 1 = 7.5s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |              |   |     |        |     |        | — Ton Time                                                                                           |                                                                                                                                                                                                                                                                                          |

SNVS647C - AUGUST 2010 - REVISED MAY 2013

www.ti.com

SNVS647C - AUGUST 2010 - REVISED MAY 2013

| Cł | nanges from Revision B (May 2013) to Revision C P  | age  |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | . 13 |

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM8850URE/NOPB   | LIFEBUY       | DSBGA        | YPD                | 9    | 250            | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | SK                      |         |

| LM8850URX/NOPB   | LIFEBUY       | DSBGA        | YPD                | 9    | 3000           | RoHS & Green    | SNAGCU                               | Level-1-260C-UNLIM   | -40 to 125   | SK                      |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

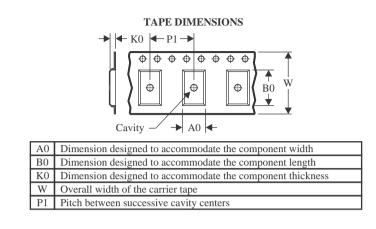

# TAPE AND REEL INFORMATION

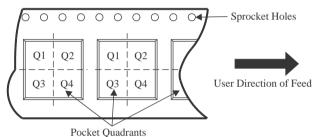

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM8850URE/NOPB              | DSBGA           | YPD                | 9 | 250  | 178.0                    | 8.4                      | 1.7        | 1.75       | 0.56       | 4.0        | 8.0       | Q1               |

| LM8850URX/NOPB              | DSBGA           | YPD                | 9 | 3000 | 178.0                    | 8.4                      | 1.7        | 1.75       | 0.56       | 4.0        | 8.0       | Q1               |

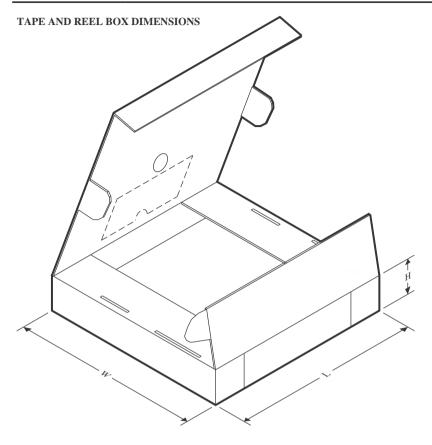

# PACKAGE MATERIALS INFORMATION

31-Aug-2023

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| LM8850URE/NOPB | DSBGA        | YPD             | 9    | 250  | 208.0       | 191.0      | 35.0        |  |

| LM8850URX/NOPB | DSBGA        | YPD             | 9    | 3000 | 208.0       | 191.0      | 35.0        |  |

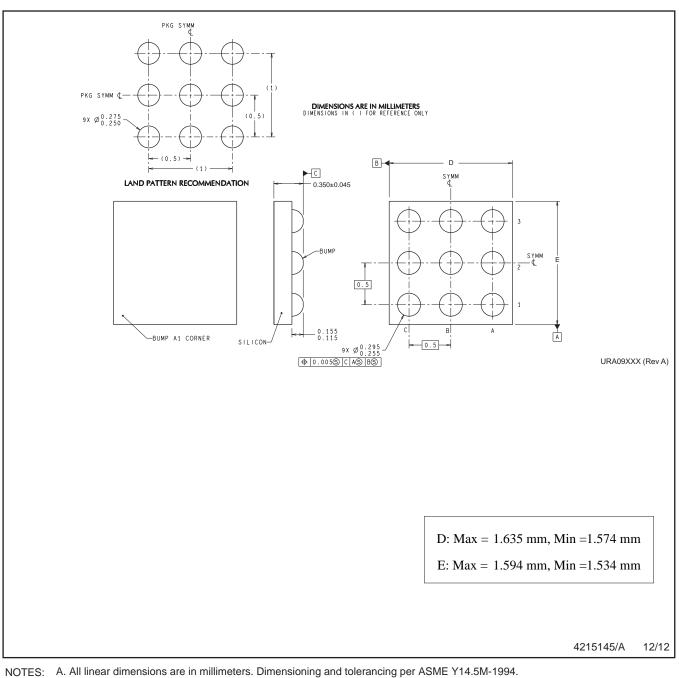

# YPD0009

B. This drawing is subject to change without notice.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated