## LMG5200 80-V, 10-A GaN Half-Bridge Power Stage

### 1 Features

- Integrated 15-mΩ GaN FETs and Driver

- 80-V Continuous, 100-V Pulsed Voltage Rating

- Package Optimized for Easy PCB Layout, Eliminating Need for Underfill, Creepage, and Clearance Requirements

- Very Low Common Source Inductance to Ensure High Slew Rate Switching Without Causing Excessive Ringing in Hard-Switched Topologies

- Ideal for Isolated and Non-Isolated Applications

- Gate Driver Capable of Up to 10 MHz Switching

- Internal Bootstrap Supply Voltage Clamping to Prevent GaN FET Overdrive

- Supply Rail Undervoltage Lockout Protection

- Excellent Propagation Delay (29.5 ns Typical) and Matching (2 ns Typical)

- Low Power Consumption

### 2 Applications

- Wide  $V_{IN}$  Multi-MHz Synchronous Buck Converters

- Class D Amplifiers for Audio

- 48-V Point-of-Load (POL) Converters for Telecom, Industrial, and Enterprise Computing

- High Power Density Single- and Three-Phase Motor Drive

### 3 Description

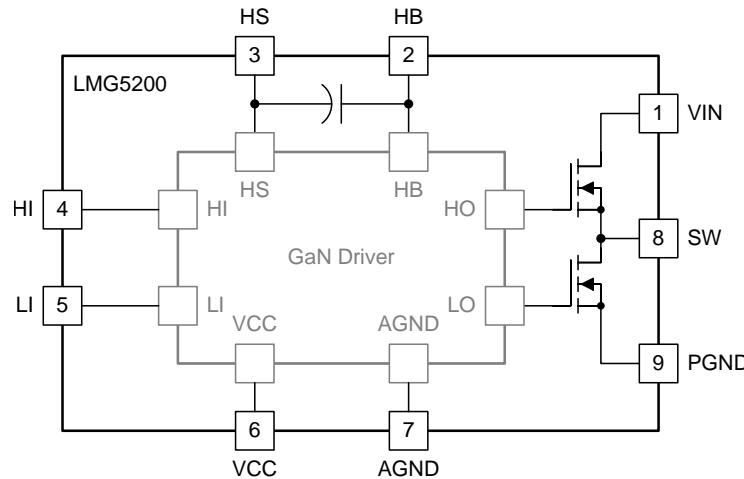

The LMG5200 device, an 80-V, 10-A driver plus GaN half-bridge power stage, provides an integrated power stage solution using enhancement-mode Gallium Nitride (GaN) FETs. The device consists of two 80-V GaN FETs driven by one high-frequency GaN FET driver in a half-bridge configuration.

GaN FETs provide significant advantages for power conversion as they have near zero reverse recovery and very small input capacitance  $C_{ISS}$ . All the devices are mounted on a completely bond-wire free package platform with minimized package parasitic elements. The LMG5200 device is available in a 6 mm × 8 mm × 2 mm lead-free package and can be easily mounted on PCBs.

The TTL logic compatible inputs can withstand input voltages up to 12 V regardless of the  $V_{CC}$  voltage. The proprietary bootstrap voltage clamping technique ensures the gate voltages of the enhancement mode GaN FETs are within a safe operating range.

The device extends advantages of discrete GaN FETs by offering a more user-friendly interface. It is an ideal solution for applications requiring high-frequency, high-efficiency operation in a small form factor. When used with the TPS53632G controller, the LMG5200 enables direct conversion from 48-V to point-of-load voltages (0.5–1.5 V).

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| LMG5200     | QFM (9) | 6.00 mm × 8.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

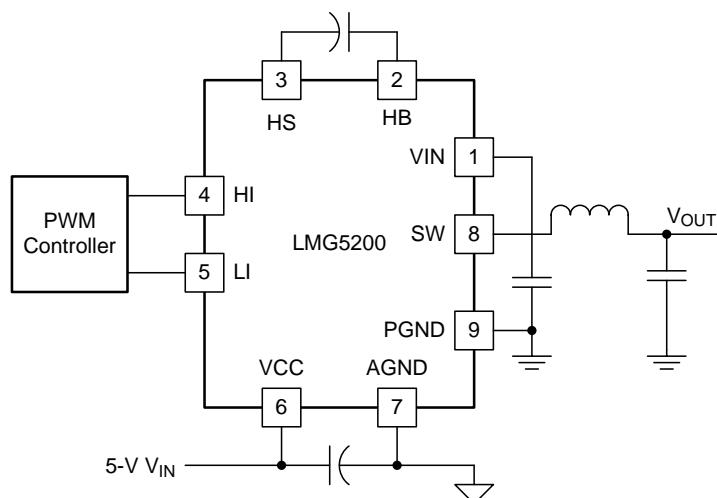

#### Simplified Block Diagram

An **IMPORTANT NOTICE** at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. **PRODUCTION DATA**.

## Table of Contents

|          |                                            |    |           |                                                 |    |

|----------|--------------------------------------------|----|-----------|-------------------------------------------------|----|

| <b>1</b> | <b>Features</b>                            | 1  | 8.4       | Device Functional Modes                         | 12 |

| <b>2</b> | <b>Applications</b>                        | 1  | <b>9</b>  | <b>Application and Implementation</b>           | 12 |

| <b>3</b> | <b>Description</b>                         | 1  | 9.1       | Application Information                         | 12 |

| <b>4</b> | <b>Revision History</b>                    | 2  | 9.2       | Typical Application                             | 12 |

| <b>5</b> | <b>Pin Configuration and Functions</b>     | 3  | <b>10</b> | <b>Power Supply Recommendations</b>             | 15 |

| <b>6</b> | <b>Specifications</b>                      | 4  | <b>11</b> | <b>Layout</b>                                   | 16 |

| 6.1      | Absolute Maximum Ratings                   | 4  | 11.1      | Layout Guidelines                               | 16 |

| 6.2      | ESD Ratings                                | 4  | 11.2      | Layout Examples                                 | 16 |

| 6.3      | Recommended Operating Conditions           | 4  | <b>12</b> | <b>Device and Documentation Support</b>         | 20 |

| 6.4      | Thermal Information                        | 5  | 12.1      | Device Support                                  | 20 |

| 6.5      | Electrical Characteristics                 | 5  | 12.2      | Documentation Support                           | 20 |

| 6.6      | Typical Characteristics                    | 7  | 12.3      | Receiving Notification of Documentation Updates | 20 |

| <b>7</b> | <b>Parameter Measurement Information</b>   | 8  | 12.4      | Community Resources                             | 20 |

| 7.1      | Propagation Delay and Mismatch Measurement | 8  | 12.5      | Trademarks                                      | 20 |

| <b>8</b> | <b>Detailed Description</b>                | 9  | 12.6      | Electrostatic Discharge Caution                 | 20 |

| 8.1      | Overview                                   | 9  | 12.7      | Glossary                                        | 20 |

| 8.2      | Functional Block Diagram                   | 10 | <b>13</b> | <b>Mechanical, Packaging, and Orderable</b>     | 20 |

| 8.3      | Feature Description                        | 10 | 13.1      | Information                                     | 21 |

## 4 Revision History

| <b>Changes from Revision D (March 2017) to Revision E</b>                   |  | <b>Page</b> |

|-----------------------------------------------------------------------------|--|-------------|

| • deleted footnote                                                          |  | 5           |

| <b>Changes from Revision C (December 2016) to Revision D</b>                |  | <b>Page</b> |

| • general editorial global authoring and SDS updates                        |  | 1           |

| <b>Changes from Revision B (January 2016) to Revision C</b>                 |  | <b>Page</b> |

| • Changed from GaN Technology Preview to Production Data                    |  | 1           |

| • Added Device Functional Modes Section                                     |  | 12          |

| • Added Typical Application Section                                         |  | 12          |

| • Updated Power Supply Recommendations Section                              |  | 15          |

| • Added Links in Development Support Section                                |  | 20          |

| <b>Changes from Revision A (March 2015) to Revision B</b>                   |  | <b>Page</b> |

| • Changed part number typographical error in <a href="#">Figure 14</a>      |  | 16          |

| <b>Changes from Original (March 2015) to Revision A</b>                     |  | <b>Page</b> |

| • Corrected typographical error in <a href="#">Simplified Block Diagram</a> |  | 1           |

| • Corrected typographical error in <a href="#">Figure 5</a>                 |  | 8           |

| • Corrected typographical error in <a href="#">Figure 10</a>                |  | 10          |

| • Corrected typographical error in <a href="#">Figure 11</a>                |  | 12          |

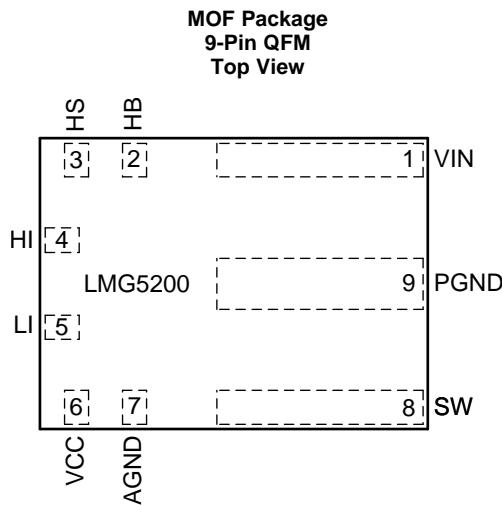

## 5 Pin Configuration and Functions

### Pin Functions

| PIN  |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                 |

|------|-----|--------------------|---------------------------------------------------------------------------------------------|

| NAME | NO. |                    |                                                                                             |

| AGND | 7   | G                  | Analog ground. Ground of driver device.                                                     |

| HB   | 2   | P                  | High-side gate driver bootstrap rail.                                                       |

| HI   | 4   | I                  | High-side gate driver control input                                                         |

| HS   | 3   | P                  | High-side GaN FET source connection                                                         |

| LI   | 5   | I                  | Low-side driver control input                                                               |

| PGND | 9   | G                  | Power ground. Low-side GaN FET source. Electrically shorted to AGND pin.                    |

| SW   | 8   | P                  | Switching node. Electrically shorted to HS pin. Ensure low capacitance at this node on PCB. |

| VCC  | 6   | P                  | 5-V positive gate drive supply                                                              |

| VIN  | 1   | P                  | Input voltage pin. Electrically connected to high-side GaN FET drain.                       |

(1) I = Input, O = Output, G = Ground, P = Power

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                                                | MIN  | MAX | UNIT |

|----------------------------------------------------------|------|-----|------|

| VIN to PGND                                              | 0    | 80  | V    |

| VIN to PGND (pulsed, 100-ms max duration) <sup>(2)</sup> |      | 100 | V    |

| HB to AGND                                               | -0.3 | 86  | V    |

| HS to AGND                                               | -5   | 80  | V    |

| HI to AGND                                               | -0.3 | 12  | V    |

| LI to AGND                                               | -0.3 | 12  | V    |

| VCC to AGND                                              | -0.3 | 6   | V    |

| HB to HS                                                 | -0.3 | 6   | V    |

| HB to VCC                                                | 0    | 80  | V    |

| SW to PGND                                               | -5   | 80  | V    |

| IOUT from SW pin                                         |      | 10  | A    |

| Junction Temperature, $T_J$                              | -40  | 125 | °C   |

| Storage Temperature, $T_{stg}$                           | -40  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Device can withstand 1000 pulses up to 100V of 100ms duration and less than 1% duty cycle over its lifetime.

### 6.2 ESD Ratings

|             |                         |                                                                                | VALUE      | UNIT |

|-------------|-------------------------|--------------------------------------------------------------------------------|------------|------|

| $V_{(ESD)}$ | Electrostatic Discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | $\pm 1000$ | V    |

|             |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | $\pm 500$  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                 | MIN          | NOM | MAX             | UNIT |

|---------------------------------|--------------|-----|-----------------|------|

| VCC                             | 4.75         | 5   | 5.25            | V    |

| LI or HI Input                  | 0            |     | 12              | V    |

| VIN                             | 0            |     | 80              | V    |

| HS, SW                          | -5           |     | 80              | V    |

| HB                              | $V_{HS} + 4$ |     | $V_{HS} + 5.25$ | V    |

| HS, SW Slew rate <sup>(1)</sup> |              |     | 50              | V/ns |

| Junction Temperature, $T_J$     | -40          |     | 125             | °C   |

(1) This parameter is guaranteed by design. Not tested in production.

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | LMG5200 | UNIT |

|-------------------------------|----------------------------------------------|---------|------|

|                               |                                              | QFN     |      |

|                               |                                              | 9 PINS  |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 35      | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 18      |      |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 16      | °C/W |

| $\psi_{JT}$                   | Junction-to-top characterization parameter   | 1.8     | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter | 16      | °C/W |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](#).

## 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| PARAMETER                       | TEST CONDITIONS                                                                                                                               | MIN  | TYP   | MAX   | UNIT |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------|

| <b>SUPPLY CURRENTS</b>          |                                                                                                                                               |      |       |       |      |

| $I_{CC}$                        | $V_{CC}$ Quiescent Current<br>$LI = HI = 0V, V_{CC} = 5V, HB-HS = 4.6V$                                                                       | 0.08 | 0.125 | 0.125 | mA   |

| $I_{CCO}$                       | Total $V_{CC}$ Operating Current<br>$f = 500$ kHz                                                                                             | 3.0  | 5.0   | 5.0   | mA   |

| $I_{HB}$                        | HB Quiescent Current<br>$LI = HI = 0V, V_{CC} = 5V, HB-HS = 4.6V$                                                                             | 0.09 | 0.150 | 0.150 | mA   |

| $I_{HBO}$                       | HB Operating Current<br>$f = 500$ kHz, 50% Duty cycle, $V_{DD} = 5V$                                                                          | 1.5  | 2.5   | 2.5   | mA   |

| <b>INPUT PINS</b>               |                                                                                                                                               |      |       |       |      |

| $V_{IH}$                        | High-Level Input Voltage Threshold<br>Rising Edge                                                                                             | 1.87 | 2.06  | 2.22  | V    |

| $V_{IL}$                        | Low-Level Input Voltage Threshold<br>Falling Edge                                                                                             | 1.48 | 1.66  | 1.76  | V    |

| $V_{HYS}$                       | Hysteresis between rising and falling threshold                                                                                               |      | 400   |       | mV   |

| $R_I$                           | Input pull down resistance                                                                                                                    | 100  | 200   | 300   | kΩ   |

| <b>UNDER VOLTAGE PROTECTION</b> |                                                                                                                                               |      |       |       |      |

| $V_{CCR}$                       | $V_{CC}$ Rising edge threshold<br>Rising                                                                                                      | 3.2  | 3.8   | 4.5   | V    |

| $V_{CC(\text{hyst})}$           | $V_{CC}$ UVLO threshold hysteresis                                                                                                            |      | 200   |       | mV   |

| $V_{HBR}$                       | HB Rising edge threshold<br>Rising                                                                                                            | 2.5  | 3.2   | 3.9   | V    |

| $V_{HB(\text{hyst})}$           | HB UVLO threshold hysteresis                                                                                                                  |      | 200   |       | mV   |

| <b>BOOTSTRAP DIODE</b>          |                                                                                                                                               |      |       |       |      |

| $V_{DL}$                        | Low-Current forward voltage<br>$I_{VDD-HB} = 100\mu A$                                                                                        | 0.45 | 0.65  | 0.65  | V    |

| $V_{DH}$                        | High current forward voltage<br>$I_{VDD-HB} = 100mA$                                                                                          | 0.9  | 1.0   | 1.0   | V    |

| $R_D$                           | Dynamic Resistance<br>$I_{VDD-HB} = 100mA$                                                                                                    | 1.85 | 2.8   | 2.8   | Ω    |

|                                 | HB-HS Clamp<br>Regulation Voltage                                                                                                             | 4.65 | 5     | 5.2   | V    |

| $t_{BS}$                        | Bootstrap diode reverse recovery time<br>$I_F = 100$ mA, $IR = 100$ mA                                                                        | 40   |       |       | ns   |

| $Q_{RR}$                        | Bootstrap diode reverse recovery charge<br>$V_{VIN} = 50$ V                                                                                   |      | 2     |       | nC   |

| <b>POWER STAGE</b>              |                                                                                                                                               |      |       |       |      |

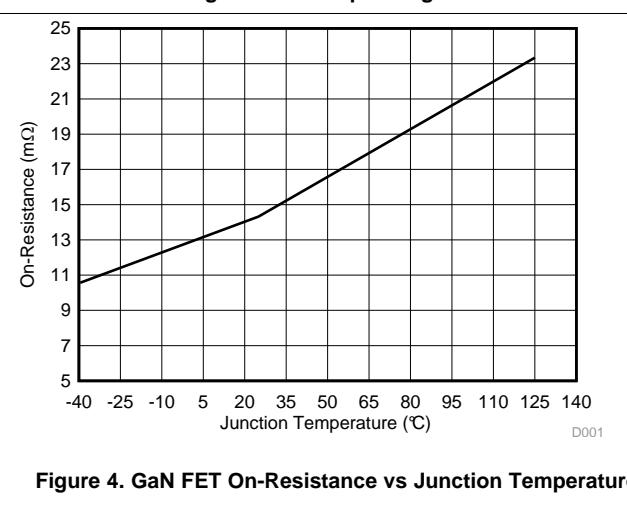

| $R_{DS(ON)HS}$                  | High-side GaN FET on-resistance<br>$LI=0V, HI=V_{CC}=5V, HB-HS=5V, V_{IN-SW}=10A, T_J = 25^\circ C$                                           | 15   | 20    | 20    | mΩ   |

| $R_{DS(ON)LS}$                  | Low-side GaN FET on-resistance<br>$LI=V_{CC}=5V, HI=0V, HB-HS=5V, SW-PGND=10A, T_J = 25^\circ C$                                              | 15   | 20    | 20    | mΩ   |

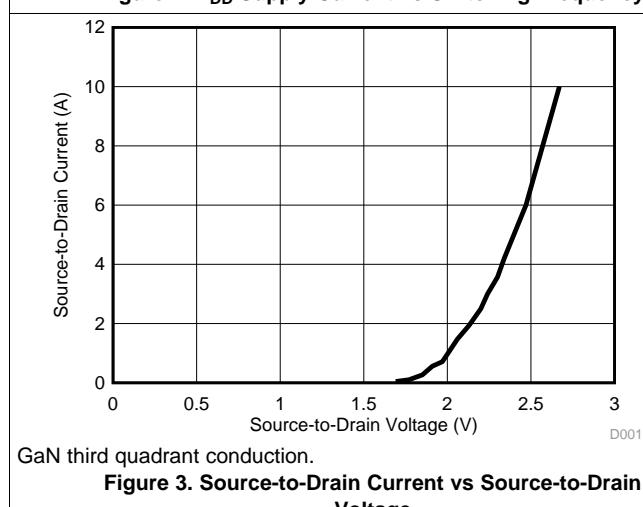

| $V_{SD}$                        | GaN 3rd quadrant conduction drop<br>$I_{SD} = 500$ mA, $V_{IN}$ floating, $V_{VCC} = 5$ V, $HI = LI = 0V$                                     | 2    |       |       | V    |

| $I_{L-VIN-SW}$                  | Leakage from $VIN$ to $SW$ when the high-side GaN FET and low-side GaN FET are off<br>$VIN = 80V, HI = LI = 0V, V_{VCC} = 5V, T_J=25^\circ C$ | 25   | 150   | 150   | μA   |

(1) Parameters that show only a typical value are guaranteed by design and may not be tested in production

## Electrical Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

| PARAMETER      |                                                                                | TEST CONDITIONS                                                       | MIN | TYP  | MAX | UNIT    |

|----------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|------|-----|---------|

| $I_{L-SW-GND}$ | Leakage from SW to GND when the high-side GaN FET and low-side GaN FET are off | $V_{DS} = 80V$ , $HI = LI = 0V$ , $V_{VCC} = 5V$ , $T_J = 25^\circ C$ |     | 25   | 150 | $\mu A$ |

| $C_{OSS}$      | Output Capacitance of high-side GaN FET and low-side GaN FET                   | $V_{DS} = 40V$ , $V_{GS} = 0V$ ( $HI = LI = 0V$ )                     |     | 266  |     | $pF$    |

| $Q_G$          | Total Gate Charge                                                              | $V_{DS} = 40V$ , $I_D = 10A$ , $V_{GS} = 5V$                          |     | 3.8  |     | $nC$    |

| $Q_{OSS}$      | Output Charge                                                                  | $V_{DS} = 40V$ , $I_D = 10A$                                          |     | 21   |     | $nC$    |

| $Q_{RR}$       | Source to Drain Reverse Recovery Charge                                        | Not including internal driver bootstrap diode                         |     | 0    |     | $nC$    |

| $t_{HIPLH}$    | Propagation delay: HI Rising <sup>(2)</sup>                                    | $LI = 0V$ , $VCC = 5V$ , $HB-HS = 5V$ , $VIN = 30V$                   |     | 29.5 | 50  | $ns$    |

| $t_{HIPHL}$    | Propagation delay: HI Falling <sup>(2)</sup>                                   | $LI = 0V$ , $VCC = 5V$ , $HB-HS = 5V$ , $VIN = 30V$                   |     | 29.5 | 50  | $ns$    |

| $t_{LPLH}$     | Propagation delay: LI Rising <sup>(2)</sup>                                    | $HI = 0V$ , $VCC = 5V$ , $HB-HS = 5V$ , $VIN = 30V$                   |     | 29.5 | 50  | $ns$    |

| $t_{LPHL}$     | Propagation delay: LI Falling <sup>(2)</sup>                                   | $HI = 0V$ , $VCC = 5V$ , $HB-HS = 5V$ , $VIN = 30V$                   |     | 29.5 | 50  | $ns$    |

| $t_{MON}$      | Delay Matching: LI high & HI low <sup>(2)</sup>                                |                                                                       |     | 2    | 8.0 | $ns$    |

| $t_{MOFF}$     | Delay Matching: LI low & HI high <sup>(2)</sup>                                |                                                                       |     | 2    | 8.0 | $ns$    |

| $t_{PW}$       | Minimum Input Pulse Width that Changes the Output                              |                                                                       |     | 10   |     | $ns$    |

(2) See *Propagation Delay and Mismatch Measurement* section

## 6.6 Typical Characteristics

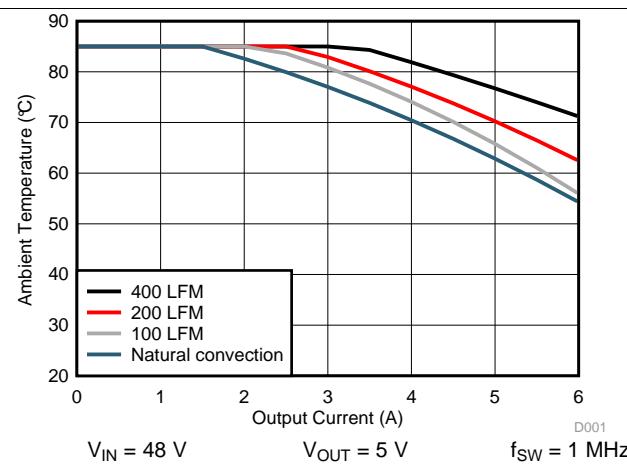

All the curves are based on measurements made on a PCB design with dimensions of 3.2 inches (W)  $\times$  2.7 inches (L)  $\times$  0.062 inch (T) and 4 layers of 2 oz copper.

The safe operating area (SOA) curves displays the temperature boundaries within an operating system by incorporating the thermal resistance and system power loss. A buck converter is used for measuring the SOA. [Figure 2](#) outlines the temperature and airflow conditions required for a given load current. The area under the curve dictates the SOA for different airflow conditions.

## 7 Parameter Measurement Information

### 7.1 Propagation Delay and Mismatch Measurement

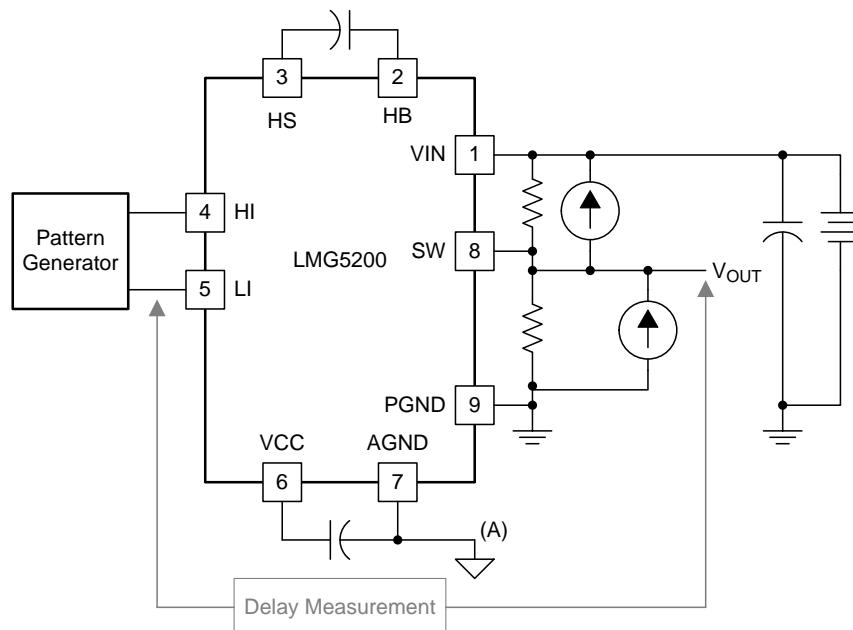

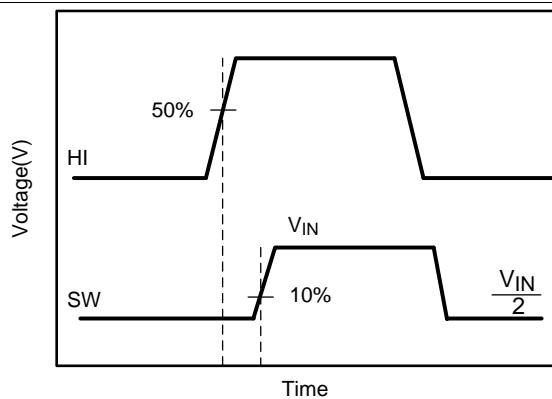

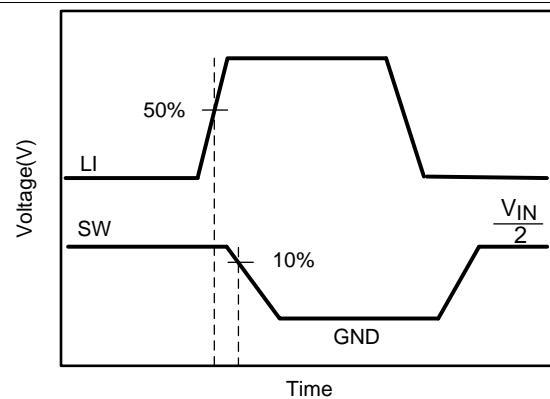

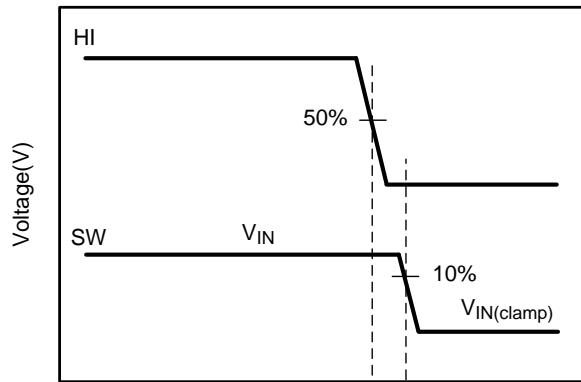

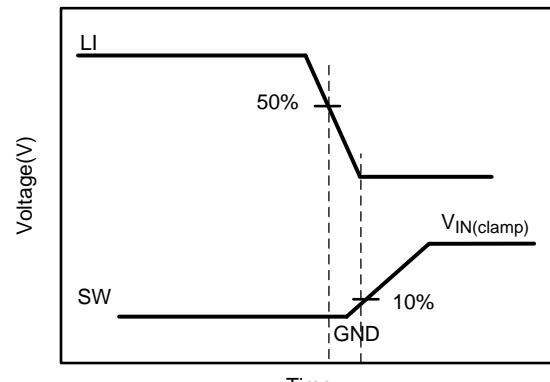

Figure 5 shows the typical test setup used to measure the propagation mismatch. As the gate drives are not accessible, pullup and pulldown resistors in this test circuit are used to indicate when the low-side GaN FET turns ON and the high-side GaN FET turns OFF and vice versa to measure the  $t_{MON}$  and  $t_{MOFF}$  parameters. Resistance values used in this circuit for the pullup and pulldown resistors are in the order of 1 k $\Omega$ ; the current sources used are 2 A.

Figure 6 through Figure 9 show propagation delay measurement waveforms. For turnon propagation delay measurements, the current sources are not used. For turnoff time measurements, the current sources are set to 2 A, and a voltage clamp limit is also set, referred to as  $V_{IN(CLAMP)}$ . When measuring the high-side component turnoff delay, the current source across the high-side FET is turned on, the current source across the low-side FET is off, HI transitions from high-to-low, and output voltage transitions from  $V_{IN}$  to  $V_{IN(CLAMP)}$ . Similarly, for low-side component turnoff propagation delay measurements, the high-side component current source is turned off, and the low-side component current source is turned on, LI transitions from high to low and the output transitions from GND potential to  $V_{IN(CLAMP)}$ . The time between the transition of LI and the output change is the propagation delay time.

Figure 5. Propagation Delay and Propagation Mismatch Measurement

## Propagation Delay and Mismatch Measurement (continued)

Figure 6. High-Side Gate Driver Turnon

Figure 7. Low-Side Gate Driver Turnon

Figure 8. High-Side Gate Driver Turnoff

Figure 9. Low-Side Gate Driver Turnoff

## 8 Detailed Description

### 8.1 Overview

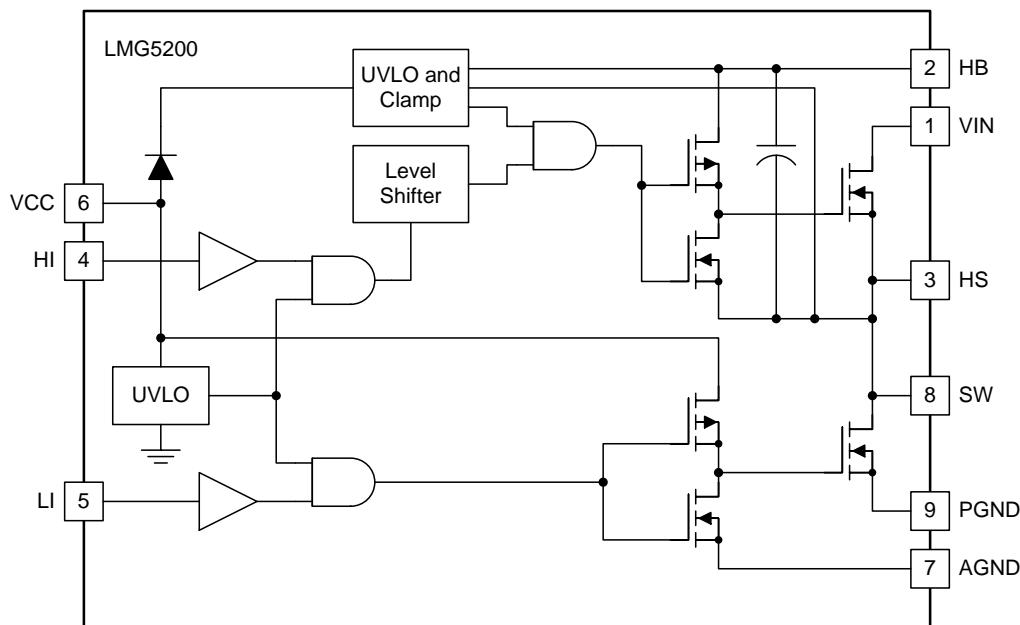

Figure 10 shows the LMG5200, half-bridge, GaN power stage with highly integrated high-side and low-side gate drivers, which includes built-in UVLO protection circuitry and an overvoltage clamp circuitry. The clamp circuitry limits the bootstrap refresh operation to ensure that the high-side gate driver overdrive does not exceed 5.4 V. The device integrates two, 15-mΩ GaN FETs in a half-bridge configuration. The device can be used in many isolated and non-isolated topologies allowing very simple integration. The package is designed to minimize the loop inductance while keeping the PCB design simple. The drive strengths for turnon and turnoff are optimized to ensure high voltage slew rates without causing any excessive ringing on the gate or power loop.

## 8.2 Functional Block Diagram

Figure 10 shows the functional block diagram of the LMG5200 device with integrated high-side and low-side GaN FETs.

Figure 10. Functional Block Diagram

## 8.3 Feature Description

The LMG5200 device brings ease of designing high power density boards without the need for underfill while maintaining creepage and clearance requirements. The propagation delays between the high-side gate driver and low-side gate driver are matched to allow very tight control of dead time. Controlling the dead time is critical in GaN-based applications to maintain high efficiency. HI and LI can be independently controlled to minimize the third quadrant conduction of the low-side FET for hard switched buck converters. A very small propagation mismatch between the HI and LI to the drivers for both the falling and rising thresholds ensures dead times of < 10 ns. Co-packaging the GaN FET half-bridge with the driver ensures minimized common source inductance. This minimized inductance has a significant performance impact on hard-switched topologies.

The built-in bootstrap circuit with clamp prevents the high-side gate drive from exceeding the GaN FETs maximum gate-to-source voltage ( $V_{GS}$ ) without any additional external circuitry. The built-in driver has an undervoltage lockout (UVLO) on the VDD and bootstrap (HB-HS) rails. When the voltage is below the UVLO threshold voltage, the device ignores both the HI and LI signals to prevent the GaN FETs from being partially turned on. Below UVLO, if there is sufficient voltage ( $V_{VCC} > 2.5$  V), the driver actively pulls the high-side and low-side gate driver output low. The UVLO threshold hysteresis of 200 mV prevents chattering and unwanted turnon due to voltage spikes. Use an external VCC bypass capacitor with a value of 0.1  $\mu$ F or higher. TI recommends a size of 0402 to minimize trace length to the pin. Place the bypass and bootstrap capacitors as close as possible to the device to minimize parasitic inductance.

### 8.3.1 Control Inputs

The LMG5200's inputs pins are independently controlled with TTL input thresholds and can withstand voltages up to 12V regardless of the VDD voltage. This allows the inputs to be directly connected to the outputs of an analog PWM controller with up to 12V power supply, eliminating the need for a buffer stage.

In order to allow flexibility to optimize deadtime according to design needs, the LMG5200 does not implement an overlap protection functionality. If both HI and LI are asserted, both the high-side and low-side GaN FETs are turned on. Careful consideration must be applied to the control inputs in order to avoid a shoot-through condition.

## Feature Description (continued)

### 8.3.2 Start-up and UVLO

The LMG5200 has an UVLO on both the  $V_{CC}$  and HB (bootstrap) supplies. When the  $V_{CC}$  voltage is below the threshold voltage of 3.8 V, both the HI and LI inputs are ignored, to prevent the GaN FETs from being partially turned on. Also, if there is insufficient  $V_{CC}$  voltage, the UVLO actively pulls the high- and low-side GaN FET gates low. When the HB to HS bootstrap voltage is below the UVLO threshold of 3.2 V, only the high-side GaN FET gate is pulled low. Both UVLO threshold voltages have 200 mV of hysteresis to avoid chattering.

**Table 1.  $V_{CC}$  UVLO Feature Logic Operation**

| CONDITION ( $V_{HB-HS} > V_{HBR}$ for all cases below)           | HI | LI | SW   |

|------------------------------------------------------------------|----|----|------|

| $V_{CC} - V_{SS} < V_{CCR}$ during device start-up               | H  | L  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR}$ during device start-up               | L  | H  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR}$ during device start-up               | H  | H  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR}$ during device start-up               | L  | L  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR} - V_{CC(hyst)}$ after device start-up | H  | L  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR} - V_{CC(hyst)}$ after device start-up | L  | H  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR} - V_{CC(hyst)}$ after device start-up | H  | H  | Hi-Z |

| $V_{CC} - V_{SS} < V_{CCR} - V_{CC(hyst)}$ after device start-up | L  | L  | Hi-Z |

**Table 2.  $V_{HB-HS}$  UVLO Feature Logic Operation**

| CONDITION ( $V_{CC} > V_{CCR}$ for all cases below)        | HI | LI | SW   |

|------------------------------------------------------------|----|----|------|

| $V_{HB-HS} < V_{HBR}$ during device start-up               | H  | L  | Hi-Z |

| $V_{HB-HS} < V_{HBR}$ during device start-up               | L  | H  | PGND |

| $V_{HB-HS} < V_{HBR}$ during device start-up               | H  | H  | PGND |

| $V_{HB-HS} < V_{HBR}$ during device start-up               | L  | L  | Hi-Z |

| $V_{HB-HS} < V_{HBR} - V_{HB(hyst)}$ after device start-up | H  | L  | Hi-Z |

| $V_{HB-HS} < V_{HBR} - V_{HB(hyst)}$ after device start-up | L  | H  | PGND |

| $V_{HB-HS} < V_{HBR} - V_{HB(hyst)}$ after device start-up | H  | H  | PGND |

| $V_{HB-HS} < V_{HBR} - V_{HB(hyst)}$ after device start-up | L  | L  | Hi-Z |

### 8.3.3 Bootstrap Supply Voltage Clamping

The high-side bias voltage is generated using a bootstrap technique and is internally clamped at 5 V (typical). This clamp prevents the gate voltage from exceeding the maximum gate-source voltage rating of the enhancement-mode GaN FETs.

### 8.3.4 Level Shift

The level-shift circuit is the interface from the high-side input HI to the high-side driver stage, which is referenced to the switch node (HS). The level shift allows control of the high-side GaN FET gate driver output, which is referenced to the HS pin and provides excellent delay matching with the low-side driver.

## 8.4 Device Functional Modes

The LMG5200 operates in normal mode and UVLO mode. See [Start-up and UVLO](#) for information on UVLO operation mode. In the normal mode, the output state is dependent on the states of the HI and LI pins. [Table 3](#) lists the output states for different input pin combinations. Note that when both HI and LI are asserted, both GaN FETs in the power stage are turned on. Careful consideration must be applied to the control inputs in order to avoid this state, as it will result in a shoot-through condition, which can permanently damage the device.

**Table 3. Truth Table**

| HI | LI | HIGH-SIDE GaN FET | LOW-SIDE GaN FET | SW   |

|----|----|-------------------|------------------|------|

| L  | L  | OFF               | OFF              | Hi-Z |

| L  | H  | OFF               | ON               | PGND |

| H  | L  | ON                | OFF              | VIN  |

| H  | H  | ON                | ON               | ---  |

## 9 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The LMG5200 GaN power stage is a versatile building block for various types of high-frequency, switch-mode power applications. The high-performance gate driver IC integrated in the package helps minimize the parasitics and results in extremely fast switching of the GaN FETs. The device design is highly optimized for synchronous buck converters and other half-bridge configurations.

### 9.2 Typical Application

[Figure 11](#) shows a synchronous buck converter application with  $V_{CC}$  connected to a 5-V supply. It is critical to optimize the power loop (loop impedance from VIN capacitor to PGND). Having a high power loop inductance causes significant ringing in the SW node and also causes the associated power loss. Refer to the [Layout Guidelines](#) section for information on how to minimize this power loop.

**Figure 11. Typical Connection Diagram For a Synchronous Buck Converter**

## Typical Application (continued)

### 9.2.1 Design Requirements

When designing a synchronous buck converter application that incorporates the LMG5200 power stage, some design considerations must be evaluated first to make the most appropriate selection. Among these considerations are the input voltages, passive components, operating frequency, and controller selection. [Table 4](#) shows some sample values for a typical application. See [Power Supply Recommendations](#), [Layout](#), and [Power Dissipation](#) for other key design considerations for the LMG5200.

**Table 4. Design Parameters**

| PARAMETER                                  | SAMPLE VALUE     |

|--------------------------------------------|------------------|

| Half-bridge input supply voltage, $V_{IN}$ | 48 V             |

| Output voltage, $V_{OUT}$                  | 12 V             |

| Output current                             | 8 A              |

| $V_{HB-HS}$ bootstrap capacitor            | 0.1 $\mu$ F, X5R |

| Switching frequency                        | 1 MHz            |

| Dead time                                  | 8 ns             |

| Inductor                                   | 4.7 $\mu$ H      |

| Controller                                 | TPS40400         |

### 9.2.2 Detailed Design Procedure

This procedure outlines the design considerations of LMG5200 in a synchronous buck converter. For additional design help, see [Related Documentation](#).

#### 9.2.2.1 $V_{CC}$ Bypass Capacitor

The  $V_{CC}$  bypass capacitor provides the gate charge for the low-side and high-side transistors and to absorb the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated with [Equation 1](#).

$$C_{VCC} = (Q_{gH} + Q_{gL} + Q_{rr}) / \Delta V \quad (1)$$

$Q_{gH}$  and  $Q_{gL}$  are the gate charge of the high-side and low-side transistors, respectively.  $Q_{rr}$  is the reverse recovery charge of the bootstrap diode.  $\Delta V$  is the maximum allowable voltage drop across the bypass capacitor. A 0.1- $\mu$ F or larger value, good-quality, ceramic capacitor is recommended. Place the bypass capacitor as close as possible to the  $V_{CC}$  and AGND pins of the device to minimize the parasitic inductance.

#### 9.2.2.2 Bootstrap Capacitor

The bootstrap capacitor provides the gate charge for the high-side gate drive, dc bias power for HB UVLO circuit, and the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated using [Equation 2](#).

$$C_{BST} = (Q_{gH} + Q_{rr} + I_{HB} * t_{ON(max)}) / \Delta V$$

where

- $I_{HB}$  is the quiescent current of the high-side gate driver (150  $\mu$ A, maximum)

- $t_{ON(max)}$  is the maximum on-time period of the high-side gate driver

- $Q_{rr}$  is the reverse recovery charge of the bootstrap diode

- $Q_{gH}$  is the gate charge of the high-side GaN FET

- $\Delta V$  is the permissible ripple in the bootstrap capacitor (< 100 mV, typical)

A 0.1- $\mu$ F, 16-V, 0402 ceramic capacitor is suitable for most applications. Place the bootstrap capacitor as close as possible to the HB and HS pins.

### 9.2.2.3 Power Dissipation

Ensure that the power loss in the driver and the GaN FETs is maintained below the maximum power dissipation limit of the package at the operating temperature. The smaller the power loss in the driver and the GaN FETs, the higher the maximum operating frequency that can be achieved in the application. The total power dissipation of the LMG5200 device is the sum of the gate driver losses, the bootstrap diode power loss and the switching and conduction losses in the FETs.

The gate driver losses are incurred by charge and discharge of the capacitive load. It can be approximated using [Equation 3](#).

$$P = (2 \times Q_g) \times V_{DD} \times f_{SW}$$

where

- $Q_g$  is the gate charge

- $V_{DD}$  is the bias supply

- $f_{SW}$  is the switching frequency

(3)

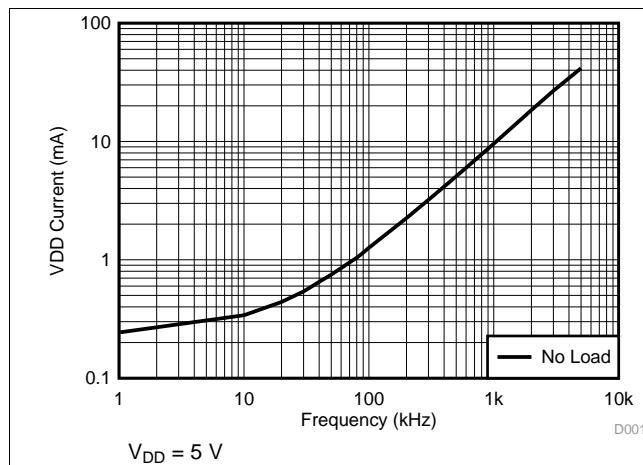

There are some additional losses in the gate drivers due to the internal CMOS stages used to buffer the outputs. [Figure 1](#) shows the measured gate driver power dissipation versus frequency and load capacitance. Use this graph to approximate the power losses due to the gate drivers.

The bootstrap diode power loss is the sum of the forward bias power loss that occurs while charging the bootstrap capacitor and the reverse bias power loss that occurs during reverse recovery. Because each of these events happens once per cycle, the diode power loss is proportional to the operating frequency. Higher input voltages ( $V_{IN}$ ) to the half bridge also result in higher reverse recovery losses.

The power losses due to the GaN FETs can be divided into conduction losses and switching losses. Conduction losses are resistive losses and can be calculated using [Equation 4](#).

$$P_{COND} = [(I_{RMS(HS)})^2 \times RDS_{(on)HS}] + [(I_{RMS(LS)})^2 \times RDS_{(on)LS}]$$

where

- $RDS_{(on)HS}$  is the high-side GaN FET on-resistance

- $RDS_{(on)LS}$  is the low-side GaN FET on-resistance

- $I_{RMS(HS)}$  is the high-side GaN FET RMS current

- $I_{RMS(LS)}$  and low-side GaN FET RMS current

(4)

The switching losses can be computed to a first order using  $t_{TR}$  can be approximated by dividing  $V_{IN}$  by 25V/ns, which is a conservative estimate of the switched node slew rate. [Equation 5](#).

$$P_{SW} = V_{IN} \times I_{OUT} \times f_{SW} \times t_{TR}$$

where

- $t_{TR}$  is the switch transition time from ON to OFF and from OFF to ON

(5)

Note that the low-side FET does not suffer from this loss. The third quadrant loss in the low-side device is ignored in this first order loss calculation.

As described previously, switching frequency has a direct effect on device power dissipation. Although the gate driver of the LMG5200 device is capable of driving the GaN FETs at frequencies up to 10 MHz, careful consideration must be applied to ensure that the running conditions for the device meet the recommended operating temperature specification. Specifically, hard-switched topologies tend to generate more losses and self-heating than soft-switched applications.

The sum of the driver loss, the bootstrap diode loss, and the switching and conduction losses in the GaN FETs is the total power loss of the device. Careful board layout with an adequate amount of thermal vias close to the power pads (VIN and PGND) allows optimum power dissipation from the package. A top-side mounted heat sink with airflow can also improve the package power dissipation.

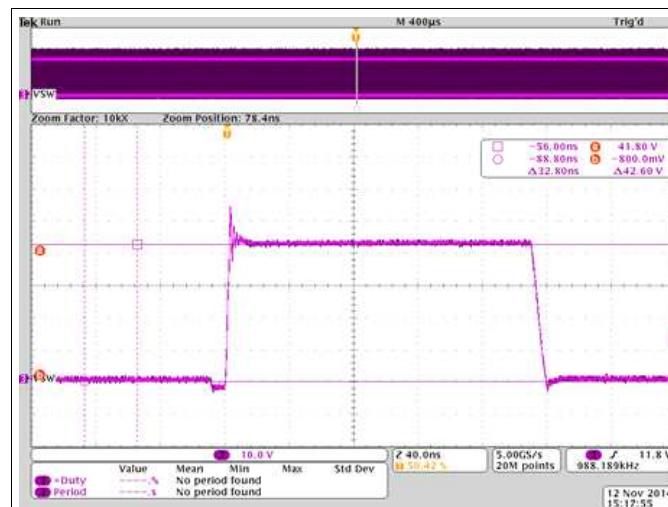

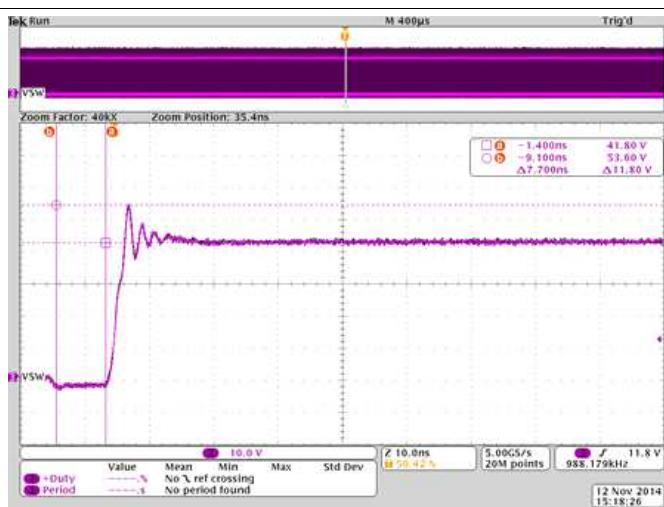

### 9.2.3 Application Curves

Figure 12. SW Node Behavior Showing the Dead Time

Figure 13. Zoom-In Showing the Dead Time of 7.7 ns and the Overshoot of the SW Node

## 10 Power Supply Recommendations

The recommended bias supply voltage range for LMG5200 is from 4.75 V to 5.25 V. The lower end of this range is governed by the internal undervoltage lockout (UVLO) protection feature of the  $V_{CC}$  supply circuit. The upper end of this range is driven by the 6 V absolute maximum voltage rating of  $V_{CC}$ . Note that the gate voltage of the low-side GaN FET is not clamped internally. Hence, it is important to keep the  $V_{CC}$  bias supply within the recommended operating range to prevent exceeding the low-side GaN transistor gate breakdown voltage.

The UVLO protection feature also involves a hysteresis function. This means that once the device is operating in normal mode, if the  $V_{CC}$  voltage drops, the device continues to operate in normal mode as far as the voltage drop does not exceed the hysteresis specification,  $V_{CC(hyst)}$ . If the voltage drop is more than hysteresis specification, the device shuts down. Therefore, while operating at or near the 4.5 V range, the voltage ripple on the auxiliary power supply output must be smaller than the hysteresis specification of LMG5200 to avoid triggering device-shutdown.

Place a local bypass capacitor between the VDD and VSS pins. This capacitor must be located as close as possible to the device. A low ESR, ceramic surface-mount capacitor is recommended. TI recommends using 2 capacitors across VDD and GND: a 100 nF ceramic surface-mount capacitor for high frequency filtering placed very close to VDD and GND pin, and another surface-mount capacitor, 220 nF to 10  $\mu$ F, for IC bias requirements.

## 11 Layout

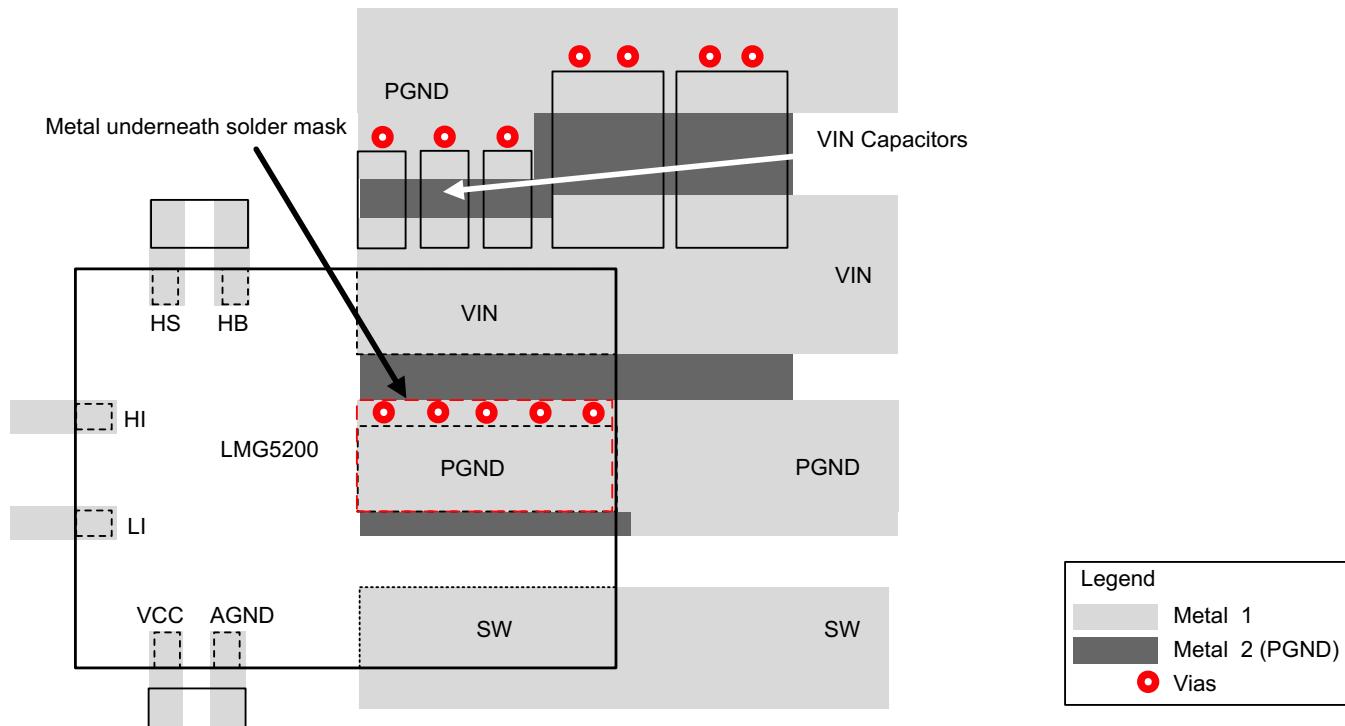

### 11.1 Layout Guidelines

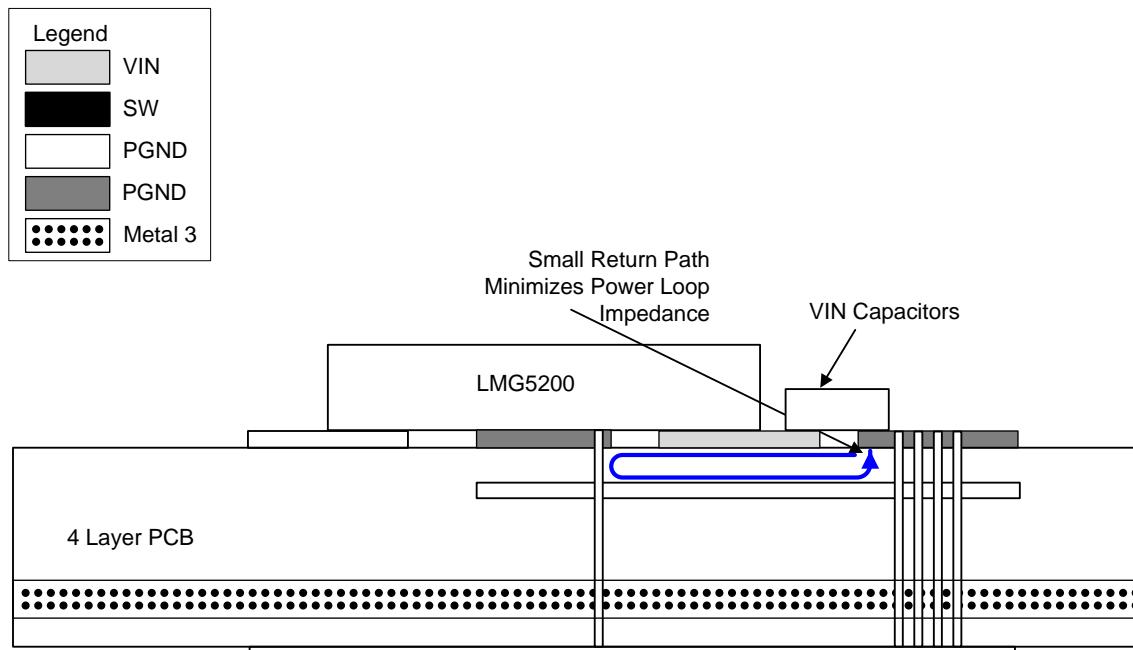

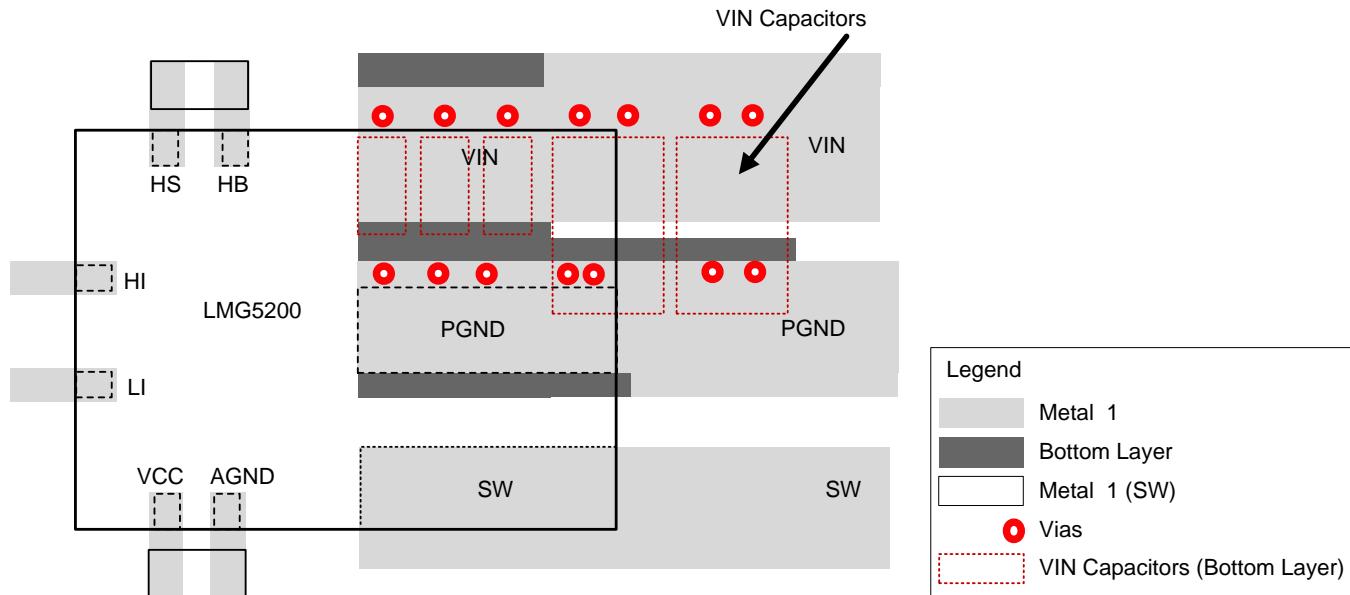

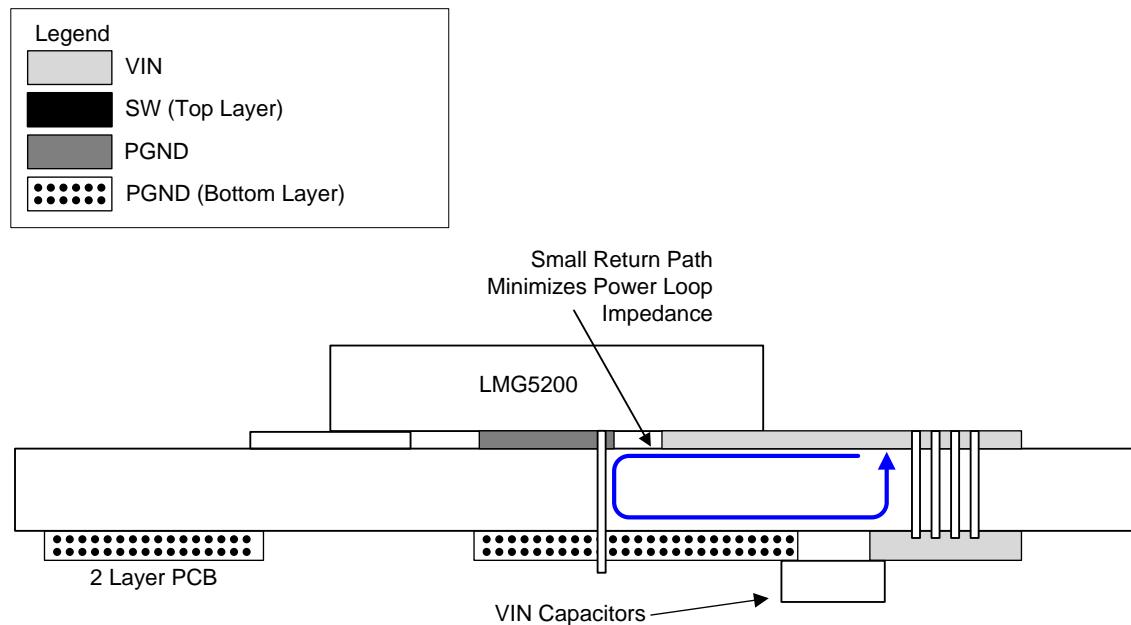

To maximize the efficiency benefits of fast switching, it is extremely important to optimize the board layout such that the power loop impedance is minimal. When using a multilayer board (more than 2 layers), power loop parasitic impedance is minimized by having the return path to the input capacitor (between VIN and PGND), small and directly underneath the first layer as shown in [Figure 14](#) and [Figure 15](#). Loop inductance is reduced due to flux cancellation as the return current is directly underneath and flowing in the opposite direction. It is also critical that the VCC capacitors and the bootstrap capacitors are as close as possible to the device and in the first layer. Carefully consider the AGND connection of LMG5200 device. It must NOT be directly connected to PGND so that PGND noise does not directly shift AGND and cause spurious switching events due to noise injected in HI and LI signals.

### 11.2 Layout Examples

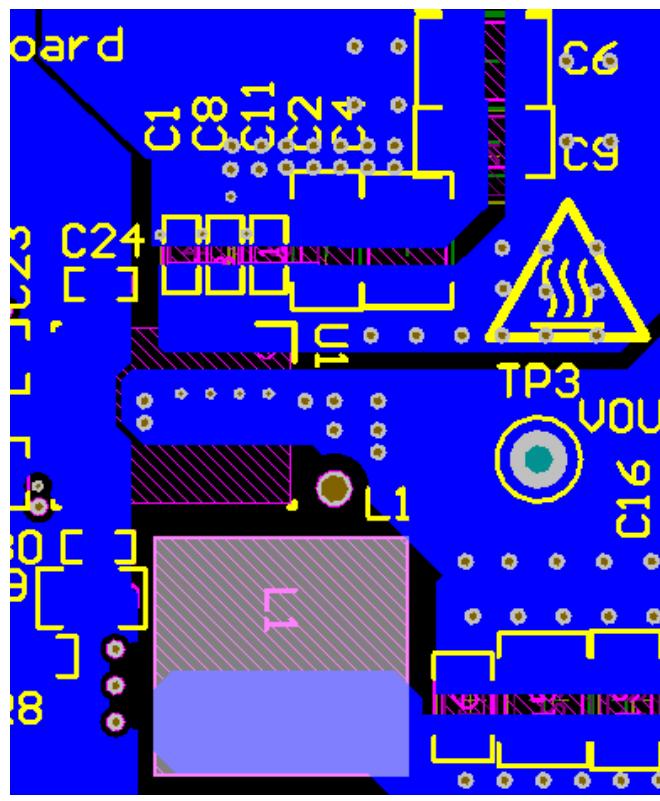

Placements shown in [Figure 14](#) and in the cross section of [Figure 15](#) show the suggested placement of the device with respect to sensitive passive components, such as VIN, bootstrap capacitors (HS and HB) and VSS capacitors. Use appropriate spacing in the layout to reduce creepage and maintain clearance requirements in accordance with the application pollution level. Inner layers if present can be more closely spaced due to negligible pollution.

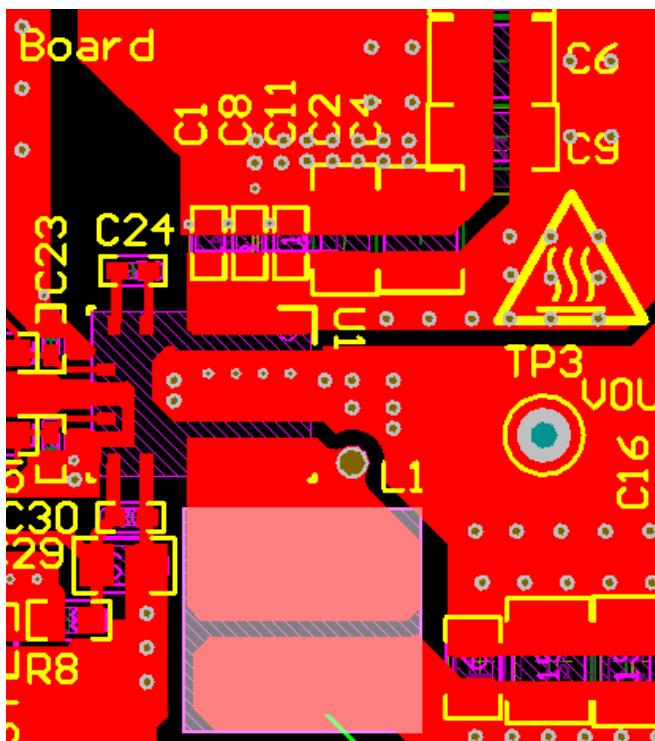

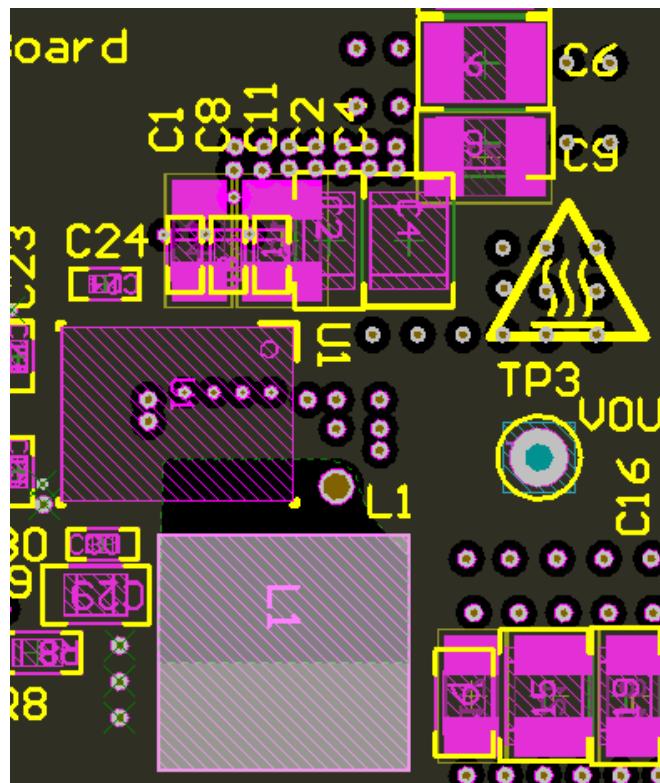

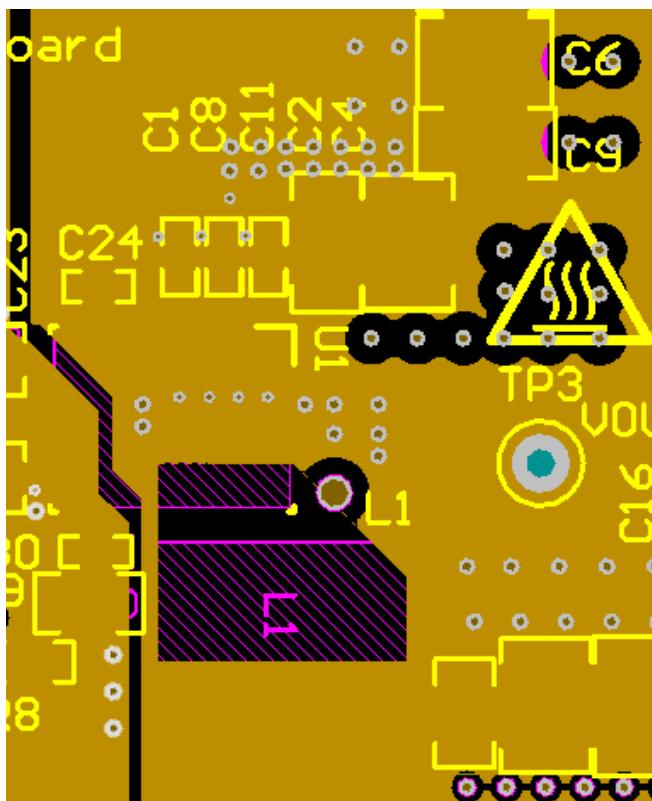

The layout must be designed to minimize the capacitance at the SW node. Use as small an area of copper as possible to connect the device SW pin to the inductor, or transformer, or other output load. Furthermore, ensure that the ground plane or any other copper plane has a cutout so that there is no overlap with the SW node, as this would effectively form a capacitor on the printed circuit board. Additional capacitance on this node reduces the advantages of the advanced packaging approach of the LMG5200 and may result in reduced performance. [Figure 16](#), [Figure 17](#), [Figure 18](#), and [Figure 19](#) show an example of how to design for minimal SW node capacitance on a four-layer board. In these figures, U1 is the LMG5200 device.

**Figure 14. External Component Placement (Single Layer)**

## Layout Examples (continued)

Figure 15. Four-Layer Board Cross Section With Return Path Directly Underneath for Power Loop

Figure 16. Top Layer

Figure 17. Ground Plane

## Layout Examples (continued)

Figure 18. Middle Layer

Figure 19. Bottom Layer

Figure 20. External Component Placement (Double Layer PCB)

## Layout Examples (continued)

**Figure 21. Two-Layer Board Cross Section With Return Path**

Two-layer boards are not recommended for use with LMG5200 device due to the larger power loop inductance. However, if design considerations allow only two board layers, place the input decoupling capacitors immediately behind the device on the back-side of the board to minimize loop inductance. [Figure 20](#) and [Figure 21](#) show a layout example for two-layer boards.

## 12 Device and Documentation Support

### 12.1 Device Support

#### 12.1.1 Development Support

[LMG5200 PSpice Transient Model](#)

[LMG5200 TINA-TI Transient Reference Design](#)

[LMG5200 TINA-TI Transient Spice Model](#)

### 12.2 Documentation Support

#### 12.2.1 Related Documentation

[Layout Guidelines for LMG5200 GaN Power Stage Module](#)

[Using the LMG5200: GaN Half-Bridge Power Module Evaluation Module](#)

### 12.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on [ti.com](http://ti.com). In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 12.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™ Online Community** **TI's Engineer-to-Engineer (E2E) Community.** Created to foster collaboration among engineers. At [e2e.ti.com](http://e2e.ti.com), you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** **TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 12.5 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 12.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.7 Glossary

[SLYZ022 — TI Glossary.](#)

This glossary lists and explains terms, acronyms, and definitions.

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### 13.1 Package Information

The LMG5200 device package is rated as an MSL3 package (Moisture Sensitivity Level 3). Refer to application report [\*AN-2029 Handling and Process Recommendations\*](#) for specific handling and process recommendations of an MSL3 package.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMG5200MOFR           | Active        | Production           | QFM (MOF)   9  | 2000   LARGE T&R      | Yes         | NIAU                                 | Level-3-260C-168 HR               | -40 to 125   | LMG5200<br>513B     |

| LMG5200MOFR.A         | Active        | Production           | QFM (MOF)   9  | 2000   LARGE T&R      | Yes         | NIAU                                 | Level-3-260C-168 HR               | -40 to 125   | LMG5200<br>513B     |

| LMG5200MOFT           | Active        | Production           | QFM (MOF)   9  | 250   SMALL T&R       | Yes         | NIAU                                 | Level-3-260C-168 HR               | -40 to 125   | LMG5200<br>513B     |

| LMG5200MOFT.A         | Active        | Production           | QFM (MOF)   9  | 250   SMALL T&R       | Yes         | NIAU                                 | Level-3-260C-168 HR               | -40 to 125   | LMG5200<br>513B     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a " ~ " will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

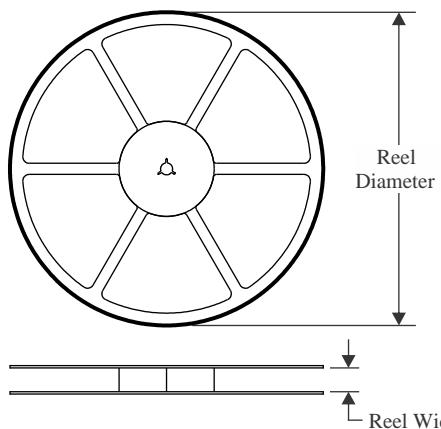

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

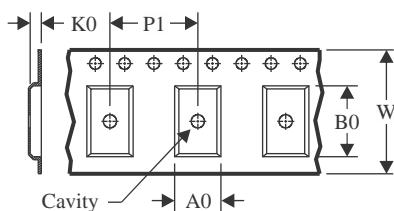

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

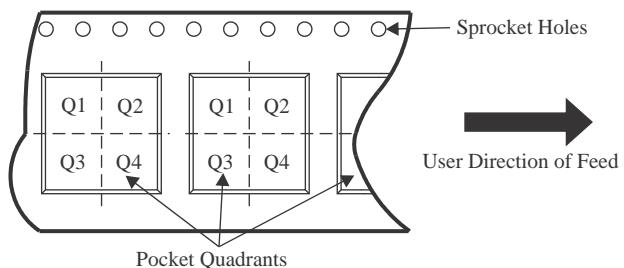

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LMG5200MOFR | QFM          | MOF             | 9    | 2000 | 330.0              | 16.4               | 6.3     | 8.3     | 2.2     | 12.0    | 16.0   | Q1            |

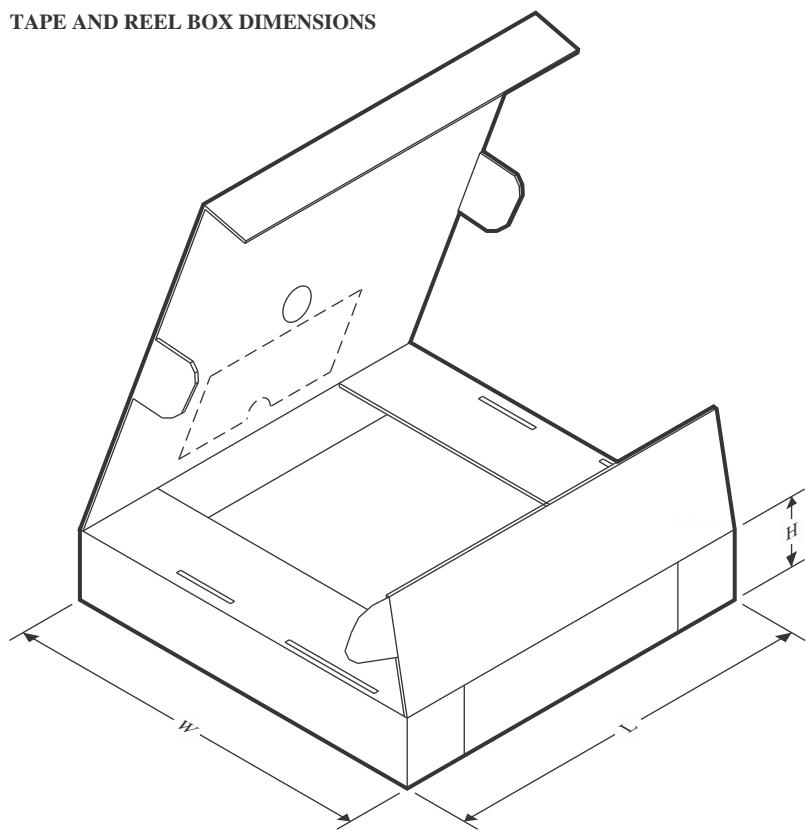

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMG5200MOFR | QFM          | MOF             | 9    | 2000 | 350.0       | 350.0      | 43.0        |

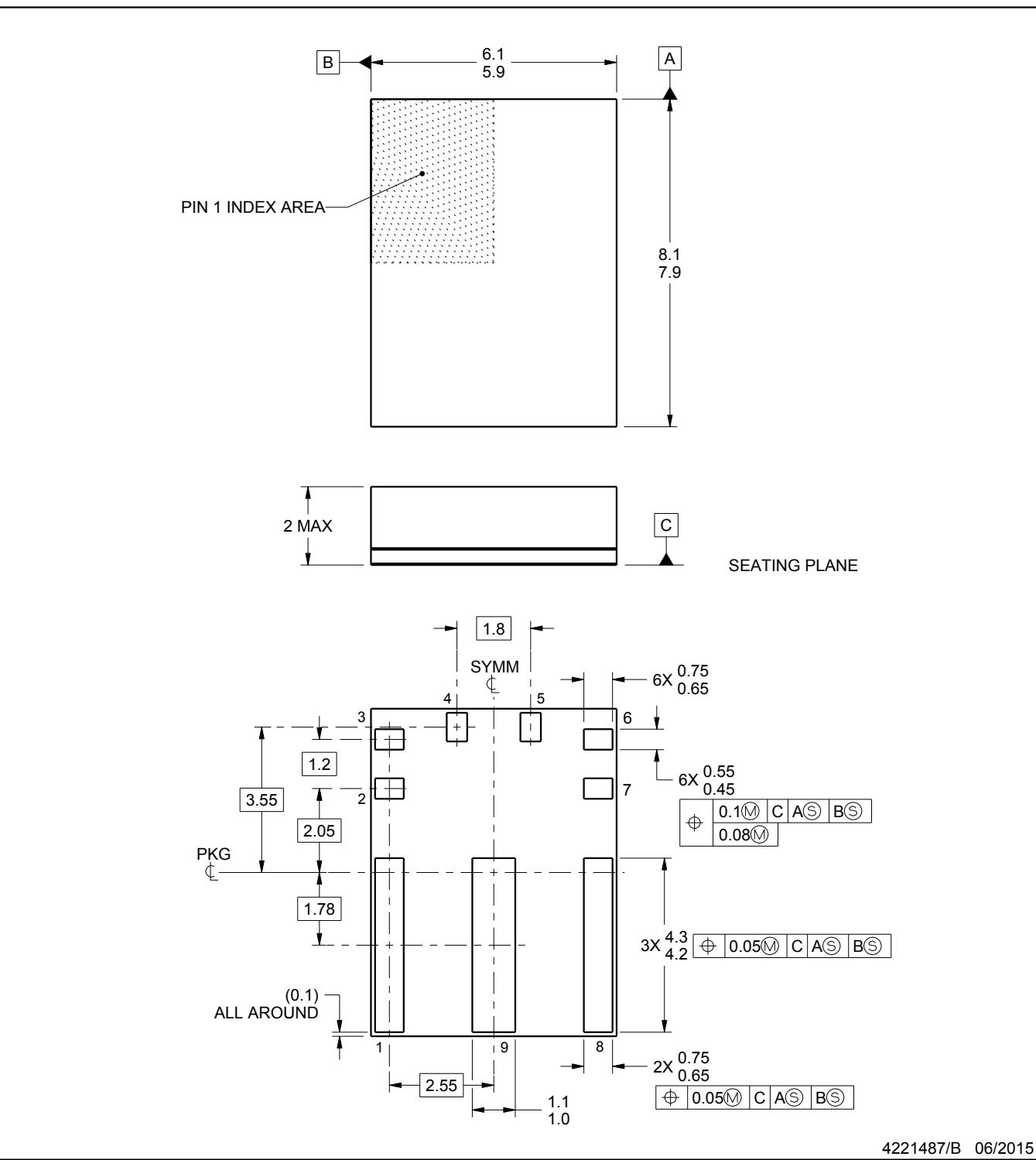

# PACKAGE OUTLINE

## QFM - 2 mm max height

QUAD FLAT MODULE

4221487/B 06/2015

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

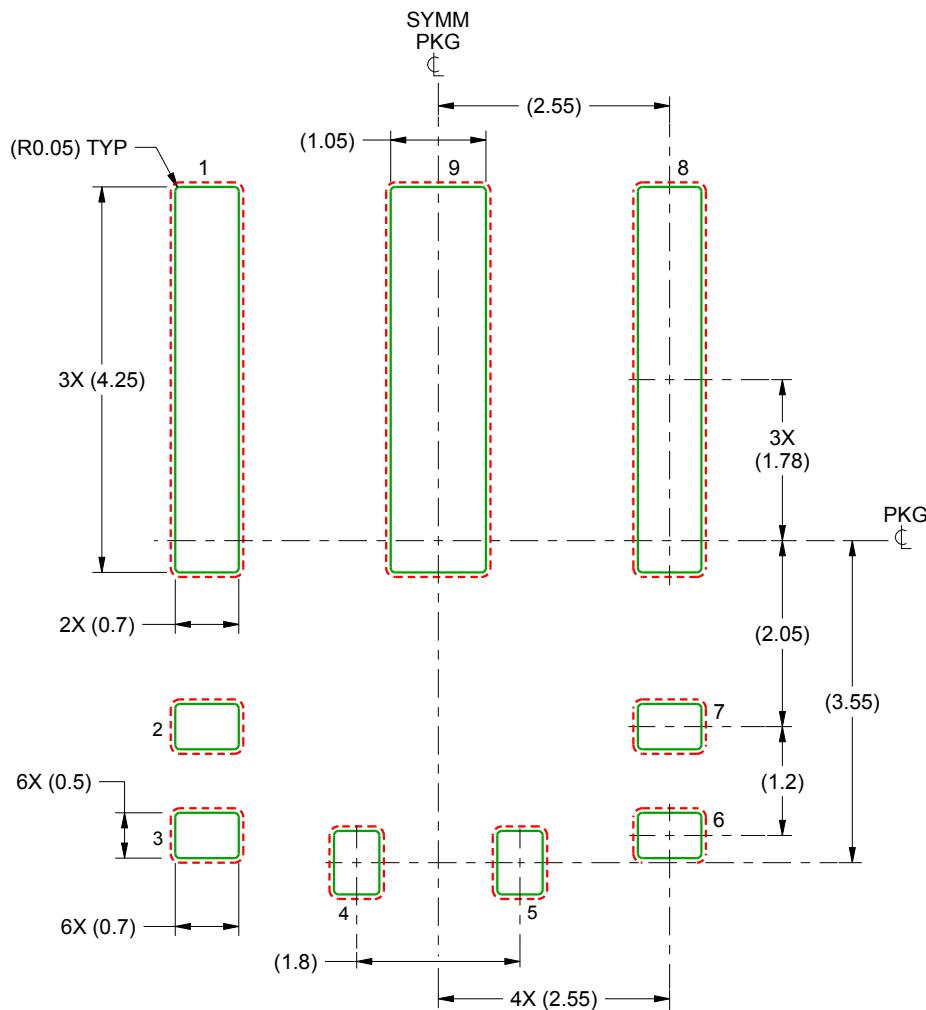

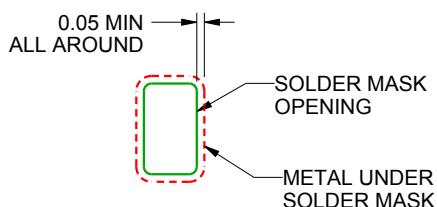

# EXAMPLE BOARD LAYOUT

MOF0009A

QFM - 2 mm max height

QUAD FLAT MODULE

LAND PATTERN EXAMPLE

SCALE:12X

SOLDER MASK DEFINED

ALL PADS

4221487/B 06/2015

NOTES: (continued)

3. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

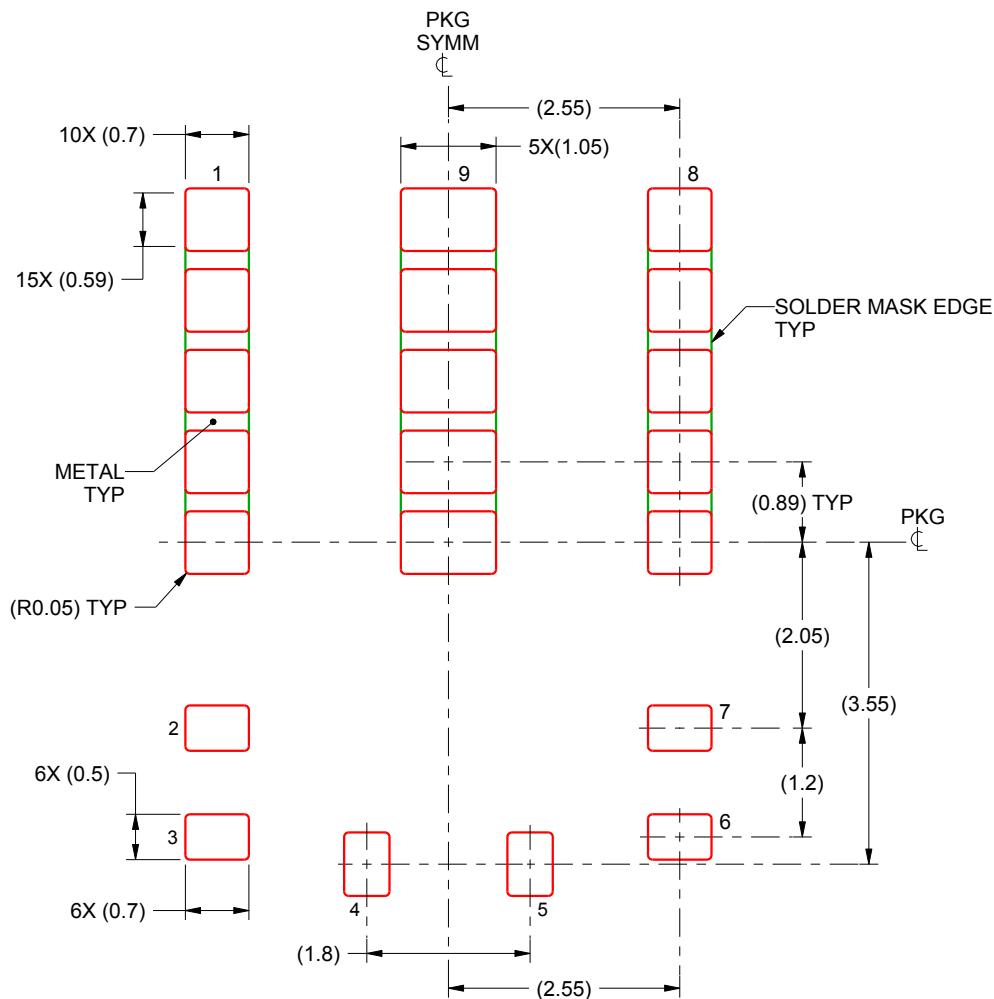

# EXAMPLE STENCIL DESIGN

MOF0009A

QFM - 2 mm max height

QUAD FLAT MODULE

4221487/B 06/2015

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to [TI's Terms of Sale](#), [TI's General Quality Guidelines](#), or other applicable terms available either on [ti.com](#) or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2026, Texas Instruments Incorporated

Last updated 10/2025