# LP3918 Battery Charge Management and Regulator Unit

Check for Samples: LP3918

## **FEATURES**

- Fully Integrated Li-Ion Battery Charger with Thermal Regulation

- USB Charge Mode

- 7 Low Noise LDO's

- 2 x 300 mA

- 3 x 150 mA

- 2 x 80 mA

- I2C Compatible Interface for Controlling LDO Outputs and Charger Operation

- Thermal Shutdown

- Under Voltage Lockout

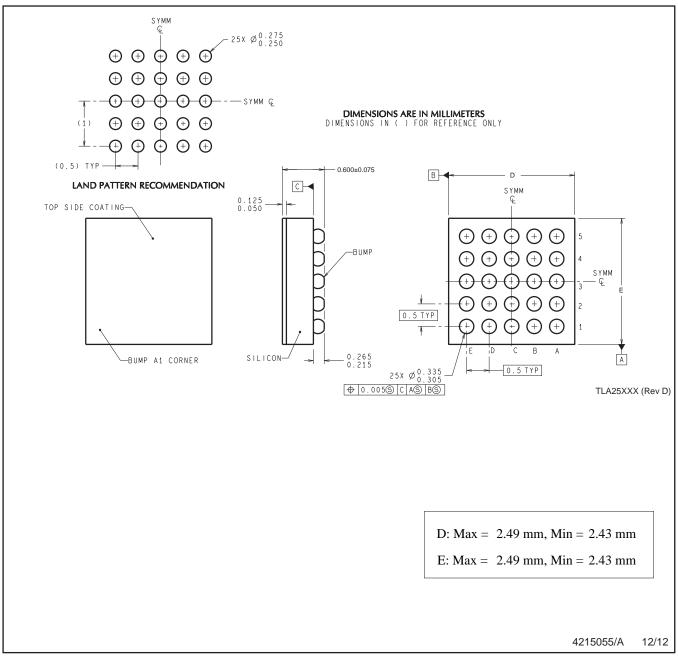

- 25-Bump Thin DSBGA Package 2.5 x 2.5 mm

- Options Available on Request, Please Contact Sales Office for Further Information;

- Level Detect on HF PWR & PWR ON

- LDO Charging Mode

- Custom Default Settings on Charger, and LDO O/P's.

## **APPLICATIONS**

- CDMA Phone Handsets

- Low Power Wireless Handsets

- Handheld Information Appliances

- Personal Media Players

- Digital Cameras

## **KEY SPECIFICATIONS**

- 50mA to 950mA Programmable Charge Current

- 3.0V to 5.5V Input Voltage Range

- 200mV Typ. Dropout Voltage on 300 mA LDO's

- 2% (Typ) Output Voltage Accuracy on LDO's

#### DESCRIPTION

The LP3918 is a fully integrated charger and multiregulator unit designed for CDMA cellular phones. The LP3918 contains a Li-lon battery charger, 7 low noise low dropout (LDO) voltage regulators and a high-speed serial interface to program on/off conditions and output voltages of individual regulators, and also to read status information from the PMU.

The Li-Ion charger integrates a power FET, reverse current blocking diode, sense resistor with current monitor output, and requires only a few external components. Charging is thermally regulated to obtain the most efficient charging rate for a given ambient temperature.

LDO regulators provide high PSRR and low noise ideally suited for supplying power to both analog and digital loads.

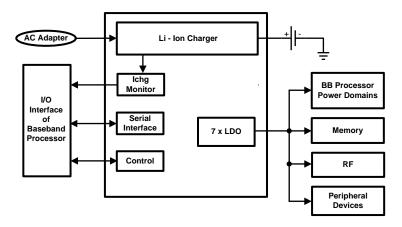

## **Functional Block Diagram**

Figure 1. Simplified Functional Block Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

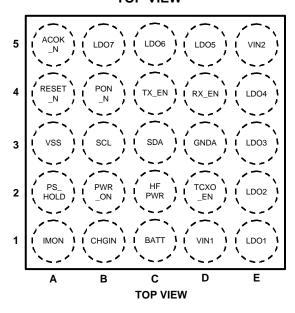

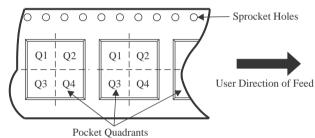

# **Device Pin Diagram**

Figure 2. LP3918 25 pin DSBGA Package TOP VIEW

## **PIN DESCRIPTION**

| Pin # | Name    | Type <sup>(1)</sup> | Description                                                                                                                                     |

|-------|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

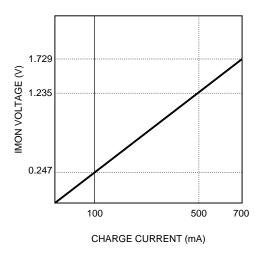

| A1    | IMON    | А                   | Charge current monitor output. This pin presents an analog voltage representation of the input charging current. VIMON(mV) = (2.47 x ICHG)(mA). |

| A2    | PS_HOLD | DI                  | Input for power control from external processor/controller.                                                                                     |

| A3    | VSS     | G                   | Digital Ground pin                                                                                                                              |

| A4    | RESET_N | DO                  | Reset Output. Pin stays LOW during power up sequence. 60ms after LDO1 (CORE) is stable this pin is asserted HIGH.                               |

| A5    | ACOK_N  | DO                  | AC Adapter indicator, LOW when 4.5V – 6.0V present at CHG_IN.                                                                                   |

| B1    | CHG_IN  | Р                   | DC power input to charger block from wall or car power adapters.                                                                                |

| B2    | PWR_ON  | DI                  | Power up sequence starts when this pin is set HIGH. Internal $500k\Omega$ pull-down resistor.                                                   |

| В3    | SCL     | DI                  | Serial Interface Clock input. External pull up resistor is needed, typ $1.5 k\Omega$                                                            |

| B4    | PON_N   | DO                  | Active low signal is PWR_ON inverted                                                                                                            |

| B5    | LDO7    | A                   | LDO7 Output (GP)                                                                                                                                |

| C1    | BATT    | Р                   | Main battery connection. Used as a power connection for current delivery to the battery.                                                        |

| C2    | HF_PWR  | DI                  | Power up sequence starts when this pin is set HIGH. Internal $500k\Omega$ pull-down resistor.                                                   |

| C3    | SDA     | DI/O                | Serial Interface, Data Input/Output Open Drain output, external pull up resistor is needed, typ 1.5k $\Omega$ .                                 |

| C4    | TX_EN   | DI                  | Enable control for LDO6 (TX). HIGH = Enable, LOW = Disable.                                                                                     |

| C5    | LDO6    | A                   | LDO6 Output (TX)                                                                                                                                |

| D1    | VIN1    | Р                   | Battery Input for LDO1 - 2                                                                                                                      |

| D2    | TCXO_EN | DI                  | Enable control for LDO4 (TCXO). HIGH = Enable, LOW = Disable.                                                                                   |

| D3    | GNDA    | G                   | Analog Ground pin                                                                                                                               |

| D4    | RX_EN   | DI                  | Enable control for LDO5 (RX). HIGH = Enable, LOW = Disable.                                                                                     |

| D5    | LDO5    | A                   | LDO5 Output (RX)                                                                                                                                |

(1) A: Analog. D: Digital. I: Input. DI/O: Digital Input/Output. G: Ground. O: Output. P: Power.

#### **PIN DESCRIPTION (continued)**

| Pin # | Name | Type <sup>(1)</sup> | Description                |

|-------|------|---------------------|----------------------------|

| E1    | LDO1 | A                   | LDO1 Output (CORE)         |

| E2    | LDO2 | A                   | LDO2 Output (DIGI)         |

| E3    | LDO3 | A                   | LDO3 Output (ANA)          |

| E4    | LDO4 | A                   | LDO4 Output (TCXO)         |

| E5    | VIN2 | Р                   | Battery Input for LDO3 - 7 |

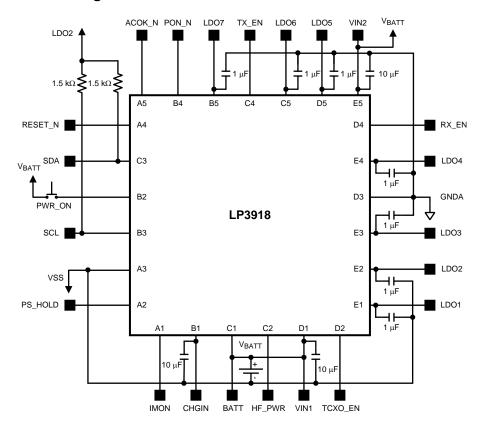

## **Applications Schematic Diagram**

Figure 3. Applications Schematic

## **Device Description**

The LP3918 Charge Management and Regulator Unit is designed to supply charger and voltage output capabilities for mobile systems, e.g. CDMA handsets. The device provides a Li-lon charging function and 7 regulated outputs. Communication with the device is via an I2C compatible serial interface that allows function control and status read-back.

The battery charge management section provides a programmable CC/CV linear charge capability. Following a normal charge cycle a maintenance mode keeps battery voltage between programmable levels. Power levels are thermally regulated to obtain optimum charge levels over the ambient temperature range.

**Charger Features**

- Pre-charge, CC, CV and Maintenance modes

- USB Charge 100mA/450mA

- Integrated FET

- Integrated Reverse Current Blocking Diode

- · Integrated Sense Resistor

- Thermal regulation

- Charge Current Monitor Output

- Programmable charge current 50mA 950mA with 50mA steps

- · Default CC mode current 100mA

- Pre-charge current fixed 50mA

- Termination voltage 4.1V, 4.2V (default), 4.3V, and 4.4V, accuracy better than +/- 0.5% (typ)

- Restart level 50mV, 100mV, 150mV (default) and 200mV below Termination voltage

- End of Charge 0.1C (default), 0.15C, 0.2C and 0.25C

- Programmable Enable Control

- Safety timer

- Input voltage operating range 4.5V 6.0V

- LDO mode on LP3918TL-L option.

#### **REGULATORS**

7 Low dropout linear regulators provide programmable voltage outputs with current capabilities of 80mA, 150mA and 300mA as given in the table below. LDO1, LDO2 and LDO3 are powered up by default with LDO1 reaching regulation before LDO2 and LDO3 are started. LDO1, LDO3 and LDO7 can be disabled/enabled via the serial interface. During power up LDO1 and LDO2 must reach their regulation voltage detection point for the device to power up and remain powered. LDO4, LDO5 and LDO6 have external enable pins and may power up following LDO2 as determined by their respective enable. Under voltage lockout oversees device start up with preset level of 2.85V(typ).

#### POWER SUPPLY CONFIGURATIONS

At PMU start up, LDO1, LDO2 and LDO3 are always started with their default voltages. The start up sequence of the LDO's is given below.

Startup Sequence

LDO1 -> LDO2 -> LDO3

LDO's with external enable control (LDO4, LDO5, LDO6) start immediately after LDO2 if enabled by logic high at their respective control inputs.

LDO7 (and LDO1 and 3) may be programmed to enable/disable once PS HOLD has been asserted.

Default voltages for the LDOs are shown in Table 1 and Table 2 shows the voltages that may be programmed via the Serial Interface.

### **DEVICE PROGRAMMABILITY**

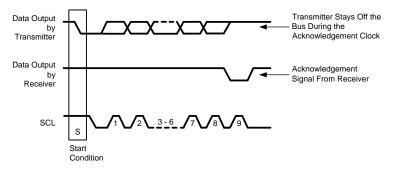

An I<sup>2</sup>C compatible Serial Interface is used to communicate with the device to program a series of registers and also to read status registers. These internal registers allow control over LDO outputs and their levels. The charger functions may also be programmed to alter termination voltage, end of charge current, charger restart voltage, full rate charge current, and also the charging mode.

This device internal logic is powered from LDO2.

**Table 1. LDO Default Voltages**

| LDO | Function | mA  | Default Voltage (V) | Startup Default | Enable Control |

|-----|----------|-----|---------------------|-----------------|----------------|

| 1   | CORE     | 300 | 1.8                 | ON              | SI             |

| 2   | DIGI     | 300 | 3.0                 | ON              | -              |

| 3   | ANA      | 80  | 3.0                 | ON              | SI             |

| 4   | TCXO     | 80  | 3.0                 | OFF             | TCXO_EN        |

| 5   | RX       | 150 | 3.0                 | OFF             | RX_EN          |

| 6   | TX       | 150 | 3.0                 | OFF             | TX_EN          |

| 7   | GP       | 150 | 3.0                 | OFF             | SI             |

### Table 2. LDO Output Voltages Selectable via Serial Interface

|   | LDO  | mA  | 1.5 | 1.8 | 1.85 | 2.5 | 2.6 | 2.7 | 2.75 | 2.8 | 2.85 | 2.9 | 2.95 | 3.0 | 3.05 | 3.1 | 3.2 | 3.3 |

|---|------|-----|-----|-----|------|-----|-----|-----|------|-----|------|-----|------|-----|------|-----|-----|-----|

| 1 | CORE | 300 | +   | +   | +    | +   | +   | +   | +    | +   | +    | +   | +    | +   | +    | +   | +   | +   |

| 2 | DIGI | 300 |     |     |      | +   | +   | +   | +    | +   | +    | +   | +    | +   | +    | +   | +   | +   |

| 3 | ANA  | 80  |     |     |      |     |     | +   | +    | +   | +    | +   | +    | +   | +    |     |     |     |

| 4 | TCXO | 80  | +   | +   | +    | +   | +   | +   | +    | +   | +    | +   | +    | +   | +    | +   | +   | +   |

| 5 | RX   | 150 |     |     |      |     |     | +   | +    | +   | +    | +   | +    | +   | +    |     |     |     |

| 6 | TX   | 150 |     |     |      |     |     | +   | +    | +   | +    | +   | +    | +   | +    |     |     |     |

| 7 | GP   | 150 | +   | +   | +    | +   | +   | +   | +    | +   | +    | +   | +    | +   | +    | +   | +   | +   |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1) (2)(3)

| - 100 0 10 10 11 10 11 1 1 1 1 1 1 1 1 1                       |                                           |

|----------------------------------------------------------------|-------------------------------------------|

| CHG-IN,                                                        | -0.3 to +6.5V                             |

| VBATT =VIN1/2, BATT,HF_PWR                                     | -0.3 to +6V                               |

| All other Inputs                                               | -0.3 to V <sub>BATT</sub> +0.3V, max 6.0V |

| Junction Temperature (T <sub>J-MAX</sub> )                     | 150°C                                     |

| Storage Temperature                                            | -40°C to +150°C                           |

| Max Continuous Power Dissipation (4) (P <sub>D-MAX</sub> ) (5) | Internally Limited                        |

| ESD (6)                                                        |                                           |

| Batt, VIN1, VIN2, HF_PWR, CHG_IN, PWR_ON                       | 8kV HBM                                   |

| All other pins                                                 | 2kV HBM                                   |

- (1) All voltages are with respect to the potential at the GND pin.

- Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is specified. Operating Ratings do not imply performance limits. For performance limits and associated test conditions, see the Electrical Characteristics tables.

- If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- Care must be exercised where high power dissipation is likely. The maximum ambient temperature may have to be derated. Like the Absolute Maximum power dissipation, the maximum power dissipation for operation depends on the ambient temperature. In applications where high power dissipation and/or poor thermal dissipation exists, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A\_MAX</sub>) is dependent on the maximum power dissipation of the device in the application  $(P_{D MAX})$ , and the junction to ambient thermal resistance of the device/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A\_MAX} = T_{J\_MAX-OP} - (\theta_{JA} \times P_{DMAX})$ Internal Thermal Shutdown circuitry protects the device from permanent damage.

- The human-body model is 100pF discharged through 1.5kΩ. The machine model is a 200pF capacitor discharged directly into each pin, MIL-STD-883 3015.7.

# Operating Ratings (1)(2)

| -                                                         |                                  |

|-----------------------------------------------------------|----------------------------------|

| CHG_IN                                                    | 4.5 to 6.0V                      |

| VBATT =VIN1/2, BATT                                       | 3.0 to 5.5V                      |

| HF_PWR, PWR_ON                                            | 0V to 5.5V                       |

| ACOK_N, SDA, SCL, RX_EN, TX_EN, TCXO_EN, PS_HOLD, RESET_N | 0V to (V <sub>LDO2</sub> + 0.3V) |

| All other pins                                            | 0V to (V <sub>BATT</sub> + 0.3V) |

| Junction Temperature (T <sub>J</sub> )                    | −40°C to +125°C                  |

| Ambient Temperature (T <sub>A</sub> )                     | -40 to 85°C                      |

- (1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is specified. Operating Ratings do not imply performance limits. For performance limits and associated test conditions, see the Electrical Characteristics tables.

- (2) All voltages are with respect to the potential at the GND pin.

# Thermal Properties (1)

| Junction to Ambient Thermal Resistance $\theta_{JA}$ |        |

|------------------------------------------------------|--------|

| Jedec Standard Thermal PCB                           | 37°C/W |

| 4L Cellphone Board                                   | 66°C/W |

(1) Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from thermal modelling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The value of (θ<sub>JA</sub>) of this product could fall within a wide range, depending on PWB material, layout, and environmental conditions. In applications where high maximum power dissipation exists (high V<sub>IN</sub>, high I<sub>OUT</sub>), special care must be paid to thermal dissipation issues in board design.

# **General Electrical Characteristics**

Unless otherwise noted,  $V_{IN}$  ( = VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a = T_J = -40$ °C to +125°C. (1)

| Symbol              | Parameter                  | Condition                                                                          | Tum  | Liı                    | mit                    | Units |

|---------------------|----------------------------|------------------------------------------------------------------------------------|------|------------------------|------------------------|-------|

|                     | Parameter                  | Condition                                                                          | Тур  | Min                    | Max                    | Units |

| Q(STANDBY)          | Standby Supply Current     | V <sub>IN</sub> = 3.6V, UVLO on, internal logic circuit on, all other circuits off | 2    |                        | 10                     | μΑ    |

| Power Monitor Fu    | unctions                   |                                                                                    |      | •                      |                        |       |

| Battery Under-Volt  | age Lockout                |                                                                                    |      |                        |                        |       |

| V <sub>UVLO-R</sub> | Under Voltage Lock-out     | V <sub>IN</sub> Rising                                                             | 2.85 | 2.7                    | 3.0                    | V     |

| Thermal Shutdow     | /n                         |                                                                                    |      |                        |                        |       |

|                     | TSD Threshold              | (2)                                                                                | 160  |                        |                        | °C    |

| LOGIC AND CON       | TROL INPUTS (LDO2 at 3.0V) |                                                                                    |      | •                      |                        |       |

| V <sub>IL</sub>     | Input Low Level            | PS_HOLD, SDA, SCL,<br>RX_EN, TCXO_EN, TX_EN                                        |      |                        | 0.25×V <sub>LDO2</sub> | V     |

|                     |                            | PWR_ON, HF_PWR                                                                     |      |                        | 0.25×V <sub>BATT</sub> | V     |

| V <sub>IH</sub>     | Input High Level           | PS_HOLD, SDA, SCL,<br>RX_EN, TCXO_EN, TX_EN                                        |      | 0.75×V <sub>LDO2</sub> |                        | V     |

|                     |                            | PWR_ON, HF_PWR                                                                     |      | 0.75×V <sub>BATT</sub> |                        | V     |

| I <sub>IL</sub>     | Logic Input Current        | All logic inputs except PWR_ON and HF_PWR                                          |      | -5                     | +5                     | μΑ    |

|                     |                            | $0V \le V_{INPUT} \le V_{BATT}$                                                    |      |                        |                        |       |

| R <sub>IN</sub>     | Input Resistance           | PWR_ON, HF_PWR Pull-<br>Down resistance to GND <sup>(2)</sup>                      | 500  |                        |                        | kΩ    |

| LOGIC AND CON       | TROL OUTPUTS (LDO2 at 3.0  | V)                                                                                 |      |                        |                        |       |

| V <sub>OL</sub>     | Output Low Level           | PON_N, RESET_N, SDA,<br>ACOK_N                                                     |      |                        | 0.25×V <sub>LDO2</sub> | V     |

|                     |                            | I <sub>OUT</sub> = 2mA                                                             |      |                        |                        |       |

| V <sub>OH</sub>     | Output High Level          | PON_N, RESET_N,<br>ACOK_N                                                          |      | 0.75×V <sub>LDO2</sub> |                        | V     |

|                     |                            | I <sub>OUT</sub> = 2mA                                                             |      |                        |                        |       |

|                     |                            | (Not applicable to Open Drain Output SDA)                                          |      |                        |                        |       |

<sup>(1)</sup> All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(2)</sup> Specified by design. Not production tested.

www.ti.com

## LDO1 (CORE) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$  ( = VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F.  $V_{OUT1}$  set to 3.0V output. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT1}$ + 0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a$  =  $T_J$  = -40°C to +125°C.

|                        |                          | 0 1111                                            | _   | Li  | mit |               |

|------------------------|--------------------------|---------------------------------------------------|-----|-----|-----|---------------|

| Symbol                 | Parameter                | Condition                                         | Тур | Min | Max | Units         |

| V <sub>OUT1</sub>      | Output Voltage Accuracy  | I <sub>OUT1</sub> = 1mA, V <sub>OUT1</sub> = 3.0V |     | -2  | +2  | %             |

|                        |                          |                                                   |     | -3  | +3  |               |

|                        | Output Voltage           | Default                                           | 1.8 |     |     | V             |

| I <sub>OUT1</sub>      | Output Current           | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$     |     |     | 300 | mA            |

|                        | Output Current Limit     | V <sub>OUT1</sub> = 0V                            | 600 |     |     |               |

| V <sub>DO1</sub>       | Dropout Voltage          | I <sub>OUT1</sub> = 300mA, <sup>(2)</sup>         | 200 |     | 280 | mV            |

| ΔV <sub>OUT1</sub>     | Line Regulation          | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$     | 2   |     |     | mV            |

|                        |                          | I <sub>OUT1</sub> = 1mA                           |     |     |     |               |

|                        | Load Regulation          | 1mA≤ I <sub>OUT1</sub> ≤ 300mA                    | 20  |     |     | mV            |

| e <sub>n1</sub>        | Output Noise Voltage     | 10Hz≤ f≤ 100KHz,                                  | 45  |     |     | $\mu V_{RMS}$ |

|                        |                          | $C_{OUT = 1\mu F}^{(3)}$                          |     |     |     |               |

| PSRR                   | Power Supply Rejection   | $F = 10kHz$ , $C_{OUT} = 1\mu F$                  | 65  |     |     | dB            |

|                        | Ratio                    | I <sub>OUT1</sub> = 20mA <sup>(3)</sup>           |     |     |     |               |

| t <sub>START-UP</sub>  | Start-Up Time from Shut- | $C_{OUT} = 1\mu F, I_{OUT1} = 300 \text{mA}$      | 60  |     | 170 | μs            |

|                        | down                     | (3)                                               |     |     |     |               |

| T <sub>Transient</sub> | Start-Up Transient       | $C_{OUT} = 1\mu F, I_{OUT1} = 300 \text{mA}$      | 60  |     | 120 | mV            |

| Transion               | Overshoot                | (3)                                               |     |     |     |               |

- (1) All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

- (2) Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 3.0V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

- (3) Specified by design. Not production tested.

## **LDO2 (DIGI) Electrical Characteristics**

Unless otherwise noted,  $V_{IN}$  (= VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT2}$ + 0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a = T_J = -40$ °C to +125°C. (1)

| Complete          | Donomoton               | Comdition                                     | T   | Li  | mit | Unita |

|-------------------|-------------------------|-----------------------------------------------|-----|-----|-----|-------|

| Symbol            | Parameter               | Condition                                     | Тур | Min | Max | Units |

| V <sub>OUT2</sub> | Output Voltage Accuracy | $I_{OUT2} = 1mA, V_{OUT2} = 3.0V$             |     | -2  | +2  | %     |

|                   |                         |                                               |     | -3  | +3  |       |

|                   | Output Voltage          | Default                                       | 3.0 |     |     | V     |

| I <sub>OUT2</sub> | Output Current          | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$ |     |     | 300 | mA    |

|                   | Output Current Limit    | $V_{OUT2} = 0V$                               | 600 |     |     |       |

| $V_{DO2}$         | Dropout Voltage         | $I_{OUT2} = 300 \text{mA}^{(2)}$              | 200 |     | 280 | mV    |

| $\Delta V_{OUT2}$ | Line Regulation         | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$ | 2   |     |     | mV    |

|                   |                         | $I_{OUT2} = 1mA$                              |     |     |     |       |

|                   | Load Regulation         | 1mA≤ I <sub>OUT2</sub> ≤ 300mA                | 20  |     |     | mV    |

<sup>(1)</sup> All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

<sup>(2)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 3.0V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

## LDO2 (DIGI) Electrical Characteristics (continued)

Unless otherwise noted,  $V_{IN}$  (= VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT2}$ + 0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a = T_J = -40$ °C to +125°C. (1)

| Comple ed              | Donomoton                | Condition                                    | T   | Limit |     | Units         |

|------------------------|--------------------------|----------------------------------------------|-----|-------|-----|---------------|

| Symbol                 | Parameter                | Condition                                    | Тур | Min   | Max | Units         |

| e <sub>n2</sub>        | Output Noise Voltage     | 10Hz≤ f≤ 100KHz,                             | 45  |       |     | $\mu V_{RMS}$ |

|                        |                          | $C_{OUT = 1\mu F}^{(3)}$                     |     |       |     |               |

| PSRR                   | Power Supply Rejection   | $F = 10kHz$ , $C_{OUT} = 1\mu F$             | 65  |       |     | dB            |

|                        | Ratio                    | $I_{OUT2} = 20 \text{mA}^{(3)}$              |     |       |     |               |

| t <sub>START-UP</sub>  | Start-Up Time from Shut- | $C_{OUT} = 1\mu F, I_{OUT2} = 300 \text{mA}$ | 40  |       | 60  | μs            |

|                        | down                     | (3)                                          |     |       |     |               |

| t <sub>Transient</sub> | Start-Up Transient       | $C_{OUT} = 1\mu F$ , $I_{OUT2} = 300 mA$     | 5   |       | 30  | mV            |

|                        | Overshoot                | (3)                                          |     |       |     |               |

<sup>(3)</sup> Specified by design. Not production tested.

## LDO3 (ANA), LDO4 (TCXO) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$  (= VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F. TCXO\_EN high. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT3/4}$  + 0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a$  =  $T_J$  = -40°C to +125°C. (1)

|                                       |                                 |                                               | _   | Li  | mit |                   |

|---------------------------------------|---------------------------------|-----------------------------------------------|-----|-----|-----|-------------------|

| Symbol                                | Parameter                       | Condition                                     | Тур | Min | Max | Units             |

| V <sub>OUT3</sub> , V <sub>OUT4</sub> | Output Voltage Accuracy         | $I_{OUT3/4} = 1mA, V_{OUT3/4} = 3.0V$         |     | -2  | +2  | %                 |

|                                       |                                 |                                               |     | -3  | +3  |                   |

|                                       | Output Voltage                  | LDO3 default                                  | 3.0 |     |     | V                 |

|                                       |                                 | LDO4 default                                  | 3.0 |     |     |                   |

| I <sub>OUT3</sub> , I <sub>OUT4</sub> | Output Current                  | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$ |     |     | 80  | mA                |

|                                       | Output Current Limit            | V <sub>OUT3/4</sub> = 0V                      | 160 |     |     |                   |

| V <sub>DO3</sub> , V <sub>DO4</sub>   | Dropout Voltage                 | I <sub>OUT3/4</sub> = 80mA <sup>(2)</sup>     | 180 |     | 220 | mV                |

| $\Delta V_{OUT3}$ , $\Delta V_{OUT4}$ | Line Regulation                 | $V_{\text{INMIN}} \le V_{\text{IN}} \le 5.5V$ | 2   |     |     | mV                |

|                                       |                                 | $I_{OUT3/4} = 1mA$                            |     |     |     |                   |

|                                       | Load Regulation                 | 1mA≤ I <sub>OUT3/4</sub> ≤ 80mA               | 20  |     |     | mV                |

| e <sub>n3,</sub> e <sub>n4</sub>      | Output Noise Voltage            | 10Hz ≤ f ≤ 100kHz,                            | 45  |     |     | μV <sub>RMS</sub> |

|                                       |                                 | $C_{OUT = 1\mu F}^{(3)}$                      |     |     |     |                   |

| PSRR                                  | Power Supply Rejection          | $F = 10kHz$ , $C_{OUT} = 1\mu F$              | 65  |     |     | dB                |

|                                       | Ratio                           | I <sub>OUT3/4</sub> = 20mA <sup>(3)</sup>     |     |     |     |                   |

| t <sub>START-UP</sub>                 | Start-Up Time from Shut-down    | $C_{OUT} = 1\mu F, I_{OUT3/4} = 80\text{mA}$  | 40  |     | 60  | μs                |

| t <sub>Transient</sub>                | Start-Up Transient<br>Overshoot | $C_{OUT} = 1\mu F, I_{OUT3/4} = 80\text{mA}$  | 5   |     | 30  | mV                |

<sup>(1)</sup> All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

## LDO5 (RX), LDO6 (TX), LDO7 (GP) Electrical Characteristics

Unless otherwise noted,  $V_{IN}$  ( = VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F. RX\_EN, TX\_EN high. LDO7 Enabled via Serial Interface. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT5/6/7}$  + 0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for

<sup>(2)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 3.0V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

<sup>(3)</sup> Specified by design. Not productino tested.

# LDO5 (RX), LDO6 (TX), LDO7 (GP) Electrical Characteristics (continued)

Unless otherwise noted,  $V_{IN}$  (= VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F. RX\_EN, TX\_EN high. LDO7 Enabled via Serial Interface. Note  $V_{INMIN}$  is the greater of 3.0V or  $V_{OUT5/6/7}$  + 0.5V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a$  =  $T_J$  = -40°C to +125°C. (1)

operation,  $T_a = T_J = -40$ °C to +125°C. (1)

| 0                                                         | D                                                             | 0                                                   | <b>T</b> | Lir | mit | 11-24-                                          |

|-----------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------|----------|-----|-----|-------------------------------------------------|

| Symbol                                                    | Parameter                                                     | Condition                                           | Тур      | Min | Max | Wnits % V  mA  mV  mV  μV <sub>RMS</sub> dB  μs |

| V <sub>OUT5</sub> , V <sub>OUT6</sub> ,                   | Output Voltage                                                | $I_{OUT5/6/7} = 1mA, V_{OUT5/6/7} =$                |          | -2  | +2  | %                                               |

| V <sub>OUT7</sub>                                         |                                                               | 3.0V                                                |          | -3  | +3  |                                                 |

|                                                           | Output Voltage                                                | LDO5 default                                        | 3.0      | 3.0 |     | V                                               |

|                                                           |                                                               | LDO6 default                                        | 3.0      |     |     | %  V  mA  mV  mV  μV <sub>RMS</sub> dB          |

|                                                           |                                                               | LDO7 default                                        | 3.0      |     |     |                                                 |

| I <sub>OUT5</sub> , I <sub>OUT6</sub> ,                   | 6, Output Current V <sub>INMIN</sub> ≤ V <sub>IN</sub> ≤ 5.5V |                                                     |          |     | 150 | mA                                              |

| I <sub>OUT7</sub>                                         | Output Current Limit                                          | V <sub>OUT5/6/7</sub> = 0V                          | 300      |     |     |                                                 |

| V <sub>DO5</sub> , V <sub>DO6</sub> ,<br>V <sub>DO7</sub> | Dropout Voltage                                               | I <sub>OUT5/6/7</sub> = 150mA <sup>(2)</sup>        | 180      |     | 240 | mV                                              |

| $\Delta V_{OUT5}$ ,                                       | Line Regulation                                               | $V_{INMIN} \le V_{IN} \le 5.5V$                     | 2        |     |     | mV                                              |

| $\Delta V_{OUT6}$ , $\Delta V_{OUT7}$                     |                                                               | $I_{OUT5/6/7} = 1mA$                                |          |     |     | mV<br>mV                                        |

|                                                           | Load Regulation                                               | 1mA≤ I <sub>OUT5/6/7</sub> ≤ 150mA                  | 20       |     |     | mV                                              |

| e <sub>n5</sub> , e <sub>n6</sub> , e <sub>n7</sub>       | Output Noise Voltage                                          | 10Hz ≤ f ≤ 100kHz,                                  | 45       |     |     | $\mu V_{RMS}$                                   |

|                                                           |                                                               | C <sub>OUT</sub> = 1µF <sup>(3)</sup>               |          |     |     | mV<br>μV <sub>RMS</sub>                         |

| PSRR                                                      | Power Supply Rejection                                        | $F = 10kHz$ , $C_{OUT} = 1\mu F$                    | 65       |     |     | dB                                              |

|                                                           | Ratio                                                         | I <sub>OUT5/6/7</sub> = 20mA <sup>(3)</sup>         |          |     |     | %  V  MA  MV  MV  μV <sub>RMS</sub> dB  μs      |

| t <sub>START-UP</sub>                                     | Start-Up Time from Shut-<br>down                              | $C_{OUT} = 1\mu F, I_{OUT5/6/7} = 150mA$            | 40       |     | 60  | μs                                              |

| t <sub>Transient</sub>                                    | Start-Up Transient<br>Overshoot                               | $C_{OUT} = 1\mu F$ , $I_{OUT5/6/7} = 150 \text{mA}$ | 5        |     | 30  | mV                                              |

<sup>(1)</sup> All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(3) Specified by design. Not production tested.

10

<sup>(2)</sup> Dropout voltage is the input-to-output voltage difference at which the output voltage is 100mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 3.0V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

# **Charger Electrical Characteristics**

Unless otherwise noted,  $V_{CHG-IN}=5V$ ,  $V_{IN}$  ( = VIN1 = VIN2 = BATT) = 3.6V. $C_{CHG\_IN}=10\mu F$ ,  $C_{BATT}=30\mu F$ . Charger set to default settings unless otherwise noted. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a=T_J=-25^{\circ}C$  to +85°C. (1)(2)

| Cumbal                                       | Doromotor                                            | Condition                                                                                                        |                    | Typ               | Limit |       | Units  |

|----------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|-------|-------|--------|

| Symbol                                       | Parameter                                            |                                                                                                                  |                    | Тур               | Min   | Max   | Ullits |

| V <sub>CHG-IN</sub>                          | Input Voltage<br>Range                               |                                                                                                                  |                    |                   | 4.5   | 6.5   | V      |

|                                              | Operating Range                                      |                                                                                                                  |                    |                   | 4.5   | 6     |        |

| $V_{OK\_CHG}$                                | CHG_IN OK trip-                                      | V <sub>CHG_IN</sub> - V <sub>BATT</sub> (Risi                                                                    | ng)                | 200               |       |       | mV     |

|                                              | point                                                | V <sub>CHG_IN</sub> - V <sub>BATT</sub> (Fall                                                                    | ing)               | 50                |       |       |        |

| $V_{TERM}$                                   | Battery Charge<br>Termination<br>voltage             | Default                                                                                                          | Default            |                   |       |       | V      |

|                                              | V <sub>TERM</sub> voltage                            | T <sub>J</sub> = 25°C                                                                                            |                    |                   | -0.35 | +0.35 | %      |

|                                              | tolerance                                            | $T_J = 0$ °C to 85°C                                                                                             |                    |                   | -1    | +1    |        |

| I <sub>CHG</sub>                             | Fast Charge<br>Current Accuracy                      | I <sub>CHG</sub> = 450mA                                                                                         |                    |                   | -10   | +10   | %      |

|                                              | Programmable full-                                   | 6.0V ≥ V <sub>CHG_IN</sub> ≥ 4.5                                                                                 | V                  |                   | 50    | 950   | mA     |

| rate charge curri<br>range(default<br>100mA) | rate charge current                                  | V <sub>BATT</sub> < (V <sub>CHG_IN</sub> - V <sub>OK_CHG</sub> )                                                 |                    |                   |       |       |        |

|                                              |                                                      | V <sub>FULL_RATE</sub> < V <sub>BATT</sub> < V <sub>TERM</sub> (3)                                               |                    |                   |       |       |        |

|                                              |                                                      | Default                                                                                                          |                    | 100               |       |       |        |

|                                              | Charge current programming step                      |                                                                                                                  |                    | 50                |       |       |        |

| I <sub>PREQUAL</sub>                         | Pre-qualification current                            | V <sub>BATT</sub> = 2V                                                                                           |                    | 50                | 40    | 60    | mA     |

| I <sub>CHG_USB</sub>                         | CHG_IN programmable                                  | 5.5V ≥ V <sub>CHG_IN</sub> ≥ 4.5V                                                                                | Low                | 100               |       |       |        |

|                                              | current in USB<br>mode                               | V <sub>BATT</sub> < (V <sub>CHG_IN</sub> - V <sub>OK_CHG</sub> )                                                 |                    | 100               |       |       | mA     |

|                                              |                                                      | V <sub>FULL_RATE</sub> < V <sub>BATT</sub> < V <sub>TERM</sub>                                                   | High               | 450               |       |       |        |

|                                              |                                                      | Default = 100mA                                                                                                  |                    | 100               |       |       |        |

| V <sub>FULL_RATE</sub>                       | Full-rate<br>qualification<br>threshold              | V <sub>BATT</sub> rising, transition full-rate charging                                                          | n from pre-qual to | 3.0               | 2.9   | 3.1   | V      |

| I <sub>EOC</sub>                             | End of Charge<br>Current, % of full-<br>rate current | 0.1C option selected                                                                                             |                    | 10                |       |       | %      |

| V <sub>RESTART</sub>                         | Restart threshold voltage                            | V <sub>BATT</sub> falling, transition from EOC to full-<br>rate charge mode. Default options<br>selected - 4.05V |                    | 4.05              | 3.97  | 4.13  | V      |

| I <sub>MON</sub>                             | I <sub>MON</sub> Voltage 1                           | I <sub>CHG</sub> = 100mA                                                                                         |                    | 0.247             |       |       | .,     |

|                                              | I <sub>MON</sub> Voltage 2                           | I <sub>CHG</sub> = 450mA                                                                                         |                    | 1.112 0.947 1.277 |       | 1.277 | V      |

| T <sub>REG</sub>                             | Regulated junction temperature                       | (4)                                                                                                              |                    | 115               |       |       | °C     |

<sup>(1)</sup> All electrical characteristics having room-temperature limits are tested during production with T<sub>J</sub> = 25°C. All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(4) Specified by design. Not production tested.

<sup>(2)</sup> Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from thermal modelling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The value of (θ<sub>JA</sub>) of this product could fall within a wide range, depending on PWB material, layout, and environmental conditions. In applications where high maximum power dissipation exists (high V<sub>IN</sub>, high I<sub>OUT</sub>), special care must be paid to thermal dissipation issues in board design.

<sup>(3)</sup> Full charge current is specified for CHG\_IN = 4.5 to 6.0V. At higher input voltages, increased power dissipation may cause the thermal regulation to limit the current to a safe level, resulting in longer charging time.

# **Charger Electrical Characteristics (continued)**

Unless otherwise noted,  $V_{CHG-IN}=5V$ ,  $V_{IN}$  ( = VIN1 = VIN2 = BATT) = 3.6V. $C_{CHG\_IN}=10\mu F$ ,  $C_{BATT}=30\mu F$ . Charger set to default settings unless otherwise noted. Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a=T_J=-25^{\circ}C$  to +85°C. (1)(2)

| Comple ed            | Danamatan                                  | Condition                                                    | T   | Li  | mit | l luita |  |

|----------------------|--------------------------------------------|--------------------------------------------------------------|-----|-----|-----|---------|--|

| Symbol               | Parameter                                  | Condition                                                    | Тур | Min | Max | Units   |  |

| Detection and Ti     | ming <sup>(5)</sup>                        |                                                              | ·   |     |     |         |  |

| T <sub>POK</sub>     | Power OK deglitch time                     | V <sub>BATT</sub> < (V <sub>CC</sub> - V <sub>OK_CHG</sub> ) | 32  |     |     | mS      |  |

| T <sub>PQ_FULL</sub> | Deglitch time                              | Pre-qualification to full-rate charge transition             | 230 |     |     | mS      |  |

| T <sub>CHG</sub>     | Charge timer                               | Precharge mode                                               | 1   |     |     | Hrs     |  |

|                      |                                            | Full Rate Charging Timeout                                   | 5   |     |     |         |  |

|                      |                                            | Constant Voltage Timeout                                     | 5   |     |     |         |  |

| T <sub>EOC</sub>     | Deglitch time for end-of-charge transition |                                                              | 230 |     |     | mS      |  |

<sup>(5)</sup> Specified by design. Not production tested.

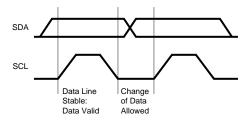

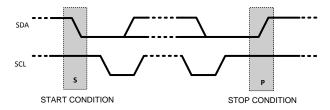

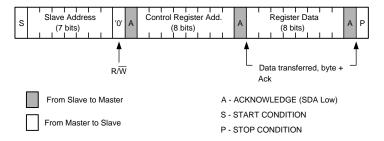

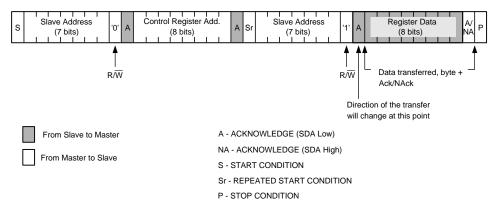

## **Serial Interface**

Unless otherwise noted,  $V_{IN}$  ( = VIN1 = VIN2 = BATT) = 3.6V, GND = 0V,  $C_{VIN1-2}$ =10 $\mu$ F,  $C_{LDOX}$ =1 $\mu$ F, and  $V_{LDO2}$  (DIG) = 3.0V. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_a$  =  $T_J$  = -40°C to +125°C. (1)(2)

| 0                      | B                                                                                                                | On wealth to me | <b>-</b> | Liı | mit | 1114  |

|------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----|-----|-------|

| Symbol                 | Parameter                                                                                                        | Condition       | Тур      | Min | Max | Units |

| f <sub>CLK</sub>       | Clock Frequency                                                                                                  |                 |          |     | 400 | kHz   |

| t <sub>BF</sub>        | Bus-Free Time between START and STOP                                                                             |                 |          | 1.3 |     | μs    |

| t <sub>HOLD</sub>      | Hold Time Repeated START Condition                                                                               |                 |          | 0.6 |     | μs    |

| t <sub>CLK-LP</sub>    | CLK Low Period                                                                                                   |                 |          | 1.3 |     | μs    |

| t <sub>CLK-HP</sub>    | CLK High Period                                                                                                  |                 |          | 0.6 |     | μs    |

| t <sub>SU</sub>        | Set-Up Time Repeated<br>START Condition                                                                          |                 |          | 0.6 |     | μs    |

| t <sub>DATA-HOLD</sub> | Data Hold Time                                                                                                   |                 |          | 50  |     | ns    |

| t <sub>DATA-SU</sub>   | Data Set-Up Time                                                                                                 |                 |          | 100 |     | ns    |

| t <sub>SU</sub>        | Set-Up Time for STOP<br>Condition                                                                                |                 |          | 0.6 |     | μs    |

| t <sub>TRANS</sub>     | Maximum Pulse Width of<br>Spikes that Must be<br>Suppressed by the Input<br>Filter of both DATA & CLK<br>Signals |                 | 50       |     |     | ns    |

All electrical characteristics having room-temperature limits are tested during production with  $T_J = 25^{\circ}\text{C}$ . All hot and cold limits are speficied by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

Copyright © 2007-2013, Texas Instruments Incorporated Submit Documentation Feedback

Specified by design. Not production tested.

# REGISTER INFORMATION, SLAVE ADDRESS CODE 7H'7E

# Table 3. Control Registers (1)(2)

|       |                                |                   |                  |                 | _                 |                  |                  |                    |                    |

|-------|--------------------------------|-------------------|------------------|-----------------|-------------------|------------------|------------------|--------------------|--------------------|

| Addr  | Register<br>(default<br>value) | D7                | D6               | D5              | D4                | D3               | D2               | D1                 | D0                 |

| 8h'00 | OP_EN<br>(0000 0101)           | Х                 | ×                | х               | Х                 | LDO7_EN          | LDO3_EN          | ×                  | LDO1_EN            |

| 8h'01 | LDO1PGM<br>O/P<br>(0000 0001)  | х                 | Х                | Х               | Х                 | V1_OP[3]         | V1_OP[2]         | V1_OP[1]           | V1_OP[0]           |

| 8h'02 | LDO2PGM<br>O/P<br>(0000 1011)  | х                 | Х                | Х               | Х                 | V2_OP[3]         | V2_OP[2]         | V2_OP[1]           | V2_OP[0]           |

| 8h'03 | LDO3PGM<br>O/P<br>(0000 1011)  | х                 | Х                | Х               | Х                 | V3_OP[3]         | V3_OP[2]         | V3_OP[1]           | V3_OP[0]           |

| 8h'04 | LDO4PGM<br>O/P<br>(0000 1011)  | x                 | х                | х               | Х                 | V4_OP[3]         | V4_OP[2]         | V4_OP[1]           | V4_OP[0]           |

| 8h'05 | LDO5PGM<br>O/P<br>(0000 1011)  | x                 | х                | х               | Х                 | V5_OP[3]         | V5_OP[2]         | V5_OP[1]           | V5_OP[0]           |

| 8h'06 | LDO6PGM<br>O/P<br>(0000 1011)  | x                 | Х                | X               | X                 | V6_OP[3]         | V6_OP[2]         | V6_OP[1]           | V6_OP[0]           |

| 8h'07 | LDO7PGM<br>O/P<br>(0000 1011)  | х                 | Х                | Х               | Х                 | V7_OP[3]         | V7_OP[2]         | V7_OP[1]           | V7_OP[0]           |

| 8h'0C | STATUS<br>(0000 0000)          | PWR_ON<br>_TRIG   | HF_PWR<br>_TRIG  | CHG_IN<br>_TRIG | X                 | ×                | X                | ×                  | Х                  |

| 8h'10 | CHGCNTL1<br>(0000 1001)        | USBMODE<br>_EN    | CHGMODE<br>_EN   | Force EOC       | TOUT_<br>doubling | EN_Tout          | En_EOC           | х                  | EN_CHG             |

| 8h'11 | CHGCNTL2<br>(0000 0001)        |                   |                  |                 | Prog_<br>ICHG[4]  | Prog_<br>ICHG[3] | Prog_<br>ICHG[2] | Prog_<br>ICHG[1]   | Prog_<br>ICHG[0]   |

| 8h'12 | CHGCNTL3<br>(0001 0010)        |                   |                  | VTERM[1]        | VTERM[0]          | Prog_<br>EOC[1]  | Prog_<br>EOC[0]  | Prog_<br>VRSTRT[1] | Prog_<br>VRSTRT[0] |

| 8h'13 | CHGSTATU<br>S1                 | Batt_Over<br>_Out | CHGIN_<br>OK_Out | EOC             | Tout_<br>Fullrate | Tout_<br>Prechg  | LDO Mode         | Fullrate           | PRECHG             |

| 8h'14 | CHGSTATU<br>S2                 |                   |                  |                 |                   |                  |                  | Tout_<br>ConstV    | Bad_Batt           |

| 8h'1C | MISC<br>Control1               |                   |                  |                 |                   |                  |                  | APU_TSD_<br>EN     | PS_HOLD<br>_DELAY  |

<sup>(1)</sup> X = Not Used

# **LDO Output Voltage Programming**

The following table summarizes the supported output voltages for the LP3918. Default voltages after startup are highlighted in **bold**.

| Data Code<br>(Reg 01 - 07) | LDO1<br>V | LDO2<br>V | VLDO3<br>V | LDO4<br>V | LDO5<br>V | LDO6<br>V | LDO7<br>V |

|----------------------------|-----------|-----------|------------|-----------|-----------|-----------|-----------|

| 8h'00                      | 1.5       |           |            | 1.5       |           |           | 1.5       |

| 8h'01                      | 1.8       |           |            | 1.8       |           |           | 1.8       |

| 8h'02                      | 1.85      |           |            | 1.85      |           |           | 1.85      |

| 8h'03                      | 2.5       | 2.5       |            | 2.5       |           |           | 2.5       |

| 8h'04                      | 2.6       | 2.6       |            | 2.6       |           |           | 2.6       |

<sup>(</sup>R/O) = Bits are Read Only type. Codes other than those shown in the table are disallowed.

<sup>(2)</sup> Note that for Serial Interface operation and thus register control, LDO2 must be active to provide the power for the internal logic.

| <b>J</b> i3 | Texas              |

|-------------|--------------------|

| ·Y          | <b>INSTRUMENTS</b> |

www.ti.com

SNVS476D - AUGUST 2007-REVISED MAY 2013

| 8h'05 | 2.7  | 2.7  | 2.7  | 2.7  | 2.7  | 2.7  | 2.7  |

|-------|------|------|------|------|------|------|------|

| 8h'06 | 2.75 | 2.75 | 2.75 | 2.75 | 2.75 | 2.75 | 2.75 |

| 8h'07 | 2.8  | 2.8  | 2.8  | 2.8  | 2.8  | 2.8  | 2.8  |

| 8h'08 | 2.85 | 2.85 | 2.85 | 2.85 | 2.85 | 2.85 | 2.85 |

| 8h'09 | 2.9  | 2.9  | 2.9  | 2.9  | 2.9  | 2.9  | 2.9  |

| 8h'0A | 2.95 | 2.95 | 2.95 | 2.95 | 2.95 | 2.95 | 2.95 |

| 8h'0B | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  | 3.0  |

| 8h'0C | 3.05 | 3.05 | 3.05 | 3.05 | 3.05 | 3.05 | 3.05 |

| 8h'0D | 3.1  | 3.1  |      | 3.1  |      |      | 3.1  |

| 8h'0E | 3.2  | 3.2  |      | 3.2  |      |      | 3.2  |

| 8h'0F | 3.3  | 3.3  |      | 3.3  |      |      | 3.3  |

# **Charger Control Register 2**

Note that Bits 7,6,5 are not used and must be set to 0 during write to this register.

# **CHARGER CURRENT PROGRAMMING**

The following table summarizes the supported charging current values for the LP3918.

Default charge current after startup is highlighted in **bold**

**Table 4. LP3918 Charger Current Programming**

| Address | Register ID |       | Current Selection Prog_ICHG<40> Bit 0 to Bit 4 |                  |               |                |       |       |  |

|---------|-------------|-------|------------------------------------------------|------------------|---------------|----------------|-------|-------|--|

| 8h'11   | OLIOONTI O  | 00000 | 00001                                          | 00010            | 00011         | 00100          | 00101 | 00110 |  |

| OHH     | CHGCNTL2    | 50mA  | 100mA                                          | 150mA            | 200mA         | 250mA          | 300mA | 350mA |  |

| Address | Register ID |       | Current Selection Prog_ICHG<40> Bit 0 to Bit 4 |                  |               |                |       |       |  |

| 0544    | CLICCNITIO  | 00111 | 01000                                          | 01001            | 01010         | 01011          | 01100 | 01101 |  |

| 8h'11   | CHGCNTL2    | 400mA | 450mA                                          | 500mA            | 550mA         | 600mA          | 650mA | 700mA |  |

| Address | Register ID |       | С                                              | urrent Selection | n Prog_ICHG<4 | 0> Bit 0 to Bi | t 4   |       |  |

| 0h!44   | CUCCNTIO    | 01110 | 01111                                          | 10000            | 10001         | 10010          |       |       |  |

| 8h'11   | CHGCNTL2    | 750mA | 800mA                                          | 850mA            | 900mA         | 950mA          |       |       |  |

# **Charger Control Register 3**

# **CHARGER TERMINATION VOLTAGE PROGRAMMING**

**Table 5. LP3918 Charger Termination Voltage Control**

| Address | Register ID | V <sub>TERM</sub> Selection Bits |             |                        |  |  |

|---------|-------------|----------------------------------|-------------|------------------------|--|--|

|         |             | VTERM[1]                         | VTERM[0]    | Termination Voltage(V) |  |  |

|         |             | CHGCNTL3<5>                      | CHGCNTL3<4> |                        |  |  |

| 0640    | CHCCNTI 2   | 0                                | 0           | 4.1                    |  |  |

| 8h'12   | CHGCNTL3    | 0                                | 1           | 4.2 (Default)          |  |  |

|         |             | 1                                | 0           | 4.3                    |  |  |

|         |             | 1                                | 1           | 4.4                    |  |  |

#### **END OF CHARGE CURRENT PROGRAMMING**

# **Table 6. LP3918 EOC Current Control**

| Address | Register ID | End Of Charge Current Selection Bits |             |                       |  |  |

|---------|-------------|--------------------------------------|-------------|-----------------------|--|--|

|         |             | PROG_EOC[1]                          | PROG_EOC[0] | End Of Charge Current |  |  |

|         |             | CHGCNTL3<3>                          | CHGCNTL3<2> |                       |  |  |

| 0540    | CHOONTLO    | 0                                    | 0           | 0.1 (Default)         |  |  |

| 8h'12   | CHGCNTL3    | 0                                    | 1           | 0.15C                 |  |  |

|         |             | 1                                    | 0           | 0.2C                  |  |  |

|         |             | 1                                    | 1           | 0.25C                 |  |  |

#### CHARGING RESTART VOLTAGE PROGRAMMING

Table 7. LP3918 Charging Restart Voltage

| Address | Register ID | Charging Restart Voltage Selection Bits |                |                           |  |  |  |

|---------|-------------|-----------------------------------------|----------------|---------------------------|--|--|--|

|         |             | PROG_VRSTRT[1]                          | PROG_VRSTRT[1] | Restart Voltage(V)        |  |  |  |

|         |             | CHGCNTL3<1>                             | CHGCNTL3<0>    |                           |  |  |  |

| 0540    | CHCCNTLO    | 0                                       | 0              | V <sub>TERM</sub> - 50mV  |  |  |  |

| 8h'12   | CHGCNTL3    | 0                                       | 1              | V <sub>TERM</sub> - 100mV |  |  |  |

|         |             | 1                                       | 0              | V <sub>TERM</sub> - 150mV |  |  |  |

|         |             | 1                                       | 1              | V <sub>TERM</sub> - 200mV |  |  |  |

# **Charger Control Register 1**

## **CHARGING MODE SELECTION**

Charging mode selection changes will only take place when the battery voltage is above the 3.0V pre-charge/Full-rate charge threshold.

Table 8. LP3918 USB Charging Selection

| Address | Register ID | USB Charge Mode Control Bits |             |             |                         |

|---------|-------------|------------------------------|-------------|-------------|-------------------------|

|         |             | USB_Mode_En                  | CHG_Mode_En | Mode        | Current                 |

|         |             | CHGCNTL1<7>                  | CHGCNTL1<6> |             |                         |

| 0540    | CHCONTI 4   | 0                            | 0           | Fast Charge | Default or<br>Selection |

| 8h'10   | CHGCNTL1    | 1                            | 0           | Fast Charge | Default or<br>Selection |

|         |             | 0                            | 1           | USB         | 100mA                   |

|         |             | 1                            | 1           | USB         | 450mA                   |

Product Folder Links: LP3918

Copyright © 2007–2013, Texas Instruments Incorporated

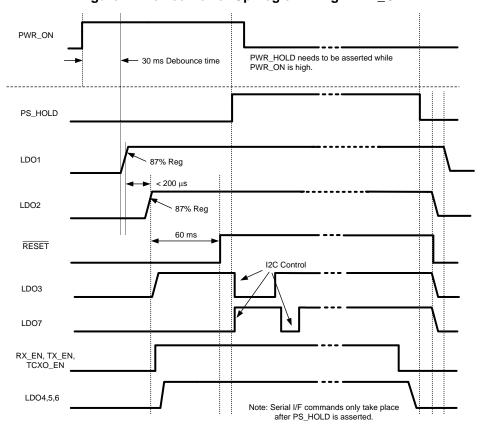

# **Device Power Up and Shutdown Timing**

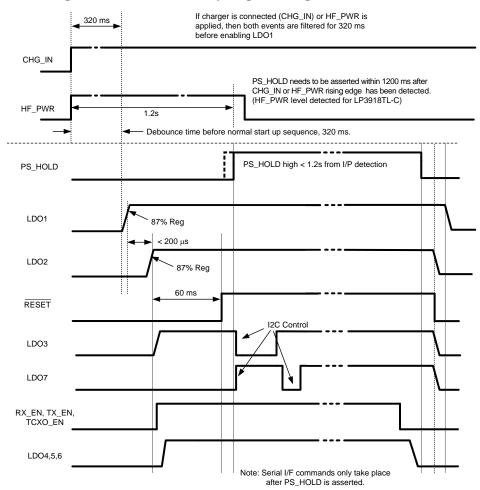

Figure 4. Device Power Up Logic Timing. PWR\_ON

Figure 5. Device Power Up Logic Timing. CHG\_IN, HF\_PWR

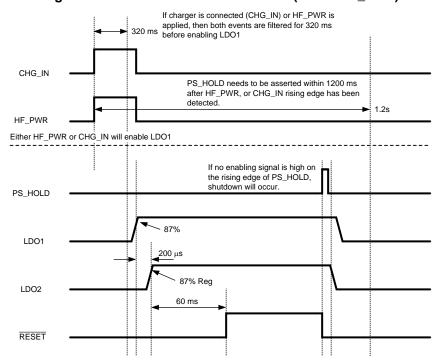

Figure 6. LP3918 Power On Behaviour (Failed PS\_Hold)

Figure 7. LP3918 Normal Shutdown Behaviour

Copyright © 2007–2013, Texas Instruments Incorporated

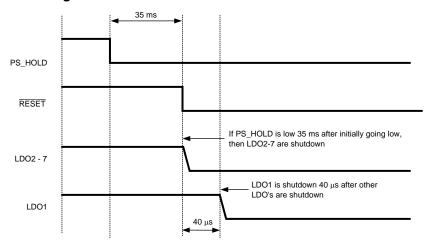

# **Functional Block Diagram**

Figure 8. LP3918 Functional Block Diagram

#### TECHNICAL DESCRIPTION

# **BATTERY CHARGE MANAGEMENT**

A charge management system allowing the safe charge and maintenance of a Li-lon battery is implemented on the LP3918. This has a CC/CV linear charge capability with programmable battery regulation voltage and end of charge current threshold. The charge current in the constant current mode is programmable and a maintenance mode monitors for battery voltage drop to restart charging at a preset level. A USB charging mode is also available with 2 charge current levels.

#### **CHARGER FUNCTION**

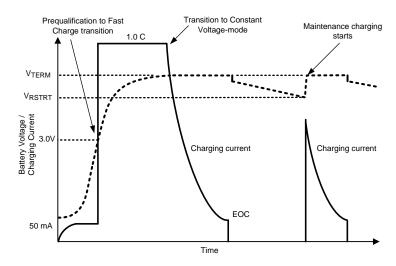

Following the correct detection of an input voltage at the charger pin the charger enters a pre-charge mode. In this mode a constant current of 50mA is available to charge the battery to 3.0V. At this voltage level the charge management applies the default (100mA) full rate constant current to raise the battery voltage to the termination voltage level (default 4.2V). The full rate charge current may be programmed to a different level at this stage. When termination voltage ( $V_{\text{TERM}}$ ) is reached, the charger is in constant voltage mode and a constant voltage of 4.2V is maintained. This mode is complete when the end of charge current (default 0.1C) is detected and the charge management enters the maintenance mode. In maintenance mode the battery voltage is monitored for the restart level (4.05V at the default settings) and the charge cycle is re-initiated to re-establish the termination voltage level.

For start up the EOC function is disabled. This function should be enabled once start up is complete and a battery has been detected. EOC is enabled via register CHGCNTL1, Table 9.

The full rate constant current rate of charge may be programmed to 19 levels from 50mA to 950mA. These values are given in Table 4, and Table 11

The charge mode may be programmed to USB mode when the charger input is applied and the battery voltage is above 3.0V. This provides two programmable current levels of 100mA and 450mA for a USB sourced supply input at CHG\_IN. Table 8

#### LDO Mode on device option LP3918TL-L

The charger circuit automatically enters an LDO mode if no battery is detected on insertion of the charger input voltage. In LDO mode the battery pin is regulated to 4.2V and can source up to 1.0A of current. Normal operation with a battery connected can be re-established via the serial interface. The serial interface allows the device to switch between modes as required however care is required to ensure that LDO mode is not initiated while a battery is present.

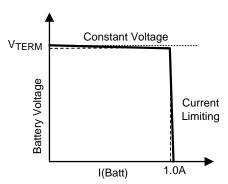

Figure 9. LDO Mode Diagram

#### **EOC**

EOC is disabled by default and should be enabled when the system processor is awake and the system detects that a battery is present.

### **Programming Information**

#### Table 9. Register Address 8h'10: CHGCNTL1

| BIT | NAME | FUNCTION                                                                                          |

|-----|------|---------------------------------------------------------------------------------------------------|

| 2   |      | Enables the End Of Charge current level threshold detection. When set to '0' the EOC is disabled. |

The End Of Charge current threshold default setting is at 0.1C. This EOC value is set relative to C the set full rate constant current. This threshold can be set to 0.1C, 0.15C, 0.2C or 0.25C bychanging the contents of the PROG\_EOC[1:0] register bits.

Table 10. Register Address 8h'12: CHGCNTL3

| BIT | NAME        | FUNCTION                       |

|-----|-------------|--------------------------------|

| 2   | Prog_EOC[0] | Set the End Of Charge Current. |

| 3   | Prog_EOC[1] | See Table 8                    |

### **CHARGER FULL RATE CURRENT**

## **Programming Information**

Table 11. Register Address 8h'11: CHGCNTL2

| Data BITs          | HEX | NAME        | FUNCTION |

|--------------------|-----|-------------|----------|

| 000[00000]         | 00  | Prog_ICHG   | 50mA     |

| 000[00001]         | 01  | 1 109_10110 | 100mA    |

|                    |     |             |          |

| 000 <b>[00010]</b> | 02  |             | 150mA    |

| 000 <b>[00011]</b> | 03  |             | 200mA    |

| 000 <b>[00100]</b> | 04  |             | 250mA    |

| 000[00101]         | 05  |             | 300mA    |

| 000 <b>[00110]</b> | 06  |             | 350mA    |

| 000 <b>[00111]</b> | 07  |             | 400mA    |

| 000 <b>[01000]</b> | 08  |             | 450mA    |

| 000[01001]         | 09  |             | 500mA    |

| 000 <b>[01010]</b> | 0A  |             | 550mA    |

| 000 <b>[01011]</b> | 0B  |             | 600mA    |

| 000 <b>[01100]</b> | 0C  |             | 650mA    |

| 000[01101]         | 0D  |             | 700mA    |

| 000 <b>[01110]</b> | 0E  |             | 750mA    |

| 000[01111]         | 0F  |             | 800mA    |

| 000[10000]         | 10  |             | 850mA    |

| 000[10001]         | 11  |             | 900mA    |

| 000[10010]         | 12  |             | 950mA    |

# **TERMINATION AND RESTART**

The termination and restart voltage levels are determined by the data in the VTERM[1:0] and PROG\_VSTRT[1:0] bits in the control register. The restart voltage is programmed relative to the selected termination voltage.

The Termination voltages available are 4.1V, 4.2V (default), 4.3V, and 4.4V.

The Restart voltages are determined relative to the termination voltage level and may be set to 50mV, 100mV, 150mV (default), and 200mV below the set termination voltage level.

## **Programming Information**

Table 12. Register Address 8h'12: CHGCNTL3

| BIT | NAME     | FUNCTION                              |

|-----|----------|---------------------------------------|

| 4   | VTERM[0] | Set the charging termination voltage. |

| 5   | VTERM[1] | See Table 5                           |

Table 13. Register Address 8h'12: CHGCNTL3

| BIT | NAME      | FUNCTION                          |

|-----|-----------|-----------------------------------|

| 0   | VRSTRT[0] | Set the charging restart voltage. |

| 1   | VRSTRT[1] | See Table 7                       |

# **Charger Operation**

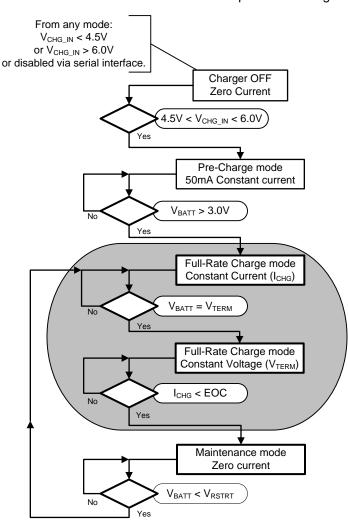

The operation of the charger with EOC enabled is shown in this simplified flow diagram.

Figure 10. Simplified Charger Functional Flow Diagram (EOC is enabled)

The charger operation may be depicted by the following graphical representation of the voltage and current profiles.

Copyright © 2007–2013, Texas Instruments Incorporated

Figure 11. Charge Cycle Diagram

# **Further Charger Register Information**

# **Charger Control Register 1**

Table 14. Register Address 8h'10: CHGCNTL1

| BIT | NAME              | FUNCTION (if bit = '1')                                                                                  |

|-----|-------------------|----------------------------------------------------------------------------------------------------------|

| 7   | USB_MODE<br>_EN   | Sets the Current Level in USB mode.                                                                      |

| 6   | CHG_MODE<br>_EN   | Forces the charger into USB mode when active high. If low, charger is in normal charge mode.             |

| 5   | FORCE<br>_EOC     | Forces an EOC event.                                                                                     |