# ADC10065 10-Bit 65 MSPS 3V A/D Converter

Check for Samples: ADC10065

#### **FEATURES**

- Single +3.0V Operation

- Selectable 2 V<sub>P-P</sub>, 1.5 V<sub>P-P</sub>, or 1 V<sub>P-P</sub> Full-scale Input

- 400 MHz -3 dB Input Bandwidth

- Low Power Consumption

- Standby Mode

- On-Chip Reference and Sample-and-Hold Amplifier

- Offset Binary or Two's Complement Data Format

- Separate Adjustable Output Driver Supply to Accommodate 2.5V and 3.3V Logic Families

- 28-pin TSSOP Package

#### **APPLICATIONS**

- Ultrasound and Imaging

- Instrumentation

- Cellular Base Stations/Communications Receivers

- Sonar/Radar

- xDSL

- Wireless Local Loops

- Data Acquisition Systems

- DSP Front Ends

#### **KEY SPECIFICATIONS**

- Resolution 10 Bits

- Conversion Rate 65 MSPS

- Full Power Bandwidth 400 MHz

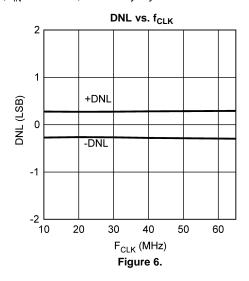

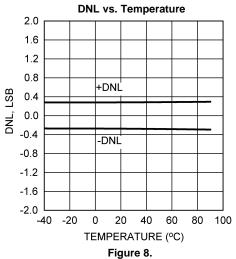

- DNL ±0.3 LSB (typ)

- SNR (f<sub>IN</sub> = 11 MHz) 59.6 dB (typ)

- SFDR (f<sub>IN</sub> = 11 MHz) -80 dB (typ)

- Power Consumption, 65 MHz 68.4 mW

#### DESCRIPTION

The ADC10065 is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 10-bit digital words at 65 Megasamples per second (MSPS). This converter uses a differential, pipeline architecture with digital error correction and an on-chip sample-and-hold circuit to provide a complete conversion solution, and to minimize power consumption, while providing excellent dynamic performance. A unique sample-and-hold stage yields a full-power bandwidth of 400 MHz. Operating on a single 3.0V power supply, this device consumes just 68.4 mW at 65 MSPS, including the reference current. The Standby feature reduces power consumption to just 14.1 mW.

The differential inputs provide a full scale selectable input swing of 2.0  $V_{P-P}$ , 1.5  $V_{P-P}$ , 1.0  $V_{P-P}$ , with the possibility of a single-ended input. Full use of the differential input is recommended for optimum performance. An internal +1.2V precision bandgap reference is used to set the ADC full-scale range, and also allows the user to supply a buffered referenced voltage for those applications requiring increased accuracy. The output data format is user choice of offset binary or two's complement.

This device is available in the 28-lead TSSOP package and will operate over the industrial temperature range of -40°C to +85°C.

ATA.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

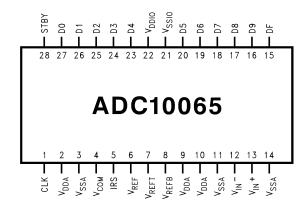

## **Connection Diagram**

Figure 1. TSSOP Package See Package Number PW0028A

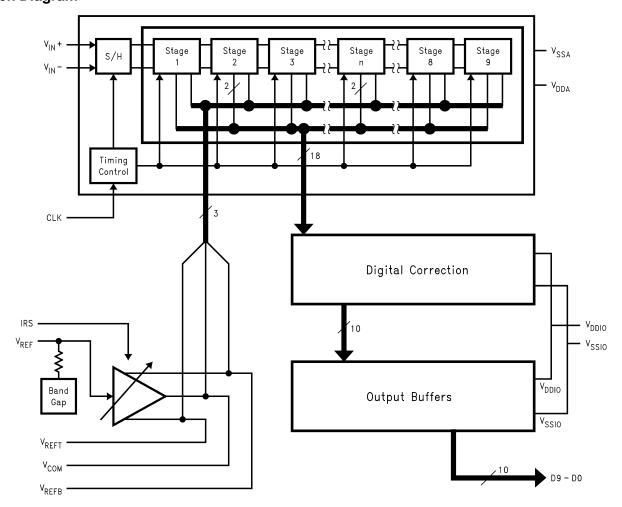

# **Block Diagram**

# **Pin Descriptions and Equivalent Circuits**

| Pin No.     | Pin Name                     | Equivalent Circuit                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG I/O  |                              | Equivalent Circuit                                                                                   | nescribrion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12          | V <sub>IN</sub> <sup>-</sup> | V <sub>DDA</sub> V <sub>SSA</sub>                                                                    | Inverting analog input signal. With a 1.2V reference the full-scale input signal level is a differential 1.0 $V_{P-P}$ . This pin may be tied to $V_{COM}$ (pin 4) for single-ended operation.  Non-inverting analog input signal. With a 1.2V reference the full-scale input signal level is a differential 1.0 $V_{P-P}$ .                                                                                                                                                                                                                                                                    |

| 6           | V <sub>REF</sub>             | V <sub>DDA</sub> V <sub>SSA</sub>                                                                    | Reference input. This pin should be bypassed to $V_{SSA}$ with a 0.1 $\mu F$ monolithic capacitor. $V_{REF}$ is 1.20V nominal. This pin may be driven by a 1.20V external reference if desired. Do not load this pin.                                                                                                                                                                                                                                                                                                                                                                           |

| 7           | $V_{REFT}$                   | W                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4           | V <sub>COM</sub>             | V <sub>DDA</sub><br><b>♀</b>                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8           | V <sub>REFB</sub>            | V <sub>DDA</sub> V <sub>DDA</sub> V <sub>DDA</sub> V <sub>DDA</sub> V <sub>DDA</sub> (7) (4) (8) (8) | These pins are high impedance reference bypass pins only. Connect a 0.1 $\mu$ F capacitor from each of these pins to V <sub>SSA</sub> . These pins should not be loaded. V <sub>COM</sub> may be used to set the input common mode voltage, V <sub>CM</sub> .                                                                                                                                                                                                                                                                                                                                   |

| DIGITAL I/O |                              |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1           | CLK                          | V <sub>DDIO</sub>                                                                                    | Digital clock input. The range of frequencies for this input is 20 MHz to 65 MHz. The input is sampled on the rising edge of this input.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15          | DF                           |                                                                                                      | DF = "1" Two's Complement DF = "0" Offset Binary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28          | STBY                         | 1,15,                                                                                                | This is the standby pin. When high, this pin sets the converter into standby mode. When this pin is low, the converter is in active mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

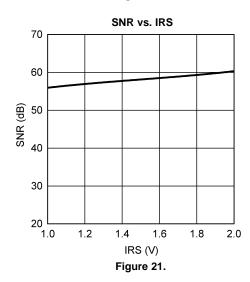

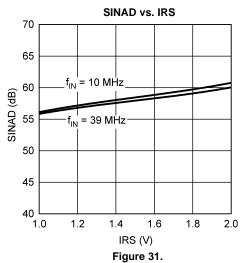

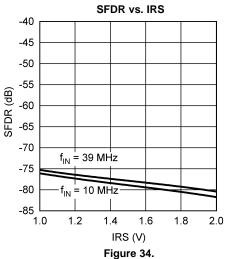

| 5           | IRS (Input Range<br>Select)  | V <sub>SSIO</sub>                                                                                    | $\begin{split} &   \text{IRS} = \text{``}V_{DDA}\text{''} \ 2.0 \ V_{P\text{-P}} \ \text{differential input range} \\ &   \text{IRS} = \text{``}V_{SSA}\text{''} \ 1.5 \ V_{P\text{-P}} \ \text{differential input range} \\ &   \text{IRS} = \text{``}Floating\text{''} \ 1.0 \ V_{P\text{-P}} \ \text{differential input range} \\ &   \text{If using both } V_{\text{IN}} + \ \text{and } V_{\text{IN}} - \ \text{pins}, \ \text{(or differential mode), then the} \\ &   \text{peak-to-peak voltage refers to the differential voltage} \ (V_{\text{IN}} + - V_{\text{IN}} -). \end{split}$ |

Copyright © 2003–2013, Texas Instruments Incorporated

# Pin Descriptions and Equivalent Circuits (continued)

| Pin No.         | Pin Name         | Equivalent Circuit                                         | Description                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16–20,<br>23–27 | D0-D9            | V <sub>DDIO</sub><br>Q <sub>D-9</sub><br>V <sub>SSIO</sub> | Digital output data. D0 is the LSB and D9 is the MSB of the binary output word.                                                                                                                                                                                                                                                           |

| ANALOG PO       | WER              |                                                            |                                                                                                                                                                                                                                                                                                                                           |

| 2, 9, 10        | $V_{DDA}$        |                                                            | Positive analog supply pins. These pins should be connected to a quiet 3.0V source and bypassed to analog ground with a 0.1 $\mu F$ monolithic capacitor located within 1 cm of these pins. A 4.7 $\mu F$ capacitor should also be used in parallel.                                                                                      |

| 3, 11, 14       | V <sub>SSA</sub> |                                                            | Ground return for the analog supply.                                                                                                                                                                                                                                                                                                      |

| DIGITAL PO      |                  |                                                            |                                                                                                                                                                                                                                                                                                                                           |

| 22              | $V_{DDIO}$       |                                                            | Positive digital supply pins for the ADC10065's output drivers. This pin should be bypassed to digital ground with a 0.1 $\mu F$ monolithic capacitor located within 1 cm of this pin. A 4.7 $\mu F$ capacitor should also be used in parallel. The voltage on this pin should never exceed the voltage on $V_{DDA}$ by more than 300 mV. |

| 21              | $V_{\rm SSIO}$   |                                                            | The ground return for the digital supply for the output drivers. This pin should be connected to the ground plane, but not near the analog circuitry.                                                                                                                                                                                     |

Submit Documentation Feedback

Product Folder Links: ADC10065

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| Abbolate maximum ratinge               | •                    |                                                         |  |  |  |

|----------------------------------------|----------------------|---------------------------------------------------------|--|--|--|

| $V_{DDA}, V_{DDIO}$                    |                      | 3.9V                                                    |  |  |  |

| Voltage on Any Pin to GND              |                      | -0.3V to V <sub>DDA</sub> or V <sub>DDIO</sub><br>+0.3V |  |  |  |

| Input Current on Any Pin               |                      | ±25 mA                                                  |  |  |  |

| Package Input Current (4)              |                      | ±50 m                                                   |  |  |  |

| Package Dissipation at T = 25°C        |                      | See (5)                                                 |  |  |  |

| ESD Susceptibility                     | Human Body Model (6) | 2500V                                                   |  |  |  |

|                                        | Machine Model (6)    | 250V                                                    |  |  |  |

| Soldering Temperature Infrared, 10 sec | . (7)                | 235°C                                                   |  |  |  |

| Storage Temperature                    |                      | −65°C to +150°C                                         |  |  |  |

- (1) All voltages are measured with respect to GND = V<sub>SSA</sub> = V<sub>SSIO</sub> = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the AC Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) When the voltage at any pin exceeds the power supplies (V<sub>IN</sub> < V<sub>SSA</sub> or V<sub>IN</sub> > V<sub>DDA</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two.

- (5) The absolute maximum junction temperature (T<sub>J</sub>max) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>J</sub>max, the junction-to-ambient thermal resistance (θ<sub>JA</sub>), and the ambient temperature (T<sub>A</sub>), and can be calculated using the formula P<sub>D</sub>MAX = (T<sub>J</sub>max T<sub>A</sub>)/θ<sub>JA</sub>. In the 28-pin TSSOP, θ<sub>JA</sub> is 96°C/W, so P<sub>D</sub>MAX = 1,302 mW at 25°C and 677 mW at the maximum operating ambient temperature of 85°C. Note that the power dissipation of this device under normal operation will typically be about 68.6 mW. The values for maximum power dissipation listed above will be reached only when the ADC10065 is operated in a severe fault condition.

- (6) Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through 0Ω.

- (7) The 235°C reflow temperature refers to infrared reflow. For Vapor Phase Reflow (VPR) the following conditions apply: Maintain the temperature at the top of the package body above 183°C for a minimum of 60 seconds. The temperature measured on the package body must not exceed 220°C. Only one excursion above 183°C is allowed per reflow cycle.

### Operating Ratings (1)(2)

| Operating Temperature Range                      | -40°C ≤ T <sub>A</sub> ≤ +85°C |

|--------------------------------------------------|--------------------------------|

| V <sub>DDA</sub> (Supply Voltage)                | +2.7V to +3.6V                 |

| V <sub>DDIO</sub> (Output Driver Supply Voltage) | +2.5V to V <sub>DDA</sub>      |

| V <sub>REF</sub>                                 | 1.20V                          |

| V <sub>SSA</sub> -V <sub>SSIO</sub>              | ≤ 100 mV                       |

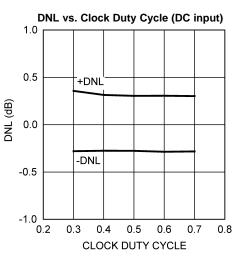

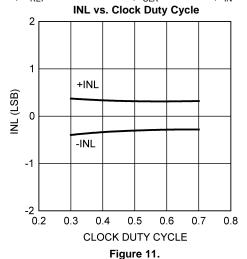

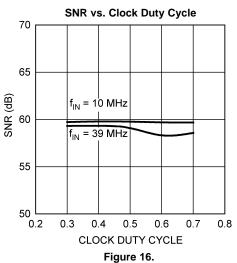

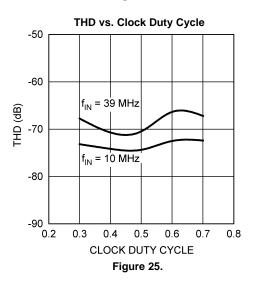

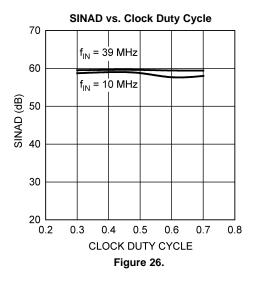

| Clock Duty Cycle                                 | 30 to 70 %                     |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the AC Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (2) All voltages are measured with respect to GND = V<sub>SSA</sub> = V<sub>SSIO</sub> = 0V, unless otherwise specified.

Product Folder Links: ADC10065

#### Converter Electrical Characteristics

Unless otherwise specified, the following specifications apply for  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF}$  = 1.20V (External),  $f_{CLK}$  = 65 MHz, 50% Duty Cycle,  $C_L$  = 10 pF/pin. **Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>:** all other limits  $T_A$  = 25°C. (1)(2)(3)(4).

|                    | Parameter                                                             | Test Conditions                                | Min      | Тур   | Max  | Units  |

|--------------------|-----------------------------------------------------------------------|------------------------------------------------|----------|-------|------|--------|

| STATIC (           | CONVERTER CHARACTERISTICS                                             | ·                                              |          |       | ,    |        |

|                    | No Missing Codes ensured                                              |                                                | 10       |       |      | Bits   |

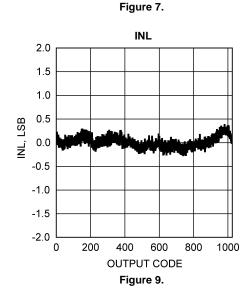

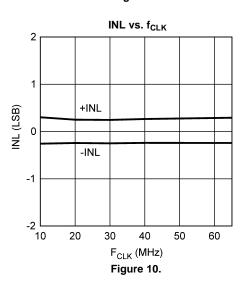

| INL                | Integral Non-Linearity                                                | F <sub>IN</sub> = 500 kHz, −0 dB Full<br>Scale | -1.0     | ±0.3  | +1.1 | LSB    |

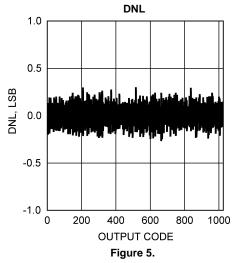

| DNL                | Differential Non-Linearity                                            | F <sub>IN</sub> = 500 kHz, −0 dB Full<br>Scale | -0.9     | ±0.3  | +0.9 | LSB    |

| 05                 | Coin Faran                                                            | Positive Error                                 | -1.5     | +0.4  | +1.9 | % FS   |

| GE                 | Gain Error                                                            | Negative Error                                 | -1.5     | +0.03 | +1.9 | % FS   |

| OE                 | Offset Error (V <sub>IN</sub> + = V <sub>IN</sub> -)                  |                                                | -1.4     | 0.2   | +1.7 | % FS   |

|                    | Under Range Output Code                                               |                                                |          | 0     |      |        |

|                    | Over Range Output Code                                                |                                                |          | 1023  |      |        |

| FPBW               | Full Power Bandwidth (5)                                              |                                                |          | 400   |      | MHz    |

| REFERE             | NCE AND INPUT CHARACTERISTICS                                         | ·                                              | <u> </u> |       | ,    |        |

| V <sub>CM</sub>    | Common Mode Input Voltage                                             |                                                | 0.5      |       | 1.5  | V      |

| V <sub>COM</sub>   | Output Voltage for use as an input common mode voltage <sup>(6)</sup> |                                                |          | 1.45  |      | V      |

| V <sub>REF</sub>   | Reference Voltage                                                     |                                                |          | 1.2   |      | V      |

| V <sub>REFTC</sub> | Reference Voltage Temperature<br>Coefficient                          |                                                |          | ±80   |      | ppm/°C |

| C <sub>IN</sub>    | V <sub>IN</sub> Input Capacitance (each pin to V <sub>SSA</sub> )     |                                                |          | 4     |      | pF     |

| POWER S            | SUPPLY CHARACTERISTICS                                                | ,                                              | ,        | •     |      |        |

|                    | A sala a Comala Comand                                                | STBY = 1                                       |          | 4.7   | 6.0  | mA     |

| $I_{VDDA}$         | Analog Supply Current                                                 | STBY = 0                                       |          | 22    | 29   | mA     |

|                    | Digital Complex Company (7)                                           | STBY = 1, f <sub>IN</sub> = 0 Hz               |          | 0     |      | mA     |

| I <sub>VDDIO</sub> | Digital Supply Current (7)                                            | STBY 0, f <sub>IN</sub> = 0 Hz                 |          | 0.97  | 1.2  | mA     |

| DWD                | David (8)                                                             | STBY = 1                                       |          | 14.1  | 18.0 | mW     |

| PWR                | Power Consumption (8)                                                 | STBY = 0                                       |          | 68.4  | 90   | mW     |

|                    |                                                                       |                                                |          |       |      |        |

- To ensure accuracy, it is required that  $|V_{DDA}-V_{DDIO}| \le 100$  mV and separate bypass capacitors are used at each power supply pin.

- With the test condition for 2  $V_{P-P}$  differential input, the 10-bit LSB is 1.95 mV. Typical figures are at  $T_A = T_J = 25^{\circ}$ C and represent most likely parametric norms. Test limits are specified to Texas Instrument's AOQL (Average Outgoing Quality Level).

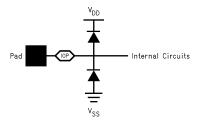

- The analog inputs are protected as shown below. Input voltage magnitude up to 500 mV beyond the supply rails will not damage this device. However, input errors will be generated if the input goes above VDDA or VDDIO and below VSSA or VSSIO. See Figure 2

- The input bandwidth is limited using a capacitor between  $V_{IN}^-$  and  $V_{IN}^+$ .

- VCOM is a typical value, measured at room temperature. It is not specified by test. Do not load this pin.

- I<sub>DDIO</sub> is the current consumed by the switching of the output drivers and is primarily determined by load capacitance on the output pins, the supply voltage,  $V_{DR}$ , and the rate at which the outputs are switching (which is signal dependent).  $I_{DR} = V_{DR} \times (C_0 \times f_0 + C_1 \times f_1 + C_2 \times f_2)$ +  $f_2$  +.... $C_{11}$  x  $f_{11}$ ) where  $V_{DR}$  is the output driver supply voltage,  $C_n$  is the total load capacitance on the output pin, and  $f_n$  is the average frequency at which the pin is toggling.

- Power consumption includes output driver power. ( $f_{IN} = 0 \text{ MHz}$ ).

## **DC and Logic Electrical Characteristics**

Unless otherwise specified, the following specifications apply for  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = 1.20V$  (External),  $f_{CLK} = 65$  MHz, 50% Duty Cycle,  $C_L = 10$  pF/pin. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}:** all other limits  $T_A = 25$ °C. (1)

|                                                   | Parameter                            | Test Conditions            | Min                    | Тур             | Max | Units |

|---------------------------------------------------|--------------------------------------|----------------------------|------------------------|-----------------|-----|-------|

| CLK, DF, STBY,                                    | SENSE                                |                            |                        |                 |     |       |

|                                                   | Logical "1" Input Voltage            |                            | 2                      |                 |     | V     |

|                                                   | Logical "0" Input Voltage            |                            |                        |                 | 0.8 | V     |

|                                                   | Logical "1" Input Current            |                            |                        |                 | +10 | μΑ    |

|                                                   | Logical "0" Input Current            |                            | -10                    |                 |     | μΑ    |

| D0-D9 OUTPUT                                      | CHARACTERISTICS                      |                            |                        |                 |     |       |

|                                                   | Logical "1" Output Voltage           | I <sub>OUT</sub> = −0.5 mA | V <sub>DDIO</sub> -0.2 |                 |     | V     |

|                                                   | Logical "0" Output Voltage           | I <sub>OUT</sub> = 1.6 mA  |                        |                 | 0.4 | V     |

| DYNAMIC CONV                                      | ERTER CHARACTERISTICS (2)            |                            |                        |                 |     |       |

| ENIOD                                             | Effective Nevel on of Pite           | f <sub>IN</sub> = 11 MHz   | 9.4, <b>9.3</b>        | 9.6             |     | Bits  |

| ENOB Effective Number of Bits                     |                                      | f <sub>IN</sub> = 32 MHz   | 9.3, <b>9.2</b>        | 9.5             |     | Bits  |

| ONID                                              | O'mark to Nation Botto               | f <sub>IN</sub> = 11 MHz   | 58.6, <b>58</b>        | 59.6            |     | dB    |

| SNR                                               | Signal-to-Noise Ratio                | f <sub>IN</sub> = 32 MHz   | 58.5, <b>57.9</b>      | 59.3            |     | dB    |

|                                                   | O'mark to Nation Botton Biotoxica    | f <sub>IN</sub> = 11 MHz   | 58.3, <b>57.6</b>      | 59.4            |     | dB    |

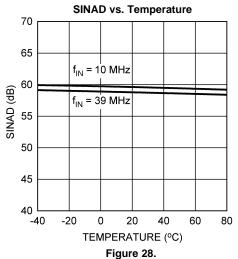

| SINAD                                             | Signal-to-Noise Ratio + Distortion   | f <sub>IN</sub> = 32 MHz   | 58, <b>57.4</b>        | 59              |     | dB    |

| 0-4110                                            | Ond Harmonia                         | f <sub>IN</sub> = 11 MHz   | -75.6,<br><b>-69.7</b> | -90             |     | dBc   |

| 2nd HD                                            | 2nd Harmonic                         | f <sub>IN</sub> = 32 MHz   | -72.7,<br><b>-68.9</b> | -82             |     | dBc   |

|                                                   |                                      | f <sub>IN</sub> = 11 MHz   | -66.2, <b>-63</b>      | -74             |     | dBc   |

| 3rd HD                                            | 3rd Harmonic                         | f <sub>IN</sub> = 32 MHz   | -65.4,<br><b>-63.3</b> | <b>-</b> 72     |     | dBc   |

|                                                   | Tatalillana aria Biatania a (Final C | f <sub>IN</sub> = 11 MHz   | -66.2, <b>-63</b>      | <del>-</del> 74 |     | dB    |

| THD Total Harmonic Distortion (First 6 Harmonics) |                                      | f <sub>IN</sub> = 32 MHz   | -65.4,<br><b>-63.3</b> | <b>-</b> 72     |     | dB    |

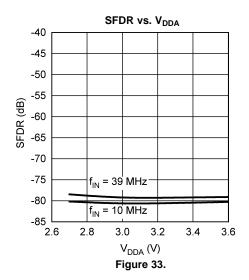

| 0500                                              | Spurious Free Dynamic Range          | f <sub>IN</sub> = 11 MHz   | -75.8,<br><b>-74.5</b> | -80             |     | dBc   |

| SFDR                                              | (Excluding 2nd and 3rd Harmonic)     | f <sub>IN</sub> = 32 MHz   | -74.4,<br><b>-73.3</b> | -80             |     | dBc   |

<sup>(1)</sup> The analog inputs are protected as shown below. Input voltage magnitude up to 500 mV beyond the supply rails will not damage this device. However, input errors will be generated if the input goes above V<sub>DDA</sub> or V<sub>DDIO</sub> and below V<sub>SSA</sub> or V<sub>SSIO</sub>. See Figure 2

# **AC Electrical Characteristics**

Unless otherwise specified, the following specifications apply for  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = 1.20V$  (External),  $f_{CLK} = 65$  MHz, 50% Duty Cycle,  $C_L = 10$  pF/pin. **Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>:** all other limits  $T_A = 25^{\circ}C$ . (1)

|                    | Parameter               | Test Conditions | Min <sup>(2)</sup> | Typ <sup>(2)</sup> | Max <sup>(2)</sup> | Units     |  |  |  |  |  |  |

|--------------------|-------------------------|-----------------|--------------------|--------------------|--------------------|-----------|--|--|--|--|--|--|

| CLK, DF            | CLK, DF, STBY, SENSE    |                 |                    |                    |                    |           |  |  |  |  |  |  |

| f <sub>CLK</sub> 1 | Maximum Clock Frequency |                 |                    |                    | 65                 | MHz (min) |  |  |  |  |  |  |

| f <sub>CLK</sub> 2 | Minimum Clock Frequency |                 |                    | 20                 |                    | MHz       |  |  |  |  |  |  |

| t <sub>CH</sub>    | Clock High Time         |                 |                    | 7.69               |                    | ns        |  |  |  |  |  |  |

| t <sub>CL</sub>    | Clock Low Time          |                 |                    | 7.69               |                    | ns        |  |  |  |  |  |  |

|                    | Conversion Latency      |                 |                    |                    | 6                  | Cycles    |  |  |  |  |  |  |

<sup>(1)</sup> The analog inputs are protected as shown below. Input voltage magnitude up to 500 mV beyond the supply rails will not damage this device. However, input errors will be generated if the input goes above V<sub>DDA</sub> or V<sub>DDIO</sub> and below V<sub>SSA</sub> or V<sub>SSIO</sub>. See Figure 2

2) Timing specifications are tested at TTL logic levels,  $V_{IL} = 0.4V$  for a falling edge, and  $V_{IH} = 2.4V$  for a rising edge.

Product Folder Links: ADC10065

<sup>(2)</sup> Optimum dynamic performance will be obtained by keeping the reference input in the +1.2V.

#### **AC Electrical Characteristics (continued)**

Unless otherwise specified, the following specifications apply for  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = 1.20V$  (External),  $f_{CLK} = 65$  MHz, 50% Duty Cycle,  $C_L = 10$  pF/pin. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}:** all other limits  $T_A = 25^{\circ}$ C. (1)

|                   | Parameter                              | Test Conditions                                                             | Min <sup>(2)</sup> | Typ <sup>(2)</sup> | Max (2) | Units       |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------|--------------------|--------------------|---------|-------------|

|                   | Data Output Delay after a Rising Clock | T = 25°C                                                                    | 2                  | 3.4                | 5       | ns          |

| t <sub>OD</sub>   | Edge                                   |                                                                             | 1                  |                    | 6       | ns          |

| t <sub>AD</sub>   | Aperture Delay                         |                                                                             |                    | 1                  |         | ns          |

| $t_{AJ}$          | Aperture Jitter                        |                                                                             |                    | 2                  |         | ps (RMS)    |

|                   | Over Range Recovery Time               | Differential V <sub>IN</sub> step from ±3V to 0V to get accurate conversion |                    | 1                  |         | Clock Cycle |

| t <sub>STBY</sub> | Standby Mode Exit Cycle                |                                                                             |                    | 20                 |         | Cycles      |

Figure 2.

## **Specification Definitions**

**APERTURE DELAY** is the time after the rising edge of the clock to when the input signal is acquired or held for conversion.

**APERTURE JITTER (APERTURE UNCERTAINTY)** is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.

**COMMON MODE VOLTAGE (V\_{CM})** is the d.c. potential present at both signal inputs to the ADC.

**CONVERSION LATENCY** See PIPELINE DELAY.

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

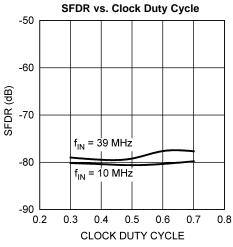

**DUTY CYCLE** is the ratio of the time that a repetitive digital waveform is high to the total time of one period. The specification here refers to the ADC clock input signal.

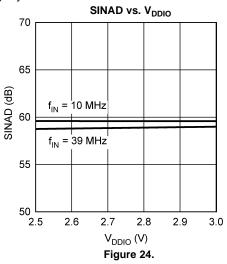

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and states that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

**GAIN ERROR** is the deviation from the ideal slope of the transfer function. It can be calculated as:

Gain Error = Positive Full-Scale Error - Negative Full-Scale Error (1)

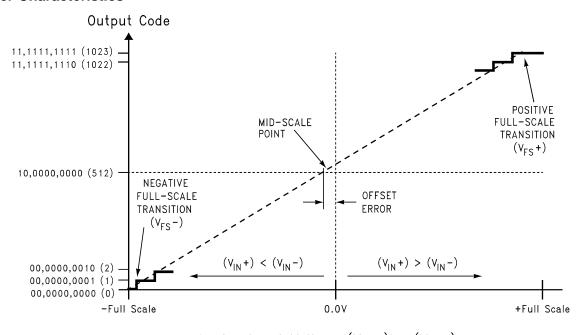

**INTEGRAL NON LINEARITY (INL)** is a measure of the deviation of each individual code from a line drawn from negative full scale through positive full scale. The deviation of any given code from this straight line is measured from the center of that code value.

**MISSING CODES** are those output codes that will never appear at the ADC outputs. The ADC10065 is specified not to have any missing codes.

**NEGATIVE FULL SCALE ERROR** is the difference between the input voltage  $(V_{IN}^+ - V_{IN}^-)$  just causing a transition from negative full scale to the first code and its ideal value of 0.5 LSB.

- **OFFSET ERROR** is the input voltage that will cause a transition from a code of 01 1111 1111 to a code of 10 0000 0000.

- **OUTPUT DELAY** is the time delay after the rising edge of the clock before the data update is presented at the output pins.

- **PIPELINE DELAY (LATENCY)** is the number of clock cycles between initiation of conversion and when that data is presented to the output driver stage. Data for any given sample is available at the output pins the Pipeline Delay plus the Output Delay after the sample is taken. New data is available at every clock cycle, but the data lags the conversion by the pipeline delay.

- **POSITIVE FULL SCALE ERROR** is the difference between the actual last code transition and its ideal value of 1½ LSB below positive full scale.

- **SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or DC.

- **SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding DC.

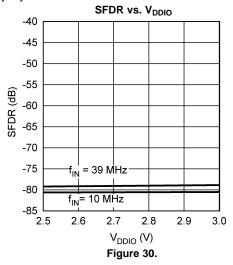

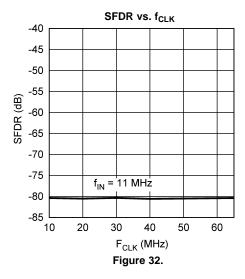

- **SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the rms values of the input signal and the peak spurious signal, where a spurious signal is any signal present in the output spectrum that is not present at the input.

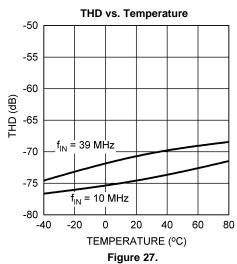

- **TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dBc, of the rms total of the first six harmonic levels at the output to the level of the fundamental at the output. THD is calculated as:

THD =

$$20 \times \log \sqrt{\frac{f_2^2 + f_3^2 + ... + f_6^2}{f_1^2}}$$

where

- f<sub>1</sub> is the RMS power of the fundamental (output) frequency

- f<sub>2</sub> through f<sub>6</sub> are the RMS power in the first 6 harmonic frequencies.

**SECOND HARMONIC DISTORTION (2ND HARM)** is the difference expressed in dB, between the RMS power in the input frequency at the output and the power in its 2nd harmonic level at the output.

**THIRD HARMONIC DISTORTION (3RD HARM)** is the difference, expressed in dB, between the RMS power in the input frequency at the output and the power in its 3rd harmonic level at the output.

Product Folder Links: ADC10065

(2)

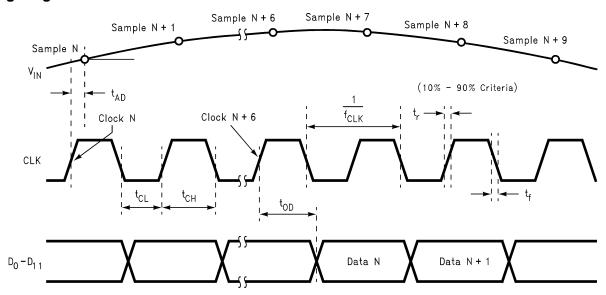

## **Timing Diagram**

Figure 3. Clock and Data Timing Diagram

## **Transfer Characteristics**

Analog Input Voltage (V<sub>IN</sub>+) - (V<sub>IN</sub>-)

Figure 4. Input vs. Output Transfer Characteristic

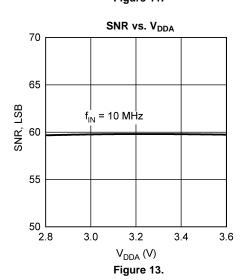

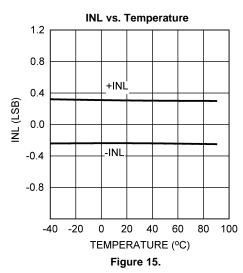

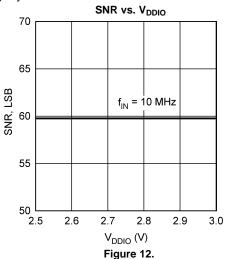

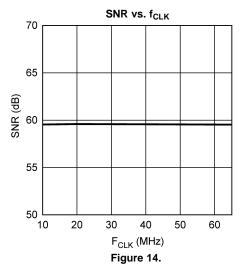

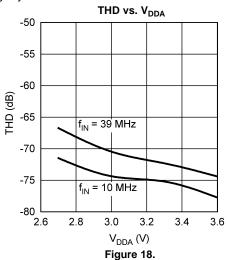

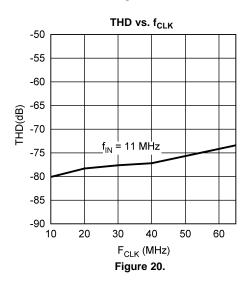

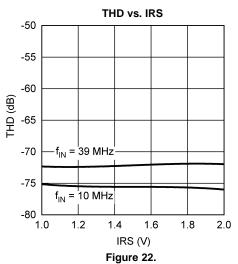

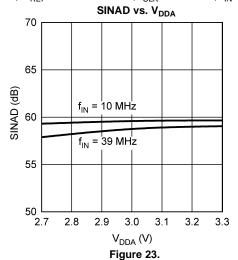

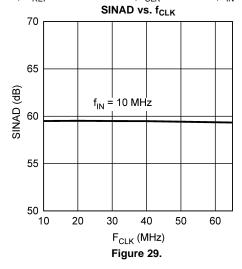

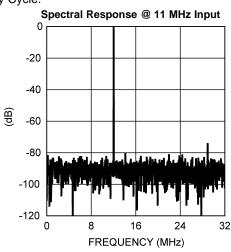

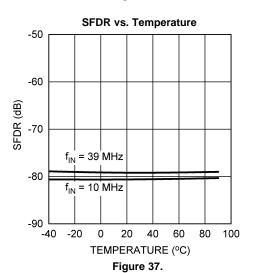

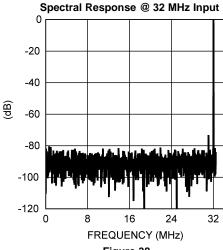

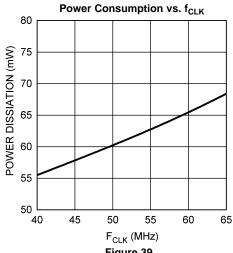

# **Typical Performance Characteristics**

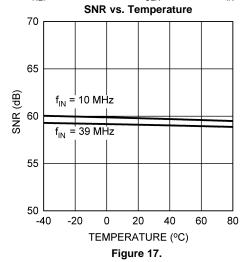

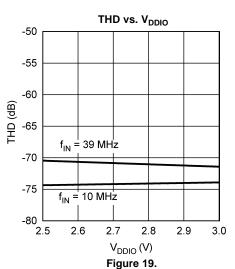

Unless otherwise specified, the following specifications apply:  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF}$  = External 1.2V,  $f_{CLK}$  = 65 MHz,  $f_{IN}$  = 11 MHz, 50% Duty Cycle.

Copyright © 2003–2013, Texas Instruments Incorporated

Unless otherwise specified, the following specifications apply:  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = External 1.2V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 11$  MHz, 50% Duty Cycle.

Unless otherwise specified, the following specifications apply:  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = External 1.2V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 11$  MHz, 50% Duty Cycle.

Unless otherwise specified, the following specifications apply:  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = External 1.2V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 11$  MHz, 50% Duty Cycle.

Unless otherwise specified, the following specifications apply:  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = External 1.2V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 11$  MHz, 50% Duty Cycle.

Unless otherwise specified, the following specifications apply:  $V_{SSA} = V_{SSIO} = 0V$ ,  $V_{DDA} = +3.0V$ ,  $V_{DDIO} = +2.5V$ ,  $V_{IN} = 2$   $V_{P-P}$ , STBY = 0V,  $V_{REF} = External 1.2V$ ,  $f_{CLK} = 65$  MHz,  $f_{IN} = 11$  MHz, 50% Duty Cycle.

Figure 36.

Figure 38.

Figure 39.

#### FUNCTIONAL DESCRIPTION

The ADC10065 uses a pipeline architecture and has error correction circuitry to help ensure maximum performance. Differential analog input signals are digitized to 10 bits. In differential mode, each analog input signal should have a peak-to-peak voltage equal to 1.0V, 0.75V or 0.5V, depending on the state of the IRS pin (pin 5), and be centered around  $V_{CM}$  and be 180° out of phase with each other. If single ended operation is desired,  $V_{IN}$ - may be tied to the  $V_{COM}$  pin (pin 4). A single ended input signal may then be applied to  $V_{IN}$ +, and should have an average value in the range of  $V_{CM}$ . The signal amplitude should be 2.0V, 1.5V or 1.0V peak-to-peak, depending on the state or the IRS pin (pin 5).

#### **Applications Information**

#### **ANALOG INPUTS**

The ADC10065 has two analog signal inputs,  $V_{IN}$ + and  $V_{IN}$ -. These two pins form a differential input pair. There is one common mode pin  $V_{COM}$  that may be used to set the common mode input voltage.

#### REFERENCE PINS

The ADC10065 is designed to operate with a 1.2V reference. The voltages at  $V_{COM}$ ,  $V_{REFT}$ , and  $V_{REFB}$  are derived from the reference voltage. It is very important that all grounds associated with the reference voltage and the input signal make connection to the analog ground plane at a single point to minimize the effects of noise currents in the ground path. The three Reference Bypass Pins  $V_{REF}$ ,  $V_{REFT}$  and  $V_{REFB}$ , are made available for bypass purposes only. These pins should each be bypassed to ground with a 0.1  $\mu$ F capacitor. DO NOT LOAD these pins.

## V<sub>COM</sub> PIN

This pin supplies a voltage for possible use to set the common mode input voltage. This pin may also be connected to  $V_{IN}$ -, so that  $V_{IN}$ + may be used as a single ended input. This pin should be bypassed with at least a 0.1  $\mu$ F capacitor. Do not load this pin.

#### **SIGNAL INPUTS**

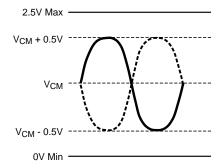

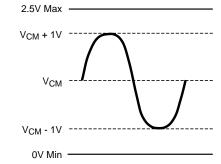

The signal inputs are  $V_{IN}$ + and  $V_{IN}$ -. The input signal amplitude is defined as  $V_{IN}$ + -  $V_{IN}$ - and is represented schematically in Figure 40:

Figure 40. Input Voltage Waveforms for a 2V<sub>P-P</sub> differential Input

Figure 41. Input Voltage Waveform for a 2V<sub>P-P</sub> Single Ended Input

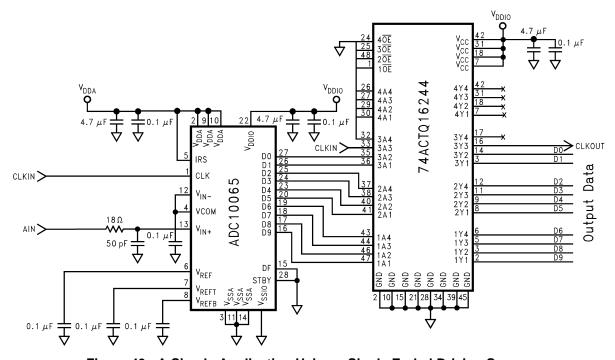

A single ended input signal is shown in Figure 41.

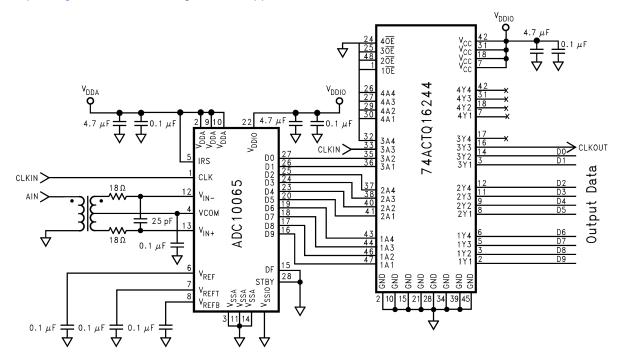

The internal switching action at the analog inputs causes energy to be output from the input pins. As the driving source tries to compensate for this, it adds noise to the signal. To prevent this, use  $18\Omega$  series resistors at each of the signal input pins with a 25 pF capacitor across the inputs, as shown in Figure 42. These components should be placed close to the ADC because the input pins of the ADC is the most sensitive part of the system and this is the last opportunity to filter the input. The two  $18\Omega$  resistors and the 25 pF capacitor form a low-pass filter with a -3 dB frequency of 177 MHz.

#### **CLK PIN**

The CLK signal controls the timing of the sampling process. Drive the clock input with a stable, low jitter clock signal in the frequency range indicated in AC Electrical Characteristics with rise and fall times of less than 2 ns. The trace carrying the clock signal should be as short as possible and should not cross any other signal line, analog or digital, not even at 90°. The CLK signal also drives an internal state machine. If the CLK is interrupted, or its frequency is too low, the charge on internal capacitors can dissipate to the point where the accuracy of the output data will degrade. This is what limits the lowest sample rate. The duty cycle of the clock signal can affect the performance of any A/D Converter. Because achieving a precise duty cycle is difficult, the ADC10065 is designed to maintain performance over a range of duty cycles. While it is specified and performance is ensured with a 50% clock duty cycle, performance is typically maintained with minimum clock low and high times indicated in AC Electrical Characteristics. Both minimum high and low times may not be held simultaneously

#### **STBY PIN**

The STBY pin, when high, holds the ADC10065 in a power-down mode to conserve power when the converter is not being used. The power consumption in this state is 15 mW. The output data pins are undefined in this mode. Power consumption during power-down is not affected by the clock frequency, or by whether there is a clock signal present. The data in the pipeline is corrupted while in power down.

#### **DF PIN**

The DF (Data Format) pin, when high, forces the ADC10065 to output the 2's complement data format. When DF is tied low, the output format is offset binary.

#### **IRS PIN**

The IRS (Input Range Select) pin defines the input signal amplitude that will produce a full scale output. Table 1 describes the function of the IRS pin.

IRS PinFull-Scale Input $V_{DDA}$  $2.0V_{P-P}$  $V_{SSA}$  $1.5V_{P-P}$ Floating $1.0V_{P-P}$

Table 1. IRS Pin Functions

#### **OUTPUT PINS**

The ADC10065 has 10 TTL/CMOS compatible Data Output pins. The offset binary data is present at these outputs while the DF and STBY pins are low. Be very careful when driving a high capacitance bus. The more capacitance the output drivers must charge for each conversion, the more instantaneous digital current flows through  $V_{\rm DDIO}$  and  $V_{\rm SSIO}$ . These large charging current spikes can cause on-chip noise and couple into the analog circuitry, degrading dynamic performance. Adequate bypassing, limiting output capacitance and careful attention to the ground plane will reduce this problem. Additionally, bus capacitance beyond the specified 10 pF/pin will cause  $t_{\rm OD}$  to increase, making it difficult to properly latch the ADC output data. The result could be an apparent reduction in dynamic performance. To minimize noise due to output switching, minimize the load currents at the digital outputs. This can be done by minimizing load capacitance and by connecting buffers between the ADC outputs and any other circuitry, which will isolate the outputs from trace and other circuit capacitances and limit the output currents, which could otherwise result in performance degradation. Only one driven input should be connected to the ADC output pins.

While the  $t_{\text{OD}}$  time provides information about output timing, a simple way to capture a valid output is to latch the data on the rising edge of the conversion clock.

#### **APPLICATION SCHEMATICS**

The following figures show simple examples of using the ADC10065. Figure 42 shows a typical differentially driven input. Figure 43 shows a single ended application circuit.

Figure 42. A Simple Application Using a Differential Driving Source

Figure 43. A Simple Application Using a Single Ended Driving Source

Copyright © 2003–2013, Texas Instruments Incorporated

## SNAS225H – JULY 2003 – REVISED APRIL 2013

# **REVISION HISTORY**

| Cł | nanges from Revision G (April 2013) to Revision H  | Pa | ge |

|----|----------------------------------------------------|----|----|

| •  | Changed layout of National Data Sheet to TI format |    | 19 |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

| ADC10065CIMT/NOPB     | Active        | Production    | TSSOP (PW)   28 | 48   TUBE             | Yes  | (4)<br>SN                     | (5)<br>Level-3-260C-168 HR | -40 to 85    | ADC10065<br>CIMT |

| ADC10065CIMT/NOPB.A   | Active        | Production    | TSSOP (PW)   28 | 48   TUBE             | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 85    | ADC10065<br>CIMT |

| ADC10065CIMTX/NOPB    | Active        | Production    | TSSOP (PW)   28 | 2500   LARGE T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 85    | ADC10065<br>CIMT |

| ADC10065CIMTX/NOPB.A  | Active        | Production    | TSSOP (PW)   28 | 2500   LARGE T&R      | Yes  | SN                            | Level-3-260C-168 HR        | -40 to 85    | ADC10065<br>CIMT |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

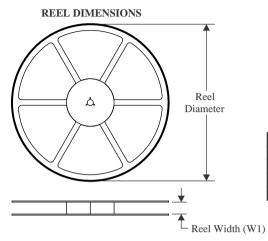

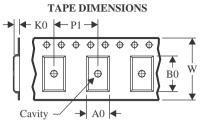

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

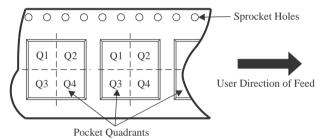

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADC10065CIMTX/NOPB | TSSOP           | PW                 | 28 | 2500 | 330.0                    | 16.4                     | 6.95       | 10.0       | 1.7        | 8.0        | 16.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

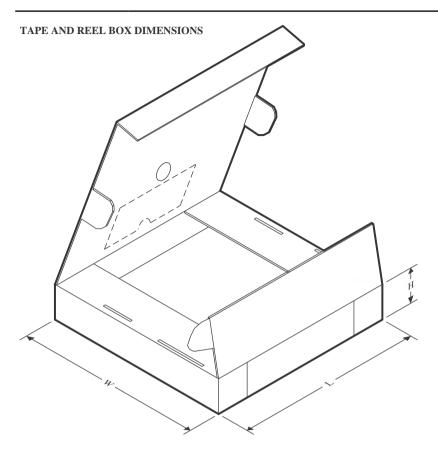

#### \*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADC10065CIMTX/NOPB | TSSOP        | PW              | 28   | 2500 | 356.0       | 356.0      | 36.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

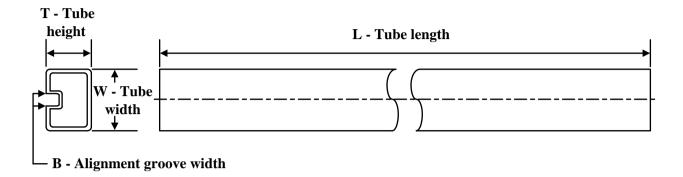

## **TUBE**

#### \*All dimensions are nominal

| Device              | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ADC10065CIMT/NOPB   | PW           | TSSOP        | 28   | 48  | 495    | 8      | 2514.6 | 4.06   |

| ADC10065CIMT/NOPB.A | PW           | TSSOP        | 28   | 48  | 495    | 8      | 2514.6 | 4.06   |

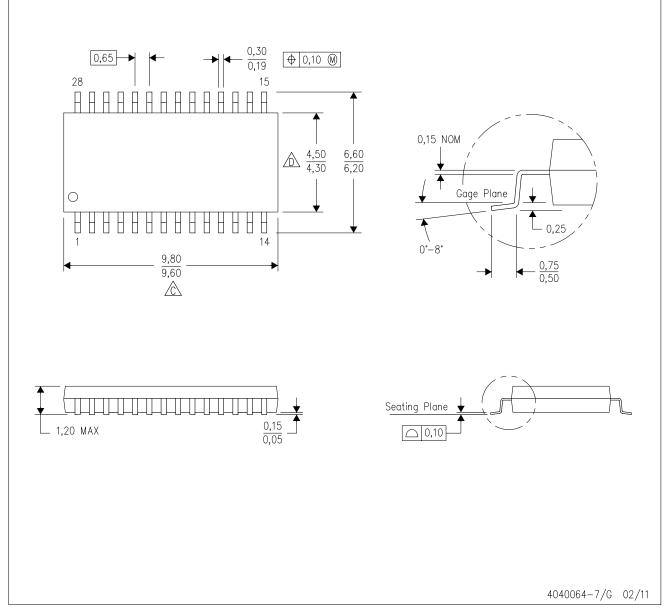

PW (R-PDSO-G28)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025