# ADC3664-SP Radiation-Hardness-Assured 14-Bit, Dual Channel, 1 to 125MSPS, Low Latency, Low Noise, Ultra-low Power, Analog-to-Digital Converter (ADC)

### 1 Features

- Screening and radiation performance

- QMLV screening and reliability assurance

- Total ionizing dose (TID): 300krad (Si)

- Single event latch-up (SEL): 75MeV-cm<sup>2</sup>/mg

- Ambient temperature range: -55°C to 105°C

- **Dual Channel ADC**

- 14-bit 125MSPS

- Noise floor: -156.9dBFS/Hz

- Low power consumption: 100mW/ch

- Latency: 2 clock cycles

- Clock rate versus voltage reference:

- External reference: 1MSPS to 125MSPS

- Internal reference: 100MSPS to 125MSPS

- 14-Bit, no missing codes

- Input bandwidth: 200MHz (-3dB)

- INL: ±2.6LSB; DNL: ±0.9LSB

- Optional digital down converter (DDC):

- Real or complex decimation

- Decimation by 2, 4, 8, 16, and 32

- 32-bit NCO

- Serial LVDS (SLVDS) interface (2-, 1-, and 1/2-wire)

- Spectral performance ( $F_{IN} = 5MHz$ ):

- SNR: 77.5dBFS

- SFDR: 84dBc HD2, HD3

- Non HD23: 91dBc

# 2 Applications

- Optical imaging payload

- Radar imaging payload

- Satellite communication payloads

# 3 Description

The ADC3664-SP is a low latency, low noise, and ultra low power, 14-bit, 125MSPS, high-speed dual channel ADC. Designed for best noise performance, the device delivers a noise spectral density of

-156.9dBFS/Hz combined with excellent linearity and dynamic range. The ADC3664-SP offers DC precision together with IF sampling support to enable the design of a wide range of applications. The low latency architecture (as low as 1 clock cycle latency) and high sample rate also enable high speed control loops. The ADC consumes only 100mW/ch at 125MSPS and the power consumption scales well with sampling rate.

The device uses a serial LVDS (SLVDS) interface to output the data which minimizes the number of digital interconnects. The device also integrates a digital down converter (DDC) to help reduce the data rate and lower system power consumption. The device is pin-to-pin compatible with the 18-bit, 65MSPS ADC3683-SP. The device comes in a 64-pin CFP package (10.9mm x 10.9mm) and supports a temperature range from -55°C to +105°C.

#### **Device Information**

| PART NUMBER                  | GRADE                                                  | PACKAGE <sup>(1)</sup>            |

|------------------------------|--------------------------------------------------------|-----------------------------------|

| 5962F2320501VXC              | Radiation hardness assured QML-V                       | 10.9mm x 10.9mm                   |

| ADC3664HBP/EM <sup>(2)</sup> | Engineering model,<br>for non-flight<br>prototype work | 64-pin Ceramic Flat<br>Pack (HBP) |

- For more information, see Section 12.

- These units are intended for engineering evaluation only. They are not put through a compliant flow (so there is no burn-in, only 25°C testing, etc.). Additionally, these units are not suitable for qualification, production, radiation testing, or flight use. The parts are not warranted for performance over temperature or operating life.

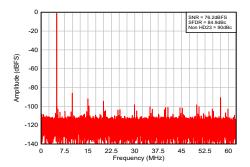

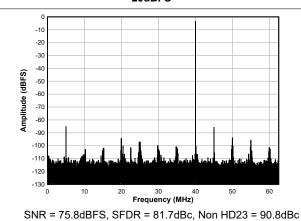

Single Tone Spectrum,  $F_s = 125MSPS$ ,  $F_{in} = 5MHz$

# **Table of Contents**

| 1 Features                                         | 1             |

|----------------------------------------------------|---------------|

| 2 Applications                                     |               |

| 3 Description                                      |               |

| 4 Pin Configuration and Functions                  |               |

| 5 Specifications                                   |               |

| 5.1 Absolute Maximum Ratings                       |               |

| 5.2 ESD Ratings                                    |               |

| 5.3 Recommended Operating Conditions               |               |

| 5.4 Thermal Information                            |               |

| 5.5 Electrical Characteristics - Power Consumption | 6             |

| 5.6 Electrical Characteristics - DC Specifications | 7             |

| 5.7 Electrical Characteristics - AC Specifications | 9             |

| 5.8 Timing Requirements                            |               |

| 5.9 Typical Characteristics                        |               |

| 6 Parameter Measurement Information                | 16 10         |

| 7 Detailed Description                             | <b>19 1</b> 1 |

| 7.1 Overview                                       |               |

| 7.2 Functional Block Diagram                       | 19            |

| 7.3 Feature Description                            | 20            |

|   | 7.4 Device Functional Modes                         | 42   |

|---|-----------------------------------------------------|------|

|   | 7.5 Programming                                     | . 43 |

| , | Application Information Disclaimer                  | .60  |

|   | 8.1 Application Information                         | . 60 |

|   | 8.2 Typical Application                             | . 60 |

|   | 8.3 Initialization Set Up                           | . 61 |

|   | 8.4 Power Supply Recommendations                    | .62  |

|   | 8.5 Layout                                          | . 63 |

| ) | Device and Documentation Support                    | 65   |

|   | 9.1 Receiving Notification of Documentation Updates | .65  |

|   | 9.2 Support Resources                               | . 65 |

|   | 9.3 Trademarks                                      | .65  |

|   | 9.4 Electrostatic Discharge Caution                 | .65  |

|   | 9.5 Glossary                                        |      |

| ( | 0 Revision History                                  | . 65 |

| • | 1 Mechanical, Packaging, and Orderable              |      |

|   | Information                                         | . 65 |

|   | 11.1 Mechanical Data                                | . 66 |

|   |                                                     |      |

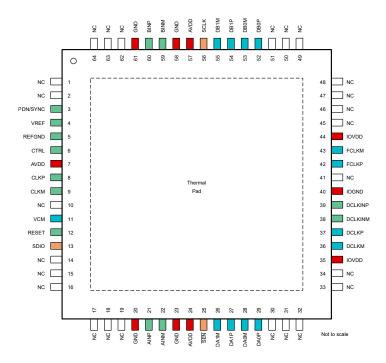

# **4 Pin Configuration and Functions**

Figure 4-1. HBP Package, 64-Pin CFP (Top View)

**Table 4-1. Pin Functions**

|          | PIN      | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |

|----------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.      | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |

| INPUT    |          |      |                                                                                                                                                                                                                                                                            |  |  |

| AINP     | 21       | I    | Positive analog input for ADC A.                                                                                                                                                                                                                                           |  |  |

| AINM     | 22       | I    | Negative analog input for ADC A.                                                                                                                                                                                                                                           |  |  |

| BINP     | 60       | I    | Positive analog input for ADC B.                                                                                                                                                                                                                                           |  |  |

| BINM     | 59       | I    | Negative analog input for ADC B.                                                                                                                                                                                                                                           |  |  |

| CLKP     | 8        | 1    | Positive sampling clock input for ADCs A and B.                                                                                                                                                                                                                            |  |  |

| CLKM     | 9        | 1    | Negative sampling clock input for ADCs A and B.                                                                                                                                                                                                                            |  |  |

| VREF     | 4        | I    | External, 1.6V, voltage reference input.                                                                                                                                                                                                                                   |  |  |

| REFGND   | 5        | I    | Voltage reference ground. This pin allows close placement of the decoupling capacitors near the VREF input when using either the internal or external reference modes.                                                                                                     |  |  |

| CTRL     | 6        | I    | This pin is used to configure the default sampling clock type and voltage reference source upon power up (see Section 7.5.1). There is an internal 100kΩ pull-up resistor to AVDD.                                                                                         |  |  |

| PDN/SYNC | 3        | I    | Dual purpose, active high, pin. The pin can be configured to control the power down state of the device or as a synchronization input. The pin functionality can be configured via SPI (default function is PDN). This pin has an internal $21k\Omega$ pull-down resistor. |  |  |

| RESET    | 12       | I    | Active high reset pin. This pin has an internal 21kΩ pull-down resistor.                                                                                                                                                                                                   |  |  |

| DCLKINP  | 39       | ı    | Positive input of the interface clock. This pin connects to DCLKINM through an internal $100\Omega$ termination resistor.                                                                                                                                                  |  |  |

| DCLKINM  | 38       | I    | Negative input of the interface clock. This pin connects to DCLKINP through an internal $100\Omega$ termination resistor.                                                                                                                                                  |  |  |

| ОИТРИТ   | <u>'</u> | •    | ·                                                                                                                                                                                                                                                                          |  |  |

| DA0P     | 29       | 0    | Positive output for interface lane A0.                                                                                                                                                                                                                                     |  |  |

| DA0M     | 28       | 0    | Negative output for interface lane A0.                                                                                                                                                                                                                                     |  |  |

# Table 4-1. Pin Functions (continued)

|                                                                                                                                                                  | PIN                                                                                                       | TVDE | DESCRIPTION                                                                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------|--|--|

| NAME                                                                                                                                                             | NO.                                                                                                       | ITPE | DESCRIPTION                                                                    |  |  |

| DA1P                                                                                                                                                             | 27                                                                                                        | 0    | Positive output for interface lane A1.                                         |  |  |

| DA1M                                                                                                                                                             | 26                                                                                                        | 0    | Negative output for interface lane A1.                                         |  |  |

| NAME         NO.           DA1P         27         O           DA1M         26         O           DB0P         52         O           DB0M         53         O |                                                                                                           | 0    | Positive output for interface lane B0.                                         |  |  |

| DB0M                                                                                                                                                             | 53                                                                                                        | 0    | Negative output for interface lane B0                                          |  |  |

| DB1P                                                                                                                                                             | 54                                                                                                        | 0    | Positive output for interface lane B1.                                         |  |  |

| DB1M                                                                                                                                                             | 55                                                                                                        | 0    | Negative output for interface lane B1.                                         |  |  |

| DCLKP                                                                                                                                                            | 37                                                                                                        | 0    | Positive output of the interface clock.                                        |  |  |

| DCLKM                                                                                                                                                            | 36                                                                                                        | 0    | Negative output of the interface clock.                                        |  |  |

| FCLKP                                                                                                                                                            | 42                                                                                                        | 0    | Positive output of the interface frame clock.                                  |  |  |

| FCLKM                                                                                                                                                            | 43                                                                                                        | 0    | Negative output of the interface frame clock.                                  |  |  |

| VCM                                                                                                                                                              | 11                                                                                                        | 0    | Common-mode output voltage of the analog inputs (typically 0.95V).             |  |  |

| SPI                                                                                                                                                              |                                                                                                           |      |                                                                                |  |  |

| SEN                                                                                                                                                              | 25                                                                                                        | I    | Active low SPI enable. This pin has an internal 21kΩ pull-up resistor to AVDD. |  |  |

| SCLK                                                                                                                                                             | 56                                                                                                        | I    | SPI clock input. This pin has an internal 21kΩ pull-down resistor.             |  |  |

| SDIO                                                                                                                                                             | 13                                                                                                        | I/O  | SPI data input or output. This pin has an internal 21kΩ pull-down resistor.    |  |  |

| POWER                                                                                                                                                            |                                                                                                           |      |                                                                                |  |  |

| AVDD                                                                                                                                                             | 7, 24, 57                                                                                                 | I    | Analog supply input, 1.8V.                                                     |  |  |

| GND                                                                                                                                                              | 20, 23, 58, 61                                                                                            | I    | Ground supply input, 0V.                                                       |  |  |

| IOVDD                                                                                                                                                            | 35, 44                                                                                                    | I    | Interface supply input, 1.8V.                                                  |  |  |

| IOGND                                                                                                                                                            | 40                                                                                                        | I    | Interface ground supply input, 0V.                                             |  |  |

| OTHER                                                                                                                                                            |                                                                                                           |      |                                                                                |  |  |

| DAP                                                                                                                                                              | DAP                                                                                                       | -    | Die attached pad (thermal pad), connect to GND.                                |  |  |

| NC                                                                                                                                                               | 1, 2, 10, 14, 15, 16, 17,<br>18, 19, 30, 31, 32, 33,<br>34, 41, 45, 46, 47, 48,<br>49, 50, 51, 62, 63, 64 | -    | No connect pins. Connect to ground or leave floating. <sup>(1)</sup>           |  |  |

<sup>(1)</sup> Thermal pad and top metal lid are connected to pin 17. Can be grounded or no connect.

# 5 Specifications

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| PARAMETER            | TEST CONDITIONS                    | MIN      | MAX                 | UNIT |

|----------------------|------------------------------------|----------|---------------------|------|

| Supply voltage range | e, AVDD, IOVDD                     | -0.3     | 2.1                 | V    |

| Supply voltage range | e, GND, IOGND, REFGND              | -0.3     | 0.3                 | V    |

|                      | AINP/M, BINP/M, CLKP/M, VREF, CTRL | -0.3 2.1 |                     |      |

| Voltage applied to   | PDN/SYNC, RESET, SCLK, SEN, SDIO   | -0.3     | MIN(2.1, AVDD+0.3)  | V    |

| mpat pino            | DCLKINP/M                          | -0.3     | MIN(2.1, IOVDD+0.3) |      |

| Junction temperature | e, T <sub>J</sub>                  |          | 125                 | °C   |

| Storage temperature  | e, T <sub>stg</sub>                | -65      | 150                 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                    |               |                                                                                          | VALUE | UNIT       |

|--------------------|---------------|------------------------------------------------------------------------------------------|-------|------------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | 1000  | \ <u>\</u> |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | 250   | <b>V</b>   |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX                | UNIT |

|----------------|--------------------------------|------|-----|--------------------|------|

| Supply         | AVDD <sup>(1)</sup>            | 1.75 | 1.8 | 1.85               | V    |

| voltage range  | IOVDD <sup>(1)</sup>           | 1.75 | 1.8 | 1.85               | V    |

| T <sub>A</sub> | Operating free-air temperature | -55  |     | 105                | °C   |

| TJ             | Operating junction temperature |      |     | 105 <sup>(2)</sup> | °C   |

- Measured with respect to GND.

- (2) Prolonged use above this junction temperature may increase the device failure-in-time (FIT) rate.

#### 5.4 Thermal Information

|                       |                                              | ADC3664-SP |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | HBP (CFP)  | UNIT |

|                       |                                              | 64 Pins    |      |

| $R_{\Theta JA}$       | Junction-to-ambient thermal resistance       | 28.4       | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 12.0       | °C/W |

| R <sub>⊝JB</sub>      | Junction-to-board thermal resistance         | 14.1       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 7.8        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 13.8       | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 7.0        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

# **5.5 Electrical Characteristics - Power Consumption**

Typical values are at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -55°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8V, external 1.6V reference, and -1dBFS differential input, unless otherwise noted.

|                    | PARAMETER                                   | TEST CONDITIONS                           | MIN TYP | MAX | UNIT        |

|--------------------|---------------------------------------------|-------------------------------------------|---------|-----|-------------|

| ADC3664-           | SP: 125MSPS                                 |                                           |         |     |             |

| 1                  | Analog gunnly gurrent                       | Internal reference                        | 72      |     |             |

| I <sub>AVDD</sub>  | Analog supply current                       | External reference                        | 66      | 82  | 82 mA<br>72 |

| I <sub>IOVDD</sub> | I/O supply current                          | 2-wire                                    | 45      | 72  |             |

| P <sub>DIS</sub>   | Power dissipation                           | External reference, 2-wire                | 200     | 277 | mW          |

|                    |                                             | 2-wire, 1/2-swing                         | 45      |     |             |

|                    | I/O supply current                          | 4x real decimation, 1-wire                | 54      |     |             |

|                    |                                             | 4x real decimation, 1/2-wire              | 55      |     |             |

|                    |                                             | 16x real decimation, 1-wire               | 49      |     | mA          |

| I <sub>IOVDD</sub> |                                             | 16x real decimation, 1/2-wire             | 49      |     |             |

|                    |                                             | 4x complex decimation, 1-wire             | 58      |     |             |

|                    |                                             | 16x complex decimation, 1-wire            | 51      |     |             |

|                    |                                             | 16x complex decimation, 1/2-wire          | 51      |     |             |

| P <sub>DIS</sub>   | Dower concumption in global newer           | Default mask settings, internal reference | 11      |     |             |

|                    | Power consumption in global power down mode | Default mask settings, external reference | 13      |     | mW          |

# 5.6 Electrical Characteristics - DC Specifications

Typical values are at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -55°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8V, 1.6V external reference, and -1dBFS differential input, unless otherwise noted.

|                         | PARAMETER                                        | TEST CONDITIONS              | MIN | TYP   | MAX   | UNIT     |

|-------------------------|--------------------------------------------------|------------------------------|-----|-------|-------|----------|

| DC ACCUR                | ACY                                              |                              |     |       |       |          |

| No missing of           | codes                                            |                              | 14  |       |       | bits     |

| PSRR                    | Power supply rejection ratio                     | F <sub>IN</sub> = 1MHz       |     | 35    |       | dB       |

| DNL                     | Differential nonlinearity                        | F <sub>IN</sub> = 5MHz       |     | ±0.9  | ±0.97 | LSB      |

| INL                     | Integral nonlinearity                            | F <sub>IN</sub> = 5MHz       |     | ±2.6  | ±9.5  | LSB      |

| Vos                     | Input offset                                     |                              |     | ±30   | ±50   | LSB      |

| V <sub>OS_DRIFT</sub>   | Offset drift                                     |                              |     | ±0.06 |       | LSB/°C   |

| Error                   | Gain error and internal reference combined error | Both channels are powered up |     | ±2    |       | %FSR     |

|                         | Gain error                                       | Both channels are powered up |     | ±1.8  |       | %FSR     |

|                         |                                                  | External 1.6V reference      |     | ±57   |       | ppm/°C   |

|                         | Gain drift                                       | Internal reference           |     | 106   |       | ppm/°C   |

| Fransition noise        |                                                  |                              |     | 0.7   |       | LSB      |

| ADC ANALO               | OG INPUT (AINP/M, BINP/M)                        |                              |     |       |       |          |

| FS                      | Input full scale                                 | Differential                 |     | 3.2   |       | $V_{pp}$ |

| V <sub>CM</sub>         | Input common-mode voltage                        |                              |     | 0.95  |       | V        |

| R <sub>IN</sub>         | Input resistance                                 | Differential at DC           |     | 8     |       | kΩ       |

| C <sub>IN</sub>         | Input capacitance                                | Differential at DC           |     | 5.4   |       | pF       |

| V <sub>OCM</sub>        | Output common-mode voltage                       |                              |     | 0.95  |       | V        |

| BW                      | Full power analog input bandwidth (-3dB)         |                              |     | 200   |       | MHz      |

| INTERNAL '              | VOLTAGE REFERENCE                                |                              |     |       |       |          |

| V <sub>REF</sub>        | Internal reference voltage                       |                              |     | 1.6   |       | V        |

| V <sub>REF</sub> output | impedance                                        |                              |     | 8     |       | Ω        |

| EXTERNAL                | VOLTAGE REFERENCE                                |                              |     |       |       |          |

| V <sub>REF</sub>        | External voltage reference                       |                              |     | 1.6   |       | V        |

| Input current           | i                                                |                              |     | 1     |       | mA       |

| Input impeda            | ance                                             |                              |     | 5.3   |       | kΩ       |

| CLOCK INP               | UT (CLKP/M)                                      |                              |     |       | -     |          |

| lanus alasti 6          |                                                  | External reference           | 1   |       | 125   | MHz      |

| Input clock fi          | equency                                          | Internal reference           | 100 | -     | 125   | MHz      |

| V <sub>ID</sub>         | Differential input voltage                       |                              | 0.5 | 1     |       | $V_{pp}$ |

| V <sub>CM</sub>         | Input common-mode voltage                        |                              |     | 0.9   |       | V        |

| R <sub>IN</sub>         | Single ended input resistance to common mode     |                              |     | 5     |       | kΩ       |

| C <sub>IN</sub>         | Single ended input capacitance                   |                              |     | 1.5   |       | pF       |

| Clock duty c            | ycle                                             |                              | 45  | 50    | 60    | %        |

# **5.6 Electrical Characteristics - DC Specifications (continued)**

Typical values are at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -55°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8V, 1.6V external reference, and -1dBFS differential input, unless otherwise noted.

|                 | PARAMETER                            | TEST CONDITIONS             | MIN            | TYP   | MAX      | UNIT      |

|-----------------|--------------------------------------|-----------------------------|----------------|-------|----------|-----------|

| DIGITAL         | INPUTS (RESET, PDN, SCLK, SEN, SDIO) |                             |                |       |          |           |

| V <sub>IH</sub> | High level input voltage             |                             | 1.5            |       |          | V         |

| V <sub>IL</sub> | Low level input voltage              |                             |                |       | 0.3      | V         |

| I <sub>IH</sub> | High level input current             |                             |                | 90    | 150      | uA        |

| I <sub>IL</sub> | Low level input current              |                             | -150           | -90   |          | uA        |

| Cı              | Input capacitance                    |                             |                | 1.5   |          | pF        |

| DIGITAL         | OUTPUT (SDOUT)                       |                             |                |       |          |           |

| V <sub>OH</sub> | High level output voltage            | I <sub>LOAD</sub> = -400 uA | IOVDD<br>– 0.1 | IOVDD |          | V         |

| V <sub>OL</sub> | Low level output voltage             | I <sub>LOAD</sub> = 400 uA  |                |       | 0.1      |           |

| LVDS lan        | e rate                               |                             |                |       | 1        | Gbps      |

| V <sub>ID</sub> | DCLKIN differential input voltage    |                             | 200            | 350   |          | $mV_{pp}$ |

| V <sub>CM</sub> | DCLKIN input common-mode voltage     |                             | 1.1            | 1.2   | 1.3      | V         |

| SLVDS IN        | ITERFACE                             |                             | <u> </u>       |       | <u> </u> |           |

| V <sub>OD</sub> | Differential output voltage          |                             | 0.585          | 700   | 0.785    | $mV_{pp}$ |

| $V_{CM}$        | Output common-mode voltage           |                             | 0.85           | 1.0   | 1.15     | V         |

# 5.7 Electrical Characteristics - AC Specifications

Typical values are at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -55°C to  $T_{MAX}$  = 105°C, ADC sampling rate = 125MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8V, 1.6V external reference, and -1dBFS differential input, unless otherwise noted.

|           | PARAMETER                                        | TEST CONDITIONS                                        | MIN  | TYP N  | IAX      | UNIT    |  |  |  |

|-----------|--------------------------------------------------|--------------------------------------------------------|------|--------|----------|---------|--|--|--|

| NSD       | Noise spectral density                           | F <sub>IN</sub> = 5MHz, A <sub>IN</sub> = -20dBFS      |      | -156.9 |          | dBFS/Hz |  |  |  |

|           |                                                  | F <sub>IN</sub> = 5MHz                                 | 70   | 77.5   |          | dBFS    |  |  |  |

|           |                                                  | F <sub>IN</sub> = 5MHz, A <sub>IN</sub> = -20dBFS      |      | 78.9   |          |         |  |  |  |

| OND       | Olam al tama is a matic                          | F <sub>IN</sub> = 10MHz                                |      | 77.6   |          | dBFS    |  |  |  |

| SNR       | Signal to noise ratio                            | F <sub>IN</sub> = 40MHz                                |      | 76.9   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 70MHz                                |      | 75.5   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 74.1   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 5 MHz                                |      | 75.7   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 10MHz                                |      |        |          |         |  |  |  |

| SINAD     | Signal to noise and distortion ratio             | F <sub>IN</sub> = 40MHz                                |      | 72.6   |          | dBFS    |  |  |  |

|           |                                                  | F <sub>IN</sub> = 70MHz                                |      | 71.3   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 72.4   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 5MHz                                 |      | 12.6   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 10MHz                                |      | 12.6   |          |         |  |  |  |

| ENOB      | Effective number of bits                         | F <sub>IN</sub> = 40MHz                                |      | 12.5   |          | bit     |  |  |  |

|           |                                                  | F <sub>IN</sub> = 70MHz                                |      | 12.3   |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 12.0   |          |         |  |  |  |

|           | Total harmonic distortion (first five harmonics) | F <sub>IN</sub> = 5MHz                                 | 68   | 80     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 10MHz                                |      | 76     |          | -       |  |  |  |

| THD       |                                                  | F <sub>IN</sub> = 40 =MHz                              |      | 74     |          | dBc     |  |  |  |

|           |                                                  | F <sub>IN</sub> = 70MHz                                |      | 72     |          | dbo     |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 76     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 5MHz                                 | 72.5 | 84     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 10MHz                                |      | 78     |          |         |  |  |  |

| HD2       | Second harmonic distortion                       | F <sub>IN</sub> = 40MHz                                |      | 75     |          | dBc     |  |  |  |

|           |                                                  | F <sub>IN</sub> = 70MHz                                |      | 77     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 79     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 5MHz                                 | 69.5 | 84     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 10MHz                                |      | 81     |          |         |  |  |  |

| HD3       | Third harmonic distortion                        | F <sub>IN</sub> = 40MHz                                |      | 88     |          | dBc     |  |  |  |

|           |                                                  | F <sub>IN</sub> = 70MHz                                |      | 76     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 81     |          |         |  |  |  |

| Non HD2,3 |                                                  | F <sub>IN</sub> = 5MHz                                 | 77   | 92     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 10MHz                                |      | 93     | $\dashv$ |         |  |  |  |

|           | Spurious free dynamic range                      | $F_{IN} = 40MHz$                                       |      | 89     |          | dBFS    |  |  |  |

| ,-        | (excluding HD2 and HD3)                          | F <sub>IN</sub> = 70MHz                                |      | 84     |          |         |  |  |  |

|           |                                                  | F <sub>IN</sub> = 100MHz                               |      | 86     |          |         |  |  |  |

| IMD3      | Two tone inter-modulation distortion             | $F_1 = 10MHz$ , $F_2 = 12MHz$ , $A_{IN} = -7dBFS/tone$ |      | 88     |          | dBc     |  |  |  |

# 5.8 Timing Requirements

Typical values are at  $T_A$  = 25°C, MIN and MAX timing values are characterized over the full temperature range  $T_{MIN}$  = -55°C to  $T_{MAX}$  = 105°C and are NOT production tested, ADC sampling rate = 125MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8V, 1.6V external reference, and -1dBFS differential input, unless otherwise noted.

|                     | PARAMETER                                                            | TEST CONDITIONS                             | MIN NOM I          | MAX   | UNIT                        |

|---------------------|----------------------------------------------------------------------|---------------------------------------------|--------------------|-------|-----------------------------|

| ADC TIMI            | NG SPECIFICATIONS                                                    | ,                                           |                    |       |                             |

| t <sub>AD</sub>     | Aperture delay                                                       |                                             | 0.85               |       | ns                          |

| t <sub>A</sub>      | Aperture jitter                                                      | Square wave clock with fast edges           | 250                |       | fs                          |

| t <sub>ACQ</sub>    | Signal acquisition period, referenced to sampling clock falling edge |                                             | -T <sub>S</sub> /4 |       | Sampling<br>clock<br>period |

| t <sub>CONV</sub>   | Signal conversion period, referenced to sampling clock falling edge  |                                             | 6                  |       | ns                          |

| Wake up<br>time     | Time to valid data after coming out of power down                    | External 1.6V reference, differential clock |                    | 100   | μs                          |

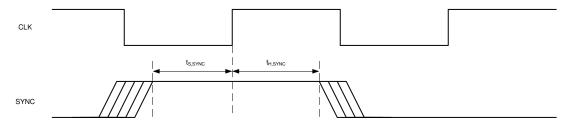

| t <sub>S,SYNC</sub> | Setup time for SYNC input signal                                     | Referenced to sampling clock rising edge    | 500                |       | ps                          |

| t <sub>H,SYNC</sub> | Hold time for SYNC input signal                                      | Referenced to sampling clock rising edge    | 600                | 600   |                             |

|                     | Signal input to data output                                          | 1/2-wire SLVDS                              | 1                  |       |                             |

|                     |                                                                      | 1-wire SLVDS                                | 1                  |       | Clock<br>cycles             |

| ADC<br>latency      |                                                                      | 2-wire SLVDS 2                              |                    |       | 0,0.00                      |

|                     |                                                                      | Real decimation by 2 21                     |                    |       | Output                      |

|                     |                                                                      | Complex decimation by 2                     | 22                 | clock |                             |

|                     |                                                                      | Real or complex decimation by 4, 8, 16, 32  | 23                 |       | cycles                      |

# 5.8 Timing Requirements (continued)

Typical values are at  $T_A$  = 25°C, MIN and MAX timing values are characterized over the full temperature range  $T_{MIN}$  = -55°C to  $T_{MAX}$  = 105°C and are NOT production tested, ADC sampling rate = 125MSPS, 50% clock duty cycle, AVDD = IOVDD = 1.8V, 1.6V external reference, and -1dBFS differential input, unless otherwise noted.

|                        | PARAMETER                                                          | TEST CONDITIONS                                                                                                                                                                      | MIN                       | NOM                                                 | MAX | UNIT    |  |  |

|------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------|-----|---------|--|--|

| INTERFAC               | E TIMING: SERIAL LVDS INTERFAC                                     | E                                                                                                                                                                                    |                           |                                                     |     |         |  |  |

|                        | Propagation delay: sampling clock falling edge to DCLK rising edge | Delay between sampling clock falling edge to DCLKIN falling edge < 2.5ns.  T <sub>DCLK</sub> = DCLK period t <sub>CDCLK</sub> = Sampling clock falling edge to DCLKIN falling edge   | +                         | 3 +<br>T <sub>DCLK</sub><br>+<br>t <sub>CDCLK</sub> | +   |         |  |  |

| t <sub>PD</sub>        |                                                                    | Delay between sampling clock falling edge to DCLKIN falling edge >= 2.5ns.  T <sub>DCLK</sub> = DCLK period  t <sub>CDCLK</sub> = Sampling clock falling edge to DCLKIN falling edge | 2 +<br>t <sub>CDCLK</sub> | 2+ 3+ 4+ tcdclk tcdclk tcdclk                       |     |         |  |  |

|                        | DCLK rising edge to output data delay                              | F <sub>out</sub> = 65MSPS, data rate = 455MBPS, 2-wire                                                                                                                               | 0                         | 0 0.1                                               |     | ns      |  |  |

| t <sub>CD</sub>        |                                                                    | F <sub>out</sub> = 125MSPS, data rate = 875MBPS, 2-wire                                                                                                                              | -0.2                      |                                                     |     |         |  |  |

|                        |                                                                    | F <sub>out</sub> = 65MSPS, data rate = 910MBPS, 1-wire                                                                                                                               | 0                         | 0.1                                                 | 0.3 |         |  |  |

|                        | Data valid                                                         | F <sub>out</sub> = 65MSPS, data rate = 455MBPS, 2-wire                                                                                                                               | 1.8                       | 1.9                                                 | 2   |         |  |  |

| $t_{DV}$               |                                                                    | F <sub>out</sub> = 125MSPS, data rate = 875MBPS, 2-wire                                                                                                                              | 0.6                       | 0.8                                                 | 0.9 | ns      |  |  |

|                        |                                                                    | F <sub>out</sub> = 65MSPS, data rate = 910MBPS, 1-wire                                                                                                                               | 0.6                       | 0.8                                                 | 0.9 | )  <br> |  |  |

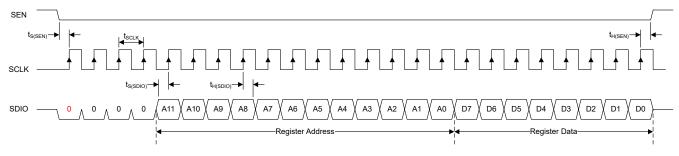

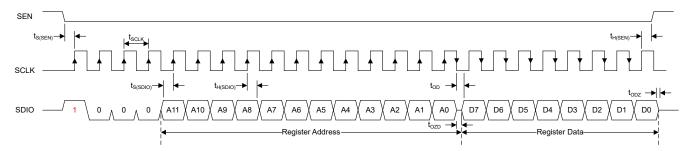

| SERIAL P               | ROGRAMMING INTERFACE (SCLK,                                        | SEN, SDIO) - INPUT                                                                                                                                                                   |                           |                                                     |     |         |  |  |

| f <sub>CLK(SCLK)</sub> | Serial clock frequency                                             |                                                                                                                                                                                      |                           |                                                     | 20  | MHz     |  |  |

| t <sub>SU(SEN)</sub>   | SEN to rising edge of SCLK                                         |                                                                                                                                                                                      |                           |                                                     | 10  |         |  |  |

| t <sub>H(SEN)</sub>    | SEN from rising edge of SCLK                                       |                                                                                                                                                                                      |                           |                                                     | 17  | ns      |  |  |

| t <sub>SU(SDIO)</sub>  | SDIO to rising edge of SCLK                                        |                                                                                                                                                                                      |                           |                                                     | 17  | 115     |  |  |

| t <sub>H(SDIO)</sub>   | SDIO from rising edge of SCLK                                      |                                                                                                                                                                                      |                           |                                                     | 10  |         |  |  |

| SERIAL P               | ROGRAMMING INTERFACE (SDIO) -                                      | OUTPUT                                                                                                                                                                               |                           |                                                     |     |         |  |  |

| t <sub>(OZD)</sub>     | SDIO HiZ to LoZ                                                    |                                                                                                                                                                                      |                           |                                                     | 19  |         |  |  |

| t <sub>(ODZ)</sub>     | SDIO LoZ to HiZ                                                    |                                                                                                                                                                                      |                           |                                                     | 17  | ns      |  |  |

| t <sub>(OD)</sub>      | Falling edge of SCLK to SDIO data valid                            |                                                                                                                                                                                      |                           |                                                     | 19  |         |  |  |

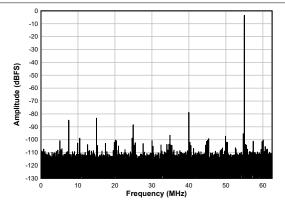

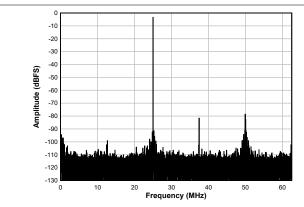

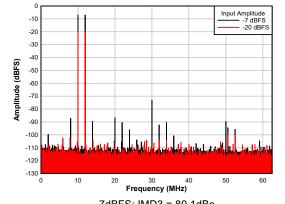

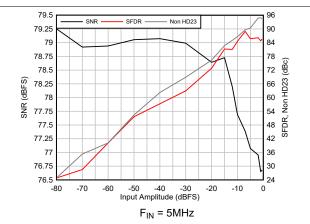

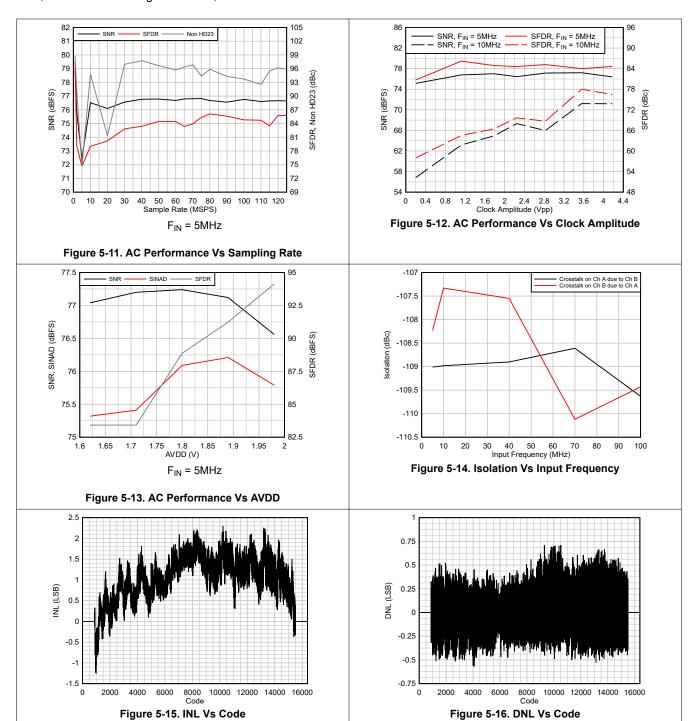

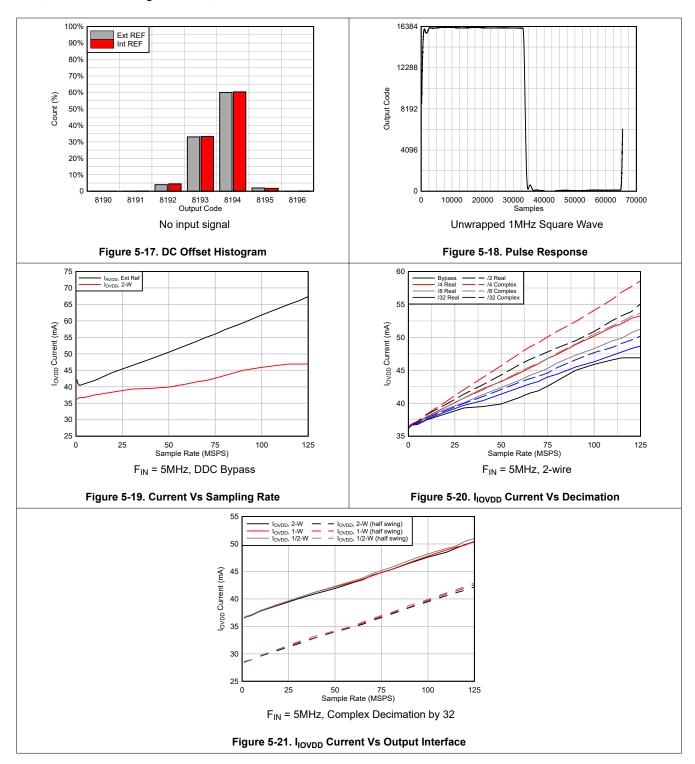

## **5.9 Typical Characteristics**

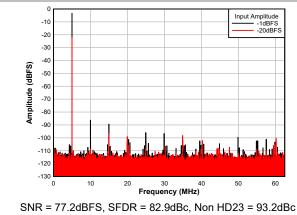

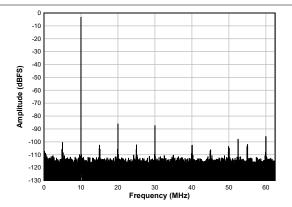

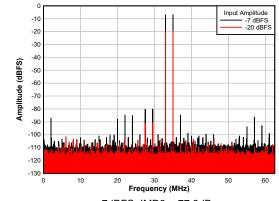

Typical values at  $T_A = 25$ °C, ADC sampling rate = 125MSPS,  $F_{IN} = 5$ MHz,  $A_{IN} = -1$ dBFS differential input, AVDD = IOVDD = 1.8V, external 1.6V voltage reference, unless otherwise noted.

SNR = 77.2dBFS, SFDR = 82.9dBc, Non HD23 = 93.2dBc -20dBFS: SNR = 78.5dBFS, SFDR = 74.1dBc, Non HD23 = 75.6dBc

Figure 5-1. Single Tone Spectrum At  $F_{IN}$  = 5MHz,  $A_{IN}$  = -1, -20dBFS

SNR = 77.1dBFS, SFDR = 82.8dBc, Non HD23 = 92.4dBc

Figure 5-2. Single Tone Spectrum At  $F_{IN}$  = 10MHz

Figure 5-3. Single Tone Spectrum At  $F_{IN}$  = 40MHz

SNR = 74.1dBFS, SFDR = 75.5dBc, Non HD23 = 81.4dBc

Figure 5-4. Single Tone Spectrum At  $F_{IN}$  = 70MHz

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# **5.9 Typical Characteristics (continued)**

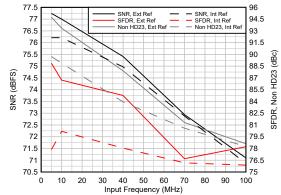

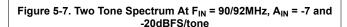

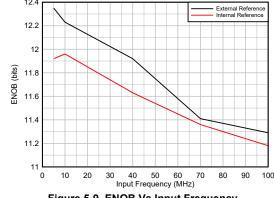

Typical values at  $T_A = 25$ °C, ADC sampling rate = 125MSPS,  $F_{IN} = 5$ MHz,  $A_{IN} = -1$ dBFS differential input, AVDD = IOVDD = 1.8V, external 1.6V voltage reference, unless otherwise noted.

SNR = 72.1dBFS, SFDR = 75dBc, Non HD23 = 78.1dBc

Figure 5-5. Single Tone Spectrum At  $F_{IN}$  = 100MHz

-7dBFS: IMD3 = 80.1dBc -20dBFS: IMD3 = 89.6dBc

Figure 5-6. Two Tone Spectrum At  $F_{\rm IN}$  = 10/12MHz,  $A_{\rm IN}$  = -7, -20dBFS/tone

-7dBFS: IMD3 = 77.8dBc -20dBFS: IMD3 = 85.7dBc

Figure 5-8. AC Performance Vs Input Frequency

Figure 5-9. ENOB Vs Input Frequency

Figure 5-10. AC Performance Vs Input Amplitude

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

# **5.9 Typical Characteristics (continued)**

Typical values at  $T_A = 25$ °C, ADC sampling rate = 125MSPS,  $F_{IN} = 5$ MHz,  $A_{IN} = -1$ dBFS differential input, AVDD = IOVDD = 1.8V, external 1.6V voltage reference, unless otherwise noted.

# **5.9 Typical Characteristics (continued)**

Typical values at  $T_A = 25$ °C, ADC sampling rate = 125MSPS,  $F_{IN} = 5$ MHz,  $A_{IN} = -1$ dBFS differential input, AVDD = IOVDD = 1.8V, external 1.6V voltage reference, unless otherwise noted.

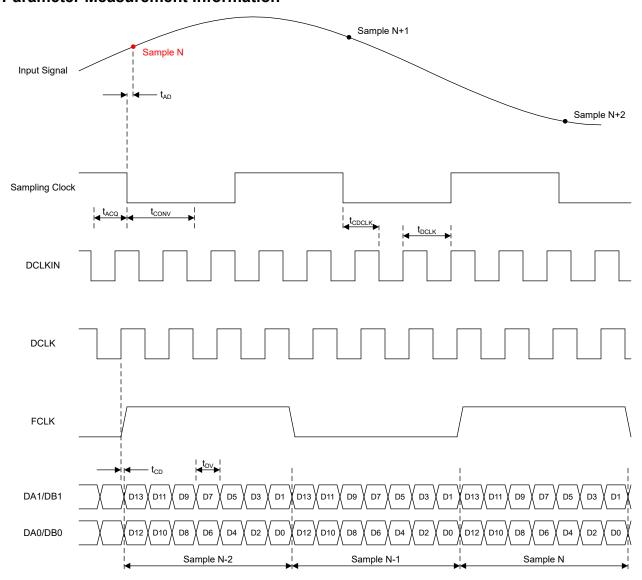

# **6 Parameter Measurement Information**

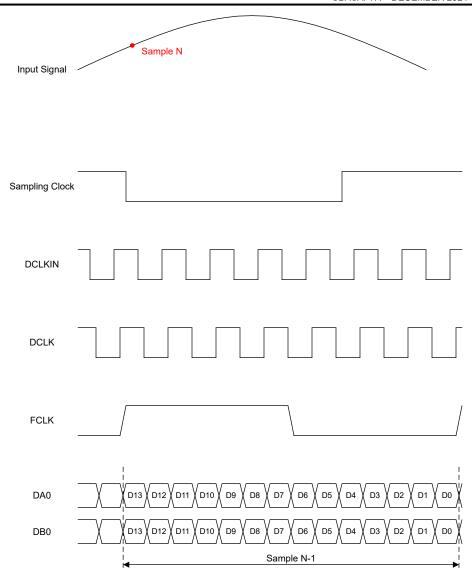

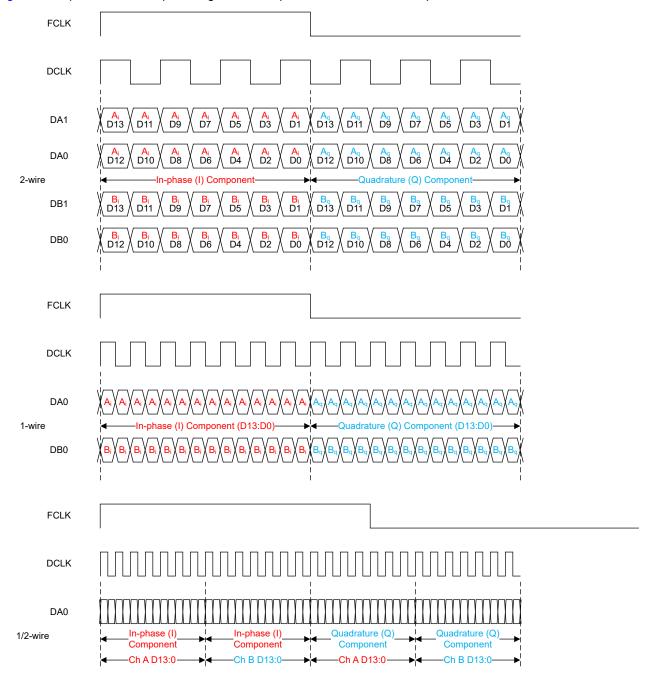

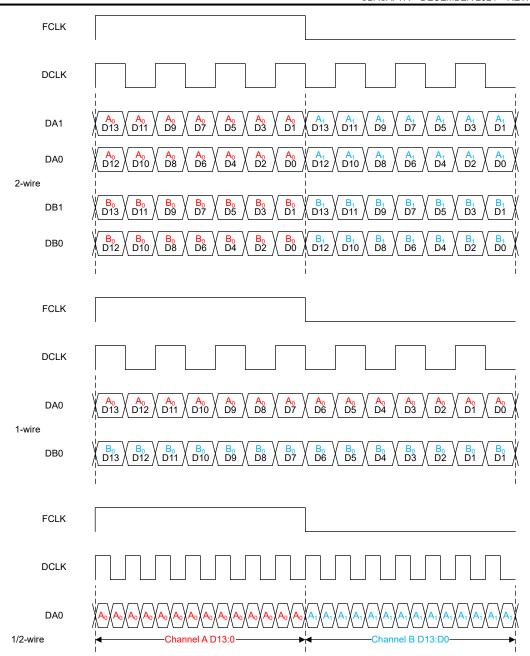

Figure 6-1. Timing diagram: 2-wire

Figure 6-2. Timing diagram: 1-wire

Figure 6-3. Timing diagram: 1/2-wire

# 7 Detailed Description

### 7.1 Overview

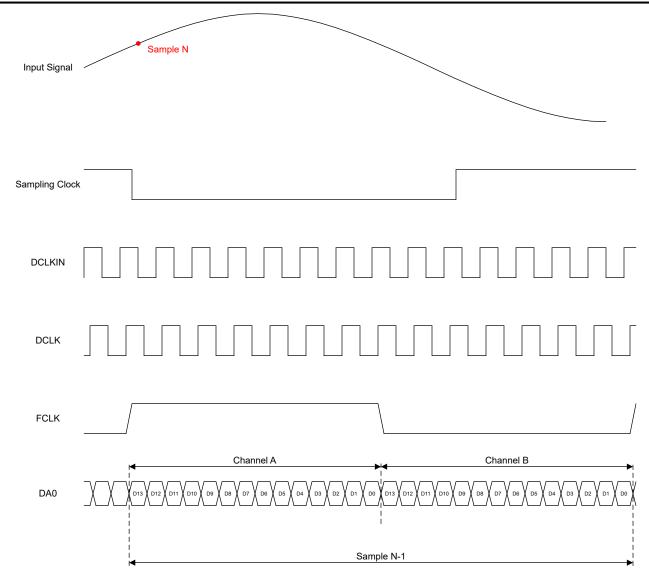

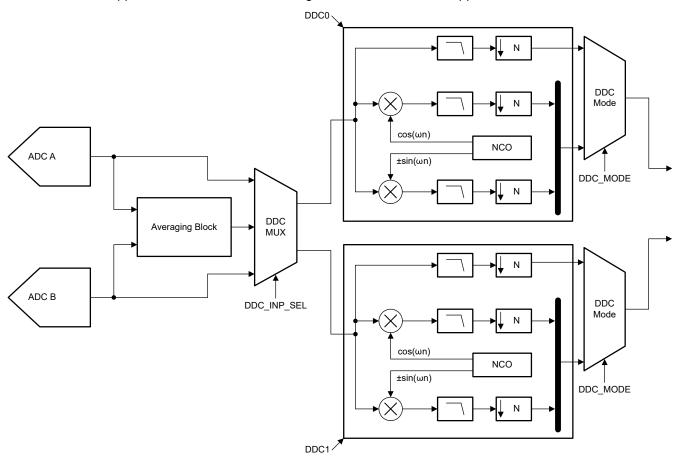

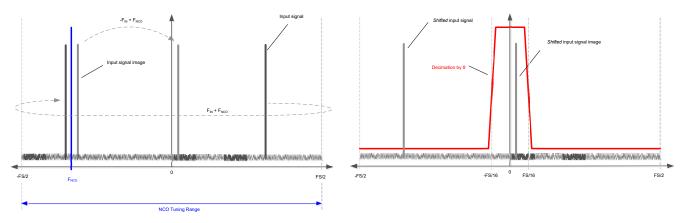

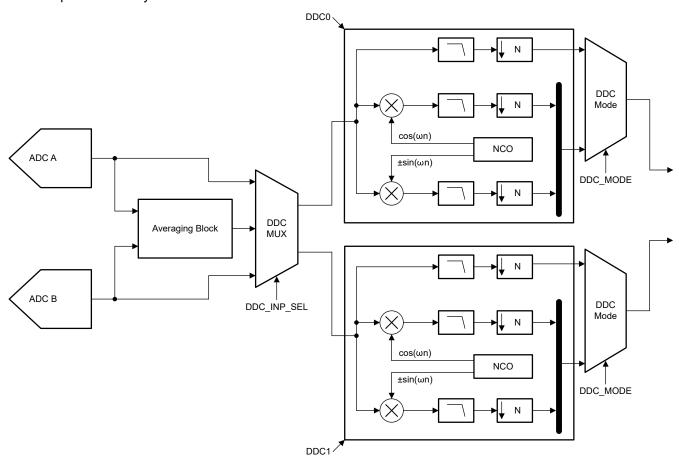

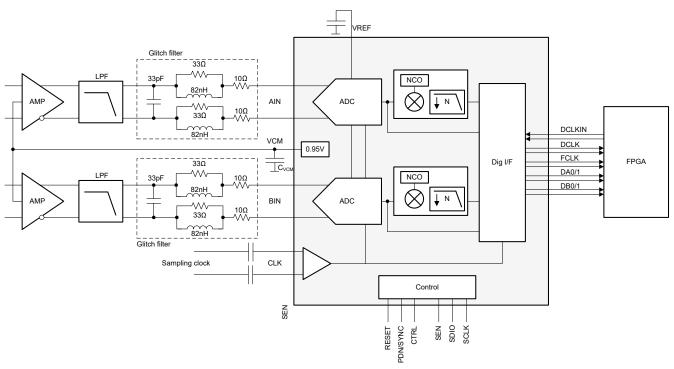

The ADC3664-SP is a low latency, low noise, and ultra low power 14-bit high-speed dual channel ADC with a max sampling rate of 125MSPS intended for use in space applications with mission profiles of total ionizing dose (TID) less than 300krad (Si) and single event latch-up (SEL) of less than 75MeV-cm²/mg. The ADC has an internal reference option and supports the use of an external, high precision, 1.6V reference (see Section 7.3.3). Optionally, integrated programmable digital down converters (DDCs) enable output data rate reduction and channelization (see Section 7.3.5). The DDCs, if operated in a complex decimation mode, offer a 32-bit programmable NCO for complex mixing. The DDCs also support a real decimation mode with no mixing.

The ADC3664-SP uses a serial LVDS (SLVDS) interface to output the data which minimizes the number of digital interconnects (see Section 7.3.4.2). The SLVDS interface can be configured to one of the following modes: two LVDS lanes per channel (2-wire), one LVDS lane per channel (1-wire), or a single lane mode (1/2-wire) where both channels are multiplexed on the same LVDS lane. The device supports configurable output resolutions from 14-bit to 20-bit. Due to the inherent low latency ADC architecture, the digital output result is available after only one or two clock cycles depending on the output interface mode.

The ADC3664-SP is intended to be controlled through the Serial Peripheral Interface (SPI) by configuring registers (Section 7.5); however, the CTRL pin can also be used to configure the voltage reference source and sampling clock input type upon power up.

## 7.2 Functional Block Diagram

Figure 7-1. Simplified Block Diagram

### 7.3 Feature Description

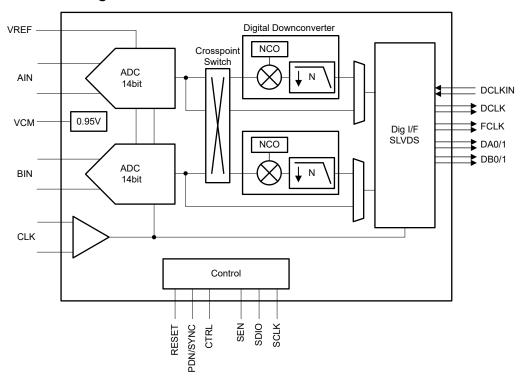

### 7.3.1 Analog Input

The analog inputs of the ADC3664-SP are intended to be driven differentially. Both AC coupling and DC coupling of the analog inputs is supported. The analog inputs are designed for an input common-mode voltage of 0.95V which must be provided externally on each input pin. Figure 7-2 shows the analog input model of the ADCs. First, 8 switches are closed during acquisition for a period of  $t_{ACQ}$ . Then, all switches are open for a period of  $t_{CONV}$ . Finally, before the next acquisition period, the reset switch is closed for a period of  $t_{RST}$ .

Figure 7-2. Analog Input Model

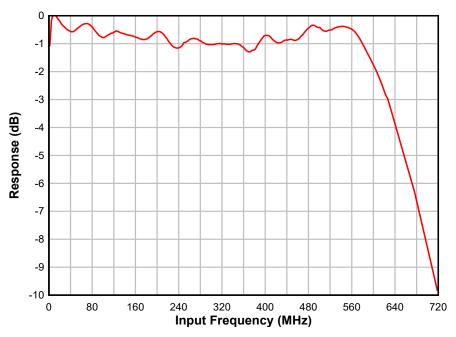

### 7.3.1.1 Analog Input Bandwidth

Figure 7-3 shows the analog full power input bandwidth of the ADC3664-SP with a  $50\Omega$  differential termination. The -3dB bandwidth is approximately 200MHz and the ADC architecture limits the full power bandwidth to 65MHz. To avoid significantly degrading the ADC performance, decreasing input power linearly with increasing input frequency above 65MHz is recommended.

Figure 7-3. ADC Analog Input Bandwidth Response

### 7.3.1.2 Analog Front End Design

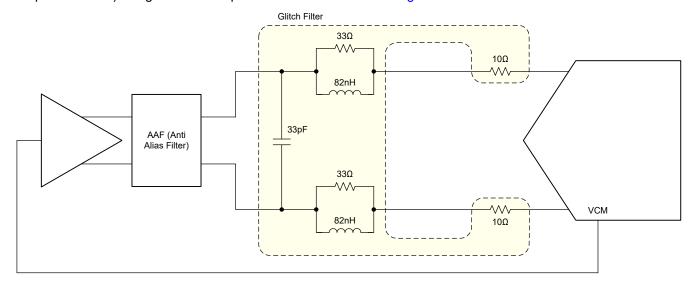

The ADC3664-SP should be used with a passive filter to absorb the glitches on the input due to sampling. Additionally, a passive DC bias circuit is needed in AC-coupled applications which can be combined with a termination network.

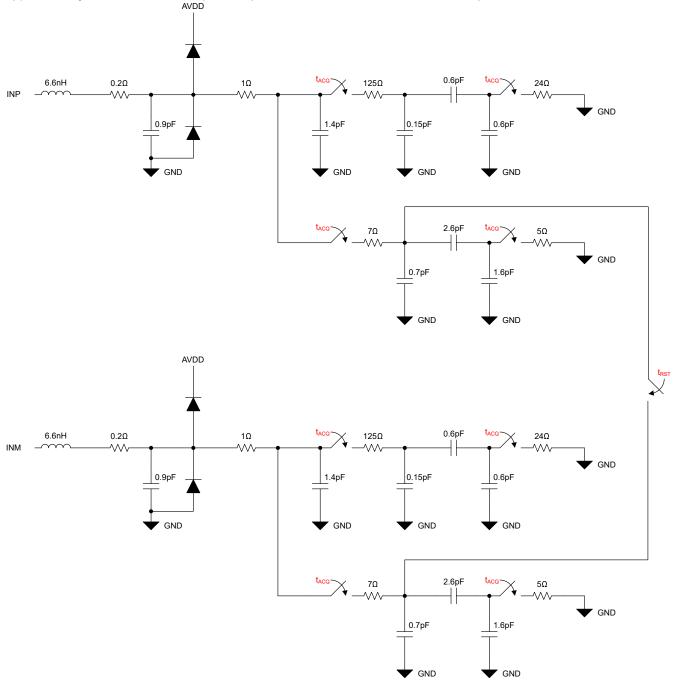

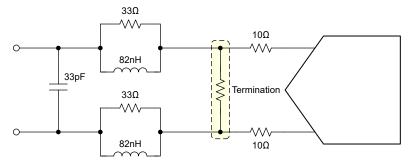

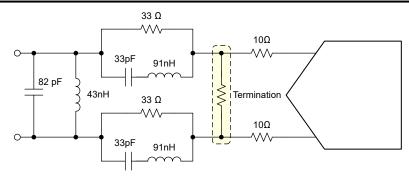

#### 7.3.1.2.1 Sampling Glitch Filter

The front end sampling glitch filter is designed to optimize the SNR and HD3 performance of the ADC. The filter performance is dependent on input frequency: therefore, the following filter designs are recommended for different input frequency ranges as shown in Figure 7-4 and Figure 7-5 (assuming a  $50\Omega$  source impedance).

Figure 7-4. Sampling Glitch Filter for Input Frequencies from 0Hz to 60MHz

Figure 7-5. Sampling Glitch Filter for Input Frequencies from 60MHz to 120MHz

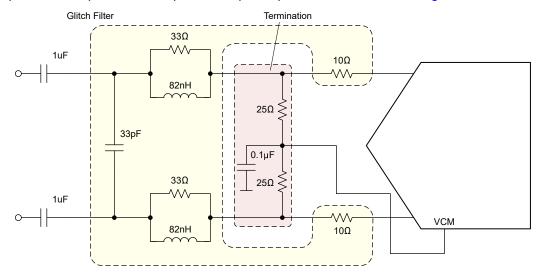

### 7.3.1.2.2 AC Coupling

The ADC3664-SP analog inputs require an external DC bias to the common-mode voltage (VCM) of the ADC when the input is AC coupled. An example AC coupled input network is shown in Figure 7-6.

Figure 7-6. AC Coupled Input Network

### 7.3.1.2.3 DC Coupling

In DC coupled applications, the DC bias needs to be provided from the driver (typically a fully differential amplifier or FDA) using the VCM output of the ADC as shown in Figure 7-7.

Figure 7-7. DC Coupled Input Network

### 7.3.2 Clock Input

To maximize the ADC3664-SP SNR performance, the external sampling clock should be a low jitter differential signal. The device provides the option to operate with a single-ended clock input to reduce the device power consumption and simplify system design at the expense of performance.

#### 7.3.2.1 Differential Vs Single-ended Clock Input

The ADC3664-SP can be operated using a differential or a single-ended clock input where the single-ended clock input consumes less power at the expense of performance.

- Differential clock input mode: the clock input must be AC coupled externally. The ADC3664-SP has an

internal DC bias.

- Single-ended clock input mode: this mode is configured either using SPI (D3 and D0 of 0x0E), or with the CTRL pin. In this mode, there is no internal clock biasing. The clock input needs to be DC coupled with a common-mode voltage of 0.9V. The unused clock input should be AC coupled to ground.

### 7.3.2.2 Signal Acquisition Time Adjust

The ADC3664-SP includes a register (D2 of 0x11) to power down an internal DLL which increases the signal acquisition time for sample rates below 30MSPS from 25% to 50% of the clock period. When powering down the DLL, the acquisition time tracks the clock duty cycle.

Table 7-1. Acquisition Time Vs DLL\_PDN Setting

| SAMPLING CLOCK F <sub>S</sub> (MSPS) | DLL_PDN (D2 of 0x11) | ACQUISITION TIME (t <sub>ACQ</sub> ) |  |  |

|--------------------------------------|----------------------|--------------------------------------|--|--|

| > 30                                 | 0                    | T <sub>S</sub> / 4                   |  |  |

| ≤ 30                                 | 1                    | T <sub>S</sub> / 2                   |  |  |

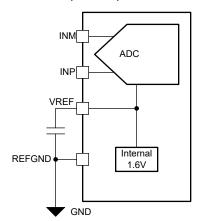

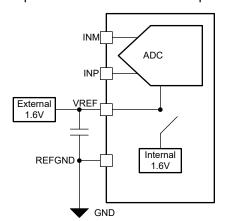

### 7.3.3 Voltage Reference

The ADC3664-SP provides two different options for supplying the voltage reference to the ADCs. The first option is an internal 1.6V reference. The second option is an external 1.6V reference that can be directly connected to the VREF input for best performance. The reference noise can be filtered by connecting a 10µF and a 0.1µF ceramic bypass capacitor to the VREF pin irrespective of the reference source (internal or external).

#### Note

The voltage reference mode can be selected via SPI or by using the CTRL pin (Section 7.5.1). If the CTRL pin is not used for configuration, the CTRL pin should be connected to AVDD and the voltage reference may be selected via SPI.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

### 7.3.3.1 Internal Voltage Reference

The ADC3664-SP has a 1.6V reference that may be used in the absence of an external reference. A  $10\mu F$  decoupling capacitor and a  $0.1\mu F$  decoupling capacitor should be connected between VREF and REFGND. The capacitors should be placed as close to the device pins as possible.

Figure 7-8. Internal Reference Mode

## 7.3.3.2 External Voltage Reference

For the highest accuracy and best drift performance, the ADC3664-SP reference voltage can be sourced externally. When using an external reference, the VREF pin can be directly connected to an external 1.6V reference. A  $10\mu\text{F}$  decoupling capacitor and a  $0.1\mu\text{F}$  decoupling capacitor should be connected between VREF and REFGND. The capacitors should be placed as close to the device pins as possible.

Figure 7-9. External Reference Mode

### 7.3.4 Digital Data Path & Interface

The ADC3664-SP uses a serial LVDS (SLVDS) interface to output the ADCs' data which minimizes the number of digital interconnects. The SLVDS interface can be configured to one of the following modes: two LVDS lanes per channel (2-wire), one LVDS lane per channel (1-wire), or a half-lane mode (1/2-wire) option where both channels are multiplexed on a single LVDS lane. The device supports configurable output resolutions from 14-bit to 20-bit.

The ADC3664-SP requires an external interface clock (DCLKIN). A delayed version of DCLKIN is used as the interface output clock (DCLK).

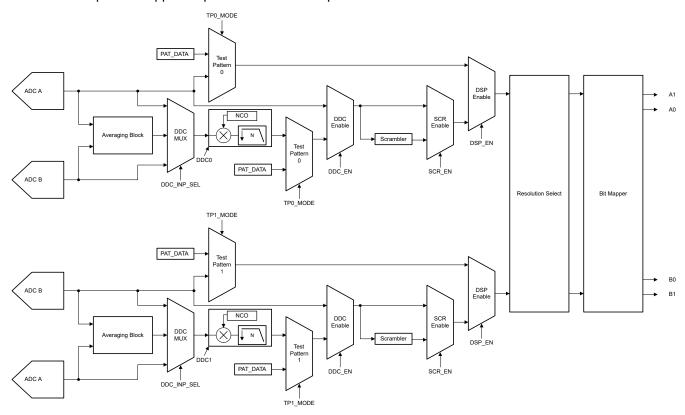

#### 7.3.4.1 Data Path Overview

The ADC3664-SP offers a flexible set of digital signal processing (DSP) features (Figure 7-10) where all or a subset of the features can be used. The ADC cores provide an 14-bit output which can be passed to the digital down converters (DDCs) or directly provided to the digital interface. Since the ADC core offers very low latency, the DSP features have to be disabled (D2 of 0x24) for the lowest latency.

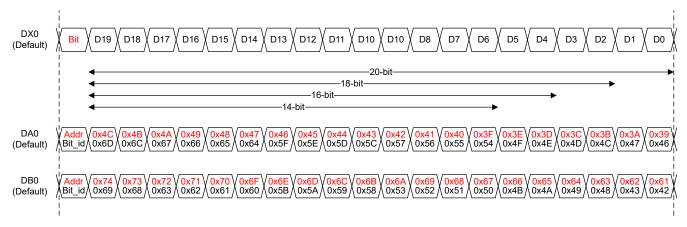

Before data is sent on the data lanes, the data first passes through a resolution selection block and then an output bit mapper. The resolution selector offers selection of output resolutions: 14-bit, 16-bit, 18-bit, or 20-bit. For 16-bit, 18-bit, and 20-bit output resolutions, if the DDCs are not used, then zeros are simply appended as LSBs. The output bit mapper maps each data bit to a position within the data stream for each active lane.

Figure 7-10. Digital Data Path Overview

#### 7.3.4.2 Digital Interface

Table 7-2 provides an overview for the resulting serialization factor depending on output resolution and interface mode. The output serialization factor is internally adjusted based on the interface mode setting and resolution; however, the maximum SLVDS interface output data rate of 1Gbps can not be exceeded regardless of the interface settings. Note, the DCLKIN frequency needs to be adjusted accordingly as well. For example, changing the output resolution from 14-bit to 16-bit in 2-wire mode results in DCLKIN equaling  $F_S$  \* 4 instead of  $F_S$  \* 3.5.

The programming sequence for changing the output interface and/or resolution is shown in Section 7.5.3.

#### Note

When possible, interface modes that allow for an integer ratio between the DCLKIN frequency and the sample clock (CLK) frequency are recommended. This eases meeting the DCLKIN to CLK timing requirements described in Section 7.3.4.3.

#### Note

Since the ADC3664-SP SNR is very high, the LVDS outputs can potentially couple and degrade the SNR. Therefore, a half swing LVDS mode is provided to reduce the LVDS output swing and minimize coupling. When possible, enable half swing (D6 of 0x1A) to minimize degrading the ADC SNR.

Table 7-2. Digital Interface Modes

| Output Resolution Interface |          | Serialization<br>Factor | FCLK              | DCLKIN               | DCLK                 | Data Rate           |

|-----------------------------|----------|-------------------------|-------------------|----------------------|----------------------|---------------------|

|                             | 2-Wire   | 7x                      | F <sub>S</sub> /2 | F <sub>S</sub> * 3.5 | F <sub>S</sub> * 3.5 | F <sub>S</sub> * 7  |

| 14-bit                      | 1-Wire   | 14x                     | F <sub>S</sub>    | F <sub>S</sub> * 7   | F <sub>S</sub> * 7   | F <sub>S</sub> * 14 |

|                             | 1/2-Wire | 28x                     | F <sub>S</sub>    | F <sub>S</sub> * 14  | F <sub>S</sub> * 14  | F <sub>S</sub> * 28 |

|                             | 2-Wire   | 8x                      | F <sub>S</sub> /2 | F <sub>S</sub> * 4   | F <sub>S</sub> * 4   | F <sub>S</sub> * 8  |

| 16-bit                      | 1-Wire   | 16x                     | F <sub>S</sub>    | F <sub>S</sub> * 8   | F <sub>S</sub> * 8   | F <sub>S</sub> * 16 |

|                             | 1/2-Wire | 32x                     | F <sub>S</sub>    | F <sub>S</sub> * 16  | F <sub>S</sub> * 16  | F <sub>S</sub> * 32 |

|                             | 2-Wire   | 9x                      | F <sub>S</sub> /2 | F <sub>S</sub> * 4.5 | F <sub>S</sub> * 4.5 | F <sub>S</sub> * 9  |

| 18-bit                      | 1-Wire   | 18x                     | F <sub>S</sub>    | F <sub>S</sub> * 9   | F <sub>S</sub> * 9   | F <sub>S</sub> * 18 |

|                             | 1/2-Wire | 36x                     | F <sub>S</sub>    | F <sub>S</sub> * 18  | F <sub>S</sub> * 18  | F <sub>S</sub> * 36 |

|                             | 2-Wire   | 10x                     | F <sub>S</sub> /2 | F <sub>S</sub> * 5   | F <sub>S</sub> * 5   | F <sub>S</sub> * 10 |

| 20-bit                      | 1-Wire   | 20x                     | F <sub>S</sub>    | F <sub>S</sub> * 10  | F <sub>S</sub> * 10  | F <sub>S</sub> * 20 |

|                             | 1/2-Wire | 40x                     | F <sub>S</sub>    | F <sub>S</sub> * 20  | F <sub>S</sub> * 20  | F <sub>S</sub> * 40 |

### 7.3.4.3 DCLKIN

DCLKIN is an external clock to the ADC3664-SP where a delayed version of this clock is used as the output interface clock (DCLK). DCLKIN can be configured for external or internal biasing to a 1.2V common-mode voltage via SPI (D5 of 0x244). DCLKIN also has an internal  $100\Omega$  termination resistor.

### Note

DCLKIN can be a maximum of 500MHz which limits the LVDS lanes to a maximum of 1Gbps per lane as data is sent on both rising edge and falling edge of DCLK.

Given the low latency architecture of the ADC3664-SP, the relationship between the sample clock (CLK) and DCLKIN needs to be controlled. DCLKIN and CLK must be phase locked to the same reference frequency. The falling edges of CLK and DCLKIN need to be 2.5ns apart otherwise a timing violation occurs. If a timing violation is observed, an internal timing violation detection circuit adds a 1ns delay between CLK and DCLKIN. The effect of this detection circuit is observed as a change in the t<sub>PD</sub> specification by one DCLK cycle.

#### 7.3.4.4 Output Scrambler

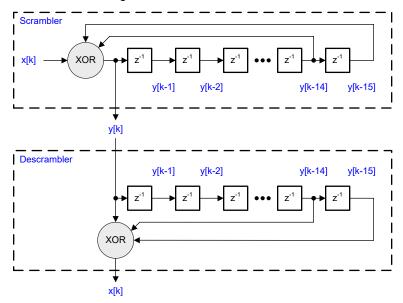

The ADC3664-SP includes an optional output scrambler feature in 2-wire mode only. The scrambler can enabled by enabling the DSP features (D2 of 0x24) and enabling scrambling (D6 of 0x22). When enabled, each sample is split into two halves. Each half of the samples stream is scrambled independently. For example, if the samples stream is at an 18-bit resolution, the stream is divided into two halves consisting of bits D17-D9 & D8-D0. The two halves are fed into independent scrambling blocks where each input bit (x[k]) of each scrambler is XOR-ed with 2 previous bits (y[k-14]) and y[k-15] as shown in Figure 7-11. Since this is a self-synchronizing scrambler, the start up state of the scrambler can be ignored.

Figure 7-11. Scrambler and Descrambler Operation

### Note

The sample streams fed into each scrambler are fed to the scrambler LSB first. Therefore, in the previous example, the sample stream half consisting of D8-D0 is provided to the scrambler with D0 first as x[k] followed by D1 as x[k+1] and so on.

For proper descrambling, the sample stream halves must be descrambled independently then the descrambled data can be used to reconstruct the samples. On the receiver side, the incoming serial data stream can be descrambled by XOR-ing each incoming bit (y[k]) with 2 previous bits (y[k-14]) and y[k-15].

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

#### Note

Since the scramblers are looking at the two halves of the sample stream, the output bit mapper needs to be configured such that each lane contains only one of the sample halves.

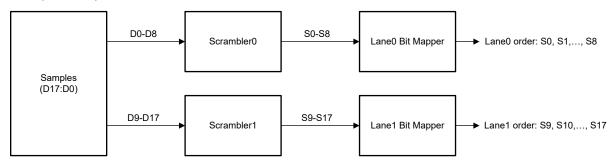

For example, in 2-wire and 18-bit mode, one lane carries the odd bits (D17, D15, D13, etc.) and one lane carries the even bits (D16, D14, D12, etc.). When scrambling is enabled, the bit mapper needs to be configured so that one lane carries bits D9-D17 and the other lane carries D0-D8 (LSB first for each lane). An example data flow diagram of scrambling an 18-bit sample stream is shown in Figure 7-12, where D17:D0 is the sample provided by the ADC after the resolution select block, the sample is split into D0-D8 and D9-D17 and fed into each scrambler (LSB first) and S0-S17 are the resultant scrambled bits.

Figure 7-12. 18-bit Scrambling Example

#### 7.3.4.5 Output Bit Mapper

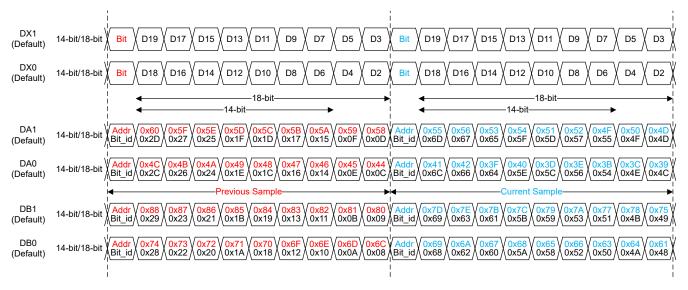

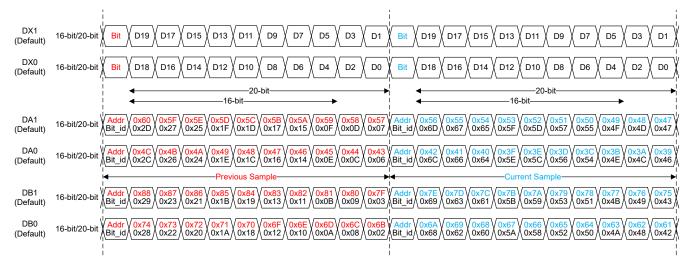

The output bit mapper sits right before the physical output interface and dictates the transmitted bit order on each active lane. Each sample bit is uniquely identifiable by a value as shown in Table 7-3. Similarly, each bit position in each lane is also uniquely identifiable with each bit position having an independent register address. To map a specific bit to a specific bit position (and a specific lane), the value for the bit from the Table 7-3 needs to be written to the address corresponding to the desired bit position in the desired lane.

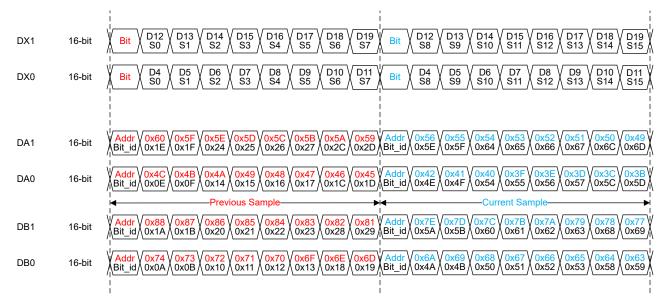

The ADC3664-SP supports a maximum output resolution of 20-bit; therefore, there are 20-bits that are uniquely identifiable per channel. In 2-wire mode, two samples are considered part of the same frame; therefore, there are two sets of 20-bits each, one for the previous sample and another for the current sample. Section 7.3.4.5.1, Section 7.3.4.5.2, and Section 7.3.4.5.3 provide the register addresses that correspond to each bit position in each lane for 2-wire, 1-wire, and 1/2-wire, respectively.

Table 7-3. Unique Bit Identifiers

| BIT_ID    | Channe                    | el A           |                           | Channel B      |  |  |  |

|-----------|---------------------------|----------------|---------------------------|----------------|--|--|--|

|           | Previous sample (2w only) | Current sample | Previous sample (2w only) | Current sample |  |  |  |

| D19 (MSB) | 0x2D                      | 0x6D           | 0x29                      | 0x69           |  |  |  |

| D18       | 0x2C                      | 0x6C           | 0x28                      | 0x68           |  |  |  |

| D17       | 0x27                      | 0x67           | 0x23                      | 0x63           |  |  |  |

| D16       | 0x26                      | 0x66           | 0x22                      | 0x62           |  |  |  |

| D15       | 0x25                      | 0x65           | 0x21                      | 0x61           |  |  |  |

| D14       | 0x24                      | 0x64           | 0x20                      | 0x60           |  |  |  |

| D13       | 0x1F                      | 0x5F           | 0x1B                      | 0x5B           |  |  |  |

| D12       | 0x1E                      | 0x5E           | 0x1A                      | 0x5A           |  |  |  |

| D11       | 0x1D                      | 0x5D           | 0x19                      | 0x59           |  |  |  |

| D10       | 0x1C                      | 0x5C           | 0x18                      | 0x58           |  |  |  |

| D9        | 0x17                      | 0x57           | 0x13                      | 0x53           |  |  |  |

| D8        | 0x16                      | 0x56           | 0x12                      | 0x52           |  |  |  |

| D7        | 0x15                      | 0x55           | 0x11                      | 0x51           |  |  |  |

| D6        | 0x14                      | 0x54           | 0x10                      | 0x50           |  |  |  |

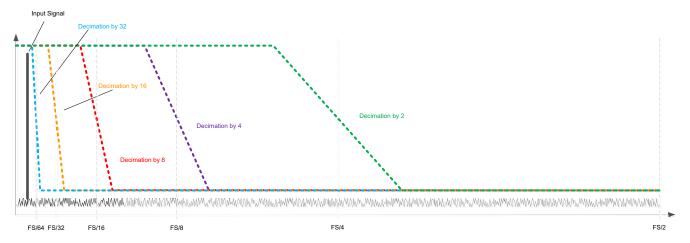

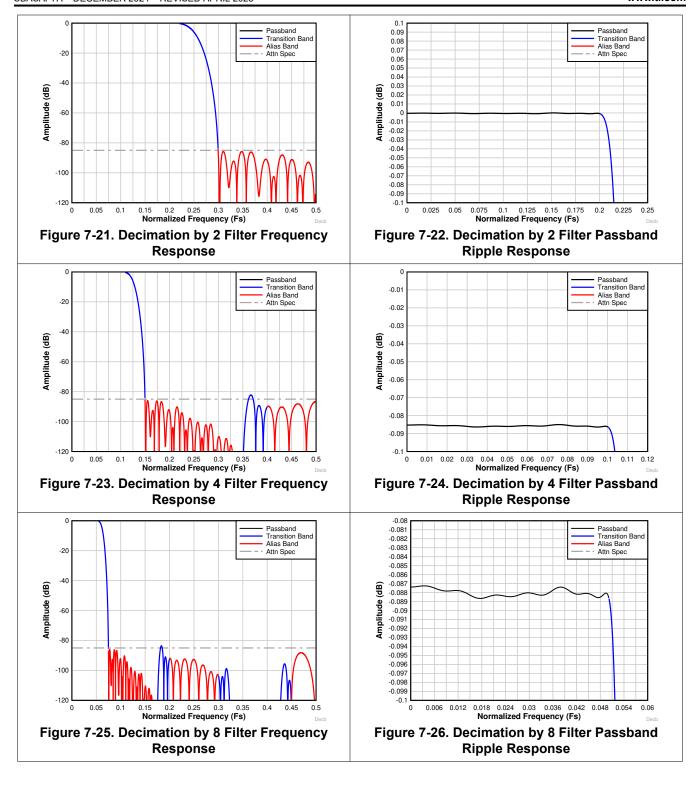

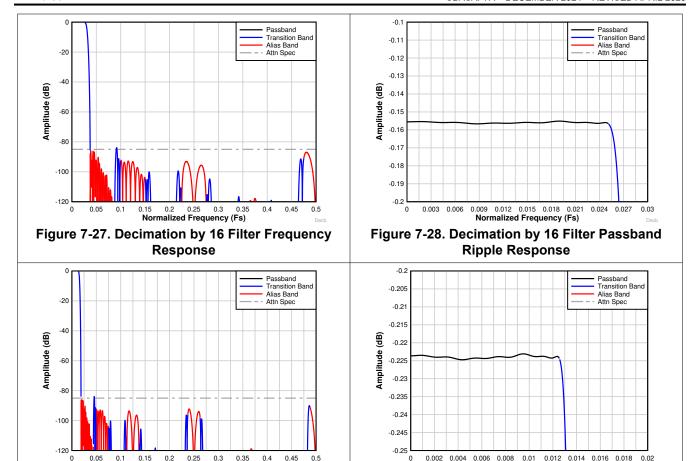

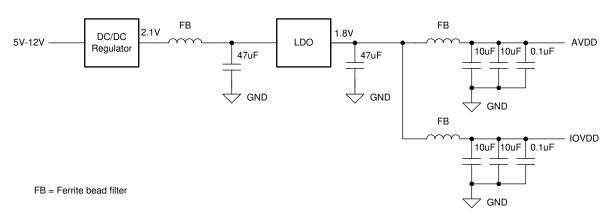

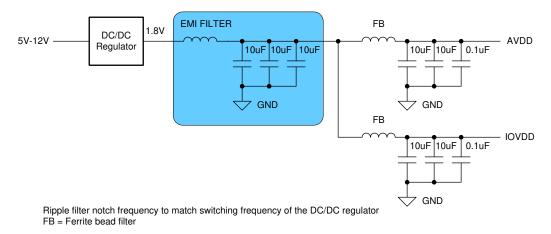

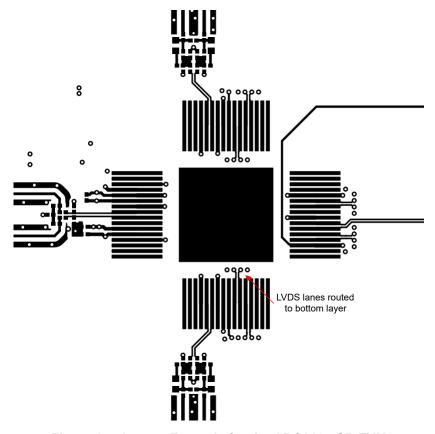

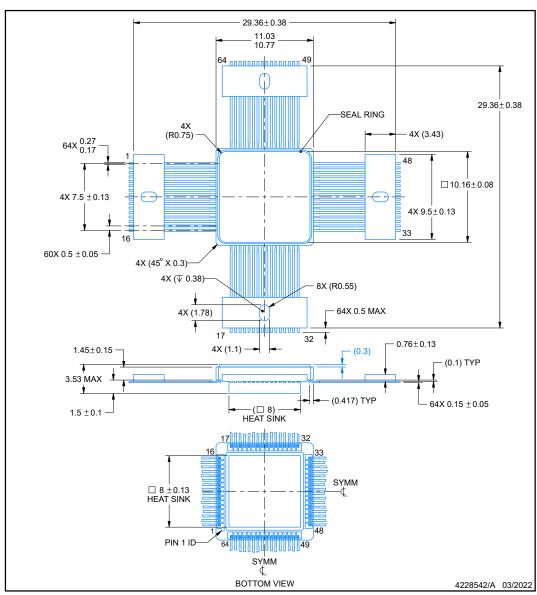

| D5        | 0x0F                      | 0x4F           | 0x0B                      | 0x4B           |  |  |  |