# 4Kb EEPROM with Single-Wire HDQ Interface and Temperature Sensor

Check for Samples: bq2028

### **FEATURES**

- Serial Non-Volatile Memory (NVM)

- 512 Byte (4Kb) EEPROM

- Provides Battery Pack NVM storage for bq27505-E1 Fuel Gauge:

- Manufacturing Data

- Operational History

- Resistance Tables

- State of Health Information

- Single Wire HDQ Communications Port

- Integrated 2.5V LDO Linear Regulator

- Ultra-low power "shutdown" mode (1µA Typical) via auto-timeout and/or host command

- Wake up from shutdown via HDQ break

- Internal Die-Temperature Sensor

- ±5°C Range = -40°C to 85°C

- Raw AD to Temperature Conversion

Performed by Host Firmware

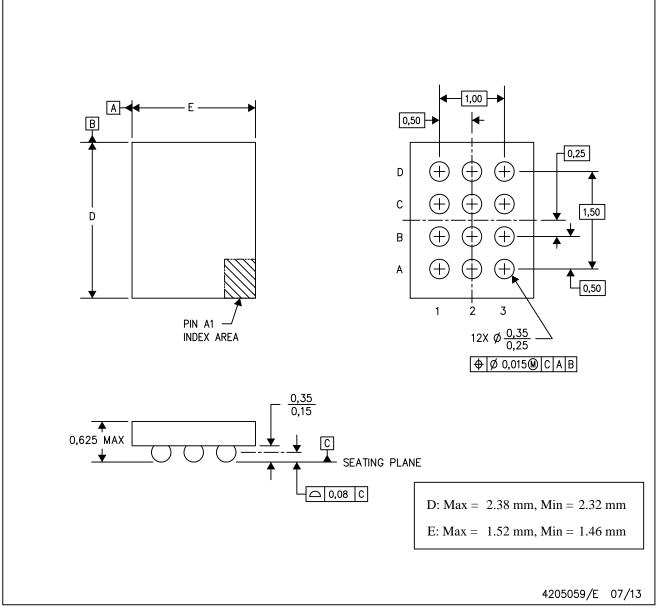

- Package

- 12-pin, 1490 x 2350 μm WCSP (YZG),

0.625mm Max Thickness, 0.5mm Pitch

#### DESCRIPTION

The Texas Instruments bq2028 serial 4Kb nonvolatile memory (EEPROM) with integrated temperature sensor and LDO linear regulator provides pack-side memory storage and temperature monitoring for a single-cell system-side battery fuel gauge solution such as the bq27505-E1.

The bq2028 communicates with the bq27505-E1 gauge over a single-wire HDQ interface with a minimal overhead protocol yet ensures error free data transfer.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DEVICE INFORMATION**

## **AVAILABLE OPTIONS**

| PRODUCTION PART # | PACKAGE     | T <sub>A</sub> | TAPE and REEL QUANTITY |  |  |

|-------------------|-------------|----------------|------------------------|--|--|

| bq2028YZGR        | 12-pin WCSP | –40°C to 85°C  | 3000                   |  |  |

| bq2028YZGT        | 12-pin WCSP | -40°C 10 85°C  | 250                    |  |  |

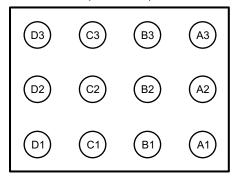

## **PIN ASSIGNMENT**

CSP-12 (bottom view)

Figure 1. bq2028 Pin Assignment (Bottom View)

## **PIN DESCRIPTIONS**

| PIN NAME | CSP-12 PIN            | I/O | DESCRIPTION                                                                   |

|----------|-----------------------|-----|-------------------------------------------------------------------------------|

| TEST3    | C3                    | I/O | Reserved for factory test. Connect to VSS in application circuit.             |

| REGIN    | D3                    | Р   | Regulator input. Typically connected to battery CELL+.                        |

| VDD      | D2                    | Р   | Regulator 2.5V output. Decouple with a 0.47µF cap to VSS.                     |

| vss      | A1, B1, D1, B2,<br>C2 | Р   | Ground pin.                                                                   |

| HDQ      | A2                    | I/O | HDQ Data pin. Open-drain I/O. Requires external pull-up for proper operation. |

| TEST1    | C1                    | I/O | Reserved for factory test. Connect to VSS in application circuit.             |

| TEST0    | B3                    | I/O | Reserved for factory test. Connect to VSS in application circuit.             |

| TEST2    | A3                    | I/O | Reserved for factory test. Connect to VSS in application circuit.             |

Product Folder Links :bq2028

### **ELECTRICAL SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                    |                                                 | ٧    | ALUE              | UNIT |

|--------------------|-------------------------------------------------|------|-------------------|------|

|                    |                                                 | MIN  | MAX               |      |

| V <sub>REGIN</sub> | Supply voltage range                            | -0.3 | 5.5               | V    |

| HDQ                | Open-drain I/O pin                              | -0.3 | 5.5               | V    |

| $V_{I}$            | Input voltage range to all other pins (TEST0-3) | -0.3 | $V_{REG25} + 0.3$ | V    |

| ESD                | HBM for pins other than TEST1, TEST2, TEST3     |      | 2                 | kV   |

| T <sub>A</sub>     | Operating free-air temperature range            | -40  | 85                | °C   |

| T <sub>F</sub>     | Functional temperature                          | -40  | 100               | °C   |

| T <sub>stg</sub>   | Storage temperature range                       | -65  | 150               | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating condition" is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

$T_A = 25$ °C,  $C_{1,DO25} = 0.47 \mu F$ ,  $V_{REGIN} = 3.6 V$  (unless otherwise noted)

|                    |                                                                 |                                                                            | MIN  | TYP  | MAX | UNIT |

|--------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|------|------|-----|------|

| $V_{REGIN}$        | Supply Voltage                                                  |                                                                            | 2.45 |      | 4.5 | V    |

| R <sub>PUEXT</sub> | HDQ external pull-up                                            | To system-side 2.5V LDO output. Recommend using $10k\Omega$ , 5% resistor. |      | 10   | 22  | kΩ   |

| $C_{HDQ}$          | HDQ capacitive loading                                          | Total external bus capacitance                                             |      | 50   | 250 | pF   |

| C <sub>REGIN</sub> | External input capacitor for internal LDO between REGIN and VSS | Nominal capacitor values specified. Recommend a 5%                         |      | 0.1  |     | μF   |

| C <sub>LDO25</sub> | External output capacitor for internal LDO between VDD and VSS  | ceramic X5R type capacitor located close to the device.                    |      | 0.47 |     | μF   |

Product Folder Links: bq2028

## DC ELECTRICAL CHARACTERISTICS

$T_A = -40$ °C to 85°C,  $C_{LDO25} = 0.47 \mu F$ ,  $V_{REGIN} = 3.6 \text{ V}$  (unless otherwise noted)

|                     | PARAMETER                  | TEST CONDITION                                                             | MIN                  | TYP    | MAX  | UNIT  |

|---------------------|----------------------------|----------------------------------------------------------------------------|----------------------|--------|------|-------|

| SUPPLY C            | URRENT                     |                                                                            |                      |        |      |       |

|                     |                            | SHUTDOWN Mode (LDO = off)                                                  |                      | 1      | 2    |       |

|                     |                            | SLEEP Mode (LFO = on; HFO = off)                                           |                      | 20     | 50   |       |

|                     | O                          | IDLE Mode (LFO, HFO = on; CONV= 0)                                         |                      | 55     | 110  | 4     |

| I <sub>CC</sub>     | Supply Current (1)         | TEMP Read (LFO, HFO = on; CONV = 1)                                        |                      | 110    | 200  | μA    |

|                     |                            | EEPROM Read (LFO, HFO = on)                                                |                      | 300    | 600  |       |

|                     |                            | EEPROM Write (LFO, HFO = on)                                               |                      | 2300   | 5000 |       |

| 2.5V LDO F          | REGULATOR                  |                                                                            |                      |        |      |       |

|                     | <b>D</b> 1                 | 2.7 V ≤ V <sub>REGIN</sub> ≤ 4.5 V, I <sub>OUT</sub> ≤ 10 mA               | 2.4                  | 2.5    | 2.6  | .,    |

| $V_{REG25}$         | Regulator output voltage   | 2.45 V ≤ V <sub>REGIN</sub> < 2.7 V (low battery), I <sub>OUT</sub> ≤ 3 mA | 2.4                  |        |      | V     |

| OTHER AN            | IALOG: POWER ON RESET, TEN | IPERATURE SENSOR, INTERNAL VOLTAGE REFERENCE                               | 1                    |        | '    |       |

| V <sub>POR+</sub>   | POR Threshold              | Positive-going input at VDD, T <sub>A</sub> = 25°C                         |                      | 2.20   | 2.31 | V     |

| V <sub>HYSPOR</sub> | POR Hysteresis             | TA=25°C                                                                    | 45                   | 115    | 185  | mV    |

| $V_{WU+}$           | HDQ Wakeup threshold       | Positive-going input at HDQ, T <sub>A</sub> = 25°C                         | 1.2                  | 1.4    |      | V     |

| V <sub>HYSWU</sub>  | HDQ Wakeup hysteresis      | T <sub>A</sub> = 25°C                                                      |                      | 505    |      | mV    |

| V <sub>ASD</sub>    | Auto shutdown threshold    |                                                                            | 2.05                 | 2.20   | 2.31 | V     |

| V <sub>HYSASD</sub> | Auto shutdown hysteresis   |                                                                            | 45                   | 115    | 185  | V     |

| V <sub>(TEMP)</sub> | Temperature sensor         |                                                                            |                      | -1.986 |      | mV/°C |

| HDQ INTER           | RFACE                      |                                                                            |                      |        |      |       |

| V <sub>IH</sub>     | Input voltage high         |                                                                            | 1.8                  |        |      | V     |

| V <sub>IL</sub>     | Input voltage low          |                                                                            |                      |        | 0.6  | V     |

| V <sub>OH</sub>     | Output voltage high        | Open drain, external pull up to VDD                                        | V <sub>DD</sub> -0.5 |        |      | V     |

| V <sub>OL</sub>     | Output voltage low         | Open-drain IOL = 1mA                                                       |                      |        | 0.4  | V     |

| Cı                  | Input capacitance          |                                                                            |                      | 10     |      | pF    |

| I <sub>itot</sub>   | HDQ input total current    | Includes leakage plus internal pull-down                                   |                      |        | 2    | μΑ    |

| I <sub>OL</sub>     | Output low sink current    | VOL = 0.4V                                                                 |                      |        | 1    | mA    |

| R <sub>PDINT</sub>  | HDQ internal pull-down     | For auto-shutdown                                                          | 1.25                 | 2.5    | 5    | ΜΩ    |

<sup>(1)</sup> An EEPROM write operation is required for proper device initialization following exit from SHUTDOWN, SLEEP, or POWER-ON RESET.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

# **AC ELECTRICAL CHARACTERISTICS**

$T_A = -40$ °C to 85°C,  $C_{LDO25} = 0.47 \mu F$ ,  $V_{REGIN} = 3.6 V$  (unless otherwise noted)

|                       | PARAMETER                | TEST CONDITION                                                                                                         | MIN   | TYP    | MAX  | UNIT     |

|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------|-------|--------|------|----------|

| EEPROM                |                          |                                                                                                                        |       |        |      |          |

|                       | Array Size               | 128 words x 32 bits = 4Kbits                                                                                           |       | 512    |      | Bytes    |

|                       | Write Cycle Endurance    |                                                                                                                        | 1000  |        |      | K cycles |

|                       | HDQ Data Access          | Via 32 bit BUFFER                                                                                                      |       | 8      |      | Bits     |

|                       | Program time             | Per word (internal timing only)                                                                                        |       | 6      | 20   | mS       |

|                       | Read time                | Per word (internal timing only)                                                                                        |       | 300    | 2000 | nS       |

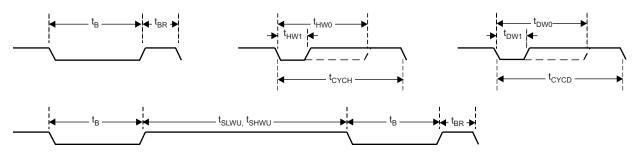

| HDQ INTER             | FACE AND MISCELLANEOUS ( | (Refer to Figure 6 and Figure 7)                                                                                       |       |        |      |          |

| t <sub>B</sub>        | Break time               |                                                                                                                        | 190   |        |      | μs       |

| t <sub>BR</sub>       | Break recovery time      |                                                                                                                        | 40    |        |      | μs       |

| t <sub>SLWU</sub>     | SLEEP wakeup             | Host drives HDQ Break. Timed from rising edge of first wakeup                                                          | 200   |        |      | μs       |

| t <sub>SHWU</sub>     | SHUTDOWN wakeup          | break pulse to falling edge of next break pulse with first data.                                                       | 20    |        |      | ms       |

| t <sub>SHUTDN</sub>   | SHUTDOWN time            | Time delay after $V_{\mbox{\scriptsize ASD}}$ threshold is met before SHUTDOWN mode is entered.                        |       | 2      | 10   | S        |

| t <sub>ASHWU</sub>    | AUTOSHUTDOWN wakeup      | Time delay after $V_{\rm ASD}$ threshold is met or 2 second timeout is met before Host can drive HDQ break for wakeup. |       | 2      | 10   | S        |

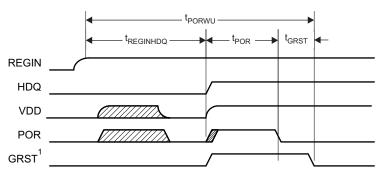

| t <sub>PORWU</sub>    | POR wakeup               | Power on reset wakeup time before device is ready to receive first HDQ message                                         | 35    |        |      | ms       |

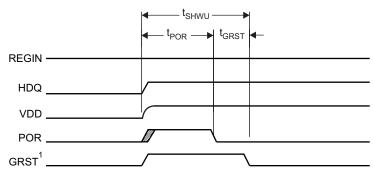

| t <sub>REGINHDQ</sub> | REGIN to HDQ             | REGIN valid to 1st rising edge of HDQ to POR device. (Figure 3)                                                        | 15    |        |      | ms       |

| t <sub>POR</sub>      | POR                      | VDD ramp to POR release.(Figure 3)                                                                                     |       |        | 11   | ms       |

| t <sub>GRST</sub>     | Global reset             | POR release to GRST release. (Figure 3)                                                                                |       | 4      |      | ms       |

| t <sub>HW1</sub>      | Host Write 1 time        | Host drives HDQ                                                                                                        | 5     |        | 50   | μs       |

| t <sub>HW0</sub>      | Host Write 0 time        | Host drives HDQ                                                                                                        | 86    |        | 145  | μs       |

| t <sub>CYCH</sub>     | Host cycle time          | Host drives HDQ                                                                                                        | 190   |        |      | μs       |

| t <sub>DW1</sub>      | Device Write 1 time      | bq2028 drives HDQ                                                                                                      | 39    | 41     | 43   | μs       |

| t <sub>DW0</sub>      | Device Write 0 time      | bq2028 drives HDQ                                                                                                      | 106   | 111    | 116  | μs       |

| t <sub>CYCD</sub>     | Device cycle time        | bq2028 drives HDQ                                                                                                      | 197   | 207    | 217  | μs       |

| t <sub>RSPS</sub>     | Device response time     | bq2028 drives HDQ                                                                                                      | 211   | 222    | 233  | μs       |

| t <sub>HDQSTDET</sub> | HDQ Start detect         | bq2028 filters out very short HDQ pulses                                                                               | 0     |        | 1.98 | μs       |

| A/D CONVE             | RTER                     |                                                                                                                        |       |        |      |          |

| f <sub>(SAMPLE)</sub> | Sampling frequency       | Delta Sigma modulator frequency                                                                                        |       | 65.5   |      | kHz      |

|                       |                          | SPEED[1:0] = 00                                                                                                        |       | 125    |      |          |

|                       | 0                        | SPEED[1:0] = 01                                                                                                        |       | 62.50  |      |          |

| t <sub>(CONV)</sub>   | Conversion time          | SPEED[1:0] = 10                                                                                                        |       | 31.25  |      | ms       |

|                       |                          | SPEED[1:0] = 11                                                                                                        |       | 7.8125 |      |          |

| V <sub>(ADC_IN)</sub> | Input voltage range      | Internal Vref, T <sub>A</sub> = 25°C, VTEMP internal channel only                                                      | -0.2  |        | 1    | V        |

| HIGH FREQU            | UENCY OSCILLATOR (HFO)   |                                                                                                                        |       |        |      | -        |

| HFosc                 | Operating frequency      |                                                                                                                        |       | 8.389  |      | MHz      |

| HF <sub>ERR</sub>     | Frequency error          | $T_A = -40$ °C to 85°C                                                                                                 | -8.0% |        | 8.0% | -        |

| HF <sub>START</sub>   | Start-up time            |                                                                                                                        |       | 14     | 200  | μs       |

| LOW FREQU             | JENCY OSCILLATOR (LFO)   |                                                                                                                        |       |        |      |          |

| LFosc                 | Operating frequency      |                                                                                                                        |       | 32.768 |      | kHz      |

| LF <sub>ERR</sub>     | Frequency error          | $T_A = -40$ °C to 85°C                                                                                                 | -8.0% |        | 8.0% |          |

| LF <sub>START</sub>   | Start-up time            |                                                                                                                        |       | 100    | 500  | μs       |

Copyright © 2012, Texas Instruments Incorporated

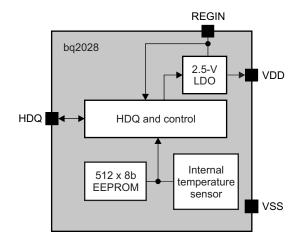

#### **BLOCK DIAGRAM**

Figure 2. bq2028 Block Diagram

### **Power Modes**

The bq2028 has multiple operational modes for reduced power consumption. defines which circuits are enabled in each of these operational modes.

Table 1. Power Mode Table (1)

| CIRCUIT       | SHUT-DOWN | SLEEP        | IDLE | HDQ<br>READ/WRITE | TEMP<br>READ | EEPROM<br>READ | EEPROM<br>WRITE |

|---------------|-----------|--------------|------|-------------------|--------------|----------------|-----------------|

| Wakeup/POR    | √         | $\checkmark$ | √    | <b>√</b>          | $\checkmark$ | $\checkmark$   | √               |

| LDO Regulator | -         | √            | √    | √                 | √            | √              | √               |

| 32kHz LFO     | -         | √            | √    | √                 | √            | √              | √               |

| 8MHz HFO      | _         | _            | √    | <b>√</b>          | $\checkmark$ | $\checkmark$   | √               |

| HDQ Interface | _         | _            | _    | <b>√</b>          | $\checkmark$ | $\checkmark$   | √               |

| ADC           | _         | _            | _    | -                 | $\checkmark$ | -              | _               |

| EEPROM Read   | -         | _            | _    | _                 | -            | √              | _               |

| EEPROM Write  | _         | _            | _    | _                 | _            | -              | V               |

(1) √: Active —: Not in use

(1) Internal digital core reset, held for 4 ms after analog POR deasserted

Figure 3. Power Up Sequence

(1) Internal digital core reset, held for 4 ms after analog POR deasserted

Figure 4. Shutdown Wake Up Sequence

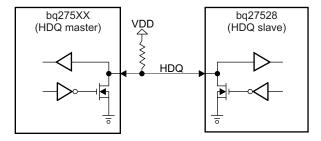

## **HDQ** Interface

The bg2028 supports a single-wire, open-drain communication interface that supports the HDQ protocol as shown in Figure 5. The HDQ protocol is based on the Texas Instruments HDQ standard as discussed in the TI application report (SLUA408A) (http://focus.ti.com.cn/cn/lit/an/slua408a/slua408a.pdf).

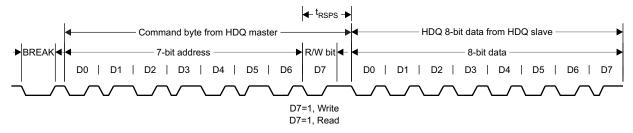

The communication protocol is asynchronous return-to-one referenced to Vss. A passive pullup resistance is required to pull the HDQ line to a high state when neither the host nor the slave is pulling the line low during twoway communication over the single wire interface. The interface uses a command-based protocol, where the host sends a command byte to the HDQ slave device. The command directs the slave to either receive or transmit the next byte of data. The last transmitted bit of the command byte determines the direction of the data (read or write) as shown in Figure 7.

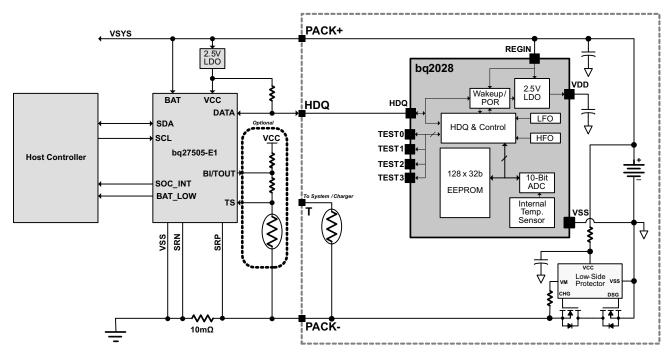

Figure 5. HDQ Interface Connections (single wire configuration)

Product Folder Links: bq2028

Figure 6. HDQ Detailed Timing Waveform

Figure 7. HDQ 8-bit Mode Read Cycle

#### **Device Control**

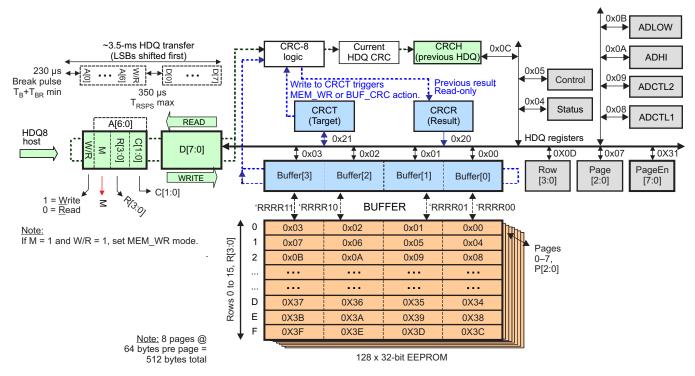

Using a register address access method, the HDQ command byte limits addressing to 7 bits so a mapping scheme is necessary to differentiate device control and status registers from EEPROM data. This register and paged EEPROM access scheme is shown in Figure 8.

Figure 8. Register and EEPROM Access Scheme

Access to device control and data registers use the "Un-Mapped" address space with the "M" (Map bit) set to '0'. Access to the EEPROM space uses a Memory Mapped scheme with the "M" bit set to '1'. Refer to Figure 9 for details.

#### **Memory Mapped Registers**

|   |       |       | !     | R[;   | C[1   | 1:0]  |       |       |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | W/R   | 1     | R3    | R2    | R1    | R0    | C1    | C0    |

| • | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

Bit 7 = W/R: Read/Write command (1 = Write, 0 = Read)

Bit 6 = Map Bit, M = 1

Bits 5:2 = Row index: R[3:0]

Bits 1:0 = Column/Buffer index: C[1:0]

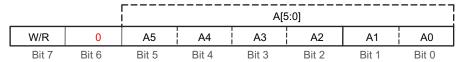

#### **Unmapped Registers**

Bit 7 = W/R: Read/Write command (1 = Write, 0 = Read)

Bits 6:5 = Map Bit, M = 0

Bits 4:0 = HDQ register: A[5:0] Range = 0x00 to 0x3F

Figure 9. HDQ Command Byte Decode

Copyright © 2012, Texas Instruments Incorporated

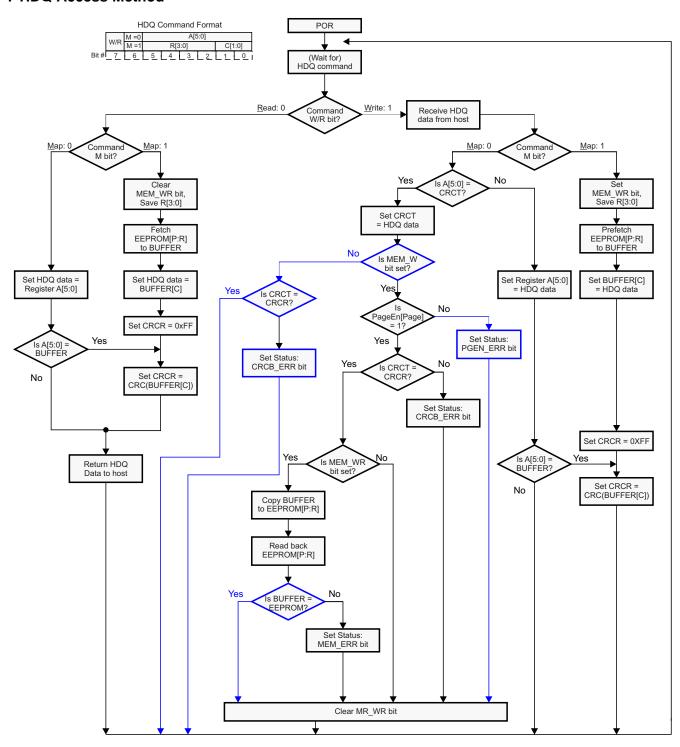

#### 7 HDQ Access Method

Figure 10. HDQ Access Flow Chart

#### **EEPROM Access**

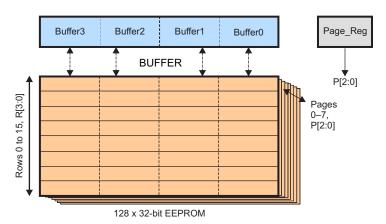

The bq2028 provides 512 bytes of EEPROM non-volatile memory storage organized as 128 words x 32 bits. Due to the address limitations of the HDQ interface protocol, the EEPROM is accessed in 8 pages, with 16 rows of 4 bytes each. For IC manufacturing and analog trim data, 16 bytes or 4 words are reserved in last page of data. The access model terminology is listed below:

EEPROM = 128x32-bit (512 bytes) non-volatile memory with paged access

BUFFER = 32-bit long word in 4x8b volatile Buffer C = 2-bit byte **C**olumn index for Buffer: C[1:0]

Buffer[C] = 8-bit access to BUFFER at index C. MSB is at byte indexed by C='11'.

P = 3-bit **P**age index for EEPROM: P[2:0] (8 pages/EEPROM)

PAGE[P] = 16x32-bit rows (64 bytes) from EEPROM indexed by [P]

R = 4-bit **R**ow index for EEPROM: R[3:0] (16 rows/page)

ROW[P,R] = 32-bit long word from EEPROM indexed by [P,R]

Pre-Fetch = Automatic copy of an ROW[P,R] to BUFFER before read/write operation

M = Mapping operations to access BUFFER and EEPROM: M[1:0]

Figure 11. Memory Map

Copyright © 2012, Texas Instruments Incorporated

## **HDQ Registers**

A summary of the Un-Mapped HDQ Registers is provided by Table 2.

# Table 2. HDQ Un-Mapped Register Summary (1)(2)

| A[5:0] | R/W | Register  | В | A[5:0] | R/W | Register   | В | A[5:0] | R/W | Register   | В | A[5:0] | R/W | Register   |

|--------|-----|-----------|---|--------|-----|------------|---|--------|-----|------------|---|--------|-----|------------|

| 0x00   | R/W | Buffer0   | - | 0x10   | -   | (Reserved) | _ | 0x20   | R   | CRCR       | - | 0x30   | R/W | (Reserved) |

| 0x01   | R/W | Buffer1   | - | 0x11   | -   | (Reserved) | _ | 0x21   | R/W | CRCT       | - | 0x31   | R/W | PageEn     |

| 0x02   | R/W | Buffer2   | - | 0x12   | -   | (Reserved) | _ | 0x22   | -   | (spare)    | - | 0x32   | R/W | (Trim)     |

| 0x03   | R/W | Buffer3   | - | 0x13   | -   | (Reserved) | _ | 0x23   | -   | (spare)    | - | 0x33   | R/W | (Trim)     |

| 0x04   | R   | Status    | - | 0x14   | -   | (Reserved) | _ | 0x24   | -   | (Reserved) | - | 0x34   | R/W | (Trim)     |

| 0x05   | R/W | Control   | - | 0x15   | -   | (Reserved) | _ | 0x25   | -   | (Reserved) | - | 0x35   | R/W | (Trim)     |

| 0x06   | -   | (spare)   | - | 0x16   | -   | (Reserved) | _ | 0x26   | -   | (Reserved) | - | 0x36   | R/W | (Trim)     |

| 0x07   | R/W | Page      | - | 0x17   | -   | (Reserved) | _ | 0x27   | -   | (Reserved) | - | 0x37   | _   | (Reserved) |

| 0x08   | R/W | ADCTL1    | - | 0x18   | -   | (spare)    | _ | 0x28   | -   | (Reserved) | - | 0x38   | _   | (Reserved) |

| 0x09   | R/W | ADCTL2    | - | 0x19   | -   | (spare)    | _ | 0x29   | -   | (spare)    | - | 0x39   | _   | (Reserved) |

| 0x0A   | R   | ADHI      | _ | 0x1A   | -   | (spare)    | _ | 0x2A   | -   | (spare)    | - | 0x3A   | _   | (Reserved) |

| 0x0B   | R   | ADLOW     | - | 0x1B   | -   | (spare)    | _ | 0x2B   | -   | (spare)    | - | 0x3B   | _   | (Reserved) |

| 0x0C   | R   | CRCH      | _ | 0x1C   | -   | (spare)    | _ | 0x2C   | -   | (Reserved) | - | 0x3C   | _   | (Reserved) |

| 0x0D   | R   | Row       | - | 0x1D   | -   | (spare)    | _ | 0x2D   | -   | (Reserved) | - | 0x3D   | _   | (Reserved) |

| 0x0E   | R   | DeviceRev | - | 0x1E   | -   | (spare)    | - | 0x2E   | -   | (spare)    | - | 0x3E   | _   | (Reserved) |

| 0x0F   | R   | DeviceID  | _ | 0x1F   | _   | (spare)    | - | 0x2F   | -   | (spare)    | - | 0x3F   | -   | (Reserved) |

<sup>(1)</sup> B = Defaults "Backed Up" in EEPROM Page[0] and auto-loaded at Power On Reset

## 32-bit BUFFER Access (addresses 0x00 through 0x03)

Access to the 32-bit words in the EEPROM is provided by a 32-bit BUFFER that is available as 8-bit HDQ registers: Buffer0 [LSB], Buffer1, Buffer2, Buffer[MSB].

| 32-BIT BUFFER |         |         |         |  |  |  |  |  |  |

|---------------|---------|---------|---------|--|--|--|--|--|--|

| MS-Byte       |         |         | LS-Byte |  |  |  |  |  |  |

| Buffer3       | Buffer2 | Buffer1 | Buffer0 |  |  |  |  |  |  |

|        | 7(MSB)                      | 6                           | 5            | 4              | 3                                  | 2        | 1   | 0   |  |  |  |  |

|--------|-----------------------------|-----------------------------|--------------|----------------|------------------------------------|----------|-----|-----|--|--|--|--|

| Name   |                             |                             | Buffer0[7:0] | (address 0x00) | <ul> <li>Least Signific</li> </ul> | ant Byte |     |     |  |  |  |  |

| Name   |                             | Buffer1[7:0] (address 0x01) |              |                |                                    |          |     |     |  |  |  |  |

| Name   | Buffer2[7:0] (address 0x02) |                             |              |                |                                    |          |     |     |  |  |  |  |

| Name   |                             |                             | Buffer3[7:0] | (address 0x03) | - Most Significa                   | ant Byte |     |     |  |  |  |  |

| Access | R/W                         | R/W                         | R/W          | R/W            | R/W                                | R/W      | R/W | R/W |  |  |  |  |

| Reset  | Undefined                   |                             |              |                |                                    |          |     |     |  |  |  |  |

## Status Register (address 0x04):

|        | 7(MSB) | 6        | 5        | 4      | 3    | 2      | 1       | 0        |

|--------|--------|----------|----------|--------|------|--------|---------|----------|

| Name   | BUSY   | ADC_DRDY | PGEN_ERR | MEM_WR | RSVD | RSTBIT | MEM_ERR | CRCB_ERR |

| Access | R      | R        | R        | R      | R    | R      | R       | R        |

| Reset  | 0      | 0        | 0        | 0      | 0    | 0      | 0       | 0        |

**BUSY (bit 7):** Busy flag. This bit is normally '0' and is set to '1' when the device is performing an extended duration function such as device initialization, an ADC measurement or EEPROM write. Upon completion of the function, the BUSY bit will automatically clear to '0'.

**ADC\_DRDY (bit 6):** ADC Data ready flag. This bit indicates that conversion data is ready in the ADC Data Registers (ADHI and ADLOW). This bit is cleared by setting the CONV bit in the Control register.

<sup>(2)</sup> Page[0] EEPROM Addresses 0x38 to 0x3F contain the TI Die ID but these are not mapped to HDQ registers.

- 1 ADC data is ready

- 0 ADC data is not ready.

**PGEN\_ERR** (bit 5): Page Enable Error flag. This indicates that an EEPROM write was attempted to a page that was not enabled for write-access.

**MEM\_WR** (bit 4): Memory Write flag. This bit is set during the EEPROM memory access scheme when the Map bit is set with an HDQ write command. This bit is cleared if the Map bit is set with an HDQ read command or upon completion of an EEPROM program cycle. Refer to Figure 10.

**RSTBIT (bit 2):** This bit is set to '1' when the device has reset due to a Power On Reset (POR) event or a soft reset initiated by the Control:Reset bit. The RSTBIT will remain set to '1' until the Control:RSTCLR bit is set to '1'.

**MEM\_ERR (bit 1):** This bit is set to '1' when the device detects an EEPROM memory error. Refer to Figure 10. This bit, along with CRCB ERR, is cleared using the Control:ERRCLR bit.

**CRCB\_ERR (bit 0):** This bit is set to '1' when the device detects a BUFFER memory error after computing a CRC check. Refer to Figure 10. This bit, along with MEM\_ERR, is cleared using the Control:ERRCLR bit.

#### Control Register (address 0x05):

|        | 7(MSB) | 6    | 5    | 4      | 3     | 2      | 1     | 0        |

|--------|--------|------|------|--------|-------|--------|-------|----------|

| Name   | CONV   | RSVD | RSVD | ERRCLR | SLEEP | RSTCLR | RESET | SHUTDOWN |

| Access | R/W    | R    | R    | R/W    | R/W   | R/W    | R/W   | R/W      |

| Reset  | 0      | 0    | 0    | 0      | 0     | 0      | 0     | 0        |

**CONV** (bit 7): Convert command bit. This bit is used to start an ADC conversion when set to '1' and is automatically cleared at the end of data conversion cycle in order to minimize HDQ traffic. At the start of data conversion, the device sets the Status:BUSY flag and automatically clears the Status:ADC\_DRDY flag to indicate data conversion is in progress. When data conversion is complete, both the CONV bit and BUSY flag are cleared and the ADC\_DRDY flag is set. To abort an ADC conversion in process, the host can clear the CONV bit to '0'.

**ERRCLR (bit 4):** A '1' written to this bit will clear both the Status:MEM\_ERR and CRCB\_ERR bits. This bit auto-clears itself so a readback always reads '0'.

**SLEEP (bit 3):** A '1' written to this bit enables a lower-power mode with the HFO disabled. This bit is automatically cleared upon detection of HDQ communication activity. Therefore a readback of this bit over HDQ will always be '0'.

Note: If SLEEP mode is commanded, the host should wake up the bq2028 by issuing an HDQ break pulse with no associated data, followed by a wait period of at least 200 us (tSLWU), then send a second HDQ break pulse with the first command.

**RSTCLR (bit 2):** A '1' written to this bit will clear the Status:RSTBIT flag and auto-clear itself so a readback always reads '0'.

**RESET (bit 1):** A '1' written to this bit will initiate a full device initialization. The device will auto-clear the RESET bit and set the Status:RSTBIT and Status:BUSY flags at the start of initialization. After initialization is complete the device will clear the BUSY flag.

**SHUTDOWN** (bit 0): A '1' written to this bit will initiate a full device Shutdown. This bit is automatically cleared upon a POR and must be cleared for correct HDQ activity. Therefore a readback of this bit over HDQ will always be '0'.

Note: If SHUTDOWN mode is commanded, the host should wake up the bq2028 by issuing an HDQ break pulse with no associated data, followed by a wait period of at least 15ms ( $t_{SHWU}$ ), then send a second HDQ break pulse with the first command.

Copyright © 2012, Texas Instruments Incorporated

## Page Register (address 0x07): EEPROM Page Register

|        | 7(MSB) | 6    | 5    | 4    | 3    | 2         | 1   | 0   |

|--------|--------|------|------|------|------|-----------|-----|-----|

| Name   | RSVD   | RSVD | RSVD | RSVD | RSVD | Page[2:0] |     |     |

| Access | R      | R    | R    | R    | R    | R/W       | R/W | R/W |

| Reset  | 0      | 0    | 0    | 0    | 0    | 0         | 0   | 0   |

Page[2:0]: This contains the current 3-bit Page pointer for EEPROM access.

## ADCTL1 (address 0x08): ADC Control Register 1

|               | 7(MSB) | 6     | 5        | 4        | 3    | 2       | 1       | 0       |

|---------------|--------|-------|----------|----------|------|---------|---------|---------|

| Final Product | RSVD   | VRVDD | SPEED[1] | SPEED[0] | RSVD | CHAN[2] | CHAN[1] | CHAN[0] |

| Access        | R/W    | R/W   | R/W      | R/W      | R/W  | R/W     | R/W     | R/W     |

| Reset         | 0      | 0     | 0        | 0        | 0    | 0       | 0       | 0       |

RSVD (bit 7) Do not use.

**VRVDD (bit 6):** Voltage reference selection bit. This bit selects which voltage reference (either  $V_{DD}$  or internal  $V_{REF}$ ) is used by the ADC.

- 1 Selects VDD as the ADC reference voltage for ratio metric conversions

- 0 Selects the internal V<sub>REF</sub> as the ADC reference voltage

## SPEED[1:0] (bits 5-4):

Conversion speed selection bits.

| SPEED[1:0] | FILTER LENGTH | CONVERSION TIME |

|------------|---------------|-----------------|

| 00         | 8192          | 125ms           |

| 01         | 4096          | 62.5ms          |

| 10         | 2048          | 31.25ms         |

| 11         | 512           | 7.8125ms        |

RSVD (bit 3) Do not use.

**CHAN[2:0] (bits 2–0):** ADC Channel selection bits. Set to VTEMP ('101') to measure the internal die temperature sensor or set to VSS ('111') for measuring ADC offset.

| CHAN[2:0] | ADC INPUT CHANNEL (Product Datasheet) |

|-----------|---------------------------------------|

| 000       | RSVD                                  |

| 001       | RSVD                                  |

| 010       | RSVD                                  |

| 011       | RSVD                                  |

| 100       | RSVD                                  |

| 101       | VTEMP                                 |

| 110       | RSVD                                  |

| 111       | VSS                                   |

Product Folder Links : bq2028

#### ADCTL2 (address 0x09): ADC Control Register 2

|               | 7(MSB) | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|--------|------|------|------|------|------|------|------|

| Final Product | RSVD   | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD |

| Access        | R      | R    | R    | R    | R    | R    | R    | R    |

| Reset         | 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

RSVD (bits 7:0): Do not use.

#### ADHI (address 0x0A): ADC High Byte Data Register

This register provides the high byte ADC conversion data in 2's complement format. A full scale (max value) for this register is 7FFFh. A zero scale (min value) for this register is 8000h.

|        | 7(MSB) | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------|--------|-----------|---|---|---|---|---|---|--|

| Name   |        | ADC[15:8] |   |   |   |   |   |   |  |

| Access | R      | R         | R | R | R | R | R | R |  |

| Reset  | 1      | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |

ADC[15:8] (bits 7:0): ADC high byte conversion data.

## ADLOW (address 0x0B): ADC Low Byte Data Register

|        | 7(MSB) | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------|--------|----------|---|---|---|---|---|---|--|

| Name   |        | ADC[7:0] |   |   |   |   |   |   |  |

| Access | R      | R        | R | R | R | R | R | R |  |

| Reset  | 1      | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |

ADC[7:0] (bits 7:0): ADC low byte conversion data.

## CRCH Register (address 0x0C): HDQ CRC Register

The register contains the CRC-8 result of the previous HDQ command + data sequence and is useful for data integrity checks for single HDQ packet transfers.

|        | 7(MSB) | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------|--------|-----------|---|---|---|---|---|---|--|

| Name   |        | CHRH[7:0] |   |   |   |   |   |   |  |

| Access | R      | R         | R | R | R | R | R | R |  |

| Reset  | 0      | 0         | 0 | 0 | 0 | 0 | 0 | 0 |  |

CHCH[7:0]: CRC-8 data from the previous HDQ packet. Data is computed using the full 16-bit HDQ package sequence included W/R bit, 7-bit command and 8-bit data.

Copyright © 2012, Texas Instruments Incorporated

#### Row Register (address 0x0D): EEPROM Row Register

|        | 7(MSB) | 6    | 5    | 4    | 3        | 2 | 1 | 0 |

|--------|--------|------|------|------|----------|---|---|---|

| Name   | RSVD   | RSVD | RSVD | RSVD | Row[3:0] |   |   |   |

| Access | R      | R    | R    | R    | R        | R | R | R |

| Reset  | 0      | 0    | 0    | 0    | 0        | 0 | 0 | 0 |

**Row[3:0]:** This contains the current 4-bit Row pointer for a particular page. The value is automatically updated by Mapped access to the EEPROM.

#### DeviceRev Register (address 0x0E): Device Revision Register

|        | 7(MSB) | 6              | 5 | 4 | 3 | 2 | 1 | 0 |  |

|--------|--------|----------------|---|---|---|---|---|---|--|

| Name   |        | DeviceRev[7:0] |   |   |   |   |   |   |  |

| Access | R      | R              | R | R | R | R | R | R |  |

| Reset  |        | DeviceRev[7:0] |   |   |   |   |   |   |  |

**DeviceRev[7:0]:** The read-only register returns the hardware device revision value The initial revision is 0x01 and increments by 1 for each design revision.

#### DeviceID Register (address 0x0F): Device ID Register

|        | 7(MSB) | 6             | 5 | 4          | 3           | 2 | 1 | 0 |  |

|--------|--------|---------------|---|------------|-------------|---|---|---|--|

| Name   |        | DeviceID[7:0] |   |            |             |   |   |   |  |

| Access | R      | R R R R R R   |   |            |             |   |   |   |  |

| Reset  |        |               |   | DeviceID[7 | 7:0] = 0x28 |   |   |   |  |

**DeviceRev[7:0]:** This read-only register returns the unique device identification value which provides a method for the host to distinguish the bq2028 from other HDQ devices. The DeviceID for the bq2028 = 0x28.

#### CRCR Register (address 0x20): BUFFER CRC Result Register

|        | 7(MSB) | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|--------|--------|-----------|---|---|---|---|---|---|--|--|

| Name   |        | CRCR[7:0] |   |   |   |   |   |   |  |  |

| Access | R      | R R R R R |   |   |   |   |   |   |  |  |

| Reset  |        | Undefined |   |   |   |   |   |   |  |  |

CRCR[7:0]: This register contains the last BUFFER CRC computation result.

## CRCT Register (address 0x21): BUFFER CRC Target Register

|        | 7(MSB) | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|--------|--------|-----------|-----|-----|-----|-----|-----|-----|--|--|

| Name   |        | CRCT[7:0] |     |     |     |     |     |     |  |  |

| Access | R/W    | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0      | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

**CRCT[7:0]:** This register contains the CRC computation target for verifying the BUFFER contents prior to writing the data to EEPROM. This method is used to prevent EEPROM data corruption due to interrupted HDQ transfers or communication errors. An HDQ write to this register triggers the comparison of the CRC previously calculated as BUFFER data is loaded from the HDQ interface. If the MEM\_WR flag is set and the CRCT target register matches the CRCR result register, the device will write the BUFFER to the EEPROM using the current ROW and PAGE register values. Then a read-back of the EEPROM will be rechecked to confirm the integrity of the memory write. Refer to flow chart in Figure 10 for CRC initialization and computations. An HDQ read of this register returns the previously written target value.

#### CONTROL2 (address 0x25): CONTROL2 Register

|        | 7(MSB) | 6    | 5    | 4    | 3    | 2    | 1    | 0       |

|--------|--------|------|------|------|------|------|------|---------|

| Name   | RSVD   | RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | MANWREN |

| Access | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W     |

| Reset  | 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0       |

RSVD (bits 7:1): Do not use.

MANWREN (Bit 0): A '1' enables write access to the Page 0 Manufacturer's area registers and associated EEPROM locations 0x30 through 0x3F. Users of the bg2028 may only change the PageEn register (0x031) without adversely changing manufacturing trim data.

## PageEn Register (address 0x31): Page Enable Register

|        | 7(MSB) | 6                            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|--------|--------|------------------------------|---|---|---|---|---|---|--|--|--|

| Name   |        | PageEn[7:0]                  |   |   |   |   |   |   |  |  |  |

| Access | R/W    | W R/W R/W R/W R/W R/W R/W    |   |   |   |   |   |   |  |  |  |

| Reset  |        | EEPROM Page[0], Address 0x31 |   |   |   |   |   |   |  |  |  |

PageEn[X]: Each bit maps to the associated EEPROM page and enables write access. An attempt to write to Page[X] with PageEn[X]=0 will cause the PGEN\_ERR bit to be set in the Status Register. This register has a hardware write protection feature. To write to this register, the MANWREN bit must be set in the Control 2 Register. This register is automatically loaded at reset with data stored in the EEPROM memory (page 0, byte address 0x31)

- 1 Page[X] is writable

- 0 Page[X] is read-only

#### CRC FUNCTIONS FOR DATA INTEGRITY

For data integrity checks, the bg2028 provides a CRC-8 computation block with the polynomial function of  $(X^8+X^5+X^4+1)$ . The following Python code indicates the parallel computation method where the 8-bit variable 'c' is the new data for calculating the CRC and the 8-bit variable 'prev' is the previous result if calculating the CRC on multiple data items. To start a new sequence, the 'prev' variable is initialized with the value 0xFF. Note: The initialization value of 0xFF is new in spec version 1.5. Previous versions used an initialization value of 0x00.

```

c ^= prev

for I in range(8):

if (c & 0x80):

c = ((c << 1 \& 0xff)) ^0x31

else:

c = (c << 1) & 0xff

return c

```

Copyright © 2012, Texas Instruments Incorporated

Refer to the table below for example data sequences and the expected CRC:

| EXAMPLE DATA SEQUENCE (Byte order left to right) | CRC  |

|--------------------------------------------------|------|

| 0x00                                             | 0xAC |

| 0xAA                                             | 0x8B |

| 0xFF                                             | 0x00 |

| 0x00 0xAA                                        | 0xA6 |

| 0xAA 0x55                                        | 0x1B |

| 0xFF 0x01 0x55                                   | 0x7F |

| 0x00 0x01 0x55 0xAA                              | 0xF1 |

The CRC-8 function is typically used for verification of EEPROM data integrity via the BUFFER. To prevent EEPROM memory corruption, BUFFER data will not be written to EEPROM without passing a CRC verification check. Refer to the Figure 10 flow-char for the HDQ Access Method related to CRC computation and verification. The additional complexity of this CRC-8 computation method is provided to minimize HDQ overhead traffic when performing data integrity checks on variable length data elements.

The CRC-8 function is initiated on every HDQ data transfer with the result of the previous CRC-8 stored in the CRCH register. The CRCH register is typically used for single HDQ data packet integrity checks. Since the HDQ protocol shifts data with the LSB arriving first, the CRC is computed in this order:

A0:A6. R/W. D0-D7.

Note: This is the opposite bit ordering from the BUFFER CRC-8 computations.

#### Memory Access HDQ host pseudo-code examples

```

8-bit EEPROM Write (Example is <Bytel>):

// Pre-Compute CRC-8 for 8-bit data

Crc8 = FnCRC8(Byte1)

WRITE '1RRRR01', Byte1

WRITE '0100001', Crc8

8-bit EEPROM Read (Example is <Byte2>):

READ '1RRRR10', Byte2 // Fetch ROW 'RRRR' to BUFFER, Peek Buffer[2], Clear MEM_WR

Crc8 = FnCRC8(Byte2) // Compute CRC-8 on 1 byte read

WRITE '0100001', Crc8 // Poke Crc8 to CRCT trigger MEM write and re-check

READ '0000100', Status // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028\_Error // B0 = CRCB\_ERR, B1 = MEM\_ERR

16-bit EEPROM Write (Lower 2-Bytes)

Crc8 = FnCRC8(Byte0, Byte1) // Pre-Compute CRC-8 for 16-bit data

WRITE '1RRRR00', Byte0 // Pre-fetch EEPROM ROW 'RRRR', Poke Buffer[0], Set MEM_WR WRITE '0000001', Byte1 // Poke Buffer[1]

WRITE '0000001', Bytel

WRITE '0100001', Crc8 // Poke Crc8 to CRCT trigger MEM write and re-check READ '0000100', Status // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028_Error // B0 = CRCB_ERR, B1 = MEM_ERR

16-bit EEPROM Read (Lower 2-Bytes)

READ '1RRRR00', Byte0 // Fetch ROW 'RRRR' to BUFFER, Peek Buffer[0], Clear MEM_WR READ '0000001', Byte1 // Peek Buffer[1]

Crc8 = FnCRC8(Byte0, Byte1) // Compute CRC-8 on 2 bytes read

WRITE '0100001', Crc8 \, // Poke Crc8 to CRCT trigger MEM write and re-check READ '0000100', Status \, // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028_Error

// B0 = CRCB_ERR, B1 = MEM_ERR

```

```

24-bit EEPROM Write (Lower 3-Bytes)

Crc8 = FnCRC8(Byte0, Byte2, Byte3) // Pre-Compute CRC-8 for 24-bit data

WRITE '1RRRR00', Byte0 // Pre-fetch EEPROM ROW 'RRRR', Poke Buffer[0], Set MEM_WR

WRITE '0000001', Byte1

WRITE '0000010', Byte2

// Poke Buffer[1]

// Poke Buffer[2]

WRITE '0100001', Crc8 // Poke Crc8 to CRCT trigger MEM write and re-check READ '0000100', Status // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028_Error // B0 = CRCB_ERR, B1 = MEM_ERR

24-bit EEPROM Read (Lower 3-Bytes)

READ '1RRRR00', Byte0

// Fetch ROW 'RRRR' to BUFFER, Peek Buffer[0], Clear MEM_WR

READ '0000001', Bytel

READ '0000001', Byte1 // Peek Buffer[1]

READ '0000010', Byte2 // Peek Buffer[2]

Crc8 = FnCRC8(Byte0, Byte2, Byte3) // Compute CRC-8 on 3 bytes read

WRITE '0100001', Crc8 // Poke Crc8 to CRCT trigger MEM write and re-check READ '0000100', Status // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028_Error // B0 = CRCB_ERR, B1 = MEM_ERR

32-bit EEPROM Write (Full 4-Bytes)

Crc8 = FnCRC8(Byte0, Byte1, Byte2, Byte3) // Pre-Compute CRC-8 for 32-bit data

WRITE '1RRRR00', Byte0

// Pre-fetch EEPROM ROW 'RRRR', Poke Buffer[0], Set MEM_WR

WRITE '0000001', Byte1

// Poke Buffer[1]

WRITE '0000010', Byte2

// Poke Buffer[2]

WRITE '0000011', Byte3 // Poke Buffer[3]

WRITE '0100001', Crc8 // Poke Crc8 to CRCT trigger MEM write and re-check

READ '0000100', Status // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028_Error // B0 = CRCB_ERR, B1 = MEM_ERR

32-bit EEPROM Read (Full 4-Bytes)

READ '1RRRR00', Byte0 // Fetch ROW 'RRRR' to BUFFER, Peek Buffer[0], Clear MEM_WR

READ '0000001', Byte1 // Peek Buffer[1]

READ '0000010', Byte2 // Peek Buffer[2]

READ '0000011', Byte3 // Peek Buffer[3]

Crc8 = FnCRC8(Byte0, Byte1, Byte2, Byte3)

// Compute CRC-8 on 3 bytes read

WRITE '0100001', Crc8 // Poke Crc8 to CRCT trigger MEM write and re-check READ '0000100', Status // Peek Status Register.

IF (Status && 0x03) THEN CALL bq2028_Error // B0 = CRCB_ERR, B1 = MEM_ERR

```

#### INTERNAL TEMPERATURE SENSOR

An internal die temperature sensor is available on the bq2028 to reduce the cost, power, and size of the external components necessary to measure temperature. Temperature sensing uses the  $V_{BE}$  method to present a voltage to a delta-sigma ADC converter. The host reads the ADC data over the HDQ interface and uses firmware to convert the data to Kelvin temperature units.

ADC data is formatted to 16-bits even though the data conversion performance may be limited to 10 effective bits. An ADC conversion starts when the Control:CONV bit is set to '1' and is automatically cleared at the end of the data conversion cycle. At the start of data conversion, the device sets the Status:BUSY flag and automatically clears the Status:ADC\_DRDY flag to indicate data conversion is in progress. When data conversion is complete, both the CONV bit and BUSY flag are cleared and the ADC\_DRDY flag is set. To abort an ADC conversion in process, the host can clear the CONV bit to '0'.

The data in the ADC Data Registers is stored in 2s complement format. Full scale (7FFFh) is referred to the reference voltage (Vref), typically 1.225 V. A hardware protection circuit will not allow the converter to rollover from a full scale value (7FFFh) to a min scale value (8000h).

### **CLOCK GENERATOR CIRCUITS**

The clock generator circuits are used to generate the internal clocks for the bq2028. The primary internal clocks are derived from the low frequency oscillator (32.768kHz), and the high frequency oscillator (8.389 MHz). The analog oscillator circuits are trimmed for accuracy, and then divided down for use throughout the device in both the analog and digital circuits. The bq2028 makes extensive use of clock gating to dynamically shutdown clocks to modules and interfaces not in use for low power operation. The low frequency oscillator (LFO) is required to run continuously during operation of the device with exception to a shutdown condition. The high frequency oscillator (HFO) is dynamically enabled and disabled as needed.

# **Low Frequency Oscillator Operation**

The 32.768 kHz low frequency oscillator clock is generated from a fully integrated oscillator circuit with no requirements for external components. This circuit is trimmed for accuracy during factory production. The LFO trim value is stored in EEPROM memory Page 0. The LFO trim value is automatically read from EEPROM and written to the LFO trim register shortly after the device comes out of reset. The LFO output is divided down for various interfaces and modules in the device, as shown in Table 3.

**Table 3. LFO Clocked Interfaces**

| INTERFACE OR MODULE | REQUIRED WHEN:                  | Frequency  | DIVIDE  |

|---------------------|---------------------------------|------------|---------|

| HFO Trim Circuit    | HFO is enabled                  | 32.768 kHz | LFO     |

| Reset Timer         | Power up of device (4ms)        | 32.768 kHz | LFO     |

| HDQ low timeout     | HDQ line is pulled low for 2sec | 128 Hz     | LFO/256 |

#### **High Frequency Oscillator Operation**

The 8.389 MHz high frequency oscillator clock is generated from a fully integrated oscillator circuit with no requirements for external components. The bq2028 trims the 8.389MHz high frequency clock output internally by using an automatic high frequency trim circuit. Using the more accurate 32.768kHz clock as a reference, the high frequency clock is adjusted until it is determined to be within the desired operating frequency. The trim circuit continues to monitor and adjust the 8.389MHz clock as needed. Due to the nature of the trim algorithm, some small changes may be noticed in the 8.389MHz clock as it is adjusted based upon operating conditions and the 32.768kHz reference clock. The HFO output is divided down for various modules in the device.

**Table 4. HFO Clocked Interfaces**

| INTERFACE OR MODULE | REQUIRED WHEN:                            | FREQUENCY  | DIVIDE  |

|---------------------|-------------------------------------------|------------|---------|

| HFO Trim Circuit    | HFO is enabled                            | 8.389 MHz  | HFO     |

| HDQ Communication   | HDQ interface is enabled                  | 1.049 MHz  | HFO/8   |

| HDQ Register Access | Writing or reading unmapped HDQ registers | 1.049 MHz  | HFO/8   |

| EEPROM Access       | Reading or programming EEPROM memory      | 1.049 MHz  | HFO/8   |

| ADC                 | ADC conversion enabled                    | 65.536 kHz | HFO/128 |

Product Folder Links :bq2028

# **REVISION HISTORY**

| Changes from Original (October 2012) to Revision A                                                                | Page       |

|-------------------------------------------------------------------------------------------------------------------|------------|

| Changed from "Typ." to "Typical" in Features bullet                                                               | 1          |

| <ul> <li>Deleted footnote "Assured by design. Not production tested" from DC Electrical Characteristic</li> </ul> | cs table 4 |

| Deleted footnote "Assured by design. Not production tested" from AC Electrical Characteristic                     | s table 5  |

| Changes from Revision A (October 2012) to Revision B                                                              | Page       |

| Added Note 1 to I <sub>CC</sub> Supply Current                                                                    | 4          |

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| BQ2028YZGR       | ACTIVE | DSBGA        | YZG                | 12   | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | BQ2028                  | Samples |

| BQ2028YZGT       | ACTIVE | DSBGA        | YZG                | 12   | 250            | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | BQ2028                  | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 6-Jun-2024

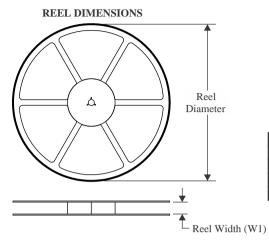

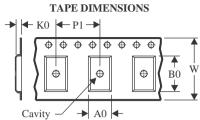

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

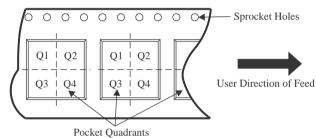

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     |       | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ2028YZGR | DSBGA | YZG                | 12 | 3000 | 180.0                    | 8.4                      | 1.59       | 2.45       | 0.69       | 4.0        | 8.0       | Q1               |

| BQ2028YZGT | DSBGA | YZG                | 12 | 250  | 180.0                    | 8.4                      | 1.59       | 2.45       | 0.69       | 4.0        | 8.0       | Q1               |

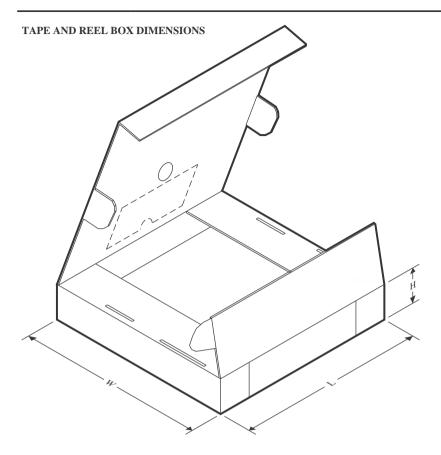

**PACKAGE MATERIALS INFORMATION**

www.ti.com 6-Jun-2024

## \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ2028YZGR | DSBGA        | YZG             | 12   | 3000 | 182.0       | 182.0      | 20.0        |

| BQ2028YZGT | DSBGA        | YZG             | 12   | 250  | 182.0       | 182.0      | 20.0        |

# YZG (R-XBGA-N12)

# DIE-SIZE BALL GRID ARRAY

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated