Data sheet acquired from Harris Semiconductor SCHS204J

February 1998 - Revised December 2003

# High-Speed CMOS Logic Phase-Locked Loop with VCO

#### Features

- Operating Frequency Range

- Up to 18MHz (Typ) at  $V_{CC} = 5V$

- Minimum Center Frequency of 12MHz at V<sub>CC</sub> = 4.5V

- · Choice of Three Phase Comparators

- EXCLUSIVE-OR

- Edge-Triggered JK Flip-Flop

- Edge-Triggered RS Flip-Flop

- Excellent VCO Frequency Linearity

- VCO-Inhibit Control for ON/OFF Keying and for Low Standby Power Consumption

- Minimal Frequency Drift

- Operating Power Supply Voltage Range

- Digital Section ......2V to 6V

- Fanout (Over Temperature Range)

- Standard Outputs......10 LSTTL Loads

- Bus Driver Outputs ...... 15 LSTTL Loads

- Wide Operating Temperature Range . . . -55°C to 125°C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity:  $N_{IL}$  = 30%,  $N_{IH}$  = 30% of  $V_{CC}$  at  $V_{CC}$  = 5V

- HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V<sub>IL</sub>= 0.8V (Max), V<sub>IH</sub> = 2V (Min)

- CMOS Input Compatibility,  $I_I \le 1\mu A$  at VOL, VOH

### **Applications**

- FM Modulation and Demodulation

- · Frequency Synthesis and Multiplication

- Frequency Discrimination

- Tone Decoding

- Data Synchronization and Conditioning

- Voltage-to-Frequency Conversion

- Motor-Speed Control

#### Description

The 'HC4046A and 'HCT4046A are high-speed silicon-gate CMOS devices that are pin compatible with the CD4046B of the "4000B" series. They are specified in compliance with JEDEC standard number 7.

The 'HC4046A and 'HCT4046A are phase-locked-loop circuits that contain a linear voltage-controlled oscillator (VCO) and three different phase comparators (PC1, PC2 and PC3). A signal input and a comparator input are common to each comparator.

The signal input can be directly coupled to large voltage signals, or indirectly coupled (with a series capacitor) to small voltage signals. A self-bias input circuit keeps small voltage signals within the linear region of the input amplifiers. With a passive low-pass filter, the 4046A forms a second-order loop PLL. The excellent VCO linearity is achieved by the use of linear op-amp techniques.

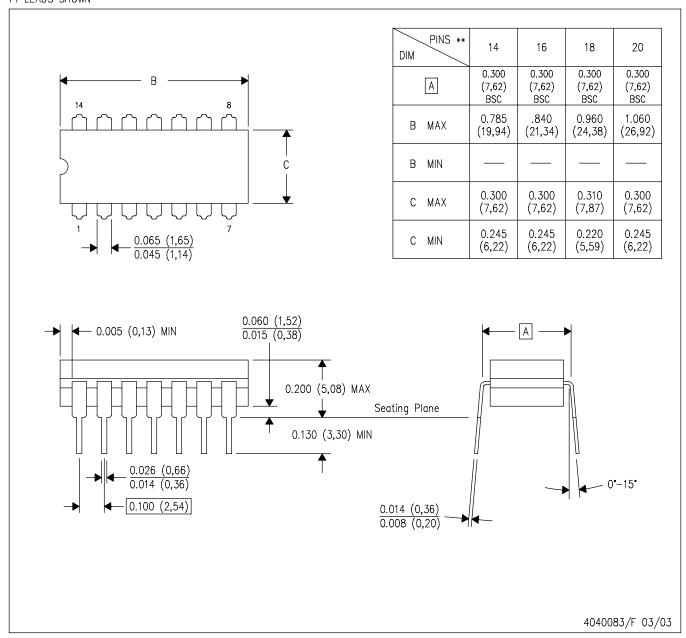

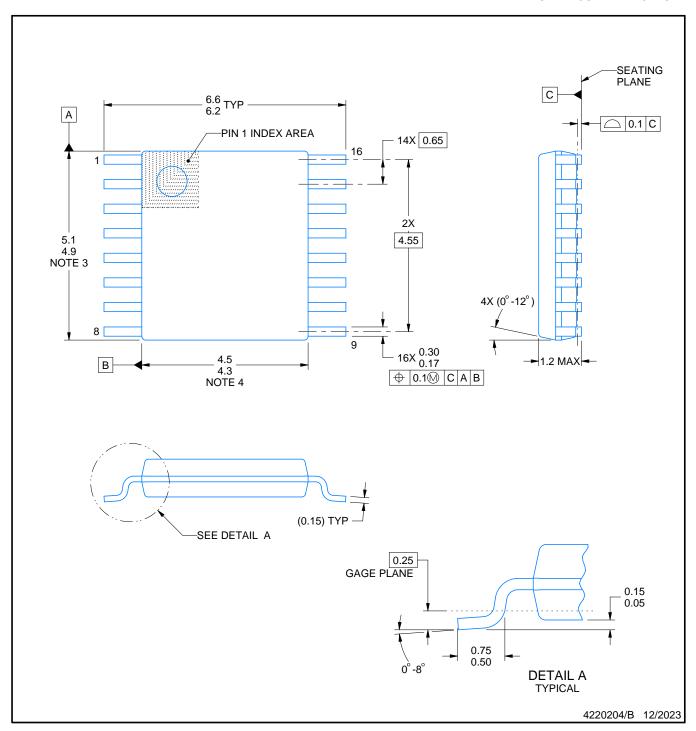

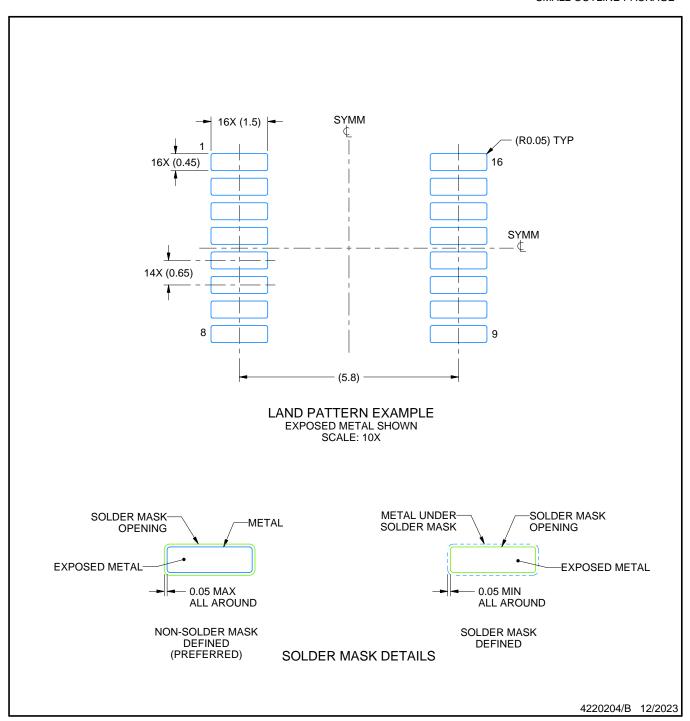

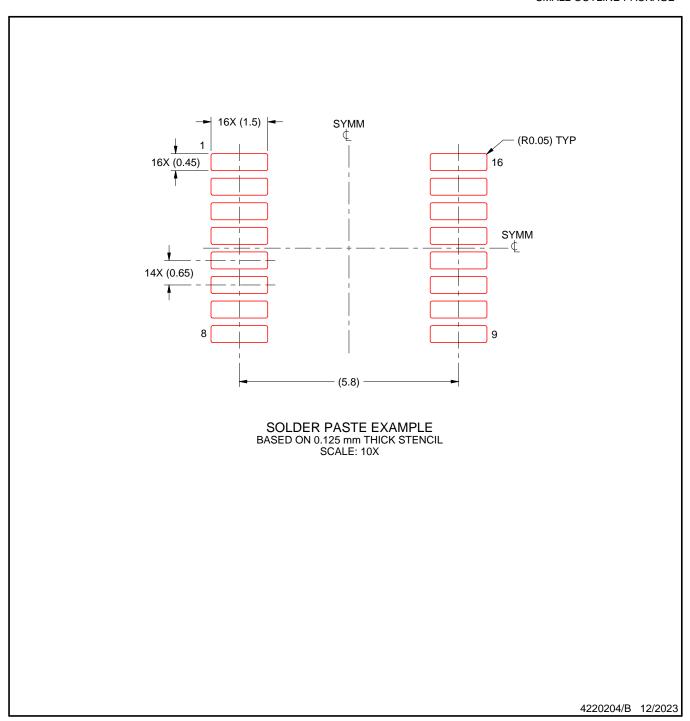

### **Ordering Information**

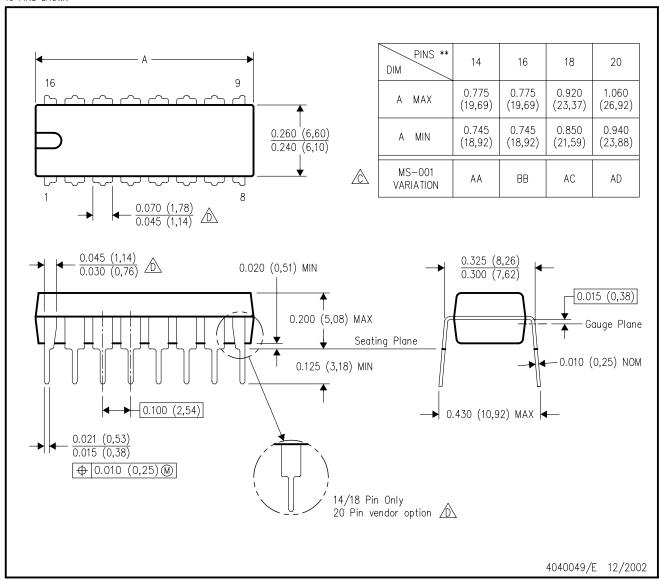

| PART NUMBER     | TEMP. RANGE<br>( <sup>O</sup> C) | PACKAGE      |

|-----------------|----------------------------------|--------------|

| CD54HC4046AF3A  | -55 to 125                       | 16 Ld CERDIP |

| CD54HCT4046AF3A | -55 to 125                       | 16 Ld CERDIP |

| CD74HC4046AE    | -55 to 125                       | 16 Ld PDIP   |

| CD74HC4046AM    | -55 to 125                       | 16 Ld SOIC   |

| CD74HC4046AMT   | -55 to 125                       | 16 Ld SOIC   |

| CD74HC4046AM96  | -55 to 125                       | 16 Ld SOIC   |

| CD74HC4046ANSR  | -55 to 125                       | 16 Ld SOP    |

| CD74HC4046APWR  | -55 to 125                       | 16 Ld TSSOP  |

| CD74HC4046APWT  | -55 to 125                       | 16 Ld TSSOP  |

| CD74HCT4046AE   | -55 to 125                       | 16 Ld PDIP   |

| CD74HCT4046AM   | -55 to 125                       | 16 Ld SOIC   |

| CD74HCT4046AMT  | -55 to 125                       | 16 Ld SOIC   |

| CD74HCT4046AM96 | -55 to 125                       | 16 Ld SOIC   |

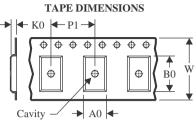

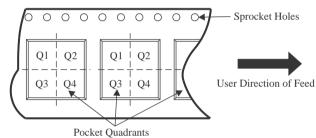

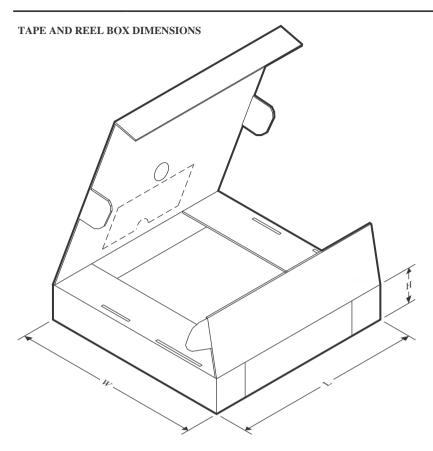

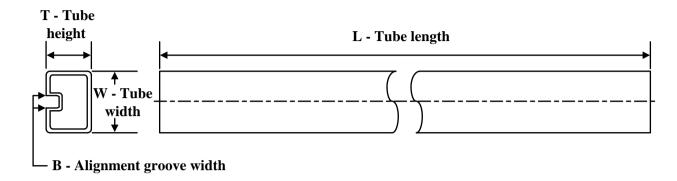

NOTE: When ordering, use the entire part number. The suffixes 96 and R denote tape and reel. The suffix T denotes a small-quantity reel of 250.

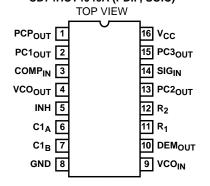

# **Pinout**

CD54HC4046A, CD54HCT4046A (CERDIP) CD74HC4046A (PDIP, SOIC, SOP, TSSOP) CD74HCT4046A (PDIP, SOIC)

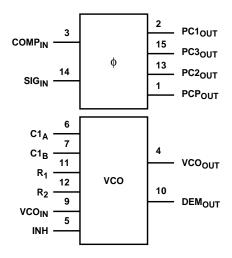

# Functional Diagram

# Pin Descriptions

| PIN NUMBER | SYMBOL             | NAME AND FUNCTION             |  |

|------------|--------------------|-------------------------------|--|

| 1          | PCP <sub>OUT</sub> | Phase Comparator Pulse Output |  |

| 2          | PC1 <sub>OUT</sub> | Phase Comparator 1 Output     |  |

| 3          | COMP <sub>IN</sub> | Comparator Input              |  |

| 4          | VCO <sub>OUT</sub> | VCO Output                    |  |

| 5          | INH                | Inhibit Input                 |  |

| 6          | C1 <sub>A</sub>    | Capacitor C1 Connection A     |  |

| 7          | C1 <sub>B</sub>    | Capacitor C1 Connection B     |  |

| 8          | GND                | Ground (0V)                   |  |

| 9          | VCO <sub>IN</sub>  | VCO Input                     |  |

| 10         | DEM <sub>OUT</sub> | Demodulator Output            |  |

| 11         | R <sub>1</sub>     | Resistor R1 Connection        |  |

| 12         | R <sub>2</sub>     | Resistor R2 Connection        |  |

| 13         | PC2 <sub>OUT</sub> | Phase Comparator 2 Output     |  |

| 14         | SIG <sub>IN</sub>  | Signal Input                  |  |

| 15         | PC3 <sub>OUT</sub> | Phase Comparator 3 Output     |  |

| 16         | V <sub>CC</sub>    | Positive Supply Voltage       |  |

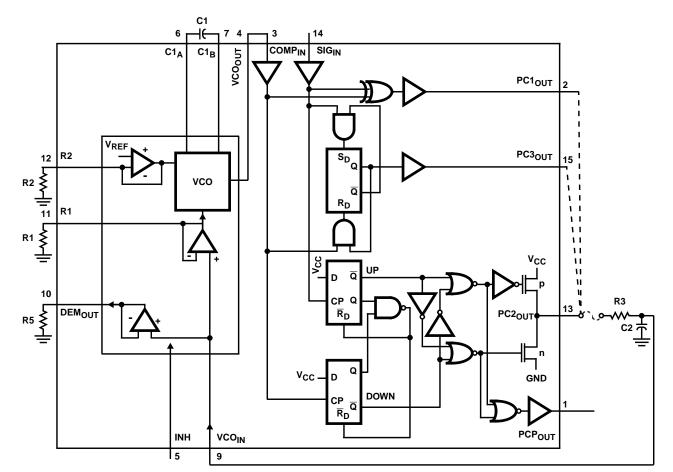

FIGURE 1. LOGIC DIAGRAM

### General Description

#### **VCO**

The VCO requires one external capacitor C1 (between C1<sub>A</sub> and C1<sub>B</sub>) and one external resistor R1 (between R<sub>1</sub> and GND) or two external resistors R1 and R2 (between R<sub>1</sub> and GND, and R<sub>2</sub> and GND). Resistor R1 and capacitor C1 determine the frequency range of the VCO. Resistor R2 enables the VCO to have a frequency offset if required. See logic diagram, Figure 1.

The high input impedance of the VCO simplifies the design of low-pass filters by giving the designer a wide choice of resistor/capacitor ranges. In order not to load the low-pass filter, a demodulator output of the VCO input voltage is provided at pin 10 (DEMOUT). In contrast to conventional techniques where the DEMOUT voltage is one threshold voltage lower than the VCO input voltage, here the DEMOUT voltage equals that of the VCO input. If DEMOUT is used, a load resistor (RS) should be connected from DEMOUT to GND; if unused, DEMOUT should be left open. The VCO output (VCO<sub>OUT</sub>) can be connected directly to the comparator input (COMPIN), or connected via a frequencydivider. The VCO output signal has a specified duty factor of 50%. A LOW level at the inhibit input (INH) enables the VCO and demodulator, while a HIGH level turns both off to minimize standby power consumption.

#### **Phase Comparators**

The signal input (SIG<sub>IN</sub>) can be directly coupled to the self-biasing amplifier at pin 14, provided that the signal swing is between the standard HC family input logic levels. Capacitive coupling is required for signals with smaller swings.

#### Phase Comparator 1 (PC1)

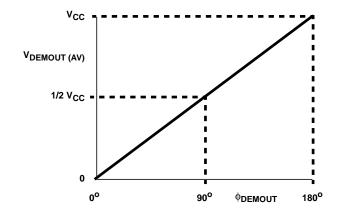

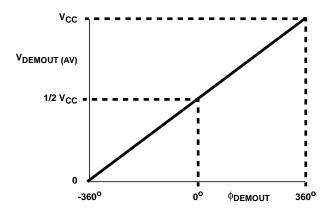

This is an Exclusive-OR network. The signal and comparator input frequencies  $(f_i)$  must have a 50% duty factor to obtain the maximum locking range. The transfer characteristic of PC1, assuming ripple  $(f_r = 2f_j)$  is suppressed, is:

$V_{DEMOUT} = (V_{CC}/\pi)$  ( $\phi SIG_{IN} - \phi COMP_{IN}$ ) where  $V_{DEMOUT}$  is the demodulator output at pin 10;  $V_{DEMOUT} = V_{PC1OUT}$  (via low-pass filter).

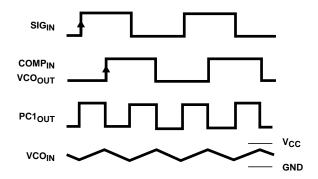

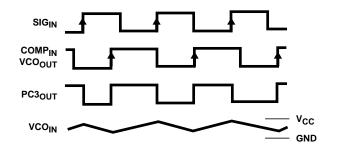

The average output voltage from PC1, fed to the VCO input via the low-pass filter and seen at the demodulator output at pin 10 (VDEMOUT), is the resultant of the phase differences of signals (SIGIN) and the comparator input (COMPIN) as shown in Figure 2. The average of VDEM is equal to 1/2 VCC when there is no signal or noise at SIGIN, and with this input the VCO oscillates at the center frequency (fo). Typical waveforms for the PC1 loop locked at fo are shown in Figure 3.

The frequency capture range  $(2f_C)$  is defined as the frequency range of input signals on which the PLL will lock if it was initially out-of-lock. The frequency lock range  $(2f_L)$  is defined as the frequency range of input signals on which the loop will stay locked if it was initially in lock. The capture range is smaller or equal to the lock range.

With PC1, the capture range depends on the low-pass filter characteristics and can be made as large as the lock range. This configuration retains lock behavior even with very noisy input signals. Typical of this type of phase comparator is that it can lock to input frequencies close to the harmonics of the VCO center frequency.

FIGURE 2. PHASE COMPARATOR 1: AVERAGE OUTPUT VOLTAGE vs INPUT PHASE DIFFERENCE:  $V_{DEMOUT} = V_{PC1OUT} = (V_{CC}/\pi) (\phi SIG_{IN} - \phi COMP_{IN}); \phi_{DEMOUT} = (\phi SIG_{IN} - \phi COMP_{IN})$

FIGURE 3. TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 1, LOOP LOCKED AT  $f_{\rm O}$

#### Phase Comparator 2 (PC2)

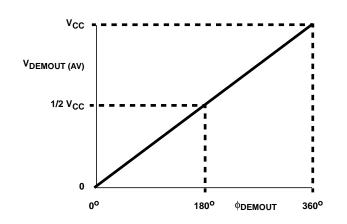

This is a positive edge-triggered phase and frequency detector. When the PLL is using this comparator, the loop is controlled by positive signal transitions and the duty factors of  ${\rm SIG_{IN}}$  and  ${\rm COMP_{IN}}$  are not important. PC2 comprises two D-type flip-flops, control-gating and a three-state output stage. The circuit functions as an up-down counter (Figure 1) where  ${\rm SIG_{IN}}$  causes an up-count and  ${\rm COMP_{IN}}$  a down-count. The transfer function of PC2, assuming ripple ( $f_r=f_i$ ) is suppressed, is:

$V_{DEMOUT} = (V_{CC}/4\pi)$  ( $\phi SIG_{IN} - \phi COMP_{IN}$ ) where  $V_{DEMOUT}$  is the demodulator output at pin 10;  $V_{DEMOUT} = V_{PC2OUT}$  (via low-pass filter).

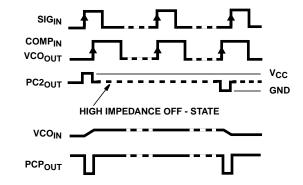

The average output voltage from PC2, fed to the VCO via the low-pass filter and seen at the demodulator output at pin 10 ( $V_{DEMOUT}$ ), is the resultant of the phase differences of SIGIN and COMPIN as shown in Figure 4. Typical waveforms for the PC2 loop locked at  $f_0$  are shown in Figure 5.

FIGURE 4. PHASE COMPARATOR 2: AVERAGE OUTPUT

VOLTAGE vs INPUT PHASE DIFFERENCE:

VDEMOUT = VPC2OUT

=  $(V_{CC}/4\pi)$  ( $\phi$ SIG<sub>IN</sub> -  $\phi$ COMP<sub>IN</sub>);  $\phi$ DEMOUT =  $(\phi$ SIG<sub>IN</sub> -  $\phi$ COMP<sub>IN</sub>)

FIGURE 5. TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 2, LOOP LOCKED AT  $f_{\rm O}$

When the frequencies of SIG<sub>IN</sub> and COMP<sub>IN</sub> are equal but the phase of SIG<sub>IN</sub> leads that of COMP<sub>IN</sub>, the p-type output driver at PC2<sub>OUT</sub> is held "ON" for a time corresponding to the phase difference ( $\phi_{DEMOUT}$ ). When the phase of SIG<sub>IN</sub> lags that of COMP<sub>IN</sub>, the n-type driver is held "ON".

When the frequency of SIG<sub>IN</sub> is higher than that of COMP<sub>IN</sub>, the p-type output driver is held "ON" for most of the input signal cycle time, and for the remainder of the cycle both n- and p-type drivers are "OFF" (three-state). If the SIG<sub>IN</sub> frequency is lower than the COMP<sub>IN</sub> frequency, then it is the n-type driver that is held "ON" for most of the cycle. Subsequently, the voltage at the capacitor (C2) of the low-pass filter connected to PC2<sub>OUT</sub> varies until the signal and comparator inputs are equal in both phase and

frequency. At this stable point the voltage on C2 remains constant as the PC2 output is in three-state and the VCO input at pin 9 is a high impedance. Also in this condition, the signal at the phase comparator pulse output (PCP<sub>OUT</sub>) is a HIGH level and so can be used for indicating a locked condition.

Thus, for PC2, no phase difference exists between  $SIG_{IN}$  and  $COMP_{IN}$  over the full frequency range of the VCO. Moreover, the power dissipation due to the low-pass filter is reduced because both p- and n-type drivers are "OFF" for most of the signal input cycle. It should be noted that the PLL lock range for this type of phase comparator is equal to the capture range and is independent of the low-pass filter. With no signal present at  $SIG_{IN}$ , the VCO adjusts, via PC2, to its lowest frequency.

#### Phase Comparator 3 (PC3)

This is a positive edge-triggered sequential phase detector using an RS-type flip-flop. When the PLL is using this comparator, the loop is controlled by positive signal transitions and the duty factors of  $SIG_{IN}$  and  $COMP_{IN}$  are not important. The transfer characteristic of PC3, assuming ripple ( $f_r = f_i$ ) is suppressed, is:

$V_{DEMOUT} = (V_{CC}/2p)$  (fSIG<sub>IN</sub> - fCOMP<sub>IN</sub>) where  $V_{DEMOUT}$  is the demodulator output at pin 10;  $V_{DEMOUT} = V_{PC3OUT}$  (via low-pass filter).

The average output from PC3, fed to the VCO via the low-pass filter and seen at the demodulator at pin 10 ( $V_{DEMOUT}$ ), is the resultant of the phase differences of SIGIN and COMPIN as shown in Figure 6. Typical waveforms for the PC3 loop locked at  $f_{0}$  are shown in Figure 7.

The phase-to-output response characteristic of PC3 (Figure 6) differs from that of PC2 in that the phase angle between  $SIG_{IN}$  and  $COMP_{IN}$  varies between  $0^{\rm o}$  and  $360^{\rm o}$  and is  $180^{\rm o}$  at the center frequency. Also PC3 gives a greater voltage swing than PC2 for input phase differences but as aconsequence the ripple content of the VCO input signal is higher. With no signal present at  $SIG_{IN}$ , the VCO adjusts, via PC3, to its highest frequency.

The only difference between the HC and HCT versions is the input level specification of the INH input. This input disables the VCO section. The comparator's sections are identical, so that there is no difference in the  ${\rm SIG_{IN}}$  (pin 14) or  ${\rm COMP_{IN}}$  (pin 3) inputs between the HC and the HCT versions.

FIGURE 6. PHASE COMPARATOR 3: AVERAGE OUTPUT VOLTAGE vs INPUT PHASE DIFFERENCE:

$\begin{aligned} & V_{DEMOUT} = V_{PC3OUT} \\ & = (V_{CC}/2\pi) \; (\phi SIG_{IN} - \phi COMP_{IN}); \\ & \phi_{DEMOUT} = (\phi SIG_{IN} - \phi COMP_{IN}) \end{aligned}$

FIGURE 7. TYPICAL WAVEFORMS FOR PLL USING PHASE COMPARATOR 3, LOOP LOCKED AT  $f_{\rm o}$

###

2V

1000ns (Max)

4.5V

500ns (Max)

6V

400ns (Max)

#### **Thermal Information**

Declare Thermal Immediance () (see Note 4).

| ŀ | Package Thermal Impedance, $\theta_{JA}$ (see Note 1): |          |

|---|--------------------------------------------------------|----------|

|   | E (PDIP) Package                                       | .67°C/W  |

|   | M (SOIC) Package                                       | .73°C/W  |

|   | NS (SOP) Package                                       | 64°C/W   |

|   | PW (TSSOP) Package                                     | 108°C/W  |

|   | Maximum Junction Temperature                           |          |

| Ν | Maximum Storage Temperature Range65°C                  | to 150°C |

| Ν | Maximum Lead Temperature (Soldering 10s)               | 300°C    |

|   | (SOIC - Lead Tips Only)                                |          |

|   |                                                        |          |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

#### **DC Electrical Specifications**

Supply Voltage Range, V<sub>CC</sub>

Input Rise and Fall Time

|                                                               |                 | TES<br>CONDI                       |                     | V <sub>CC</sub> |      | 25°C |      | -40°C T | O 85°C | -55°C T | O 125°C |       |

|---------------------------------------------------------------|-----------------|------------------------------------|---------------------|-----------------|------|------|------|---------|--------|---------|---------|-------|

| PARAMETER                                                     | SYMBOL          | V <sub>I</sub> (V)                 | I <sub>O</sub> (mA) | (V)             | MIN  | TYP  | MAX  | MIN     | MAX    | MIN     | MAX     | UNITS |

| HC TYPES                                                      |                 |                                    |                     |                 |      |      |      |         |        |         |         |       |

| VCO SECTION                                                   |                 |                                    |                     |                 |      |      |      |         |        |         |         |       |

| INH High Level Input                                          | V <sub>IH</sub> | -                                  | -                   | 3               | 2.1  | -    | -    | 2.1     | -      | 2.1     | -       | V     |

| Voltage                                                       |                 |                                    |                     | 4.5             | 3.15 | -    | -    | 3.15    | -      | 3.15    | -       | V     |

|                                                               |                 |                                    |                     | 6               | 4.2  | -    | -    | 4.2     | -      | 4.2     | -       | V     |

| INH Low Level Input                                           | V <sub>IL</sub> | -                                  | -                   | 3               | -    | -    | 0.9  | -       | 0.9    | -       | 0.9     | V     |

| Voltage                                                       |                 |                                    |                     | 4.5             | -    | -    | 1.35 | -       | 1.35   | -       | 1.35    | V     |

|                                                               |                 |                                    | 6                   | -               | -    | 1.8  | -    | 1.8     | -      | 1.8     | V       |       |

| VCO <sub>OUT</sub> High Level<br>Output Voltage<br>CMOS Loads | Voн             | H VIH OT VIL                       | -0.02               | 3               | 2.9  | -    | -    | 2.9     | -      | 2.9     | -       | V     |

|                                                               |                 |                                    | -0.02               | 4.5             | 4.4  | -    | -    | 4.4     | -      | 4.4     | -       | V     |

| CIVICO Educa                                                  |                 |                                    | -0.02               | 6               | 5.9  | -    | -    | 5.9     | -      | 5.9     | -       | V     |

| VCO <sub>OUT</sub> High Level                                 | Ī               |                                    | -                   | -               | -    | -    | -    | -       | -      | -       | -       | V     |

| Output Voltage<br>TTL Loads                                   |                 |                                    | -4                  | 4.5             | 3.98 | -    | -    | 3.84    | -      | 3.7     | -       | V     |

| TTE Louis                                                     |                 |                                    | -5.2                | 6               | 5.48 | -    | -    | 5.34    | -      | 5.2     | -       | V     |

| VCO <sub>OUT</sub> Low Level                                  | V <sub>OL</sub> | V <sub>IH</sub> or V <sub>IL</sub> | 0.02                | 2               | -    | -    | 0.1  | -       | 0.1    | -       | 0.1     | V     |

| Output Voltage<br>CMOS Loads                                  |                 |                                    | 0.02                | 4.5             | -    | -    | 0.1  | -       | 0.1    | -       | 0.1     | V     |

| CIVICO Educa                                                  |                 |                                    | 0.02                | 6               | -    | -    | 0.1  | -       | 0.1    | -       | 0.1     | V     |

| VCO <sub>OUT</sub> Low Level                                  |                 |                                    | -                   | -               | -    | -    | -    | -       | -      | -       | -       | V     |

| Output Voltage<br>TTL Loads                                   |                 |                                    | 4                   | 4.5             | -    | -    | 0.26 | -       | 0.33   | -       | 0.4     | V     |

|                                                               |                 |                                    | 5.2                 | 6               | -    | -    | 0.26 | -       | 0.33   | -       | 0.4     | V     |

| C1A, C1B Low Level                                            | V <sub>OL</sub> | V <sub>IL</sub> or V <sub>IH</sub> | 4                   | 4.5             | -    | -    | 0.40 | -       | 0.47   | -       | 0.54    | V     |

| Output Voltage<br>(Test Purposes Only)                        |                 |                                    | 5.2                 | 6               | -    | -    | 0.40 | -       | 0.47   | -       | 0.54    | V     |

# DC Electrical Specifications (Continued)

|                                                     |                                          | TES<br>CONDI                       |                     | v <sub>cc</sub> |      | 25°C |       | -40°C 1 | O 85°C | -55°C T | O 125°C |       |

|-----------------------------------------------------|------------------------------------------|------------------------------------|---------------------|-----------------|------|------|-------|---------|--------|---------|---------|-------|

| PARAMETER                                           | SYMBOL                                   | V <sub>I</sub> (V)                 | I <sub>O</sub> (mA) | (V)             | MIN  | TYP  | MAX   | MIN     | MAX    | MIN     | MAX     | UNITS |

| INH VCO <sub>IN</sub> Input<br>Leakage Current      | lı                                       | V <sub>CC</sub> or<br>GND          | -                   | 6               | -    | -    | ±0.1  | -       | ±1     | -       | ±1      | μА    |

| R1 Range (Note 2)                                   | -                                        | -                                  | -                   | 4.5             | 3    | -    | 300   | -       | -      | -       | -       | kΩ    |

| R2 Range (Note 2)                                   | -                                        | -                                  | -                   | 4.5             | 3    | -    | 300   | -       | -      | -       | -       | kΩ    |

| C1 Capacitance                                      | -                                        | -                                  | -                   | 3               | -    | -    | No    | -       | -      | -       | -       | pF    |

| Range                                               |                                          |                                    |                     | 4.5             | -    | -    | Limit | -       | -      | -       | -       | pF    |

|                                                     |                                          |                                    |                     | 6               | -    | -    | 1     | -       | -      | -       | -       | pF    |

| VCO <sub>IN</sub> Operating                         | -                                        | Over the                           |                     | 3               | 1.1  | -    | 1.9   | -       | -      | -       | -       | V     |

| Voltage Range                                       |                                          | specified f<br>Linearity S         |                     | 4.5             | 1.1  | -    | 3.2   | -       | -      | -       | -       | V     |

|                                                     |                                          | 10, and<br>(Note                   | 34 - 37             | 6               | 1.1  | -    | 4.6   | -       | -      | -       | -       | ٧     |

| PHASE COMPARATO                                     | R SECTIO                                 | N .                                |                     |                 |      |      | •     |         | •      | •       |         |       |

| SIG <sub>IN</sub> , COMP <sub>IN</sub>              | V <sub>IH</sub>                          | -                                  | -                   | 2               | 1.5  | -    | -     | 1.5     | -      | 1.5     | -       | V     |

| DC Coupled<br>High-Level Input                      |                                          |                                    |                     | 4.5             | 3.15 | -    | -     | 3.15    | -      | 3.15    | -       | V     |

| Voltage                                             |                                          |                                    |                     | 6               | 4.2  | -    | -     | 4.2     | -      | 4.2     | -       | V     |

| SIG <sub>IN</sub> , COMP <sub>IN</sub>              | V <sub>IL</sub>                          | -                                  | -                   | 2               | -    | -    | 0.5   | -       | 0.5    | -       | 0.5     | V     |

| DC Coupled<br>Low-Level Input                       |                                          |                                    |                     | 4.5             | -    | -    | 1.35  | -       | 1.35   | -       | 1.35    | ٧     |

| Voltage                                             |                                          |                                    |                     | 6               | -    | -    | 1.8   | -       | 1.8    | -       | 1.8     | V     |

| PCP <sub>OUT</sub> , PCn OUT                        | V <sub>OH</sub>                          | V <sub>IL</sub> or V <sub>IH</sub> | -0.02               | 2               | 1.9  | -    | -     | 1.9     | -      | 1.9     | -       | V     |

| High-Level Output                                   |                                          |                                    |                     | 4.5             | 4.4  | -    | -     | 4.4     | -      | 4.4     | -       | V     |

| Voltage<br>CMOS Loads                               |                                          |                                    |                     | 6               | 5.9  | -    | -     | 5.9     | -      | 5.9     | -       | V     |

| PCP <sub>OUT</sub> , PCn OUT                        | V <sub>OH</sub>                          | V <sub>IL</sub> or V <sub>IH</sub> | -4                  | 4.5             | 3.98 | -    | -     | 3.84    | -      | 3.7     | -       | V     |

| High-Level Output<br>Voltage<br>TTL Loads           |                                          |                                    | -5.2                | 6               | 5.48 | -    | -     | 5.34    | -      | 5.2     | -       | V     |

| PCP <sub>OUT</sub> , PCn OUT                        | V <sub>OL</sub>                          | V <sub>IL</sub> or V <sub>IH</sub> | 0.02                | 2               | -    | -    | 0.1   | -       | 0.1    | -       | 0.1     | V     |

| Low-Level Output                                    |                                          |                                    |                     | 4.5             | -    | -    | 0.1   | -       | 0.1    | -       | 0.1     | V     |

| Voltage<br>CMOS Loads                               |                                          |                                    |                     | 6               | -    | -    | 0.1   | -       | 0.1    | -       | 0.1     | V     |

| PCP <sub>OUT</sub> , PCn OUT                        | V <sub>OL</sub>                          | V <sub>IL</sub> or V <sub>IH</sub> | 4                   | 4.5             | -    | -    | 0.26  | -       | 0.33   | -       | 0.4     | V     |

| Low-Level Output<br>Voltage<br>TTL Loads            |                                          |                                    | 5.2                 | 6               | -    | -    | 0.26  | -       | 0.33   | -       | 0.4     | V     |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> Input        | lı                                       | V <sub>CC</sub> or                 | -                   | 2               | -    | -    | ±3    | -       | ±4     | -       | ±5      | μА    |

| Leakage Current                                     |                                          | GND                                |                     | 3               | -    | -    | ±7    | -       | ±9     | -       | ±11     | μΑ    |

|                                                     |                                          |                                    |                     | 4.5             | -    | -    | ±18   | -       | ±23    | -       | ±29     | μΑ    |

|                                                     |                                          |                                    |                     | 6               | -    | -    | ±30   | -       | ±38    | -       | ±45     | μΑ    |

| PC2 <sub>OUT</sub> Three-State<br>Off-State Current | l <sub>OZ</sub>                          | V <sub>IL</sub> or V <sub>IH</sub> | -                   | 6               | -    | -    | ±0.5  | -       | ±5     | -       | ±10     | μА    |

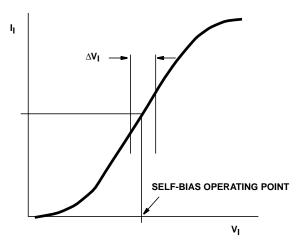

| SIG <sub>IN</sub> , COMP <sub>IN</sub> Input        | R <sub>I</sub>                           | V <sub>I</sub> at Se               |                     | 3               | -    | 800  | -     | -       | -      | -       | -       | kΩ    |

| Resistance                                          |                                          | Operatio $\Delta V_1 = 0$          |                     | 4.5             | -    | 250  | -     | -       | -      | -       | -       | kΩ    |

|                                                     | $\Delta V_{I} = 0.5V$ ,<br>See Figure 10 |                                    |                     | 6               | -    | 150  | -     | -       | -      | -       | -       | kΩ    |

| DEMODULATOR SEC                                     | TION                                     |                                    |                     |                 |      |      |       |         |        |         |         |       |

| Resistor Range                                      | R <sub>S</sub>                           | at R <sub>S</sub> >                |                     | 3               | 50   | -    | 300   | -       | -      | -       | -       | kΩ    |

|                                                     |                                          | Leakage<br>Can Infl                |                     | 4.5             | 50   | -    | 300   | -       | -      | -       | -       | kΩ    |

|                                                     |                                          | V <sub>DEM</sub>                   |                     | 6               | 50   | -    | 300   | -       | -      | -       | -       | kΩ    |

# DC Electrical Specifications (Continued)

|                                                                                     |                  | CONDI                                                                         |                                    | V <sub>CC</sub> |      | 25°C |             | -40°C 1 | го 85°C | -55°C T | O 125°C |      |

|-------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------|------------------------------------|-----------------|------|------|-------------|---------|---------|---------|---------|------|

| PARAMETER                                                                           | SYMBOL           | V <sub>I</sub> (V)                                                            | I <sub>O</sub> (mA)                | (S)             | MIN  | TYP  | MAX         | MIN     | MAX     | MIN     | MAX     | UNIT |

| Offset Voltage VCO <sub>IN</sub>                                                    | V <sub>OFF</sub> | $V_I = V_{VO}$                                                                | CO IN =                            | 3               | -    | ±30  | -           | -       | -       | -       | -       | mV   |

| to V <sub>DEM</sub>                                                                 |                  | V <sub>CC</sub>                                                               |                                    | 4.5             | -    | ±20  | -           | -       | -       | -       | -       | mV   |

|                                                                                     |                  | Values Tal<br>R <sub>S</sub> Ra<br>See Fig                                    | ange                               | 6               | -    | ±10  | -           | -       | -       | -       | -       | mV   |

| Dynamic Output                                                                      | R <sub>D</sub>   | VDEMO                                                                         | DUT =                              | 3               | -    | 25   | -           | -       | -       | -       | -       | Ω    |

| Resistance at DEM <sub>OUT</sub>                                                    |                  | V <sub>CC</sub>                                                               |                                    | 4.5             | -    | 25   | -           | -       | -       | -       | -       | Ω    |

| DEMIO01                                                                             |                  | _                                                                             |                                    | 6               | -    | 25   | -           | -       | -       | -       | -       | Ω    |

| Quiescent Device<br>Current                                                         | Icc              | Pins 3, 5<br>at V <sub>CC</sub> F<br>GND, I <sub>1</sub> a<br>and 14<br>exclu | Pin 9 at at Pins 3 to be           | 6               | -    | -    | 8           | -       | 80      | -       | 160     | μА   |

| HCT TYPES                                                                           | •                | •                                                                             |                                    |                 | •    | •    |             | •       |         |         | •       |      |

| VCO SECTION                                                                         |                  |                                                                               |                                    |                 |      |      |             |         |         |         |         |      |

| INH High Level Input<br>Voltage                                                     | V <sub>IH</sub>  | -                                                                             | -                                  | 4.5 to<br>5.5   | 2    | -    | -           | 2       | -       | 2       | -       | V    |

| INH Low Level Input<br>Voltage                                                      | V <sub>IL</sub>  | -                                                                             | -                                  | 4.5 to<br>5.5   | -    | -    | 0.8         | -       | 0.8     | -       | 0.8     | V    |

| VCO <sub>OUT</sub> High Level<br>Output Voltage<br>CMOS Loads                       | V <sub>OH</sub>  | V <sub>IH</sub> or V <sub>IL</sub>                                            | -0.02                              | 4.5             | 4.4  | -    | -           | 4.4     | -       | 4.4     | -       | V    |

| VCO <sub>OUT</sub> High Level<br>Output Voltage<br>TTL Loads                        |                  |                                                                               | -4                                 | 4.5             | 3.98 | -    | -           | 3.84    | -       | 3.7     | -       | ٧    |

| VCO <sub>OUT</sub> Low Level<br>Output Voltage<br>CMOS Loads                        | V <sub>OL</sub>  | V <sub>IH</sub> or V <sub>IL</sub>                                            | 0.02                               | 4.5             | -    | -    | 0.1         | -       | 0.1     | -       | 0.1     | V    |

| VCO <sub>OUT</sub> Low Level<br>Output Voltage<br>TTL Loads                         |                  |                                                                               | 4                                  | 4.5             | -    | -    | 0.26        | -       | 0.33    | -       | 0.4     | V    |

| C1A, C1B Low Level<br>Output Voltage<br>(Test Purposes Only)                        | V <sub>OL</sub>  | V <sub>IH</sub> or V <sub>IL</sub>                                            | 4                                  | 4.5             | -    | -    | 0.40        | -       | 0.47    | -       | 0.54    | ٧    |

| INH VCO <sub>IN</sub> Input<br>Leakage Current                                      | II               | Any Vo<br>Between '<br>GN                                                     | $V_{CC}$ and                       | 5.5             | -    |      | ±0.1        | -       | ±1      | -       | ±1      | μА   |

| R1 Range (Note 2)                                                                   | -                | -                                                                             | -                                  | 4.5             | 3    | -    | 300         | -       | -       | -       | -       | kΩ   |

| R2 Range (Note 2)                                                                   | -                | -                                                                             | -                                  | 4.5             | 3    | -    | 300         | -       | -       | -       | -       | kΩ   |

| C1 Capacitance<br>Range                                                             | -                | -                                                                             | -                                  | 4.5             | 0    | -    | No<br>Limit | -       | -       | -       | -       | pF   |

| VCO <sub>IN</sub> Operating<br>Voltage Range                                        | -                | Over the<br>specified f<br>Linearity So<br>10, and<br>(Note                   | for R1 for<br>ee Figure<br>34 - 37 | 4.5             | 1.1  | -    | 3.2         | -       | -       | -       | -       | V    |

| PHASE COMPARATO                                                                     | OR SECTION       | N                                                                             |                                    |                 | -    | -    | -           | -       |         | -       | •       | •    |

| SIG <sub>IN</sub> , COMP <sub>IN</sub><br>DC Coupled<br>High-Level Input<br>Voltage | V <sub>IH</sub>  | -                                                                             | -                                  | 4.5 to<br>5.5   | 2    | -    | -           | 2       | -       | 2       | -       | V    |

# DC Electrical Specifications (Continued)

|                                                                                    |                              | TES<br>CONDI                                                          |                     | Vcc           |      | 25°C |      | -40°C 1 | го 85°C | -55°C T | O 125°C | 4     |

|------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------|---------------------|---------------|------|------|------|---------|---------|---------|---------|-------|

| PARAMETER                                                                          | SYMBOL                       | V <sub>I</sub> (V)                                                    | I <sub>O</sub> (mA) | (V)           | MIN  | TYP  | MAX  | MIN     | MAX     | MIN     | MAX     | UNITS |

| SIG <sub>IN</sub> , COMP <sub>IN</sub><br>DC Coupled<br>Low-Level Input<br>Voltage | V <sub>IL</sub>              | -                                                                     | -                   | 4.5 to<br>5.5 | -    | -    | 0.8  | -       | 0.8     | -       | 0.8     | V     |

| PCP <sub>OUT</sub> , PCn OUT<br>High-Level Output<br>Voltage<br>CMOS Loads         | V <sub>OH</sub>              | V <sub>IL</sub> or V <sub>IH</sub>                                    | -                   | 4.5           | 4.4  | -    | -    | 4.4     | -       | 4.4     | -       | V     |

| PCP <sub>OUT</sub> , PCn OUT<br>High-Level Output<br>Voltage<br>TTL Loads          | V <sub>OH</sub>              | V <sub>IL</sub> or V <sub>IH</sub>                                    | -                   | 4.5           | 3.98 | -    | -    | 3.84    | -       | 3.7     | -       | V     |

| PCP <sub>OUT</sub> , PCn OUT<br>Low-Level Output<br>Voltage<br>CMOS Loads          | V <sub>OL</sub>              | V <sub>IL</sub> or V <sub>IH</sub>                                    | -                   | 4.5           | -    | -    | 0.1  | -       | 0.1     | -       | 0.1     | V     |

| PCP <sub>OUT</sub> , PCn OUT<br>Low-Level Output<br>Voltage<br>TTL Loads           | V <sub>OL</sub>              | V <sub>IL</sub> or V <sub>IH</sub>                                    | -                   | 4.5           | -    | -    | 0.26 | -       | 0.33    | -       | 0.4     | V     |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> Input<br>Leakage Current                    | I <sub>I</sub>               | Any<br>Voltage<br>Between<br>V <sub>CC</sub> and<br>GND               | -                   | 5.5           | -    | -    | ±30  |         | ±38     |         | ±45     | μА    |

| PC2 <sub>OUT</sub> Three-State<br>Off-State Current                                | l <sub>OZ</sub>              | V <sub>IL</sub> or V <sub>IH</sub>                                    | -                   | 5.5           | -    | -    | ±0.5 | ±5      | -       | -       | ±10     | μΑ    |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> Input<br>Resistance                         | R <sub>I</sub>               | V <sub>I</sub> at Se<br>Operatio<br>ΔV <sub>I</sub> = 0<br>See Fig    | n Point:<br>0.5V,   | 4.5           | -    | 250  | -    | -       | -       | -       | -       | kΩ    |

| DEMODULATOR SEC                                                                    | CTION                        |                                                                       |                     |               |      |      | _    |         |         |         |         |       |

| Resistor Range                                                                     | R <sub>S</sub>               | at R <sub>S</sub> ><br>Leakage<br>Can Infl<br>V <sub>DEM</sub>        | Current<br>uence    | 4.5           | 5    | -    | 300  | -       | -       | -       | -       | kΩ    |

| Offset Voltage VCO <sub>IN</sub> to V <sub>DEM</sub>                               | Voff                         | $V_{I} = V_{VC}$ $\frac{V_{CC}}{2}$ $Values tal$ $R_{S} Ra$ $See Fig$ | ken over<br>ange    | 4.5           | -    | ±20  | -    | -       | -       | -       | -       | mV    |

| Dynamic Output<br>Resistance at<br>DEM <sub>OUT</sub>                              | R <sub>D</sub>               | V <sub>DEM</sub> (                                                    | OUT =               | 4.5           | -    | 25   | -    | -       | -       | -       | -       | Ω     |

| Quiescent Device<br>Current                                                        | Icc                          | V <sub>CC</sub> or<br>GND                                             | -                   | 5.5           | -    | -    | 8    | -       | 80      | -       | 160     | μΑ    |

| Additional Quiescent<br>Device Current Per<br>Input Pin: 1 Unit Load               | ΔI <sub>CC</sub><br>(Note 4) | V <sub>CC</sub><br>-2.1<br>Excluding<br>Pin 5                         | -                   | 4.5 to<br>5.5 | -    | 100  | 360  | -       | 450     | -       | 490     | μА    |

- 2. The value for R1 and R2 in parallel should exceed 2.7k $\!\Omega.$

- 3. The maximum operating voltage can be as high as  $V_{CC}$  -0.9V, however, this may result in an increased offset voltage.

- 4. For dual-supply systems theoretical worst case ( $V_I$  = 2.4V,  $V_{CC}$  = 5.5V) specification is 1.8mA.

# **HCT Input Loading Table**

| INPUT | UNIT LOADS |

|-------|------------|

| INH   | 1          |

NOTE: Unit load is  $\Delta I_{CC}$  limit specific in DC Electrical Specifications Table, e.g., 360 $\mu$ A max. at 25 $^{o}$ C.

# **Switching Specifications** $C_L = 50pF$ , Input $t_r$ , $t_f = 6ns$

|                                                              |                                     | TEST                                 |                     |     | 25°C |     | -40°(<br>85 | С ТО<br>°С | -55°C TO<br>125°C |     |       |

|--------------------------------------------------------------|-------------------------------------|--------------------------------------|---------------------|-----|------|-----|-------------|------------|-------------------|-----|-------|

| PARAMETER                                                    | SYMBOL                              | CONDITIONS                           | V <sub>CC</sub> (V) | MIN | TYP  | MAX | MIN         | MAX        | MIN               | MAX | UNITS |

| HC TYPES                                                     |                                     |                                      |                     |     | •    | •   |             |            |                   | •   |       |

| PHASE COMPARATOR SECTI                                       | ON                                  |                                      |                     |     |      |     |             |            |                   |     |       |

| Propagation Delay                                            | t <sub>PLH</sub> , t <sub>PHL</sub> |                                      |                     |     |      |     |             |            |                   |     |       |

| $SIG_{IN}$ , $COMP_{IN}$ to $PCI_{OUT}$                      |                                     |                                      | 2                   | -   | -    | 200 | -           | 250        | -                 | 300 | ns    |

|                                                              |                                     |                                      | 4.5                 | -   | -    | 40  | -           | 50         | -                 | 60  | ns    |

|                                                              |                                     |                                      | 6                   | -   | -    | 34  | -           | 43         | -                 | 51  | ns    |

| $SIG_{IN}$ , $COMP_{IN}$ to $PCP_{OUT}$                      |                                     |                                      | 2                   | -   | -    | 300 | -           | 375        | -                 | 450 | ns    |

|                                                              |                                     |                                      | 4.5                 | -   | -    | 60  | -           | 75         | -                 | 90  | ns    |

|                                                              |                                     |                                      | 6                   | -   | -    | 51  | -           | 64         | -                 | 77  | ns    |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> to PC3 <sub>OUT</sub> |                                     |                                      | 2                   | -   | -    | 245 | -           | 305        | -                 | 307 | ns    |

|                                                              |                                     |                                      | 4.5                 | -   | -    | 49  | -           | 61         | -                 | 74  | ns    |

|                                                              |                                     |                                      | 6                   | -   | -    | 42  | -           | 52         | -                 | 63  | ns    |

| Output Transition Time                                       | t <sub>THL</sub> , t <sub>TLH</sub> |                                      | 2                   | -   | -    | 75  | -           | 95         | -                 | 110 | ns    |

|                                                              |                                     |                                      | 4.5                 | -   | -    | 15  | -           | 19         | -                 | 22  | ns    |

|                                                              |                                     |                                      | 6                   | -   | -    | 13  | -           | 16         | -                 | 19  | ns    |

| Output Enable Time, SIG <sub>IN</sub> ,                      | t <sub>PZH</sub> , t <sub>PZL</sub> |                                      | 2                   | -   | -    | 265 | -           | 330        | -                 | 400 | ns    |

| COMP <sub>IN</sub> to PC2 <sub>OUT</sub>                     |                                     |                                      | 4.5                 | ı   | -    | 53  | ı           | 66         | 1                 | 80  | ns    |

|                                                              |                                     |                                      | 6                   | ı   | -    | 45  | ı           | 56         | 1                 | 68  | ns    |

| Output Disable Time, SIG <sub>IN</sub> ,                     | t <sub>PHZ</sub> , t <sub>PLZ</sub> |                                      | 2                   | -   | -    | 315 | -           | 395        | -                 | 475 | ns    |

| COMP <sub>IN</sub> to PC2 <sub>OUT</sub>                     |                                     |                                      | 4.5                 | -   | -    | 63  | -           | 79         | -                 | 95  | ns    |

|                                                              |                                     |                                      | 6                   | -   | -    | 54  | -           | 67         | -                 | 81  | ns    |

| AC Coupled Input Sensitivity                                 |                                     | V <sub>I(P-P)</sub>                  | 3                   | -   | 11   | -   | -           | -          | -                 | -   | mV    |

| $(P-P)$ at $SIG_{IN}$ or $COMP_{IN}$                         |                                     |                                      | 4.5                 | -   | 15   | -   | -           | -          | -                 | -   | mV    |

|                                                              |                                     |                                      | 6                   | -   | 33   | -   | -           | -          | -                 | -   | mV    |

| VCO SECTION                                                  |                                     |                                      |                     |     |      |     |             |            |                   |     |       |

| Frequency Stability with                                     | Δf                                  | $R_1 = 100k\Omega$ ,                 | 3                   | -   | 0.11 | -   | -           | -          | -                 | -   | %/°C  |

| Temperature Change                                           | $\overline{\Delta}\overline{T}$     | R <sub>2</sub> = ∞                   | 4.5                 | -   | 0.11 | -   | -           | -          | -                 | -   | %/ºC  |

|                                                              |                                     |                                      | 6                   | -   | 0.11 | -   | -           | -          | -                 | -   | %/ºC  |

| Maximum Frequency                                            | f <sub>MAX</sub>                    | C <sub>1</sub> = 50pF                | 3                   | -   | 24   | -   | -           | -          | -                 | -   | MHz   |

|                                                              |                                     | $R_1 = 3.5k\Omega$<br>$R_2 = \infty$ | 4.5                 | -   | 24   | -   | -           | -          | -                 | -   | MHz   |

|                                                              |                                     | 2                                    | 6                   | -   | 24   | -   | -           | -          | -                 | -   | MHz   |

|                                                              |                                     | C <sub>1</sub> = 0pF                 | 3                   | -   | 38   | -   | -           | -          | -                 | -   | MHz   |

|                                                              |                                     | $R_1 = 9.1k\Omega$ $R_2 = \infty$    | 4.5                 | -   | 38   | -   | -           | -          | -                 | -   | MHz   |

|                                                              |                                     | · · · <b>Z</b>                       | 6                   | -   | 38   | -   | -           | -          | -                 | -   | MHz   |

# Switching Specifications $C_L = 50 pF$ , Input $t_r$ , $t_f = 6 ns$ (Continued)

|                                                                                  |                                        | TEST                                                              |                     |     | 25°C     |     | -40°(<br>85 |     |     | C TO<br>5°C |        |

|----------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------|---------------------|-----|----------|-----|-------------|-----|-----|-------------|--------|

| PARAMETER                                                                        | SYMBOL                                 | CONDITIONS                                                        | V <sub>CC</sub> (V) | MIN | TYP      | MAX | MIN         | MAX | MIN | MAX         | UNITS  |

| Center Frequency                                                                 |                                        | $C_1 = 40pF$                                                      | 3                   | 7   | 10       | -   | -           | -   | -   | -           | MHz    |

|                                                                                  |                                        | $R_1 = 3k\Omega$ $R_2 = \infty$                                   | 4.5                 | 12  | 17       | -   | -           | -   | -   | -           | MHz    |

|                                                                                  |                                        | VCO <sub>IN</sub> =<br>VCC/2                                      | 6                   | 14  | 21       | -   | -           | -   | -   | -           | MHz    |

| Frequency Linearity                                                              | $\Delta f_{VCO}$                       | $R_1 = 100k\Omega$                                                | 3                   | -   | 0.4      | -   | -           | -   | -   | -           | %      |

|                                                                                  |                                        | $R_2 = \infty$<br>$C_1 = 100pF$                                   | 4.5                 | -   | 0.4      | -   | -           | -   | -   | -           | %      |

|                                                                                  |                                        |                                                                   | 6                   | -   | 0.4      | -   | -           | -   | -   | -           | %      |

| Offset Frequency                                                                 |                                        | $R_2 = 220k\Omega$                                                | 3                   | -   | 400      | -   | -           | -   | -   | -           | kHz    |

|                                                                                  |                                        | C <sub>1</sub> = 1nF                                              | 4.5                 | -   | 400      | -   | -           | -   | -   | -           | kHz    |

|                                                                                  |                                        |                                                                   | 6                   | -   | 400      | -   | -           | -   | -   | -           | kHz    |

| DEMODULATOR SECTION                                                              | •                                      |                                                                   |                     |     |          |     |             |     |     |             |        |

| V <sub>OUT</sub> V <sub>S</sub> f <sub>IN</sub>                                  |                                        | $R_1 = 100k\Omega$                                                | 3                   | -   | -        | -   | -           | -   | -   | -           | mV/kHz |

|                                                                                  |                                        | $R_2 = \infty$ $C_1 = 100pF$                                      | 4.5                 | -   | 330      | -   | -           | -   | -   | -           | mV/kH  |

|                                                                                  |                                        | $R_S = 10k\Omega$<br>$R_3 = 100k\Omega$<br>$C_2 = 100pF$          | 6                   | ı   | -        | -   | -           | -   | -   | -           | mV/kHz |

| HCT TYPES                                                                        |                                        | -Z                                                                |                     |     | <u> </u> |     |             |     |     |             |        |

| PHASE COMPARATOR SECT                                                            | ION                                    |                                                                   |                     |     |          |     |             |     |     |             |        |

| Propagation Delay                                                                | t <sub>PHL</sub> , t <sub>PLH</sub>    |                                                                   |                     |     | <u> </u> |     |             |     |     | 1           |        |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> to PCI <sub>OUT</sub>                     | PHL, PLH                               | $C_L = 50pF$                                                      | 4.5                 | -   | -        | 45  | -           | 56  | -   | 68          | ns     |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> to PCP <sub>OUT</sub>                     | t <sub>PHL</sub> , t <sub>PLH</sub>    | C <sub>L</sub> = 50pF                                             | 4.5                 | -   | -        | 68  | -           | 85  | -   | 102         | ns     |

| SIG <sub>IN</sub> , COMP <sub>IN</sub> to PC3 <sub>OUT</sub>                     | t <sub>PHL</sub> , t <sub>PLH</sub>    | C <sub>L</sub> = 50pF                                             | 4.5                 | -   | -        | 58  | -           | 73  | -   | 87          | ns     |

| Output Transition Time                                                           | t <sub>TLH</sub> , t <sub>THL</sub>    | C <sub>L</sub> = 50pF                                             | 4.5                 | -   | -        | 15  | -           | 19  | -   | 22          | ns     |

| Output Enable Time, SIG <sub>IN</sub> , COMP <sub>IN</sub> to PC2 <sub>OUT</sub> | t <sub>PZH</sub> , t <sub>PZL</sub>    | C <sub>L</sub> = 50pF                                             | 4.5                 | -   | -        | 60  | -           | 75  | -   | 90          | pF     |

| Output Disable Time, $SIG_{IN}$ , $COMP_{IN}$ to $PCZ_{OUT}$                     | t <sub>PHZ</sub> , t <sub>PLZ</sub>    | C <sub>L</sub> = 50pF                                             | 4.5                 | -   | -        | 68  | -           | 85  | -   | 102         | pF     |

| AC Coupled Input Sensitivity (P-P) at SIGIN or COMPI                             |                                        | V <sub>I(P-P)</sub>                                               | 4.5                 | -   | 15       | -   | -           | -   | -   | -           | mV     |

| VCO SECTION                                                                      |                                        |                                                                   |                     |     |          |     |             |     |     |             |        |

| Frequency Stability with<br>Temperature Change                                   | $\frac{\Delta f}{\overline{\Delta T}}$ | $R_1 = 100k\Omega$ , $R_2 = \infty$                               | 4.5                 | -   | 0.11     | -   | -           | -   | -   | -           | %/ºC   |

| Maximum Frequency                                                                | f <sub>MAX</sub>                       | $C_1 = 50pF$ $R_1 = 3.5k\Omega$ $R_2 = \infty$                    | 4.5                 | -   | 24       | -   | -           | -   | -   | -           | MHz    |

|                                                                                  |                                        | $C_1 = 0pF$ $R_1 = 9.1k\Omega$ $R_2 = \infty$                     | 4.5                 | -   | 38       | -   | -           | -   | -   | -           | MHz    |

| Center Frequency                                                                 |                                        | $C_1 = 40pF$ $R_1 = 3k\Omega$ $R_2 = \infty$ $VCO_{IN} =$ $VCC/2$ | 4.5                 | 12  | 17       | -   | -           | -   | -   | -           | MHz    |

| Frequency Linearity                                                              | Δf <sub>VCO</sub>                      | $R_1 = 100k\Omega$ $R_2 = \infty$ $C_1 = 100pF$                   | 4.5                 | -   | 0.4      | -   | -           | -   | -   | -           | %      |

### Switching Specifications $C_L = 50pF$ , Input $t_r$ , $t_f = 6ns$ (Continued)

|                                                 | TEST   |                                                                                                    |                     | 25°C |     |     | -40°C TO<br>85°C |     | -55°C TO<br>125°C |     |        |  |

|-------------------------------------------------|--------|----------------------------------------------------------------------------------------------------|---------------------|------|-----|-----|------------------|-----|-------------------|-----|--------|--|

| PARAMETER                                       | SYMBOL | CONDITIONS                                                                                         | V <sub>CC</sub> (V) | MIN  | TYP | MAX | MIN              | MAX | MIN               | MAX | UNITS  |  |

| Offset Frequency                                |        | $R_2 = 220k\Omega$ $C_1 = 1nF$                                                                     | 4.5                 | -    | 400 | -   | -                | -   | -                 | -   | kHz    |  |

| DEMODULATOR SECTION                             |        |                                                                                                    |                     |      |     |     |                  |     |                   |     |        |  |

| V <sub>OUT</sub> V <sub>S</sub> f <sub>IN</sub> |        | $R_1 = 100k\Omega$ $R_2 = \infty$ $C_1 = 100pF$ $R_S = 10k\Omega$ $R_3 = 100k\Omega$ $C_2 = 100pF$ | 4.5                 | -    | 330 | -   | -                | -   | -                 | -   | mV/kHz |  |

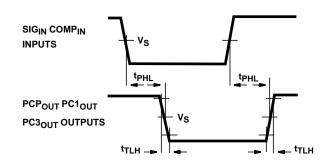

### Test Circuits and Waveforms

COMPIN INPUTS

COMPIN INPUTS

VS

VS

tpzH

PC2<sub>OUT</sub>

OUTPUT

VS

10%

FIGURE 8. INPUT TO OUTPUT PROPAGATION DELAYS AND OUTPUT TRANSITION TIMES

FIGURE 9. THREE STATE ENABLE AND DISABLE TIMES FOR  $\mathsf{PC2}_\mathsf{OUT}$

# **Typical Performance Curves**

FIGURE 10. TYPICAL INPUT RESISTANCE CURVE AT  $SIG_{IN}$ ,  $COMP_{IN}$

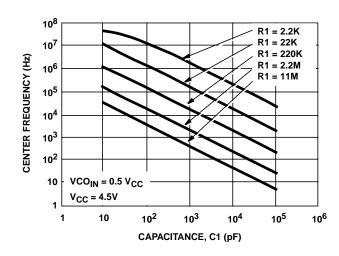

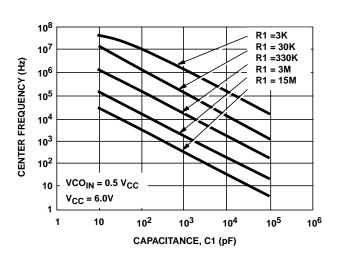

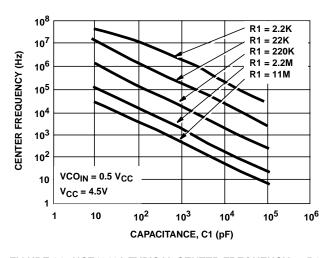

FIGURE 11. HC4046A TYPICAL CENTER FREQUENCY vs R1, C1 (V<sub>CC</sub> = 4.5V)

FIGURE 12. HC4046A TYPICAL CENTER FREQUENCY vs R1, C1 (V<sub>CC</sub> = 6V)

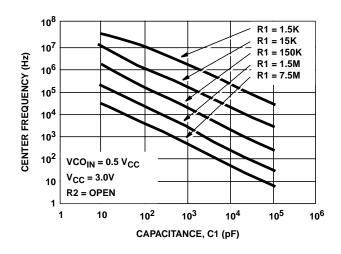

FIGURE 13. HC4046A TYPICAL CENTER FREQUENCY vs R1, C1 (V<sub>CC</sub> = 3V, R2 = OPEN)

FIGURE 14. HCT4046A TYPICAL CENTER FREQUENCY vs R1, C1 (V<sub>CC</sub> = 4.5V)

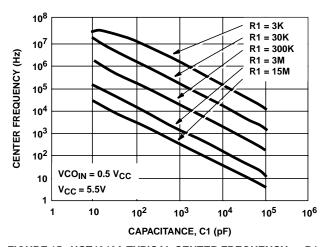

FIGURE 15. HCT4046A TYPICAL CENTER FREQUENCY vs R1, C1 ( $V_{CC} = 5.5V$ )

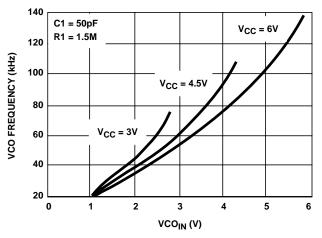

FIGURE 16. HC4046A TYPICAL VCO FREQUENCY vs VCO $_{\mbox{\scriptsize IN}}$  (R1 = 1.5M $_{\mbox{\scriptsize \Omega}}$ , C1 = 50pF)

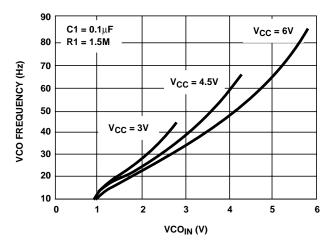

FIGURE 17. HC4046A TYPICAL VCO FREQUENCY vs VCO\_IN (R1 =  $1.5M\Omega$ , C1 =  $0.1\mu F$ )

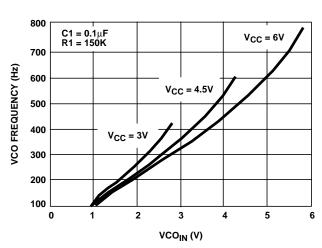

FIGURE 18. HC4046A TYPICAL VCO FREQUENCY vs VCO IN (R1 = 150k $\Omega$ , C1 = 0.1 $\mu$ F)

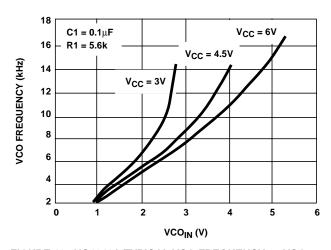

FIGURE 19. HC4046A TYPICAL VCO FREQUENCY vs VCO<sub>IN</sub>  $(R1 = 5.6k\Omega, C1 = 0.1\mu F)$

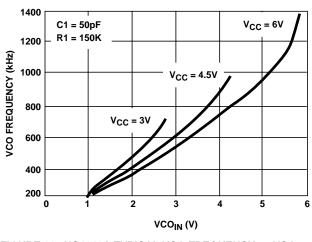

FIGURE 20. HC4046A TYPICAL VCO FREQUENCY vs VCO<sub>IN</sub>  $(R1 = 150k\Omega, C1 = 50pF)$

FIGURE 21. HC4046A TYPICAL VCO FREQUENCY vs VCO $_{IN}$  (R1 = 5.6k $\Omega$ , C1 = 50pF)

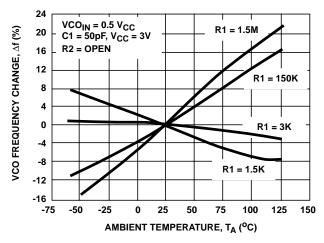

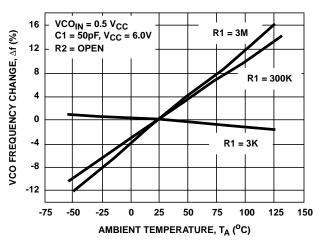

FIGURE 22. HC4046A TYPICAL CHANGE IN VCO FREQUENCY vs AMBIENT TEMPERATURE AS A FUNCTION OF R1 ( $V_{CC}$  = 3V)

FIGURE 23. HC4046A TYPICAL CHANGE IN VCO FREQUENCY VS AMBIENT TEMPERATURE AS A FUNCTION OF R1 (V<sub>CC</sub> = 4.5V)

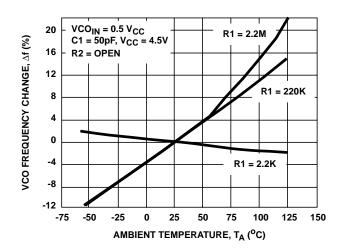

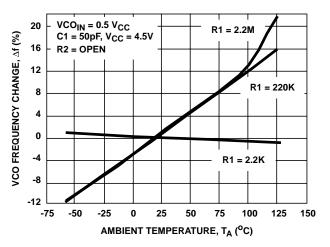

FIGURE 25. HCT4046A TYPICAL CHANGE IN VCO FREQUENCY vs AMBIENT TEMPERATURE AS A FUNCTION OF R1

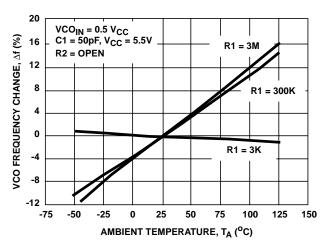

FIGURE 24. HC4046A TYPICAL CHANGE IN VCO FREQUENCY VS AMBIENT TEMPERATURE AS A FUNCTION OF R1 (V<sub>CC</sub> = 6V)

FIGURE 26. HC4046A TYPICAL CHANGE IN VCO FREQUENCY VS AMBIENT TEMPERATURE AS A FUNCTION OF R1 (V<sub>CC</sub> = 4.5V)

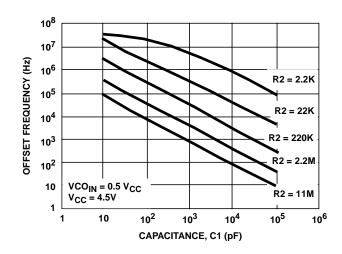

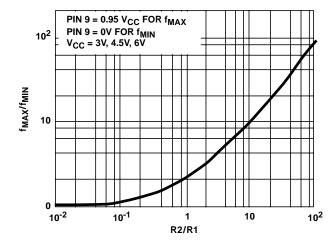

FIGURE 27. HC4046A OFFSET FREQUENCY vs R2, C1 ( $V_{CC} = 4.5V$ )

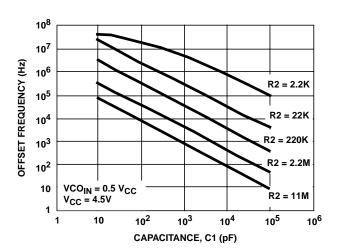

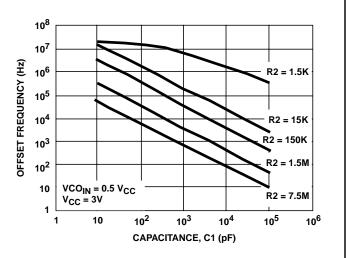

FIGURE 29. HCT4046A OFFSET FREQUENCY vs R2, C1  $(V_{CC} = 4.5V)$

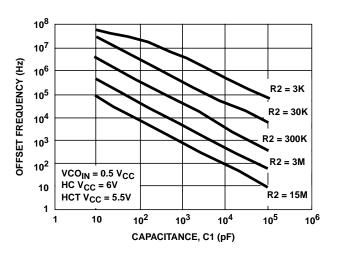

FIGURE 31. HC4046A  $f_{MIN}/f_{MAX}$  vs R2/R1 ( $V_{CC} = 3V, 4.5V, 6V$ )

FIGURE 28. HC4046A OFFSET FREQUENCY vs R2, C1 (V<sub>CC</sub> = 3V)

FIGURE 30. HC4046A AND HCT4046A OFFSET FREQUENCY vs R2, C1 ( $V_{CC}$  = 6V,  $V_{CC}$  = 5.5V)

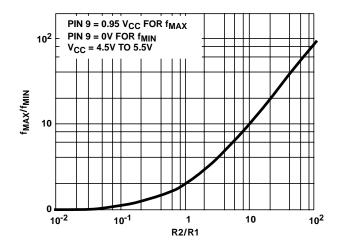

FIGURE 32. HCT4046A  $f_{MAX}/f_{MIN}$  vs R2/R1 ( $V_{CC} = 4.5V$  TO 5.5V)

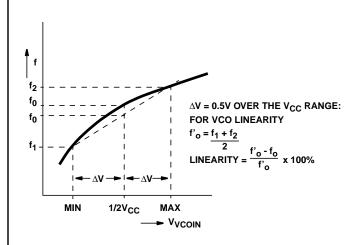

FIGURE 33. DEFINITION OF VCO FREQUENCY LINEARITY

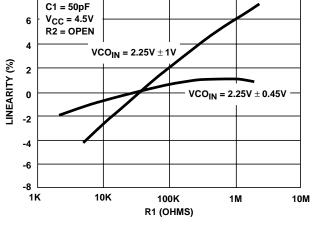

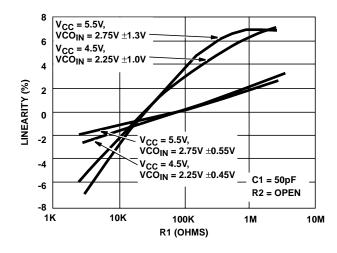

FIGURE 34. HC4046A VCO LINEARITY vs R1 (V<sub>CC</sub> = 4.5V)

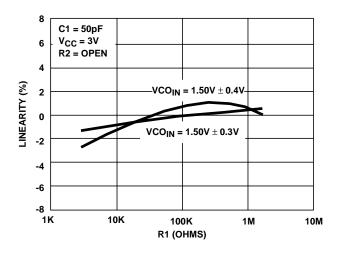

FIGURE 35. HC4046A VCO LINEARITY vs R1 (V<sub>CC</sub> = 3V)

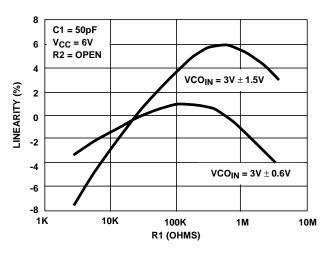

FIGURE 36. HC4046A VCO LINEARITY vs R1 (V<sub>CC</sub> = 6V)

FIGURE 37. HCT4046A VCO LINEARITY vs R1 ( $V_{CC}$  = 4.5V,  $V_{CC}$  = 5.5V)

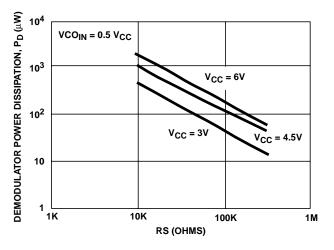

FIGURE 38. HC4046A DEMODULATOR POWER DISSIPATION vs RS (TYP) ( $V_{CC} = 3V, 4.5V, 6V$ )

FIGURE 39. HCT4046A DEMODULATOR POWER DISSIPATION vs RS (TYP) ( $V_{CC}$  = 3V, 4.5V, 6V)

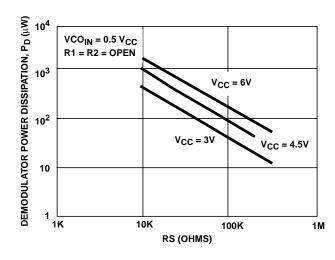

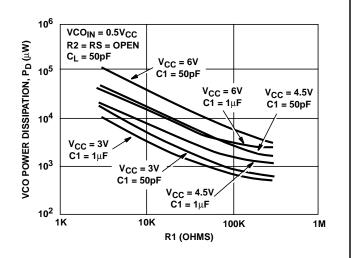

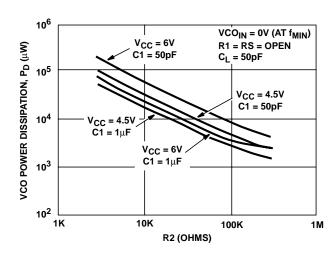

FIGURE 41. HCT4046A VCO POWER DISSIPATION vs R2 (C1 = 50pF,  $1\mu$ F)

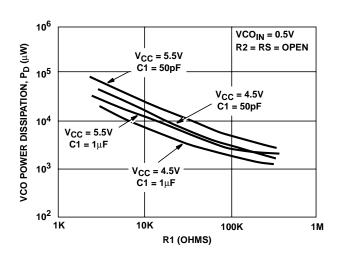

FIGURE 42. HCT4046A VCO POWER DISSIPATION vs R1 (C1 = 50pF,  $1\mu$ F)

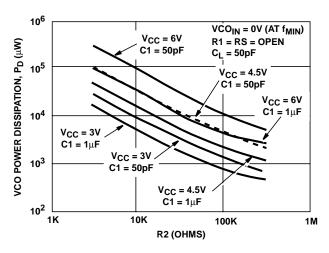

FIGURE 43. HC4046A VCO POWER DISSIPATION vs R2 (C1 = 50pF,  $1\mu$ F)

#### HC/HCT4046A CPD

| CHIP SECTION        | нс | нст | UNIT |

|---------------------|----|-----|------|

| Comparator 1        | 48 | 50  | pF   |

| Comparators 2 and 3 | 39 | 48  | pF   |

| vco                 | 61 | 53  | pF   |

**Application Information**

This information is a guide for the approximation of values of external components to be used with the 'HC4046A and 'HCT4046A in a phase-lock-loop system.

References should be made to Figures 11 through 15 and Figures 27 through 32 as indicated in the table.

Values of the selected components should be within the following ranges:

R1 Between  $3k\Omega$  and  $300k\Omega$ R2 Between  $3k\Omega$  and  $300k\Omega$ R1 + R2 Parallel Value >  $2.7k\Omega$ C1 Greater Than 40pF

| SUBJECT                               | PHASE<br>COMPARATOR | DESIGN CONSIDERATIONS                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| VCO Frequency<br>Without Extra Offset | PC1, PC2 or PC3     | VCO Frequency Characteristic With R2 = $\infty$ and R1 within the range 3kΩ < R1 < 300kΩ, the characteristics of the VCO operation will be as shown in Figures 11 - 15. (Due to R1, C1 time constant a small offset remains when R2 = $\infty$ .)   |  |  |  |  |  |  |  |

|                                       |                     | f <sub>MAX</sub>                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                       |                     | f <sub>vco</sub>                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                       |                     | f <sub>o</sub> 2f <sub>L</sub>                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                       |                     |                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                                       |                     | MIN 1/2 V <sub>CC</sub> V <sub>VCOIN</sub> MAX                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                       |                     | FIGURE 44. FREQUENCY CHARACTERISTIC OF VCO OPERATING WITHOUT OFFSET: f <sub>o</sub> = CENTER FREQUENCY: 2f <sub>L</sub> = FREQUENCY LOCK RANGE                                                                                                      |  |  |  |  |  |  |  |

|                                       | PC1                 | Selection of R1 and C1<br>Given f <sub>0</sub> , determine the values of R1 and C1 using Figures 11 - 15                                                                                                                                            |  |  |  |  |  |  |  |

|                                       | PC2 or PC3          | Given $f_{MAX}$ calculate $f_0$ as $f_{MAX}/2$ and determine the values of R1 and C1 using Figures 11 - 15. To obtain $2f_L$ : $2f_L \approx 1.2 \ (V_{CC} - 1.8V)/(R1C1)$ where valid range of $VCO_{IN}$ is $1.1V < VCO_{IN} < V_{CC} - 0.9V$     |  |  |  |  |  |  |  |

| VCO Frequency with<br>Extra Offset    | PC1, PC2 or PC3     | VCO Frequency Characteristic With R1 and R2 within the ranges $3k\Omega$ < R1 < $300k\Omega$ , $3k\Omega$ , < R2 < $300k\Omega$ , the characteristics of the VCO operation will be as shown in Figures 27 - 32.                                     |  |  |  |  |  |  |  |

|                                       |                     | f <sub>MAX</sub>                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                       |                     | fvco<br>f <sub>o</sub>                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                       |                     | f <sub>Min</sub>                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                       |                     |                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                                       |                     |                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                                       |                     | MIN 1/2 V <sub>CC</sub> V <sub>VCOIN</sub> MAX                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                       |                     | FIGURE 45. FREQUENCY CHARACTERISTIC OF VCO OPERATING WITH OFFSET: $f_0$ = CENTER FREQUENCY: $2f_L$ = FREQUENCY LOCK RANGE                                                                                                                           |  |  |  |  |  |  |  |

|                                       | PC1, PC2 or PC3     | Selection of R1, R2 and C1 Given $f_0$ and $f_L$ , offset frequency, $f_{MIN}$ , may be calculated from $f_{MIN} \approx f_0 - 1.6 f_L$ . Obtain the values of C1 and R2 by using Figures 27 - 30. Calculate the values of R1 from Figures 31 - 32. |  |  |  |  |  |  |  |

| SUBJECT                             | PHASE<br>COMPARATOR | DESIGN CONSIDERATIONS                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|-------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| PLL Conditions with                 | PC1                 | VCO adjusts to $f_0$ with $\phi_{DEMOUT} = 90^{\circ}$ and $V_{VCOIN} = 1/2 V_{CC}$ (see Figure 2)                                                                                                                            |  |  |  |  |  |  |  |

| No Signal at the                    | PC2                 | VCO adjusts to f <sub>MIN</sub> with $\phi_{DEMOUT}$ = -360° and $V_{VCOIN}$ = 0V (see Figure 4)                                                                                                                              |  |  |  |  |  |  |  |

| SIG <sub>IN</sub> Input             | PC3                 | VCO adjusts to $f_{MAX}$ with $\phi_{DEMOUT} = 360^{\circ}$ and $V_{VCOIN} = V_{CC}$ (see Figure 6)                                                                                                                           |  |  |  |  |  |  |  |

| PLL Frequency<br>Capture Range      | PC1, PC2 or PC3     | Loop Filter Component Selection                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                     |                     | R3 IF(j $\omega$ )  (A) $\tau$ = R3 x C2 (B) AMPLITUDE CHARACTERISTIC (C) POLE-ZERO DIAGRAM A small capture range (2f $_{\rm c}$ ) is obtained if $\tau$ > 2f $_{\rm c}$ $\approx$ 1/ $\pi$ (2 $\pi$ f $_{\rm c}$ / $\tau$ .) |  |  |  |  |  |  |  |