**DAC12DL3200** SBAS649B - JUNE 2021 - REVISED JUNE 2022

# DAC12DL3200 up to 6.4-GSPS Single-Channel or 3.2-GSPS Dual-Channel 12-bit Digital-to-Analog Converter (DAC) with Low-Latency LVDS Interface

#### 1 Features

- 12-bit resolution

- Maximum input and output sample rate:

- Single channel up to 6.4 GSPS

- Dual channel up to 3.2 GSPS

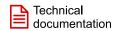

- Multi-Nyquist operating modes:

- Single channel modes: NRZ, RTZ, RF

- Dual channel modes: NRZ, RTZ, RF, 2xRF

- Low latency through device: 6 to 8 ns

- Matching transmit capabilities to the low latency receiver ADC12DL3200

- DAC and ADC combined latency < 15 ns (not</li> including FPGA)

- Parallel DDR LVDS interface:

- Source synchronous interface to simplify timing:

- 24 or 48 LVDS pairs up to 1.6 Gbps

- 1 LVDS DDR clock per 12-bit bus

- Output frequency range: > 8 GHz

- Full-scale current: 21 mA

- Simplified clocking and synchronization

- SYSREF windowing eases setup and hold

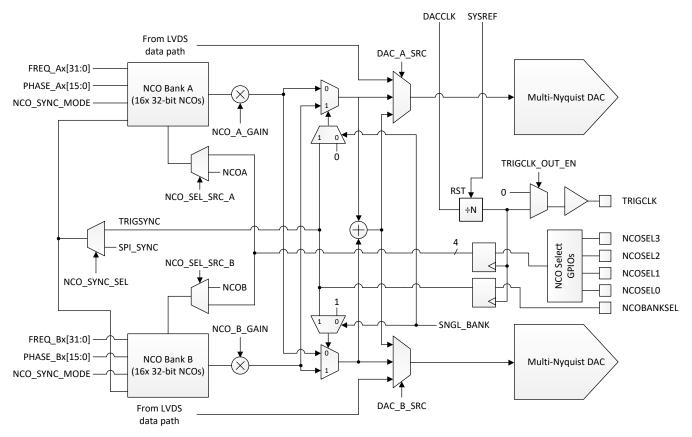

- On-chip direct digital synthesizer (DDS)

- Single-tone and two-tone sine wave generation

- 32 x 32-bit numerically controlled oscillators

- Fast frequency hopping capability (< 500 ns)</li>

- Synchronous CMOS frequency/phase input

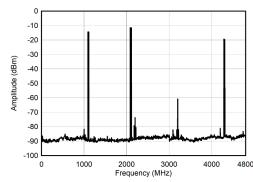

- Performance at f<sub>OUT</sub> = 4.703 GHz, 6.4 GSPS, RF

- Output power: -3 dBm

- Noise floor (70 MHz offset): –147 dBc/Hz

- SFDR: 60 dBc

- Power supplies: 1.0 V, 1.8 V, -1.8 V

- Power consumption: 1.49 W (2-ch, RF mode, 3.2

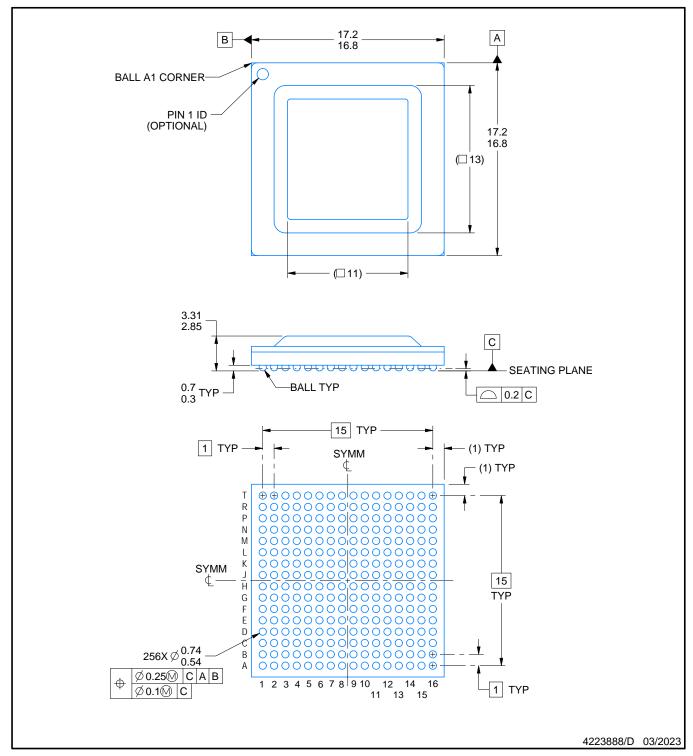

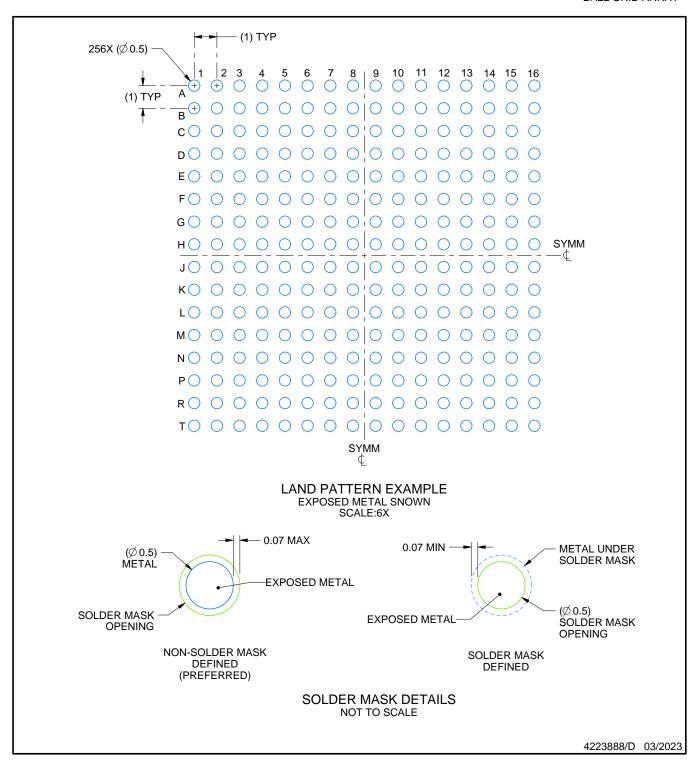

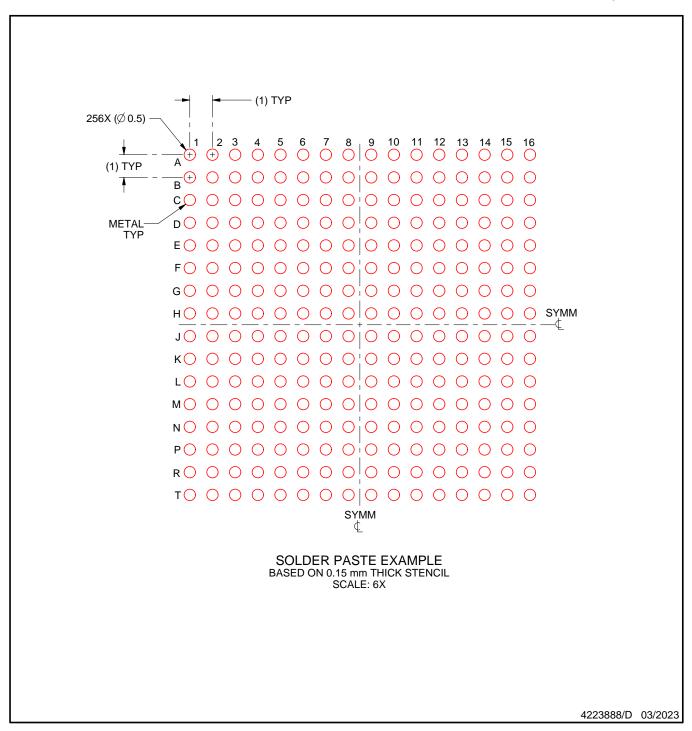

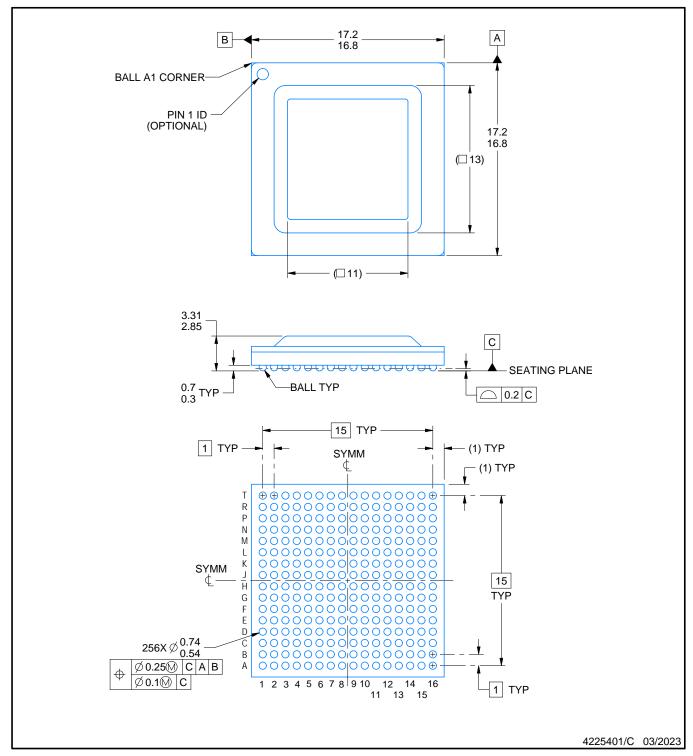

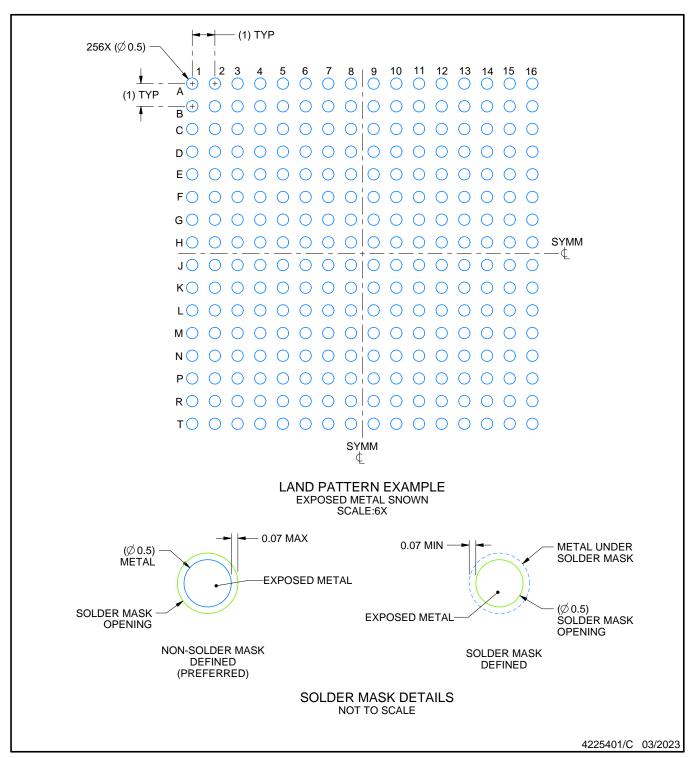

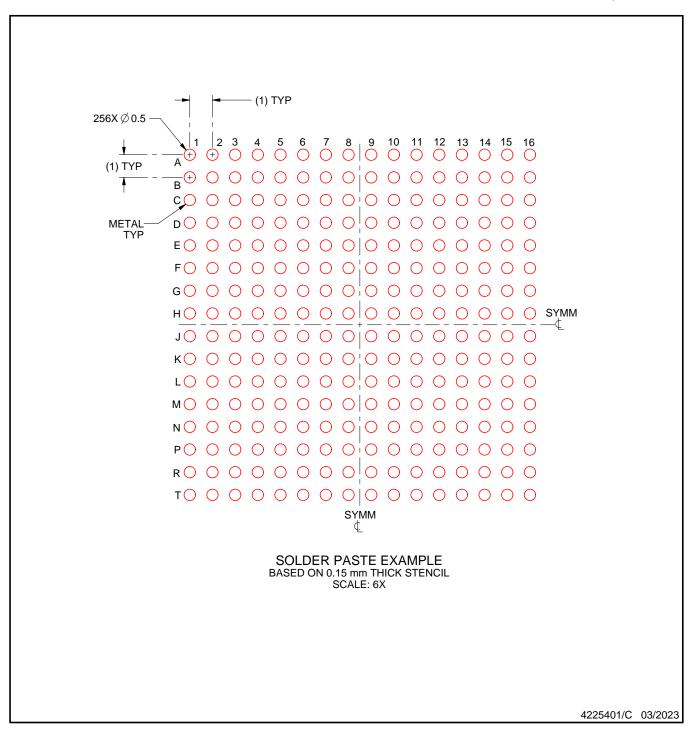

- Package: 256-Ball FCBGA (17x17 mm, 1 mm pitch)

#### 2 Applications

- Electronic warfare

- Generator: pulse, pattern and arbitrary waveform (AWG)

#### 3 Description

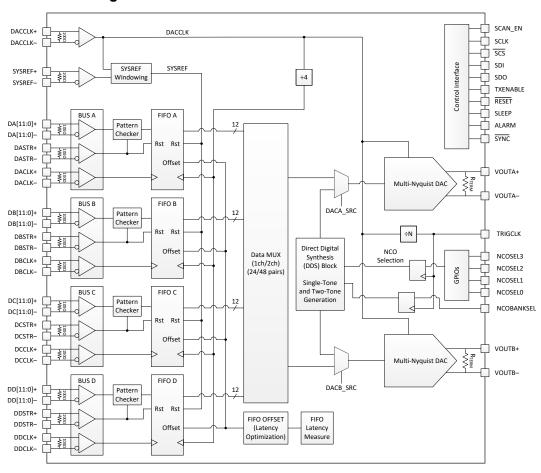

The DAC12DL3200 is a very low latency, dual channel, RF sampling digital-to-analog converter (DAC) capable of input and output rates of up to 3.2-GSPS in dual channel mode or 6.4-GSPS in single channel mode. The DAC can transmit signal bandwidths beyond 2 GHz at carrier frequencies approaching 8 GHz when using the multi-Nyquist output modes. The high output frequency range enables direct sampling through C-band (8 GHz) and beyond.

The DAC12DL3200 can be used as an I/Q baseband DAC in dual channel mode. The high sampling rate and output frequency range also makes the DAC12DL3200 capable of arbitrary waveform generation (AWG) and direct digital synthesis (DDS). An integrated DDS block enables single tone and two tone generation on chip.

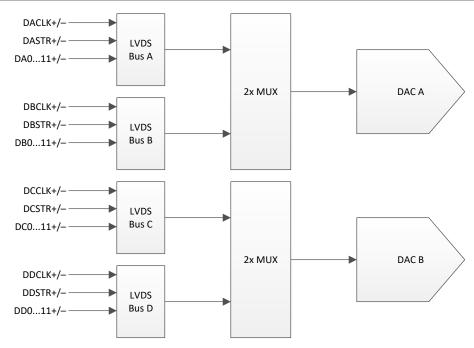

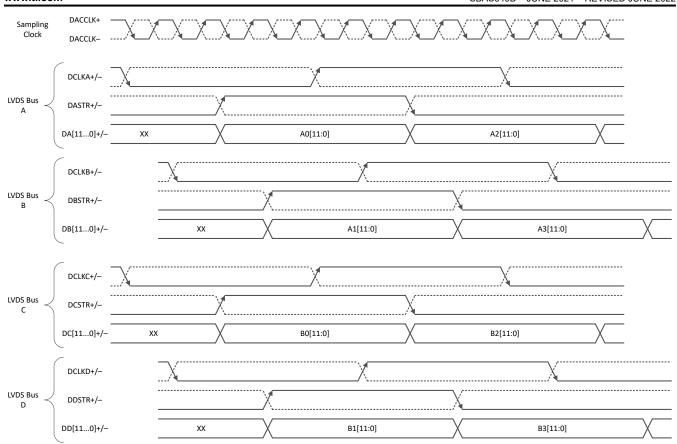

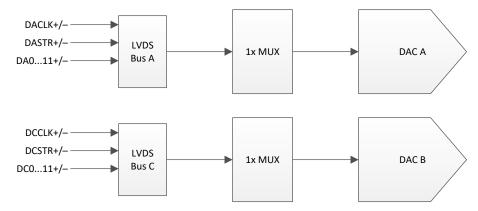

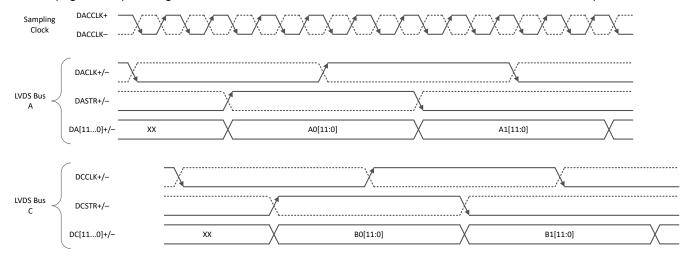

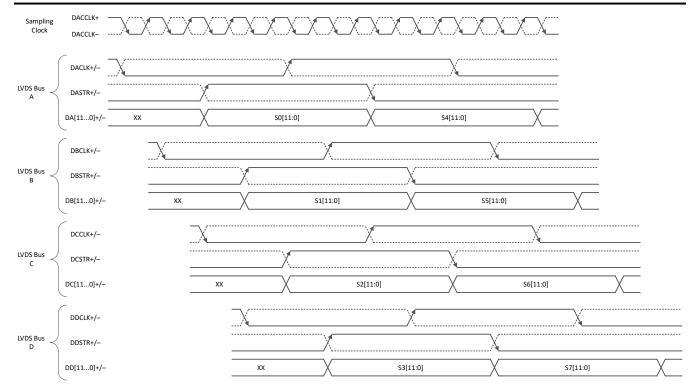

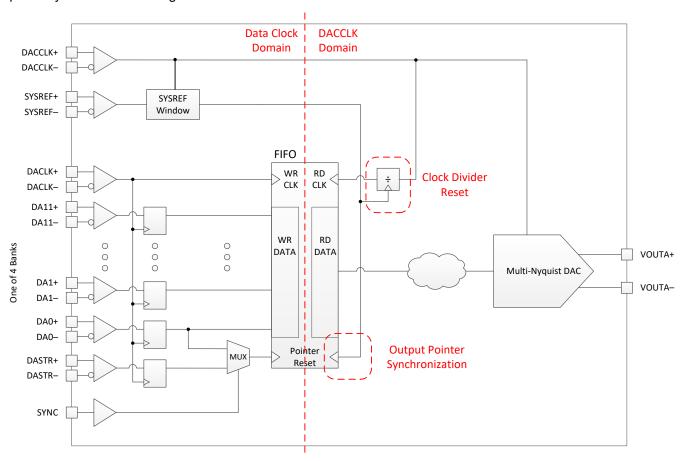

The DAC12DL3200 has a parallel LVDS interface that consists of up to 48 LVDS pairs and 4 DDR LVDS clocks. A strobe signal is used to synchronize the interface which can be sent over the least significant bit (LSB) or optionally over dedicated strobe LVDS lanes. Each LVDS pair is capable of up to 1.6 Gbps. Multi-device synchronization is supported using a synchronization signal (SYSREF) and is compatible with JESD204B/C clocking devices. SYSREF windowing eases synchronization in multidevice systems.

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM) |

|-------------|------------------------|-----------------|

| DAC12DL3200 | FCBGA (256)            | 17 mm x 17 mm   |

For all available packages, see the orderable addendum at the end of the data sheet.

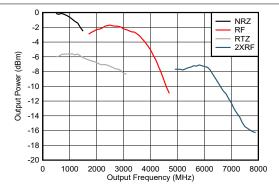

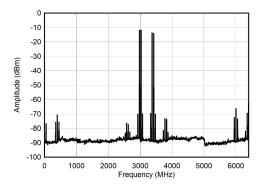

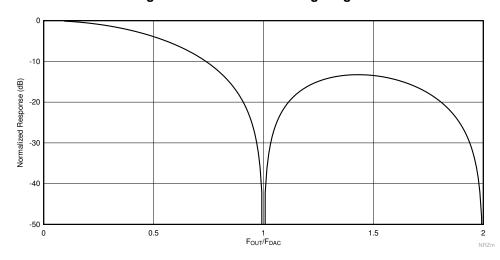

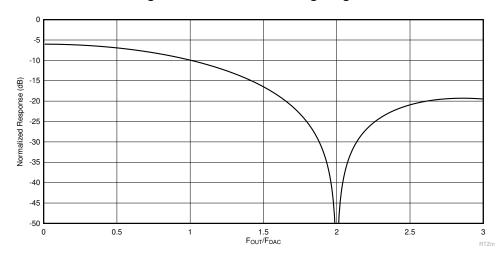

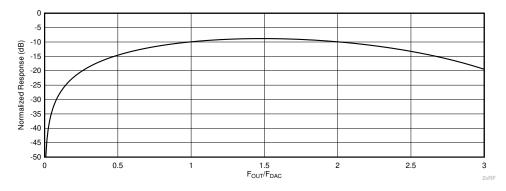

**Dual Channel Mode Frequency Response**

### **Table of Contents**

| 1 Features1                                           | 7.2 Functional Block Diagram                         | 53  |

|-------------------------------------------------------|------------------------------------------------------|-----|

| 2 Applications1                                       | 7.3 Feature Description                              |     |

| 3 Description1                                        | 7.4 Device Functional Modes                          |     |

| 4 Revision History2                                   | 7.5 Programming                                      | 73  |

| 5 Pin Configuration and Functions3                    | 8 Application and Implementation 1                   | 110 |

| 6 Specifications 11                                   | 8.1 Application Information1                         | 110 |

| 6.1 Absolute Maximum Ratings11                        | 8.2 Typical Application1                             |     |

| 6.2 ESD Ratings11                                     | 8.3 Power Supply Recommendations1                    |     |

| 6.3 Recommended Operating Conditions12                | 8.4 Layout 1                                         | 116 |

| 6.4 Thermal Information13                             | 9 Device and Documentation Support1                  | 21  |

| 6.5 Electrical Characteristics - DC Specifications14  | 9.1 Receiving Notification of Documentation Updates1 | 21  |

| 6.6 Electrical Characteristics - Power Consumption 16 | 9.2 Support Resources1                               | 21  |

| 6.7 Electrical Characteristics - AC Specifications 18 | 9.3 Trademarks1                                      | 21  |

| 6.8 Timing Requirements28                             | 9.4 Electrostatic Discharge Caution1                 | 21  |

| 6.9 Switching Characteristics29                       | 9.5 Glossary1                                        | 21  |

| 6.10 Typical Characteristics30                        | 10 Mechanical, Packaging, and Orderable              |     |

| 7 Detailed Description53                              | Information1                                         | 21  |

| 7.1 Overview53                                        |                                                      |     |

|                                                       |                                                      |     |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision A (October 2021) to Revision B (June 2022)                                          | Page            |

|---|----------------------------------------------------------------------------------------------------------|-----------------|

|   | Added the Trigger Clock section                                                                          |                 |

| • | Deleted text Streaming mode can be disabled by setting the ADDR_HOLD bit from the Streaming Mode section |                 |

| • | Changed the description of Bit 2 in SYS_ALM Register Field Descriptions                                  | <mark>74</mark> |

| • | Changed the description of Bit 1 in FIFO_ALIGN Register Field Descriptions                               | 74              |

| С | hanges from Revision * (June 2021) to Revision A (October 2021)                                          | Page            |

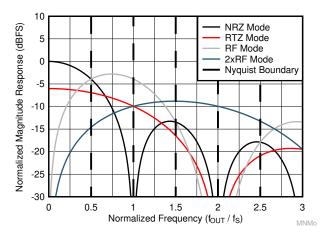

### 5 Pin Configuration and Functions

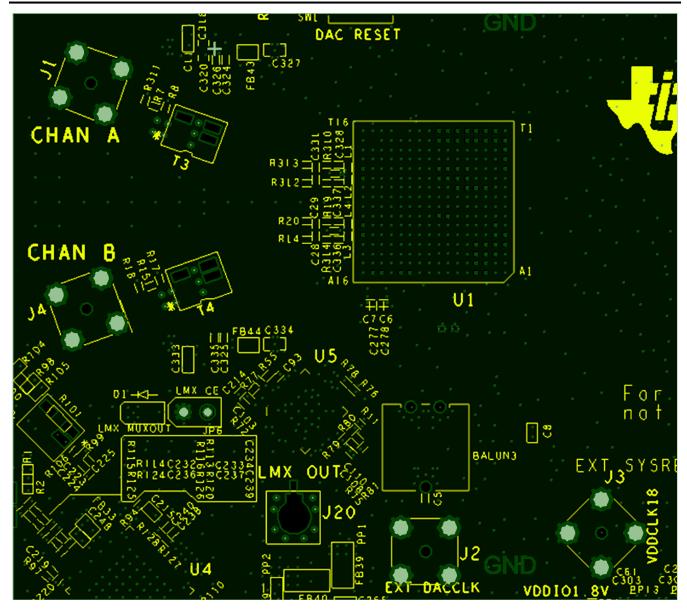

### ACF, 256 Ball FCBGA, Top View

#### Table 5-1. Pin Functions

| PIN   |                                                                                                                  | 1/0 | I/O DESCRIPTION                                                                                                                                                                          |  |

|-------|------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME  | NO.                                                                                                              | 1/0 | DESCRIPTION                                                                                                                                                                              |  |

| AGND  | D14, D15,<br>D16, E15,<br>F15, G15,<br>G16, K15,<br>K16, L15,<br>M15, N13,<br>N14, N15,<br>N16, P15,<br>P16, T16 | _   | Analog supply ground, must be directly connected to DGND and VSSCLK                                                                                                                      |  |

| ALARM | P14                                                                                                              | 0   | ALARM pin is asserted when an internal unmasked alarm is detected. Alarm mask is set by ALM_MASK register.                                                                               |  |

| ATEST | R15                                                                                                              | 0   | Analog test pin. Can be left disconnected if not used.                                                                                                                                   |  |

| CLK+  | A15                                                                                                              | I   | Device clock input positive terminal. There is an internal 100-Ω differential termination between CLK+ and CLK–. This input is self-biased and should be AC coupled to the clock source. |  |

| CLK-  | A14                                                                                                              | I   | Device clock input negative terminal. See CLK+ description.                                                                                                                              |  |

| PIN      |    |     | Table 5-1. Pin Functions (continued)                                                                                                                                                                            |  |  |

|----------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |    | I/O | DESCRIPTION                                                                                                                                                                                                     |  |  |

| DA0+     | L5 | I   | LVDS bus A bit 0 data input positive terminal. There is an internal 100-Ω differential termination between DA0+ and DA0                                                                                         |  |  |

| DA0-     | M5 | I   | LVDS bus A bit 0 data input negative terminal. There is an internal $100-\Omega$ differential termination between DA0+ and DA0                                                                                  |  |  |

| DA1+     | L6 | I   | LVDS bus A bit 1 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DA1+ and DA1                                                                                 |  |  |

| DA1–     | M6 | I   | LVDS bus A bit 1 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA1+ and DA1                                                                                 |  |  |

| DA10+    | R7 | I   | LVDS bus A bit 10 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DA10+ and DA10                                                                              |  |  |

| DA10-    | T7 | I   | LVDS bus A bit 10 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA10+ and DA10                                                                              |  |  |

| DA11+    | R8 | I   | LVDS bus A bit 11 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DA11+ and DA11–.                                                                            |  |  |

| DA11-    | Т8 | I   | LVDS bus A bit 11 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA11+ and DA11–.                                                                            |  |  |

| DA2+     | L7 | I   | LVDS bus A bit 2 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DA2+ and DA2–.                                                                               |  |  |

| DA2-     | M7 | I   | LVDS bus A bit 2 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA2+ and DA2–.                                                                               |  |  |

| DA3+     | L8 | I   | LVDS bus A bit 3 data input positive terminal. There is an internal $100-\Omega$ differential termination between DA3+ and DA3                                                                                  |  |  |

| DA3-     | M8 | I   | LVDS bus A bit 3 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA3+ and DA3–.                                                                               |  |  |

| DA4+     | N5 | I   | LVDS bus A bit 4 data input positive terminal. There is an internal $100-\Omega$ differential termination between DA4+ and DA4–.                                                                                |  |  |

| DA4–     | P5 | I   | LVDS bus A bit 4 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA4+ and DA4–.                                                                               |  |  |

| DA5+     | N6 | I   | LVDS bus A bit 5 data input positive terminal. There is an internal $100-\Omega$ differential termination between DA5+ and DA5                                                                                  |  |  |

| DA5–     | P6 | I   | LVDS bus A bit 5 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA5+ and DA5–.                                                                               |  |  |

| DA6+     | N7 | I   | LVDS bus A bit 6 data input positive terminal. There is an internal $100-\Omega$ differential termination between DA6+ and DA6                                                                                  |  |  |

| DA6-     | P7 | I   | LVDS bus A bit 6 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA6+ and DA6                                                                                 |  |  |

| DA7+     | N8 | I   | LVDS bus A bit 7 data input positive terminal. There is an internal 100-Ω differential termination between DA7+ and DA7–.                                                                                       |  |  |

| DA7-     | P8 | I   | LVDS bus A bit 7 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DA7+ and DA7–.                                                                               |  |  |

| DA8+     | R5 | I   | LVDS bus A bit 8 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DA8+ and DA8–.                                                                               |  |  |

| DA8-     | T5 | I   | LVDS bus A bit 8 data input negative terminal. There is an internal 100-Ω differential termination between DA8+ and DA8                                                                                         |  |  |

| DA9+     | R6 | I   | LVDS bus A bit 9 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DA9+ and DA9–.                                                                               |  |  |

| DA9-     | Т6 | I   | LVDS bus A bit 9 data input negative terminal. There is an internal 100-Ω differential termination between DA9+ and DA9                                                                                         |  |  |

| DACLK+   | K8 | I   | LVDS bus A data clock positive terminal. A DDR data clock is applied to DACLK+/– to capture the DA[11:0]+/– and DASTR+/– inputs. There is an internal 100-Ω differential termination between DACLK+ and DACLK–. |  |  |

| DACLK-   | K7 | I   | LVDS bus A data clock negative terminal. See DACLK+ description.                                                                                                                                                |  |  |

| PIN    |     |     | Table 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| DASTR+ | K6  | I   | LVDS bus A strobe positive terminal. DASTR+/– is used to synchronize the input pointer of the interface FIFO by marking a specific sample on each LVDS bus. DAx+/– can optionally be used for this purpose instead to reduce the number of LVDS pairs, where x = (12 - LVDS_RESOLUTION). There is an internal $100-\Omega$ differential termination between DASTR+ and DASTR |  |  |

| DASTR- | K5  | I   | LVDS bus A strobe negative terminal. See DASTR+ description.                                                                                                                                                                                                                                                                                                                 |  |  |

| DB0+   | K1  | I   | LVDS bus B bit 0 data input positive terminal. There is an internal 100-Ω differential termination between DB0+ and DB0                                                                                                                                                                                                                                                      |  |  |

| DB0-   | L1  | I   | LVDS bus B bit 0 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB0+ and DB0                                                                                                                                                                                                                                               |  |  |

| DB1+   | L2  | I   | LVDS bus B bit 1 data input positive terminal. There is an internal 100-Ω differential termination between DB1+ and DB1                                                                                                                                                                                                                                                      |  |  |

| DB1-   | M2  | I   | LVDS bus B bit 1 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB1+ and DB1                                                                                                                                                                                                                                               |  |  |

| DB10+  | R3  | I   | LVDS bus B bit 10 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DB10+ and DB10                                                                                                                                                                                                                                           |  |  |

| DB10-  | ТЗ  | I   | LVDS bus B bit 10 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB10+ and DB10                                                                                                                                                                                                                                            |  |  |

| DB11+  | R4  | I   | LVDS bus B bit 11 data input positive terminal. There is an internal $100-\Omega$ differential termination between DB11+ and DB11                                                                                                                                                                                                                                            |  |  |

| DB11-  | T4  | I   | LVDS bus B bit 11 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB11+ and DB11                                                                                                                                                                                                                                            |  |  |

| DB2+   | L3  | I   | LVDS bus B bit 2 data input positive terminal. There is an internal 100-Ω differential termination between DB2+ and DB2                                                                                                                                                                                                                                                      |  |  |

| DB2-   | M3  | I   | LVDS bus B bit 2 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB2+ and DB2                                                                                                                                                                                                                                               |  |  |

| DB3+   | L4  | I   | LVDS bus B bit 3 data input positive terminal. There is an internal 100-Ω differential termination between DB3+ and DB3                                                                                                                                                                                                                                                      |  |  |

| DB3-   | M4  | I   | LVDS bus B bit 3 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DB3+ and DB3                                                                                                                                                                                                                                              |  |  |

| DB4+   | M1  | I   | LVDS bus B bit 4 data input positive terminal. There is an internal 100-Ω differential termination between DB4+ and DB4–.                                                                                                                                                                                                                                                    |  |  |

| DB4-   | N1  | I   | LVDS bus B bit 4 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB4+ and DB4                                                                                                                                                                                                                                               |  |  |

| DB5+   | N2  | I   | LVDS bus B bit 5 data input positive terminal. There is an internal 100-Ω differential termination between DB5+ and DB5–.                                                                                                                                                                                                                                                    |  |  |

| DB5-   | P2  | I   | LVDS bus B bit 5 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DB5+ and DB5                                                                                                                                                                                                                                              |  |  |

| DB6+   | N3  | I   | LVDS bus B bit 6 data input positive terminal. There is an internal 100-Ω differential termination between DB6+ and DB6                                                                                                                                                                                                                                                      |  |  |

| DB6-   | P3  | I   | LVDS bus B bit 6 data input negative terminal. There is an internal $100-\Omega$ differential termination between DB6+ and DB6                                                                                                                                                                                                                                               |  |  |

| DB7+   | N4  | I   | LVDS bus B bit 7 data input positive terminal. There is an internal 100-Ω differential termination between DB7+ and DB7                                                                                                                                                                                                                                                      |  |  |

| DB7-   | P4  | I   | LVDS bus B bit 7 data input negative terminal. There is an internal 100-Ω differential termination between DB7+ and DB7                                                                                                                                                                                                                                                      |  |  |

| DB8+   | P1  | I   | LVDS bus B bit 8 data input positive terminal. There is an internal 100-Ω differential termination between DB8+ and DB8–.                                                                                                                                                                                                                                                    |  |  |

| DB8-   | R1  | I   | LVDS bus B bit 8 data input negative terminal. There is an internal 100-Ω differential termination between DB8+ and DB8–.                                                                                                                                                                                                                                                    |  |  |

| DB9+   | R2  | I   | LVDS bus B bit 9 data input positive terminal. There is an internal 100-Ω differential termination between DB9+ and DB9–.                                                                                                                                                                                                                                                    |  |  |

| PIN    |     |     | Table 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| DB9-   | T2  | I   | LVDS bus B bit 9 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DB9+ and DB9                                                                                                                                                                                                                                                |  |  |

| DBCLK+ | K4  | I   | LVDS bus B data clock positive terminal. A DDR data clock is applied to DBCLK+/– to capture the DB[11:0]+/– and DBSTR+/– inputs. There is an internal 100-Ω differential termination between DBCLK+ and DBCLK–.                                                                                                                                                                |  |  |

| DBCLK- | K3  | I   | LVDS bus B data clock negative terminal. See DBCLK+ description.                                                                                                                                                                                                                                                                                                               |  |  |

| DBSTR+ | J2  | I   | LVDS bus B strobe positive terminal. DBSTR+/– is used to synchronize the input pointer of the interface FIFO by marking a specific sample on each LVDS bus. DBx+/– can optionally be used for this purpose instead to reduce the number of LVDS pairs, where x = (12 - LVDS_RESOLUTION). There is an internal $100-\Omega$ differential termination between DBSTR+ and DBSTR–. |  |  |

| DBSTR- | J1  | I   | LVDS bus B strobe negative terminal. See DBSTR+ description.                                                                                                                                                                                                                                                                                                                   |  |  |

| DC0+   | F5  | I   | LVDS bus C bit 0 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DC0+ and DC0                                                                                                                                                                                                                                                |  |  |

| DC0-   | E5  | I   | LVDS bus C bit 0 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DC0+ and DC0                                                                                                                                                                                                                                                |  |  |

| DC1+   | F6  | I   | LVDS bus C bit 1 data input positive terminal. There is an internal $100-\Omega$ differential termination between DC1+ and DC1                                                                                                                                                                                                                                                 |  |  |

| DC1-   | E6  | I   | LVDS bus C bit 1 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DC1+ and DC1                                                                                                                                                                                                                                                |  |  |

| DC10+  | В7  | I   | LVDS bus C bit 10 data input positive terminal. There is an internal $100-\Omega$ differential termination between DC10+ and DC10                                                                                                                                                                                                                                              |  |  |

| DC10-  | A7  | I   | LVDS bus C bit 10 data input negative terminal. There is an internal 100-Ω differential termination between DC10+ and DC10                                                                                                                                                                                                                                                     |  |  |

| DC11+  | B8  | I   | LVDS bus C bit 11 data input positive terminal. There is an internal 100-Ω differential termination between DC11+ and DC11                                                                                                                                                                                                                                                     |  |  |

| DC11-  | A8  | I   | LVDS bus C bit 11 data input negative terminal. There is an internal $100-\Omega$ differential termination between DC11+ and DC11                                                                                                                                                                                                                                              |  |  |

| DC2+   | F7  | I   | LVDS bus C bit 2 data input positive terminal. There is an internal 100-Ω differential termination between DC2+ and DC2                                                                                                                                                                                                                                                        |  |  |

| DC2-   | E7  | I   | LVDS bus C bit 2 data input negative terminal. There is an internal 100-Ω differential termination between DC2+ and DC2                                                                                                                                                                                                                                                        |  |  |

| DC3+   | F8  | I   | LVDS bus C bit 3 data input positive terminal. There is an internal 100-Ω differential termination between DC3+ and DC3                                                                                                                                                                                                                                                        |  |  |

| DC3-   | E8  | I   | LVDS bus C bit 3 data input negative terminal. There is an internal 100-Ω differential termination between DC3+ and DC3                                                                                                                                                                                                                                                        |  |  |

| DC4+   | D5  | I   | LVDS bus C bit 4 data input positive terminal. There is an internal 100-Ω differential termination between DC4+ and DC4                                                                                                                                                                                                                                                        |  |  |

| DC4-   | C5  | I   | LVDS bus C bit 4 data input negative terminal. There is an internal $100-\Omega$ differential termination between DC4+ and DC4                                                                                                                                                                                                                                                 |  |  |

| DC5+   | D6  | I   | LVDS bus C bit 5 data input positive terminal. There is an internal 100-Ω differential termination between DC5+ and DC5–.                                                                                                                                                                                                                                                      |  |  |

| DC5-   | C6  | I   | LVDS bus C bit 5 data input negative terminal. There is an internal $100-\Omega$ differential termination between DC5+ and DC5                                                                                                                                                                                                                                                 |  |  |

| DC6+   | D7  | I   | LVDS bus C bit 6 data input positive terminal. There is an internal 100-Ω differential termination between DC6+ and DC6–.                                                                                                                                                                                                                                                      |  |  |

| DC6-   | C7  | I   | LVDS bus C bit 6 data input negative terminal. There is an internal $100-\Omega$ differential termination between DC6+ and DC6                                                                                                                                                                                                                                                 |  |  |

| DC7+   | D8  | I   | LVDS bus C bit 7 data input positive terminal. There is an internal 100-Ω differential termination between DC7+ and DC7                                                                                                                                                                                                                                                        |  |  |

| DC7-   | C8  | I   | LVDS bus C bit 7 data input negative terminal. There is an internal 100-Ω differential termination between DC7+ and DC7                                                                                                                                                                                                                                                        |  |  |

| PIN    |     |     | Table 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                           |  |

|--------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |

| DC8+   | B5  | ı   | LVDS bus C bit 8 data input positive terminal. There is an internal 100-Ω differential termination between DC8+ and DC8–.                                                                                                                                                                                                                                                      |  |

| DC8-   | A5  | I   | LVDS bus C bit 8 data input negative terminal. There is an internal 100-Ω differential termination between DC8+ and DC8–.                                                                                                                                                                                                                                                      |  |

| DC9+   | В6  | ı   | LVDS bus C bit 9 data input positive terminal. There is an internal 100-Ω differential termination between DC9+ and DC9–.                                                                                                                                                                                                                                                      |  |

| DC9-   | A6  | I   | LVDS bus C bit 9 data input negative terminal. There is an internal $100-\Omega$ differential termination between DC9+ and DC9                                                                                                                                                                                                                                                 |  |

| DCCLK+ | G8  | I   | LVDS bus C data clock positive terminal. A DDR data clock is applied to DCCLK+/– to capture the DC[11:0]+/– and DCSTR+/– inputs. There is an internal 100-Ω differential termination between DCCLK+ and DCCLK–.                                                                                                                                                                |  |

| DCCLK- | G7  | I   | LVDS bus C data clock negative terminal. See DCCLK+ description.                                                                                                                                                                                                                                                                                                               |  |

| DCSTR+ | G6  | I   | LVDS bus C strobe positive terminal. DCSTR+/– is used to synchronize the input pointer of the interface FIFO by marking a specific sample on each LVDS bus. DCx+/– can optionally be used for this purpose instead to reduce the number of LVDS pairs, where x = (12 - LVDS_RESOLUTION). There is an internal $100-\Omega$ differential termination between DCSTR+ and DCSTR–. |  |

| DCSTR- | G5  | 1   | LVDS bus C strobe negative terminal. See DCSTR+ description.                                                                                                                                                                                                                                                                                                                   |  |

| DD0+   | G1  | I   | LVDS bus D bit 0 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD0+ and DD0                                                                                                                                                                                                                                                 |  |

| DD0-   | F1  | I   | LVDS bus D bit 0 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD0+ and DD0                                                                                                                                                                                                                                                |  |

| DD1+   | F2  | I   | LVDS bus D bit 1 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD1+ and DD1                                                                                                                                                                                                                                                 |  |

| DD1-   | E2  | I   | LVDS bus D bit 1 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD1+ and DD1                                                                                                                                                                                                                                                |  |

| DD10+  | В3  | 1   | LVDS bus D bit 10 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD10+ and DD10                                                                                                                                                                                                                                              |  |

| DD10-  | А3  | I   | LVDS bus D bit 10 data input negative terminal. There is an internal $100-\Omega$ differential termination between DD10+ and DD10                                                                                                                                                                                                                                              |  |

| DD11+  | B4  | ı   | LVDS bus D bit 11 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DD11+ and DD11                                                                                                                                                                                                                                             |  |

| DD11-  | A4  | ı   | LVDS bus D bit 11 data input negative terminal. There is an internal $100-\Omega$ differential termination between DD11+ and DD11                                                                                                                                                                                                                                              |  |

| DD2+   | F3  | I   | LVDS bus D bit 2 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD2+ and DD2                                                                                                                                                                                                                                                 |  |

| DD2-   | E3  | I   | LVDS bus D bit 2 data input negative terminal. There is an internal $100-\Omega$ differential termination between DD2+ and DD2                                                                                                                                                                                                                                                 |  |

| DD3+   | F4  | I   | LVDS bus D bit 3 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD3+ and DD3                                                                                                                                                                                                                                                 |  |

| DD3-   | E4  | I   | LVDS bus D bit 3 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD3+ and DD3                                                                                                                                                                                                                                                |  |

| DD4+   | E1  | I   | LVDS bus D bit 4 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DD4+ and DD4                                                                                                                                                                                                                                                |  |

| DD4–   | D1  | I   | LVDS bus D bit 4 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD4+ and DD4                                                                                                                                                                                                                                                |  |

| DD5+   | D2  | I   | LVDS bus D bit 5 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD5+ and DD5                                                                                                                                                                                                                                                 |  |

| DD5-   | C2  | I   | LVDS bus D bit 5 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD5+ and DD5                                                                                                                                                                                                                                                |  |

| DD6+   | D3  | I   | LVDS bus D bit 6 data input positive terminal. There is an internal $100-\Omega$ differential termination between DD6+ and DD6                                                                                                                                                                                                                                                 |  |

| PIN            |                                                                                                                  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | NAME NO.                                                                                                         |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| DD6-           | C3                                                                                                               | I   | LVDS bus D bit 6 data input negative terminal. There is an internal $100-\Omega$ differential termination between DD6+ and DD6                                                                                                                                                                                                                                                 |  |  |

| DD7+           | D4                                                                                                               | I   | LVDS bus D bit 7 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DD7+ and DD7                                                                                                                                                                                                                                                |  |  |

| DD7-           | C4                                                                                                               | I   | LVDS bus D bit 7 data input negative terminal. There is an internal $100-\Omega$ differential termination between DD7+ and DD7                                                                                                                                                                                                                                                 |  |  |

| DD8+           | C1                                                                                                               | I   | LVDS bus D bit 8 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DD8+ and DD8                                                                                                                                                                                                                                                |  |  |

| DD8-           | B1                                                                                                               | I   | LVDS bus D bit 8 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD8+ and DD8–.                                                                                                                                                                                                                                              |  |  |

| DD9+           | B2                                                                                                               | I   | LVDS bus D bit 9 data input positive terminal. There is an internal 100- $\Omega$ differential termination between DD9+ and DD9–.                                                                                                                                                                                                                                              |  |  |

| DD9-           | A2                                                                                                               | I   | LVDS bus D bit 9 data input negative terminal. There is an internal 100- $\Omega$ differential termination between DD9+ and DD9–.                                                                                                                                                                                                                                              |  |  |

| DDCLK+         | G4                                                                                                               | I   | LVDS bus D data clock positive terminal. A DDR data clock is applied to DDCLK+/– to capture the DD[11:0]+/– and DDSTR+/– inputs. There is an internal 100- $\Omega$ differential termination between DDCLK+ and DDCLK–.                                                                                                                                                        |  |  |

| DDCLK-         | G3                                                                                                               | I   | LVDS bus D data clock negative terminal. See DDCLK+ description.                                                                                                                                                                                                                                                                                                               |  |  |

| DDSTR+         | H2                                                                                                               | I   | LVDS bus D strobe positive terminal. DDSTR+/– is used to synchronize the input pointer of the interface FIFO by marking a specific sample on each LVDS bus. DDx+/– can optionally be used for this purpose instead to reduce the number of LVDS pairs, where x = (12 - LVDS_RESOLUTION). There is an internal $100-\Omega$ differential termination between DDSTR+ and DDSTR–. |  |  |

| DDSTR-         | H1                                                                                                               | I   | LVDS bus D strobe negative terminal. See DDSTR+ description.                                                                                                                                                                                                                                                                                                                   |  |  |

| DGND           | A1, A9, B9,<br>D10, E9, F10,<br>G2, G9, H10,<br>H5, H6, H7,<br>H8, J3, J4,<br>J9, K10, K2,<br>L9, M10, N9,<br>T1 | _   | Digital supply ground, must be directly connected to AGND and VSSCLK                                                                                                                                                                                                                                                                                                           |  |  |

| EXTIO          | T15                                                                                                              | 0   | Reference voltage output. Requires a 0.1 µF decoupling capacitor to AGND.                                                                                                                                                                                                                                                                                                      |  |  |

| NCOBANKSE<br>L | P11                                                                                                              | I   | Used to select the NCO bank updated by NCOSEL[0:3] inputs (0=A, 1=B). It is also possible to update both banks at once, in which case NCOBANKSEL can be used as a 5 <sup>th</sup> bit to effectively have 32 different NCO accumulators. Latched by TRIGCLK. Internal pulldown.                                                                                                |  |  |

| NCOSEL0        | Т9                                                                                                               | I   | Bit 0 of NCOSEL. Internal pulldown.                                                                                                                                                                                                                                                                                                                                            |  |  |

| NCOSEL1        | R9                                                                                                               | I   | Bit 1 of NCOSEL. Internal pulldown.                                                                                                                                                                                                                                                                                                                                            |  |  |

| NCOSEL2        | T10                                                                                                              | I   | Bit 2 of NCOSEL. Internal pulldown.                                                                                                                                                                                                                                                                                                                                            |  |  |

| NCOSEL3        | R10                                                                                                              | I   | Bit 3 of NCOSEL. Internal pulldown.                                                                                                                                                                                                                                                                                                                                            |  |  |

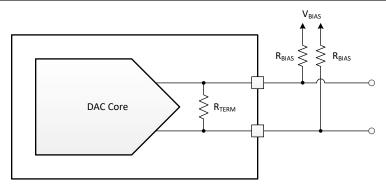

| RBIAS          | R16                                                                                                              | 0   | Full-scale output current bias is set by the resistor tied from this terminal to AGND. A $3.6\text{-k}\Omega$ resistor is expected for 20.5 mA full scale output with default settings. The full-scale output current can be adjusted using the SPI interface by programming the COARSE_CUR_A/B and FINE_CUR_A/B register settings.                                            |  |  |

| RESET          | T12                                                                                                              | I   | Device reset input, active low. Must be toggled after power up and application of a stable clock. Internal pullup.                                                                                                                                                                                                                                                             |  |  |

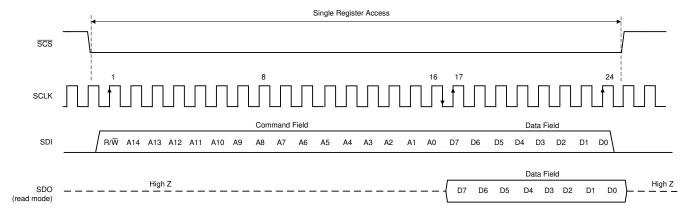

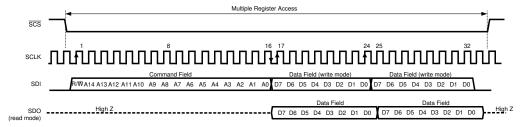

| SCLK           | T13                                                                                                              | I   | Serial programming interface (SPI) clock input. Internal pulldown.                                                                                                                                                                                                                                                                                                             |  |  |

| SCS            | T14                                                                                                              | I   | Serial programming interface (SPI) device select input, active low. Internal pullup.                                                                                                                                                                                                                                                                                           |  |  |

| SDI            | R14                                                                                                              | I   | Serial programming interface (SPI) data input. Internal pulldown.                                                                                                                                                                                                                                                                                                              |  |  |

| SDO            | R13                                                                                                              | 0   | Serial programming interface (SPI) data output. High-Z when not outputting SPI data.                                                                                                                                                                                                                                                                                           |  |  |

| SLEEP          | R12                                                                                                              | I   | Device sleep control. The device changes to the mode specified by the SLEEP_CFG register when high. Internal pulldown.                                                                                                                                                                                                                                                         |  |  |

| PIN      |                                                                                 |     | lable 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------|---------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |                                                                                 | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| SYNC     | R11                                                                             | I   | Allows data LSB to be used as the LVDS sync input. Internal pullup. Has SPI register override: LSB_SYNC.                                                                                                                                                                                                                                                                                                  |  |  |

| SYSREF+  | A11                                                                             | I   | System timing reference (SYSREF) input positive terminal. This input is used to synchronize internal clock dividers and the LVDS interface FIFO output pointer. SYSREF+/– and data interface strobes must be used to achieve deterministic latency through the device. There is an internal $100-\Omega$ differential termination between SYSREF+ and SYSREF–. This input is self-biased when AC coupled. |  |  |

| SYSREF-  | A12                                                                             | I   | System timing reference (SYSREF) input negative terminal. See SYSREF+ description.                                                                                                                                                                                                                                                                                                                        |  |  |

| SCAN_EN  | P13                                                                             | I   | This pin is used for factory testing. Connect to ground for normal operation. Internal pulldown.                                                                                                                                                                                                                                                                                                          |  |  |

| TRIGCLK  | P12                                                                             | 0   | Trigger clock output. Rising edge latches NCOBANKSEL and NCOSEL[3:0].                                                                                                                                                                                                                                                                                                                                     |  |  |

| TXENABLE | T11                                                                             | I   | Transmit enable active high input. This pin must be enabled using register <u>TXEN_SEL</u> . The DAC output is forced to midcode (0x0000 in 2's complement) when transmission is disabled. Internal pullup.                                                                                                                                                                                               |  |  |

| VDDA     | H15, J15                                                                        | I   | 1.0-V supply voltage for internal reference. Must be separate from VDDDIG for best performance.                                                                                                                                                                                                                                                                                                           |  |  |

| VDDA18A  | J16                                                                             | I   | 1.8-V supply voltage for DAC channel A. Can be combined with VDDA18B, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                                                                                                                                               |  |  |

| VDDA18B  | H16                                                                             | ı   | 1.8-V supply voltage for DAC channel B. Can be combined with VDDA18A, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                                                                                                                                               |  |  |

| VDDCLK10 | D13, F13,<br>H13, J13, L13                                                      | I   | 1.0-V supply voltage for internal sampling clock distribution path. Noise or spurs on this supply may degrade phase noise performance. Recommended to separate from VDDDIG and VDDA for best performance.                                                                                                                                                                                                 |  |  |

| VDDCLK18 | B14, B15                                                                        | I   | 1.8-V supply voltage for clock (CLK+/–) input buffer. Noise or spurs on this supply may degrade phase noise performance.                                                                                                                                                                                                                                                                                  |  |  |

| VDDDIG   | D9, E10, F9,<br>G10, H3, H4,<br>H9, J10, J5,<br>J6, J7, J8, K9,<br>L10, M9, N10 | ı   | 1.0-V supply voltage for digital block and LVDS input receivers. Recommended to separate from VDDA and VDDCLK for best performance.                                                                                                                                                                                                                                                                       |  |  |

| VDDEA    | J11, K11, L11,<br>M11, N11                                                      | I   | 1.0-V supply voltage for channel A DAC encoder. Can be combined with VDDEB.                                                                                                                                                                                                                                                                                                                               |  |  |

| VDDEB    | D11, E11,<br>F11, G11, H11                                                      | I   | 1.0-V supply voltage for channel B DAC encoder. Can be combined with VDDEA.                                                                                                                                                                                                                                                                                                                               |  |  |

| VDDHAF   | C14, C15                                                                        | I   | 1.0-V supply voltage. Can be combined with VDDCLK10. Noise or spurs on this supply may degrade phase noise performance.                                                                                                                                                                                                                                                                                   |  |  |

| VDDIO    | P9, P10                                                                         | I   | 1.8-V supply for CMOS input and output terminals.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| VDDL2A   | J12, J14                                                                        | I   | 1.0-V supply for DAC analog latch for channel A. Separate from VDDL2B for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance.                                                                                                                                                                                                                                  |  |  |

| VDDL2B   | H12, H14                                                                        | I   | 1.0-V supply for DAC analog latch for channel B. Separate from VDDL2A for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance.                                                                                                                                                                                                                                  |  |  |

| VDDSYS18 | C11, C12                                                                        | I   | 1.8-V supply voltage for SYSREF (SYSREF+/–) input buffer. Can be combined with VDDCLK18 when SYSREF is disabled during normal operation. This supply should be separate from VDDCLK18 when SYSREF is run continuously during operation to avoid noise and spur coupling and reduced phase noise performance.                                                                                              |  |  |

| VEEAM18  | L14, M14                                                                        | ı   | -1.8-V supply voltage for DAC current source bias for channel A. Can be combined with VEEBM18, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                                                                                                                      |  |  |

| VEEBM18  | E14, F14                                                                        | I   | -1.8-V supply voltage for DAC current source bias for channel B. Can be combined with<br>VEEAM18, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                                                                                                                   |  |  |

| VOUTA+   | M16                                                                             | 0   | DAC channel A analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                                                                                                                                                                                                                                  |  |  |

| VOUTA-   | L16                                                                             | 0   | DAC channel A analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                                                                                                                                                                                                                                  |  |  |

| Р      | PIN                                                                                                                           |   |                                                                                                                                          |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NAME NO.                                                                                                                      |   | DESCRIPTION                                                                                                                              |  |  |

| VOUTB+ | E16                                                                                                                           | 0 | DAC channel B analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. |  |  |

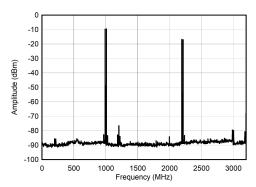

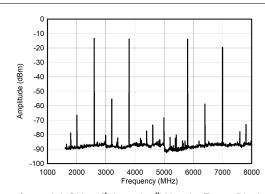

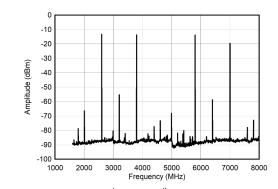

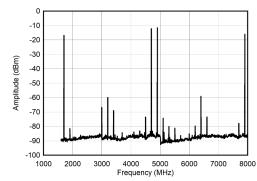

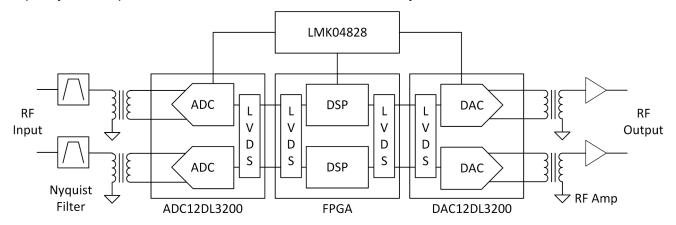

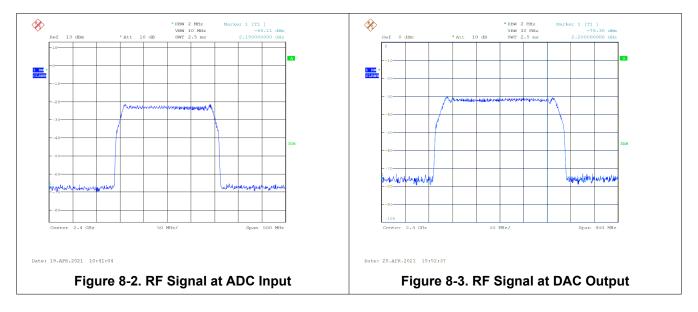

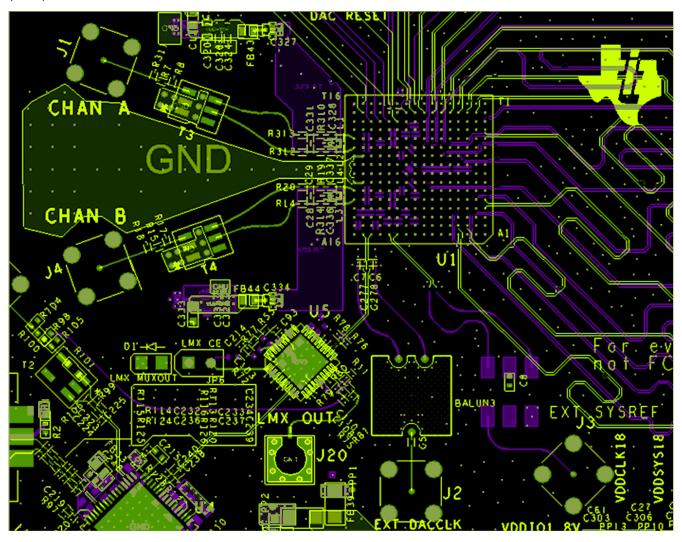

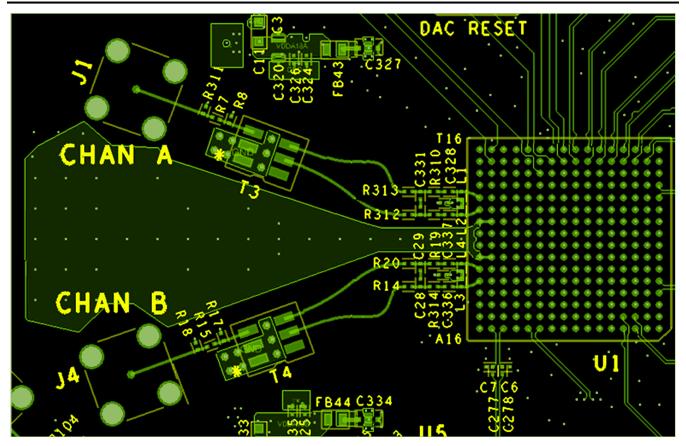

| VOUTB- | F16                                                                                                                           | 0 | DAC channel B analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. |  |  |