# Sensor Signal Conditioning IC for Closed-Loop Magnetic Current Sensors

Check for Samples: DRV411

# **FEATURES**

- Optimized for Symmetric Hall-Elements (for example, AKM HW-322, HW-302, or similar)

- Spinning Current Hall Sensor Excitation

- Elimination of Hall Sensor Offset and Drift

- Elimination of 1/f Noise

- Extended Current Measurement Range

- H-Bridge Drive Capability: 250 mA

- Precision Difference Amplifier:

- Offset and Drift: 100 μV (max), 2 μV/°C (max)

- System Bandwidth: 200 kHz

- Precision Reference:

- Accuracy: 0.2% (max)Drift: 50 ppm/°C (max)

- Pin-Selectable for 2.5 V, 1.65 V, and Ratiometric Mode

- Overrange and Error Flags

- Supply: 2.7 V to 5.5 V

- Packages: 4-mm x 4-mm QFN and TSSOP-20 PowerPAD™

- Temperature Range: –40°C to +125°C

# **DESCRIPTION**

The DRV411 is designed to condition InSb Hall elements for use in closed-loop current-sensor modules. The DRV411 provides precision excitation circuitry for the Hall-element effectively eliminating the offset and offset-drift of the Hall element. This device also provides a 250-mA H-bridge for driving the sensor compensation coil as well a precision differential amplifier to generate the output signal. The 250-mA drive capability of the H-bridge roughly doubles the current measurement range compared to conventional single-ended drive methods.

The Hall sensor front-end circuit and the differential amplifier employ proprietary offset cancelling techniques. These techniques, along with a high-accuracy voltage reference, significantly improve the accuracy of the overall current-sensor module. The output voltage is pin-selectable to support a 2.5-V output for use with a 5-V power supply, as well as 1.65-V for 3.3-V sensors.

For optimum heat dissipation, the DRV411 is available in thermally enhanced 4-mm × 4-mm QFN and TSSOP-20 with PowerPAD packages. The DRV411 is specified for operation over the full extended industrial temperature range of -40°C to +125°C.

# **APPLICATIONS**

- Closed-Loop Current-Sensor Modules

- DC and AC Current Measurement

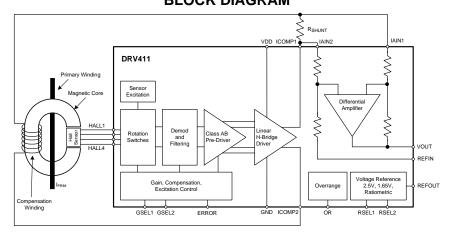

# **BLOCK DIAGRAM**

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# PACKAGE INFORMATION(1)

(1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet, or visit the device product folder at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range (unless otherwise noted).

|                                             |                                                                 | VALUE     | VALUE     |      |  |

|---------------------------------------------|-----------------------------------------------------------------|-----------|-----------|------|--|

|                                             |                                                                 | MIN       | MAX       | UNIT |  |

| Supply voltage (VDD to GND)                 |                                                                 |           | +7        | V    |  |

| Input voltage (2)                           |                                                                 | GND - 0.5 | VDD + 0.5 | V    |  |

| Differential amplifier in                   | nputs                                                           | GND – 6   | VDD + 6   | V    |  |

| Input current to input                      | terminals <sup>(3)</sup>                                        | -25       | -25 +25   |      |  |

| ICOMP short circuit (4)                     |                                                                 |           | 300       | mA   |  |

| Junction temperature,                       | T <sub>J</sub> max                                              | -50       | +150      | °C   |  |

| Storage temperature i                       | range, T <sub>stg</sub>                                         | -65       | +150      | °C   |  |

|                                             | Human body model (HBM) JEDEC standard 22, test method A114-C.01 | -2000     | +2000     | V    |  |

| Electrostatic<br>discharge (ESD)<br>ratings | Charged device model (CDM) JEDEC standard 22, test method C101  | -1000     | +1000     | V    |  |

|                                             | Machine model (MM) JEDEC standard 22, test method A115          | -150      | +150      | V    |  |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum rated conditions for extended periods may affect device reliability.

- (2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5 V beyond the supply rails must be current limited, except for the differential amplifier input pins.

- (3) These inputs are not internally protected against overvoltage. The differential amplifier input pins must be limited to 5 mA (max) or ±1.5 V (max).

- (4) Power-limited; observe maximum junction temperature.

#### THERMAL INFORMATION

|                  |                                              | DR\         | DRV411    |       |  |  |  |

|------------------|----------------------------------------------|-------------|-----------|-------|--|--|--|

|                  | THERMAL METRIC <sup>(1)</sup>                | PWP (TSSOP) | RGP (QFN) | UNITS |  |  |  |

|                  |                                              | 20 PINS     | 20 PINS   | 1     |  |  |  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 37.2        | 33.8      |       |  |  |  |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 24.3        | 34.6      |       |  |  |  |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 19.8        | 11.1      | 90044 |  |  |  |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.7         | 0.4       | °C/W  |  |  |  |

| ΨЈВ              | Junction-to-board characterization parameter | 19.6        | 11.2      |       |  |  |  |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.0         | 2.4       |       |  |  |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = +25$ °C,  $V_{DD} = +2.7$  V to +5.5 V, and zero output current  $I_{COMP}$ , unless otherwise noted.

|                         |                                                                 |                                                                        |                      | DRV411               |                     |                    |

|-------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|----------------------|----------------------|---------------------|--------------------|

|                         | PARAMETER                                                       | TEST CONDITIONS                                                        | MIN                  | TYP                  | MAX                 | UNIT               |

| HALL ELEM               | ENT EXCITATION / AMPLIFICATION                                  |                                                                        |                      |                      |                     |                    |

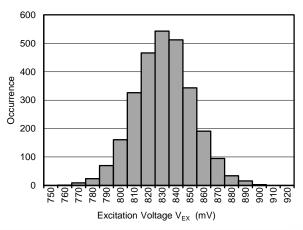

| .,                      | 11.0                                                            | T <sub>A</sub> = -40°C to +125°C, GSEL [00,01,10]                      | 0.7                  | 0.8                  | 0.95                | V                  |

| V <sub>EX</sub>         | Hall sensor excitation voltage                                  | T <sub>A</sub> = -40°C to +125°C, GSEL [1,1]                           | 0.6                  | 0.74                 | 0.95                | V                  |

| I <sub>EX</sub>         | Hall sensor excitation current                                  | T <sub>A</sub> = -40°C to +125°C                                       |                      |                      | 10                  | mA                 |

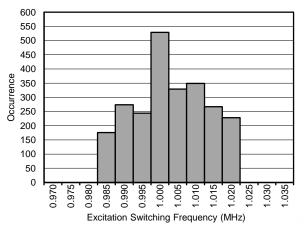

| f <sub>spin</sub>       | Excitation switching frequency                                  |                                                                        |                      | 1                    |                     | MHz                |

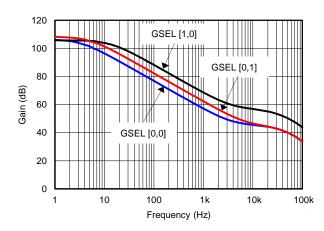

|                         |                                                                 | GSEL [0,0] <sup>(1)</sup> , f <sub>Zero</sub> = 3.8 kHz                |                      | 250                  |                     | V/V                |

| AOL <sub>FB</sub>       | Front-end open-loop flatband gain                               | GSEL [0,1], f <sub>Zero</sub> = 7.2 kHz                                |                      | 250                  |                     | V/V                |

|                         |                                                                 | GSEL [1,0], f <sub>Zero</sub> = 3.8 kHz                                |                      | 1000                 |                     | V/V                |

| AOL                     | Front-end open-loop gain                                        | T <sub>A</sub> = -40°C to +125°C,<br>GSEL [00,01,10,11]                | 94                   | 120                  |                     | dB                 |

|                         | - · · · · · · · · · · · · · · · · · · ·                         | No Hall sensor, GSEL [00, 01, 10]                                      |                      | 20                   | 100                 | μV                 |

| V <sub>OS_FE</sub>      | Front-end voltage offset                                        | GSEL [1,1]                                                             |                      | 5                    | 12                  | mV                 |

| dV <sub>OS FE</sub> /dT | Front-end voltage offset drift                                  | T <sub>A</sub> = -40°C to +125°C, no Hall sensor,<br>GSEL [00,01,10]   |                      | 0.2                  |                     | μV/°C              |

| 03_12                   | <b>3</b>                                                        | T <sub>A</sub> = -40°C to +125°C, GSEL [1,1]                           |                      | 5                    |                     | μV/°C              |

| GBWP                    | Gain-bandwidth product                                          | GSEL [1,1]                                                             |                      | 14                   |                     | MHz                |

| CMRR                    | Common-mode-rejection ratio                                     | GSEL [1,1], V <sub>CM</sub> = 0 V to VDD - 1.8 V                       |                      | 300                  |                     | μV/V               |

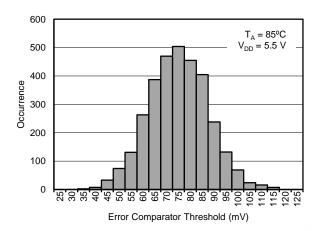

|                         | Error comparator threshold                                      |                                                                        |                      | 75                   |                     | mV                 |

| DIFFERENT               | IAL AMPLIFIER                                                   |                                                                        |                      |                      |                     |                    |

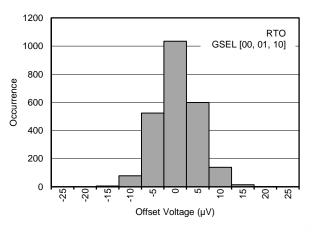

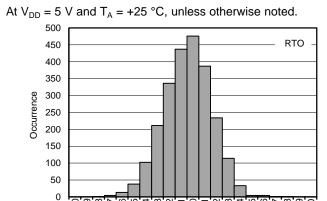

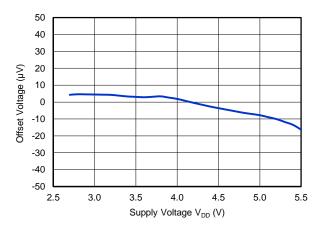

| Vos                     | Input offset voltage, RTO <sup>(2) (3)</sup>                    | $V_{IN1} = V_{IN2} = V_{REFIN}$                                        |                      | ±0.01                | ±0.1                | mV                 |

| dV <sub>OS</sub> /dT    | Input offset voltage drift, RTO                                 | T <sub>A</sub> = -40°C to +125°C                                       |                      | ±0.4                 | ±2                  | μV/°C              |

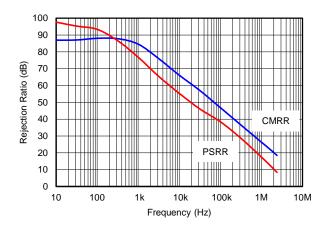

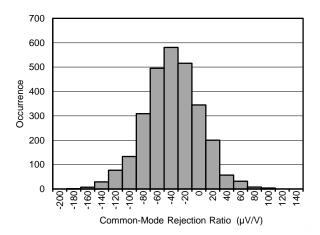

| CMRR                    | vs common-mode voltage, RTO                                     | $V_{CM} = -1 \text{ V to } V_{DD} + 1 \text{ V}, V_{REF} = V_{DD} / 2$ |                      | ±50                  | ±250                | μV/V               |

| PSRR                    | vs power-supply, RTO                                            | $V_{DD} = +2.7 \text{ V to } +5.5 \text{ V}, V_{CM} = V_{REFIN}$       |                      | ±4                   | ±50                 | μV/V               |

| V <sub>CM</sub>         | Common-mode input range                                         |                                                                        | -1                   |                      | V <sub>DD</sub> + 1 | V                  |

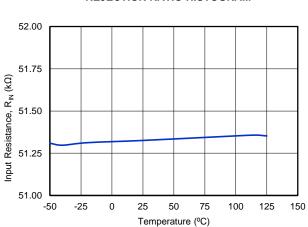

|                         | Differential impedance                                          |                                                                        | 16.5                 | 20                   | 23.5                | kΩ                 |

|                         | Common-mode impedance                                           |                                                                        | 40                   | 50                   | 60                  | kΩ                 |

|                         | External reference input impedance                              |                                                                        | 40                   | 50                   | 60                  | kΩ                 |

| G                       | Gain, V <sub>OUT</sub> /V <sub>IN_DIFF</sub>                    | T <sub>A</sub> = -40°C to +125°C                                       |                      | 4                    |                     | V/V                |

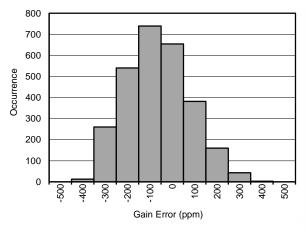

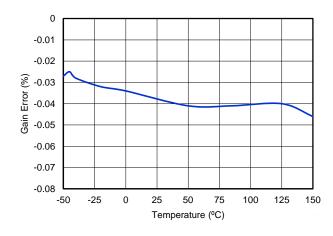

| G <sub>ERR</sub>        | Gain error                                                      |                                                                        |                      | ±0.02%               | ±0.3%               |                    |

|                         | Gain error drift                                                | T <sub>A</sub> = -40°C to +125°C                                       |                      | ±1                   | ±5                  | ppm/°C             |

|                         | Linearity error                                                 | $R_L = 1 \text{ k}\Omega$                                              |                      | 12                   |                     | ppm                |

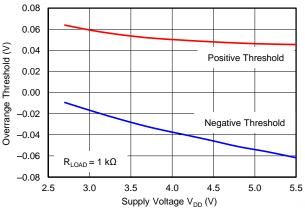

|                         | Voltage output swing from negative rail (3) (OR pin trip level) | I = +2.5 mA, V <sub>DD</sub> = 5 V, comparator trip level              |                      | 48                   | 85                  | mV                 |

|                         | Voltage output swing from positive rail (3) (OR pin trip level) | $I = -2.5$ mA, $V_{DD} = 5$ V, comparator trip level                   | V <sub>DD</sub> – 85 | V <sub>DD</sub> – 48 |                     | mV                 |

|                         | Chart sire it surrent(3)                                        | V <sub>OUT</sub> connected to GND                                      |                      | -18                  |                     | mA                 |

| I <sub>SC</sub>         | Short-circuit current <sup>(3)</sup>                            | V <sub>OUT</sub> connected to V <sub>DD</sub>                          |                      | 20                   |                     | mA                 |

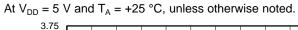

|                         | Signal overrange indication delay (OR pin) <sup>(3)</sup>       | V <sub>IN</sub> = 1-V step, see note <sup>(3)</sup>                    |                      | 2.5 to 3.5           |                     | μs                 |

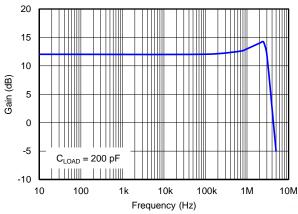

| BW <sub>-3dB</sub>      | Bandwidth <sup>(3)</sup>                                        |                                                                        |                      | 2                    |                     | MHz                |

| SR                      | Slew rate                                                       |                                                                        |                      | 6.5                  |                     | V/µs               |

|                         | Settling time large-signal (3)                                  | $\Delta V = \pm 2 V$ to 1%, no external filter                         |                      | 0.9                  |                     | μs                 |

|                         | Settling time <sup>(3)</sup>                                    | $\Delta V = \pm 0.4 \text{ V to } 0.01\%$                              |                      | 8                    |                     | µs                 |

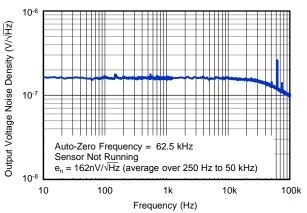

| e <sub>n</sub>          | Output voltage noise density, RTO <sup>(3)</sup>                | f = 1 kHz, compensation loop disabled                                  |                      | 170                  |                     | nV/√ <del>Hz</del> |

<sup>(1)</sup> Note that the numbers in the brackets correspond to the GSEL number and its value. For example, in this case, GSEL [0,0] means that GSEL1 = 0 and GSEL2 = 0.

<sup>(2)</sup> Parameter value referred to output (RTO).(3) See Typical Characteristic curves.

At  $T_A = +25$ °C,  $V_{DD} = +2.7$  V to +5.5 V, and zero output current  $I_{COMP}$ , unless otherwise noted.

|                  |                                        |                                                                                           |                     | DRV411              |                     |                      |

|------------------|----------------------------------------|-------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|----------------------|

|                  | PARAMETER                              | TEST CONDITIONS                                                                           | MIN                 | TYP                 | MAX                 | UNIT                 |

| COMPEN           | SATION COIL DRIVER, H-BRIDGE           |                                                                                           |                     |                     | "                   |                      |

|                  | Deals augrent                          | $T_A$ = -40°C to +125°C,<br>$V_{ICOMP1}$ - $V_{ICOMP2}$ = 4.2 $V_{PP}$ , $V_{DD}$ = 5 $V$ | 210                 | 250                 |                     | mA                   |

|                  | Peak current                           | $T_A = -40$ °C to +125°C,<br>$V_{ICOMP1} - V_{ICOMP2} = 2.5 V_{PP}, V_{DD} = 3.3 V$       | 125                 | 150                 |                     | mA                   |

|                  | Vallana surias                         | 20-Ω load, $V_{DD} = 5 \text{ V}$                                                         | 4.2                 |                     |                     | $V_{PP}$             |

|                  | Voltage swing                          | 20-Ω load, V <sub>DD</sub> = 3.3 V                                                        | 2.5                 |                     |                     | $V_{PP}$             |

|                  | Output common-mode                     |                                                                                           |                     | V <sub>DD</sub> / 2 |                     | V                    |

| VOLTAGE          | E REFERENCE                            |                                                                                           |                     |                     | •                   |                      |

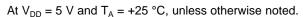

|                  |                                        | REFSEL [0,0] <sup>(5)</sup> , no load                                                     | 2.495               | 2.5                 | 2.505               | V                    |

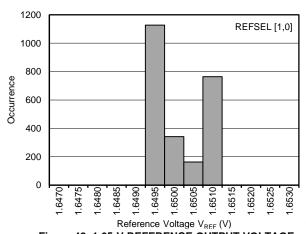

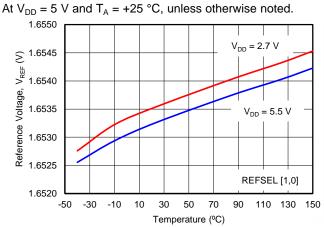

| $V_{REF}$        | Reference voltage (4)                  | REFSEL [1,0], no load                                                                     | 1.647               | 1.65                | 1.653               | V                    |

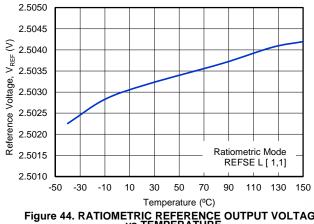

| KLI              |                                        | REFSEL [1,1], no load                                                                     | 49.6                | 50                  | 50.4                | % of V <sub>DD</sub> |

|                  | Reference voltage drift <sup>(4)</sup> | $T_A = -40$ °C to +125°C, REFSEL [00,10]                                                  |                     | ±5                  | ±50                 | ppm/°C               |

|                  | Voltage divider gain error drift       | $T_A = -40$ °C to +125°C, REFSEL [1,1]                                                    |                     | ±5                  | ±50                 | ppm/°C               |

| DODD             | D (4)                                  | REFSEL [00,10], RGP package                                                               |                     | ±15                 | ±200                | μV/V                 |

| PSRR             | Power-supply rejection ratio (4)       | REFSEL [00,10], PWP package                                                               |                     | ±15                 | ±300                | μV/V                 |

|                  | Load regulation                        | Load to GND or VDD,<br>ΔI <sub>LOAD</sub> = 0 mA to 5 mA                                  |                     | 0.15                | 0.35                | mV/mA                |

|                  | 01                                     | REFOUT connected to VDD                                                                   |                     | 20                  |                     | mA                   |

| I <sub>SC</sub>  | Short-circuit current                  | REFOUT connected to GND                                                                   |                     | -18                 |                     | mA                   |

| DIGITAL I        | INPUT/OUTPUT                           |                                                                                           |                     |                     | <u> </u>            |                      |

| Logic Inp        | uts (GSEL, REFSEL pins)                | CMOS-type levels                                                                          |                     |                     |                     |                      |

|                  | Input leakage current                  |                                                                                           |                     | 0.01                |                     | μA                   |

| V <sub>IH</sub>  | High-level input voltage               |                                                                                           | $0.7 \times V_{DD}$ |                     | $V_{DD} + 0.3$      | V                    |

| V <sub>IL</sub>  | Low-level input voltage                |                                                                                           | -0.3                |                     | $0.3 \times V_{DD}$ | V                    |

| Logic Ou         | tputs (ERROR, OR pins)                 |                                                                                           |                     |                     | <u>"</u>            |                      |

| V <sub>OL</sub>  | Low-level output voltage               | 4-mA sink                                                                                 |                     | 0.3                 |                     | V                    |

| V <sub>OH</sub>  | High-level output voltage              |                                                                                           |                     | See (6)             |                     | V                    |

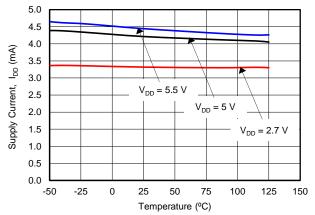

| POWER S          | SUPPLY                                 |                                                                                           |                     |                     | <u>"</u>            |                      |

| $V_{DD}$         | Specified voltage                      |                                                                                           | 2.7                 |                     | 5.5                 | V                    |

| IQ               | Quiescent current                      | $T_A$ = -40°C to +125°C, $I_{COMP}$ = 0 mA, no excitation                                 |                     |                     | 6                   | mA                   |

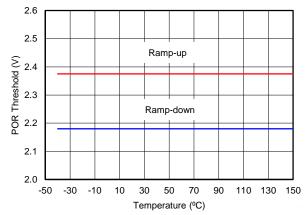

| V <sub>RST</sub> | Power-on reset threshold               | T <sub>A</sub> = -40°C to +125°C                                                          |                     | 2.4                 |                     | V                    |

| TEMPERA          | ATURE                                  |                                                                                           |                     |                     | •                   |                      |

|                  | Specified range                        |                                                                                           | -40                 |                     | +125                | °C                   |

|                  | Operating range                        |                                                                                           | -50                 |                     | +150                | °C                   |

<sup>(4)</sup> See Typical Characteristic curves.

<sup>(5)</sup> Note that the numbers in the brackets correspond to the REFSEL number and its value. For example, in this case, REFSEL [0,0] means that REFSEL1 = 0 and REFSEL2 = 0.

<sup>(6)</sup> OR and ERROR are open-drain outputs. No internal pull-up resistor. Output voltage depends on the external pull up resistor that is used.

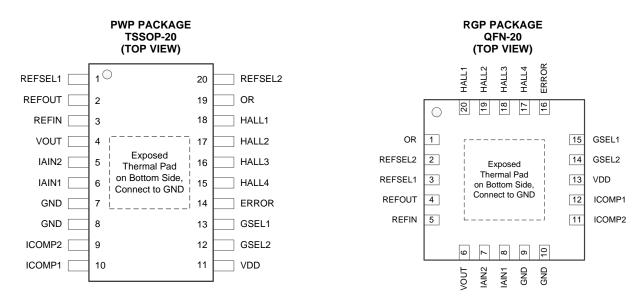

## **PIN CONFIGURATION**

## **PIN ASSIGNMENTS**

| PIN     |                |              |                                                                                                       |

|---------|----------------|--------------|-------------------------------------------------------------------------------------------------------|

| NAME    | PWP<br>(TSSOP) | RGP<br>(QFN) | DESCRIPTION                                                                                           |

| ERROR   | 14             | 16           | Open-drain output for error indication. See the Error Conditions section.                             |

| GND     | 7              | 9            | Ground connection                                                                                     |

| GND     | 8              | 10           | Ground connection                                                                                     |

| GSEL1   | 13             | 15           | Input. Selects the gain of the Hall amplifier. See Gain Selection and Compensation Frequency section. |

| GSEL2   | 12             | 14           | Input. Selects the gain of the Hall amplifier. See Gain Selection and Compensation Frequency section. |

| HALL1   | 18             | 20           | Pin 1 of AKM HW322 / HW302 or similar                                                                 |

| HALL2   | 17             | 19           | Pin 2 of AKM HW322 / HW302 or similar                                                                 |

| HALL3   | 16             | 18           | Pin 3 of AKM HW322 / HW302 or similar                                                                 |

| HALL4   | 15             | 17           | Pin 4 of AKM HW322 / HW302 or similar                                                                 |

| IAIN1   | 6              | 8            | Inverting input of differential amplifier                                                             |

| IAIN2   | 5              | 7            | Noninverting input of differential amplifier                                                          |

| ICOMP1  | 10             | 12           | Output 1 of compensation coil driver                                                                  |

| ICOMP2  | 9              | 11           | Output 2 of compensation coil driver                                                                  |

| OR      | 19             | 1            | Open-drain output for overrange indication. See the <i>Error Conditions</i> section.                  |

| REFIN   | 3              | 5            | Input for zero reference to differential amplifier                                                    |

| REFOUT  | 2              | 4            | Output terminal for selected reference voltage                                                        |

| REFSEL1 | 1              | 3            | Input. Sets reference mode. See the Voltage Reference section.                                        |

| REFSEL2 | 20             | 2            | Input. Sets reference mode. See the Voltage Reference section.                                        |

| VDD     | 11             | 13           | Supply voltage                                                                                        |

| VOUT    | 4              | 6            | Output of differential amplifier                                                                      |

|         | Thermal Pad    |              | Connect to GND                                                                                        |

#### TYPICAL CHARACTERISTICS

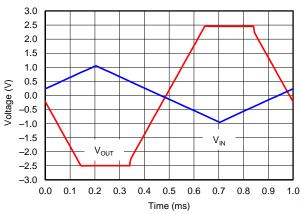

At  $V_{DD}$  = 5 V and  $T_A$  = +25 °C, unless otherwise noted.

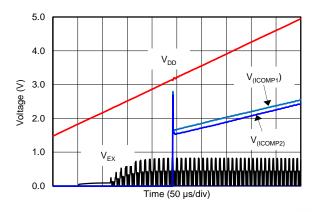

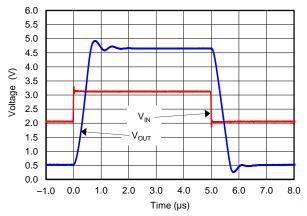

Figure 1. START-UP BEHAVIOR

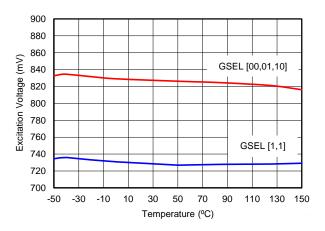

Figure 3. HALL SENSOR EXCITATION VOLTAGE vs TEMPERATURE

Figure 5. EXCITATION SWITCHING FREQUENCY HISTOGRAM

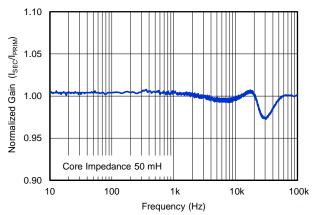

Figure 2. FRONT-END GAIN FLATNESS vs FREQUENCY

Figure 4. HALL SENSOR EXCITATION VOLTAGE HISTOGRAM

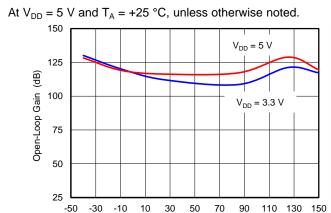

Figure 6. FRONT-END OPEN-LOOP GAIN vs FREQUENCY

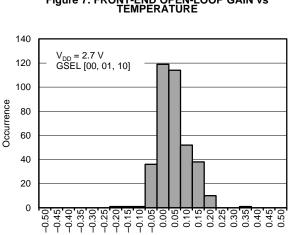

Figure 7. FRONT-END OPEN-LOOP GAIN vs TEMPERATURE

Temperature (°C)

Offset Voltage Drift (µV/°C) Figure 9. FRONT-END OFFSET VOLTAGE DRIFT HISTOGRAM

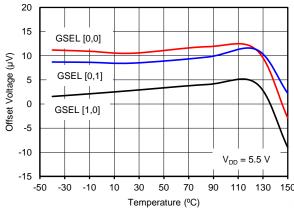

Figure 11. FRONT-END OFFSET VOLTAGE vs TEMPERATURE

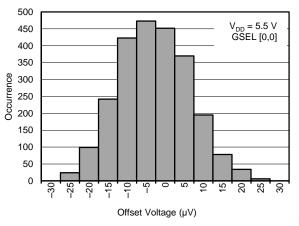

Figure 8. FRONT-END OFFSET VOLTAGE HISTOGRAM

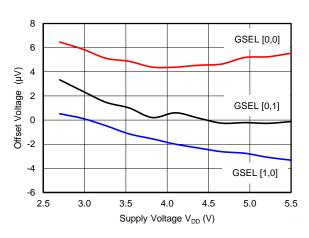

Figure 10. FRONT-END OFFSET VOLTAGE vs POWER SUPPLY

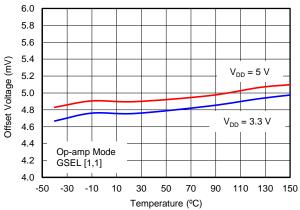

Figure 12. FRONT-END OFFSET VOLTAGE vs TEMPERATURE (OP-AMP MODE)

5.5

At  $V_{DD} = 5$  V and  $T_A = +25$  °C, unless otherwise noted.

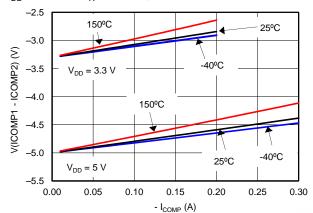

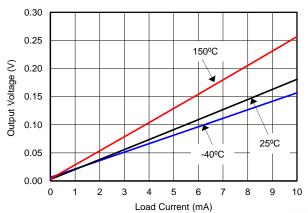

Figure 13. OUTPUT VOLTAGE SWING vs NEGATIVE OUTPUT CURRENT

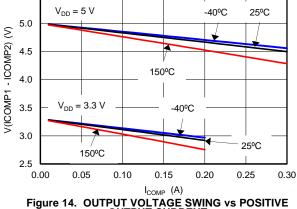

Figure 14. OUTPUT VOLTAGE SWING vs POSITIVE OUTPUT CURRENT

Figure 15. ERROR COMPARATOR THRESHOLD HISTOGRAM

Figure 16. DIFFERENTIAL AMPLIFIER, OFFSET VOLTAGE HISTOGRAM

Figure 17. DIFFERENTIAL AMPLIFIER CMRR AND PSRR vs FREQUENCY

Figure 18. DIFFERENTIAL AMPLIFIER COMMON-MODE REJECTION RATIO HISTOGRAM

Figure 19. DIFFERENTIAL AMPLIFIER POWER-SUPPLY REJECTION RATIO HISTOGRAM

Power-Supply Rejection Ratio PSRR (µV/V)

Figure 21. DIFFERENTIAL AMPLIFIER REFERENCE INPUT IMPEDANCE vs TEMPERATURE

Figure 23. DIFFERENTIAL AMPLIFIER GAIN ERROR HISTOGRAM

Figure 20. DIFFERENTIAL AMPLIFIER OFFSET VOLTAGE vs POWER SUPPLY

Figure 22. DIFFERENTIAL AMPLIFIER GAIN vs FREQUENCY

Figure 24. DIFFERENTIAL AMPLIFIER GAIN ERROR vs TEMPERATURE

Figure 25. DIFFERENTIAL AMPLIFIER OUTPUT VOLTAGE vs OUTPUT CURRENT (POSITIVE RAIL)

Figure 26. DIFFERENTIAL AMPLIFIER OUTPUT VOLTAGE vs OUTPUT CURRENT (NEGATIVE RAIL)

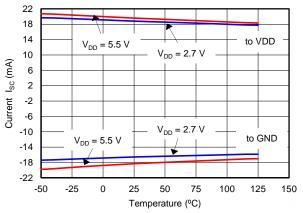

Figure 27. DIFFERENTIAL AMPLIFIER SHORT-CIRCUIT CURRENT vs TEMPERATURE

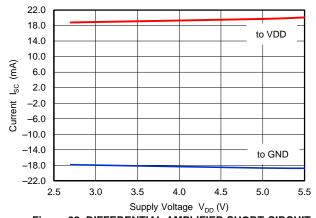

Figure 28. DIFFERENTIAL AMPLIFIER SHORT-CIRCUIT CURRENT vs POWER SUPPLY

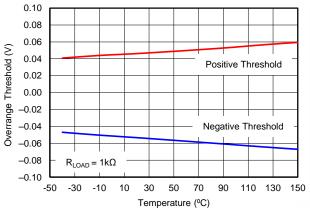

Figure 29. OVERRANGE TRIP LEVEL vs TEMPERATURE

Figure 30. OVERRANGE TRIP LEVEL vs POWER SUPPLY

Figure 31. OVERRANGE DELAY vs TEMPERATURE

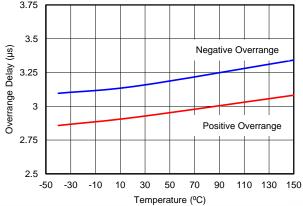

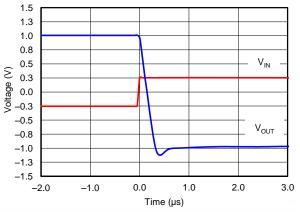

Figure 32. DIFFERENTIAL AMPLIFIER OVERLOAD RECOVERY

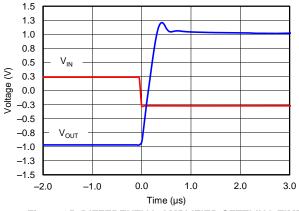

Figure 33. DIFFERENTIAL AMPLIFIER STEP RESPONSE

Figure 34. DIFFERENTIAL AMPLIFIER SETTLING TIME (RISING EDGE)

Figure 35. DIFFERENTIAL AMPLIFIER SETTLING TIME (FALLING EDGE)

Figure 36. DIFFERENTIAL AMPLIFIER OUTPUT VOLTAGE NOISE DENSITY

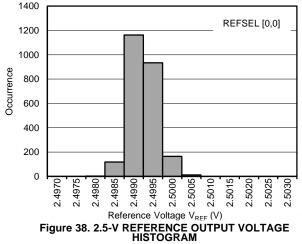

Figure 37. 2.5-V REFERENCE OUTPUT VOLTAGE vs LOAD CURRENT

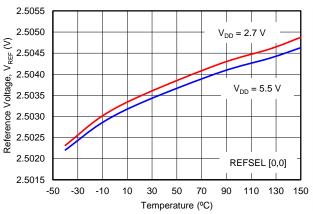

Figure 39. 2.5-V REFERENCE OUTPUT VOLTAGE vs TEMPERATURE

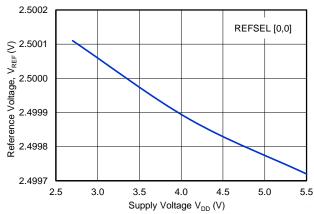

Figure 40. 2.5-V REFERENCE OUTPUT VOLTAGE vs POWER SUPPLY

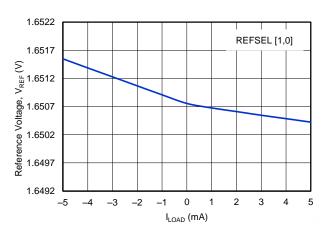

Figure 41. 1.65-V REFERENCE OUTPUT VOLTAGE vs LOAD CURRENT

Figure 42. 1.65-V REFERENCE OUTPUT VOLTAGE

Figure 43. 1.65-V REFERENCE OUTPUT VOLTAGE vs TEMPERATURE

Figure 44. RATIOMETRIC REFERENCE OUTPUT VOLTAGE VS TEMPERATURE

Figure 45. SUPPLY CURRENT vs TEMPERATURE

Figure 46. POWER-ON-RESET vs TEMPERATURE

#### **FUNCTIONAL DESCRIPTION**

## **OVERVIEW**

The DRV411 is a complete sensor signal conditioning circuit that directly connects to the current sensor, providing all necessary functions for the sensor operation. The DRV411 operates from a single +2.7-V to +5.5-V supply, and provides magnetic field probe (Hall sensor) excitation, signal conditioning, and compensation-coil driver amplification. In addition, this device detects error conditions and handles overload situations. A precise differential amplifier allows translation of the compensation current into an output voltage using a small shunt resistor. A buffered voltage reference can be used for comparator, analog-to-digital converter (ADC), or bipolar zero reference voltages. Dynamic error correction ensures high dc precision over temperature and long-term accuracy.

The DRV411 uses analog signal conditioning circuitry; the internal loop filter and integrator are switched capacitor-based circuits. The DRV411 can be combined with high-precision sensors for exceptional accuracy and resolution. An internal clock and counter logic control power-up, overload detection and recovery, error, and time-out conditions. The DRV411 is built using a highly reliable CMOS process. Unique protection cells at critical connections enable the design to handle inductive energy.

#### HALL SENSOR INTERFACE

The DRV411 works best with symmetrical InSb Hall elements, such as the HW322 and HW302 from AKM or other vendors. Symmetrical Hall elements are Hall elements where input impedance and output impedance are closely matched. However, hall elements suffer from offset and offset drift across temperature that affects the accuracy and linearity of the current sensor. The DRV411 contains patented excitation and conditioning circuitry that significantly reduces offset and offset drift. The excitation circuit regulates the voltage across the hall element to a maximum voltage of 0.95 V. This voltage is very stable across the full temperature range. The excitation current varies with temperature in order to keep the hall sensitivity constant. A special current limiting circuit limits the current delivered to the hall element to a maximum current of 10 mA regardless of the temperature or the impedance of the hall element.

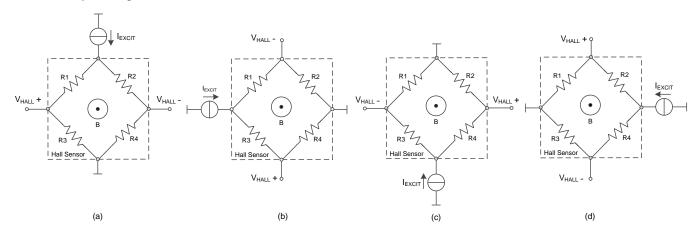

### DYNAMIC OFFSET AND NOISE CANCELLATION USING SPINNING CURRENT METHOD

The DRV411 incorporates dynamic offset cancellation circuitry that helps eliminate offset drift and 1/f noise of the hall sensor. The excitation current is spun through the hall sensor in orthogonal directions at a fixed clock frequency using rotation multiplexer switches, as shown in Figure 47 (a) to (d). The excitation source ensures a constant current during each spin cycle but keeps the sensitivity of the hall sensor independent by varying the current across temperature for impedance variations from 100  $\Omega$  to 2 k $\Omega$ . The corresponding Hall output is averaged across the four orthogonal directions to effectively cancel the Hall offset and the 1/f noise. The DRV411 continuously monitors the offset of the Hall element and triggers an error flag if the offset remains > 50 mV as a result of any damage to the Hall sensor. Refer to the *Error Conditions* section for more details.

Figure 47. Hall Sensor Current Spinning Method

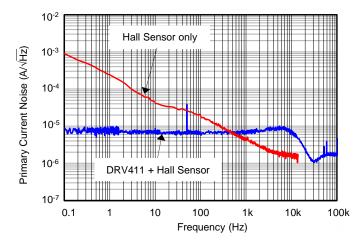

Low-frequency noise can be a concern for Hall sensors with constant voltage and current excitation. The dynamic offset cancellation technique eliminates 1/f noise from the Hall sensor. Figure 48 shows the effect of current spinning on the Hall sensor, referred to primary current noise.

Figure 48. Effect of Noise Cancellation with Current Spinning

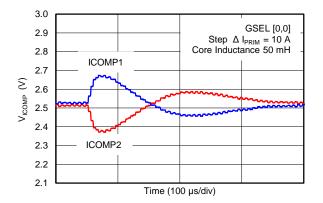

## **COMPENSATION COIL DRIVER**

The compensation coil driver provides the driving current for the compensation coil. A fully differential driver stage offers the high-signal voltage to overcome the wire resistance of the coil with only a 5-V supply. The compensation coil is connected between ICOMP1 and ICOMP2, both generating an analog voltage across the coil (see Figure 51) that turns into current from the wire resistance (and eventually from the inductance). The compensation current represents the primary current transformed by the turns ratio. A shunt resistor is connected in this loop and the high precision differential amplifier translates the voltage from this shunt to an output voltage (see the Functional Principle of Closed-Loop Current Sensors with a Hall Sensor section).

Both compensation driver outputs provide low impedance over a wide frequency range that insures smooth transition between the closed-loop compensation frequency range and the high-frequency range, where the primary winding directly couples the primary current into the compensation coil according to the winding ratio (transformer effect).

The two compensation driver outputs are specially protected to handle inductive energy. However, it might be necessary to use high-current sensors to add external protection diodes (see the *Protection Recommendations* section).

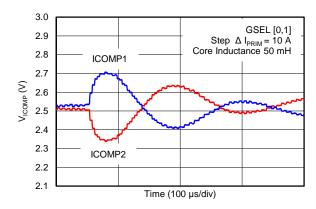

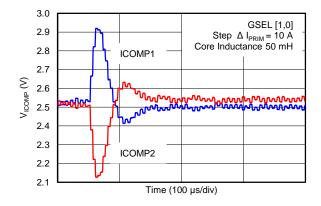

### **GAIN SELECTION AND COMPENSATION FREQUENCY**

Proper selection of the GSEL mode enables the sensor designer to create a sensor with stable gain over a wide frequency range and excellent loop stability. Modes Gain\_1 to Gain\_3 allow for different fixed gain and zero-frequency options to be selected according to the requirements of the individual sensor. See Table 1 for more information. Evaluate Gain\_3 mode (GSEL [1,0]) first because it works with most common sensors.

#### **Mode Selection**

**Gain\_1 Mode** For use with sensors with compensation coil inductance < 50 mH.

**Gain\_2 Mode** For use with sensors with very small form factor (small core diameter), where the transformer effect starts to dominate the transfer function at frequencies significantly above 3.8 kHz. Typically the inductance of the compensation coil would be very small.

Gain\_3 Mode Works well with a wide selection of sensors with compensation coil inductance typically ≥ 50 mH.

## **Table 1. Gain Setting and Compensation Frequency**

| MODE                                         | GSEL1 | GSEL2 | DESCRIPTION                                                                                                                                                                                        |  |  |  |

|----------------------------------------------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Gain_1                                       | 0     | 0     | G = 250 V/V. Compensation frequency set to 3.8 kHz.                                                                                                                                                |  |  |  |

| Gain_2                                       | 0     | 1     | G = 250 V/V. Compensation frequency set to 7.2 kHz.                                                                                                                                                |  |  |  |

| Gain_3                                       | 1     | 0     | G = 1000 V/V. Compensation frequency set to 3.8 kHz.                                                                                                                                               |  |  |  |

| External gain and compensation (op-amp mode) | 1     | 1     | Current spinning and front-end chopping are turned off. Constant voltage excitation is enabled. Gain and compensation set by using external resistors and capacitors, such as in discrete designs. |  |  |  |

Figure 49. Settling of ICOMP1 and ICOMP2 (Mode Gain\_1)

Figure 50. Settling of ICOMP1 and ICOMP2 (Mode Gain 2)

Figure 51. Settling of ICOMP1 and ICOMP2 (Mode Gain\_3)

Along with symmetrical InSb Hall elements, the DRV411 can also be connected to symmetrical GaAs Hall elements. The advantage of GaAs Hall elements is that they provide an extended temperature range to +125°C. See the following section, *External Gain and Compensation (Op-amp Mode)* for more details. This type of Hall element has a lower sensitivity than InSb-type sensors. In order to compensate for this difference, TI recommends using gain setting mode Gain\_3 with GaAs sensors. If the sensitivity is too low and the loop gain is insufficient, the loop can become unstable. In op-amp mode, gain can be set with external components.

www.ti.com

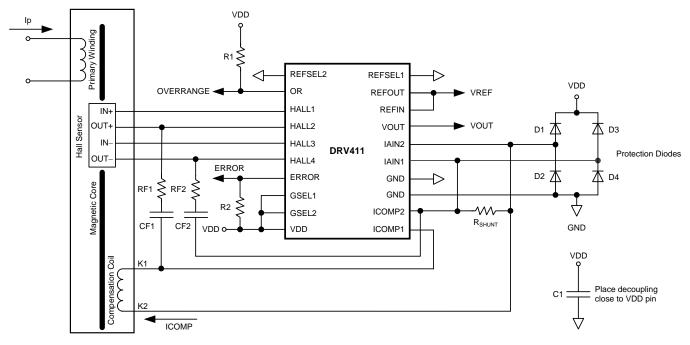

# **EXTERNAL GAIN AND COMPENSATION (OP-AMP MODE)**

Op-amp mode allows several degrees of freedom for the sensor designer. In op-amp mode, the DRV411 functions like a conventional operation amplifier with high open loop gain (> 100 dB). The internal compensation is disconnected, so that the sensor gain and compensation can be set externally. The DRV411 still provides a stable excitation voltage of 0.74 V between terminals HALL1 and HALL3. The outputs of the Hall sensor must be connected to terminal HALL2 and HALL4. The maximum current is limited to 10 mA to protect the Hall element. The following list shows some ways to use op-amp mode:

- Op-amp mode can be used in cases where modes Gain\_1 to Gain\_3 do not lead to an acceptable frequency response from the sensor module. In this mode, external compensation must be designed in to suit the sensor requirements (see Figure 57).

- DRV411 can be used with symmetrical GaAs Hall sensors. However, because of the inherently low sensitivity

of GaAs sensors, the internal gain (compensation) may not be sufficient. In such cases, use op-amp mode to

make the system stable with external compensation. In op-amp mode, the excitation circuit provides a

constant 0.74 V across the HALL1 and HALL3 outputs, with HALL3 referred to GND. Connect the Hall

outputs to the HALL2 and HALL4 pins (see Figure 57). For Hall sensors with large input impedances, do not

exceed the common-mode input range of the op-amp inputs (see the Electrical Characteristics section).

- Op-amp mode can also be used for interfacing to nonsymmetrical Hall elements, which are Hall elements

where the input impedance and output impedance are not equal. Different Hall sensor input and output

impedances lead to very large sensor offsets that might be outside the correction range of the DRV411

excitation circuit. In this mode, the ERROR pin is disabled (see the *Error Conditions* for more details). For

Hall sensors with large input impedances, do not exceed the common-mode input range of the op amp inputs.

- If an external excitation circuit is required for the Hall sensor in op-amp mode, bypass the internal sensor by

ignoring the HALL1 and HALL3 terminals. Connect the Hall sensor outputs to the HALL2 and HALL4

terminals. For Hall sensors with large input impedances, do not exceed the common-mode input range of the

op amp inputs.

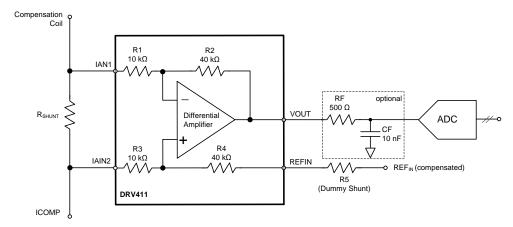

#### SHUNT SENSE AMPLIFIER

The differential (H-bridge) driver arrangement for the compensation coil requires a differential sense amplifier for the shunt voltage. This differential amplifier offers wide bandwidth and a high slew rate for fast current sensors. Excellent dc stability and accuracy result from an auto-zero technique. The voltage gain is 4 V/V, set by precisely matched and stable internal resistors.

For gains of 4 V/V:

$$4 = \frac{R_2}{R_1} = \frac{R_4 + R_5}{R_{SHUNT} + R_3}$$

where:

•

$$R_2 / R_1 = R_4 / R_3 = 4$$

•  $R_5 = R_{SHUNT} \times 4$  (1)

Both inputs of the differential amplifier are normally connected to the current shunt resistor. This resistor adds to the internal  $10\text{-k}\Omega$  resistor, slightly reducing the gain in this signal path. For best common-mode rejection (CMR), a dummy shunt resistor ( $R_5 = 4 \times R_{SHUNT}$ ) is placed in series with the REF<sub>IN</sub> pin to restore matching of both resistor dividers; see Figure 52.

Figure 52. Internal Difference Amplifier with Example of a Decoupling Filter

Typically, the gain error resulting from the resistance of  $R_{SHUNT}$  is negligible; for 70 dB of common-mode rejection, however, the match of both divider ratios must be higher than 1/3000.

The amplifier output can drive close to the supply rails, and is designed to drive the input of a SAR-type ADC; adding an RC low-pass filter stage between the DRV411 and the ADC is recommended. This filter not only limits the signal bandwidth but also decouples the high-frequency component of the converter input sampling noise from the amplifier output. For  $R_F$  and  $C_F$  values, refer to the specific converter recommendations in the respective product data sheet. Empirical evaluation may be necessary to obtain optimum results.

The output drives 100 pF directly and shows 50% overshoot with approximately 1-nF capacitance. Adding  $R_F$  allows for much larger capacitive loads. Note that with an  $R_F$  of only 20  $\Omega$ , the load capacitor must be either less than 1 nF or more than 33 nF to avoid overshoot; with an  $R_F$  of 50  $\Omega$ , this transient area is avoided.

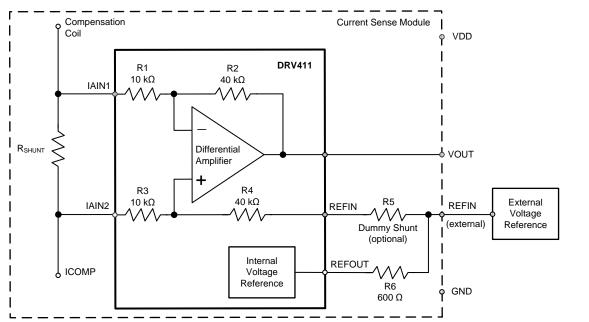

The reference input (REFIN) is the reference node for the exact output signal (VOUT). Connecting REFIN to the reference output (REFOUT) results in a live zero reference voltage that is user-selectable. Use the same reference for REFIN and the ADC to avoid mismatch errors that exist between the two reference sources.

### **OVERRANGE COMPARATOR**

High peak current can overload the differential amplifier connected to the shunt. The OR pin, an open-drain output, indicates an overvoltage condition for the differential amplifier by pulling low. The output of this flag is suppressed for 3 µs, preventing unwanted triggering from transients and noise. This pin returns to high as soon as the overload condition is removed (an external pull-up is required to return the pin high).

This error flag not only provides a warning about a signal-clipping condition, but is also a window comparator output for actively shutting off circuits in the system. The value of the shunt resistor defines the operating window for the current and sets the ratio between the nominal signal and the trip level of the overrange flag. The trip current of this window comparator is calculated using the following example:

With a 5-V supply, the output voltage swing is approximately ±2.45 V (load and supply voltage-dependent).

The gain of 4 V/V enables an input swing of ±0.6125 V.

Thus, the clipping current is IMAX =  $0.6125 \text{ V} / R_{\text{SHUNT}}$ .

See Figure 13 and Figure 14 in the *Typical Characteristics* section for details.

The overrange condition is internally detected as soon as the amplifier exceeds its linear operating range, not just a preset voltage level. Therefore, the error of the overrange comparator level is reliably indicated in fault conditions such as output shorts, low load, or low-supply conditions. As soon as the output cannot drive the voltage higher, the flag is activated. This configuration is a safety improvement over a voltage-level comparator.

Note that the internal resistance of the compensation coil may prevent high compensation current from flowing because of ICOMP driver overload. Therefore, the differential amplifier may not overload with this current. However, a fast rate of change of the primary current is transmitted through transformer action and safely triggers the overload flag.

#### VOLTAGE REFERENCE

The precision reference circuit offers low drift (typically 5 ppm/K) and is used for internal biasing; it is also connected to the REFOUT pin. The circuit is intended as the reference point of the output signal to allow a bipolar signal around it. This output is buffered for low impedance and tolerates sink and source currents of  $\pm 5$  mA. Capacitive loads can be directly connected, but generate ringing on fast load transients. A small series resistor of a few ohms improves the response, especially for a capacitive load in the range of 1  $\mu$ F.

## **Reference Output Voltage Selection**

As shown in Table 2, the most common use-cases for the DRV411 are with 5-V and 3.3-V power supplies, where the sensor output must be centered at 2.5 V and 1.65 V, respectively. The internal reference provides very good accuracy and drift performance. See the *Electrical Characteristics* for detailed information.

Table 2. Reference Output Voltage Selection

| MODE               | REFSEL1         | REFSEL2 | DESCRIPTION                                    |

|--------------------|-----------------|---------|------------------------------------------------|

| REF = 2.5 V        | 0               | 0       | Used with sensor module supply of 5 V          |

| REF = 1.65 V       | EF = 1.65 V 1 0 |         | Used with sensor module supply of 3.3 V        |

| Ratiometric output | 1               | 1       | Provides output centered on V <sub>S</sub> / 2 |

In the ratiometric output mode, the reference is bypassed and the power supply is divided by two. The internal resistor divider offers very tight tolerances and a temperature coefficient of less than 10 ppm/ $^{\circ}$ C. In this case, the sensor module output is centered on  $V_S/2$ .

For sensor modules with a reference pin, the DRV411 also allows overwriting the internal reference with an external reference voltage, as shown in Figure 53. When an external reference that has a significant voltage difference compared to the internal reference is connected, resistor R<sub>5</sub> limits the current flowing from the internal reference. In this case, the internal reference sources the current shown in Equation 2:

$$I_{\text{int\_ref}} = \frac{V_{\text{int\_ref}} - V_{\text{ext\_ref}}}{600 \,\Omega}$$

(2)

Figure 53. DRV411 with External Reference

The example of  $600~\Omega$  for R6 was chosen for illustration purposes; different values are possible. Note that if no external reference is connected, R6 has little impact on the common-mode rejection of the differential amplifier, and therefore, should be as small as possible.

#### POWER-ON STARTUP AND BROWNOUT

Power-on is detected when the supply voltage exceeds 2.4 V at VDD. At this point, digital logic starts up and waits for 100  $\mu$ s for the excitation source to settle to its final value. During this period, ICOMP1 and ICOMP2 outputs are pulled low, so that there is no undesired signal drive on the compensation coil. Also, the error conditions are suppressed and the ERROR pin is asserted low for 100  $\mu$ s. This ensures that the excitation voltage has reached the final level and there is no false error triggered on the output. The output on the VOUT terminal is only valid 100  $\mu$ s after power-on reset.

The DRV411 tests for low supply voltages with a brownout voltage level of +2.4 V. Good power-supply and low ESR bypass capacitors are required to maintain the supply voltage during the large current pulses driven by the DRV411. Supply voltage drops below the brown-out level lasting less than 25 µs are ignored. A supply drop lasting longer than 25 µs generates power-on reset. A voltage dip on VDD down to +1.8 V also initiates a power-on reset. After the power supply returns to 2.4 V (see the power-on reset threshold parameter in the Electrical Characteristics), the device initiates a startup cycle as previously described.

#### **ERROR CONDITIONS**

In addition to the overrange flag that indicates signal clipping in the output amplifier (differential amplifier), a system error flag is provided. The error flag indicates conditions when the output voltage does not represent the primary current. The error flag is active during a power fail or brown-out, or when the Hall sensor offset becomes greater than 50 mV, which usually means that the Hall sensor is not functioning within its normal operating range. The error flag also goes active with an open circuit in the Hall sensor connection. As soon as the error condition is no longer present and the circuit has returned to normal operation, the flag resets.

Both the error and overrange flags are open-drain logic outputs. They can be connected together for a wired-OR, and require an external pull-up resistor for proper operation.

The following conditions result in error flag activation (ERROR asserts low):

- 1. For 100  $\mu$ s from power-up, or if a supply-voltage low (brown-out) condition lasts for more than 25  $\mu$ s. Recovery is the same as power-up.

- 2. If the Hall sensor offset becomes greater than 50 mV.

- 3. If one or more of the Hall sensor terminals is disconnected.

# PROTECTION RECOMMENDATIONS

The inputs IAIN1 and IAIN2 require external protection to limit the voltage swing below 6 V of the supply voltage. Driver outputs ICOMP1 and ICOMP2 can handle high-current pulses protected by internal clamp circuits to the supply voltage. If large magnitude overcurrents are expected, it is highly recommended to connect external Schottky diodes to the supply rails. This external protection prevents current flowing into the die and destroying the circuitry.

All other pins offer standard protection; see the Absolute Maximum Ratings table.

#### APPLICATION INFORMATION

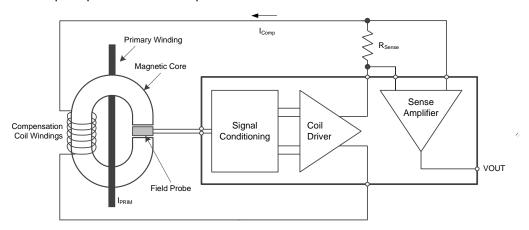

#### FUNCTIONAL PRINCIPLE OF CLOSED-LOOP CURRENT SENSORS WITH A HALL SENSOR

Closed-loop current sensors measure currents over wide frequency ranges, including dc currents. These types of devices offer a contact-free method, as well as excellent galvanic isolation performance combined with high resolution, accuracy, and reliability. At dc and in low-frequency ranges, the magnetic field induced from the current in the primary winding is compensated by a current driven through a compensation coil. A magnetic field probe (Hall sensor) located in the magnetic core loop detects the magnetic flux. This probe delivers the signal to the signal conditioning circuitry that drives the current through the compensation coil, bringing the magnetic flux back to zero. This compensation current is proportional to the primary current, relative to the winding ratio.

In higher frequency ranges, the compensation winding acts as the secondary winding in the current transformer, while the H-bridge compensation driver is rolled off and provides low output impedance.

A difference amplifier senses the voltage across a small shunt resistor that is connected to the compensation loop. This difference amplifier generates the output voltage that is proportional to the primary current. Figure Figure 54 shows the principle of a closed-loop current sensor.

Figure 54. Principle of a Closed-Loop Current Sensor

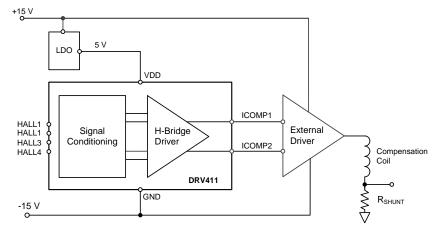

### USING DRV411 IN ±15-V SENSOR APPLICATIONS

To take advantage of the current spinning architecture for  $\pm 15$ -V sensor modules, the application circuit shown in Figure 55 can be used. The DRV411 max supply voltage is 5.5 V; therefore, the  $\pm 15$ V supplies must be externally regulated to less than 5.5 V across the power supply pins of the DRV411. In addition, an external power driver stage must be implemented that then drives the compensation coil. These techniques allow the design of exceptionally precise and stable  $\pm 15$ -V current-sense modules.

Figure 55. DRV411 Application Example: ±15-V Sensor Modules

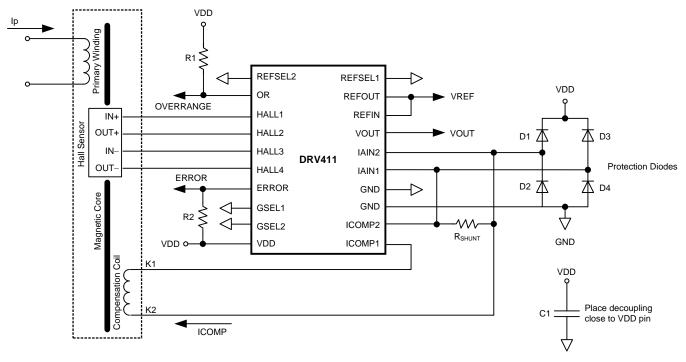

## **ADDITIONAL APPLICATION EXAMPLES**

Figure 56. Typical Application Example with Gain\_1 Setting (see Table 1)

Figure 57. Application Example with External Gain and Compensation Setting (GSEL1 and GSEL2 set High), No Current Spinning

www.ti.com

#### LAYOUT CONSIDERATIONS

The DRV411 operates with relatively large currents and offers wide bandwidth. It is often exposed to large distortion energy from the primary signal and from the environment. Therefore, the wiring layout must provide shielding and low impedance connections between critical points. Power-supply decoupling requires low-ESR capacitors, and eventually a combination of a 4.7-nF NP0-type capacitor and a second capacitor of 1  $\mu$ F or larger. Use low-impedance tracks to connect the capacitors to the pins. Avoid plated through-hole connectors; use multiple plated through-holes instead. The ground (GND) should be connected to a local ground plane. Best supply decoupling is achieved with ferrite beads in series to the main supply. The ferrite beads decouple the DRV411, and thus reduce interaction with other circuits powered from the same supply voltage source.

The reference output (REFOUT) is referred to GND. A low-impedance and star-type connection is required to avoid the driver current and the probe current modulating the voltage drop on the ground track. The REFOUT and VOUT outputs can drive some capacitive load, but avoid large direct capacitive loading because it increases internal pulse currents. Given the wide bandwidth of the differential amplifier, isolate large capacitive loads with a small series resistor. Using a small capacitor of some pF improves the transient response on high resistive loads.

The exposed thermal pad, or PowerPAD, on the bottom of the package must be soldered to GND because it is internally connected to the substrate that must be connected to the most negative potential.

#### POWER DISSIPATION

The use of the thermally-enhanced PowerPAD SOIC and QFN packages dramatically reduces the thermal impedance from junction to case. These packages are constructed using a down-set lead frame that the die is mounted on. This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package. The PowerPAD has direct thermal contact with the die; therefore, excellent thermal performance can be achieved as a result of providing a good thermal path away from the thermal pad.

The two outputs, ICOMP1 and ICOMP2, are linear outputs, and therefore the power dissipation on each output is proportional to the current multiplied by the internal voltage drop on the active transistor. For ICOMP1 and ICOMP2, it is the voltage drop to VDD or GND according to the current-conducting side of the output.

#### **CAUTION**

Output short-circuit conditions are particularly critical for the ICOMP driver because the full supply voltage can be seen across the conducting transistor and the current is not limited other than by the current density limitation of the FET; permanent damage can occur. The DRV411 does not feature temperature protection or thermal shut-down.

#### **Thermal Pad**

Packages with an exposed thermal pad are specifically designed to provide excellent power dissipation, but board layout greatly influences the overall heat dissipation. Technical details are described in Application Report SLMA002, *PowerPad Thermally Enhanced Package*, available for download at www.ti.com.

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in this version.

| Cr | nanges from Revision A (August 2013) to Revision B                                                                                      | Page |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed ESD parameter in Absolute Maximum Ratings table: deleted first human body model row, added machine model row                    |      |

| •  | Changed Hall Element Excitation, <i>Error comparator threshold</i> parameter typical specification in Electrical Characteristics table  | 3    |

| •  | Changed Voltage Reference, <i>PSRR</i> parameter: added second row to PSRR parameter, added RGP package to test conditions of first row | 4    |

| •  | Changed Digital Input/Output, $V_{OL}$ and $V_{OH}$ parameters: swapped symbols and parameter names                                     | 4    |

| •  | Changed Figure 15                                                                                                                       |      |

| •  | Changed Figure 36: changed units in y-axis                                                                                              | 11   |

| •  | Changed last paragraph of Gain Selection and Compensation Frequency section                                                             | 16   |

| Cł | nanges from Original (August 2013) to Revision A                                                                                        | Page |

| •  | Changed Figure 14 to show correct image                                                                                                 | 8    |

| •  | Changed Figure 25 to show correct image                                                                                                 | 10   |

| •  | Changed Figure 34 to show correct image                                                                                                 | 11   |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status           | Material type | Package   Pins    | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|------------------|---------------|-------------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)              | (2)           |                   |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |                  |               |                   |                       |      | (4)           | (5)                 |              |              |

| DRV411AIPWP           | Obsolete         | Production    | HTSSOP (PWP)   20 | -                     | -    | Call TI       | Call TI             | -40 to 125   | DRV411       |

| DRV411AIPWPR          | Active           | Production    | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 125   | DRV411       |

| DRV411AIPWPR.B        | Active           | Production    | HTSSOP (PWP)   20 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 125   | DRV411       |

| DRV411AIRGPR          | Active           | Production    | QFN (RGP)   20    | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 125   | DRV411       |

| DRV411AIRGPR.B        | Active           | Production    | QFN (RGP)   20    | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 125   | DRV411       |

| DRV411AIRGPT          | Last<br>Time Buy | Production    | QFN (RGP)   20    | 250   SMALL T&R       | Yes  | NIPDAU        | Level-3-260C-168 HR | -40 to 125   | DRV411       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

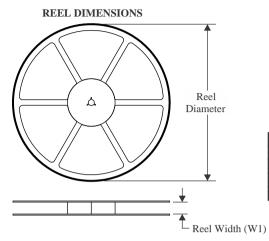

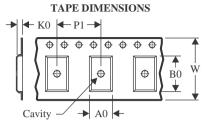

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

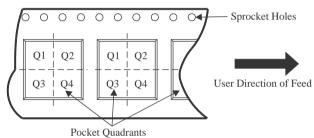

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ı | DRV411AIPWPR | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

|   | DRV411AIRGPR | QFN             | RGP                | 20 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

|   | DRV411AIRGPT | QFN             | RGP                | 20 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

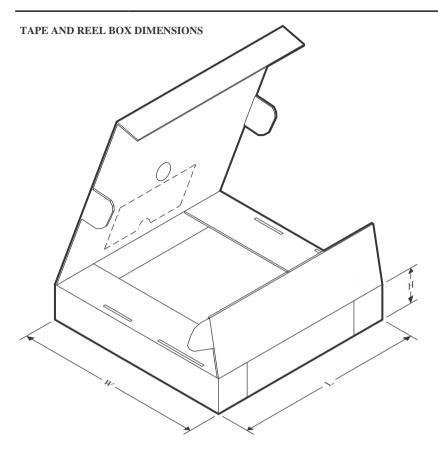

www.ti.com 25-Sep-2024

# \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV411AIPWPR | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| DRV411AIRGPR | QFN          | RGP             | 20   | 3000 | 346.0       | 346.0      | 33.0        |

| DRV411AIRGPT | QFN          | RGP             | 20   | 250  | 210.0       | 185.0      | 35.0        |

6.5 x 4.4, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

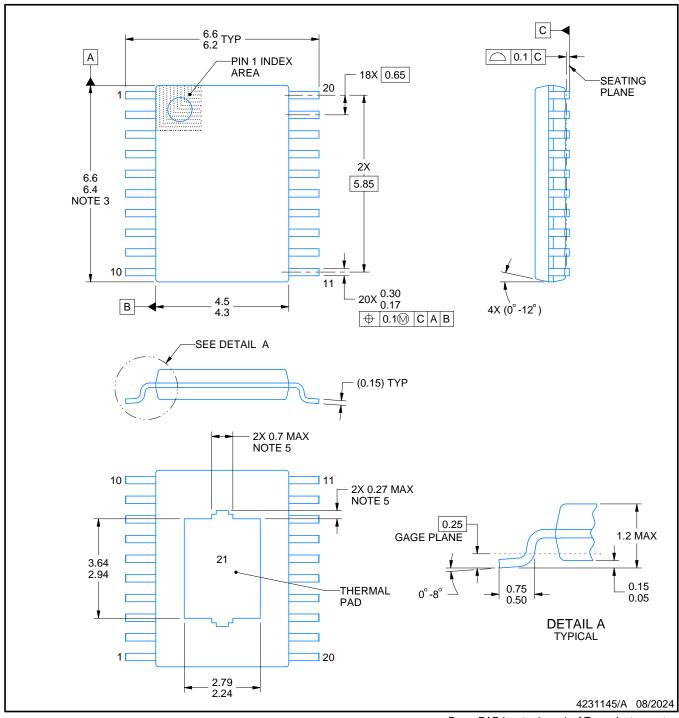

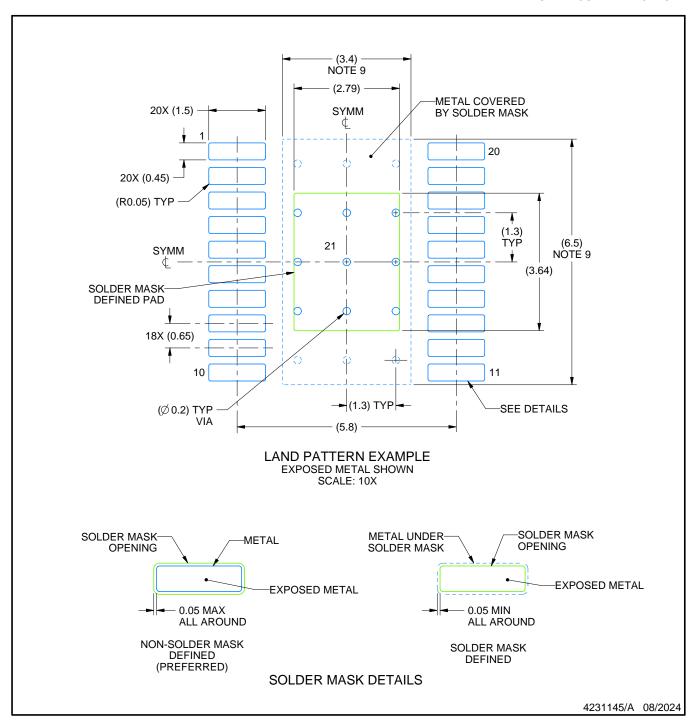

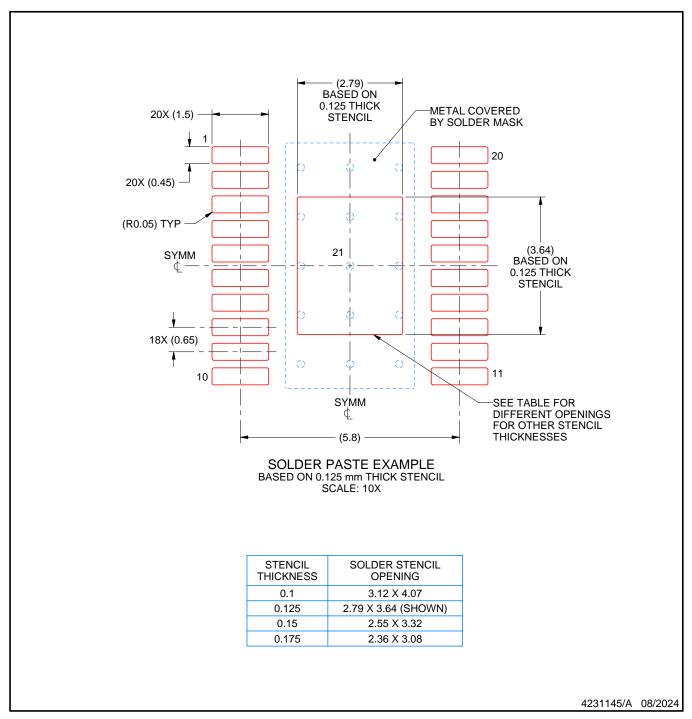

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

# PowerPAD is a trademark of Texas Instruments.

#### NOTES:

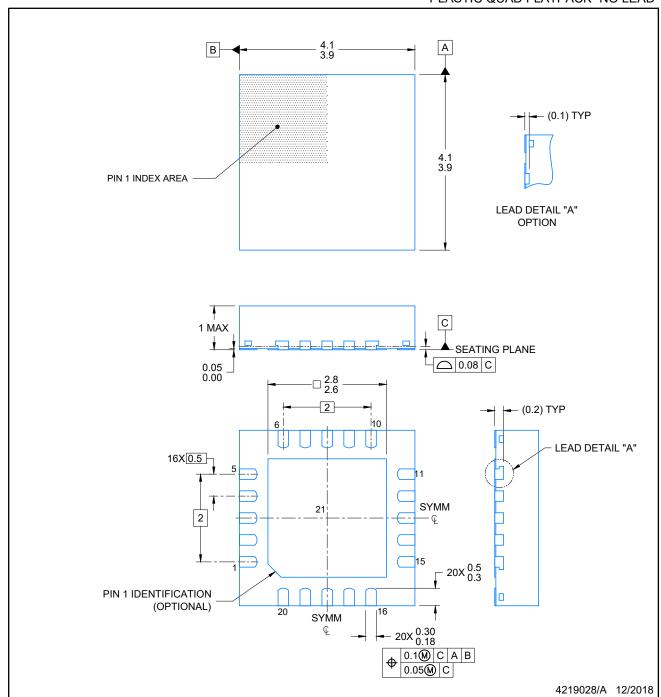

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- 4. Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

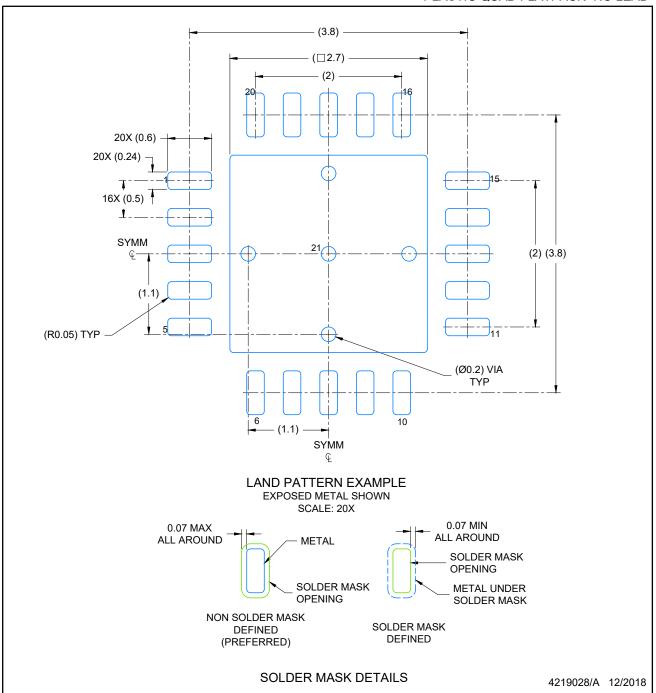

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- 10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

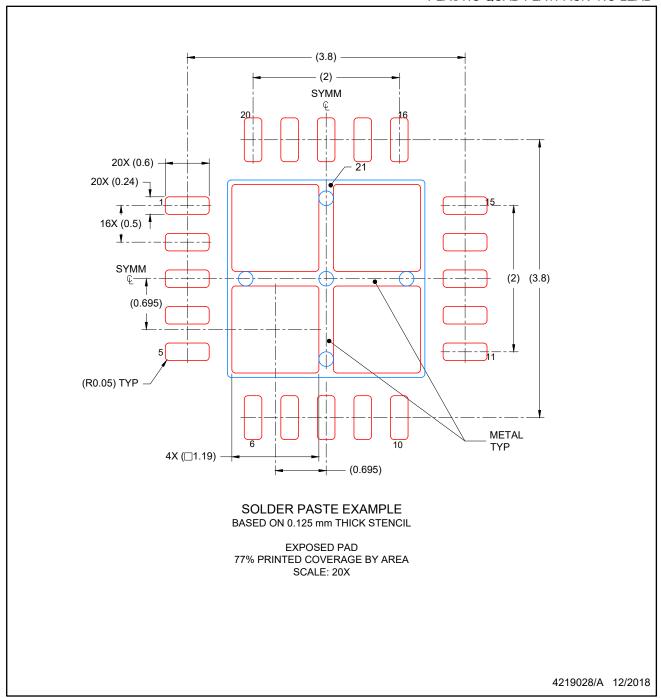

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

4 x 4, 0.5 mm pitch

VERY THIN QUAD FLATPACK

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224735/A

PLASTIC QUAD FLATPACK- NO LEAD

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025