# +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display Link-87.5 MHz

Check for Samples: DS90C385A

## **FEATURES**

- Pin-to-Pin Compatible to DS90C383, DS90C383A and DS90C385

- No Special Start-Up Sequence Required between Clock/Data and /PD Pins. Input Signals (Clock and Data) can be Applied Either Before or After the Device is Powered.

- Support Spread Spectrum Clocking up to 100kHz Frequency Modulation and Deviations of ±2.5% Center Spread or -5% Down Spread

- "Input Clock Detection" Feature Will Pull All LVDS Pairs to Logic Low When Input Clock is Missing and When /PD Pin is Logic High

- 18 to 87.5 MHz Shift Clock Support

- Tx Power Consumption < 147 mW (typ) at 87.5MHz Grayscale

- Tx Power-Down Mode < 60 μW (typ)</li>

- Supports VGA, SVGA, XGA, SXGA(Dual Pixel), SXGA+(Dual Pixel), UXGA(Dual Pixel).

- Narrow Bus Reduces Cable Size and Cost

- Up to 2.45 Gbps Throughput

- Up to 306.25Megabyte/sec Bandwidth

- 345 mV (typ) Swing LVDS Devices for Low EMI

- PLL Requires No External Components

- Compliant to TIA/EIA-644 LVDS standard

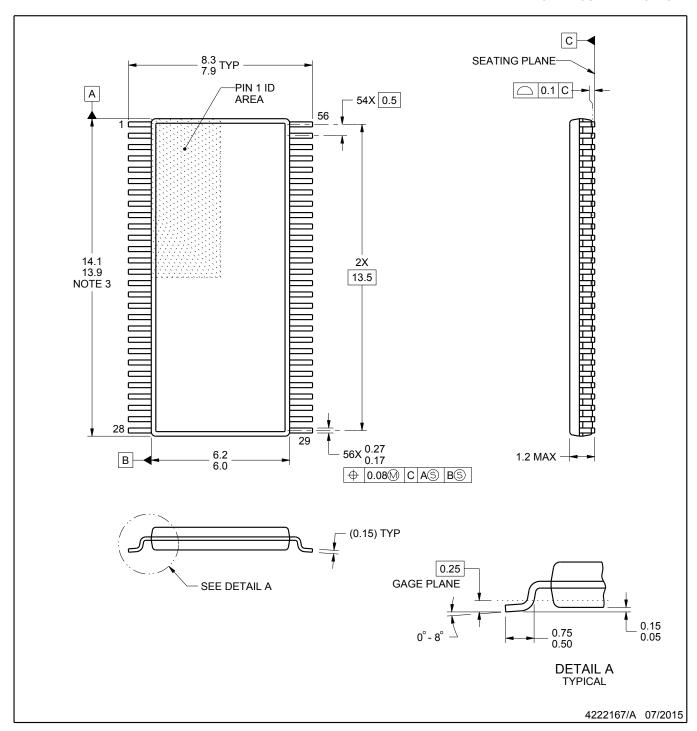

- Low Profile 56-lead TSSOP Package

#### DESCRIPTION

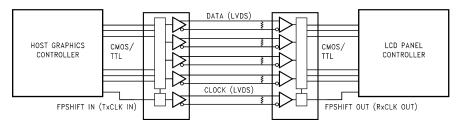

The DS90C385A is a pin to pin compatible replacement for DS90C383, DS90C383A and DS90C385. The DS90C385A has additional features and improvements making it an ideal replacement for DS90C383, DS90C383A and DS90C385. family of LVDS Transmitters.

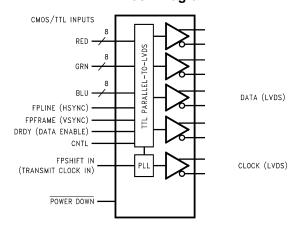

The DS90C385A transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over the fifth LVDS link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock frequency of 87.5 MHz, 24 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 612.5Mbps per LVDS data channel. Using a 87.5 MHz clock, the data throughput 306.25Mbytes/sec. This transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. A Rising edge or Falling edge strobe transmitter will interoperate with a Falling edge strobe FPDLink Receiver without any translation logic.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces with added Spread Spectrum Clocking support.

#### **Block Diagram**

Figure 1. DS90C385A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TRI-STATE is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Absolute Maximum Ratings(1)

| Absolute maximum rutings                           |                                   |                                   |

|----------------------------------------------------|-----------------------------------|-----------------------------------|

| Supply Voltage (V <sub>CC</sub> )                  | -0.3V to +4V                      |                                   |

| CMOS/TTL Input Voltage                             | -0.5V to (V <sub>CC</sub> + 0.3V) |                                   |

| LVDS Driver Output Voltage                         |                                   | -0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Output Short Circuit Duration                 |                                   | Continuous                        |

| Junction Temperature                               |                                   | +150°C                            |

| Storage Temperature                                | -65°C to +150°C                   |                                   |

| Lead Temperature (Soldering, 4 seconds)            |                                   | +260°C                            |

| Maximum Package Power Dissipation Capacity at 25°C | TSSOP Package                     | 1.63 W                            |

| Package Derating                                   |                                   | 12.5 mW/°C above +25°C            |

| ESD Rating                                         | HBM, 1.5kΩ, 100pF                 | 7kV                               |

|                                                    | EIAJ, 0Ω, 200 pF                  | 500V                              |

| Latch Up Tolerance at 25°C                         |                                   | ±100mA                            |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

## **Recommended Operating Conditions**

|                                                  | Min | Nom | Max  | Unit      |

|--------------------------------------------------|-----|-----|------|-----------|

| Supply Voltage (V <sub>CC</sub> )                | 3.0 | 3.3 | 3.6  | V         |

| Operating Free Air Temperature (T <sub>A</sub> ) | -10 | +25 | +70  | °C        |

| Supply Noise Voltage (V <sub>CC</sub> )          |     |     | 200  | $mV_{PP}$ |

| TxCLKIN frequency                                | 18  |     | 87.5 | MHz       |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                                                                        | Conditions                                                                                                                     |                | Min  | Тур   | Max             | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------|------|-------|-----------------|------|

| LVCMOS           | /LVTTL DC SPECIFICATIONS                                                                                         |                                                                                                                                |                |      |       |                 |      |

| V <sub>IH</sub>  | High Level Input Voltage                                                                                         |                                                                                                                                |                | 2.0  |       | V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Low Level Input Voltage                                                                                          |                                                                                                                                |                | 0    |       | 0.8             | V    |

| V <sub>CL</sub>  | Input Clamp Voltage                                                                                              | I <sub>CL</sub> = -18 mA                                                                                                       |                |      | -0.79 | -1.5            | V    |

| I <sub>IN</sub>  | Input Current                                                                                                    | $V_{IN} = 0.4V$ , 2.5V or $V_{CC}$                                                                                             |                |      | +1.8  | +10             | μΑ   |

|                  |                                                                                                                  | V <sub>IN</sub> = GND                                                                                                          |                | -10  | 0     |                 | μA   |

| LVDS DC          | SPECIFICATIONS                                                                                                   |                                                                                                                                |                | •    |       |                 |      |

| V <sub>OD</sub>  | Differential Output Voltage                                                                                      | $R_L = 100\Omega$                                                                                                              |                | 250  | 345   | 450             | mV   |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between complimentary output states                                                    |                                                                                                                                |                |      |       | 35              | mV   |

| Vos              | Offset Voltage (1)                                                                                               |                                                                                                                                |                | 1.13 | 1.25  | 1.38            | V    |

| ΔV <sub>OS</sub> | Change in V <sub>OS</sub> between complimentary output states                                                    |                                                                                                                                |                |      |       |                 |      |

| los              | Output Short Circuit Current                                                                                     | $V_{OUT} = 0V$ , $R_L = 100\Omega$                                                                                             |                |      | -3.5  | -5              | mA   |

| l <sub>OZ</sub>  | Output TRI-STATE® Current                                                                                        | Power Down = 0V,<br>V <sub>OUT</sub> = 0V or V <sub>CC</sub>                                                                   |                |      | ±1    | ±10             | μA   |

| TRANSM           | ITTER SUPPLY CURRENT                                                                                             |                                                                                                                                |                |      |       | 1               |      |

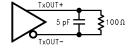

| ICCTW            | Transmitter Supply Current,                                                                                      | $R_L = 100\Omega$ ,                                                                                                            | f = 25 MHz     |      | 31    | 45              | mA   |

|                  | Worst Case                                                                                                       | C <sub>L</sub> = 5 pF,<br>Worst Case Pattern                                                                                   | f = 40 MHz     |      | 37    | 50              | mA   |

|                  |                                                                                                                  | (Figure 2 Figure 4 ) "Typ" values are                                                                                          | f = 65 MHz     |      | 48    | 60              | mA   |

|                  |                                                                                                                  | given for $V_{CC} = 3.6V$ and $T_A = +25^{\circ}C$ ,<br>"Max" values are given for $V_{CC} = 3.6V$<br>and $T_A = -10^{\circ}C$ | f = 87.5 MHz   |      | 55    | 65              | mA   |

| ICCTG            | Transmitter Supply Current,                                                                                      | $R_L = 100\Omega$ ,                                                                                                            | f = 25 MHz     |      | 29    | 40              | mA   |

|                  | 16 Grayscale                                                                                                     | C <sub>L</sub> = 5 pF,<br>16 Grayscale Pattern                                                                                 | f = 40 MHz     |      | 33    | 45              | mA   |

|                  |                                                                                                                  | (Figure 3 Figure 4 ) "Typ" values are                                                                                          | f = 65 MHz     |      | 39    | 50              | mA   |

|                  | given for $V_{CC}=3.6V$ and $T_A=+25^{\circ}C$ , "Max" values are given for $V_{CC}=3.6V$ and $T_A=-10^{\circ}C$ |                                                                                                                                | f = 87.5 MHz   |      | 44    | 55              | mA   |

| ICCTZ            | Transmitter Supply Current,<br>Power Down                                                                        | Power Down = Low<br>Driver Outputs in TRI-STATE® under Po                                                                      | ower Down Mode |      | 17    | 150             | μA   |

<sup>(1)</sup>  $V_{OS}$  previously referred as  $V_{CM}$ .

# **Recommended Transmitter Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                   | Min   | Тур  | Max   | Unit |

|--------|---------------------------------------------|-------|------|-------|------|

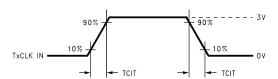

| TCIT   | TxCLK IN Transition Time (Figure 6)         | 1.0   |      | 6.0   | ns   |

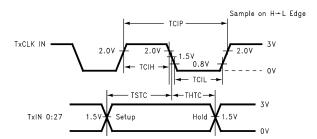

| TCIP   | TxCLK IN Period (Figure 7)                  | 11.42 | Т    | 55.55 | ns   |

| TCIH   | TxCLK IN High Time (Figure 7)               | 0.35T | 0.5T | 0.65T | ns   |

| TCIL   | TxCLK IN Low Time (Figure 7)                | 0.35T | 0.5T | 0.65T | ns   |

| TXIT   | TxIN , and PWR DOWN pin Transition Time     | 1.5   |      | 6.0   | ns   |

| TXPD   | Minimum pulse width for PWR DOWN pin signal | 1     |      |       | us   |

## **Transmitter Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                                                                                                                                                                              | Min                                                                                                                                                                                                           | Тур   | Max   | Unit  |    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----|

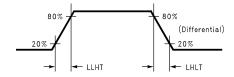

| LLHT   | LVDS Low-to-High Transition Time (Figure 5)                                                                                                                                                            |                                                                                                                                                                                                               | 0.75  | 1.4   | ns    |    |

| LHLT   | LVDS High-to-Low Transition Time (Figure 5)                                                                                                                                                            |                                                                                                                                                                                                               |       | 0.75  | 1.4   | ns |

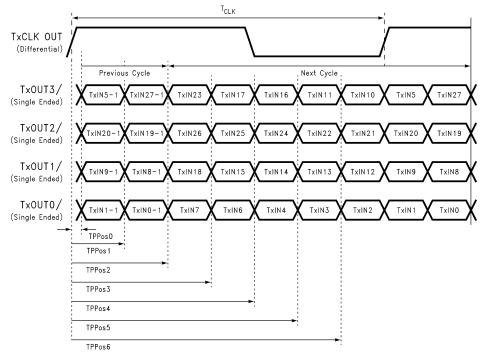

| TPPos0 | Transmitter Output Pulse Position (Figure 13) <sup>(1)</sup>                                                                                                                                           | -0.45                                                                                                                                                                                                         | 0     | +0.45 | ns    |    |

| TPPos1 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 5.26  | 5.71  | 6.16  | ns |

| TPPos2 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 10.98 | 11.43 | 11.88 | ns |

| TPPos3 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 16.69 | 17.14 | 17.59 | ns |

| TPPos4 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 22.41 | 22.86 | 23.31 | ns |

| TPPos5 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 28.12 | 28.57 | 29.02 | ns |

| TPPos6 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 33.84 | 34.29 | 34.74 | ns |

| TPPos0 | Transmitter Output Pulse Position (Figure 13) <sup>(1)</sup>                                                                                                                                           | f = 40 MHz                                                                                                                                                                                                    | -0.25 | 0     | +0.25 | ns |

| TPPos1 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 3.32  | 3.57  | 3.82  | ns |

| TPPos2 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 6.89  | 7.14  | 7.39  | ns |

| TPPos3 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 10.46 | 10.71 | 10.96 | ns |

| TPPos4 | Transmitter Output Pulse Position                                                                                                                                                                      | 1                                                                                                                                                                                                             | 14.04 | 14.29 | 14.54 | ns |

| TPPos5 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 17.61 | 17.86 | 18.11 | ns |

| TPPos6 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 21.18 | 21.43 | 21.68 | ns |

| TPPos0 | Transmitter Output Pulse Position (Figure 13)(1)                                                                                                                                                       | f = 65 MHz                                                                                                                                                                                                    | -0.20 | 0     | +0.20 | ns |

| TPPos1 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 2.00  | 2.20  | 2.40  | ns |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                                                                                                                                                            | =                                                                                                                                                                                                             | 4.20  | 4.40  | 4.60  | ns |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                                                                                                                                                            | =                                                                                                                                                                                                             | 6.39  | 6.59  | 6.79  | ns |

| TPPos4 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 8.59  | 8.79  | 8.99  | ns |

| TPPos5 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 10.79 | 10.99 | 11.19 | ns |

| TPPos6 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 12.99 | 13.19 | 13.39 | ns |

| TPPos0 | Transmitter Output Pulse Position (Figure 13)(1)                                                                                                                                                       | f = 87.5 MHz                                                                                                                                                                                                  | -0.20 | 0     | +0.20 | ns |

| TPPos1 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 1.48  | 1.68  | 1.88  | ns |

| TPPos2 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 3.16  | 3.36  | 3.56  | ns |

| TPPos3 | Transmitter Output Pulse Position                                                                                                                                                                      |                                                                                                                                                                                                               | 4.84  | 5.04  | 5.24  | ns |

| TPPos4 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 6.52  | 6.72  | 6.92  | ns |

| TPPos5 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 8.20  | 8.40  | 8.60  | ns |

| TPPos6 | Transmitter Output Pulse Position                                                                                                                                                                      | =                                                                                                                                                                                                             | 9.88  | 10.08 | 10.28 | ns |

| TSTC   | Required TxIN Setup to TxCLK IN (Figure 7) at 85MHz                                                                                                                                                    |                                                                                                                                                                                                               | 2.5   |       |       | ns |

| THTC   | Required TxIN Hold to TxCLK IN (Figure 7) at 87.5 MHz                                                                                                                                                  |                                                                                                                                                                                                               | 0.5   |       |       | ns |

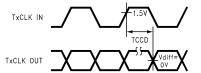

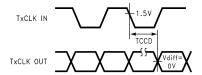

| TCCD   | TxCLK IN to TxCLK OUT Delay. Measure from TxCLK IN edge to immediately crossing point of differential TxCLK OUT by following the positive TxCLK OUT. 50% duty cycle input clock is assumed. (Figure 8) | $\begin{split} T_A &= -10^\circ, \text{ and} \\ 87.5\text{MHz for "Min",} \\ T_A &= 70^\circ, \text{ and} \\ 25\text{MHz for "Max",} \\ V_{CC} &= 3.6\text{V, R\_FB} \\ \text{pin} &= \text{VCC} \end{split}$ | 3.086 |       | 7.211 | ns |

|        | Measure from TxCLK IN edge to immediately crossing point of differential TxCLK OUT by following the positive TxCLK OUT. 50% duty cycle input clock is assumed. (Figure 9)                              | $T_A$ = -10°, and 87.5MHz for "Min", $T_A$ = 70°, and 25MHz for "Max", $V_{CC}$ = 3.6V, $R_FB$ pin = GND                                                                                                      | 2.868 |       | 6.062 | ns |

Submit Documentation Feedback

Copyright © 2004–2013, Texas Instruments Incorporated

<sup>(1)</sup> The Minimum and Maximum Limits are based on statistical analysis of the device performance over process, voltage, and temperature ranges. This parameter is functionality tested only on Automatic Test Equipment (ATE).

## **Transmitter Switching Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                                                      | Min          | Тур | Max                 | Unit |    |

|--------|--------------------------------------------------------------------------------|--------------|-----|---------------------|------|----|

| SSCG   | Spread Spectrum Clock support; Modulation frequency with a linear profile. (2) | f = 25 MHz   |     | 100kHz<br>±2.5%/-5% |      |    |

|        |                                                                                | f = 40 MHz   |     | 100kHz<br>±2.5%/-5% |      |    |

|        |                                                                                | f = 65 MHz   |     | 100kHz<br>±2.5%/-5% |      |    |

|        |                                                                                | f = 87.5 MHz |     | 100kHz<br>±2.5%/-5% |      |    |

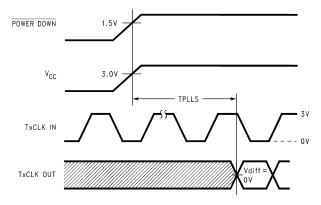

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 10)                                    |              |     |                     | 10   | ms |

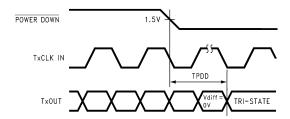

| TPDD   | Transmitter Power Down Delay (Figure 12)                                       |              |     |                     | 100  | ns |

(2) Care must be taken to ensure TSTC and THTC are met so input data are sampling correctly. This SSCG parameter only shows the performance of tracking Spread Spectrum Clock applied to TxCLK IN pin, and reflects the result on TxCLKOUT+ and TxCLKOUT- pins.

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/LVTTL I/O.

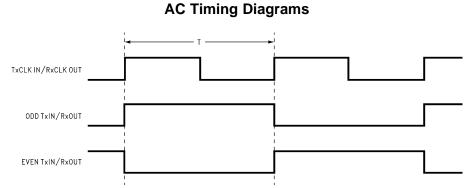

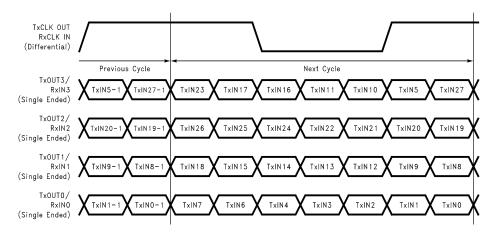

- B. Figure 2 and Figure 3 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

Figure 2. "Worst Case" Test Pattern

Copyright © 2004–2013, Texas Instruments Incorporated

## **AC Timing Diagrams (continued)**

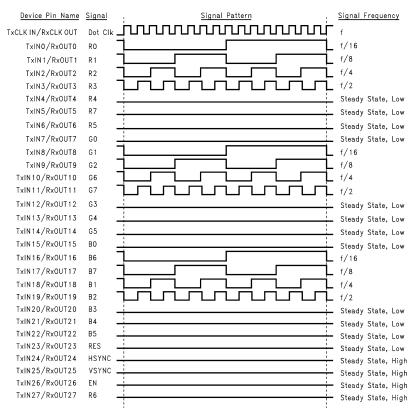

- A. The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

- B. Figure 2 and Figure 3 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

- C. Recommended pin to signal mapping. Customer may choose to define differently.

Figure 3. "16 Grayscale" Test Pattern - DS90C385A

Figure 4. DS90C385A (Transmitter) LVDS Output Load. 5pF is showed as board loading

Figure 5. DS90C385A (Transmitter) LVDS Transition Times

Figure 6. DS90C385A (Transmitter) Input Clock Transition Time

## **AC Timing Diagrams (continued)**

Figure 7. DS90C385A (Transmitter) Setup/Hold and High/Low Times with R\_FB pin = GND (Falling Edge Strobe)

Figure 8. DS90C385A (Transmitter) Clock In to Clock Out Delay with R\_FB pin = VCC

Figure 9. DS90C385A (Transmitter) Clock In to Clock Out Delay with R\_FB pin = GND

Figure 10. DS90C385A (Transmitter) Phase Lock Loop Set Time

## **AC Timing Diagrams (continued)**

Figure 11. 28 Parallel TTL Data Inputs Mapped to LVDS Outputs - DS90C385A

Figure 12. Transmitter Power Down Delay

Figure 13. Transmitter LVDS Output Pulse Position Measurement - DS90C385A

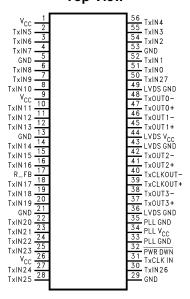

## DS90C385A DGG (TSSOP) Package Pin Descriptions — FPD Link Transmitter

| Pin Name             | I/O | No. | Description                                                                                                                                             |

|----------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxIN                 | I   | 28  | LVTTL level input. This includes: 8 Red, 8 Green, 8 Blue, and 4 control lines—FPLINE, FPFRAME and DRDY (also referred to as HSYNC, VSYNC, Data Enable). |

| TxOUT+               | 0   | 4   | Positive LVDS differential data output.                                                                                                                 |

| TxOUT-               | 0   | 4   | Negative LVDS differential data output.                                                                                                                 |

| TxCLKIN              | I   | 1   | LVTTL level clock input. Pin name TxCLK IN.                                                                                                             |

| R_FB                 | I   | 1   | LVTTL level programmable strobe select (See Table 1).                                                                                                   |

| TxCLK OUT+           | 0   | 1   | Positive LVDS differential clock output.                                                                                                                |

| TxCLK OUT-           | 0   | 1   | Negative LVDS differential clock output.                                                                                                                |

| PWR DOWN             | I   | 1   | LVTTL level input. When asserted (low input) TRI-STATE the outputs, ensuring low current at power down.                                                 |

| V <sub>CC</sub>      | I   | 3   | Power supply pins for LVTTL inputs.                                                                                                                     |

| GND                  | I   | 5   | Ground pins for LVTTL inputs.                                                                                                                           |

| PLL V <sub>CC</sub>  | I   | 1   | Power supply pin for PLL.                                                                                                                               |

| PLL GND              | I   | 2   | Ground pins for PLL.                                                                                                                                    |

| LVDS V <sub>CC</sub> | I   | 1   | Power supply pin for LVDS outputs.                                                                                                                      |

| LVDS GND             | I   | 3   | Ground pins for LVDS outputs.                                                                                                                           |

# Pin Diagram for TSSOP Package

## **Top View**

Order Number DS90C385AMT **DGG Package**

Product Folder Links: DS90C385A

#### APPLICATION INFORMATION

The DS90C385A is backward compatible with the DS90C385, DS90C383A, DS90C383 in TSSOP 56-lead package, and it is a pin-for-pin replacements.

This device DS90C385A also features reduced variation of the TCCD parameter which is important for dual pixel applications. (See AN-1084)

This device may also be used as a replacement for the DS90CF583 (5V, 65MHz) and DS90CF581 (5V, 40MHz) FPD-Link Transmitters with certain considerations/modifications:

- 1. Change 5V power supply to 3.3V. Provide this 3.3V supply to the  $V_{CC}$ , LVDS  $V_{CC}$  and PLL  $V_{CC}$  of the transmitter.

- The DS90C385A transmitter input and control inputs accept 3.3V LVTTL/LVCMOS levels. They are not 5V tolerant.

- 3. To implement a falling edge device for the DS90C385A, the R\_FB pin may be tied to ground OR left unconnected (an internal pull-down resistor biases this pin low). Biasing this pin to Vcc implements a rising edge device.

#### TRANSMITTER INPUT PINS

The TxIN and control input pins are compatible with LVCMOS and LVTTL levels. These pins are not 5V tolerant.

#### TRANSMITTER INPUT CLOCK/DATA SEQUENCING

Unlike the DS90C385, DS90C(F)383A/363A, the DS90C385A does not require any special requirement for sequencing of the input clock/data and PD (PowerDown) signal. The DS90C385A offers a more robust input sequencing feature where the input clock/data can be inserted after the release of the PD signal. In the case where the clock/data is stopped and reapplied, such as changing video mode within Graphics Controller, it is not necessary to cycle the PD signal. However, there are in certain cases where the PD may need to be asserted during these mode changes. In cases where the source (Graphics Source) may be supplying an unstable clock or spurious noisy clock output to the LVDS transmitter, the LVDS Transmitter may attempt to lock onto this unstable clock signal but is unable to do so due the instability or quality of the clock source. The PD signal in these cases should then be asserted once a stable clock is applied to the LVDS transmitter. Asserting the PWR DOWN pin will effectively place the device in reset and disable the PLL, enabling the LVDS Transmitter into a power saving standby mode. However, it is still generally a good practice to assert the PWR DOWN pin or reset the LVDS transmitter whenever the clock/data is stopped and reapplied but it is not mandatory for the DS90C385A.

#### SPREAD SPECTRUM CLOCK SUPPORT

The DS90C385A can support Spread Spectrum Clocking signal type inputs. The DS90C385A outputs will accurately track Spread Spectrum Clock/Data inputs with modulation frequencies of up to 100kHz (max.)with either center spread of ±2.5% or down spread -5% deviations.

#### **POWER SOURCES SEQUENCE**

In typical applications, it is recommended to have  $V_{CC}$ , LVDS  $V_{CC}$  and PLL  $V_{CC}$  from the same power source with three separate de-coupling bypass capacitor groups. There is no requirement on which VCC entering the device first.

## **Typical Application**

Figure 14. Typical Application

# Table 1. Truth Table – Programmable Transmitter (DS90C385A)

| Pin  | Condition        | Strobe Status       |

|------|------------------|---------------------|

| R_FB | $R_FB = V_{CC}$  | Rising edge strobe  |

| R_FB | R_FB = GND or NC | Falling edge strobe |

## SNLS167K - MARCH 2004-REVISED APRIL 2013

## **REVISION HISTORY**

| Cł | nanges from Revision J (April 2013) to Revision K  | Pa | ıge |

|----|----------------------------------------------------|----|-----|

| •  | Changed layout of National Data Sheet to TI format |    | 11  |

www.ti.com 1-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                 |              |              |

| DS90C385AMT/NOPB      | Active | Production    | TSSOP (DGG)   56 | 34   TUBE             | Yes  | SN            | Level-2-260C-1 YEAR | -10 to 70    | DS90C385AMT  |

| DS90C385AMT/NOPB.A    | Active | Production    | TSSOP (DGG)   56 | 34   TUBE             | Yes  | SN            | Level-2-260C-1 YEAR | -10 to 70    | DS90C385AMT  |

| DS90C385AMTX/NOPB     | Active | Production    | TSSOP (DGG)   56 | 1000   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -10 to 70    | DS90C385AMT  |

| DS90C385AMTX/NOPB.A   | Active | Production    | TSSOP (DGG)   56 | 1000   LARGE T&R      | Yes  | SN            | Level-2-260C-1 YEAR | -10 to 70    | DS90C385AMT  |

| DS90C385AMTX/NOPB.B   | Active | Production    | TSSOP (DGG)   56 | 1000   LARGE T&R      | -    | Call TI       | Call TI             | -10 to 70    |              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Oct-2025

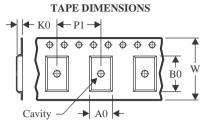

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

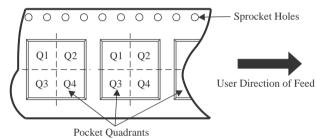

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device            |       | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DS90C385AMTX/NOPB | TSSOP | DGG                | 56 | 1000 | 330.0                    | 24.4                     | 8.6        | 14.5       | 1.8        | 12.0       | 24.0      | Q1               |

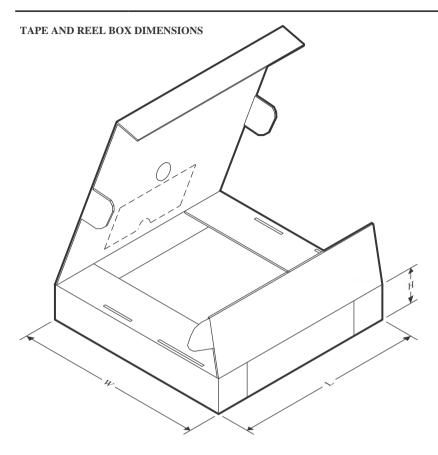

**PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Oct-2025

### \*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS90C385AMTX/NOPB | TSSOP        | DGG             | 56   | 1000 | 356.0       | 356.0      | 45.0        |

# **PACKAGE MATERIALS INFORMATION**

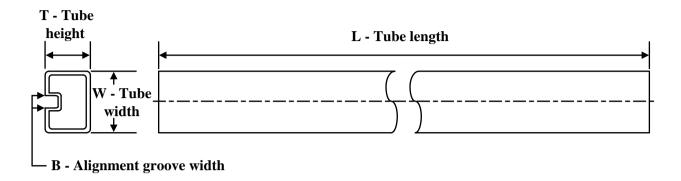

www.ti.com 31-Oct-2025

## **TUBE**

#### \*All dimensions are nominal

| Device             | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| DS90C385AMT/NOPB   | DGG          | TSSOP        | 56   | 34  | 495    | 10     | 2540   | 5.79   |

| DS90C385AMT/NOPB.A | DGG          | TSSOP        | 56   | 34  | 495    | 10     | 2540   | 5.79   |

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

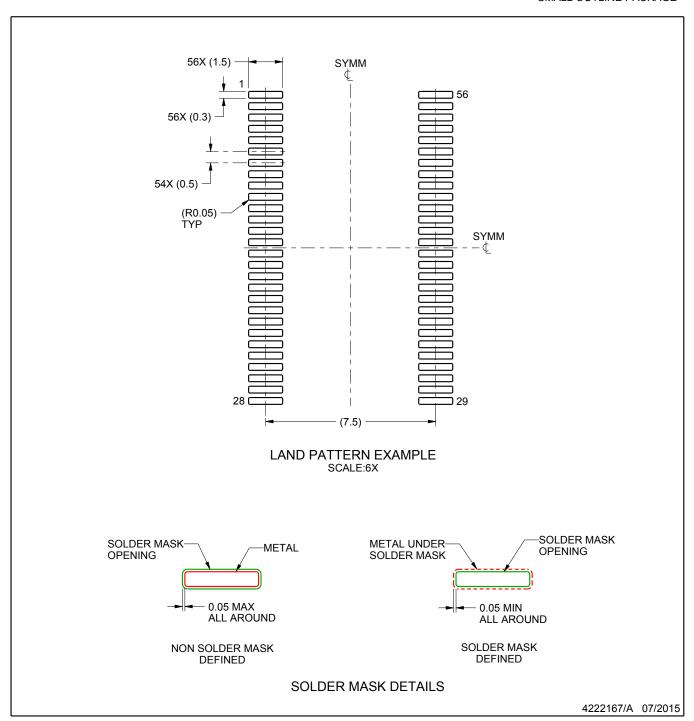

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.

- 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

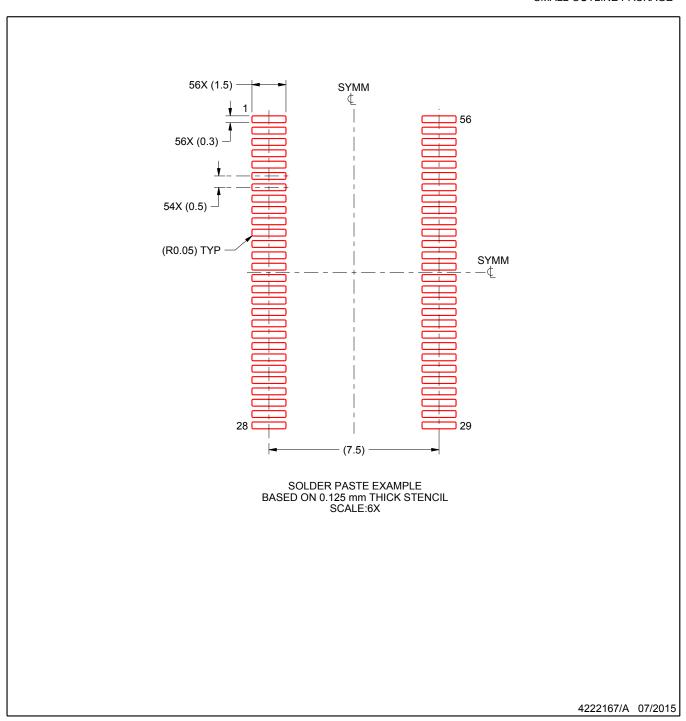

SMALL OUTLINE PACKAGE

NOTES: (continued)

- Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 8. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025