INA200, INA201, INA202

SBOS374E - NOVEMBER 2006 - REVISED SEPTEMBER 2017

# INA20x High-Side Measurement Current-Shunt Monitor With Open-Drain Comparator and Reference

## **Features**

- Complete Current Sense Solution

- Three Gain Options Available:

- INA200 = 20 V/V

- INA201 = 50 V/V

- INA202 = 100 V/V

- 0.6-V Internal Voltage Reference

- Internal Open-Drain Comparator

- Latching Capability on Comparator

- Common-Mode Range: -16 V to 80 V

- High Accuracy: 3.5% Maximum Error Over Temperature

- Bandwidth: 500 kHz (INA200)

- Quiescent Current: 1800 µA (Maximum)

- Packages: SOIC-8, VSSOP-8

## **Applications**

- **Notebook Computers**

- Cell Phones

- Telecom Equipment

- Automotive

- **Power Management**

- **Battery Chargers**

- Welding Equipment

## 3 Description

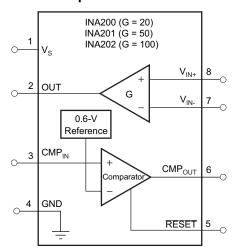

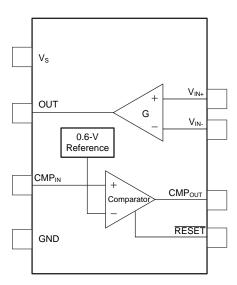

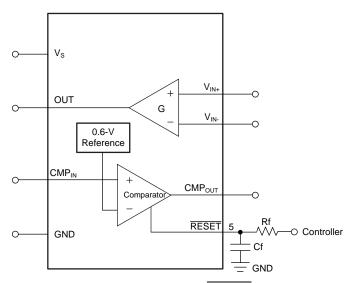

The INA200, INA201, and INA202 devices are highside current-shunt monitors with voltage output and integrated comparator. The INA20x devices can sense drops across shunts at common-mode voltages from -16 V to 80 V. The INA20x series is available with three output voltage scales: 20 V/V, 50 V/V, and 100 V/V, with a bandwidth up to 500-kHz.

INA200, INA201, and INA202 incorporate an open-drain comparator and internal reference providing a 0.6-V threshold. External dividers set the current trip point. The comparator includes a latching capability, that can be made transparent by grounding (or leaving open) the RESET pin.

The INA200, INA201, and INA202 devices operate from a single 2.7-V to 18-V supply, drawing a maximum of 1800 μA of supply current. Package options include the very small VSSOP-8 and the SOIC-8. All versions are specified over the extended operating temperature range of -40°C to +125°C.

## Device Information<sup>(1)</sup>

| PART NUMBER      | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

|------------------|-----------|-------------------|--|--|--|--|

| INA200           | SOIC (8)  | 4.90 mm × 3.91 mm |  |  |  |  |

| INA201<br>INA202 | VSSOP (8) | 3.00 mm × 3.00 mm |  |  |  |  |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the data sheet.

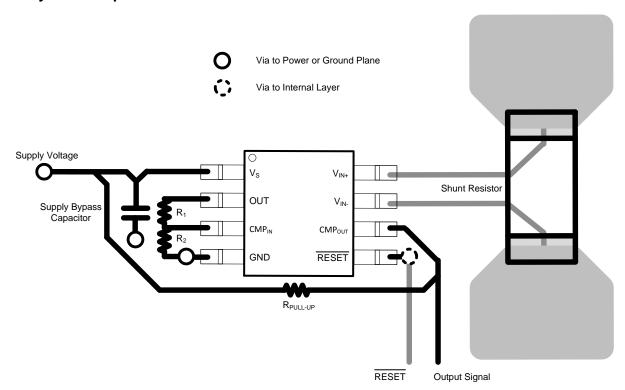

#### Simplified Schematic

Copyright © 2017, Texas Instruments Incorporated

| Table ( | of ( | Con | tents |

|---------|------|-----|-------|

|---------|------|-----|-------|

| 1 | Features 1                                              |    | 7.3 Feature Description                          | 13 |

|---|---------------------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                                          |    | 7.4 Device Functional Modes                      | 19 |

| 3 | Description 1                                           | 8  | Application and Implementation                   | 22 |

| 4 | Revision History2                                       |    | 8.1 Application Information                      | 22 |

| 5 | Pin Configuration and Functions                         |    | 8.2 Typical Application                          | 22 |

| 6 | Specifications4                                         | 9  | Power Supply Recommendations                     | 23 |

| · | 6.1 Absolute Maximum Ratings                            |    | 9.1 Output vs Supply Ramp Considerations         | 23 |

|   | 6.2 ESD Ratings                                         | 10 | Layout                                           | 25 |

|   | 6.3 Recommended Operating Conditions                    |    | 10.1 Layout Guidelines                           | 25 |

|   | 6.4 Thermal Information                                 |    | 10.2 Layout Example                              | 25 |

|   | 6.5 Electrical Characteristics: Current-Shunt Monitor 5 | 11 | Device and Documentation Support                 | 26 |

|   | 6.6 Electrical Characteristics: Comparator              |    | 11.1 Related Links                               | 26 |

|   | 6.7 Electrical Characteristics: General                 |    | 11.2 Community Resources                         | 26 |

|   | 6.8 Typical Characteristics 9                           |    | 11.3 Trademarks                                  | 26 |

| 7 | Detailed Description                                    |    | 11.4 Electrostatic Discharge Caution             | 26 |

|   | 7.1 Overview                                            |    | 11.5 Glossary                                    | 26 |

|   | 7.2 Functional Block Diagram                            | 12 | Mechanical, Packaging, and Orderable Information | 26 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision D (October 2015) to Revision E                                                                                                                                                                | Page |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Reformatted Thermal Information table note                                                                                                                                                                         | 4    |

| • | Corrected typo in Voltage Output section in Electrical Characteristics table                                                                                                                                       | 6    |

| • | Added text to Comparator subsection in Feature Description section                                                                                                                                                 | 14   |

| • | Added Figure 31 to Feature Description section                                                                                                                                                                     | 18   |

| • | Added Output vs Supply Ramp Considerations subsection in Feature Description section                                                                                                                               | 23   |

| • | Added Figure 36, Figure 37, and Figure 38                                                                                                                                                                          | 23   |

| С | hanges from Revision C (October 2010) to Revision D                                                                                                                                                                | Page |

| • | Added ESD Ratings table, Thermal Information table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and | rage |

|   | Documentation Support section, and Mechanical, Packaging, and Orderable Information section                                                                                                                        | 4    |

|   |                                                                                                                                                                                                                    |      |

|   |                                                                                                                                                                                                                    |      |

| С | hanges from Revision B (October, 2007) to Revision C                                                                                                                                                               | Page |

Submit Documentation Feedback

Copyright © 2006–2017, Texas Instruments Incorporated

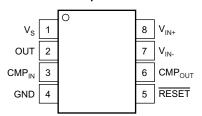

## 5 Pin Configuration and Functions

## DGK and D Packages 8-Pin VSSOP and SOIC Top View

## **Pin Functions**

| PI                 | IN  | I/O           | DESCRIPTION                      |

|--------------------|-----|---------------|----------------------------------|

| NAME               | NO. | 1/0           | DESCRIPTION                      |

| CMPIN              | 3   | Analog input  | Comparator input                 |

| CMP <sub>OUT</sub> | 6   | Analog output | Comparator output                |

| GND                | 4   | Analog        | Ground                           |

| OUT                | 2   | Analog output | Output voltage                   |

| RESET              | 5   | Analog input  | Comparator reset pin, active low |

| V <sub>IN</sub> -  | 7   | Analog input  | Connect to shunt low side        |

| V <sub>IN+</sub>   | 8   | Analog input  | Connect to shunt high side       |

| Vs                 | 1   | Analog        | Power supply                     |

Copyright © 2006–2017, Texas Instruments Incorporated

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                          |                                                        | MIN       | MAX           | UNIT |

|--------------------------------------------------------------------------|--------------------------------------------------------|-----------|---------------|------|

| Supply voltage, V <sub>s</sub>                                           |                                                        | 2.7       | 18            | V    |

| Current-shunt monitor analog inputs, V <sub>IN+</sub> , V <sub>IN-</sub> | Differential (V <sub>IN+</sub> ) – (V <sub>IN</sub> -) | -18       | 18            | V    |

|                                                                          | Common-mode <sup>(2)</sup>                             | -16       | 80            | V    |

| Comparator analog input                                                  | and reset pins <sup>(2)</sup>                          | GND – 0.3 | $(V_s) + 0.3$ | V    |

| Analog output, OUT(2)                                                    |                                                        | GND – 0.3 | $(V_s) + 0.3$ | V    |

| Comparator output, OUT                                                   | (2)                                                    | GND – 0.3 | 18            | V    |

| Input current into any pin                                               | (2)                                                    |           | 5             | mA   |

| Operating temperature                                                    |                                                        | -55       | 150           | °C   |

| Junction temperature                                                     |                                                        | -65       | 150           | °C   |

| Storage temperature, T <sub>stg</sub>                                    | 1                                                      | -65       | 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                                | MIN | NOM | MAX | UNIT |

|----------|--------------------------------|-----|-----|-----|------|

| $V_{CM}$ | Common-mode input voltage      | -16 | 12  | 80  | V    |

| Vs       | Operating supply voltage       | 2.7 | 12  | 18  | V    |

| $T_A$    | Operating free-air temperature | -40 | 25  | 125 | °C   |

#### 6.4 Thermal Information

|                      |                                              | IN       | INA20x     |      |  |

|----------------------|----------------------------------------------|----------|------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGK (SOIC) | UNIT |  |

|                      |                                              | 8 PINS   | 8 PINS     |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 110.5    | 162.2      | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 50.4     | 37.7       | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 52.7     | 82.9       | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 7.8      | 1.3        | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 51.9     | 81.4       | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>2)</sup> This voltage may exceed the ratings shown if the current at that pin is limited to 5 mÅ.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.5 Electrical Characteristics: Current-Shunt Monitor

at  $T_A$  = 25°C,  $V_S$  = 12 V,  $V_{CM}$  = 12 V,  $V_{SENSE}$  = 100 mV,  $R_L$  = 10 k $\Omega$  to GND,  $R_{PULL-UP}$  = 5.1 k $\Omega$  connected from CMP<sub>OUT</sub> to  $V_S$ , and CMP<sub>IN</sub> = GND, (unless otherwise noted)

|                                                                                                                                                     | PARAMETER                               | TEST CONDITIONS                                                                                    | MIN | TYP  | MAX                            | UNIT  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|--------------------------------|-------|

| INPUT                                                                                                                                               |                                         |                                                                                                    |     |      |                                |       |

| V <sub>SENSE</sub>                                                                                                                                  | Full-scale sense input voltage          | $V_{SENSE} = V_{IN+} - V_{IN-}$                                                                    |     | 0.15 | (V <sub>S</sub> - 0.25) / Gain | V     |

| V <sub>CM</sub>                                                                                                                                     | Common-mode input range                 | T <sub>A</sub> = -40°C to 125°C                                                                    | -16 |      | 80                             | V     |

| OMD                                                                                                                                                 | Common mondo animatica                  | $V_{IN+} = -16 \text{ V to } 80 \text{ V}$                                                         | 80  | 100  |                                | dB    |

| CIVIR                                                                                                                                               | Common-mode rejection                   | V <sub>IN+</sub> = 12 V to 80 V, T <sub>A</sub> = -40°C to 125°C                                   | 100 | 123  |                                | dB    |

|                                                                                                                                                     |                                         | T <sub>A</sub> = 25°C                                                                              |     | ±0.5 | ±2.5                           | mV    |

| V <sub>CM</sub> Col           CMR         Col           V <sub>OS</sub> Offs           dV <sub>OS</sub> /dT         Offs           PSR         Offs | Offset voltage, RTI <sup>(1)</sup>      | T <sub>A</sub> = 25°C to 125°C                                                                     |     |      | ±3                             | mV    |

|                                                                                                                                                     |                                         | $T_A = -40$ °C to 25°C                                                                             |     |      | ±3.5                           | mV    |

| dV <sub>OS</sub> /dT                                                                                                                                | Offset voltage, RTI, vs temperature     | $T_{MIN}$ to $T_{MAX}$ , $T_{A} = -40^{\circ}$ C to 125°C                                          |     | 5    |                                | μV/°C |

| PSR                                                                                                                                                 | Offset voltage, RTI, vs power supply    | $V_{OUT} = 2 \text{ V}, V_{IN+} = 18 \text{ V}, 2.7 \text{ V}, T_A = -40^{\circ}\text{C to}$ 125°C |     | 2.5  | 100                            | μV/V  |

| I <sub>B</sub>                                                                                                                                      | Input bias current, V <sub>IN</sub> pin | $T_A = -40$ °C to 125°C                                                                            |     | ±9   | ±16                            | μΑ    |

<sup>(1)</sup> Offset is extrapolated from measurements of the output at 20-mV and 100-mV  $V_{SENSE}$ .

## **Electrical Characteristics: Current-Shunt Monitor (continued)**

at  $T_A$  = 25°C,  $V_S$  = 12 V,  $V_{CM}$  = 12 V,  $V_{SENSE}$  = 100 mV,  $R_L$  = 10 k $\Omega$  to GND,  $R_{PULL-UP}$  = 5.1 k $\Omega$  connected from CMP<sub>OUT</sub> to  $V_S$ , and CMP<sub>IN</sub> = GND, (unless otherwise noted)

|                | PARAMETER                                     | TEST C                                                                      | ONDITIONS                                                                       | MIN TYP                  | MAX            | UNIT               |

|----------------|-----------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------|----------------|--------------------|

| OUTPU          | T (V <sub>SENSE</sub> ≥ 20 mV)                |                                                                             | ·                                                                               |                          |                |                    |

|                |                                               | INA200                                                                      |                                                                                 | 20                       |                | V/V                |

| G              | Gain                                          | INA201                                                                      |                                                                                 | 50                       |                | V/V                |

|                |                                               | INA202                                                                      |                                                                                 | 100                      |                | V/V                |

|                |                                               | V <sub>SENSE</sub> = 20 mV to 10                                            | O mV                                                                            | ±0.2%                    | ±1%            |                    |

|                | Gain error                                    | V <sub>SENSE</sub> = 20 mV to 100<br>125°C                                  | 0 mV, $T_A = -40^{\circ}$ C to                                                  |                          | ±2%            |                    |

|                |                                               | V <sub>SENSE</sub> = 120 mV, V <sub>S</sub>                                 | = 16 V                                                                          | ±0.75%                   | ±2.2%          |                    |

|                | Total output error <sup>(2)</sup>             | V <sub>SENSE</sub> = 120 mV, V <sub>S</sub> = 125°C                         |                                                                                 |                          | ±3.5%          |                    |

|                | Nonlinearity error <sup>(3)</sup>             | V <sub>SENSE</sub> = 20 mV to 10                                            | SENSE = 20 mV to 100 mV                                                         |                          |                |                    |

| R <sub>O</sub> | Output impedance                              |                                                                             |                                                                                 | 1.5                      |                | Ω                  |

|                | Maximum capacitive load                       | No sustained oscillation                                                    | n                                                                               | 10                       |                | nF                 |

| OUTPU          | T (V <sub>SENSE</sub> < 20 mV) <sup>(4)</sup> |                                                                             |                                                                                 |                          |                |                    |

|                |                                               | INA200, INA201,<br>INA202                                                   | -16 V ≤ V <sub>CM</sub> < 0 V                                                   | 300                      |                | mV                 |

|                |                                               | INA200                                                                      | $0 V \le V_{CM} \le V_S, V_S = 5 V$                                             |                          | 0.4            | V                  |

|                | Output                                        | INA201                                                                      | $0 V \le V_{CM} \le V_S, V_S = 5 V$                                             |                          | 1              | V                  |

|                |                                               | INA202                                                                      | $\begin{array}{c} 0 \ V \leq V_{CM} \leq V_{S}, \ V_{S} = \\ 5 \ V \end{array}$ |                          | 2              | V                  |

|                |                                               | INA200, INA201,<br>INA202                                                   | V <sub>S</sub> < V <sub>CM</sub> ≤ 80 V                                         | 300                      |                | mV                 |

| VOLTA          | GE OUTPUT <sup>(5)</sup>                      |                                                                             |                                                                                 |                          |                |                    |

|                | Output swing to the positive rail             | V <sub>IN-</sub> = 11 V, V <sub>IN+</sub> = 12                              | V, T <sub>A</sub> = -40°C to 125°C                                              | (V <sub>s</sub> ) – 0.15 | $(V_s) - 0.25$ | V                  |

|                | Output swing to GND (6)                       | $V_{IN-} = 0 \text{ V}, V_{IN+} = -0.5$                                     | $V, T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                                | (GND) + 0.004            | (GND) + 0.05   | V                  |

| FREQU          | ENCY RESPONSE                                 |                                                                             |                                                                                 |                          |                |                    |

|                |                                               | INA200                                                                      | C <sub>LOAD</sub> = 5 pF                                                        | 500                      |                | kHz                |

| BW             | Bandwidth                                     | INA201                                                                      | C <sub>LOAD</sub> = 5 pF                                                        | 300                      |                | kHz                |

|                |                                               | INA202                                                                      | C <sub>LOAD</sub> = 5 pF                                                        | 200                      |                | kHz                |

|                | Phase margin                                  | C <sub>LOAD</sub> < 10 nF                                                   |                                                                                 | 40                       |                | °C                 |

| SR             | Slew rate                                     |                                                                             |                                                                                 | 1                        |                | V/μs               |

|                | Settling time (1%)                            | $V_{SENSE} = 10 \text{ mV}_{PP} \text{ to } 1$<br>$C_{LOAD} = 5 \text{ pF}$ | 00 mV <sub>PP</sub> ,                                                           | 2                        |                | μS                 |

| NOISE,         | RTI                                           | •                                                                           | -                                                                               |                          |                |                    |

|                | Voltage noise density                         |                                                                             |                                                                                 | 40                       |                | nV/√ <del>Hz</del> |

<sup>(2)</sup> Total output error includes effects of gain error and VOS.

<sup>(3)</sup> Linearity is best fit to a straight line.

<sup>(4)</sup> For details on this region of operation, see Accuracy Variations section in Device Functional Modes.

<sup>(5)</sup> See Figure 8.

<sup>(6)</sup> Specified by design.

## 6.6 Electrical Characteristics: Comparator

at  $T_A$  = 25°C,  $V_S$  = 12 V,  $V_{CM}$  = 12 V,  $V_{SENSE}$  = 100 mV,  $R_L$  = 10 k $\Omega$  to GND, and  $R_{PULL-UP}$  = 5.1 k $\Omega$  connected from CMP<sub>OUT</sub> to  $V_S$ , (unless otherwise noted)

|                  | PARAMETER                                                 | TEST CONDITIONS                                                                          | MIN    | TYP                    | MAX | UNIT |

|------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|--------|------------------------|-----|------|

| OFFSET           | VOLTAGE                                                   |                                                                                          |        |                        | '   |      |

|                  | Threshold                                                 | T <sub>A</sub> = 25°C                                                                    | 590    | 608                    | 620 | mV   |

|                  | mesnoid                                                   | T <sub>A</sub> = -40°C to 125°C                                                          | 586    |                        | 625 | mV   |

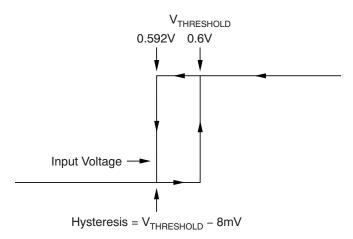

|                  | Hysteresis (1)                                            | T <sub>A</sub> = -40°C to 85°C                                                           |        | -8                     |     | mV   |

| INPUT BI         | AS CURRENT <sup>(2)</sup>                                 |                                                                                          |        |                        |     |      |

|                  | Input bias current, CMP <sub>in</sub> PIN                 |                                                                                          |        | 0.005                  | 10  | nA   |

|                  | Input bias current, CMP <sub>in</sub> PIN, vs temperature | T <sub>A</sub> = -40°C to 125°C                                                          |        |                        | 15  | nA   |

| INPUT VO         | DLTAGE RANGE                                              |                                                                                          |        |                        |     |      |

|                  | Input voltage range, CMP <sub>in</sub> PIN                |                                                                                          | 0 V to | V <sub>S</sub> – 1.5 V |     | V    |

| OUTPUT           | (OPEN-DRAIN)                                              |                                                                                          |        |                        |     |      |

|                  | Large-signal differential voltage gain                    | CMP V <sub>OUT</sub> 1 V to 4 V,<br>R <sub>L</sub> $\geq$ 15 k $\Omega$ connected to 5 V |        | 200                    |     | V/mV |

| I <sub>LKG</sub> | High-level leakage current (3)(4)                         | V <sub>ID</sub> = 0.4 V, V <sub>OH</sub> = V <sub>S</sub>                                |        | 0.0001                 | 1   | μΑ   |

| V <sub>OL</sub>  | Low-level output voltage <sup>(3)</sup>                   | $V_{ID} = -0.6 \text{ V}, I_{OL} = 2.35 \text{ mA}$                                      |        | 220                    | 300 | mV   |

| RESPON           | SE TIME                                                   |                                                                                          |        |                        |     |      |

|                  | Response time <sup>(5)</sup>                              | R <sub>L</sub> to 5 V, C <sub>L</sub> = 15 pF, 100-mV Input<br>Step with 5-mV overdrive  |        | 1.3                    |     | μs   |

| RESET            |                                                           |                                                                                          |        |                        | *   |      |

|                  | RESET threshold <sup>(6)</sup>                            |                                                                                          |        | 1.1                    |     | V    |

|                  | Logic input impedance                                     |                                                                                          |        | 2                      |     | MΩ   |

|                  | Minimum RESET pulse width                                 |                                                                                          |        | 1.5                    |     | μS   |

|                  | RESET propagation delay                                   |                                                                                          |        | 3                      |     | μS   |

- (1) Hysteresis refers to the threshold (the threshold specification applies to a rising edge of a noninverting input) of a falling edge on the noninverting input of the comparator; refer to Figure 1.

- (2) Specified by design.

- (3) V<sub>ID</sub> refers to the differential voltage at the comparator inputs.

- (4) Open-drain output can be pulled to the range of 2.7 to 18 V, regardless of V<sub>s</sub>.

- (5) The comparator response time specified is the interval between the input step function and the instant when the output crosses 1.4 V.

- (6) The RESET input has an internal 2 MΩ (typical) pull-down. Leaving RESET open results in a LOW state, with transparent comparator operation.

#### 6.7 Electrical Characteristics: General

at  $T_A$  = 25°C,  $V_S$  = 12 V,  $V_{CM}$  = 12 V,  $V_{SENSE}$  = 100 mV,  $R_L$  = 10 k $\Omega$  to GND,  $R_{PULL-UP}$  = 5.1 k $\Omega$  connected from CMP<sub>OUT</sub> to  $V_S$ , and CMP<sub>IN</sub> = 1 V, unless otherwise noted.

|                   | PARAMETER                                          | TEST CONDITIONS                             | MIN | TYP  | MAX  | UNIT |

|-------------------|----------------------------------------------------|---------------------------------------------|-----|------|------|------|

| POWE              | R SUPPLY                                           |                                             |     |      |      |      |

| Vs                | Operating power supply                             | T <sub>A</sub> = -40°C to 125°C             | 2.7 |      | 18   | V    |

|                   | Outpoont surrent                                   | V <sub>OUT</sub> = 2 V                      |     | 1350 | 1800 | μА   |

| IQ                | Quiescent current                                  | $V_{SENSE} = 0$ mV, $T_A = -40$ °C to 125°C |     |      | 1850 | μА   |

|                   | Comparator power-on reset threshold <sup>(1)</sup> |                                             |     | 1.5  |      | ٧    |

| TEMPI             | ERATURE                                            |                                             | -   |      |      |      |

|                   | Specified temperature                              |                                             | -40 |      | 125  | °C   |

|                   | Operating temperature                              |                                             | -55 |      | 150  | °C   |

|                   | Storage temperature                                |                                             | -65 |      | 150  | °C   |

| 0                 | The area of an electrical and                      | VSSOP-8 Surface-Mount                       |     | 200  |      | °C/W |

| $\theta_{\sf JA}$ | Thermal resistance                                 | SOIC-8                                      |     | 150  |      | °C/W |

(1) The INA200, INA201, and INA202 are designed to power-up with the comparator in a defined reset state as long as RESET is open or grounded. The comparator is in reset as long as the power supply is below the voltage shown here. The comparator assumes a state based on the comparator input above this supply voltage. If RESET is high at power-up, the comparator output comes up high and requires a reset to assume a low state, if appropriate.

Figure 1. Typical Comparator Hysteresis

20

18

16

14

12

10

8

6

4

2

20

100

200

300

Vou

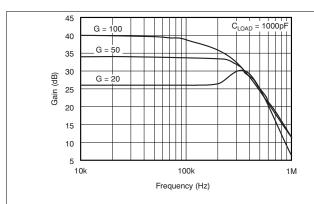

## 6.8 Typical Characteristics

at  $T_A = 25$ °C,  $V_S = 12$  V,  $V_{IN+} = 12$  V, and  $V_{SENSE} = 100$  mV, (unless otherwise noted)

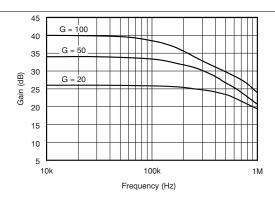

Figure 2. Gain vs Frequency

Figure 2. Gain vs Frequency

600

700

800

Figure 3. Gain vs Frequency

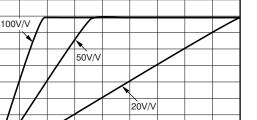

Figure 4. Gain Plot

400 500

V<sub>DIFFERENTIAL</sub> (mV)

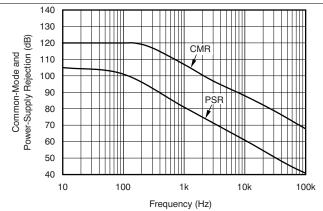

Figure 5. Common-Mode and Power-Supply Rejection vs Frequency

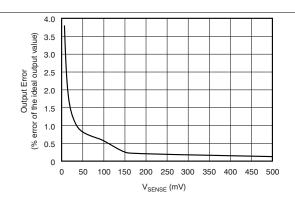

Figure 6. Output Error vs V<sub>SENSE</sub>

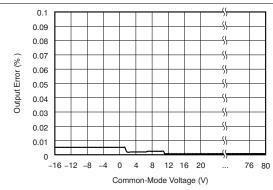

Figure 7. Output Error vs Common-Mode Voltage

# TEXAS INSTRUMENTS

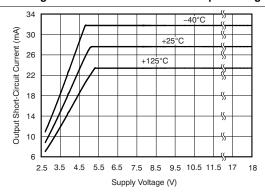

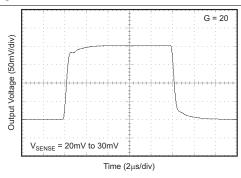

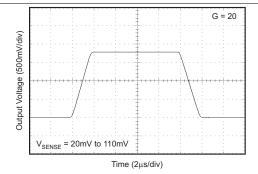

## **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_S = 12$  V,  $V_{IN+} = 12$  V, and  $V_{SENSE} = 100$  mV, (unless otherwise noted)

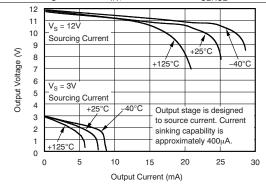

Figure 8. Positive Output Voltage Swing vs Output Current

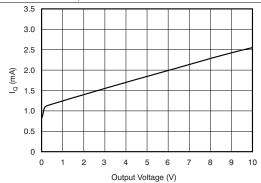

Figure 9. Quiescent Current vs Output Voltage

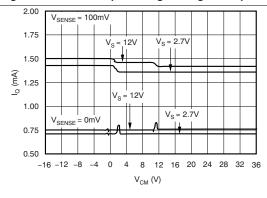

Figure 10. Quiescent Current vs Common-Mode Voltage

Figure 11. Output Short-Circuit Current vs Supply Voltage

Figure 12. Step Response

Figure 13. Step Response

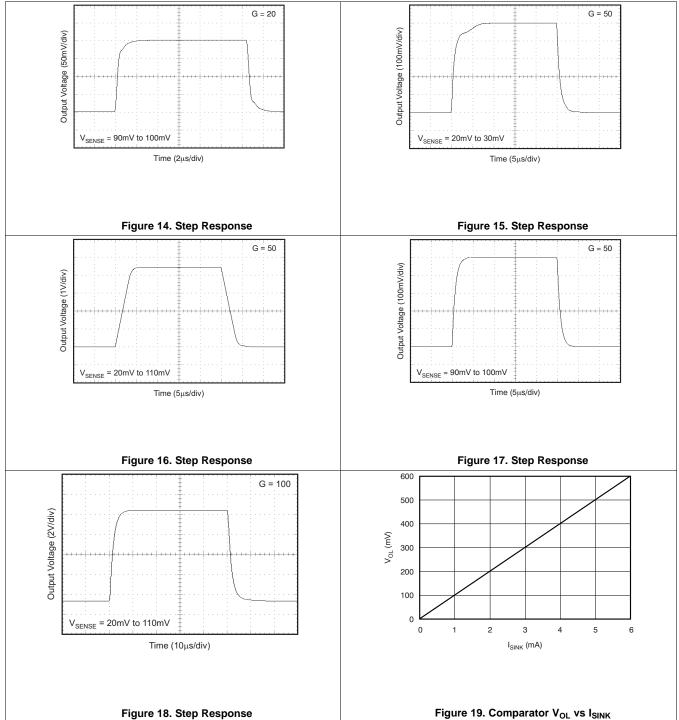

## **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_S = 12$  V,  $V_{IN+} = 12$  V, and  $V_{SENSE} = 100$  mV, (unless otherwise noted)

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_S = 12$  V,  $V_{IN+} = 12$  V, and  $V_{SENSE} = 100$  mV, (unless otherwise noted)

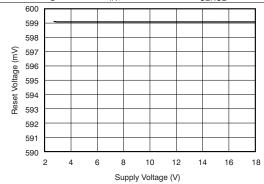

Figure 20. Comparator Trip Point vs Supply Voltage

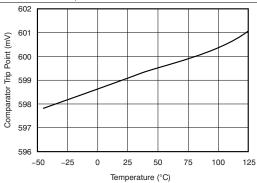

Figure 21. Comparator Trip Point vs Temperature

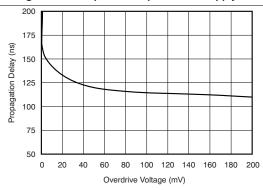

Figure 22. Comparator Propagation Delay vs Overdrive Voltage

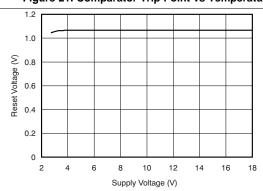

Figure 23. Comparator Reset Voltage vs Supply Voltage

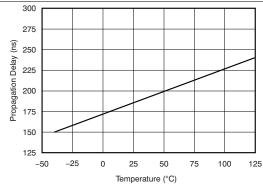

Figure 24. Comparator Propagation Delay vs Temperature

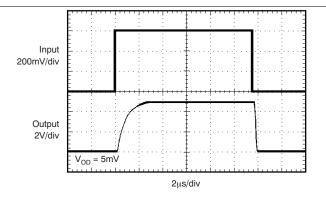

Figure 25. Comparator Propagation Delay

## 7 Detailed Description

#### 7.1 Overview

The INA200, INA201, and INA202 devices are high-side current-shunt monitors with voltage output. The INA20x devices can sense drops across shunts at common-mode voltages from -16 V to 80 V. The INA200–INA202 devices are available with three output voltage scales: 20 V/V, 50 V/V, and 100 V/V, with up to 500-kHz bandwidth. The INA200, INA201, and INA202 devices incorporate an open-drain comparator and internal reference providing a 0.6-V threshold. External dividers set the current trip point. The comparator includes a latching capability, that can be made transparent by grounding (or leaving open) the RESET pin. The INA200, INA201, and INA202 devices operate from a single 2.7 to 18-V supply, drawing a maximum of 1800  $\mu$ A of supply current. Package options include the very small MSOP-8 and the SO-8. All versions are specified over the extended operating temperature range of -40°C to +125°C.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

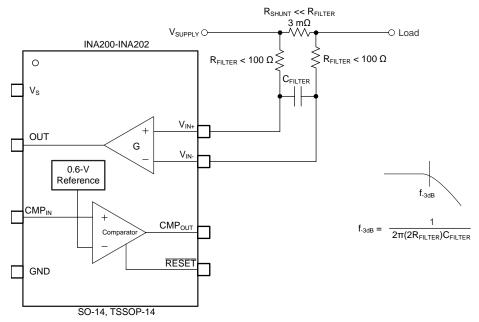

#### 7.3.1 Basic Connections

Figure 26 shows the basic connections of the INA20x devices. The input pins  $(V_{IN+} \text{ and } V_{IN-})$  must be connected as closely as possible with Kelvin connections to the shunt resistor to minimize any resistance in series with the shunt resistance.

Power-supply bypass capacitors are required for stability. Applications with noisy or high-impedance power supplies may require additional decoupling capacitors to reject power-supply noise. Connect bypass capacitors close to the device pins.

Copyright © 2006–2017, Texas Instruments Incorporated

Figure 26. INA200 Basic Connections

## 7.3.2 Selecting R<sub>S</sub>

The selected value for the shunt resistor,  $R_S$ , depends on the application and is a compromise between small-signal accuracy and maximum permissible voltage loss in the measurement line. High values of  $R_S$  provide better accuracy at lower currents by minimizing the effects of offset, while low values of  $R_S$  minimize voltage loss in the supply line. For most applications, using an  $R_S$  value that provides a full-scale shunt voltage range of 50 mV to 100 mV results in the best performance. Maximum input voltage for accurate measurements is 500 mV, but output voltage is limited by supply.

#### 7.3.3 Comparator

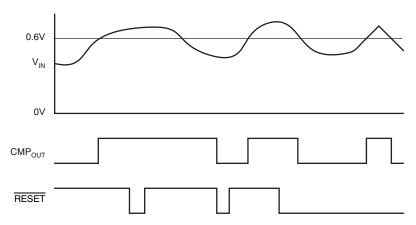

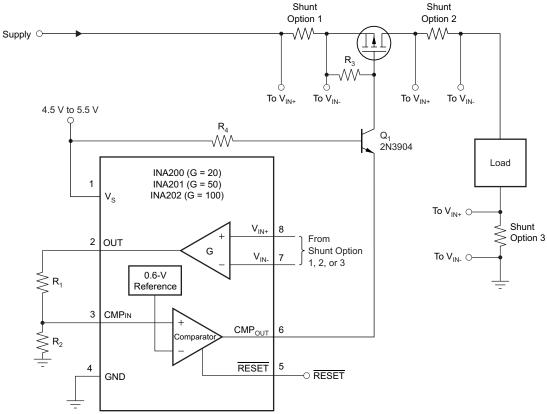

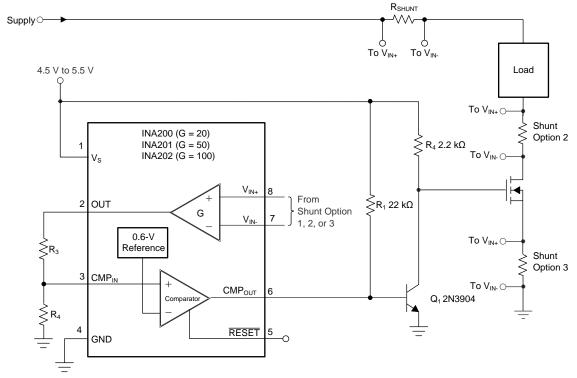

The INA200, INA201, and INA202 devices incorporate an open-drain comparator. This comparator typically has 2 mV of offset and a 1.3-μs (typical) response time. The output of the comparator latches and is reset through the RESET pin; see Figure 28.

When  $V_s$  and  $\overline{RESET}$  are different, TI recommends adding a low-pass filter (LPF) on the  $\overline{RESET}$  pin to avoid comparator behavior inconsistent with the data sheet. For instance, with a 12-V supply and a 3.3-V RESET, a rise time of 400 ns is appropriate. Similarly, with an 18-V supply and a 2.7-V RESET, a 1- $\mu$ s rise time is appropriate; see Figure 31.

Copyright © 2017, Texas Instruments Incorporated

Figure 27. Input Filter (Gain Error: 1.5% to 2.8%)

Figure 28. Comparator Latching Capability

Copyright © 2017, Texas Instruments Incorporated

(1) Q1 cascodes the comparator output to drive a high-side FET (the 2N3904) shown is good up to 60 V. The shunt can be located in any one of the three locations shown. The latching capability must be used in shutdown applications to prevent oscillation at the trip point.

Figure 29. High-Side Switch Overcurrent Shutdown

Copyright © 2017, Texas Instruments Incorporated

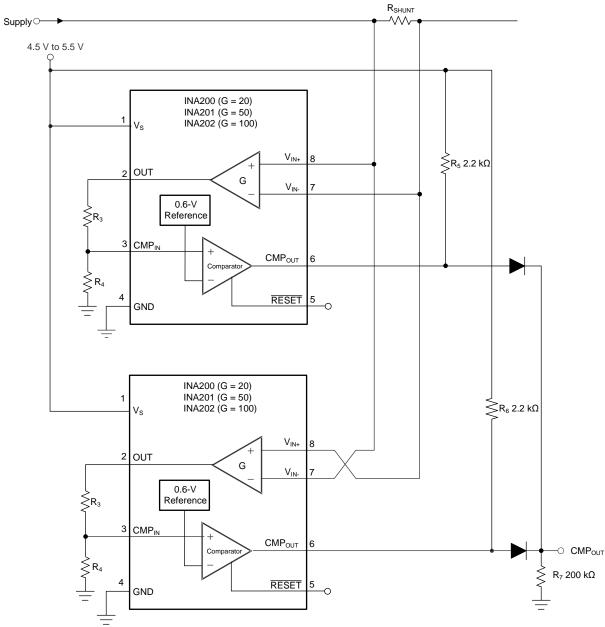

(1) It is possible to set different limits for each direction.

Figure 30. Bidirectional Overcurrent Comparator

Figure 31. Filter on RESET Pin

#### 7.4 Device Functional Modes

### 7.4.1 Input Filtering

An obvious and straightforward location for filtering is at the output of the INA20x series; however, this location negates the advantage of the low output impedance of the internal buffer. The only other option for filtering is at the input pins of the INA20x devices, which is complicated by the internal 5 k $\Omega$  + 30% input impedance. This is shown in Figure 27. Using the lowest possible resistor values minimizes the initial shift in gain and effects of tolerance. The effect on initial gain is shown in Equation 1:

Gain Error % =

$$100 - \left[100 \times \frac{5k\Omega}{5k\Omega + R_{FILT}}\right]$$

(1)

Total effect on gain error can be calculated by replacing the 5-k $\Omega$  term with 5 k $\Omega$  – 30%, (or 3.5 k $\Omega$ ) or 5 k $\Omega$  + 30% (or 6.5 k $\Omega$ ). The tolerance extremes of R<sub>FILT</sub> can be inserted into the equation. If a pair of 100- $\Omega$  1% resistors are used on the inputs, the initial gain error equals 1.96%. Worst-case tolerance conditions always occur at the lower excursion of the internal 5-k $\Omega$  resistor (3.5 k $\Omega$ ), and the higher excursion of R<sub>FILT</sub> – 3% in this case.

The specified accuracy of the INA20x devices must then be combined in addition to these tolerances. While this discussion treated accuracy worst-case conditions by combining the extremes of the resistor values, it is appropriate to use geometric mean or root sum square calculations to total the effects of accuracy variations.

## 7.4.2 Accuracy Variations as a Result of V<sub>SENSE</sub> and Common-Mode Voltage

The accuracy of the INA200, INA201, and INA202 current shunt monitors is a function of two main variables:  $V_{SENSE}$  ( $V_{IN+} - V_{IN-}$ ), common-mode voltage, ( $V_{CM}$ ), relative to the supply voltage ( $V_{S}$ ).  $V_{CM}$  is expressed as ( $V_{IN+} + V_{IN-}$ ) / 2; however, in practice,  $V_{CM}$  is seen as the voltage at  $V_{IN+}$  because the voltage drop across  $V_{SENSE}$  is typically small.

This section addresses the accuracy of these specific operating regions:

- Normal Case 1: V<sub>SENSE</sub> ≥ 20 mV, V<sub>CM</sub> ≥ V<sub>S</sub>

- Normal Case 2: V<sub>SENSE</sub> ≥ 20 mV, V<sub>CM</sub> < V<sub>S</sub>

- Low V<sub>SENSE</sub> Case 1: V<sub>SENSE</sub> < 20 mV, −16 V ≤ V<sub>CM</sub> < 0</li>

- Low V<sub>SENSE</sub> Case 2: V<sub>SENSE</sub> < 20 mV, 0 V ≤ V<sub>CM</sub> ≤ V<sub>S</sub>

- Low V<sub>SENSE</sub> Case 3: V<sub>SENSE</sub> < 20 mV, V<sub>S</sub> < V<sub>CM</sub> ≤ 80 V

## 7.4.2.1 Normal Case 1: $V_{SENSE} \ge 20 \text{ mv}, V_{CM} \ge V_{S}$

This region of operation provides the highest accuracy. Here, the input offset voltage is characterized and measured using a two-step method. First, the gain is determined by Equation 2.

$$G = \frac{V_{OUT1} - V_{OUT2}}{100mV - 20mV}$$

where

V<sub>OUT1</sub> = output voltage with V<sub>SENSE</sub> = 100 mV

•

$$V_{OUT2}$$

= output voltage with  $V_{SENSE}$  = 20 mV (2)

Then the offset voltage is measured at  $V_{SENSE} = 100$  mV, and referred to the input (RTI) of the current shunt monitor, as shown in *Electrical Characteristics: Current-Shunt Monitor*.

$$V_{OS}RTI \text{ (Referred-To-Input)} = \left(\frac{V_{OUT1}}{G}\right) - 100\text{mV}$$

(3)

In the *Typical Characteristics*, *Figure 7* shows the highest accuracy for the this region of operation. In this plot,  $V_S = 12 \text{ V}$ . For  $V_{CM} \ge 12 \text{ V}$ , the output error is at the minimum value. This case creates the  $V_{SENSE} \ge 20\text{-mV}$  output specifications in *Electrical Characteristics: Current-Shunt Monitor*.

## **Device Functional Modes (continued)**

## 7.4.2.2 Normal Case 2: $V_{SENSE} \ge 20 \text{ mv}$ , $V_{CM} < V_{S}$

This region of operation is less accurate than normal case 1 as a result of the common-mode operating area in which the part functions, as shown in the Figure 7 curve (Figure 7). As noted, for this graph  $V_S = 12 \text{ V}$ ; for  $V_{CM} <$ 12 V, the output error increases as V<sub>CM</sub> decreases to less than 12 V, with a typical maximum error of 0.005% at the most negative  $V_{CM} = -16 \text{ V}$ .

7.4.2.3 Low

$$V_{SENSE}$$

Case 1:  $V_{SENSE}$  < 20 mV, -16 V  $\leq$   $V_{CM}$  < 0 and Low  $V_{SENSE}$  Case 3:  $V_{SENSE}$  < 20 mV,  $V_{S}$  <  $V_{CM}$   $\leq$  80 V

Although the INA200 family of devices are not designed for accurate operation in these regions, some applications are exposed to these conditions. For example, when monitoring power supplies that are switched on and off while V<sub>S</sub> is still applied to the INA20x devices, it is important to know what the behavior of the devices is

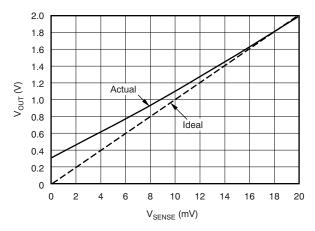

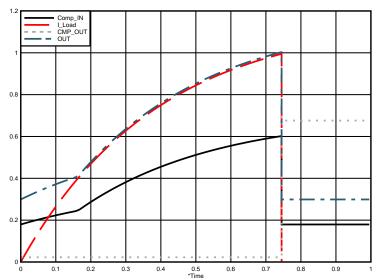

As V<sub>SENSE</sub> approaches 0 mV, in these V<sub>CM</sub> regions, the accuracy of the device output degrades. A larger-thannormal offset can appear at the current shunt monitor output with a typical maximum value of  $V_{OUT} = 300$  mV for V<sub>SENSE</sub> = 0 mV. As V<sub>SENSE</sub> approaches 20 mV, V<sub>OUT</sub> returns to the expected output value with accuracy as shown in *Electrical Characteristics: Current-Shunt Monitor*. Figure 32 shows this effect using the INA202 (gain = 100).

Figure 32. Example For Low  $V_{SENSE}$  Cases 1 and 3 (INA202, Gain = 100)

## 7.4.2.4 Low $V_{SENSE}$ Case 2: $V_{SENSE}$ < 20 mV, 0 V $\leq$ $V_{CM}$ $\leq$ $V_{S}$

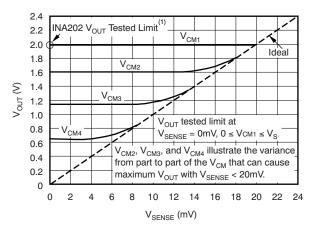

This region of operation is the least accurate for the INA20x family. To achieve the wide input common-mode voltage range, these devices use two op amp front ends in parallel. One op amp front end operates in the positive input common-mode voltage range, and the other in the negative input region. For this case, neither of these two internal amplifiers dominates and overall loop gain is low. Within this region, V<sub>OUT</sub> approaches voltages close to linear operation levels for normal case 2. This deviation from linear operation becomes greatest the closer V<sub>SENSE</sub> approaches 0 V. Within this region, as V<sub>SENSE</sub> approaches 20 mV, device operation is closer to that is described in normal case 2. Figure 33 shows this behavior for the INA202. The V<sub>OUT</sub> maximum peak for this case is tested by maintaining a constant  $V_S$ , setting  $V_{SENSE}$  equal to 0 mV and sweeping  $V_{CM}$  from 0 V to  $V_S$ . The exact  $V_{CM}$  at which  $V_{OUT}$  peaks during this test varies from device to device, but the  $V_{OUT}$  maximum peak is tested to be less than the specified V<sub>OUT</sub> tested limit.

## **Device Functional Modes (continued)**

NOTE: (1) INA200 V<sub>OUT</sub> Tested Limit = 0.4V. INA201 V<sub>OUT</sub> Tested Limit = 1V.

Figure 33. Example For Low  $V_{SENSE}$  Case 2 (INA202, Gain = 100)

#### 7.4.3 Transient Protection

The –16 to 80 V common-mode range of the INA20x devices is ideal for withstanding automotive fault conditions ranging from 12-V battery reversal up to 80-V transients, since no additional protective components are required up to those levels. In the event that the INA20x devices are exposed to transients on the inputs in excess of their ratings, then external transient absorption with semiconductor transient absorbers (such as Zeners) are required. TI does not recommend using MOVs or VDRs, except when they are used in addition to a semiconductor transient absorber. Select the transient absorber so the absorber does not allow the INA20x devices to be exposed to transients greater than 80 V (that is, allow for transient absorber tolerance and additional voltage due to transient absorber dynamic impedance). Despite the use of internal Zener-type ESD protection, the INA20x devices do not lend themselves to using external resistors in series with the inputs since the internal gain resistors can vary up to ±30%. (If gain accuracy is not important, then resistors can be added in series with the INA200, INA201, and INA202 inputs with two equal resistors on each input.)

## 7.4.4 Output Voltage Range

The output of the INA20x devices is accurate within the output voltage swing range set by the power supply pin  $(V_S)$ . This performance is best illustrated when using the INA202 (a gain of 100 version), where a 100-mV full-scale input from the shunt resistor requires an output voltage swing of 10 V, and a power-supply voltage sufficient to achieve 10 V on the output.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The INA20x series is designed to enable simple configuration for detecting overcurrent conditions and current monitoring in an application. This device is individually targeted towards overcurrent detection of a single threshold. However, this device can pair with additional devices and circuitry to create more complex monitoring functional blocks.

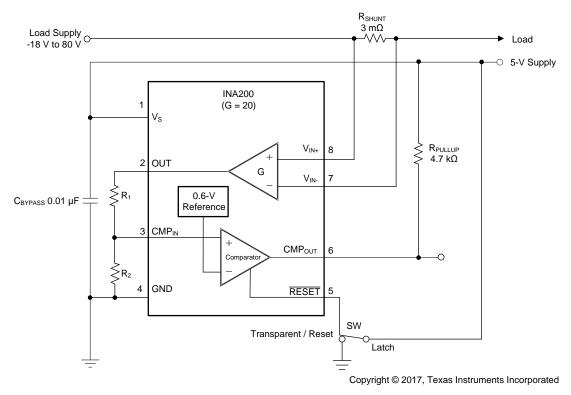

## 8.2 Typical Application

Copyright © 2017, Texas Instruments Incorporated

(1) In this case, Q inverts the comparator output.

Figure 34. Low-Side Switch Overcurrent Shutdown

## 8.2.1 Design Requirements

The device measures current through a resistive shunt with current flowing in one direction that enables detection of an overcurrent event only when the differential input voltage exceeds the threshold limit. When the current reaches the set limit of the divider  $R_1$  /  $R_2$ , the output of CMP<sub>OUT</sub> transitions high, which turns Q1 on, pulls the gate of the pass-FET low, and turns off the flow off current.

## **Typical Application (continued)**

#### 8.2.2 Detailed Design Procedure

Figure 34 shows the basic connections of the device. The input terminals (IN+ and IN –) must be connected as closely as possible to the current-sensing resistor to minimize any resistance in series with the shunt resistance. Additional resistance between the current-sensing resistor and input terminals results in errors in the measurement. When input current flows through this external input resistance, the voltage developed across the shunt resistor differs from the voltage reaching the input terminals.

Use the gain of the INA20x and shunt value to calculate the OUT voltage for the desired trip current. Configure R1 and R2 so that the current trip point is equal to the 0.6-V reference voltage.

## 8.2.3 Application Curve

Figure 35. Low-Side Switch Overcurrent Shutdown Response

## 9 Power Supply Recommendations

The input circuitry of the INA20x devices can accurately measure beyond the power-supply voltage,  $V_s$ . For example, the  $V_s$  power supply is 5 V, whereas the load power-supply voltage is up to 80 V. However, the output voltage range of the OUT pin is limited by the voltages on the power supply pin.

## 9.1 Output vs Supply Ramp Considerations

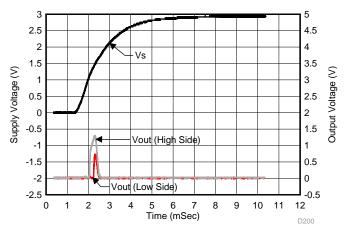

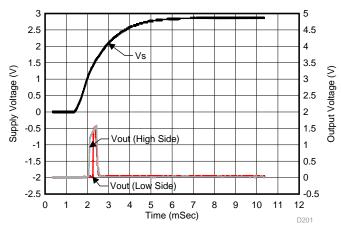

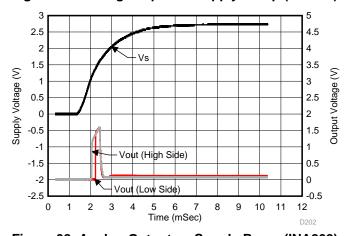

Figure 36, Figure 37, and Figure 38 show the typical output voltages for high and low-side configurations with the given ramp supply voltage. These fluctuations on the output during power-up may require a controller to incorporate a blanking time to disregard the artifacts.

## **Output vs Supply Ramp Considerations (continued)**

Figure 36. Analog Output vs Supply Ramp (INA200)

Figure 37. Analog Output vs Supply Ramp (INA201)

Figure 38. Analog Output vs Supply Ramp (INA202)

24

## 10 Layout

## 10.1 Layout Guidelines

- Connect the input pins to the sensing resistor using a Kelvin or 4-wire connection. This connection technique

ensures that only the current-sensing resistor impedance is detected between the input pins. Poor routing of

the current-sensing resistor commonly results in additional resistance present between the input pins. Given

the very-low-ohmic value of the current resistor, any additional high-current carrying impedance causes

significant measurement errors.

- The power-supply bypass capacitor must be placed as close as possible to the supply and ground pins. The

recommended value of this bypass capacitor is 0.1 μF. Additional decoupling capacitance can be added to

compensate for noisy or high-impedance power supplies.

## 10.2 Layout Example

Figure 39. INA20x Layout Example

## 11 Device and Documentation Support

#### 11.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 1. Related Links

| PARTS  | PRODUCT FOLDER | ORDER NOW  | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|--------|----------------|------------|---------------------|---------------------|---------------------|

| INA200 | Click here     | Click here | Click here          | Click here          | Click here          |

| INA201 | Click here     | Click here | Click here          | Click here          | Click here          |

| INA202 | Click here     | Click here | Click here          | Click here          | Click here          |

## 11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com

2-Dec-2025

## **PACKAGING INFORMATION**

| Orderable part number | Status           | Material type | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material  | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------------|---------------|-----------------|-----------------------|-------------|--------------------------------|----------------------------|--------------|------------------|

| INA200AID             | Last<br>Time Buy | Production    | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>200A      |

| INA200AIDGKR          | Active           | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG              | Level-2-260C-1 YEAR        | -40 to 125   | BQH              |

| INA200AIDGKR.A        | Active           | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | BQH              |

| INA200AIDGKT          | Last<br>Time Buy | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | NIPDAU   NIPDAUAG              | Level-2-260C-1 YEAR        | -40 to 125   | BQH              |

| INA200AIDR            | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>200A      |

| INA200AIDR.A          | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>200A      |

| INA200AIDRG4          | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>200A      |

| INA200AIDRG4.A        | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>200A      |

| INA201AID             | Last<br>Time Buy | Production    | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>201A      |

| INA201AIDGKR          | Active           | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | Call TI   Nipdauag<br>  Nipdau | Level-2-260C-1 YEAR        | -40 to 125   | BQJ              |

| INA201AIDGKR.A        | Active           | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | BQJ              |

| INA201AIDGKRG4        | Active           | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | -           | Call TI                        | Call TI                    | -40 to 125   | BQJ              |

| INA201AIDGKT          | Last<br>Time Buy | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes         | Call TI   Nipdauag<br>  Nipdau | Level-2-260C-1 YEAR        | -40 to 125   | BQJ              |

| INA201AIDR            | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>201A      |

| INA201AIDR.A          | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>201A      |

| INA201AIDRG4          | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>201A      |

| INA201AIDRG4.A        | Active           | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>201A      |

| INA202AID             | Last<br>Time Buy | Production    | SOIC (D)   8    | 75   TUBE             | Yes         | NIPDAU                         | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>202A      |

| INA202AIDGKR          | Active           | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG              | Level-2-260C-1 YEAR        | -40 to 125   | BQL              |

2-Dec-2025

www.ti.com

| Orderable part number | Status (1)       | Material type (2) | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------------|-------------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

|                       |                  |                   |                 |                       |                 | (4)                           | (5)                        |              |                  |

| INA202AIDGKR.A        | Active           | Production        | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | BQL              |

| INA202AIDGKT          | Last<br>Time Buy | Production        | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes             | NIPDAU   NIPDAUAG             | Level-2-260C-1 YEAR        | -40 to 125   | BQL              |

| INA202AIDR            | Active           | Production        | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>202A      |

| INA202AIDR.A          | Active           | Production        | SOIC (D)   8    | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | INA<br>202A      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF INA200, INA201, INA202:

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

## PACKAGE OPTION ADDENDUM

www.ti.com 2-Dec-2025

• Automotive : INA200-Q1, INA201-Q1, INA202-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 24-Jul-2025

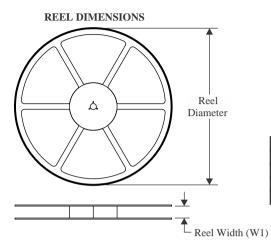

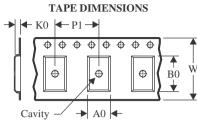

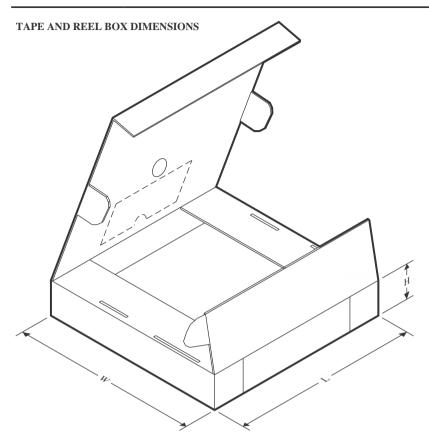

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

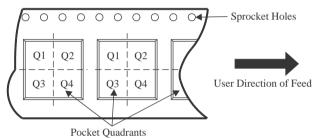

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| INA200AIDGKR | VSSOP           | DGK                | 8    | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA200AIDGKT | VSSOP           | DGK                | 8    | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA200AIDR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| INA200AIDRG4 | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| INA201AIDGKR | VSSOP           | DGK                | 8    | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA201AIDGKT | VSSOP           | DGK                | 8    | 250  | 180.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA201AIDGKT | VSSOP           | DGK                | 8    | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA201AIDGKT | VSSOP           | DGK                | 8    | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA201AIDR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| INA201AIDRG4 | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| INA202AIDGKR | VSSOP           | DGK                | 8    | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA202AIDGKT | VSSOP           | DGK                | 8    | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA202AIDGKT | VSSOP           | DGK                | 8    | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| INA202AIDR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 24-Jul-2025

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| INA200AIDGKR | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA200AIDGKT | VSSOP        | DGK             | 8    | 250  | 353.0       | 353.0      | 32.0        |

| INA200AIDR   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA200AIDRG4 | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA201AIDGKR | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA201AIDGKT | VSSOP        | DGK             | 8    | 250  | 213.0       | 191.0      | 35.0        |

| INA201AIDGKT | VSSOP        | DGK             | 8    | 250  | 353.0       | 353.0      | 32.0        |

| INA201AIDGKT | VSSOP        | DGK             | 8    | 250  | 366.0       | 364.0      | 50.0        |

| INA201AIDR   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA201AIDRG4 | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA202AIDGKR | VSSOP        | DGK             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA202AIDGKT | VSSOP        | DGK             | 8    | 250  | 353.0       | 353.0      | 32.0        |

| INA202AIDGKT | VSSOP        | DGK             | 8    | 250  | 366.0       | 364.0      | 50.0        |

| INA202AIDR   | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

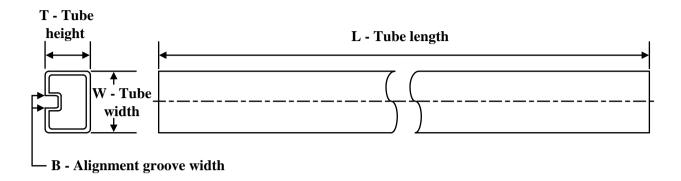

## **TUBE**

\*All dimensions are nominal

| Device    | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------|--------------|--------------|------|-----|--------|--------|--------|--------|

| INA200AID | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| INA201AID | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| INA202AID | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

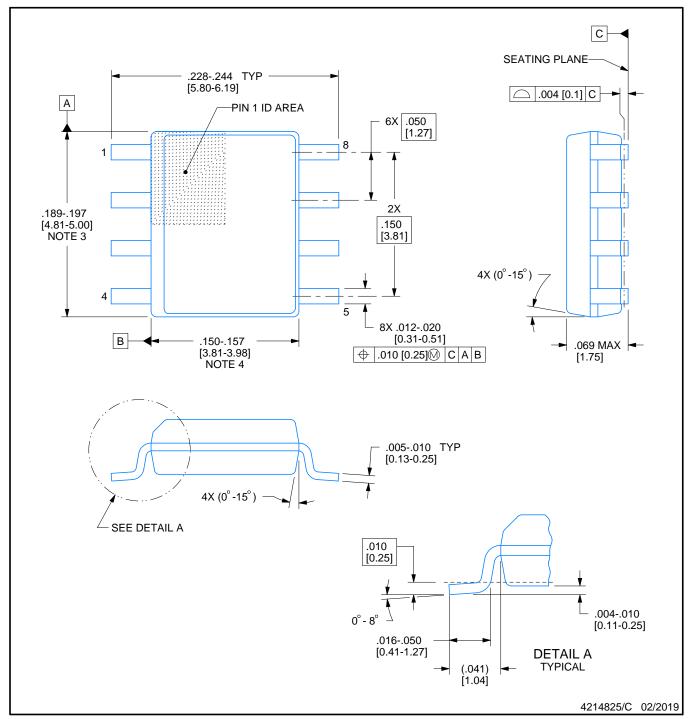

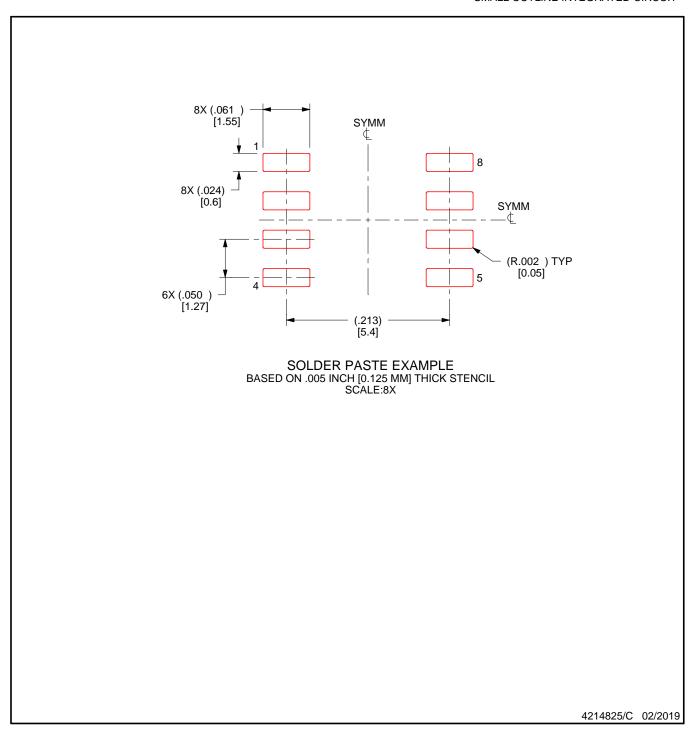

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

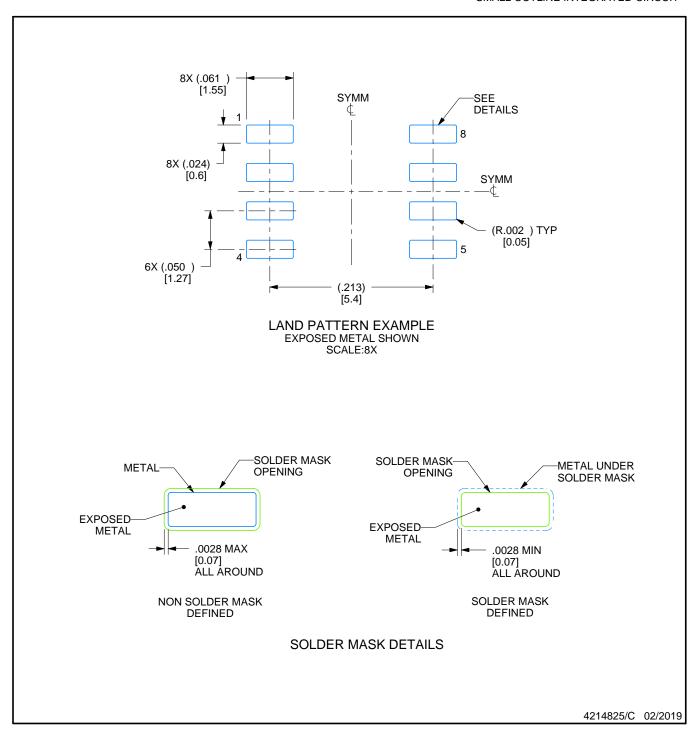

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

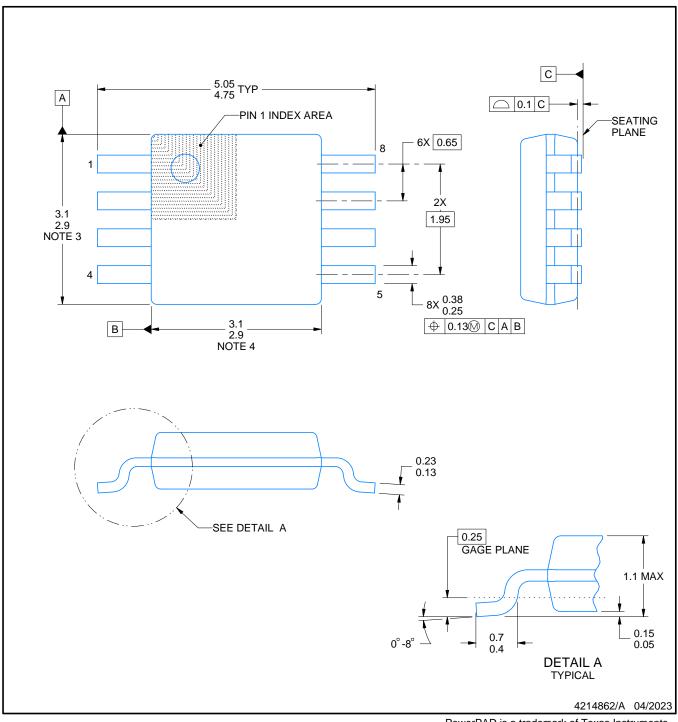

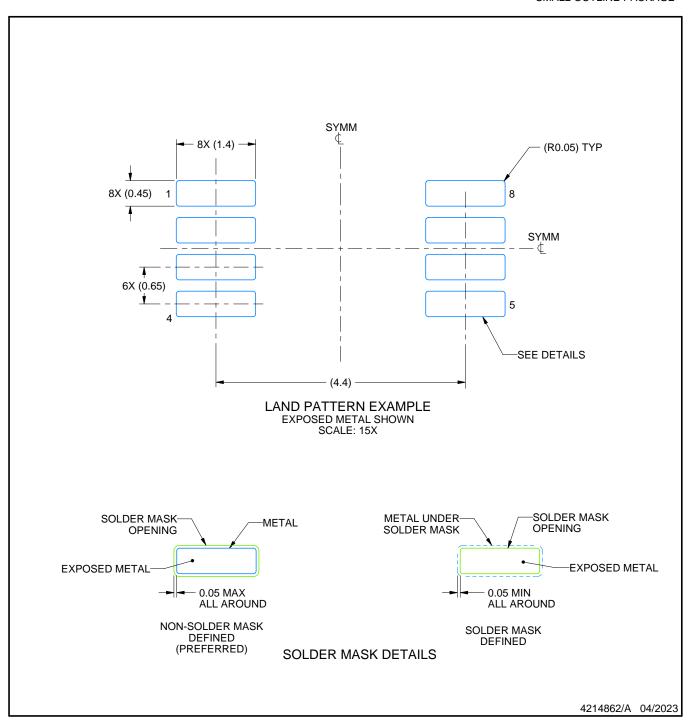

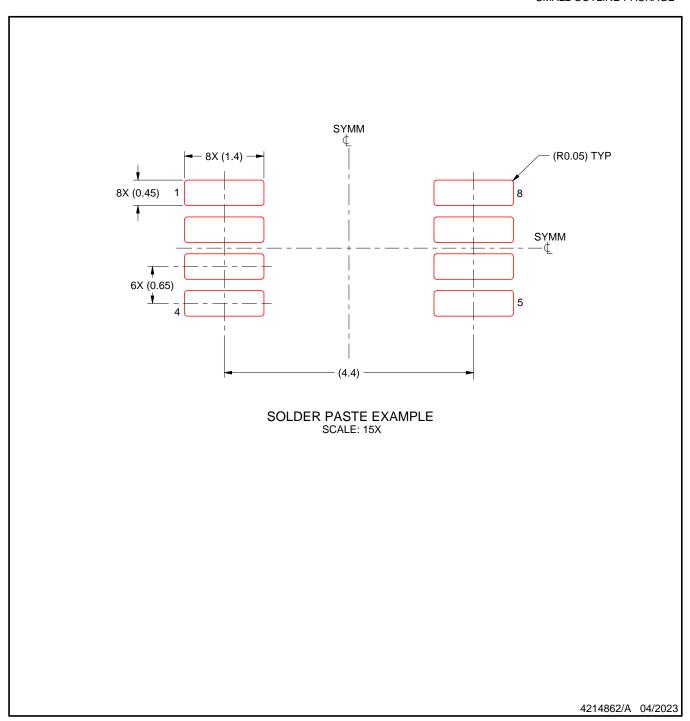

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025