LM10-MIL SNOSD68 – JUNE 2017

# LM10-MIL Operational Amplifier and Voltage Reference

## 1 Features

- Input Offset Voltage: 2 mV (Maximum)

- Input Offset Current: 0.7 nA (Maximum)

- Input Bias Current: 20 nA (Maximum)

- Reference Regulation: 0.1% (Maximum)

- Offset Voltage Drift: 2 μV/°C

- Reference Drift: 0.002%/°C

## 2 Applications

- Remote Amplifiers

- Battery-Level Indicators

- Thermocouple Transmitters

- Voltage and Current regulators

## **3** Description

The LM10-MIL is a monolithic linear IC consisting of a precision reference, an adjustable reference buffer, and an independent, high-quality operational amplifier.

The unit can operate from a total supply voltage as low as 1.1 V or as high as 40 V, drawing only 270  $\mu$ A. A complementary output stage swings within 15 mV of the supply terminals or will deliver ±20-mA output current with ±0.4-V saturation. Reference output can be as low as 200 mV.

The circuit is recommended for portable equipment and is completely specified for operation from a single power cell. In contrast, high output-drive capability, both voltage and current, along with thermal overload protection, suggest it in demanding general-purpose applications.

The device is capable of operating in a floating mode, independent of fixed supplies. It can function as a remote comparator, signal conditioner, SCR controller or transmitter for analog signals, delivering the processed signal on the same line used to supply power. It is also suited for operation in a wide range of voltage and current regulator applications, from low voltages to several hundred volts, providing greater precision than existing ICs.

This series is available in the three standard temperature ranges, with the commercial part having relaxed limits. In addition, a low-voltage specification (suffix L) is available in the limited temperature ranges at a cost savings.

| Device Information <sup>(</sup> | 1) |

|---------------------------------|----|

|---------------------------------|----|

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

|             | SOIC (14) | 8.992 mm × 7.498 mm |

| LM10-MIL    | SDIP (8)  | 8.255 mm × 8.255 mm |

|             | PDIP (8)  | 9.81 mm × 6.35 mm   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

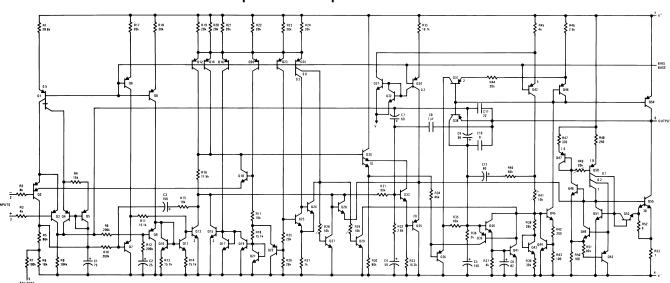

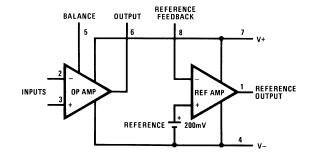

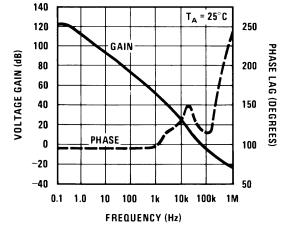

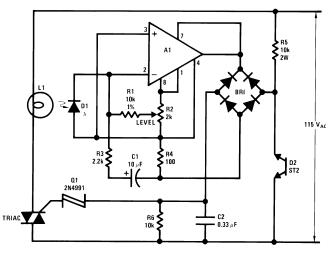

**Operational Amplifier Schematic**

(Pin numbers are for 8-pin packages)

Texas Instruments

www.ti.com

## **Table of Contents**

| 1 | Feat | tures                            | 1  |

|---|------|----------------------------------|----|

| 2 | Арр  | lications                        | 1  |

| 3 | Des  | cription                         | 1  |

| 4 | Rev  | ision History                    | 2  |

| 5 | Pin  | Configuration and Functions      | 3  |

| 6 | Spe  | cifications                      | 4  |

|   | 6.1  | Absolute Maximum Ratings         | 4  |

|   | 6.2  | Recommended Operating Conditions | 4  |

|   | 6.3  | Thermal Information              | 4  |

|   | 6.4  | Electrical Characteristics       | 5  |

|   | 6.5  | Typical Characteristics          | 7  |

| 7 | Deta | ailed Description                | 13 |

|   | 7.1  | Overview                         | 13 |

|   | 7.2  | Functional Block Diagram         | 13 |

|   | 7.3  | Feature Description              | 13 |

|   | 7.4  | Device Functional Modes          | 13 |

|   |      |                                  |    |

| 8  | Арр  | lication and Implementation              | 14 |

|----|------|------------------------------------------|----|

|    | 8.1  | Application Information                  | 14 |

|    | 8.2  | Typical Application                      | 14 |

|    | 8.3  | System Examples                          | 15 |

| 9  | Pow  | er Supply Recommendations                | 23 |

| 10 | Lay  | out                                      | 23 |

|    | 10.1 | Layout Guidelines                        | 23 |

|    | 10.2 | Layout Example                           | 23 |

| 11 | Dev  | ice and Documentation Support            | 24 |

|    | 11.1 | Device Support                           | 24 |

|    | 11.2 | Documentation Support                    | 24 |

|    | 11.3 | Community Resources                      | 24 |

|    | 11.4 | Trademarks                               | 25 |

|    | 11.5 | Electrostatic Discharge Caution          | 25 |

|    | 11.6 | Glossary                                 | 25 |

| 12 |      | hanical, Packaging, and Orderable mation | 25 |

## 4 Revision History

| DATE      | REVISION | NOTES           |

|-----------|----------|-----------------|

| June 2017 | *        | Initial Release |

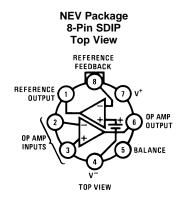

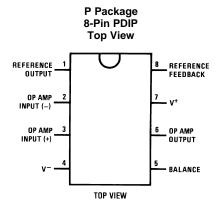

## 5 Pin Configuration and Functions

#### Pin Functions — 8-Pin SDIP or PDIP

| PIN                | l   | 1/0 | DESCRIPTION                                 |  |

|--------------------|-----|-----|---------------------------------------------|--|

| NAME               | NO. | I/O | DESCRIPTION                                 |  |

| Balance            | 5   | I   | Used for offset nulling                     |  |

| Op Amp Input (+)   | 3   | I   | Noninverting input of operational amplifier |  |

| Op Amp Input (-)   | 2   | I   | Inverting input of operational amplifier    |  |

| Op Amp Output      | 6   | 0   | Output terminal of operational amplifier    |  |

| Reference Feedback | 8   | I   | Feedback terminal of reference              |  |

| Reference Output   | 1   | 0   | Output terminal of reference                |  |

| V+                 | 7   | I   | Positive supply voltage                     |  |

| V–                 | 4   | I   | Negative supply voltage                     |  |

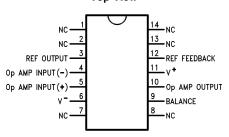

#### NPA Package 14-Pin SOIC Top View

#### Pin Functions — 14-Pin SOIC

| PIN                | I                  | 1/0 | DESCRIPTION                                 |  |

|--------------------|--------------------|-----|---------------------------------------------|--|

| NAME               | NO.                | I/O | DESCRIPTION                                 |  |

| Balance            | 9                  | I   | Used for offset nulling                     |  |

| NC                 | 1, 2, 7, 8, 14, 13 | —   | No connection                               |  |

| Op Amp Input (–)   | 4                  | I   | Inverting input of operational amplifier    |  |

| Op Amp Input (+)   | 5                  | I   | Noninverting input of operational amplifier |  |

| Op Amp Output      | 10                 | 0   | Output terminal of operational amplifier    |  |

| Reference Feedback | 12                 | I   | Feedback terminal of reference              |  |

| Reference Output   | 3                  | 0   | Output terminal of reference                |  |

| V+                 | 11                 | I   | Positive supply voltage                     |  |

| V-                 | 6                  | I   | Negative supply voltage                     |  |

Copyright © 2017, Texas Instruments Incorporated

## 6 Specifications

### 6.1 Absolute Maximum Ratings

See (1)(2)(3)

|                                  |                      |                          | MIN MAX            | UNIT |

|----------------------------------|----------------------|--------------------------|--------------------|------|

| Total supply voltage             |                      |                          | 45                 | V    |

| Differential input voltage       | e <sup>(4)</sup>     |                          | ±40                | V    |

| Power dissipation <sup>(5)</sup> |                      |                          | Internally limited |      |

| Output short-circuit dura        | ation <sup>(6)</sup> |                          | Continuous         |      |

|                                  | то                   | Soldering (10 seconds)   | 300                | °C   |

|                                  |                      | Soldering (10 seconds)   | 260                | °C   |

| Lead temperature                 | DIP                  | Vapor phase (60 seconds) | 215                | °C   |

|                                  |                      | Infrared (15 seconds)    | 220                | °C   |

| Maximum junction temp            | erature              |                          | 150                | °C   |

| Storage temperature, T           | stg                  |                          | -55 150            | °C   |

(1) Refer to RETS10X for LM10H military specifications.

(2) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(4) The Input voltage can exceed the supply voltages provided that the voltage from the input to any other terminal does not exceed the maximum differential input voltage and excess dissipation is accounted for when V<sub>IN</sub> < V<sup>-</sup>.

(5) The maximum, operating-junction temperature is 150°C for the LM10-MIL. At elevated temperatures, devices must be derated based on package thermal resistance.

(6) Internal thermal limiting prevents excessive heating that could result in sudden failure, but the IC can be subjected to accelerated stress with a shorted output and worst-case conditions.

## 6.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                        | MIN  | NOM MAX     | UNIT |

|------------------|----------------------------------------|------|-------------|------|

| Vs               | Supply input voltage range (V–) – (V+) | 1.2  | 40          | V    |

| V <sub>CM</sub>  | Common-mode voltage                    | (V–) | (V+) – 0.85 | V    |

| V <sub>REF</sub> | Reference voltage                      |      | 0.2         | V    |

| I <sub>REF</sub> | Reference current                      | 0    | 1           | mA   |

#### 6.3 Thermal Information

|                      |                                           | LM10-MIL   |            |          |      |

|----------------------|-------------------------------------------|------------|------------|----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>             | NEV (SDIP) | NPA (SOIC) | P (PDIP) | UNIT |

|                      |                                           | 8 PINS     | 14 PINS    | 8 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance    | 150        | 90         | 87       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance | 45         | —          | —        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.4 Electrical Characteristics

| PARAMETER                           | TEST CONDITIONS                                                                                                                                                | MIN | TYP   | MAX   | UNIT  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|

| Input offset voltage                | T <sub>J</sub> =25°C                                                                                                                                           |     | 0.3   | 2     | mV    |

| input onset voltage                 | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                                            |     |       | 3     | mV    |

| Input offset current <sup>(2)</sup> | T <sub>J</sub> =25°C                                                                                                                                           |     | 0.25  | 0.7   | nA    |

| input onset current.                | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                                            |     |       | 1.5   | nA    |

| Input bias current                  | T <sub>J</sub> =25°C                                                                                                                                           |     | 10    | 20    | nA    |

| input bias current                  | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                                            |     |       | 30    | nA    |

| Input resistance                    | T <sub>J</sub> =25°C                                                                                                                                           | 250 | 500   |       | kΩ    |

| Input resistance                    | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                                            | 150 |       |       | kΩ    |

|                                     | $V_{S} = \pm 20 \text{ V}, \text{ I}_{OUT} = 0$                                                                                                                | 120 | 400   |       | V/mV  |

|                                     | $V_{OUT}$ = ±19.95 V, $T_{MIN} \leq T_J \leq T_{MAX}$ (see $^{(1)})$                                                                                           | 80  |       |       | V/mV  |

|                                     | $V_{S} = \pm 20 \text{ V}, V_{OUT} = \pm 19.4 \text{ V}$                                                                                                       | 50  | 130   |       | V/mV  |

|                                     | $I_{OUT} = \pm 20$ mA, $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                     | 20  |       |       | V/mV  |

| Large signal voltage gain           | $I_{OUT} = \pm 15 \text{ mA}, T_{MIN} \leq T_J \leq T_{MAX} \text{ (see }^{(1)}\text{)}$                                                                       | 20  |       |       | V/mV  |

| 95                                  | $V_S = \pm 0.6 \text{ V}, I_{OUT} = \pm 2 \text{ mA}$                                                                                                          | 1.5 | 3     |       | V/mV  |

|                                     | $V_{S} = \pm 0.65 \text{ V}, \text{ I}_{OUT} = \pm 2 \text{ mA}, \text{ T}_{MIN} \leq \text{T}_{J} \leq \text{T}_{MAX} \text{ (see }^{(1)})$                   | 1.5 | 3     |       | V/mV  |

|                                     | $V_{OUT} = \pm 0.4 \text{ V}, T_{MIN} \le T_J \le T_{MAX} \text{ (see }^{(1)}\text{)}$                                                                         | 0.5 |       |       | V/mV  |

|                                     | $V_{OUT} = \pm 0.3 \text{ V}, V_{CM} = -0.4 \text{ V}, T_{MIN} \leq T_J \leq T_{MAX} \text{ (see }^{(1)})$                                                     | 0.5 |       |       | V/mV  |

|                                     | $1.2 \text{ V} \le \text{V}_{\text{OUT}} \le 40 \text{ V}, \text{ R}_{\text{L}} = 1.1 \text{ k}\Omega$                                                         | 14  | 33    |       | V/mV  |

|                                     | 1.3 V $\leq$ V <sub>OUT</sub> $\leq$ 40 V, R <sub>L</sub> = 1.1 kΩ, T <sub>MIN</sub> $\leq$ T <sub>J</sub> $\leq$ T <sub>MAX</sub> (see <sup>(1)</sup> )       | 14  | 33    |       | V/mV  |

| Shunt gain <sup>(3)</sup>           | 0.1 mA $\leq$ I <sub>OUT</sub> $\leq$ 5 mA, T <sub>MIN</sub> $\leq$ T <sub>J</sub> $\leq$ T <sub>MAX</sub> (see <sup>(1)</sup> )                               | 6   |       |       | V/mV  |

|                                     | 1.5 V $\leq$ V <sup>+</sup> $\leq$ 40 V, R <sub>L</sub> = 250 $\Omega$                                                                                         | 8   | 25    |       | V/mV  |

|                                     | 0.1 mA $\leq$ I <sub>OUT</sub> $\leq$ 20 mA, T <sub>MIN</sub> $\leq$ T <sub>J</sub> $\leq$ T <sub>MAX</sub> (see <sup>(1)</sup> )                              | 4   |       |       | V/mV  |

|                                     | $-20 \text{ V} \le \text{V}_{\text{CM}} \le 19.15 \text{ V}$                                                                                                   | 93  | 102   |       | dB    |

| Common-mode rejection               | $-20 \text{ V} \le \text{V}_{CM} \le 19 \text{ V}, \text{ T}_{MIN} \le \text{T}_{\text{J}} \le \text{T}_{MAX} \text{ (see }^{(1)}\text{)}$                     | 93  | 102   |       | dB    |

|                                     | $V_{S} = \pm 20 \text{ V}, \text{ T}_{MIN} \leq \text{T}_{J} \leq \text{T}_{MAX} \text{ (see }^{(1)}\text{)}$                                                  | 87  |       |       | dB    |

|                                     | -0.2 V ≥ V <sup>-</sup> ≥ -39 V                                                                                                                                | 90  | 96    |       | dB    |

|                                     | $V^+ = 1 V, T_{MIN} \le T_J \le T_{MAX} \text{ (see }^{(1)}\text{)}$                                                                                           | 84  |       |       | dB    |

| Supply-voltage                      | $V^{+} = 1.1 V, T_{MIN} \le T_{J} \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                           | 84  |       |       | dB    |

| rejection                           | $1 \text{ V} \leq \text{V}^+ \leq 39.8 \text{ V}$                                                                                                              | 96  | 106   |       | dB    |

|                                     | 1.1 V $\leq$ V <sup>+</sup> $\leq$ 39.8 V, T <sub>MIN</sub> $\leq$ T <sub>J</sub> $\leq$ T <sub>MAX</sub> (see <sup>(1)</sup> )                                | 96  | 106   |       | dB    |

|                                     | $V^{-} = -0.2 V, T_{MIN} \le T_{J} \le T_{MAX}$ (see <sup>(1)</sup> )                                                                                          | 90  |       |       | dB    |

| Offset voltage drift                |                                                                                                                                                                |     | 2     |       | μV/°C |

| Offset current drift                |                                                                                                                                                                |     | 2     |       | pA/°C |

| Bias current drift                  | $T_{\rm C} < 100^{\circ}{\rm C}$                                                                                                                               |     | 60    |       | pA/°C |

|                                     | $1.2 \text{ V} \le \text{V}_{\text{S}} \le 40 \text{ V}$                                                                                                       |     | 0.001 | 0.003 | %/V   |

| Line regulation                     | $1.3 \text{ V} \le \text{V}_{\text{S}} \le 40 \text{ V}, \text{ T}_{\text{MIN}} \le \text{T}_{\text{J}} \le \text{T}_{\text{MAX}} \text{ (see }^{(1)}\text{)}$ |     | 0.001 | 0.003 | %/V   |

|                                     | $0 \le I_{REF} \le 1$ mA, $V_{REF} = 200$ mV, $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> )                                                              |     |       | 0.006 | %/V   |

|                                     | $0 \le I_{REF} \le 1 mA$                                                                                                                                       |     | 0.01% | 0.1%  |       |

| Load regulation                     | V <sup>+</sup> - V <sub>REF</sub> $\ge$ 1 V, T <sub>MIN</sub> $\le$ T <sub>J</sub> $\le$ T <sub>MAX</sub> (see <sup>(1)</sup> )                                |     |       | 0.15% |       |

|                                     |                                                                                                                                                                |     |       |       |       |

(1) These specifications apply for  $V^- \le V_{CM} \le V^+ - 0.85 V$ ,  $1 \lor (T_{MIN} \le T_J \le T_{MAX})$ ,  $1.2 \lor$ ,  $1.3 \lor (T_{MIN} \le T_J \le T_{MAX}) < V_S \le V_{MAX}$ ,  $V_{REF} = 0.2 \lor$  and  $0 \le I_{REF} \le 1$  mA, unless otherwise specified:  $V_{MAX} = 40 \lor$  for the standard part and  $6.5 \lor$  for the low voltage part. The full-temperature-range operation is  $-55^\circ$ C to  $125^\circ$ C for the LM10-MIL. The specifications do not include the effects of thermal gradients ( $\tau_1 \simeq T_{MAX} = 10 \lor$   $V_{MAX} = 10 \lor$   $V_{MAX} = 10 \lor$   $V_{MAX} = 10 \lor$ 20 ms), die heating ( $\tau_2 \approx 0.2$  s) or package heating. Gradient effects are small and tend to offset the electrical error (see curves). For  $T_J > 90^{\circ}$ C,  $I_{OS}$  may exceed 1.5 nA for  $V_{CM} = V^-$ . With  $T_J = 125^{\circ}$ C and  $V^- \leq V_{CM} \leq V^- + 0.1$  V,  $I_{OS} \leq 5$  nA. This defines operation in floating applications such as the bootstrapped regulator or two-wire transmitter. Output is connected to the V<sup>+</sup>

V<sup>+</sup>– V<sub>REF</sub>  $\ge$  1.1 V, T<sub>MIN</sub>  $\le$  T<sub>J</sub>  $\le$  T<sub>MAX</sub> (see <sup>(1)</sup>)

(3) terminal of the IC and input common mode is referred to V<sup>-</sup> (see System Examples). Effect of larger output-voltage swings with higher load resistance can be accounted for by adding the positive-supply rejection error.

Copyright © 2017, Texas Instruments Incorporated

0.15%

## **Electrical Characteristics (continued)**

| T <sub>J</sub> =25°C unless otherwise specified <sup>(1)</sup> | specified <sup>(1)</sup> | otherwise | T <sub>I</sub> =25°C unless |

|----------------------------------------------------------------|--------------------------|-----------|-----------------------------|

|----------------------------------------------------------------|--------------------------|-----------|-----------------------------|

| PARAMETER             | Т                                                   | MIN                                                 | TYP | MAX   | UNIT |      |

|-----------------------|-----------------------------------------------------|-----------------------------------------------------|-----|-------|------|------|

| A 1171 -              |                                                     | T <sub>J</sub> =25°C                                | 50  | 75    |      | V/mV |

| Amplifier gain        | 0.2 V ≤ V <sub>REF</sub> ≤ 35 V                     | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> ) | 23  |       |      | V/mV |

| Feedback sense        | T <sub>J</sub> =25°C                                | 195                                                 | 200 | 205   | mV   |      |

| voltage               | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> ) |                                                     | 194 |       | 206  | mV   |

| Feedback current      | T <sub>J</sub> =25°C                                |                                                     |     | 20    | 50   | nA   |

|                       | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> ) |                                                     |     |       | 65   | nA   |

| Reference drift       |                                                     |                                                     |     | 0.002 |      | %/°C |

| O market and the      | T <sub>J</sub> =25°C                                |                                                     |     | 270   | 400  | μA   |

| Supply current        | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> ) |                                                     |     |       | 500  | μA   |

| 0                     | 1.2 V ≤ V <sub>S</sub> ≤ 40 V                       | T <sub>J</sub> =25°C                                |     | 15    |      |      |

|                       | $1.2 V \leq V_{\rm S} \leq 40 V$                    | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> ) |     |       | 75   | μA   |

| Supply current change | 1.3 V ≤ V <sub>S</sub> ≤ 40 V                       | T <sub>J</sub> =25°C                                |     | 15    |      |      |

|                       | $1.3 V \ge V_S \ge 40 V$                            | $T_{MIN} \le T_J \le T_{MAX}$ (see <sup>(1)</sup> ) |     |       | 75   | μA   |

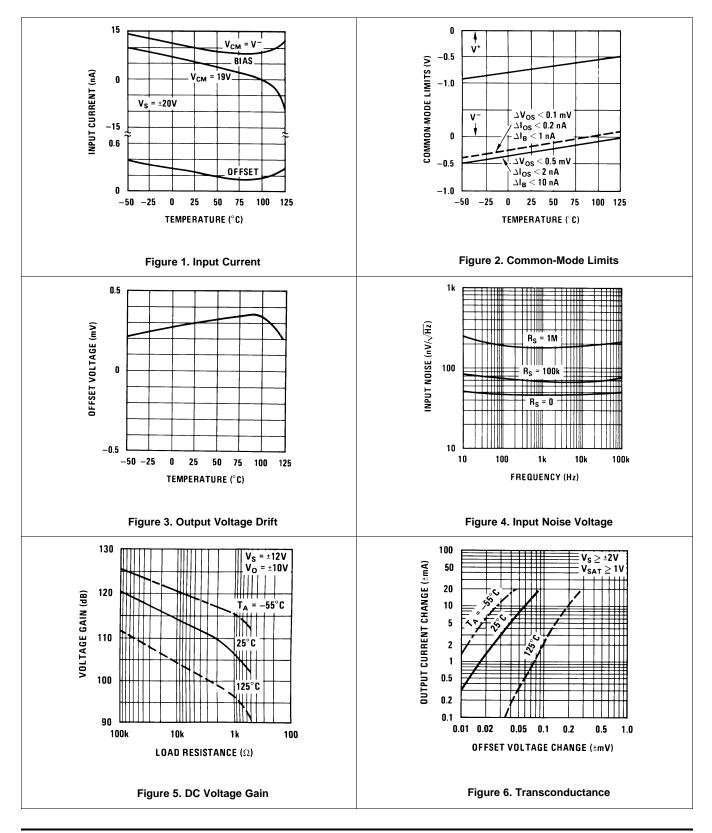

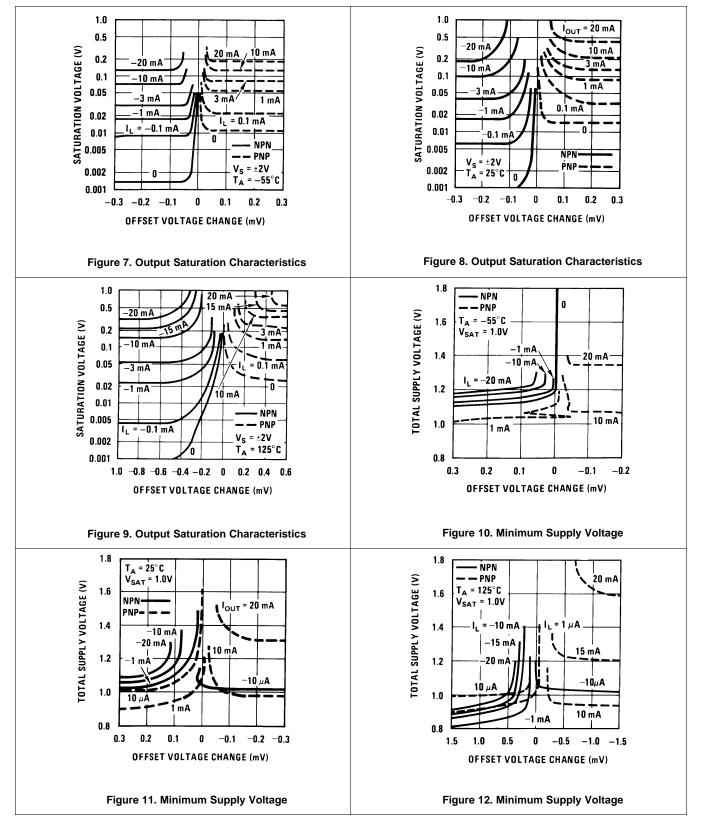

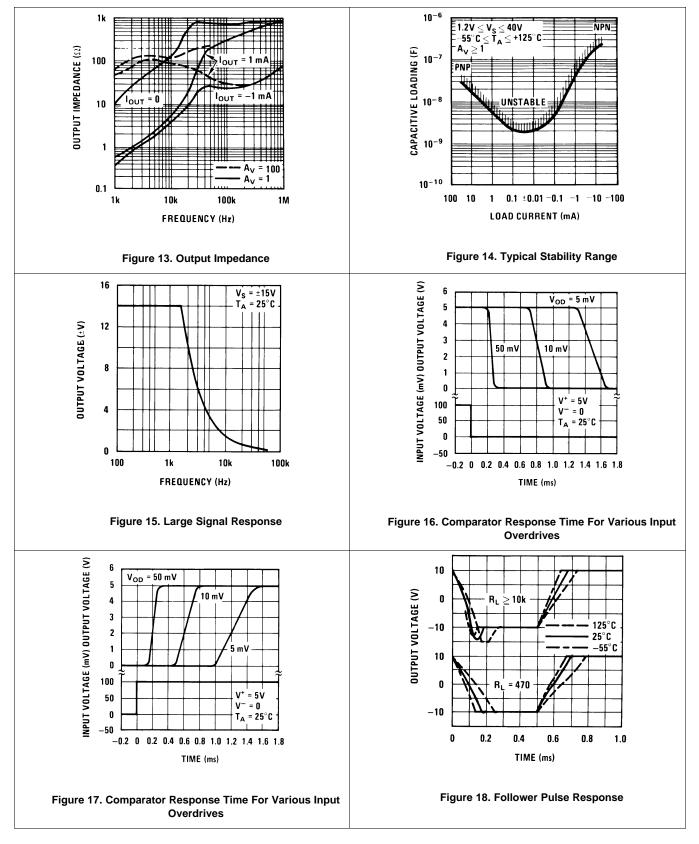

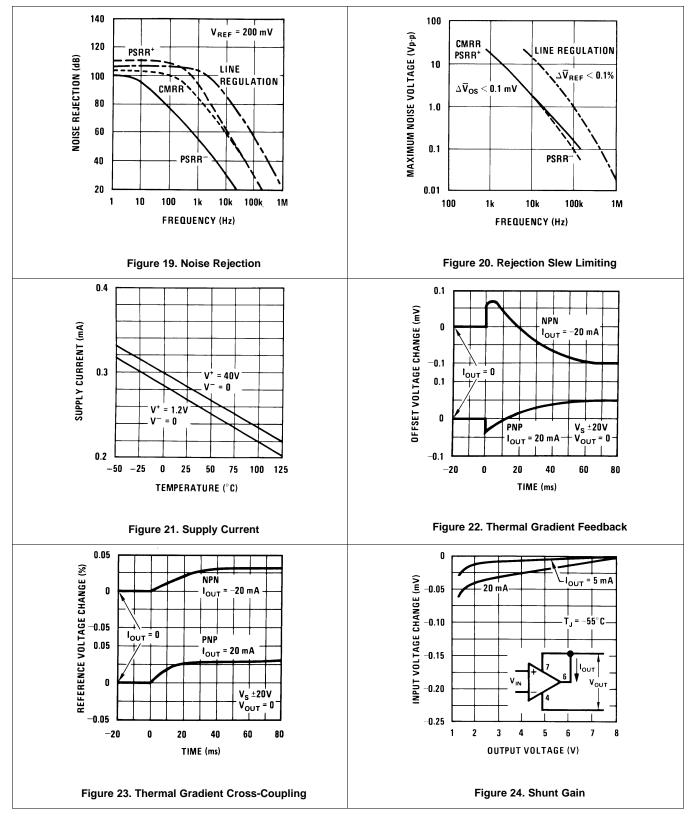

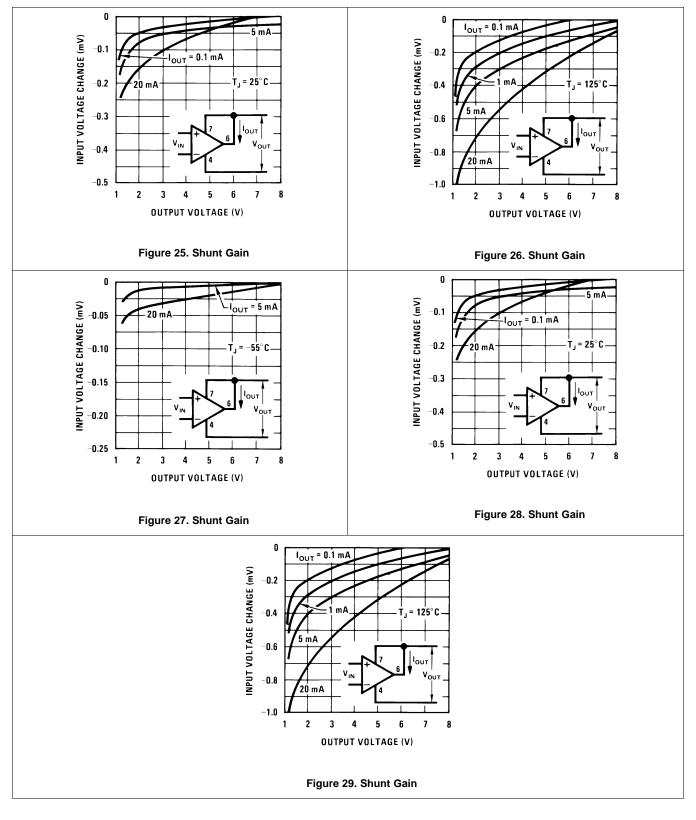

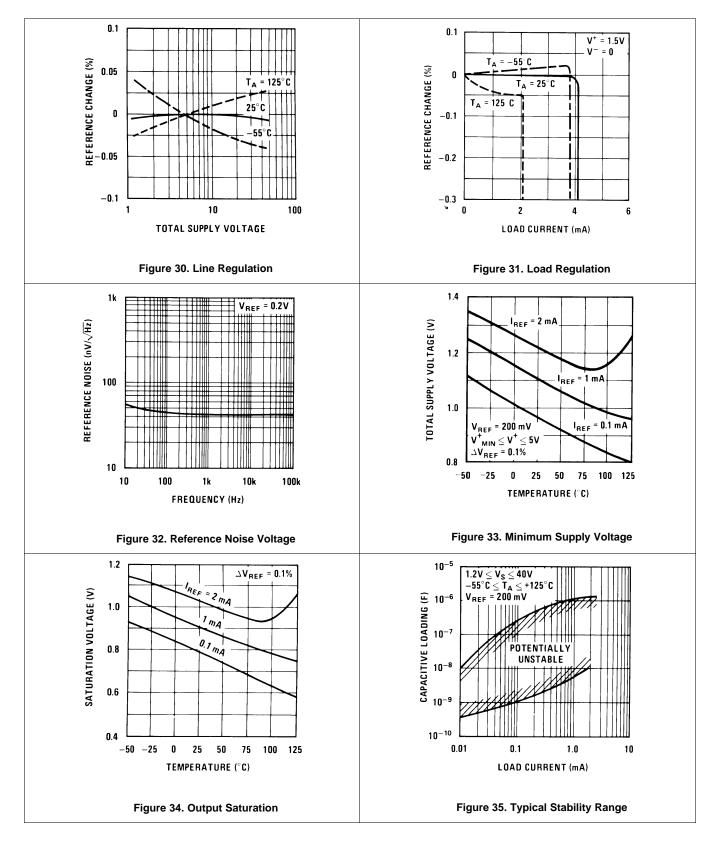

#### 6.5 Typical Characteristics

### 6.5.1 Typical Characteristics (Op Amp)

TEXAS INSTRUMENTS

www.ti.com

#### 6.5.2 Typical Characteristics (Reference)

### 7 Detailed Description

#### 7.1 Overview

The LM10-MIL is a dual-operational amplifier combined with a voltage reference capable of a single-supply operation down to 1.1 V. It provides high overall performance, making it ideal for many general-purpose applications. The circuit can also operate in a floating mode, powered by residual voltage, independent of fixed supplies and it is well-protected from temperature drift.

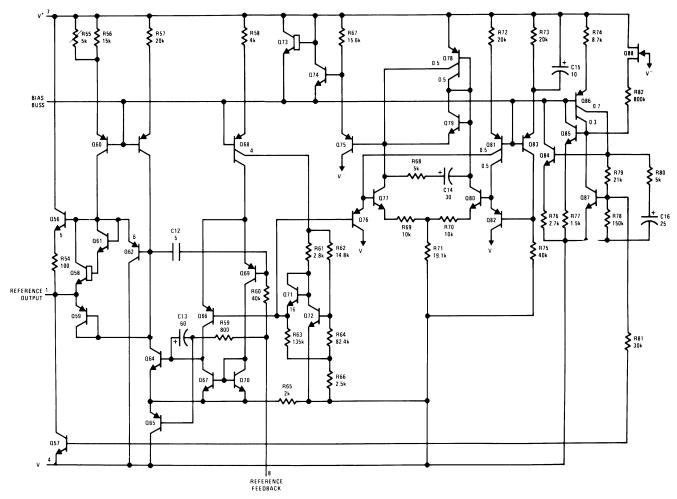

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Operating Characteristics

The LM10-MIL is specified for operation from 1.2 V to 40 V. Many of the specifications apply from -55°C to 125°C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in electrical characteristics tables under *Specifications* and in the *Typical Characteristics* section.

#### 7.3.2 Common-Mode Voltage Range

The input common-mode voltage range of the LM10-MIL extends from the negative rail to 0.85 V less than the positive rail.

#### 7.3.3 Operational Amplifier

The minimum operating voltage is reduced to nearly one volt and the current gain is less affected by temperature, resulting in a fairly flat bias current over temperature.

#### 7.3.4 Voltage Reference

Second-order nonlinearities are compensated for which eliminates the bowed characteristics of conventional designs, resulting in better temperature stability.

#### 7.4 Device Functional Modes

#### 7.4.1 Floating Mode

To use the device in a floating mode, the operational amplifier output is shorted to V+ which disables the PNP portion of the output stage. Thus, with a positive input signal, neither halves of the output conducts and the current between the supply terminals is equal to the quiescent supply current. With negative input signals, the NPN portion of the output begins to turn on, reaching the short circuit current for a few hundred microvolts overdrive.

#### 7.4.2 Linear Operation

This device can also operate linearly while in the floating mode. An example of this is shown in the *Typical Application* section.

Copyright © 2017, Texas Instruments Incorporated

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

With heavy amplifier loading to V<sup>-</sup>, resistance drops in the V<sup>-</sup> lead can adversely affect reference regulation. Lead resistance can approach 1  $\Omega$ . Therefore, the common to the reference circuitry should be connected as close as possible to the package.

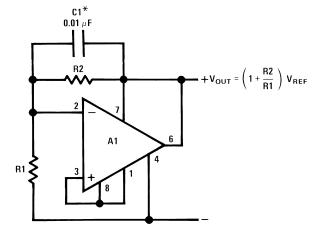

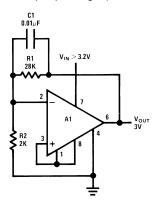

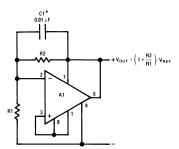

### 8.2 Typical Application

\* required for capacitive loading

### 8.2.1 Design Requirements

Table 1 lists the design parameters for this example.

| Table | 1. | Design | Parameters |

|-------|----|--------|------------|

|-------|----|--------|------------|

| DESIGN PARAMETERS         | EXAMPLE VALUE         |

|---------------------------|-----------------------|

| Ambient Temperature Range | -55°C to 125°C        |

| Supply Voltage Range      | 1.2 V to 40 V         |

| Common-Mode Input Range   | (V–) to (V+) – 0.85 V |

#### 8.2.2 Detailed Design Procedure

Given that the transfer function of this circuit is:

$$V_{OUT} = (1 + \frac{R_2}{R_1})V_{REF}$$

(1)

the output can be set between 0.2 V and the breakdown voltage of the IC by selecting an appropriate value for R2. The circuit regulates for input voltages within a saturation drop of the output (typically 0.4 V at 20 mA and 0.15 V at 5 mA). The regulator is protected from shorts or overloads by current limiting and thermal shutdown.

Typical regulation is about 0.05% load and 0.003%/V line. A substantial improvement in regulation can be effected by connecting the operational amplifier as a follower and setting the reference to the desired output voltage. This has the disadvantage that the minimum input-output differential is increased to a little more than a diode drop. If the operational amplifier were connected for a gain of 2, the output could again saturate. But this requires an additional pair of precision resistors.

The regulator in Figure 36 could be made adjustable to zero by connecting the operational amplifier to a potentiometer on the reference output. This has the disadvantage that the regulation at the lower voltage settings is not as good as it might otherwise be.

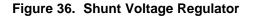

#### 8.2.3 Application Curve

Figure 37. Frequency Response

### 8.3 System Examples

Circuit descriptions available in application note AN-211 (SNOA638).

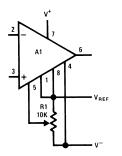

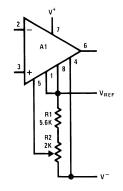

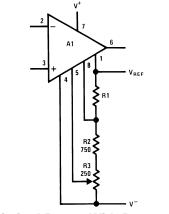

### 8.3.1 Operational Amplifier Offset Adjustment

(Pin numbers are for 8-pin packages)

Figure 38. Standard

Figure 39. Limited Range

## System Examples (continued)

(Pin numbers are for 8-pin packages)

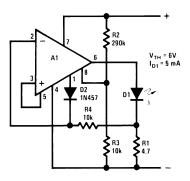

Figure 40. Limited Range With Boosted Reference

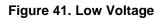

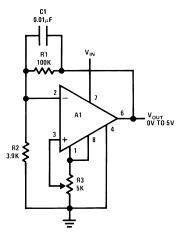

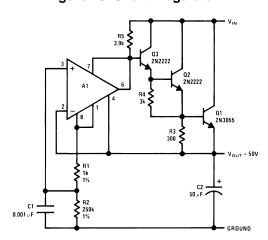

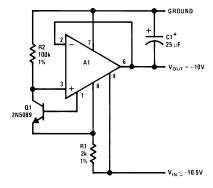

#### 8.3.2 Positive Regulators

(Pin numbers are for 8-pin packages)

Use only electrolytic output capacitors.

### Figure 43. Zero Output

Figure 42. Best Regulation

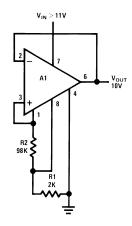

## Figure 44. Current Regulator

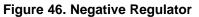

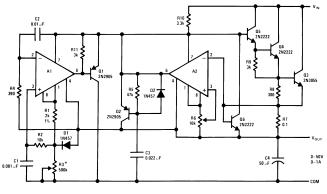

#### System Examples (continued)

(Pin numbers are for 8-pin packages)

Required For Capacitive Loading

Figure 45. Shunt Regulator

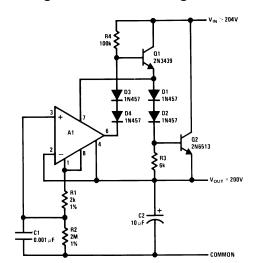

Figure 47. Precision Regulator

$V_{OUT} = \frac{R2}{R1} V_{REF}$

### Figure 49. HV Regulator

\*Electrolytic

\*V<sub>OUT</sub>=10<sup>-4</sup> R3

#### Figure 48. Laboratory Power Supply

#### Figure 50. Protected HV Regulator

TEXAS INSTRUMENTS

www.ti.com

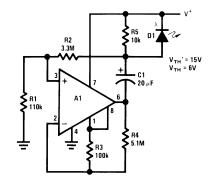

## System Examples (continued)

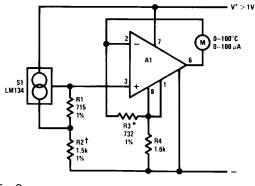

\*800°C Threshold Is Established By Connecting Balance To  $\mathsf{V}_{\mathsf{REF}}.$

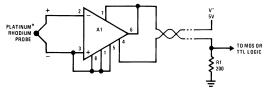

Figure 51. Flame Detector

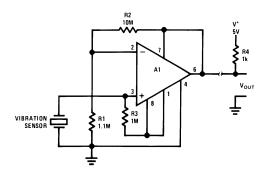

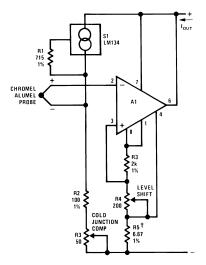

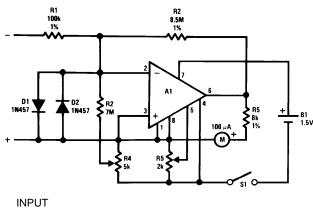

Figure 53. Remote Amplifier

\*Provides Hysteresis

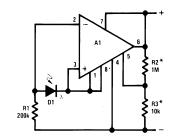

Figure 52. Light Level Sensor

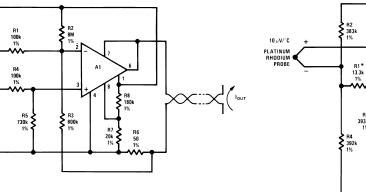

### Figure 54. Remote Thermocouple Amplifier

Figure 55. Transmitter for Bridge Sensor

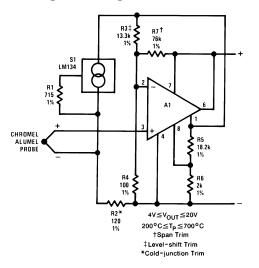

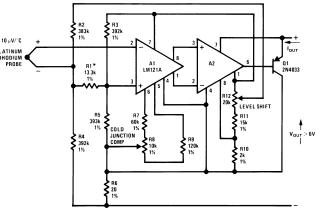

Figure 56. Precision Thermocouple Transmitter

RESISTIVE BRIDGE

#### System Examples (continued)

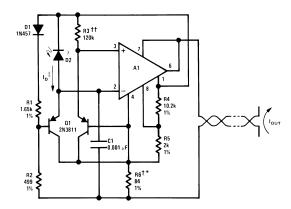

(Pin numbers are for 8-pin packages)

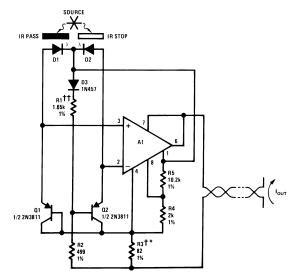

††Level-shift Trim \*Scale Factor Trim **†**Copper Wire Wound  $1 \text{ mA} \le I_{OUT} \le 5 \text{ mA}$  $0.01 \le \frac{I_{D2}}{I_{D1}} \le 100$

### Figure 57. Resistance Thermometer Transmitter

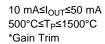

200°C≤T<sub>p</sub>≤700°C 1 mA≤l<sub>OUT</sub>≤5 mA †Gain Trim

> Figure 59. Thermocouple Transmitter

Figure 58. Optical Pyrometer

1 mA≤l<sub>OUT</sub>≤5 mA ‡50 μA≤I<sub>D</sub>≤500 μA ††Center Scale Trim +Scale Factor Trim \*Copper Wire Wound

TEXAS INSTRUMENTS

www.ti.com

## System Examples (continued)

(Pin numbers are for 8-pin packages)

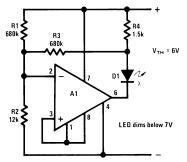

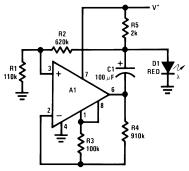

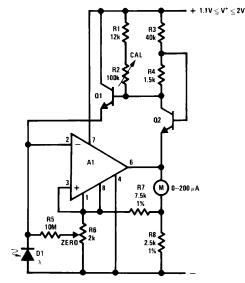

#### Figure 61. Battery-level Indicator

Flashes Above 1.2V Rate Increases With Voltage

### Figure 63. Single-cell Voltage Monitor

INPUT 10 mV, 100nA FULL-SCALE

Figure 62. Battery-threshold Indicator

Flash Rate Increases Above 6V and Below 15V

#### Figure 64. Double-ended Voltage Monitor

\*Trim For Span †Trim For Zero

Figure 66. Thermometer

### System Examples (continued)

(Pin numbers are for 8-pin packages)

$1 \leq \lambda/\lambda_0 \leq 10^5$

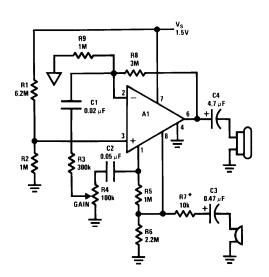

#### Figure 67. Light Meter

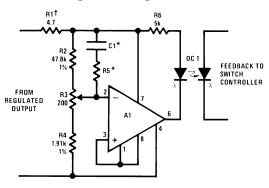

†Controls "Loop Gain"\*Optional Frequency Shaping

#### Figure 69. Isolated Voltage Sensor

$Z_{OUT}$ ~680 $\Omega$  @ 5 kHz A<sub>V</sub>≤1k  $f_1$ ~100 Hz  $f_2$ ~5 kHz R<sub>L</sub>~500 \*Max Gain Trim

#### Figure 68. Microphone Amplifier

Figure 70. Light-Level Controller

## System Examples (continued)

(Pin numbers are for 8-pin packages)

8.3.3 Reference and Internal Regulator

Figure 71. Reference and Internal Regulator

### 9 Power Supply Recommendations

The LM10-MIL is specified for operation from 1.2 V to 40 V unless otherwise stated. Many specifications apply from -55°C to 125°C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in the *Specifications* section.

#### CAUTION

Supply voltages larger than 40 V can permanently damage the device; see the *Absolute Maximum Ratings* table.

## 10 Layout

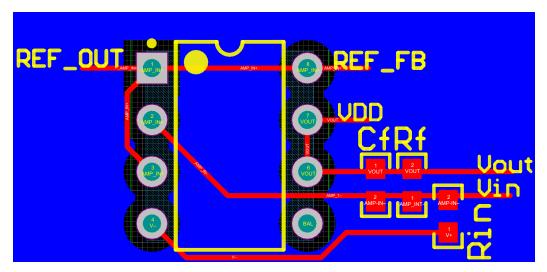

#### 10.1 Layout Guidelines

For best operational performance of the device, good printed-circuit board (PCB) layout practices are recommended. Low-loss, 0.1-uF bypass capacitors should be connected between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable to single-supply applications.

#### 10.2 Layout Example

Figure 72. Layout Example

## **11** Device and Documentation Support

#### 11.1 Device Support

#### 11.1.1 Device Nomenclature

#### 11.1.1.1 Definition of Terms

- Input offset voltage: That voltage which must be applied between the input terminals to bias the unloaded output in the linear region.

- Input offset current: The difference in the currents at the input terminals when the unloaded output is in the linear region.

- Input bias current: The absolute value of the average of the two input currents.

- Input resistance: The ratio of the change in input voltage to the change in input current on either input with the other grounded.

- Large signal voltage gain: The ratio of the specified output voltage swing to the change in differential input voltage required to produce it.

- **Shunt gain:** The ratio of the specified output voltage swing to the change in differential input voltage required to produce it with the output tied to the V<sup>+</sup> terminal of the IC. The load and power source are connected between the V<sup>+</sup> and V<sup>-</sup> terminals, and input common-mode is referred to the V<sup>-</sup> terminal.

- **Common-mode rejection:** The ratio of the input voltage range to the change in offset voltage between the extremes.

- Supply-voltage rejection: The ratio of the specified supply-voltage change to the change in offset voltage between the extremes.

Line regulation: The average change in reference output voltage over the specified supply voltage range.

Load regulation: The change in reference output voltage from no load to that load specified.

- **Feedback sense voltage:** The voltage, referred to V<sup>-</sup>, on the reference feedback terminal while operating in regulation.

- **Reference amplifier gain:** The ratio of the specified reference output change to the change in feedback sense voltage required to produce it.

Feedback current: The absolute value of the current at the feedback terminal when operating in regulation.

Supply current: The current required from the power source to operate the amplifier and reference with their outputs unloaded and operating in the linear range.

#### **11.2 Documentation Support**

#### 11.2.1 Related Documentation

For related documentation, see the following: AN-211 New Op Amp Ideas, SNOA638

#### . . .

### **11.3 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

- TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

- **Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan     | Lead finish/  | inish/ MSL Peak Temp |           | Device Marking                        | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|----------------------|-----------|---------------------------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                  |           | (4/5)                                 |         |

|                  |        |              |         |      |         |              | (6)           |                      |           |                                       |         |

| LM10BH           | ACTIVE | TO-CAN       | LMG     | 8    | 500     | Non-RoHS     | Call TI       | Level-1-NA-UNLIM     | -40 to 85 | ( LM10BH, LM10BH)                     | Samples |

|                  |        |              |         |      |         | & Green      |               |                      |           |                                       | Bampies |

| LM10BH/NOPB      | ACTIVE | TO-CAN       | LMG     | 8    | 500     | RoHS & Green | Call TI       | Level-1-NA-UNLIM     | -40 to 85 | ( LM10BH, LM10BH)                     | Samples |

|                  |        |              |         |      |         |              |               |                      |           |                                       | Samples |

| LM10CH           | ACTIVE | TO-CAN       | LMG     | 8    | 500     | Non-RoHS     | Call TI       | Level-1-NA-UNLIM     | 0 to 70   | ( LM10CH, LM10CH)                     | Samples |

|                  |        |              |         |      |         | & Green      |               |                      |           |                                       | Bampies |

| LM10CH/NOPB      | ACTIVE | TO-CAN       | LMG     | 8    | 500     | RoHS & Green | Call TI       | Level-1-NA-UNLIM     | 0 to 70   | ( LM10CH, LM10CH)                     | Comulas |

|                  |        |              |         |      |         |              |               |                      |           | · · · · · · · · · · · · · · · · · · · | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

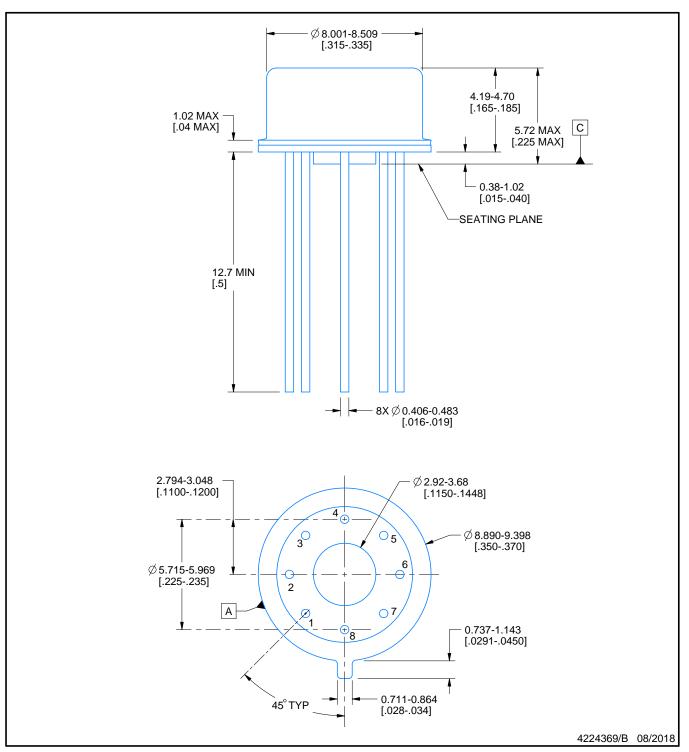

# LMG0008A

# **PACKAGE OUTLINE**

## TO-CAN - 5.72 mm max height

METAL CYLINDRICAL PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters [inches]. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

# LMG0008A

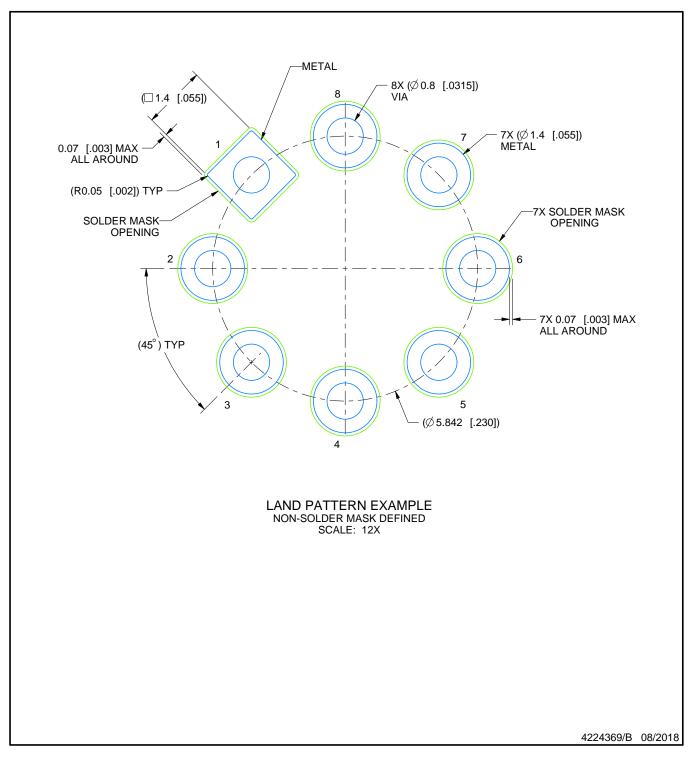

# **EXAMPLE BOARD LAYOUT**

# TO-CAN - 5.72 mm max height

METAL CYLINDRICAL PACKAGE

| REVISIONS |                                              |         |            |                          |  |  |  |

|-----------|----------------------------------------------|---------|------------|--------------------------|--|--|--|

| REV       | DESCRIPTION                                  | ECR     | DATE       | ENGINEER / DRAFTER       |  |  |  |

| А         | RELEASE NEW DRAWING                          | 2174627 | 07/10/2018 | V. DASIKA / K. SINCERBOX |  |  |  |

| В         | CHANGE TO DUAL DIMENSIONING MM [INCH] FORMAT | 2175848 | 08/17/2018 | V. DASIKA / K. SINCERBOX |  |  |  |

|           |                                              |         |            |                          |  |  |  |

| SCALE | SIZE<br>A | 4224369 | B | PAGE<br>4 of 4 |

|-------|-----------|---------|---|----------------|

|       |           |         |   |                |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated