LMX2531

SNAS252S - OCTOBER 2005 - REVISED DECEMBER 2014

# LMX2531 High-Performance Frequency Synthesizer System With Integrated VCO

## **Features**

- Multiple Frequency Options Available

- See Device Information Table

- Frequencies From: 553 MHz to 3132 MHz

- **PLL Features**

- Fractional-N Delta-Sigma Modulator Order Programmable up to Fourth Order

- FastLock/Cycle Slip Reduction with Timeout Counter

- Partially Integrated, Adjustable Loop Filter

- Very Low Phase Noise and Spurs

- **VCO** Features

- Integrated Tank Inductor

- Low Phase Noise

- Other Features

- 2.8-V to 3.2-V Operation

- Low Operating Current

- Low Power-Down Current

- 1.8-V MICROWIRE Support

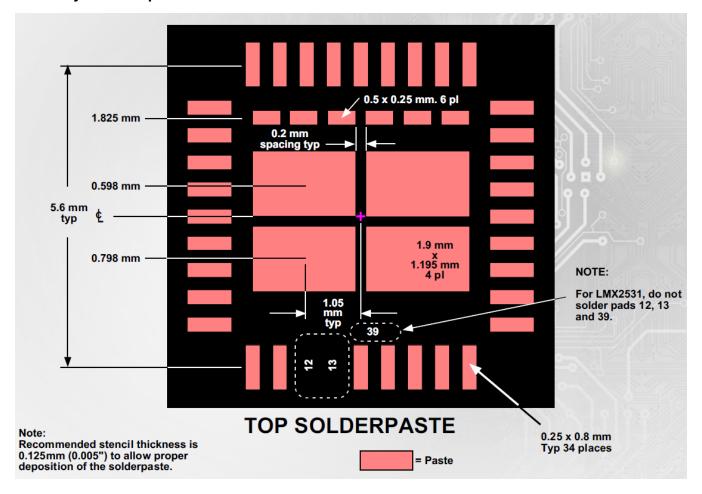

- 36-Pin 6-mm x 6-mm x 0.8-mm WQFN Package

## **Applications**

- Cellular Base Stations

- Wireless LANs

- **Broadband Wireless Access**

- Satellite Communications

- Wireless Radios

- Automotive

- **CATV** Equipment

- Instrumentation and Test Equipment

- **RFID Readers**

- **Data Converter Clocking**

## 3 Description

The LMX2531 is a low-power, high-performance frequency synthesizer system which includes a fully integrated delta-sigma PLL and VCO with fully integrated tank circuit. The third and fourth poles are also integrated and adjustable. Ultra-low noise and high-precision LDOs are integrated for the PLL and VCO, which yield higher supply-noise immunity and more consistent performance. When combined with a high-quality reference oscillator, the LMX2531 device generates very stable, low-noise local-oscillator signals for up and down conversion in wireless communication devices. The LMX2531 device is a monolithic integrated circuit, fabricated in an BiCMOS process. advanced Several different versions of this product accommodate different frequency bands.

#### Device Information<sup>(1)</sup>

| Device information, |                 |                 |  |  |  |  |  |

|---------------------|-----------------|-----------------|--|--|--|--|--|

| PART                | LOW BAND        | HIGH BAND       |  |  |  |  |  |

| LMX2531LQ1146E      | 553 — 592 MHz   | 1106 — 1184 MHz |  |  |  |  |  |

| LMX2531LQ1226E      | 592 — 634 MHz   | 1184 — 1268 MHz |  |  |  |  |  |

| LMX2531LQ1312E      | 634 — 680 MHz   | 1268 — 1360 MHz |  |  |  |  |  |

| LMX2531LQ1415E      | 680 — 735 MHz   | 1360 — 1470 MHz |  |  |  |  |  |

| LMX2531LQ1500E      | 749.5 — 755 MHz | 1499 — 1510 MHz |  |  |  |  |  |

| LMX2531LQ1515E      | 725 — 790 MHz   | 1450 — 1580 MHz |  |  |  |  |  |

| LMX2531LQ1570E      | 765 — 818 MHz   | 1530 — 1636 MHz |  |  |  |  |  |

| LMX2531LQ1650E      | 795 — 850 MHz   | 1590 — 1700 MHz |  |  |  |  |  |

| LMX2531LQ1700E      | 831 — 885 MHz   | 1662 — 1770 MHz |  |  |  |  |  |

| LMX2531LQ1742       | 880 — 933 MHz   | 1760 — 1866 MHz |  |  |  |  |  |

| LMX2531LQ1778E      | 863 — 920 MHz   | 1726 — 1840 MHz |  |  |  |  |  |

| LMX2531LQ1910E      | 917 — 1014 MHz  | 1834 — 2028 MHz |  |  |  |  |  |

| LMX2531LQ2080E      | 952 — 1137 MHz  | 1904 — 2274 MHz |  |  |  |  |  |

| LMX2531LQ2265E      | 1089 — 1200 MHz | 2178 — 2400 MHz |  |  |  |  |  |

| LMX2531LQ2570E      | 1168 — 1395 MHz | 2336 — 2790 MHz |  |  |  |  |  |

| LMX2531LQ2820E      | 1355 — 1462 MHz | 2710 — 2925 MHz |  |  |  |  |  |

| LMX2531LQ3010E      | 1455 — 1566 MHz | 2910 — 3132 MHz |  |  |  |  |  |

|                     |                 |                 |  |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

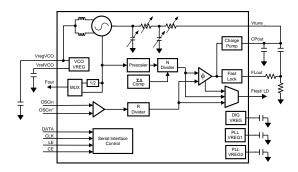

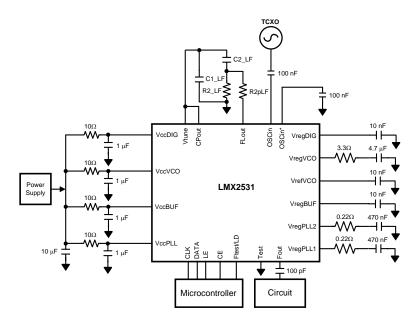

# **Simplified Schematic**

## **Table of Contents**

| 1 | Features 1                              |       | 8.4 Device Functional Modes          | 20   |

|---|-----------------------------------------|-------|--------------------------------------|------|

| 1 |                                         |       | 8.5 Programming                      |      |

| 2 | Applications 1                          |       | 8.6 Register Maps                    |      |

| 3 | Description 1                           | •     |                                      |      |

| 4 | Simplified Schematic1                   | 9     | Application and Implementation       |      |

| 5 | Revision History2                       |       | 9.1 Application Information          | . 33 |

| 6 | Pin Configuration and Functions 3       |       | 9.2 Typical Application              | . 33 |

|   | _                                       |       | 9.3 Do's and Don'ts                  | . 35 |

| 7 | Specifications5                         | 10    | Power Supply Recommendations         | . 35 |

|   | 7.1 Absolute Maximum Ratings 5          | 11    | Layout                               |      |

|   | 7.2 ESD Ratings5                        | • • • |                                      |      |

|   | 7.3 Recommended Operating Conditions 5  |       | 11.1 Layout Guidelines               |      |

|   | 7.4 Thermal Information5                |       | 11.2 Layout Example                  | . 36 |

|   | 7.5 Electrical Characteristics          | 12    | Device and Documentation Support     | . 37 |

|   | 7.6 MICROWIRE Timing Requirements       |       | 12.1 Device Support                  | . 37 |

|   | 7.7 Typical Performance Characteristics |       | 12.2 Trademarks                      | . 37 |

| 8 | · · ·                                   |       | 12.3 Electrostatic Discharge Caution | . 37 |

| 0 | Detailed Description                    |       | 12.4 Glossary                        |      |

|   | 8.1 Overview                            | 42    | •                                    |      |

|   | 8.2 Functional Block Diagram 15         | 13    | Mechanical, Packaging, and Orderable | 27   |

|   | 8.3 Feature Description                 |       | Information                          | . 37 |

|   |                                         |       |                                      |      |

# 5 Revision History

| Changes from | Revision  | R ( | April | 2013) | to | Revision  | S |

|--------------|-----------|-----|-------|-------|----|-----------|---|

| Onangeo nom  | 110101011 | .,, | , (P  | _0.0, |    | 110101011 | • |

**Page**

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

## Changes from Revision Q (February 2013) to Revision R

**Page**

# 6 Pin Configuration and Functions

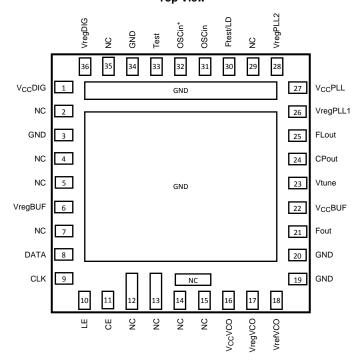

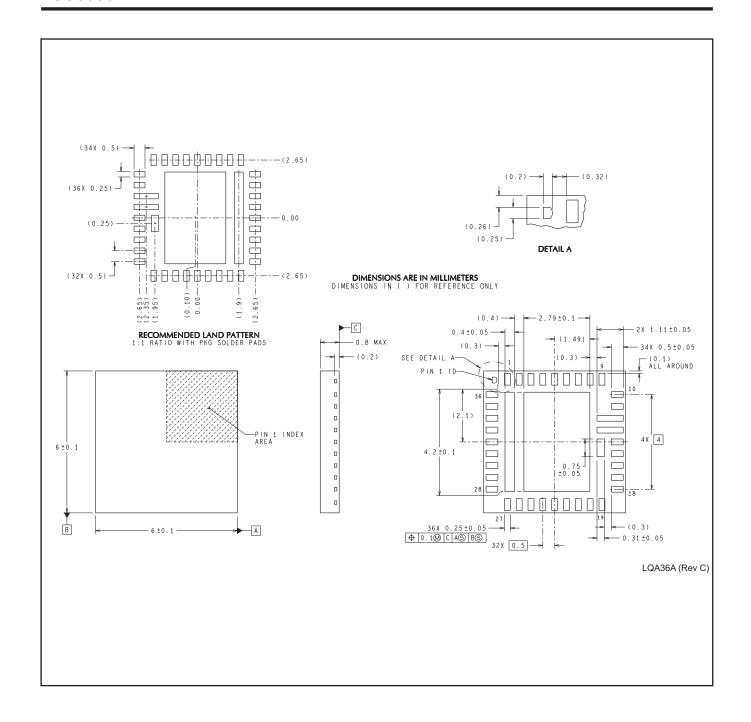

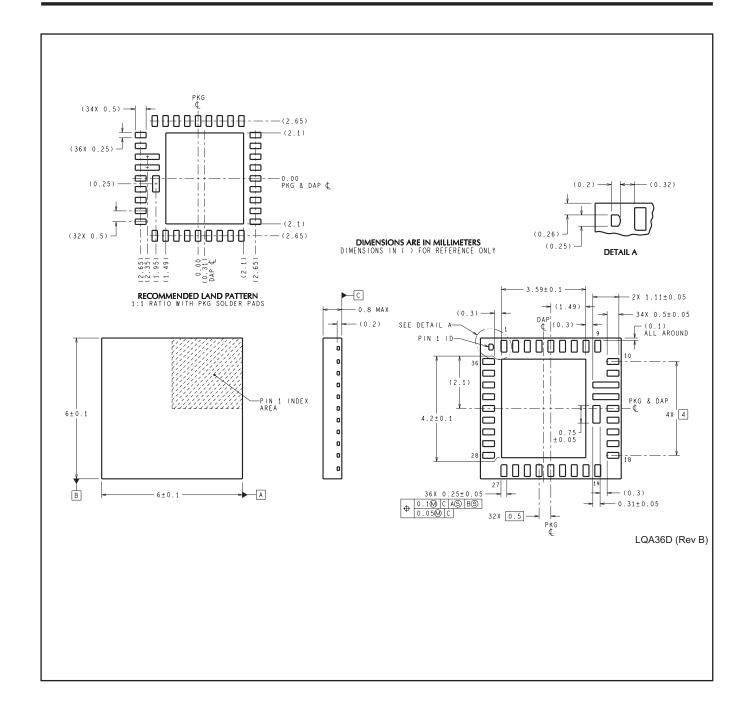

NJH0036D Package 36-Pin WQFN, D Version, (LMX2531LQ1146E/1226E/1312E/1415E/1515E/2820E/3010E) Top View

#### NJG0036A Package 36-Pin WQFN, A Version, (All Other Versions) Top View

## **Pin Functions**

| PI       | N                             |        |                                                                                                                                                                                                                                                                                                                          |  |  |

|----------|-------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.                           | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                              |  |  |

| CE       | 11                            | Input  | Chip Enable Input. High impedance CMOS input. This pin must not exceed 2.75 V. When CE is brought high the LMX2531 is powered up corresponding to the internal power control bits. Although the part can be programmed when powered down, it is still necessary to reprogram the R0 register to get the part to re-lock. |  |  |

| CLK      | 9                             | Input  | MICROWIRE clock input. High impedance CMOS input. This pin must not exceed 2.75 V. Data is clocked into the shift register on the rising edge.                                                                                                                                                                           |  |  |

| CPout    | 24                            | Output | Charge pump output for PLL. For connection to Vtune through an external passive loop filter.                                                                                                                                                                                                                             |  |  |

| DATA     | 8                             | Input  | MICROWIRE serial data input. High impedance CMOS input. This pin must not exceed 2.75 V. Data is clocked in MSB first. The last bits clocked in form the control or register select bits.                                                                                                                                |  |  |

| FLout    | 25                            | Output | An open drain NMOS output which is used for FastLock or a general purpose output.                                                                                                                                                                                                                                        |  |  |

| Fout     | 21                            | Output | Buffered RF Output for the VCO.                                                                                                                                                                                                                                                                                          |  |  |

| Ftest/LD | 30                            | Output | Multiplexed CMOS output. Typically used to monitor PLL lock condition.                                                                                                                                                                                                                                                   |  |  |

| GND      | 3                             | _      | Ground                                                                                                                                                                                                                                                                                                                   |  |  |

| GND      | 19                            | _      | Ground for the VCO circuitry.                                                                                                                                                                                                                                                                                            |  |  |

| GND      | 20                            | _      | Ground for the VCO Output Buffer circuitry.                                                                                                                                                                                                                                                                              |  |  |

| GND      | 34                            | _      | Ground                                                                                                                                                                                                                                                                                                                   |  |  |

| LE       | 10                            | Input  | MICROWIRE Latch Enable input. High impedance CMOS input. This pin must not exceed 2.75 V. Data stored in the shift register is loaded into the selected latch register when LE goes HIGH.                                                                                                                                |  |  |

| NC       | 2, 4, 5, 7, 12,<br>13, 29, 35 | _      | No Connect.                                                                                                                                                                                                                                                                                                              |  |  |

| NC       | 14, 15                        | _      | No Connect. Do NOT ground. This also includes the pad above these pins.                                                                                                                                                                                                                                                  |  |  |

| OSCin    | 31                            | Input  | Oscillator input.                                                                                                                                                                                                                                                                                                        |  |  |

| OSCin*   | 32                            | Input  | Oscillator complimentary input. When a single ended source is used, then a bypass capacitor should be placed as close as possible to this pin and be connected to ground.                                                                                                                                                |  |  |

| Test     | 33                            | Output | This pin is for test purposes and should be grounded for normal operation.                                                                                                                                                                                                                                               |  |  |

| VccBUF   | 22                            | _      | Power Supply for the VCO Buffer circuitry. Input may range from 2.8 $-$ 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                           |  |  |

| VccDIG   | 1                             | _      | Power Supply for digital LDO circuitry. Input may range from 2.8 — 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                                |  |  |

| VccPLL   | 27                            | _      | Power Supply for the PLL. Input may range from 2.8 $-$ 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                                            |  |  |

| VccVCO   | 16                            | _      | Power Supply for VCO regulator circuitry. Input may range from 2.8 — 3.2 V. Bypass capacitors should be placed as close as possible to this pin and ground.                                                                                                                                                              |  |  |

| VrefVCO  | 18                            | _      | Internal reference voltage for VCO LDO. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                                                                                      |  |  |

| VregBUF  | 6                             | _      | Internally regulated voltage for the VCO buffer circuitry. Connect to ground with a capacitor.                                                                                                                                                                                                                           |  |  |

| VregDIG  | 36                            | _      | Internally regulated voltage for LDO digital circuitry.                                                                                                                                                                                                                                                                  |  |  |

| VregPLL1 | 26                            | _      | Internally regulated voltage for PLL charge pump. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                                                                            |  |  |

| VregPLL2 | 28                            | _      | Internally regulated voltage for RF digital circuitry. Not intended to drive an external load. Connect to ground with a capacitor.                                                                                                                                                                                       |  |  |

| VregVCO  | 17                            | _      | Internally regulated voltage for VCO circuitry. Not intended to drive an external load. Connect to ground with a capacitor and some series resistance.                                                                                                                                                                   |  |  |

| Vtune    | 23                            | Input  | Tuning voltage input for the VCO. For connection to the CPout pin through an external passive loop filter.                                                                                                                                                                                                               |  |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                        |                                  | MIN  | MAX | UNIT |

|--------------------------------------------------------|----------------------------------|------|-----|------|

| V <sub>CC</sub><br>(VccDIG, VccVCO,<br>VccBUF, VccPLL) | Power Supply Voltage             | -0.3 | 3.5 | V    |

| All other pins (Except Ground)                         | Power Supply Voltage             | -0.3 | 3.0 | V    |

| T <sub>L</sub>                                         | Lead Temperature (solder 4 sec.) |      | 260 | °C   |

| T <sub>J</sub>                                         | Junction Temperature             |      | 125 | °C   |

| T <sub>stg</sub>                                       | Storage temperature              | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

7.2 ESD Ratings

|                    |                                                        |                                                                                | VALUE | UNIT |

|--------------------|--------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±500                                                                           |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                               | MIN | NOM | MAX  | UNIT |

|-----------------|-----------------------------------------------|-----|-----|------|------|

| V <sub>CC</sub> | Power Supply Voltage (VccDig, VccVCO, VccBUF) | 2.8 | 3.0 | 3.2  | V    |

| Vi              | Serial Interface and Power Control Voltage    | 0   |     | 2.75 | ٧    |

| T <sub>A</sub>  | Ambient Temperature <sup>(1)</sup>            | -40 |     | 85   | °C   |

<sup>(1)</sup> Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the R0 register was last programmed, and still have the part stay in lock. The action of programming the R0 register, even to the same value, activates a frequency calibration routine. This implies that the part will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reload the R0 register to ensure that it stays in lock. Regardless of what temperature the part was initially programmed at, the temperature can never drift outside the frequency range of −40°C ≤ T<sub>A</sub> ≤ 85°C without violating specifications.

#### 7.4 Thermal Information

|                 |                                              | LMX2531  | LMX2531  |      |

|-----------------|----------------------------------------------|----------|----------|------|

|                 | THERMAL METRIC <sup>(1)</sup>                | NJH0036D | NJG0036A | UNIT |

|                 |                                              | 36 PINS  | 36 PINS  |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 35.5     | 35.5     | °C/W |

| ΨЈВ             | Junction-to-board characterization parameter | 9.1      | 9.1      | C/VV |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report (SPRA953).

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

#### 7.5 Electrical Characteristics

$(V_{CC} = 3.0 \text{ V}, -40^{\circ}\text{C} \le T_A \le 85 ^{\circ}\text{C}; \text{ except as specified.})$

|                        | PARAMETER                                                | TEST COND                                                   | ITIONS                   | MIN  | TYP  | MAX | UNIT   |

|------------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------|------|------|-----|--------|

| CURRENT                | T CONSUMPTION                                            | ,                                                           |                          | 1    |      |     |        |

|                        | Divider Disabled                                         |                                                             | LMX2531LQ2265E/<br>2570E |      | 38   | 44  |        |

|                        |                                                          | Divider Disabled                                            | LMX2531LQ2820E/<br>3010E |      | 38   | 46  |        |

|                        | Power Supply Current Power                               |                                                             | All Other Options        |      | 34   | 41  | mA     |

| lcc                    | Supply Current                                           |                                                             | LMX2531LQ2265E/<br>2570E |      | 41   | 49  | MA     |

|                        |                                                          | Divider Enabled                                             | LMX2531LQ2820E/<br>3010E |      | 44   | 52  |        |

|                        |                                                          |                                                             | All Other Options        |      | 37   | 46  |        |

| I <sub>CC</sub> PD     | Power Down Current                                       | CE = 0 V, Part Initialized                                  |                          |      | 7    |     | μΑ     |

| OSCILLA                | TOR                                                      |                                                             |                          |      |      |     |        |

| I <sub>IH</sub> OSC    | Oscillator Input High Current                            | V <sub>IH</sub> = 2.75 V                                    |                          |      |      | 100 | μΑ     |

| I <sub>IL</sub> OSC    | Oscillator Input Low Current                             | V <sub>IL</sub> = 0                                         |                          | -100 |      |     | μA     |

| f <sub>OSCin</sub>     | Frequency Range                                          | See <sup>(1)</sup>                                          |                          | 5    |      | 80  | MHz    |

| V <sub>OSCin</sub>     | Oscillator Sensitivity                                   |                                                             |                          | 0.5  |      | 2.0 | Vpp    |

| PLL                    |                                                          |                                                             |                          |      |      |     |        |

| f <sub>PD</sub>        | Phase Detector Frequency                                 |                                                             |                          |      |      | 32  | MHz    |

|                        |                                                          | ICP = 0                                                     |                          |      | 90   |     | μA     |

|                        | Charge Pump                                              | ICP = 1                                                     |                          |      | 180  |     | μA     |

| CPout                  | Output Current Magnitude                                 | ICP = 3                                                     |                          |      | 360  |     | μA     |

|                        |                                                          | ICP = 15                                                    |                          |      | 1440 |     | μA     |

| I <sub>CPout</sub> TRI | CP TRI-STATE Current                                     | 0.4 V < V <sub>CPout</sub> < 2.0 V                          |                          |      | 2    | 10  | nA     |

| I <sub>CPout</sub> MM  | Charge Pump<br>Sink vs Source Mismatch                   | $V_{CPout} = 1.2 V$<br>$T_A = 25$ °C                        |                          |      | 2%   | 8%  |        |

| I <sub>CPout</sub> V   | Charge Pump<br>Current vs CP Voltage Variation           | 0.4 V < V <sub>CPout</sub> < 2.0 V<br>T <sub>A</sub> = 25°C |                          |      | 4%   |     |        |

| I <sub>CPout</sub> T   | CP Current vs Temperature Variation                      | V <sub>CPout</sub> = 1.2 V                                  |                          |      | 8%   |     |        |

|                        | Normalized PLL 1/f Noise                                 | ICP = 1X Charge Pump Gain                                   |                          |      | -94  |     |        |

| LN(f)                  | LN <sub>PLL flicker</sub> (10 kHz)<br>See <sup>(2)</sup> | ICP = 16X Charge Pump Gain                                  |                          |      | -104 |     | dBc/Hz |

| LIN(I)                 | Normalized PLL Noise Floor                               | ICP = 1X Charge Pump Gain                                   |                          |      | -202 |     | ID //: |

|                        | LN <sub>PLL_flat</sub><br>See <sup>(3)</sup>             | ICP = 16X Charge Pump Gain                                  |                          |      | -212 |     | dBc/Hz |

- (1) There are program bits that need to be set based on the OSCin frequency. Refer to the following sections: XTLSEL[2:0] -- OSCin Select, XTLDIV[1:0] -- Division Ratio for the OSCin Frequency, XTLMAN[11:0] -- Manual OSCin Mode, XTLMAN2 -- Manual Crystal Mode Second Adjustment, and LOCKMODE -- Frequency Calibration Mode. Not all bit settings can be used for all frequency choices of OSCin. For instance, automatic modes described in XTLSEL[2:0] -- OSCin Select do not work below 8 MHz.

- (2) One of the specifications for modeling PLL in-band phase noise is the PLL 1/f noise normalized to 1 GHz carrier frequency and 10 kHz offset, L<sub>PLL\_flicker</sub>(10 kHz). From this normalized index of PLL 1/f noise, the PLL 1/f noise can be calculated for any carrier and offset frequency as: LN<sub>PLL\_flicker</sub>(f) = L<sub>PLL\_flicker</sub>(10 kHz) 10 x log (10 kHz / f) + 20 x log (F<sub>out</sub> / 1 GHz). Flicker noise can dominate at low offsets from the carrier and has a 10 dB/decade slope and improves with higher charge pump currents and at higher offset frequencies. To accurately measure L<sub>PLL\_flicker</sub>(10 kHz) it is important to use a high phase detector frequency and a clean reference to make it such that this measurement is on the 10 dB/decade slope close to the carrier. L<sub>PLL\_flicker</sub>(f) can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of L<sub>PLL\_flicker</sub>(f) and L<sub>PLL\_flicker</sub>(f) = 10 x log (10 (LN<sub>PLL\_flicker</sub>(f) + 10) + 10(LN<sub>PLL\_flicker</sub>(f) / 10)

(3) A specification used for modeling PLL in-band phase noise floor is the Normalized PLL noise floor, LN<sub>PLL\_flick</sub>, and is defined as:

- (3) A specification used for modeling PLL in-band phase noise floor is the Normalized PLL noise floor, LN<sub>PLL\_flat</sub>, and is defined as: LN<sub>PLL\_flat</sub> = L(f) 20 × log (N) 10 × log(f<sub>PD</sub>). L<sub>PLL\_flat</sub> is the single side band phase noise in a 1 Hz Bandwidth and f<sub>PD</sub> is the phase detector frequency of the synthesizer. L<sub>PLL\_flat</sub> contributes to the total noise, L(f). To measure L<sub>PLL\_flat</sub> the offset frequency must be chosen sufficiently smaller then the loop bandwidth of the PLL, and yet large enough to avoid a substantial noise contribution from the reference and PLL flicker noise. L<sub>PLL\_flat</sub> can be masked by the reference oscillator performance if a low power or noisy source is used. The total PLL in-band phase noise performance is the sum of L<sub>PLL\_flicker</sub>(f) and L<sub>PLL\_flat</sub>. In other words, L<sub>PLL</sub>(f) = 10 × log (10 (LN<sub>PLL\_flat</sub>) / 10 ) + 10 (LN<sub>PLL\_flat</sub>) / 10 )

Submit Documentation Feedback

Copyright © 2005–2014, Texas Instruments Incorporated

$(V_{CC} = 3.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le 85 ^{\circ}\text{C}; \text{ except as specified.})$

| . 55              | $3.0 \text{ V}, -40^{\circ}\text{C} \le 1_{\text{A}} \le 85 ^{\circ}\text{C}; \text{ exce}$         | TEST CONDITIONS                                              | MIN  | TYP MAX | UNIT |

|-------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|---------|------|

| VCO FR            | EQUENCIES                                                                                           |                                                              |      |         |      |

|                   |                                                                                                     | LMX2531LQ1146E                                               | 1106 | 1184    |      |

|                   |                                                                                                     | LMX2531LQ1226E                                               | 1184 | 1268    |      |

|                   |                                                                                                     | LMX2531LQ1312E                                               | 1268 | 1360    |      |

|                   |                                                                                                     | LMX2531LQ1415E                                               | 1360 | 1470    |      |

| f <sub>Fout</sub> |                                                                                                     | LMX2531LQ1500E                                               | 1499 | 1510    |      |

|                   |                                                                                                     | LMX2531LQ1515E                                               | 1450 | 1580    |      |

|                   |                                                                                                     | LMX2531LQ1570E                                               | 1530 | 1636    |      |

|                   | Operating Frequency Range (All options have a frequency                                             | LMX2531LQ1650E                                               | 1590 | 1700    |      |

|                   | divider, this applies before the divider. The frequency after the divider is half of what is shown) | LMX2531LQ1700E                                               | 1662 | 1770    | MHz  |

|                   |                                                                                                     | LMX2531LQ1742                                                | 1760 | 1866    |      |

|                   | divider is than or what is shown,                                                                   | LMX2531LQ1778E                                               | 1726 | 1840    |      |

|                   |                                                                                                     | LMX2531LQ1910E                                               | 1834 | 2028    |      |

|                   |                                                                                                     | LMX2531LQ2080E                                               | 1904 | 2274    |      |

|                   |                                                                                                     | LMX2531LQ2265E                                               | 2178 | 2400    |      |

|                   |                                                                                                     | LMX2531LQ2570E                                               | 2336 | 2790    |      |

|                   |                                                                                                     | LMX2531LQ2820E                                               | 2710 | 2925    |      |

|                   |                                                                                                     | LMX2531LQ3010E                                               | 2910 | 3132    |      |

| OTHER             | VCO SPECIFICATIONS                                                                                  |                                                              | ,    |         |      |

|                   |                                                                                                     | LMX2531LQ1742                                                | 65   |         |      |

| $\Delta T_{CL}$   | Maximum Allowable Temperature Drift for Continuous Lock                                             | LMX2531LQ1500E/1570E/1650E/<br>1146E/1226/1312E/1415E/1515E  | 90   |         | °C   |

|                   | See <sup>(4)</sup>                                                                                  | LMX2531LQ1700E/1778E/1910E/<br>2080E/2265E/2570E/2820E/3010E | 125  |         |      |

Copyright © 2005–2014, Texas Instruments Incorporated

<sup>(4)</sup> Maximum Allowable Temperature Drift for Continuous Lock is how far the temperature can drift in either direction from the value it was at the time that the R0 register was last programmed, and still have the part stay in lock. The action of programming the R0 register, even to the same value, activates a frequency calibration routine. This implies that the part will work over the entire frequency range, but if the temperature drifts more than the maximum allowable drift for continuous lock, then it will be necessary to reload the R0 register to ensure that it stays in lock. Regardless of what temperature the part was initially programmed at, the temperature can never drift outside the frequency range of −40°C ≤T<sub>A</sub>≤ 85°C without violating specifications.

$(V_{CC} = 3.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le 85 \text{ °C}; \text{ except as specified.})$

|                   | PARAMETER                             |                  | TEST CONDITIONS | MIN  | TYP  | MAX | UNIT |

|-------------------|---------------------------------------|------------------|-----------------|------|------|-----|------|

|                   |                                       |                  | LMX2531LQ1146E  | 1    | 4.0  | 7   |      |

|                   |                                       |                  | LMX2531LQ1226E  | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ1312E  | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ1415E  | 0    | 3.0  | 6   |      |

|                   |                                       |                  | LMX2531LQ1500E  | 1    | 3.5  | 7.0 |      |

|                   |                                       |                  | LMX2531LQ1515E  | -1   | 2.5  | 5   |      |

|                   |                                       |                  | LMX2531LQ1570E  | 2    | 4.5  | 8   |      |

|                   |                                       |                  | LMX2531LQ1650E  | 2    | 4.5  | 8   |      |

|                   |                                       | Divider Disabled | LMX2531LQ1700E  | 1    | 3.5  | 7   | dBm  |

|                   |                                       |                  | LMX2531LQ1742   | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ1778E  | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ1910E  | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ2080E  | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ2265E  | 1    | 3.5  | 7   |      |

|                   |                                       |                  | LMX2531LQ2570E  | 0    | 3.0  | 6   |      |

|                   |                                       |                  | LMX2531LQ2820E  | -0.5 | 2.5  | 5.5 |      |

| _                 | Output Power to a 50-Ω Load           |                  | LMX2531LQ3010E  | -1.5 | 1.5  | 4.5 |      |

| P <sub>Fout</sub> | (Applies across entire tuning range.) |                  | LMX2531LQ1146E  | -1   | 2.0  | 5   | 5    |

|                   |                                       |                  | LMX2531LQ1226E  | -1   | 2.0  | 5   |      |

|                   |                                       |                  | LMX2531LQ1312E  | -1   | 1.5  | 4   |      |

|                   |                                       |                  | LMX2531LQ1415E  | -2   | 0.5  | 3   |      |

|                   |                                       |                  | LMX2531LQ1500E  | 1    | 3.0  | 6.0 |      |

|                   |                                       |                  | LMX2531LQ1515E  | -2   | 0.5  | 3   |      |

|                   |                                       |                  | LMX2531LQ1570E  | 1    | 3.0  | 6   |      |

|                   |                                       |                  | LMX2531LQ1650E  | 1    | 3.0  | 6   |      |

|                   |                                       | Divider Enabled  | LMX2531LQ1700E  | 1    | 3.0  | 6   | dBm  |

|                   |                                       |                  | LMX2531LQ1742   | 1    | 3.0  | 6   |      |

|                   |                                       |                  | LMX2531LQ1778E  | 1    | 3.0  | 6   |      |

|                   |                                       |                  | LMX2531LQ1910E  | 1    | 3.0  | 6   |      |

|                   |                                       |                  | LMX2531LQ2080E  | 0    | 2.5  | 5   |      |

|                   |                                       |                  | LMX2531LQ2265E  | 0    | 2.5  | 5   |      |

|                   |                                       |                  | LMX2531LQ2570E  | -1   | 1.5  | 4   |      |

|                   |                                       |                  | LMX2531LQ2820E  | -2.5 | 0    | 2.5 |      |

|                   |                                       |                  | LMX2531LQ3010E  | -3   | -0.5 | 2   |      |

Product Folder Links: LMX2531

John Documentation Feedback

(V<sub>CC</sub> = 3.0 V,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85 °C; except as specified.)

|                      | PARAMETER                                                                |                                  | TEST CONDIT         | TIONS                                          | MIN TYP   | MAX  | UNIT  |  |          |                          |     |

|----------------------|--------------------------------------------------------------------------|----------------------------------|---------------------|------------------------------------------------|-----------|------|-------|--|----------|--------------------------|-----|

|                      |                                                                          | LMX2531LQ1146E                   |                     |                                                | 2.5 — 5.5 |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ1226E                   |                     |                                                | 3-6       |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ1312E                   |                     |                                                | 3-6       |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ1415E                   |                     |                                                | 3.5 — 6.5 |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ1500E                   |                     |                                                | 4 — 7     |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ1515E                   |                     |                                                | 4 — 7     |      |       |  |          |                          |     |

|                      | Fine Tuning Sensitivity                                                  | LMX2531LQ1570E                   |                     |                                                | 4 — 7     |      |       |  |          |                          |     |

|                      | (When a range is displayed in the typical column, indicates the lower    | LMX2531LQ1650E                   |                     |                                                | 4 — 7     |      |       |  |          |                          |     |

| K <sub>Vtune</sub>   | sensitivity is typical at the lower end                                  | LMX2531LQ1700E                   |                     |                                                | 6 — 10    |      | MHz/V |  |          |                          |     |

|                      | of the tuning range, and the higher tuning sensitivity is typical at the | LMX2531LQ1742                    |                     |                                                | 4 — 7     |      |       |  |          |                          |     |

|                      | higher end of the tuning range.)                                         | LMX2531LQ1778E                   |                     |                                                | 6 — 10    |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ1910E                   |                     |                                                | 8 — 14    |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ2080E                   |                     |                                                | 9 — 20    |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ2265E                   |                     |                                                | 10 — 16   |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ2570E                   |                     |                                                | 10 — 23   |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ2820E                   |                     |                                                | 12 — 28   |      |       |  |          |                          |     |

|                      |                                                                          | LMX2531LQ3010E                   |                     |                                                | 13 — 29   |      |       |  |          |                          |     |

|                      |                                                                          |                                  | Divider             | LMX2531LQ1146E<br>/1226E/1312E<br>/1415E/1515E | -35       | -25  |       |  |          |                          |     |

|                      |                                                                          |                                  |                     |                                                |           |      |       |  | Disabled | LMX2531LQ2820E<br>/3010E | -40 |

|                      |                                                                          | Second Harmonic 50 $\Omega$ Load |                     | All Other Options                              | -30       | -25  |       |  |          |                          |     |

|                      |                                                                          |                                  | Divider             | LMX2531LQ1146E<br>/1226E/1312E<br>/1415E/1515E | -30       | -20  |       |  |          |                          |     |

|                      | Harmonic Suppression                                                     |                                  | Enabled             | LMX2531LQ2820E<br>/3010E                       | -30       | -15  |       |  |          |                          |     |

| HS <sub>Fout</sub>   | (Applies Across Entire Tuning                                            |                                  |                     | All Other Options                              | -20       | -15  | dBc   |  |          |                          |     |

|                      | Range)                                                                   |                                  |                     | LMX2531LQ1146E<br>/1226E/1312E                 | -35       | -30  |       |  |          |                          |     |

|                      |                                                                          |                                  | Divider<br>Disabled | LMX2531LQ2820E<br>/3010E                       | -50       |      |       |  |          |                          |     |

|                      |                                                                          | Third Harmonic                   |                     | All Other Options                              | -40       | -35  |       |  |          |                          |     |

|                      |                                                                          | 50 Ω Load                        | Divider             | LMX2531LQ1146E<br>/1226E/1312E<br>/1570E/1650E | -20       | -15  |       |  |          |                          |     |

|                      |                                                                          |                                  | Enabled             | LMX2531LQ2820E<br>/3010E                       | -40       | -20  |       |  |          |                          |     |

|                      |                                                                          |                                  | All Other Options   |                                                |           | -20  |       |  |          |                          |     |

| PUSH <sub>Fout</sub> | Frequency Pushing                                                        | Creg = 0.1 $\mu$ F, $V_{DD}$ ±   | 100 mV, Open        | Loop                                           | 300       |      | kHz/V |  |          |                          |     |

| PULLFout             | Frequency Pulling                                                        | VSWR = 2:1, Open L               |                     |                                                |           | ±600 | kHz   |  |          |                          |     |

| Z <sub>Fout</sub>    | Output Impedance                                                         |                                  |                     |                                                | 50        |      | Ω     |  |          |                          |     |

$(V_{CC} = 3.0 \text{ V}, -40^{\circ}\text{C} \le T_A \le 85 ^{\circ}\text{C}; \text{ except as specified.})$

|                      | PARAMETER        |                               | TEST CONDITIONS   | MIN TYP MA  | XX UNIT     |  |  |  |  |

|----------------------|------------------|-------------------------------|-------------------|-------------|-------------|--|--|--|--|

| VCO PHA              | ASE NOISE (5)    |                               |                   |             |             |  |  |  |  |

|                      |                  |                               | 10-kHz Offset     | -96         |             |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 1146 MHz  | 100-kHz Offset    | -121        |             |  |  |  |  |

|                      |                  | DIV2 = 0                      | 1-MHz Offset      | -142        |             |  |  |  |  |

| 1 (6)                | Phase Noise      |                               | 5-MHz Offset      | -156        | -ID - // I- |  |  |  |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1146E) |                               | 10-kHz Offset     | -101        | dBc/Hz      |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 573 MHz   | 100-kHz Offset    | -126        |             |  |  |  |  |

|                      |                  | DIV2 = 1                      | 1-MHz Offset      | -147        |             |  |  |  |  |

|                      |                  |                               | 5-MHz Offset      | -156        |             |  |  |  |  |

|                      |                  |                               | 10-kHz Offset     | -95         |             |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 1226 MHz  | 100-kHz Offset    | -121        |             |  |  |  |  |

|                      |                  | DIV2 = 0                      | 1-MHz Offset      | -142        |             |  |  |  |  |

| 1.70                 | Phase Noise      |                               | 5-MHz Offset      | <b>–155</b> | ID ""       |  |  |  |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1226E) |                               | 10-kHz Offset     | -101        | dBc/Hz      |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 613 MHz   | 100-kHz Offset    | -126        |             |  |  |  |  |

|                      |                  | DIV2 = 1                      | 1-MHz Offset      | -147        |             |  |  |  |  |

|                      |                  |                               | 5-MHz Offset      | -155        |             |  |  |  |  |

|                      |                  |                               | 10-kHz Offset     | -95         |             |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 1314 MHz  | 100-kHz Offset    | -121        |             |  |  |  |  |

|                      |                  | DIV2 = 0                      | 1-MHz Offset      | -140        |             |  |  |  |  |

|                      | Phase Noise      |                               | 5-MHz Offset      | -154        |             |  |  |  |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1312E) |                               | 10-kHz Offset     | -101        | dBc/Hz      |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 657 MHz   | 100-kHz Offset    | -126        |             |  |  |  |  |

|                      |                  | DIV2 = 1                      | 1-MHz Offset      | -146        |             |  |  |  |  |

|                      |                  |                               | 5-MHz Offset      | -154        |             |  |  |  |  |

|                      |                  |                               | 10-kHz Offset     | <b>-95</b>  |             |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 1415 MHz  | 100-kHz Offset    | -121        |             |  |  |  |  |

|                      |                  | DIV2 = 0                      | 1-MHz Offset      | -141        |             |  |  |  |  |

|                      | Phase Noise      |                               | 5-MHz Offset      | -154        | 15 (1)      |  |  |  |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1415E) |                               | 10-kHz Offset     | -100        | dBc/Hz      |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 707.5 MHz | 100-kHz Offset    | -126        |             |  |  |  |  |

|                      |                  | DIV2 = 1                      | 1-MHz Offset      | -146        |             |  |  |  |  |

|                      |                  |                               | 5-MHz Offset      | -154        |             |  |  |  |  |

|                      |                  |                               | 10-kHz Offset     | -97         |             |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 1500 MHz  | 100-KHz Offset    | -120        |             |  |  |  |  |

|                      |                  | DIV2 = 1                      | 1-MHz Offset      | -142        |             |  |  |  |  |

|                      | Phase Noise      |                               | 5-MHz Offset      | -155        | ,           |  |  |  |  |

| L(f) <sub>Fout</sub> | (LMX2531LQ1500E) |                               | 10-kHz Offset     | -103        | dBc/Hz      |  |  |  |  |

|                      |                  | f <sub>Fout</sub> = 750 MHz   | 100-kHz Offset    | -126        | dBc/Hz      |  |  |  |  |

|                      |                  | DIV2 = 1                      | 1-MHz Offset -131 |             |             |  |  |  |  |

|                      |                  |                               | 5-MHz Offset      | -155        |             |  |  |  |  |

<sup>(5)</sup> The VCO phase noise is measured assuming that the loop bandwidth is sufficiently narrow that the VCO noise dominates. The maximum limits apply only at center frequency and over temperature, assuming that the part is reloaded at each test frequency. Over frequency, the phase noise can vary 1 to 2 dB, with the worst case performance typically occurring at the highest frequency. Over temperature, the phase noise typically varies 1 to 2 dB, assuming the part is reloaded.

(V<sub>CC</sub> = 3.0 V,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85 °C; except as specified.)

|                      | PARAMETER                       |                                            | TEST CONDITIONS | MIN TYP MAX     | UNIT    |

|----------------------|---------------------------------|--------------------------------------------|-----------------|-----------------|---------|

|                      |                                 |                                            | 10-kHz Offset   | <b>–</b> 96     |         |

|                      |                                 | f <sub>Fout</sub> = 1515 MHz               | 100-kHz Offset  | -122            |         |

|                      |                                 | DIV2 = 0                                   | 1-MHz Offset    | -142            |         |

| L(f) <sub>Fout</sub> | Phase Noise                     |                                            | 5-MHz Offset    | -153            | dBc/Hz  |

| -(·/Fout             | (LMX2531LQ1515E)                |                                            | 10-kHz Offset   | <b>–99</b>      | abo/112 |

|                      |                                 | f <sub>Fout</sub> = 757.5 MHz              | 100-kHz Offset  | <b>–125</b>     |         |

|                      |                                 | DIV2 = 1                                   | 1-MHz Offset    | -145            |         |

|                      |                                 |                                            | 5-MHz Offset    | -154            |         |

|                      |                                 |                                            | 10-kHz Offset   | <del>-9</del> 3 |         |

|                      |                                 | f <sub>Fout</sub> = 1583 MHz               | 100-kHz Offset  | -118            |         |

|                      |                                 | DIV2 = 0                                   | 1-MHz Offset    | -140            |         |

| _(f) <sub>Fout</sub> | Phase Noise                     |                                            | 5-MHz Offset    | -154            | dBc/Hz  |

| ·\'/Fout             | (LMX2531LQ1570E)                |                                            | 10-kHz Offset   | -99             | ubc/112 |

|                      |                                 | f <sub>Fout</sub> = 791.5 MHz              | 100-kHz Offset  | -122            |         |

|                      |                                 | DIV2 = 1                                   | 1-MHz Offset    | -144            |         |

|                      |                                 |                                            | 5-MHz Offset    | -155            |         |

|                      |                                 |                                            | 10-kHz Offset   | -93             |         |

|                      |                                 | f <sub>Fout</sub> = 1645 MHz               | 100-kHz Offset  | -118            |         |

|                      |                                 | DIV2 = 0                                   | 1-MHz Offset    | -140            |         |

| (0)                  | Phase Noise                     |                                            | 5-MHz Offset    | -154            | 15 //   |

| (f) <sub>Fout</sub>  | (LMX2531LQ1650E)                |                                            | 10-kHz Offset   | <b>–99</b>      | dBc/Hz  |

|                      |                                 | f <sub>Fout</sub> = 822.5 MHz              | 100-kHz Offset  | -122            |         |

|                      |                                 | $f_{Fout} = 822.5 \text{ MHz}$<br>DIV2 = 1 | 1-MHz Offset    | -144            |         |

|                      |                                 |                                            | 5-MHz Offset    | -155            |         |

|                      |                                 |                                            | 10-kHz Offset   | -92             |         |

|                      |                                 | f <sub>Fout</sub> = 1716 MHz               | 100-kHz Offset  | -117            |         |

|                      |                                 | DIV2 = 0                                   | 1-MHz Offset    | -139            | •       |

|                      | Phase Noise                     |                                            | 5-MHz Offset    | -153            |         |

| .(f) <sub>Fout</sub> | (LMX2531LQ1700E)                |                                            | 10-kHz Offset   | -98             | dBc/Hz  |

|                      |                                 | f <sub>Fout</sub> = 858 MHz                | 100-kHz Offset  | -122            | •       |

|                      |                                 | DIV2 = 1                                   | 1-MHz Offset    | -144            |         |

|                      |                                 |                                            | 5-MHz Offset    | -154            |         |

|                      |                                 |                                            | 10-kHz Offset   | -92             |         |

|                      |                                 | f <sub>Fout</sub> = 1813 MHz               | 100-kHz Offset  | -117            |         |

|                      |                                 | DIV2 = 0                                   | 1-MHz Offset    | -140            | •       |

|                      | Phase Noise                     |                                            | 5-MHz Offset    | -152            |         |

| (f) <sub>Fout</sub>  | (LMX2531LQ1742)                 |                                            | 10-kHz Offset   | -99             | dBc/Hz  |

|                      |                                 | f <sub>Fout</sub> = 906.5 MHz              | 100-kHz Offset  | -122            | -       |

|                      |                                 | DIV2 = 1                                   | 1-MHz Offset    | -143            | -       |

|                      |                                 |                                            | 5-MHz Offset    | -152            |         |

|                      |                                 |                                            | 10-kHz Offset   | -92             |         |

|                      |                                 | f 1700 MU-                                 | 100-kHz Offset  | -117            | -       |

|                      |                                 | $f_{Fout} = 1783 \text{ MHz}$<br>DIV2 = 0  | 1-MHz Offset    | -139            |         |

|                      | Dhace Naise                     |                                            | 5-MHz Offset    | -152            | -       |

| .(f) <sub>Fout</sub> | Phase Noise<br>(LMX2531LQ1778E) |                                            | 10-kHz Offset   | -97             | dBc/Hz  |

|                      | ,                               | 4 004 - 1111                               | 100-kHz Offset  | -122            |         |

|                      |                                 | f <sub>Fout</sub> = 891.5 MHz<br>DIV2 = 1  | 1-MHz Offset    | -122<br>-144    |         |

|                      |                                 |                                            | 1 WII IZ Oliset | -144            |         |

$(V_{CC} = 3.0 \text{ V}, -40^{\circ}\text{C} \le T_{A} \le 85 \text{ °C}; \text{ except as specified.})$

|                      | PARAMETER        |                                | TEST CONDITIONS | MIN TYP I   | MAX UNIT    |

|----------------------|------------------|--------------------------------|-----------------|-------------|-------------|

|                      |                  |                                | 10-kHz Offset   | -89         |             |

|                      |                  | f <sub>Fout</sub> = 1931 MHz   | 100-kHz Offset  | -115        |             |

|                      |                  | DIV2 = 0                       | 1-MHz Offset    | -138        |             |

| (6)                  | Phase Noise      |                                | 5-MHz Offset    | -151        | -ID - // I- |

| _(f) <sub>Fout</sub> | (LMX2531LQ1910E) |                                | 10-kHz Offset   | <b>–</b> 95 | dBc/Hz      |

|                      |                  | f <sub>Fout</sub> = 965.5 MHz  | 100-kHz Offset  | -121        |             |

|                      |                  | DIV2 = 1                       | 1-MHz Offset    | -143        |             |

|                      |                  |                                | 5-MHz Offset    | -155        |             |

|                      |                  |                                | 10-kHz Offset   | -87         |             |

|                      |                  | f <sub>Fout</sub> = 2089 MHz   | 100-kHz Offset  | -113        |             |

|                      |                  | DIV2 = 0                       | 1-MHz Offset    | -136        |             |

| (f)                  | Phase Noise      |                                | 5-MHz Offset    | -150        | dDa/U-      |

| (f) <sub>Fout</sub>  | (LMX2531LQ2080E) |                                | 10-kHz Offset   | -93         | dBc/Hz      |

|                      |                  | f <sub>Fout</sub> = 1044.5 MHz | 100-kHz Offset  | -119        |             |

|                      |                  | DIV2 = 1                       | 1-MHz Offset    | -142        |             |

|                      |                  |                                | 5-MHz Offset    | -154        |             |

|                      |                  |                                | 10-kHz Offset   | -88         |             |

|                      |                  | f <sub>Fout</sub> = 2264 MHz   | 100-kHz Offset  | -113        |             |

|                      |                  | DIV2 = 0                       | 1-MHz Offset    | -136        |             |

| (£)                  | Phase Noise      |                                | 5-MHz Offset    | -150        | dDa/U       |

| (f) <sub>Fout</sub>  | (LMX2531LQ2265E) |                                | 10-kHz Offset   | -94         | dBc/Hz      |

|                      |                  | f <sub>Fout</sub> = 1132 MHz   | 100-kHz Offset  | -118        |             |

|                      |                  | DIV2 = 1                       | 1-MHz Offset    | -141        |             |

|                      |                  |                                | 5-MHz Offset    | -154        |             |

|                      |                  |                                | 10-kHz Offset   | -86         |             |

|                      |                  | f <sub>Fout</sub> = 2563 MHz   | 100-kHz Offset  | -112        |             |

|                      |                  | DIV2 = 0                       | 1-MHz Offset    | -135        |             |

| (£)                  | Phase Noise      |                                | 5-MHz Offset    | -149        | dDa/U-      |

| (f) <sub>Fout</sub>  | (LMX2531LQ2570E) |                                | 10-kHz Offset   | -91         | dBc/Hz      |

|                      |                  | f <sub>Fout</sub> = 1281.5 MHz | 100-kHz Offset  | -117        |             |

|                      |                  | DIV2 = 1                       | 1-MHz Offset    | -139        |             |

|                      |                  |                                | 5-MHz Offset    | -152        |             |

|                      |                  |                                | 10-kHz Offset   | -84         |             |

|                      |                  | f <sub>Fout</sub> = 2818 MHz   | 100-kHz Offset  | -111        |             |

|                      |                  | DIV2 = 0                       | 1-MHz Offset    | -133        |             |

| (f)                  | Phase Noise      |                                | 5-MHz Offset    | -148        | dBc/Hz      |

| (f) <sub>Fout</sub>  | (LMX2531LQ2820E) |                                | 10-kHz Offset   | -90         | UDC/112     |

|                      |                  | f <sub>Fout</sub> = 1409 MHz   | 100-kHz Offset  | -117        |             |

|                      |                  | DIV2 = 1                       | 1-MHz Offset    | -138        |             |

|                      |                  |                                | 5-MHz Offset    | -150        |             |

|                      |                  |                                | 10-kHz Offset   | -83         |             |

|                      |                  | f <sub>Fout</sub> = 3021 MHz   | 100-kHz Offset  | -110        |             |

|                      |                  | DIV2 = 0                       | 1-MHz Offset    | -132        |             |

| ′ <b>f</b> \         | Phase Noise      |                                | 5-MHz Offset    | -147        | dDa/I I-    |

| (f) <sub>Fout</sub>  | (LMX2531LQ3010E) |                                | 10-kHz Offset   | -88         | dBc/Hz      |

|                      |                  | f <sub>Fout</sub> = 1510.5 MHz | 100-kHz Offset  | -116        |             |

|                      |                  | DIV2 = 1                       | 1-MHz Offset    | -137        |             |

|                      |                  |                                | 5-MHz Offset    | -148        |             |

( $V_{CC} = 3.0 \text{ V}$ ,  $-40^{\circ}\text{C} \le T_{A} \le 85 ^{\circ}\text{C}$ ; except as specified.)

|                 | PARAMETER                         | TEST CONDITIONS        | MIN  | TYP  | MAX  | UNIT |

|-----------------|-----------------------------------|------------------------|------|------|------|------|

| DIGITAL         | L INTERFACE (DATA, CLK, LE, CE, I | Ftest/LD, FLout)       |      |      |      | •    |

| $V_{\text{IH}}$ | High-Level Input Voltage          |                        | 1.6  |      | 2.75 | V    |

| $V_{IL}$        | Low-Level Input Voltage           |                        |      |      | 0.4  | V    |

| I <sub>IH</sub> | High-Level Input Current          | V <sub>IH</sub> = 1.75 | -3.0 |      | 3.0  | μΑ   |

| I <sub>IL</sub> | Low-Level Input Current           | V <sub>IL</sub> = 0 V  | -3.0 |      | 3.0  | μΑ   |

| $V_{OH}$        | High-Level Output Voltage         | $I_{OH} = 500 \mu A$   | 2.0  | 2.65 |      | V    |

| V <sub>OL</sub> | Low-Level Output Voltage          | $I_{OL} = -500 \mu A$  |      | 0.0  | 0.4  | V    |

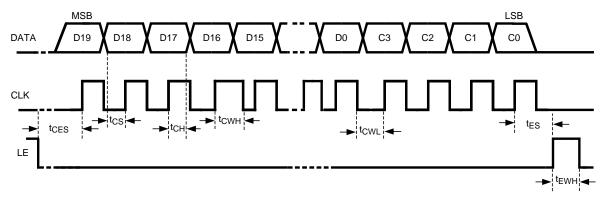

# 7.6 MICROWIRE Timing Requirements

See Figure 2 and Serial Data Timing Requirements.

|                  | <u> </u>                    | MIN | NOM | MAX | UNIT |

|------------------|-----------------------------|-----|-----|-----|------|

| t <sub>CS</sub>  | Data to Clock Set-Up Time   | 25  |     |     | ns   |

| t <sub>CH</sub>  | Data to Clock Hold Time     | 20  |     |     | ns   |

| t <sub>CWH</sub> | Clock Pulse Width High      | 25  |     |     | ns   |

| t <sub>CWL</sub> | Clock Pulse Width Low       | 25  |     |     | ns   |

| t <sub>ES</sub>  | Clock to Enable Set-Up Time | 25  |     |     | ns   |

| t <sub>CES</sub> | Enable to Clock Set-Up Time | 25  |     |     | ns   |

| t <sub>EWH</sub> | Enable Pulse Width High     | 25  |     |     | ns   |

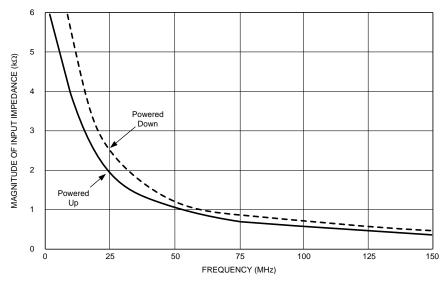

# 7.7 Typical Performance Characteristics

See Table 1.

Figure 1. OSCin Input Impedance

Submit Documentation Feedback

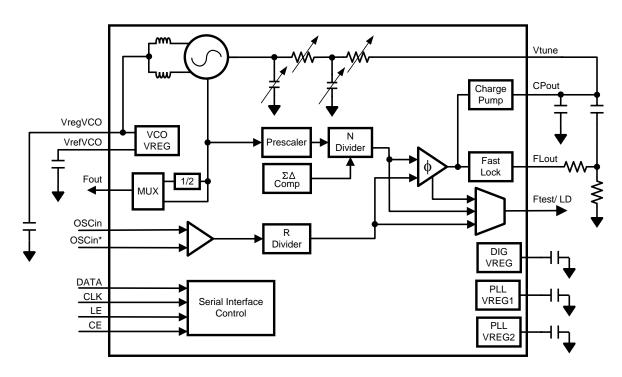

## 8 Detailed Description

#### 8.1 Overview

The LMX2531 is a low-power, high-performance frequency synthesizer system which includes the PLL, VCO, and partially integrated loop filter. *Feature Description* gives a discussion of the various blocks of this device.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

#### 8.3.1 Reference Oscillator Input

Because the VCO frequency calibration algorithm is based on clocks from the OSCin pin, there are certain bits that need to be set depending on the OSCin frequency. XTLSEL (R6[22:20]) and XTLDIV (R7[9:8]) are both need to be set based on the OSCin frequency, f<sub>OSCin</sub>. For some options and for low OSCin frequencies, the XTLMAN (R7[21:10]) and XTLMAN2 (R8[4]) words need to be set to the correct value.

Table 1. OSCin Input Impedance (See Figure 1)

| FREQUENCY |      | POWERED UP (kΩ) | )         | P    | OWERED DOWN (k | Ω)        |

|-----------|------|-----------------|-----------|------|----------------|-----------|

| (MHz)     | REAL | IMAGINARY       | MAGNITUDE | REAL | IMAGINARY      | MAGNITUDE |

| 1         | 4.98 | -2.70           | 5.66      | 6.77 | -8.14          | 10.59     |

| 5         | 3.44 | -3.04           | 4.63      | 5.73 | -6.72          | 9.03      |

| 10        | 1.42 | -2.67           | 3.02      | 1.72 | -5.24          | 5.51      |

| 20        | 0.52 | -1.63           | 1.71      | 0.53 | -2.94          | 2.98      |

| 30        | 0.29 | -1.22           | 1.25      | 0.26 | -2.12          | 2.14      |

| 40        | 0.18 | -0.92           | 0.94      | 0.17 | -1.58          | 1.59      |

| 50        | 0.13 | -0.74           | 0.75      | 0.14 | -1.24          | 1.25      |

| 60        | 0.10 | -0.63           | 0.64      | 0.10 | -1.06          | 1.06      |

| 70        | 0.09 | -0.56           | 0.56      | 0.09 | -0.95          | 0.95      |

| 80        | 0.07 | -0.50           | 0.50      | 0.08 | -0.86          | 0.87      |

| 90        | 0.07 | -0.46           | 0.46      | 0.07 | -0.80          | 0.80      |

## **Feature Description (continued)**

Table 1. OSCin Input Impedance (See Figure 1) (continued)

| FREQUENCY |      | POWERED UP (kΩ) |           | Р    | OWERED DOWN (k | Ω)        |

|-----------|------|-----------------|-----------|------|----------------|-----------|

| (MHz)     | REAL | IMAGINARY       | MAGNITUDE | REAL | IMAGINARY      | MAGNITUDE |

| 100       | 0.06 | -0.41           | 0.42      | 0.07 | -0.72          | 0.72      |