# LMX5453 Micro-Module Integrated Bluetooth®2.0 Baseband Controller and Radio

Check for Samples: LMX5453

## **FEATURES**

The LMX5453 is a drop in replacement for the LMX5452. The LMX5453 has new features added:

- **eSCO**

- eSCO over USB HCI transport

- **Enhanced scatternet**

- Interlaced scan

- Flushing

- **Audio PCM slave mode support**

- **Generic PCM configuration**

- Compliant with the Bluetooth 2.0 Core **Specification**

- Better than -80 dBm input sensitivity

- Class 2 operation

- Low power consumption:

- Accepts external clock or crystal input:

- Clocking option 12/13 MHz with PLL bypass mode for power reduction

- 10-20 MHz external clock or crystal network

- Secondary 32.768 kHz oscillator for lowpower modes

- Advanced power management features

- **High integration:**

- Implemented in 0.18 µm CMOS technology

- RF includes on-chip antenna filter and switch

- On-chip firmware with complete HCI

- Embedded ROM (200K) and Patch RAM (16.6K)

- **Up to 7 Asynchronous Connection Less (ACL)** links

- Support for two simultaneous voice or **Extended Synchronous Connection Oriented** (eSCO) and Synchronous Connection Oriented (SCO) and links.

- **Enhanced scatternet**

- Interlaced scan

- Flushing

- Audio PCM slave mode support

- **Generic PCM configuration**

- Fractional-N Sigma/Delta modulator

- Operating voltage range 2.5-3.6V

- I/O voltage range 1.6-3.6V

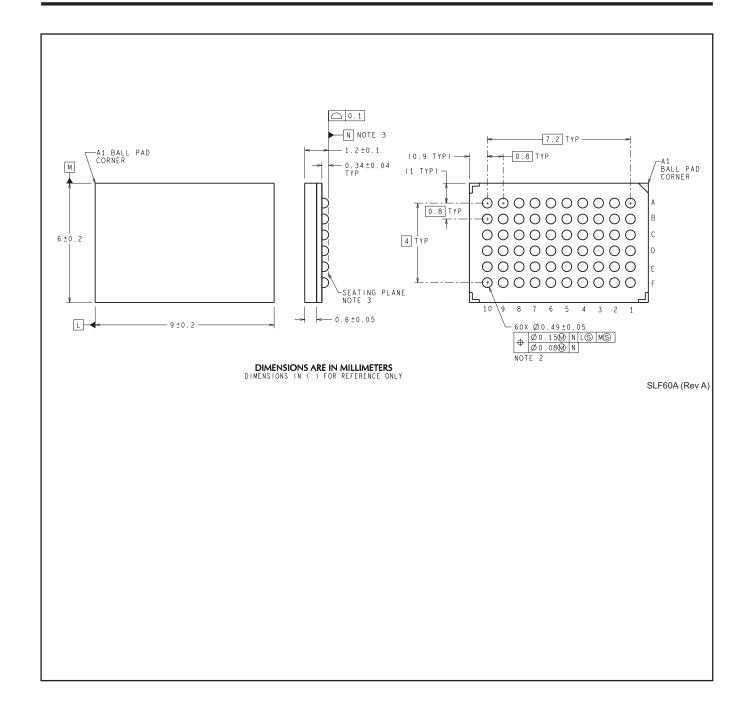

- 60-pad micro-module BGA package (6.1 mm x  $9.1 \text{ mm} \times 1.2 \text{ mm}$

#### **APPLICATIONS**

- **Mobile Handsets**

- **USB Dongles**

- **Stereo Headsets**

- **Personal Digital Assistants**

- **Personal Computers**

- **Automotive Telematics**

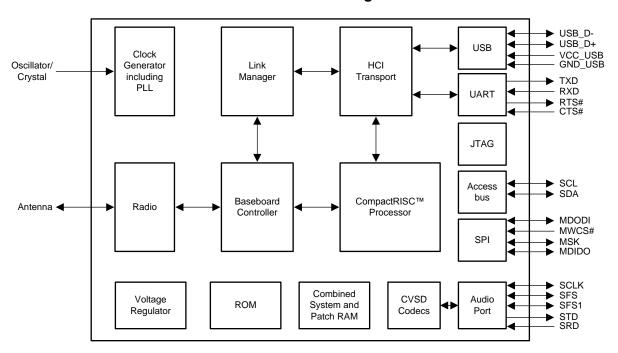

## DESCRIPTION

The LMX5453 is a highly integrated Bluetooth 2.0 baseband compliant solution. The integrated controller and 2.4 GHz radio combine to form a complete, small form-factor (6.1 mm × 9.1 mm × 1.2 mm) Bluetooth node.

The on-chip memory, ROM, and Patch RAM provide lowest cost and minimize design risk with the flexibility of firmware upgrades.

The firmware supplied in the on-chip ROM supports a complete Bluetooth Link Manager and HCI with communication through a UART or USB interface. This firmware features point-to-point and point-tomultipoint link management, supporting data rates up to 723 kbps.

The radio employs an integrated antenna filter and switch to minimize the number of external components.

The radio has a heterodyne receiver architecture with a low intermediate frequency (IF), which enables the IF filters to be integrated on-chip. The transmitter uses direct IQ-modulation with Gaussian-filtered bitstream data, a voltage-controlled oscillator (VCO) buffer, and a power amplifier.

The LMX5453 module is lead free and RoHS (Restriction of Hazardous Substances) compliant. For more information on those quality standards, please green compliance website http://www.national.com/quality/green/

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Bluetooth is a registered trademark of Texas Instruments.

# **Functional Block Diagram**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **INTERFACES**

- Full-duplex UART supporting transfer rates up to 921.6 kbps including baud rate detection for HCI

- Full speed (12 Mbps) USB 2.0 for HCI

- ACCESS.bus and SPI/Microwire for interfacing with external non-volatile memory

- Advanced Audio Interface (AAI) for interfacing with external 8-kHz PCM codec

- Up to 3 GPIO port pins (OP4/PG4, PG6, PG7) controllable by HCl commands

- JTAG based serial on-chip debug interface

- Single Rx/Tx-pad radio interface

Submit Documentation Feedback

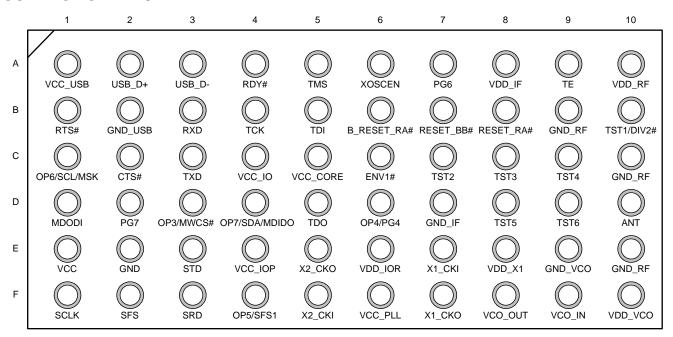

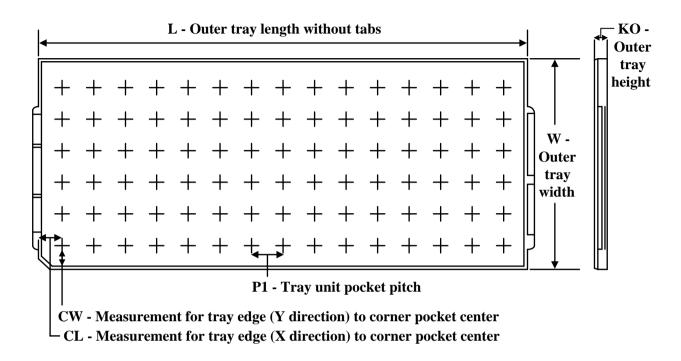

# **CONNECTION DIAGRAM**

Figure 1. X-ray - Top View

# **SIGNAL DESCRIPTIONS**

**Table 1. Signal Descriptions**

| Pad Name             | Pad Location | Туре                            | Default Layout            | Description                                                                                                                                 |

|----------------------|--------------|---------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| X1_CKO               | F7           | 0                               |                           | Crystal 10-20 MHz                                                                                                                           |

| X1_CKI               | E7           | I                               |                           | Crystal or External Clock 10-20 MHz                                                                                                         |

| X2_CKI               | F5           | I                               | GND (if not used)         | 32.768 kHz Crystal Oscillator                                                                                                               |

| X2_CKO               | E5           | 0                               | NC (if not used)          | 32.768 kHz Crystal Oscillator                                                                                                               |

| RESET_RA#            | B8           | I                               |                           | Radio Reset Input (active low)                                                                                                              |

| B_RESET_RA#          | B6           | 0                               |                           | Buffered Radio Reset Output (active low)                                                                                                    |

| RESET_BB#            | B7           | I                               |                           | Baseband Controller Reset (active low)                                                                                                      |

| ENV1                 | C6           | I                               | NC                        | ENV1: Environment Select used for manufacturing test only                                                                                   |

| TE                   | A9           | I                               | GND                       | Test Enable - Used for manufacturing test only                                                                                              |

| TST1/DIV2#           | B10          | I                               | NC                        | TST1: Test Mode. Leave not connected to permit use with VTune automatic tuning algorithm.  DIV2#: No longer supported                       |

| TST2                 | C7           | I                               | GND                       | Test Mode, Connect to GND                                                                                                                   |

| TST3                 | C8           | I                               | GND                       | Test Mode, Connect to GND                                                                                                                   |

| TST4                 | C9           | I                               | GND                       | Test Mode, Connect to GND                                                                                                                   |

| TST5                 | D8           | ļ                               | GND                       | Test Mode, Connect to GND                                                                                                                   |

| TST6                 | D9           | I                               | VCO_OUT                   | Test Input, Connect to VCO_OUT through a zero-<br>ohm resistor to permit use with VTune automatic<br>tuning algorithm                       |

| USB_D-               | A3           | I                               |                           | USB Data (negative)                                                                                                                         |

| USB_D+               | A2           | I                               |                           | USB Data (positive)                                                                                                                         |

| MDODI <sup>(1)</sup> | D1           | I/O                             |                           | SPI Master Data Out/Slave Data In                                                                                                           |

| OP6/SCL/MSK          | C1           | OP6: I<br>SCL/MSK:<br>I/O       | See Table 20              | OP6: Pin checked during the start-up sequence for configuration option SCL: ACCESS.Bus Clock MSK: SPI Shift                                 |

| OP7/SDA/MDIDO        | D4           | OP7: I<br>SDA/MDID<br>O:<br>I/O | See Table 20              | OP7: Pin checked during the start-up sequence for configuration option SDA: ACCESS.Bus Serial Data MDIDO: SPI Master Data In/Slave Data Out |

| OP3/MWCS#            | D3           | ı                               | See Table 20 and Table 21 | OP3: Pin checked during the start-up sequence for configuration option  MWCS#: SPI Slave Select Input (active low)                          |

| OP4/PG4              | D6           | OP4: I<br>PG4: I/O              | See Table 20 and Table 21 | OP4: Pin checked during the start-up sequence for configuration option PG4: GPIO                                                            |

| OP5/SFS1             | F4           | I/O                             | See Table 20 and Table 21 | OP5: Pin checked during the start-up sequence for configuration option SFS1: Audio PCM Interface - Frame Synchronization for second codec   |

| SCLK                 | F1           | I/O                             |                           | Audio PCM Interface Clock                                                                                                                   |

| SFS                  | F2           | I/O                             |                           | Audio PCM Interface Frame Synchronization                                                                                                   |

| SRD                  | F3           | ļ                               |                           | Audio PCM Interface Receive Data Input                                                                                                      |

| STD                  | E3           | 0                               |                           | Audio PCM Interface Transmit Data Output                                                                                                    |

| XOSCEN               | A6           | 0                               |                           | Clock Request. Toggles with X2 (LP0) crystal enable/disable                                                                                 |

| PG6                  | A7           | 0                               | See NVS Table 21          | GPIO - Default setup USB status indication                                                                                                  |

| PG7                  | D2           | 0                               | See NVS Table 21          | GPIO - Default setup TL (Transport Layer) traffic LED indication                                                                            |

Product Folder Links: LMX5453

# (1) Must use 1k ohm pull up

Submit Documentation Feedback

Copyright © 2006–2014, Texas Instruments Incorporated

# **Table 1. Signal Descriptions (continued)**

| Pad Name            | Pad Location | Туре | Default Layout    | Description                                   |

|---------------------|--------------|------|-------------------|-----------------------------------------------|

| CTS#(2)             | C2           | I    | GND (if not used) | Host Serial Port Clear To Send (active low)   |

| RXD                 | B3           | I    |                   | Host Serial Port Receive Data                 |

| RTS# <sup>(3)</sup> | B1           | 0    | NC (if not used)  | Host Serial Port Request To Send (active low) |

| TXD                 | C3           | 0    |                   | Host Serial Port Transmit Data                |

| RDY#                | A4           | 1    | NC                | JTAG Ready Output (active low)                |

| TCK                 | B4           | I    | NC                | JTAG Test Clock Input                         |

| TDI                 | B5           | I    | NC                | JTAG Test Data Input                          |

| TDO                 | D5           | 0    | NC                | JTAG Test Data Output                         |

| TMS                 | A5           | 1    | NC                | JTAG Test Mode Select Input                   |

| VCO_OUT             | F8           | 0    |                   | Charge Pump Output, connect to loop filter    |

| VCO_IN              | F9           | I    |                   | VCO Tuning Input, feedback from loop filter   |

| ANT                 | D10          | 0    |                   | RF Antenna, 50-ohm nominal impedance          |

| VCC_PLL             | F6           | 0    |                   | 1.8V Core Logic Power Supply Output           |

| VCC_CORE            | C5           | 0    |                   | 1.8V Voltage Regulator Output                 |

| VDD_X1              | E8           | I    |                   | Power Supply Crystal Oscillator               |

| VDD_VCO             | F10          | I    |                   | Power Supply VCO                              |

| VDD_RF              | A10          | I    |                   | Power Supply RF                               |

| VDD_IOR             | E6           | ı    |                   | Power Supply I/O Radio/BB                     |

| VDD_IF              | A8           | ı    |                   | Power Supply IF                               |

| VCC_USB             | A1           | 1    |                   | Power Supply USB Transceiver                  |

| VCC_IOP             | E4           | I    |                   | Power Supply Audio Interface                  |

| VCC_IO              | C4           | I    |                   | Power Supply I/O                              |

| VCC                 | E1           | I    |                   | Voltage Regulator Input                       |

| GND_VCO             | E9           |      |                   | Ground                                        |

| GND_USB             | B2           |      |                   | Ground                                        |

| GND_RF              | B9, C10, E10 |      |                   | Ground                                        |

| GND_IF              | D7           |      |                   | Ground                                        |

| GND                 | E2           |      |                   | Ground                                        |

<sup>(2)</sup> Connect to GND if CTS is not used

<sup>(3)</sup> Treat as No Connect if RTS is not used. Pad required for mechanical stability

# **Electrical Specifications**

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. This device is ESD sensitive. Handling and assembly of this device should be performed at ESD-free workstations. All pads are rated 2 kV. This device operates between -40 and +85°C.

**Absolute Maximum Ratings**

|                    | Parameter                                      | Min  | Max       | Units |

|--------------------|------------------------------------------------|------|-----------|-------|

| VCC                | Power Supply Voltage                           | -0.2 | 4.0       | V     |

| VI                 | Voltage on any pad with GND = 0V               | -0.2 | VCC + 0.2 | V     |

| VDD_RF             |                                                | 0.2  | 3.3       | V     |

| VDD_IF             | Owner Welferen De l'e                          |      |           |       |

| VDD_X1             | Supply Voltage Radio                           |      |           |       |

| VDD_VCO            |                                                |      |           |       |

| P <sub>IN</sub> RF | RF Input Power                                 |      | 0         | dBm   |

| V <sub>ANT</sub>   | Applied Voltage to ANT pad                     |      | 1.95      | V     |

| T <sub>S</sub>     | Storage Temperature Range                      | -65  | +150      | °C    |

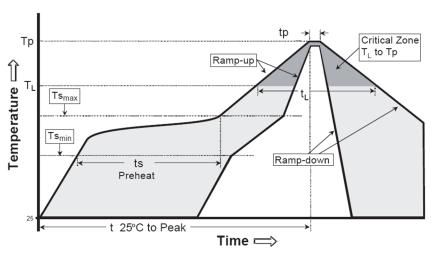

| $T_L$              | Lead Temperature <sup>(1)</sup> (solder 4 sec) |      | 225       | °C    |

| T <sub>LNOPB</sub> | Lead Temperature NOPB (1)(2) (solder 40 sec)   |      | 260       | °C    |

| ESD <sub>HBM</sub> | ESD - Human Body Model                         |      | 2000      | V     |

| ESD <sub>MM</sub>  | ESD - Machine Model                            |      | 200       | V     |

| ESD <sub>CDM</sub> | ESD - Charged Device Model                     |      | 1000      | V     |

<sup>(1)</sup> Reference IPC/JEDEC J-STD-020C spec.

# **Recommended Operating Conditions**

|                 | Parameter                                                            | Min  | Тур  | Max    | Units |

|-----------------|----------------------------------------------------------------------|------|------|--------|-------|

| VCC             | Module Power Supply Voltage                                          | 2.5  | 2.75 | 3.6    | V     |

| T <sub>R</sub>  | Module Power Supply Rise Time                                        |      |      | 10     | μS    |

| T <sub>A</sub>  | Ambient Opoerating Temperature Range Fully Functional Bluetooth Node | -40  | +25  | +85    | °C    |

| VCC_IO          | Supply Voltage Digital I/O                                           | 1.6  | 3.3  | 3.6    | V     |

| VCC_USB         | Supply Voltage USB                                                   | 2.97 | 3.3  | 3.63   | V     |

| VCC_PLL         | Internally connected to VCC_Core                                     |      |      |        |       |

| VDD_RF          |                                                                      |      |      |        |       |

| VDD_IF          | Cumply Vallage Dedia                                                 | 0.5  | 0.75 | 2.0    | \ /   |

| VDD_X1          | Supply Voltage Radio                                                 | 2.5  | 2.75 | 3.0    | V     |

| VDD_VCO         |                                                                      |      |      |        |       |

| VDD_IOR         | Supply Voltage Radio I/O                                             | 1.6  | 2.75 | VDD_RF | V     |

| VCC_IOP         | Supply Voltage PCM Interface                                         | 1.6  | 3.3  | 3.6    | V     |

| VCC_CORE        | Supply Voltage Output                                                |      | 1.8  |        | V     |

| VCC_CORE        | Supply Voltage Output Max Load                                       |      | 5    |        | mA    |

| MAX             |                                                                      |      |      |        |       |

| $VCC\_CORE_{S}$ | When used as supply input (VCC grounded)                             | 1.6  | 1.8  | 2.0    | V     |

| HORT            |                                                                      |      |      |        |       |

<sup>(2)</sup> NOPB = No Pb (No Lead)

www.ti.com

# Power Supply Requirements (1)(2)

|                      | Parameter                                                   | Min | Тур | Max | Units |

|----------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>RXDM5</sub>   | During Receive DM5                                          |     | 26  |     | mA    |

| I <sub>TXDM5</sub>   | During Transmit DM5                                         |     | 27  |     | mA    |

| I <sub>RXDH5</sub>   | During Receive DH5                                          |     | 26  |     | mA    |

| I <sub>TXDH5</sub>   | During Transmit DH5                                         |     | 27  |     | mA    |

| I <sub>RXHV1</sub>   | During Receive HV1                                          |     | 12  |     | mA    |

| I <sub>TXHV1</sub>   | During Transmit HV1                                         |     | 12  |     | mA    |

| I <sub>CC-RX</sub>   | Receive Power Supply Current (Receive in Continuous Mode)   |     |     | 65  | mA    |

| І <sub>сс-тх</sub>   | Transmit Power Supply Current (Transmit in Continuous Mode) |     |     | 65  | mA    |

| I <sub>CC-PWDN</sub> | Power-down Current (Standby, XO off)                        |     | 34  |     | μΑ    |

| I <sub>ACTIVE</sub>  | Active Mode - Page/Inquiry Scan Enabled                     |     | 6   |     | mA    |

| I <sub>SNIFF</sub>   | Sniff Mode - Sniff Interval 1.28 sec.                       |     | 5   |     | mA    |

<sup>(1)</sup> Power supply requirements are based on Class 2 output power. (2) VCC = 2.75V,  $T_A = +25^{\circ}C$

# **DC Characteristics**

|                                | Parameter                                            | Condition                                  | Min                    | Max                                | Units |

|--------------------------------|------------------------------------------------------|--------------------------------------------|------------------------|------------------------------------|-------|

| V <sub>IH</sub>                | Logical 1 Input Voltage High (except oscillator I/O) | 1.6V ≤ VCC_IO ≤ 3.0<br>3.0V ≤ VCC_IO ≤ 3.6 | 0.7 x<br>VCC_IO<br>2.0 | VCC_IO +<br>0.2<br>VCC_IO +<br>0.2 | V     |

| V <sub>IL</sub>                | Logical 1 Input Voltage Low (except oscillator I/O)  | 1.6V ≤ VCC_IO ≤ 3.0<br>3.0V ≤ VCC_IO ≤ 3.6 | -0.2<br>-0.2           | 0.25 x<br>VCC_IO<br>0.8            | V     |

| I <sub>OH</sub> <sup>(1)</sup> | Logical 1 Output Current                             | V <sub>OH</sub> = 2.4V, VCC_IO = 3.0V      | -10                    |                                    | mA    |

| I <sub>OL</sub> <sup>(1)</sup> | Logical 0 Output Current                             | V <sub>OL</sub> = 0.4V, VCC_IO = 3.0V      | 10                     |                                    | mA    |

<sup>(1)</sup> Maximum current is 50mA per VCC\_IO/GND pair.

# **USB Transceiver**

|                  | Parameter                        | Condition                      | Min  | Тур | Max  | Units |

|------------------|----------------------------------|--------------------------------|------|-----|------|-------|

| VCC_USB          | USB Power Supply Voltage         |                                | 2.97 | 3.3 | 3.63 | V     |

| $V_{DI}$         | Differential Input Sensitivity   | (D+) - (D-)                    | -0.2 |     | +0.2 | V     |

| V <sub>CM</sub>  | Differential Common Mode Range   |                                | 0.8  |     | 2.5  | V     |

| V <sub>SE</sub>  | Siungle Ended Received Threshold |                                | 0.8  |     | 2.0  | V     |

| V <sub>OL</sub>  | Output Low Voltage               | R <sub>L</sub> = 1.5k, to 3.6V |      |     | 0.3  | V     |

| V <sub>OH</sub>  | Output High Voltage              |                                | 2.8  |     |      | V     |

| l <sub>OZ</sub>  | TRI-STATE Data Line Leakage      | 0V < V <sub>IN</sub> < 3.3V    | -10  |     | +10  | μA    |

| C <sub>TRN</sub> | Transceiver Capacitance          |                                |      |     | 20   | pF    |

## **RF Characteristics**

|                                     | Parameter                             | Condition                                                                              |                                 | Min | Typ <sup>(1)</sup> | Max | Units |

|-------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|---------------------------------|-----|--------------------|-----|-------|

|                                     |                                       |                                                                                        | 2.402 GHz                       |     | -80                | -76 | dBm   |

| RX <sub>sense</sub>                 | Receive Sensitivity                   | BER < 0.001                                                                            | 2.441 GHz                       |     | -80                | -76 | dBm   |

|                                     |                                       |                                                                                        | 2.480 GHz                       |     | -80                | -76 | dBm   |

| PinRF                               | Maximum Input Level                   |                                                                                        | ·                               | -10 | 0                  |     | dBm   |

| IMP <sup>(2)</sup> , <sup>(3)</sup> | Intermodulation<br>Performance        | F <sub>1</sub> = + 3 MHz,<br>F <sub>2</sub> = + 6 MHz,<br>P <sub>in</sub> RF = -64 dBm |                                 | -38 | -36                |     | dBm   |

| RSSI                                | RSSI Dynamic Range at LNA Input       |                                                                                        |                                 | -72 |                    | -52 | dBm   |

| Z <sub>RFIN</sub> (3)               | Input Impedance of RF Port (RF_inout) | Single input imped                                                                     | dance F <sub>in</sub> = 2.5 GHz |     | 32                 |     | Ω     |

| Return Loss (3)                     | Return Loss                           |                                                                                        |                                 |     |                    | -8  | dB    |

|                                     |                                       | P <sub>in</sub> RF = -10 dBm,<br>30 MHz < F <sub>CWI</sub> < 2<br>BER < 0.001          |                                 | -10 |                    |     | dBm   |

| OOB <sup>(2)</sup> , <sup>(3)</sup> | Out of Band Blocking                  | P <sub>in</sub> RF = -27 dBm,<br>2000 MHz < F <sub>CWI</sub><br>BER < 0.001            | < 2399 MHz,                     | -27 |                    |     | dBm   |

|                                     | Performance                           | P <sub>in</sub> RF = -27 dBm,<br>2498 MHz < F <sub>CWI</sub><br>BER < 0.001            | < 3000 MHz,                     | -27 |                    |     | dBm   |

|                                     |                                       | P <sub>in</sub> RF = -10 dBm,<br>3000 MHz < F <sub>CWI</sub><br>BER < 0.001            |                                 | -10 |                    |     | dBm   |

(1) Typical operating conditions are at 2.75V operating voltage and 25°C ambient temperature.

#### **Transmitter Characteristics**

|                                                                | Parameter                                                 | Condition                                                    | Min | Typ <sup>(1)</sup> | Max | Units |

|----------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|-----|--------------------|-----|-------|

| P <sub>OUT</sub> 2 x f <sub>o</sub> <sup>d<sub>(2)</sub></sup> | PA 2nd Harmonic<br>Suppression                            | Maximum gain setting: $f_0 = 2402$ MHz, $P_{out} = 4804$ MHz |     |                    | -30 | dBm   |

| Z <sub>RFOUT</sub> θ                                           | RF Output Impedance/Input Impedance of RF Port (RF_inout) | P <sub>out</sub> @ 2.5 GHz                                   |     | 47                 |     | Ω     |

(1) Typical operating conditions are at 2.75V operating voltage and 25°C ambient temperature.

# **Synthesizer Characteristics**

|                                       | Parameter                              | Condition               | Min  | Тур | Max  | Units        |

|---------------------------------------|----------------------------------------|-------------------------|------|-----|------|--------------|

| f <sub>VCO</sub>                      | VCO Frequency Range                    |                         | 2402 |     | 2480 | MHz          |

| t <sub>LOCK</sub>                     | Lock Time                              | f <sub>0</sub> ± 20 kHz |      | 120 |      | μs           |

| Δf <sub>0</sub> offset <sup>(1)</sup> | Initial Carrier<br>Frequency Tolerance | During preamble         | -75  | 0   | 75   | kHz          |

|                                       |                                        | DH1 data packet         | -25  | 0   | 25   | kHz          |

|                                       |                                        | DH3 data packet         | -40  | 0   | 40   | kHz          |

| Δf <sub>0</sub> drift <sup>(1)</sup>  | Initial Carrier Frequency Drift        | DH5 data packet         | -40  | 0   | 40   | kHz          |

|                                       |                                        | Drift Rate              | -20  | 0   | 20   | kHz/50<br>µs |

| t <sub>D</sub> -Tx                    | Transmitter Delay Time                 | From Tx data to antenna |      | 4   |      | μs           |

Frequency accuracy is dependent on crystal oscillator chosen. The crystal must have a cumulative accuracy of <20 ppm to meet Bluetooth specifications.

<sup>(2)</sup> The f<sub>0</sub> = -64 dBm Bluetooth modulated signal, f<sub>1</sub> = -39 dbm sine wave, f<sub>2</sub> = -39 dbm Bluetooth modulated signal, f<sub>0</sub> = 2f<sub>1</sub> - f<sub>2</sub>, and |f<sub>2</sub> - f<sub>1</sub>| = n × 1 MHz, where n is 3, 4, or 5. For the typical case, n = 3.

<sup>(3)</sup> Not tested in production.

<sup>(2)</sup> Out-of-Band spurs only exist at 2nd and 3rd harmonics of the CW frequency for each channel.

## **Crystal Requirements**

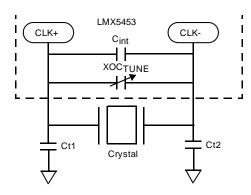

The LMX5453 provides an on-chip driver that may be used with an external crystal and capacitors to form an oscillator. Figure 2 shows the recommended crystal circuit. Table 5 specifies the system clock requirements.

The RF local oscillator and internal digital clocks for the LMX5453 are derived from the reference clock at the CLK+ input. This reference may come from either an external clock signal or the oscillator using the on-chip driver.

When the on-chip driver is used, the board- and design dependent capacitance must be considered in tuning the crystal circuit. Equations that provide a close approximation of the crystal tuning capacitance are used as a starting point, but the optimal values will vary with the capacitive properties of the circuit board. As a result, fine tuning of the crystal circuit must be performed experimentally, by testing different values of load capacitance.

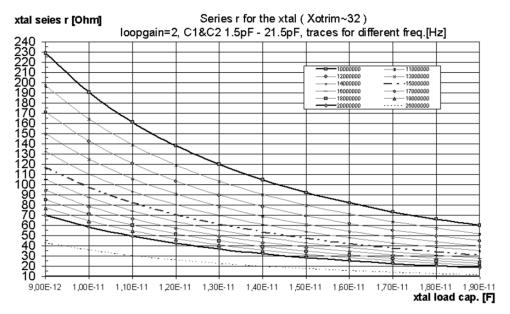

Many different crystals can be used with the LMX5453. A key requirement from the Bluetooth specification is a cumulative accuracy of <20 ppm. Additionally, ESR (Equivalent Series Resistance) must be carefully considered. The LMX5453 can support a maximum ESR of  $230\Omega$ , but it is recommended to stay < $100\Omega$  for best performance over voltage and temperature. See Figure 3 for ESR as part of the crystal circuit for more information. The ESR of the crystal also has an impact on the start-up time of the crystal oscillator circuit. See \*\* Section 15.0 and Table 18 for system start-up timing.

## Crystal

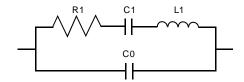

The crystal appears inductive near its resonant frequency. It forms a resonant circuit with its load capacitors. The resonant frequency may be trimmed with the crystal load capacitance.

## **Load Capacitance**

For resonance at the correct frequency, the crystal should be loaded with its specified load capacitance. Load capacitance is a parameter specified by the crystal vendor, typically expressed in pF. The crystal circuit shown in Figure 3 is composed of:

- C1 (motional capacitance)

- R1 (motional resistance)

- L1 (motional inductance)

- C0 (static or shunt capacitance)

The LMX5453 provides some of the load with internal capacitors  $C_{int}$  and  $XOC_{TUNE}$ . The remainder must come from the external capacitors labeled Ct1 and Ct2 shown in Figure 2. For best noise performance, Ct1 and Ct2 should have the same the value.

The value of  $XOC_{TUNE}$  can be programmed in register 2. There are 7 bits of tuning for  $XOC_{TUNE}$ . The default value is 0028h, which results in an additional 2.6 pF internal capacitance. This register can be used in production testing for additional tuning, if necessary. See Table 19 for the range of  $XOC_{TUNE}$  values.

The crystal load capacitance (C<sub>L</sub>) is calculated as:

$$C_{L} = C_{int} + XOC_{TUNE} + Ct1//Ct2$$

(1)

The  $C_L$  above does not include the crystal internal self capacitance  $C_0$  as shown in Figure 3, so the total capacitance is:

$$C_{\text{total}} = C_{L} + C_{0} \tag{2}$$

Based on the crystal specification and equation:

$$C_{L} = C_{int} + XOC_{TUNE} + Ct1//Ct2$$

(3)

$$C_L = 8 pF + 2.6 pF + 6 pF = 16.6 pF$$

(4)

16.6 pF is very close to the TEW crystal requirement of 16 pF load capacitance. With the internal shunt capacitance  $C_{total}$ :

$$C_{total} = 16.6 \text{ pF} + 5 \text{ pF} = 21.6 \text{ pF}$$

(5)

Figure 2. Recommended Crystal Circuit

Figure 3. Crystal Equivalent Circuit

# **Crystal Pullability**

Pullability is another important crystal parameter, which is the change in frequency of a crystal with units of ppm/pF, either from the natural resonant frequency to a load resonant frequency, or from one load resonant frequency to another. The frequency can be pulled in a parallel resonant circuit by changing the value of load capacitance. A decrease in load capacitance causes an increase in frequency, and an increase in load capacitance causes a decrease in frequency.

## **Frequency Tuning**

Frequency tuning is performed by adjusting the crystal load capacitance with external capacitors. It is a Bluetooth requirement that the frequency is always within 20 ppm. The crystal/oscillator must have cumulative accuracy specifications of **15 ppm** to provide margin for frequency drift with aging and temperature.

## **TEW Crystal**

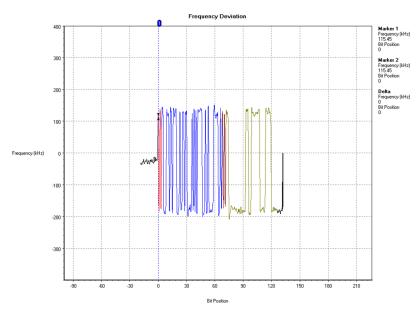

The LMX5453 has been tested with the TEW TAS-4025A crystal (see Table 3). Because the internal capacitance of the crystal circuit is 8 pF and the load capacitance is 16 pF, 12 pF is a good starting point for both Ct1 and Ct2. The 2480 MHz RF frequency offset is then tested. Figure 5 shows the RF frequency offset test results.

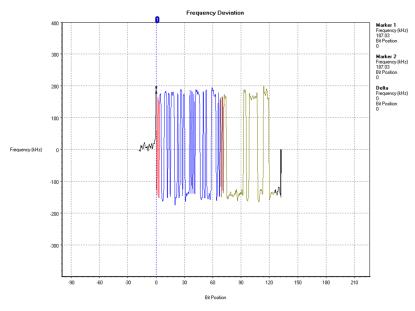

Figure 5 shows the results are -20 kHz off the center frequency, which is -1 ppm. The pullability of the crystal is 2 ppm/pF, so the load capacitance must be decreased by about 1.0 pF. By changing Ct1 or Ct2 to 10 pF, the total load capacitance is decreased by 1.0 pF. Figure 6 shows the frequency offset test results. The frequency offset is now zero with Ct1 = 10 pF and Ct2 = 10 pF.

See Table 3 for crystal tuning values used on the Phoenix Development Board with the TEW crystal.

Table 2. TEW TAS-4025A

| Specification        | Value                        |  |

|----------------------|------------------------------|--|

| Package              | 4.0 × 2.5 × 0.65 mm - 4 pads |  |

| Frequency            | 13.000 MHz                   |  |

| Mode                 | Fundamental                  |  |

| Stability            | <15ppm @ -40 to +85°C        |  |

| CL Load Capacitance  | 16 pF                        |  |

| ESR                  | 80Ω max                      |  |

| CO Shunt Capacitance | 5 pF                         |  |

## Table 2. TEW TAS-4025A (continued)

| Specification       | Value              |

|---------------------|--------------------|

| Drive Level         | 50 ± 10uV          |

| Pullability         | 2 ppm/pF (minimum) |

| Storage Temperature | −40 to +85°C       |

# Table 3. TEW on Phoenix Board

| Specification | Value |

|---------------|-------|

| Ct1           | 10 pF |

| Ct2           | 10 pF |

# **TCXO (Temperature Compensated Crystal Oscillator)**

The LMX5453 also can operate with an external TCXO (Temperature Compensated Crystal Oscillator). The TCXO signal is directly connected to the CLK+.

1. Input Impedance

The LMX5453 CLK+ pin has in input impedance of 2pF capacitance in parallel with >400kΩ resistance

# **Optional 32 KHZ Oscillator**

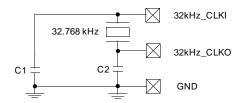

A second oscillator is provided (see Figure 4) that is tuned to provide optimum performance and low-power consumption while operating with a 32.768 kHz crystal. An external crystal clock network is required between the 32kHz\_CLKI clock input (pad B13) and the 32kHz\_CLKO clock output (pad C13) signals. The oscillator is built in a Pierce configuration and uses two external capacitors. Figure 4 provides the oscillator's specifications.

In case the 32Khz is placed optionally, it is recommended to remove C2 and replace C1 with a zero ohm resistor.

Figure 4. 32.768 kHz Oscillator

## Table 4. 32.768 kHz Oscillator Specifications

| Symbol             | Parameter                   | Condition | Min Typ Max   |   | Unit |    |

|--------------------|-----------------------------|-----------|---------------|---|------|----|

| $V_{DD}$           | Supply Voltage              |           | 1.62 1.8 1.98 |   | V    |    |

| I <sub>DDACT</sub> | Supply Current (Active)     |           |               | 2 |      | μΑ |

| f                  | Nominal Output<br>Frequency |           | 32.768        |   | kHz  |    |

| V <sub>PPOSC</sub> | Oscillating Amplitude       |           | 1.8           |   | V    |    |

|                    | Duty Cycle                  |           | 40            |   | 60   | %  |

## **Table 5. System Clock Requirements**

| Symbol              | Parameter                                                       | Min | Тур | Max | Unit |

|---------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| C <sub>REF</sub>    | External Reference Clock Frequency <sup>(1)</sup>               | 10  | 13  | 20  | MHz  |

| $C_{TOL}$           | Frequency Tolerance (over full operating temperature and aging) | -20 | 15  | 20  | ppm  |

| XOC <sub>TUNE</sub> | Digital Crystal Tuning Load Range                               |     | 8   |     | pF   |

| Cosc                | Crystal Oscillator                                              | 10  | 13  | 20  | MHz  |

<sup>(1)</sup> Frequencies supported: 10.00, 10.368, 12.00, 12.60, 12.80, 13.00, 13.824, 14.40, 15.36, 16.00, 16.20, 16.80, 19.20, 19.44, 19.68, and 19.80 MHz

**Table 5. System Clock Requirements (continued)**

| Symbol              | Parameter                                           |     | Тур | Max | Unit     |

|---------------------|-----------------------------------------------------|-----|-----|-----|----------|

| C <sub>ESR</sub>    | Crystal Serial Resistance                           |     |     | 230 | Ω        |

| C <sub>REF-PS</sub> | External Reference Clock Power Swing (peak to peak) | 100 | 200 | 400 | mV       |

| C <sub>int</sub>    | Internal Load Capacitance                           |     | 8   |     | pF       |

| C <sub>AGE</sub>    | Aging                                               |     |     | 1   | ppm/year |

Figure 5. Frequency Offset with 12 pF//12 pF Capacitors

Figure 6. Frequency Offset with 10 pF//10 pF Capacitors

## Table 6. Register 2: XOCTUNE Tuning Load Range

| Binary Value | Hex Value         | Value | Units |

|--------------|-------------------|-------|-------|

| 000 0000     | 00                | 0     | pF    |

| 010 1000     | 28 <sup>(1)</sup> | 2.6   | pF    |

| 111 1111     | 7F                | 8     | pF    |

(1) Default value for RF initialization register 2.

Figure 7. ESR vs. Load Capacitance for the Crystal

# **Antenna Matching and Front-End Filtering**

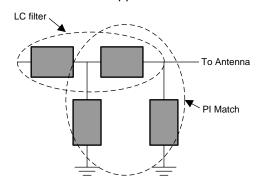

Figure 8 shows the recommended component layout to be used between RF output and antenna input. Allows for versatility in the design such that the match to the antenna maybe improved and/or the blocking margin increased by addition of a LC filter. Refer to antenna application note for further details.

Figure 8. Front End Layout

Copyright © 2006–2014, Texas Instruments Incorporated

Product Folder Links: LMX5453

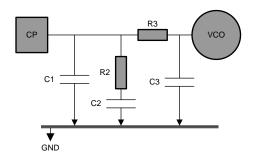

# **Loop Filter Design**

Since the LMX5453 has an external loop filter that determines the performance of the device to a great extent, it is important that it is designed correctly. Texas Instruments will provide the starting component values but the end customer may have to make adjustments to optimize the performance. Please refer to Loop Filter application note and also Texas Instrument's Webench design tool for detailed information.

# **Component Calculations**

The following parameters are required for component value calculation of a third order passive loop filter.

| symbol?           | Phase Margin: Phase of the open loop transfer function             |  |

|-------------------|--------------------------------------------------------------------|--|

| F <sub>c</sub>    | Loop Bandwidth                                                     |  |

| F <sub>comp</sub> | Comparison Frequency: Phase detector frequency                     |  |

| KVOC              | VCO gain: Sensitivity of the VCO to control volts                  |  |

| K symbol?         | Charge Pump gain: Magnitude of the alternating current during lock |  |

| F <sub>OUT</sub>  | Mean RF output frequency                                           |  |

| T31               | Ratio of the poles T3 to T1 in a 3rd order filter                  |  |

| symbol?           | Gamma optimization parameter                                       |  |

The third order loop filter being defined has the topology shown in Figure 10.

Figure 9. Third Order Loop Filter

$$\phi = \tan^{-1} \left( \frac{\gamma}{\omega_{\mathbf{C}} \cdot \mathsf{T1} \cdot \mathsf{T1} + \mathsf{T31}} \right) - \tan^{-1} (\omega_{\mathbf{C}} \cdot \mathsf{T1}) - \tan^{-1} (\omega_{\mathbf{C}} \cdot \mathsf{T1} \cdot \mathsf{T31})$$

(6)

Calculate the poles and zeros. Use exact method to solve for T1 using numerical methods.

$$T3 = T31 \times T1 \qquad T2 = \frac{\gamma}{\omega_{\mathbb{C}} \cdot (T1 + T3)} \tag{7}$$

$$A0 = \frac{K\phi \cdot K_{vco}}{\omega_{C}^{2} \cdot N} \cdot \sqrt{\frac{1 + \omega_{C}^{2} \cdot T2^{2}}{(1 + \omega_{C}^{2} \cdot T1^{2})(1 + \omega_{C}^{2} \cdot T3^{2})}}$$

(8)

Calculate the loop filter coefficients,

$$A1 = A0 \cdot (T1 + T3)$$

$A2 = A0 \cdot T1 \cdot T3$  (9)

C1 =

$$\frac{A2}{T2^2} \cdot \left( 1 + \sqrt{1 + \left( \frac{T2 \cdot A0 - T2 \cdot A1}{A2} \right)} \right)$$

(10)

#### Summary:

| Symbol | Description      | Units |  |

|--------|------------------|-------|--|

| η      | N counter value  | None  |  |

|        | Loop Bandwidth   | rad/s |  |

| T1     | Loop filter pole | S     |  |

www.ti.com

| Symbol | Description                           | Units |

|--------|---------------------------------------|-------|

| T2     | Loop filter zero                      | S     |

| T3     | Loop filter zero                      | S     |

| A0     | Total capacitance                     | nF    |

| A1     | First order loop filter coefficient   | nFs   |

| A2     | Second order loop filter coefficients | nFs2  |

Components can then be calculated from loop filter coefficients

$$C3 = \frac{1 \cdot T2^2 \cdot C1^2 + T2 \cdot A1 \cdot C1 - A2 \cdot A0}{T2^2 \cdot C1 - A2} \qquad C2 = A0 - C1 - C3$$

$$R2 = \frac{T2}{C2} \qquad R3 = \frac{A2}{C1 \cdot C3 \cdot T2}$$

$$LT = \frac{400}{F_C} (1 - \log_{10} \Delta F) \qquad \text{where } \Delta F = \frac{Frequency - tolerance}{Frequency - jump}$$

$$(13)$$

$$R2 = \frac{T2}{C2} \qquad R3 = \frac{A2}{C1 \cdot C3 \cdot T2}$$

(12)

$$LT = \frac{400}{F_C} (1 - \log_{10} \Delta F) \qquad \text{where } \Delta F = \frac{\text{Frequency} - \text{tolerance}}{\text{Frequency} - \text{jump}}$$

(13)

Some typical values for the LMX5453 are:

| Symbol               | Description | Units     |

|----------------------|-------------|-----------|

| Comparison Frequency | 13          | MHz       |

| Phase Margin         | 48          | PI rad    |

| Loop bandwidth       | 100         | kHz       |

| T3 or T1 ratio       | 40          | %         |

| Gamma                | 1.0         |           |

| VCO gain             | 120         | MHz per V |

| Charge pump gain     | 0.6         | mA        |

| Fout                 | 2441        | MHz       |

Which give the following component values:

| Symbol | Description | Units |

|--------|-------------|-------|

| C1     | 0.17        | nF    |

| C2     | 2.38        | nF    |

| C3     | 0.04        | nF    |

| R2     | 1737        | ohms  |

| R3     | 7025        | ohms  |

## **Phase Noise and Lock-Time Calculations**

Phase noise has three sources, the VCO, crystal oscillator and the rest of the PLL consisting of the phase detector, dividers, charge pump and loop filter. Assuming the VCO and crystal are very low noise, it is possible to put down approximate equations that govern the phase noise of the PLL.

Phase noise (in-band) =  $PN1Hz + 20Log[N] + 10Log[F_{comp}]$

Where PH1Hz is the PLL normalized noise floor in 1 Hz resolution bandwidth.

Further out from the carrier, the phase noise will be affected by the loop filter roll-off and hence its bandwidth.

As a rule-of-thumb;  $\Delta$  Phase noise = 40Log [ $\Delta$  F<sub>c</sub>]

Where Fc is the relative change in loop BW expressed as a fraction.

For example if the loop bandwidth is reduced from 100kHz to 50kHz or by one half, then the change in phase noise will be -12dB. Loop BW in reality should be selected to meet the lower limit of the modulation deviation, this will yield the best possible phase noise.

Even further out from the carrier, the phase noise will be mainly dominated by the VCO noise assuming the crystal is relatively clean.

Lock-time is dependent on three factors, the loop bandwidth, the maximum frequency jump that the PLL must make and the final tolerance to which the frequency must settle. As a rule-of-thumb it is given by:

$$LT = \frac{400}{F_C} (1 - log_{10} \Delta F) \qquad \text{where } \Delta F = \frac{Frequency - tolerance}{Frequency - jump} \tag{14}$$

These equations are approximations of the ones used by Webench to calculate phase noise and lock-time.

# **Practical Optimisation**

In an example where frequency drift and drift rate can be improved though loop filter tweaks, consider the results taken below. The drift rate is 26.1 kHz per 50us and the maximum drift is 25 kHz for DH1 packets, both of which are exceeding or touching the Bluetooth pass limits. These measurements are taken with component values shown above.

Table 7. TRM/CA/09/C (Carrier Drift) Hopping On - Low Channel

|                   | DH1       | DH3 | DH5       |

|-------------------|-----------|-----|-----------|

| Drift Rate / 50us | 26, 1 kHz | N/A | −30,5 kHz |

| Max Drift         | 25 kHz    | N/A | 36 kHz    |

| Average Drift     | −1 kHz    | N/A | 12 kHz    |

| Packets Tested    | 10        | N/A | 10        |

| Packets Failed    | 2         | N/A | 10        |

| Overall Result    | Failed    | N/A | Failed    |

Results below were taken on the same board with three loop filter values changed. C2 and R2 have been increased in value and C1 has been reduced. The drift rate has improved by 13 kHz per 50  $\mu$ s and the maximum drift has improved by 10 kHz.

Table 8. TRM/CA/09/C (Carrier Drift) Hopping On - Low Channel

|                   | DH1       | DH3 | DH5      |

|-------------------|-----------|-----|----------|

| Drift Rate / 50us | –13,6 kHz | N/A | 15,6 kHz |

| Max Drift         | 15 kHz    | N/A | 21 kHz   |

| Average Drift     | 3 kHz     | N/A | 1 kHz    |

| Packets Tested    | 10        | N/A | 10       |

| Packets Failed    | 0         | N/A | 0        |

| Overall Result    | Passed    | N/A | Passed   |

The effect of changing these three components is to reduce the loop bandwidth which reduces the phase noise. The reduction in this noise level corresponds directly to the reduction of noise in the payload area where drift is measured. This noise reduction comes at the expense of locktime which can be increased to 120 µs without suffering any ill effects, however if we continue to reduce the loop BW further the lock-time will increase such that the PLL does not have time to lock before data transmission and the drift will again increase. Before the lock-time goes out of spec, the modulation index will start to fall since it is being cut by the reducing loop BW. Therefore a compromise has to be found between lock-time, phase noise and modulation, which yields best performance.

Note// The values shown on the LMX5453 datasheet are the best case optimized values that have been shown to produce the best overall results and are recommended as a starting point for all designs.

Another example of how the loop filter values can affect frequency drift rate, these results below show the DUT with maximum drift on mid and high channels failing. Adjusting the loop bandwidth as shown provides the improvement required to pass qualification.

# Table 9. Original results:

| Hopping OFF - L   | ow Channel |            |            |                 |

|-------------------|------------|------------|------------|-----------------|

|                   | DH1        | DH3        | DH5        | Limits          |

| Drift Rate / 50us | –15.00 kHz | –28.10 kHz | –19.10 kHz | +/- 20 kHz      |

| Maximum Drift     | −19 kHz    | –37 kHz    | –20 kHz    | DH1: +/- 25 kHz |

| Average Drift     | –11 kHz    | –32 kHz    | –10 kHz    | DH3: +/- 40 kHz |

| Packets Tested    | 10         | 10         | 10         | DH5: +/- 40 kHz |

| Packets Failed    | 0          | 1          | 0          |                 |

| Result            | Pass       | Fail       | Pass       |                 |

| Hopping OFF - M   | led Channel |           |            |                 |

|-------------------|-------------|-----------|------------|-----------------|

|                   | DH1         | DH3       | DH5        | Limits          |

| Drift Rate / 50us | –18.60 kHz  | 16.30 kHz | -18.00 kHz | +/- 20 kHz      |

| Maximum Drift     | –29 kHz     | –44 kHz   | –28 kHz    | DH1: +/- 25 kHz |

| Average Drift     | –19 kHz     | –37 kHz   | –19 kHz    | DH3: +/- 40 kHz |

| Packets Tested    | 10          | 10        | 10         | DH5: +/- 40 kHz |

| Packets Failed    | 2           | 2         | 0          |                 |

| Result            | Fail        | Fail      | Pass       |                 |

| Hopping OFF - Hig | gh Channel |           |            |                 |

|-------------------|------------|-----------|------------|-----------------|

|                   | DH1        | DH3       | DH5        | Limits          |

| Drift Rate / 50us | –16.30 kHz | 16.80 kHz | −17.70 kHz | +/- 20 kHz      |

| Maximum Drift     | –36 kHz    | –61 kHz   | –38 kHz    | DH1: +/- 25 kHz |

| Average Drift     | –31 kHz    | –48 kHz   | –29 kHz    | DH3: +/- 40 kHz |

| Packets Tested    | 10         | 10        | 10         | DH5: +/- 40 kHz |

| Packets Failed    | 10         | 8         | 0          |                 |

| Result            | Fail       | Fail      | Pass       |                 |

# Table 10. New Results:

| Hopping OFF - Lo  | w Channel  |            |           |                 |

|-------------------|------------|------------|-----------|-----------------|

|                   | DH1        | DH3        | DH5       | Limits          |

| Drift Rate / 50us | –12.00 kHz | –15.10 kHz | 18.80 kHz | +/- 20 kHz      |

| Maximum Drift     | –15 kHz    | –35 kHz    | –19 kHz   | DH1: +/- 25 kHz |

| Average Drift     | −6 kHz     | –25 kHz    | −9 kHz    | DH3: +/- 40 kHz |

| Packets Tested    | 10         | 10         | 10        | DH5: +/- 40 kHz |

| Packets Failed    | 0          | 0          | 0         |                 |

| Result            | Pass       | Pass       | Pass      |                 |

| Hopping OFF - N   | Hopping OFF - Med Channel |            |           |                 |  |

|-------------------|---------------------------|------------|-----------|-----------------|--|

|                   | DH1                       | DH3        | DH5       | Limits          |  |

| Drift Rate / 50us | –14.20 kHz                | –16.10 kHz | 17.20 kHz | +/- 20 kHz      |  |

| Maximum Drift     | −16 kHz                   | –34 kHz    | –22 kHz   | DH1: +/- 25 kHz |  |

| Average Drift     | −11 kHz                   | –27 kHz    | −9 kHz    | DH3: +/- 40 kHz |  |

| Packets Tested    | 10                        | 10         | 10        | DH5: +/- 40 kHz |  |

| Packets Failed    | 0                         | 0          | 0         |                 |  |

| Result            | Pass                      | Pass       | Pass      |                 |  |

| Hopping OFF - Hi  | igh Channel |            |            |                 |

|-------------------|-------------|------------|------------|-----------------|

|                   | DH1         | DH3        | DH5        | Limits          |

| Drift Rate / 50us | –12.70 kHz  | –17.40 kHz | -16.50 kHz | +/- 20 kHz      |

| Maximum Drift     | –23 kHz     | –29 kHz    | –25 kHz    | DH1: +/- 25 kHz |

| Average Drift     | –12 kHz     | –25 kHz    | –16 kHz    | DH3: +/- 40 kHz |

| Packets Tested    | 10          | 10         | 10         | DH5: +/- 40 kHz |

| Packets Failed    | 0           | 0          | 0          |                 |

| Result            | Pass        | Pass       | Pass       |                 |

# **Reference Starting Values**

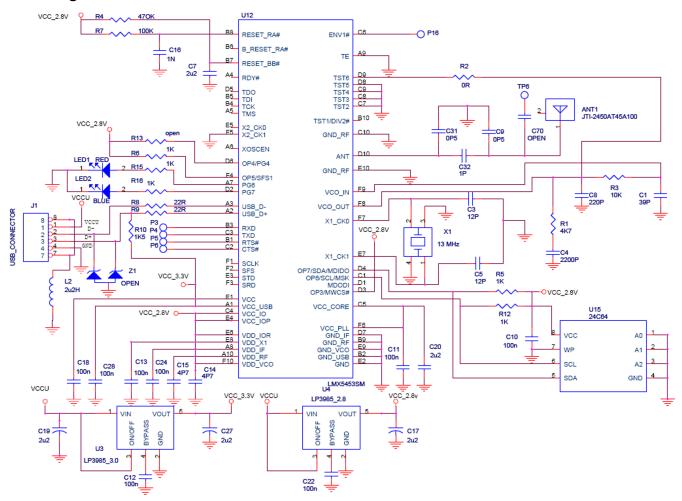

Recommended starting values for the LMX5453 as also stated in the reference design towards the end of this datasheet are a as shown in Table 11. These values have been optimized through testing to yield the best results from the design. However minor changes to the layout could mean the values need re-optimization.

**Table 11. Loop Filter Values**

| Device  | C1     | C2      | C3    | R2   | R3  |

|---------|--------|---------|-------|------|-----|

| LMX5453 | 220 pF | 2200 pF | 39 pF | 4.7k | 10k |

## **Functional Blocks**

# **Baseband Processor And Link Management Processor**

Baseband and lower link control functions are implemented using a combination of a CompactRISC 16-bit processor and the Bluetooth Lower Link Controller (LLC). These processors operate from integrated ROM memory and RAM. They execute on-board firmware implementing all Bluetooth functions.

#### **Bluetooth Lower Link Controller**

The integrated Bluetooth Lower Link Controller complies with the Bluetooth Specification version 2.0 and implements the following functions:

- Faster connection

- Interlaced Scanning

- Adaptive frequency hopping (AFH)

- Enhanced Error detection

- Support for 1-, 3-, and 5-slot packet types

- 79 channel hop-frequency generation circuitry

- Fast frequency hopping at 1600 hops per second

- Power management control

- · Access code correlation and slot timing recovery

#### Memory

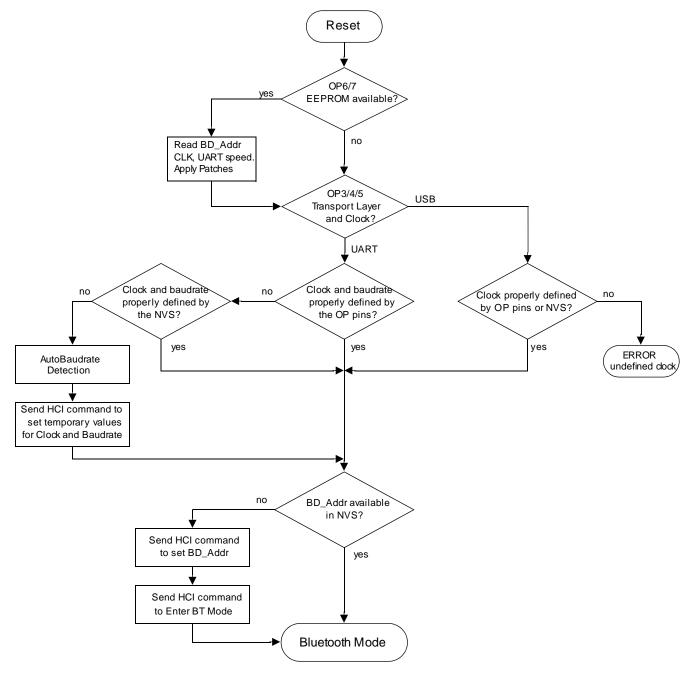

The LMX5453 provides 16K of combined system and Patch RAM memory that can be used for data and/or code upgrades of the ROM-based firmware. Due to the flexible startup used for the LMX5453, operating parameters like the Bluetooth Device Address (BD\_ADDR) are defined during boot time. This allows reading the parameters from an external EEPROM or programming them directly over HCI.

# **External Memory Interfaces**

Because the LMX5453 is a ROM-based device with no onchip non-volatile storage, the operation parameters will be lost after a power cycle or hardware reset. To avoid reinitializing operation parameters, patches, or user data, the LMX5453 offers two options for connecting with an external EEPROM:

- Microwire/SPI

- ACCESS.bus (I<sup>2</sup>C compatible)

The interface is selected during start-up, based on states sampled from the option pins. See Table 20 for the option pin descriptions.

#### Microwire/SPI Interface

If the configuration selected by the option pins uses a Microwire/SPI interface, the LMX5453 activates that interface and attempts to read the EEPROM. The external memory must be compatible with the features listed in Table 12.

The largest size EEPROM supported is limited by the addressing format of the selected EEPROM. The device must have a page size equal to N x 32 bytes.

The LMX5453 firmware requires that the EEPROM supports page write. The clock must be high when idle.

|                               | Table 12. III30040 0 EEI Rolli olk x 0    |  |  |  |  |  |

|-------------------------------|-------------------------------------------|--|--|--|--|--|

| Parameter                     | Value                                     |  |  |  |  |  |

| Supplier                      | ST Microelectronics                       |  |  |  |  |  |

| Supply Voltage <sup>(1)</sup> | 1.8 - 3.6 V                               |  |  |  |  |  |

| Interface                     | SPI compatible (positive clock SPI modes) |  |  |  |  |  |

| Memory Size                   | 8K x 8 (64 Kbits)                         |  |  |  |  |  |

| Clock Rate <sup>(1)</sup>     | 2 MHz                                     |  |  |  |  |  |

| Arress                        | Ryte and page write (up to 32 hytes)      |  |  |  |  |  |

**Table 12. M95640-S EEPROM 8K × 8**

#### **ACCESS.bus Interface**

If the configuration selected by the option pins uses an ACCESS.bus or I2C-compatible interface, the LMX5453 activates that interface and attempts to read the EEPROM. The external memory must be compatible with the features listed in Table 13.

The largest size EEPROM supported is limited by the addressing format of the selected EEPROM. The device must have a page size equal to N x 32 bytes. The device uses a 16-bit address format. The device address must be 000.

| Parameter                     | Value                   |  |

|-------------------------------|-------------------------|--|

| Supplier                      | Atmel                   |  |

| Supply Voltage <sup>(1)</sup> | 2.7 - 5.5 V             |  |

| Interface                     | 2-wire serial interface |  |

| Memory Size                   | 8K x 8 (64 Kbits)       |  |

| Clock Rate <sup>(1)</sup>     | 100 kHz                 |  |

| Access                        | 32-byte page-write mode |  |

**Table 13. 24C64 EEPROM 8K x 8**

# **Host Controller Interface Port**

#### **UART Interface**

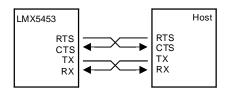

The LMX5453 provides one Universal Asynchronous Receiver Transmitter (UART). It supports 8-bit data with or without parity, and with one or two stop bits. The UART can operate at standard baud rates from 300 baud up to a maximum of 921.6 kbaud. DMA transfers are supported to allow for fast processor-independent receive and transmit operation. The UART implements flow-control signals (RTS# and CTS#) for hardware handshaking.

The reference clock and UART baud rate are configured during start-up by sampling option pins OP3, OP4, and OP5. If the auto baud rate detect option is selected, the firmware checks an area in non-volatile storage (NVS) for a valid UART baud rate stored during a previous session. If no value was saved, the LMX5453 will switch to auto baud rate detection and wait for an incoming reference signal.

<sup>(1)</sup> Parameter range reduced to requirements of Texas Instruments' reference design.

<sup>(1)</sup> Parameter range reduced to requirements of Texas Instruments' reference design.

The UART can detect a BREAK signal, which forces the LMX5453 to reset. This is useful when the only connection between the LMX5453 and the host system is the HCl port.

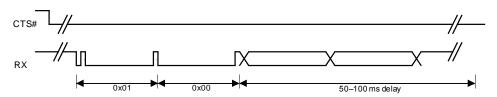

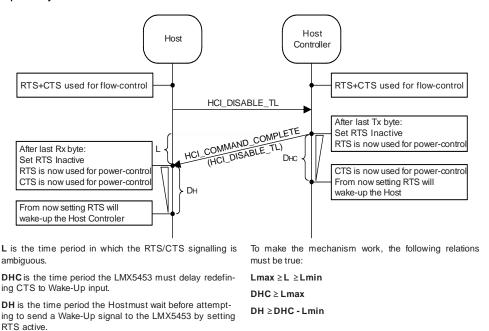

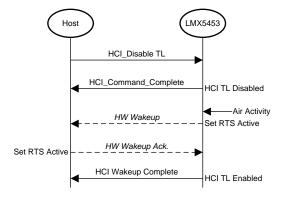

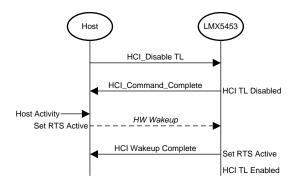

The UART offers wake-up from low-power modes through its Multi-Input Wake-Up module (MIWU). When the LMX5453 is in a low-power mode, RTS# and CTS# can function as Host\_WakeUp and Bluetooth\_WakeUp, respectively. Table 14 represents the operational modes supported by the LMX5453 firmware for implementing the HCI transport port with the UART.

**Table 14. UART Operation Modes**

| Modes        | Range              | Default at Power-Up                                                            | With Auto Baud Detect |

|--------------|--------------------|--------------------------------------------------------------------------------|-----------------------|

| Baud Rate    | 0.3 to 921.6 kbaud | Configured by option<br>pins, NVS parameter,<br>or auto baud rate<br>detection | 0.3 to 921.6 kbaud    |

| Flow Control | RTS#/CTS# or None  | RTS#/CTS#                                                                      | RTS#/CTS#             |

| Parity       | Odd, Even, or None | None                                                                           | None                  |

| Stop Bits    | 1 or 2             | 1                                                                              | 1                     |

| Data Bits    | 8                  | 8                                                                              | 8                     |

#### **USB** Interface

The LMX5453 USB node controller features enhanced DMA support with many automatic data handling features. It is certifiable to USB specification version 2.0. The USB interface is the standard 12 Mbit/s. An internal PLL provides the necessary 48 MHz clock.

The USB node controller integrates the required USB transceiver, a Serial Interface Engine (SIE) and USB endpoint FIFOs. Seven endpoint pipelines are supported: one for the mandatory control endpoint and six to support interrupt, bulk, and isochronous endpoints. Each endpoint pipeline has a dedicated FIFO (8 bytes for the control endpoint, and 64 bytes for the other endpoints).

#### **Audio Port**

#### **Advanced Audio Interface**

The Advanced Audio Interface (AAI) is an advanced version of the Synchronous Serial Interface (SSI) that provides a full-duplex communications port to a variety of industry-standard 13/14/15/16-bit linear or 8-bit log PCM codecs, DSPs, and other serial audio devices.

The interface supports up to two codecs or interfaces. The firmware selects the desired audio path and interface configuration using a parameter in RAM (imported from nonvolatile storage or programmed during boot-up). The audio path options include 16-bit two's complement linear audio through the HCI transport, the Motorola MC145483 codec, and the OKI MSM7717 codec through the AAI, or No Audio. See NVS Table 21.

If an external codec or DSP is used, the LMX5453 audio interface generates the necessary bit and frame clock for driving the interface.

Table 15 summarizes the audio path selection and the configuration of the audio interface at the specific modes.

The LMX5453 supports two simultaneous SCO links.

#### Table 15. Audio Path configuration

| Audio setting                       | Interface                | Freq     | Format                     | AAI Bit Clock | AAI Frame Clock | AAI Frame Sync<br>Pulse Length |

|-------------------------------------|--------------------------|----------|----------------------------|---------------|-----------------|--------------------------------|

| OKI MSM7717                         | Advanced audio interface | ANY (1)  | 8-bit log PCM (a-law only) | 480 KHz       | 8 KHz           | 14 Bits                        |

| Motorola<br>MC145483 <sup>(2)</sup> | Advanced audio interface | AINY (*) | 13-bit linear              | 480 KHz       | 8 KHz           | 13 Bits                        |

(1) For supported frequencies see Table 5

(2) Due to internal clock divider limitations the optimum of 512KHz, 8KHz can not be reached. The values are set to the best possible values. The clock mismatch does not result in any discernible loss in audio quality.

#### Table 15. Audio Path configuration (continued)

|                                     |                          |                    |                                   | • ,            | •               |                                |

|-------------------------------------|--------------------------|--------------------|-----------------------------------|----------------|-----------------|--------------------------------|

| Audio setting                       | Interface                | Freq               | Format                            | AAI Bit Clock  | AAI Frame Clock | AAI Frame Sync<br>Pulse Length |

| OKI MSM7717                         | Advanced audio interface | 13MHz              | 8-bit log PCM (a-law only)        | 520 KHz        | 8 KHz           | 14 Bits                        |

| Motorola<br>MC145483 <sup>(3)</sup> | Advanced audio interface | ISIVIMZ            | 13-bit linear                     | 520 KHz        | 8 KHz           | 13 Bits                        |

| Winbond<br>W681310                  | Advanced audio interface | 13MHz              | 8 bit log PCM A-law and u-law     | 520 KHz        | 8 KHz           | 14 Bits                        |

| Winbond<br>W681360                  | Advanced audio interface | 13MHz              | 13-bit linear                     | 520 KHz        | 8 KHz           | 13 Bits                        |

| PCM slave <sup>(4)</sup>            | Advanced audio interface | ANY <sup>(1)</sup> | 8/16 bits                         | 128 - 1024 KHz | 8 KHz           | 8/16 Bits                      |

| Audio over<br>HCI                   | HCI Transport            |                    | 16-Bit Two's<br>Complement Linear |                |                 |                                |

<sup>(3)</sup> Due to internal clock divider limitations the optimum of 512KHz, 8KHz can not be reached. The values are set to the best possible values. The clock mismatch does not result in any discernible loss in audio quality.

**PCM slave configuration example:** PCM slave uses the slot 0, 1 slot per frame, 16 bit linear mode, long frame sync, normal frame sync. In this case, 0x03E0 should be stored in NVS. See \*\* "LMX5453 Software User's Guide" for more details.

# **Auxiliary Ports**

#### **RESET#**

There are two reset inputs: RESET\_RA# for the radio and RESET\_BB# for the baseband. Both are active low.

There is also a reset output, B\_RESET\_RA# (Buffered Radio Reset), which is also active low. This output follows input RESET\_RA#. When RESET\_RA# is released, going high, B\_RESET\_RA# stays low until the clock has started.

See \*\* Section 15.0 for details and Section 16.0 for schematics.

## **General Purpose I/O Ports**

The LMX5453 provides 3 GPIO ports which either can be used as indication and configuration pins or can be used for general-purpose functionality. The states which select these options are sampled during the start-up sequence.

In a general-purpose configuration, the pins are controlled by hardware-specific HCI commands. These commands provide the ability to set the direction of the pin, drive the pin high or low, and enable a weak pull-up on the pin.

In the alternate-function configuration, the pins have predefined indication functions. See Table 16 for a description of the alternate-function configuration.

**Table 16. Alternate GPIO Pin Configuration**

| Pin     | Description                                                             |

|---------|-------------------------------------------------------------------------|

| OP4/PG4 | Operation mode pin to configure transport layer settings during boot-up |

| PG6     | USB status indication                                                   |

| PG7     | TL (Transport Layer) traffic indication                                 |

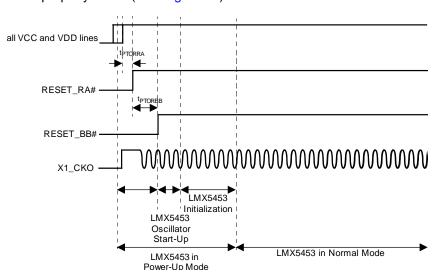

# System Power-Up

To power-up the LMX5453 the following sequence must be performed:

- 1. Apply VCC\_IO and VCC to the LMX5453.

- 2. The RESET\_RA# should be driven high.

<sup>(4)</sup> In PCM slave mode, parameters are stored in NVS. Bit clock and frame clock must be generated by the host interface.

3. Then RESET\_BB# should be driven high at a recommended time of 1ms after the LMX5453 voltage rails are high. The LMX5453 is properly reset. (See Figure 10).

Figure 10. LMX5453 Power-On Reset Timing

Table 17. LMX5453 Power to Reset Timing

| Symbol              | Parameter      | Condition                                                | Min                 | Тур | Max | Units |

|---------------------|----------------|----------------------------------------------------------|---------------------|-----|-----|-------|

| t <sub>PTORRA</sub> | Power to Reset | VCC and VCC_IO at operating voltage level to valid reset | <500 <sup>(1)</sup> |     |     | μs    |

| t <sub>PTORBB</sub> | Reset to Reset | VCC and VCC_IO at operating voltage level to valid reset | 1 <sup>(2)</sup>    |     |     | ms    |

- (1) Rise time on power must switch on fast, rise time <500 μs

- (2) Recommended value.

Table 18. ESR vs. Start-Up Time

| ESR (Ω) | Typical <sup>(1)(2)</sup> | Units |

|---------|---------------------------|-------|

| 10      | 12                        | ms    |

| 25      | 13                        | ms    |

| 40      | 16                        | ms    |

| 50      | 24                        | ms    |

| 80      | 30                        | ms    |

- (1) Frequency, loading caps, and ESR all must be considered for determining the start-up time.

- (2) For reference only, must be tested on each system to accurately determine the start-up time.

## **Start-Up Sequence**

During start-up, the LMX5453 samples the option inputs OP3 to OP7 for configuration, external clock source, HCI transport layer, and available non-volatile storage EEPROM interface. The start-up options are described in Table 20.

## **Options Register**

The states sampled from the OP inputs listed in Table 20 are latched in this register at the end of reset. The Options register can be read by the LMX5453 firmware at any time.

All pads are inputs with weak on-chip pull-up/down resistors during reset. The resistors are disconnected at the end of RESET BB#.

- 1 = Pull-up resistor connected in application

- 0 = Pull-down resistor connected in application

x = Don't care

## Start-Up With External EEPROM

To read information from an external EEPROM, the OP inputs have to be strapped according to Table 20.

The start-up sequence performs these operations:

- 1. From the Options register bits OP6 and OP7, the firmware checks whether a serial EEPROM is available to use (ACCESS.bus or Microwire/SPI).

- 2. If a serial EEPROM is available, the permanent parameter block, patch block, and non-volatile storage (NVS) are initialized from it.

- 3. From the Options register bits OP3, OP4, and OP5, the firmware checks for clocking information and transport layer settings. If the NVS information are not sufficient, the firmware will send the Await Initialization event on the TL and wait for additional information (see \*\* Section 15.1.3)

- 4. The firmware compensates the UART for new BBCLK information from the NVS.

- 5. The firmware starts up the Bluetooth core.

## Start-Up Without External EEPROM

The following sequence will take place if OP6 and OP7 have selected No external memory, as described in Table 20.

The start-up sequence performs these operations:

- 1. From the Options registers OP6 and OP7, the firmware checks if an EEPROM is available to use.

- 2. From the Options register OP3, OP4 and OP5, the firmware checks the clocking mode and transport layer settings.

- 3. The firmware sends the Await Initialization event on the transport layer and waits for NVS configuration commands. The configuration is finalized by sending the Enter Bluetooth Mode command.

- 4. The firmware compensates the UART for new BBCLK information from the NVS.

- 5. The firmware starts up the Bluetooth core.

Table 19. Start-Up Sequence Options<sup>(1)</sup>

|        | Description |     |          |          |                 |                                                                                   |

|--------|-------------|-----|----------|----------|-----------------|-----------------------------------------------------------------------------------|

| OP3    | OP4         | OP5 | OP6      | OP7      | ENV1#           | Description                                                                       |

| PD     | PD          | PD  | PD       | PD       | PU              | PD = Internal pull-<br>down during reset<br>PU = Internal pull-up<br>during reset |

| х      | Х           | х   | Open (0) | Open (0) | Open (1) BBCLK  | No serial memory                                                                  |

| х      | Х           | х   | 1        | Open (0) | Open (1) BBCLK  | TBD                                                                               |

| х      | х           | х   | Open (0) | 1        | Open (1) BBCLK  | Microwire serial memory                                                           |

| х      | х           | х   | 1        | 1        | Open (1) BBCLK  | ACCESS.bus serial memory                                                          |

| T_SCLK | Х           | х   | T_RFDATA | T_RFCE   | 0 BBCLK/US BCLK | Test mode                                                                         |

(1) I/O pull-up/down resistor connected in application.

# **Table 20. Fixed Frequencies**

| Osc Freq<br>(MHz) | BBLCK (MHz)          | PLL (48<br>MHz) | OP3 | OP4 | OP5 | Description                          |

|-------------------|----------------------|-----------------|-----|-----|-----|--------------------------------------|

| 12                | 12                   | Off             | 0   | 0   | 0   | HCI UART transport                   |

| 13                | 13                   | Off             | 1   | 0   | 0   | layer with baud rate                 |

| 10-20             | 10-20 <sup>(1)</sup> | On              | 0   | 1   | 0   | detection                            |

| 13                | 13                   | Off             | 1   | 1   | 0   | HCI UART transport layer 115.2 kbaud |

| 12                | 12                   | On              | 0   | 0   | 1   |                                      |

| 13                | 13                   | On              | 1   | 0   | 1   | HCI USB transport layer              |

| 10-20             | 10-20 <sup>(1)</sup> | On              | 0   | 1   | 1   | layer                                |

| 13                | 13                   | Off             | 1   | 1   | 1   | HCI UART transport layer 921.6 kbaud |

<sup>(1)</sup> See Table 5 for supported frequencies.

# Configuring the LMX5453 Through the Transport Layer

As described in Section 15.0, the LMX5453 checks the Options register during start-up to determine whether an external EEPROM is available. If the EEPROM information is incomplete or no EEPROM is installed, the LMX5453 will boot into the initialization mode. The mode is confirmed by the Await Initialization event.