# 24-BIT, 96-kHz STEREO AUDIO CODEC WITH MICROPHONE AMPLIFIER, BIAS, MUXTIPLEXER, AND PGA

#### **FEATURES**

- Microphone Amplifier and Bias

- Monaural Microphone Amplifier: 34-dB Gain at Differential Input

- Microphone Bias: 1 mA at 3.75 V

- Multiplexer and PGA

- Multiplex of Stereo Single-Ended Line Inputs and Monaural Microphone Amplifier

- 0.1 Vrms to 1.5 Vrms Full-Scale Input Range

- 22-kΩ Input Resistance at 0.1-Vrms Input

- 20 dB to -4 dB/range, 1 dB/step PGA

- Reference Output: ±10 mA at 2.5 V

- 24-Bit Delta-Sigma ADC and DAC

- Stereo ADC:

- Full-Scale Input: 3 Vp-p

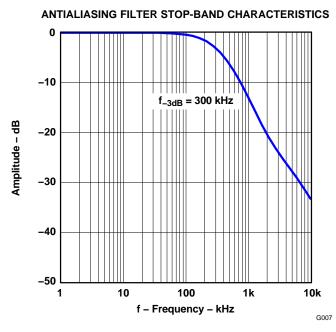

- Antialiasing Filter Included

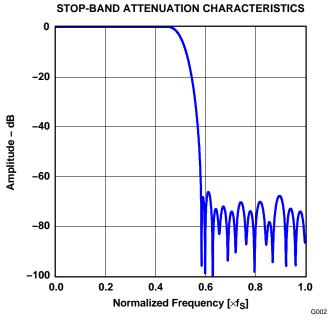

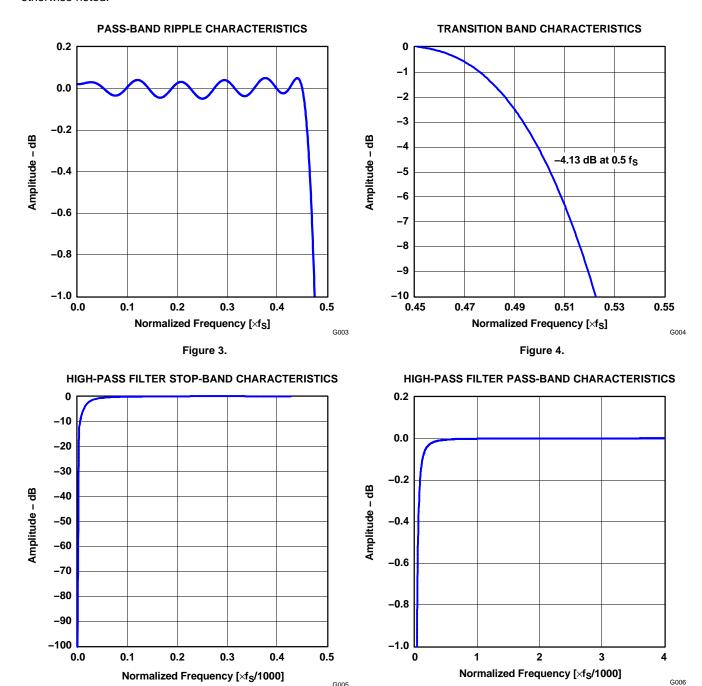

- 1/64 Decimation Filter:

- Pass-Band Ripple: ±0.05 dB

- Stop-Band Attenuation: -65 dB

- On-Chip High-Pass Filter: 0.91 Hz at

- $f_S = 48 \text{ kHz}$

- High Performance:

- THD+N: -94 dB (Typical)

- SNR: 101 dB (Typical)

- Dynamic Range: 101 dB (Typical)

- Stereo DAC:

- Single-Ended Voltage Output: 4 Vp-p

- Analog Low-Pass Filter Included

- ×8 Oversampling Digital Filter:

- Pass-Band Ripple: ±0.03 dB

- Stop-Band Attenuation: –50 dB

- High Performance:

- THD+N: -97 dB (Typical)

- SNR: 105 dB (Typical)

- Dynamic Range: 104 dB (Typical)

- S/PDIF Output for DAC Digital Input

- Multiple Functions With I<sup>2</sup>C Interface:

- Digital De-Emphasis: 32-, 44.1-, 48-kHz

- Zipper-Noise-Free Digital Attenuation and Soft Mute for DAC

- HPF Bypass Control for ADC

- S/PDIF Output Control

- Power Down: ADC/DAC Independently

- External Power-Down Pin:

- ADC/DAC Simultaneously

- Audio Data Format: 24-Bit I<sup>2</sup>S Only

- Sampling Rate:

- 16-96 kHz for Both ADC and DAC

- System Clock: 256 f<sub>S</sub> Only

- Dual Power Supplies:

- 5 V for Analog and 3.3 V for Digital

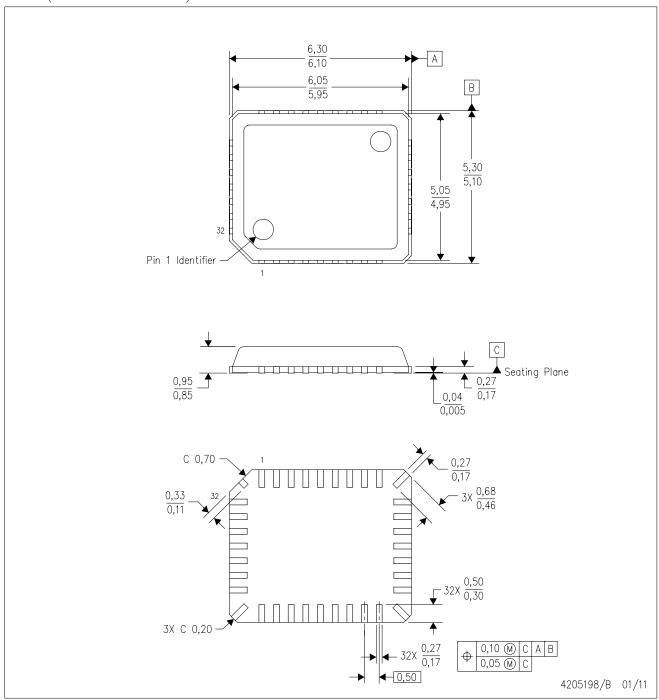

- Package: VQFN-32

## **DESCRIPTION**

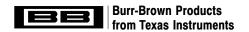

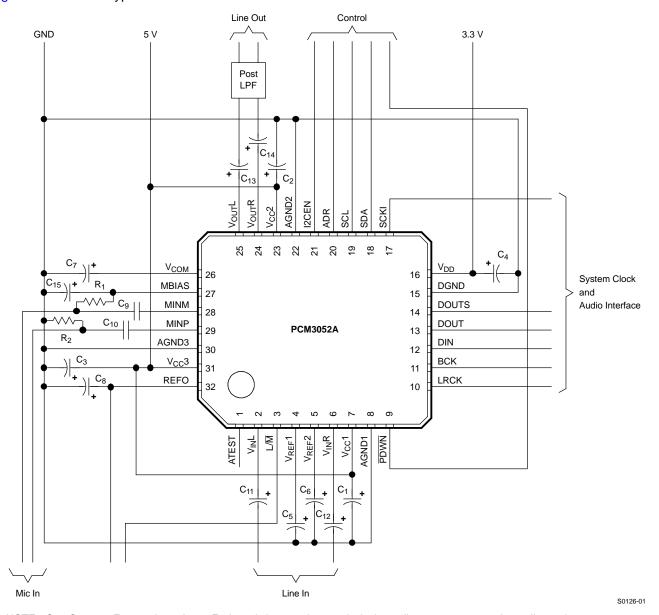

The PCM3052A is a low-cost, single-chip, 24-bit stereo audio codec (ADC and DAC) single-ended analog voltage input and output. It also has an analog front end consisting of a 34-dB microphone amplifier, microphone bias generator, 2 stereo multiplexers, and a wide-range PGA. Analogto-digital converters (ADCs) employ delta-sigma modulation with 64-times oversampling. On the other hand, digital-to-analog converters (DACs) employ modulation with 64- and 128-times oversampling. ADCs include a digital decimation filter with a high-pass filter, and DACs include an 8-times oversampling digital interpolation filter. PCM3052A has many functions which are controlled using the I<sup>2</sup>C interface: DAC digital de-emphasis, digital attenuation, soft mute etc. The PCM3052A also has an S/PDIF output pin for the DAC digital input. The power-down mode, which works on ADCs and DACs simultaneously, is provided by an external pin. The PCM3052A is suitable for a wide variety of cost-sensitive PC audio (recorder and player) applications where good performance is required. The PCM3052A is fabricated using a highly advanced CMOS process and is available in a small 32-pin VQFN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

System Two, Audio Precision are trademarks of Audio Precision, Inc. All trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                                |                                                                                                                                                                           | PCM3052A                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Cupalyyeltaga                  | V <sub>CC</sub> 1, V <sub>CC</sub> 2, V <sub>CC</sub> 3                                                                                                                   | −0.3 V to 6.5 V                                               |

| Supply voltage                 | $V_{DD}$                                                                                                                                                                  | -0.3 V to 4 V                                                 |

| Supply voltage differences     | V <sub>CC</sub> 1, V <sub>CC</sub> 2, V <sub>CC</sub> 3                                                                                                                   | ±0.1 V                                                        |

| Ground voltage differences     | AGND1, AGND2, AGND3, DGND                                                                                                                                                 | ±0.1 V                                                        |

| Digital input valtage          | PDWN, DIN, SCKI, SDA, SCL, ADR, I2CEN                                                                                                                                     | -0.3 V to 6.5 V                                               |

| Digital input voltage          | DOUT, LRCK, BCK, DOUTS                                                                                                                                                    | $-0.3 \text{ V to } (V_{DD} + 0.3 \text{ V}) < 4 \text{ V}$   |

| Analog input voltage           | $V_{\text{IN}}L,V_{\text{IN}}R,V_{\text{REF}}1,V_{\text{REF}}2,\text{REFO},\text{ATEST},L/\overline{M},V_{\text{OUT}}R,V_{\text{OUT}}L,V_{\text{COM}},$ MINP, MINM, MBIAS | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V}) < 6.5 \text{ V}$ |

| Input current (any pins except | t supplies)                                                                                                                                                               | ±10 mA                                                        |

| Ambient temperature under bi   | ias                                                                                                                                                                       | –40°C to 125°C                                                |

| Storage temperature            |                                                                                                                                                                           | −55°C to 150°C                                                |

| Junction temperature           |                                                                                                                                                                           | 150°C                                                         |

| Lead temperature (soldering)   |                                                                                                                                                                           | 260°C, 5 s                                                    |

| Package temperature (reflow,   | peak)                                                                                                                                                                     | 260°C                                                         |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                |                                 |                                          | MIN  | NOM               | MAX | UNIT  |

|----------------|---------------------------------|------------------------------------------|------|-------------------|-----|-------|

| $V_{DD}$       | Digital supply voltage          |                                          | 3    | 3.3               | 3.6 | V     |

| $V_{CC}$       | Analog supply voltage           |                                          | 4.5  | 5                 | 5.5 | V     |

|                | Digital input logic family      |                                          |      | TTL<br>compatible |     |       |

|                | Digital input alogic fraguency  | System clock                             | 4    |                   | 25  | MHz   |

|                | Digital input clock frequency   | Sampling clock                           | 16   |                   | 96  | kHz   |

|                | Analog input valtage            | Line input, full scale, PGA = 0 dB       |      | 3                 |     | Vp-p  |

|                | Analog input voltage            | Microphone input, full scale, PGA = 0 dB |      | 30                |     | mVp-p |

|                | Digital output load capacitance |                                          |      |                   | 20  | pF    |

|                | Line output load resistance     |                                          | 5    |                   |     | kΩ    |

|                | Line output load capacitance    |                                          |      |                   | 50  | pF    |

|                | Microphone bias output load re  | sistance                                 | 3.75 |                   |     | kΩ    |

|                | Reference output load resistant | ce                                       | 250  |                   |     | Ω     |

| T <sub>A</sub> | Operating free-air temperature  |                                          | -40  |                   | 85  | °C    |

# **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted

|                                    | PARAMETER                   | TEST CONDITIONS                      | MIN                              | TYP                   | MAX                              | UNIT  |

|------------------------------------|-----------------------------|--------------------------------------|----------------------------------|-----------------------|----------------------------------|-------|

| DIGITAL                            | INPUT/OUTPUT – DATA FORMAT  |                                      |                                  |                       |                                  |       |

|                                    | Audio data interface format |                                      |                                  | I <sup>2</sup> S      |                                  |       |

|                                    | Audio data bit length       |                                      |                                  | 24                    |                                  | Bits  |

|                                    | Audio data format           |                                      | MSB-first,                       | 2s comple             | ment                             |       |

| 4                                  | Sampling frequency, ADC     |                                      | 16                               | 48                    | 96                               | kHz   |

| f <sub>S</sub>                     | Sampling frequency, DAC     |                                      | 16                               | 48                    | 96                               | kHz   |

|                                    | System clock frequency      | 256 f <sub>S</sub>                   | 4                                |                       | 25                               | MHz   |

| INPUT LC                           | OGIC                        |                                      |                                  |                       |                                  |       |

| V <sub>IH</sub> <sup>(1)</sup>     | land lania lanal            |                                      | 2                                |                       | $V_{DD}$                         | VDC   |

| V <sub>IL</sub> <sup>(1)</sup>     | Input logic level           |                                      |                                  |                       | 0.8                              | VDC   |

| V <sub>IH</sub> <sup>(2)(3)</sup>  |                             |                                      | 2                                |                       | 5.5                              | \/D0  |

| V <sub>IL</sub> <sup>(2)</sup> (3) | Input logic level           |                                      |                                  |                       | 0.8                              | VDC   |

| I <sub>IH</sub> <sup>(2)</sup>     |                             | $V_{IN} = V_{DD}$                    |                                  |                       | ±10                              |       |

| I <sub>IL</sub> <sup>(2)</sup>     | Input logic current         | V <sub>IN</sub> = 0 V                |                                  |                       | ±10                              | μΑ    |

| I <sub>IH</sub> <sup>(1)(3)</sup>  |                             | $V_{IN} = V_{DD}$                    |                                  | 65                    | 100                              |       |

| I <sub>IL</sub> <sup>(1)</sup> (3) | Input logic current         | V <sub>IN</sub> = 0 V                |                                  |                       | ±10                              | μΑ    |

| OUTPUT                             | LOGIC                       |                                      |                                  |                       |                                  |       |

| V <sub>OH</sub> <sup>(4)</sup>     |                             | $I_{OUT} = -4 \text{ mA}$            | 2.8                              |                       |                                  |       |

| V <sub>OL</sub> <sup>(4)(5)</sup>  |                             | I <sub>OUT</sub> = 4 mA              |                                  |                       | 0.5                              | VDC   |

| V <sub>OH</sub> <sup>(6)</sup>     | Output logic level          | $I_{OUT} = -0.3 \text{ mA}$          | 4.5                              |                       |                                  |       |

| V <sub>OL</sub> <sup>(6)</sup>     |                             | I <sub>OUT</sub> = 0.3 mA            |                                  |                       | 0.5                              | VDC   |

|                                    | HONE AMPLIFIER              | 7 001                                |                                  |                       |                                  |       |

|                                    | Input level                 | Single-ended                         |                                  | 1                     | 15                               | mVrms |

|                                    | Gain                        | Single-ended                         |                                  | 40                    |                                  | dB    |

|                                    | Input resistance            | Single-ended                         | 5                                | 6                     |                                  | kΩ    |

|                                    | Frequency response          | -3 dB                                |                                  | 20                    |                                  | kHz   |

|                                    | SNR                         | 1-kHz, 100-mVrms output              |                                  | 59                    |                                  | dB    |

|                                    | THD+N                       | 1-kHz, 1-Vrms output                 |                                  | -77                   |                                  | dB    |

| MICROPH                            | IONE BIAS GENERATOR         |                                      |                                  |                       |                                  |       |

|                                    | Output voltage              | I <sub>OUT</sub> = -1 mA             | 0.75 V <sub>CC</sub> 1<br>- 0.15 | 75 V <sub>CC</sub> 1  | 0.75 V <sub>CC</sub> 1<br>+ 0.15 | V     |

|                                    | Output source current       |                                      |                                  |                       | 1                                | mA    |

|                                    | Output impedance            |                                      |                                  | 48                    |                                  | Ω     |

|                                    | Output noise voltage        | 100 Hz–20 kHz, with 10-μF decoupling |                                  | 1.8                   |                                  | μVrms |

| REFEREN                            | NCE OUTPUT                  |                                      | I                                |                       | <u> </u>                         |       |

|                                    | Output voltage              | $I_{OUT} = \pm 10 \text{ mA}$        | 0.5 V <sub>CC</sub> 1<br>- 0.15  | 0.5 V <sub>CC</sub> 1 | 0.5 V <sub>CC</sub> 1<br>+ 0.15  | V     |

|                                    | Output source/sink current  |                                      |                                  |                       | 10                               | mA    |

|                                    | Output impedance            |                                      |                                  | 6                     |                                  | Ω     |

|                                    | Output noise voltage        | 100 Hz–20 kHz, with 10-μF decoupling |                                  | 1.8                   |                                  | μVrms |

Pins 10, 11: LRCK, BCK (Schmitt-trigger input with 50-kΩ typical internal pulldown resistor)

Pins 12, 17, 18, 19, 21: DIN, SCKI, SDA, SCL, I2CEN (Schmitt-trigger input, 5-V tolerant)

Pins 9, 20: PDWN, ADR (Schmitt-trigger input with 50-kΩ typical internal pulldown resistor, 5-V tolerant).

Pins 13, 14: DOUT, DOUTS

Pin 18: SDA (Open-drain LOW output)

Pin 3: L/M (3)

<sup>(5)</sup>

<sup>(6)</sup>

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A$  = 25°C,  $V_{CC}1$  =  $V_{CC}2$  =  $V_{CC}3$  = 5 V,  $V_{DD}$  = 3.3 V,  $f_S$  = 48 kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted

|             | PARAMETER                              | TEST CONDITIONS                                         | MIN                  | TYP                   | MAX                  | UNIT     |  |

|-------------|----------------------------------------|---------------------------------------------------------|----------------------|-----------------------|----------------------|----------|--|

| AFE MUL     | TIPLEXER                               |                                                         |                      |                       |                      |          |  |

|             | Input channel                          |                                                         |                      | 2                     |                      | СН       |  |

|             | Input range for full scale             | V <sub>IN</sub> L, V <sub>IN</sub> R                    | 0.1                  | 1                     | 1.5                  | Vrms     |  |

|             | Input Impedance                        | V <sub>IN</sub> L, V <sub>IN</sub> R                    | 22                   | 143                   |                      | kΩ       |  |

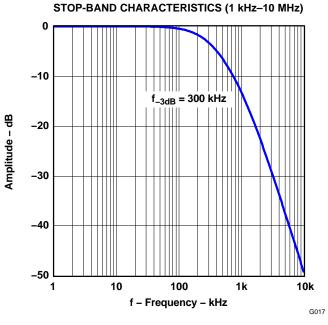

|             | Antialiasing filter frequency response | −3 dB, PGA gain = 0 dB                                  |                      | 300                   |                      | kHz      |  |

|             | Input center voltage (VREF1)           |                                                         |                      | 0.5 V <sub>CC</sub> 1 |                      | V        |  |

| AFE PGA     |                                        |                                                         |                      |                       |                      |          |  |

|             | Gain range                             |                                                         | -4                   | 0                     | 20                   | dB       |  |

|             | Gain step                              |                                                         |                      | 1                     |                      | dB       |  |

|             | Monotonicity                           |                                                         |                      | Ensured               |                      |          |  |

| ADC CHA     | RACTERISTICS                           |                                                         |                      |                       |                      |          |  |

|             | Resolution                             |                                                         |                      | 24                    |                      | Bits     |  |

|             | Full-scale input voltage               | V <sub>IN</sub> L, V <sub>IN</sub> R at PGA gain = 0 dB |                      | 0.6 V <sub>CC</sub> 1 |                      | Vp-p     |  |

| DC Accur    |                                        |                                                         |                      |                       |                      |          |  |

|             | Gain mismatch, channe-to-channel       | Full scale input, V <sub>IN</sub> L, V <sub>IN</sub> R  |                      | ±1                    | ±2                   | % of FSR |  |

|             | Gain error                             | Full scale input, V <sub>IN</sub> L, V <sub>IN</sub> R  |                      | ±2                    | ±4                   | % of FSR |  |

|             | Bipolar-zero error                     | HPF bypass, V <sub>IN</sub> L, V <sub>IN</sub> R        |                      | ±2                    |                      | % of FSR |  |

| Dynamic     | Performance <sup>(7)</sup>             |                                                         |                      |                       |                      |          |  |

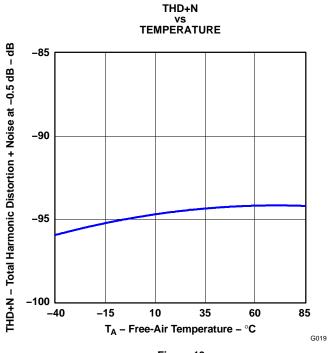

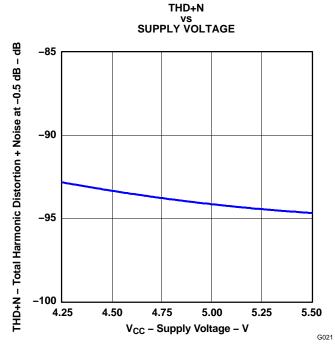

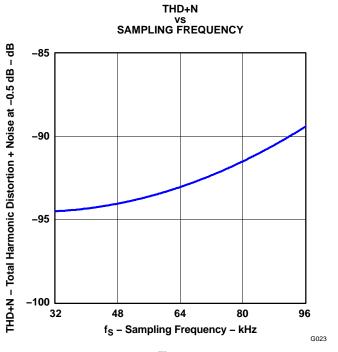

|             |                                        | $f_S = 48 \text{ kHz}, V_{IN} = -0.5 \text{ dB}$        |                      | -94                   | -88                  |          |  |

|             |                                        | $f_S = 96 \text{ kHz}, V_{IN} = -0.5 \text{ dB}$        |                      | -89                   |                      |          |  |

| THD+N       | Total harmonic distortion + noise      | $f_S = 48 \text{ kHz}, V_{IN} = -60 \text{ dB}$         |                      | -38                   |                      | dB       |  |

|             |                                        | $f_S = 96 \text{ kHz}, V_{IN} = -60 \text{ dB}$         |                      | -38                   |                      |          |  |

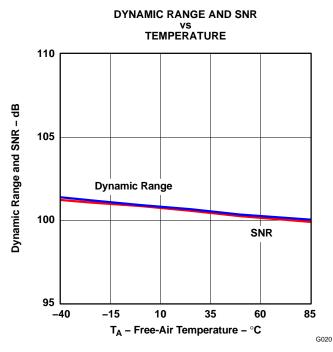

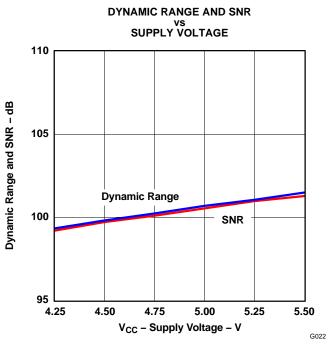

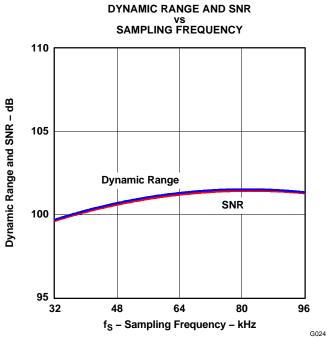

|             |                                        | f <sub>S</sub> = 48 kHz, A-weighted                     | 95                   | 101                   |                      |          |  |

|             | Dynamic range                          | f <sub>S</sub> = 96 kHz, A-weighted                     |                      | 101                   |                      | dB       |  |

|             |                                        | f <sub>S</sub> = 48 kHz, A-weighted                     | 95                   | 101                   |                      |          |  |

| S/N         | Signal-to-noise ratio                  | f <sub>S</sub> = 96 kHz, A-weighted                     |                      | 101                   |                      | dB       |  |

|             | Channel separation                     | f <sub>S</sub> = 48 kHz                                 | 92                   | 98                    |                      |          |  |

|             | (between L-ch and R-ch of line-in)     | f <sub>S</sub> = 96 kHz                                 |                      | 99                    |                      | dB       |  |

|             | Channel separation                     | f <sub>S</sub> = 48 kHz                                 | 92                   | 98                    |                      |          |  |

|             | (between microphone and line-in)       | f <sub>S</sub> = 96 kHz                                 |                      | 99                    |                      | dB       |  |

| Digital Fil | Iter Performance                       | 1                                                       |                      |                       |                      |          |  |

|             | Pass band                              | ±0.05 dB                                                |                      |                       | 0.454 f <sub>S</sub> | Hz       |  |

|             | Stop band                              |                                                         | 0.583 f <sub>S</sub> |                       |                      | Hz       |  |

|             | Pass-band ripple                       |                                                         |                      |                       | ±0.05                | dB       |  |

|             | Stop-band attenuation                  | 0.583 f <sub>S</sub>                                    | -65                  |                       |                      | dB       |  |

|             | Delay time                             |                                                         |                      | 17.4/f <sub>S</sub>   |                      | s        |  |

|             | HPF frequency response                 | -3 dB                                                   |                      | 0.019 f <sub>S</sub>  |                      | MHz      |  |

| DAC CHA     | ARACTERISTICS                          |                                                         |                      | <u> </u>              |                      | I        |  |

|             | Resolution                             |                                                         |                      | 24                    |                      | Bits     |  |

| DC Accur    |                                        |                                                         |                      | ·                     |                      | 1        |  |

|             | Gain mismatch, channel-to-channel      |                                                         |                      | ±1                    | ±2                   | % of FSR |  |

|             | Gain error                             |                                                         |                      | ±2                    | ±6                   | % of FSR |  |

|             | Bipolar zero error                     |                                                         |                      | ±1                    |                      | % of FSR |  |

$f_{IN}$  = 1 kHz, using System Two<sup>TM</sup> audio measurement system by Audio Precision<sup>TM</sup> in the RMS mode with 20-kHz LPF and 400-Hz HPF in the calculation, at PGA gain = 0 dB, for  $V_{IN}L$  and  $V_{IN}R$ .

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted

|                                                             | PARAMETER                         | TEST CONDITIONS                                         | MIN                  | TYP                   | MAX                  | UNIT |  |

|-------------------------------------------------------------|-----------------------------------|---------------------------------------------------------|----------------------|-----------------------|----------------------|------|--|

| Dynamic                                                     | Performance (8)                   |                                                         |                      |                       | 1                    |      |  |

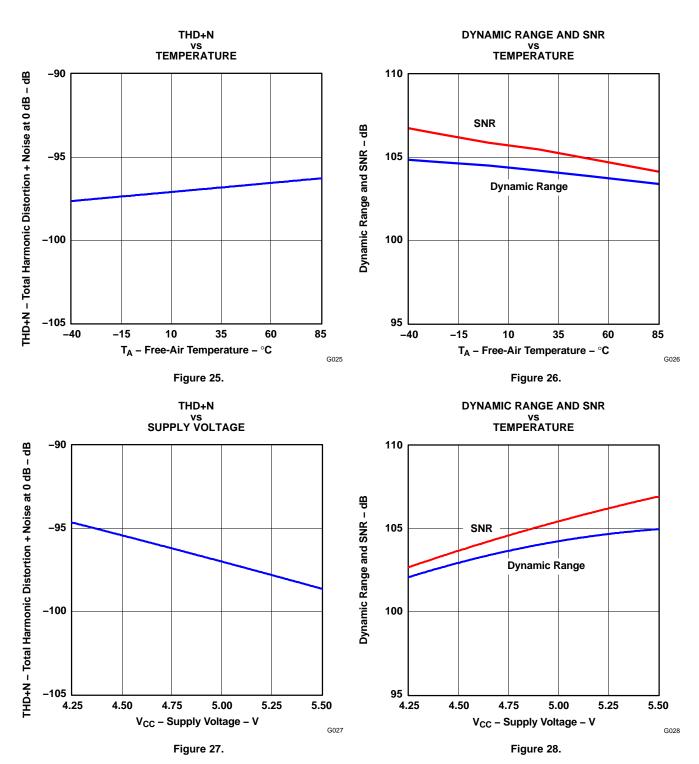

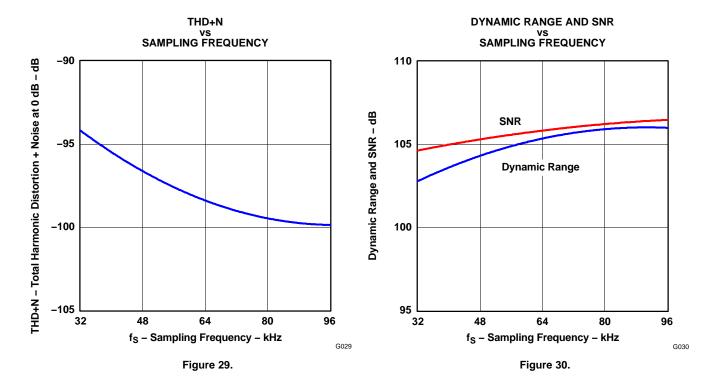

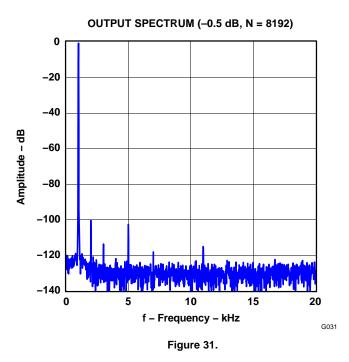

| -                                                           |                                   | f <sub>S</sub> = 48 kHz, V <sub>OUT</sub> = 0 dB        |                      | -97                   | -90                  |      |  |

|                                                             |                                   | f <sub>S</sub> = 96 kHz, V <sub>OUT</sub> = 0 dB        |                      | -99                   |                      |      |  |

| THD+N                                                       | Total harmonic distortion + noise | f <sub>S</sub> = 48 kHz, V <sub>OUT</sub> = -60 dB      |                      | -42                   |                      | dB   |  |

|                                                             |                                   | $f_S = 96 \text{ kHz}, V_{OUT} = -60 \text{ dB}$        |                      | -43                   |                      |      |  |

|                                                             |                                   | f <sub>S</sub> = 48 kHz, EIAJ, A-weighted               | 98                   | 104                   |                      |      |  |

|                                                             | Dynamic range                     | f <sub>S</sub> = 96 kHz, EIAJ, A-weighted               |                      | 106                   |                      | dB   |  |

|                                                             |                                   | f <sub>S</sub> = 48 kHz, EIAJ, A-weighted               | 99                   | 105                   |                      |      |  |

| S/N                                                         | Signal-to-noise ratio             | f <sub>S</sub> = 96 kHz, EIAJ, A-weighted               |                      | 106                   |                      | dB   |  |

|                                                             |                                   | f <sub>S</sub> = 48 kHz                                 | 97                   | 103                   |                      |      |  |

|                                                             | Channel separation                | f <sub>S</sub> = 96 kHz                                 |                      | 104                   |                      | dB   |  |

| Analog O                                                    | Output                            |                                                         |                      |                       |                      |      |  |

|                                                             | Output voltage                    |                                                         |                      | 0.8 V <sub>CC</sub> 2 |                      | Vp-p |  |

|                                                             | Center voltage                    |                                                         |                      | 0.5 V <sub>CC</sub> 2 |                      | V    |  |

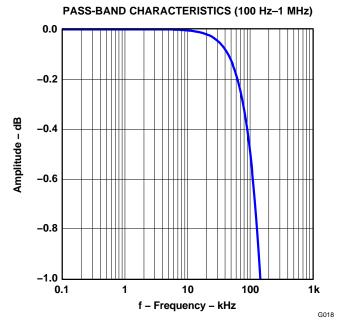

|                                                             | Load impedance                    | AC coupling                                             | 5                    |                       |                      | kΩ   |  |

|                                                             |                                   | f = 20 kHz                                              |                      | -0.03                 |                      |      |  |

|                                                             | LPF frequency response            | f = 40 kHz                                              |                      | -0.20                 |                      | dB   |  |

| Digital Fi                                                  | Iter Performance                  |                                                         |                      |                       |                      |      |  |

|                                                             | Pass band                         | ±0.03 dB                                                |                      |                       | 0.454 f <sub>S</sub> | Hz   |  |

|                                                             | Stop band                         |                                                         | 0.546 f <sub>S</sub> |                       | -                    | Hz   |  |

|                                                             | Pass-band ripple                  |                                                         |                      |                       | ±0.03                | dB   |  |

|                                                             | Stop-band attenuation             | 0.546 f <sub>S</sub>                                    | -50                  |                       |                      | dB   |  |

|                                                             | Delay time                        | 0                                                       |                      | 20/f <sub>S</sub>     |                      | s    |  |

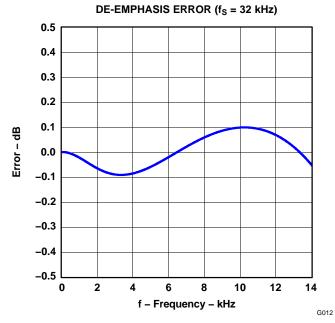

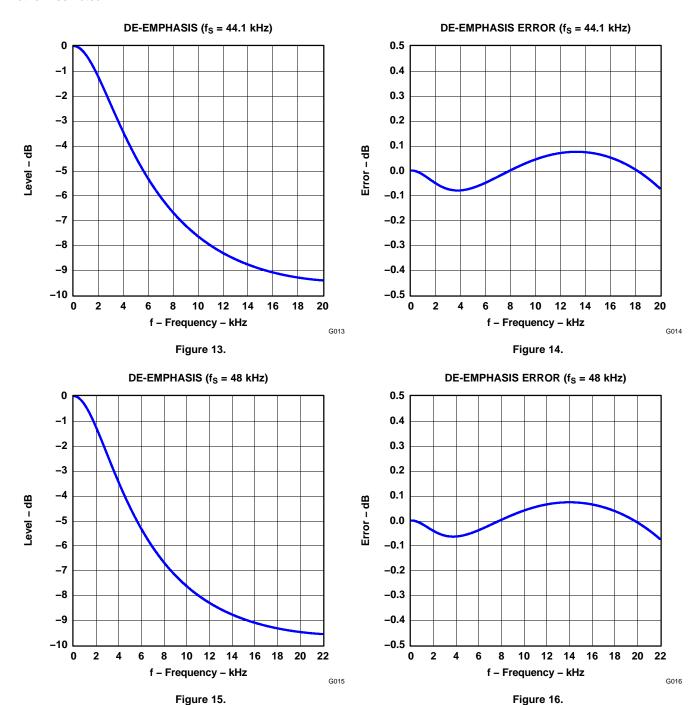

|                                                             | De-emphasis error                 |                                                         |                      | ±0.1                  |                      | dB   |  |

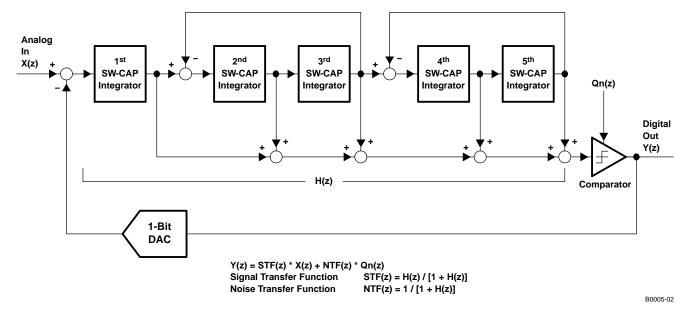

| POWER S                                                     | SUPPLY REQUIREMENTS               |                                                         |                      |                       |                      |      |  |

| V <sub>CC</sub> 1<br>V <sub>CC</sub> 2<br>V <sub>CC</sub> 3 | Voltage range                     |                                                         | 4.25                 | 5                     | 5.5                  | VDC  |  |

| $V_{DD}$                                                    |                                   |                                                         | 3                    | 3.3                   | 3.6                  |      |  |

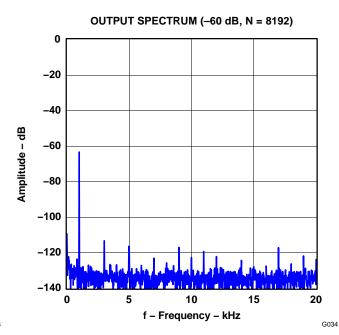

|                                                             |                                   | f <sub>S</sub> = 48 kHz                                 |                      | 39                    | 50                   | Λ    |  |

| I <sub>CC</sub> <sup>(9)</sup>                              |                                   | f <sub>S</sub> = 96 kHz                                 |                      | 41                    |                      | mA   |  |

|                                                             |                                   | Full power down (10)                                    |                      | 300                   |                      | μΑ   |  |

|                                                             | Supply current                    | f <sub>S</sub> = 48 kHz                                 |                      | 10                    | 15                   |      |  |

| I <sub>DD</sub>                                             |                                   | f <sub>S</sub> = 96 kHz                                 |                      | 19                    |                      | mA   |  |

|                                                             |                                   | Full power down <sup>(10)</sup>                         |                      | 90                    |                      | μΑ   |  |

|                                                             | ,                                 | Operation, f <sub>S</sub> = 48 kHz                      |                      | 228                   | 300                  |      |  |

| Power dissipation                                           |                                   | Operation, f <sub>S</sub> = 96 kHz                      |                      | 268                   |                      |      |  |

|                                                             |                                   | ADC operation at f <sub>S</sub> = 48 kHz/DAC power down |                      | 180                   |                      | mW   |  |

|                                                             |                                   | ADC power down/DAC operation at $f_S = 48 \text{ kHz}$  |                      | 63                    |                      |      |  |

|                                                             |                                   | Full power down <sup>(10)</sup>                         |                      | 1.8                   |                      |      |  |

<sup>(8)</sup> f<sub>OUT</sub> = 1 kHz, using System Two audio measurement system by Audio Precision in the RMS mode with 20-kHz LPF and 400-Hz HPF.

(9) I<sub>CC</sub> = I<sub>CC</sub>1 + I<sub>CC</sub>2 + I<sub>CC</sub>3

(10) Halt SCKI, BCK, LRCK.

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A$  = 25°C,  $V_{CC}1$  =  $V_{CC}2$  =  $V_{CC}3$  = 5 V,  $V_{DD}$  = 3.3 V,  $f_S$  = 48 kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted

| PARAMETER                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------------|-----------------|-----|-----|-----|------|

| TEMPERATURE RANGE                  |                 |     |     |     |      |

| Operation temperature              |                 | -40 |     | 85  | °C   |

| θ <sub>JA</sub> Thermal resistance |                 |     | 100 |     | °C/W |

## **DEVICE INFORMATION**

## **BLOCK DIAGRAM**

# **DEVICE INFORMATION (continued)**

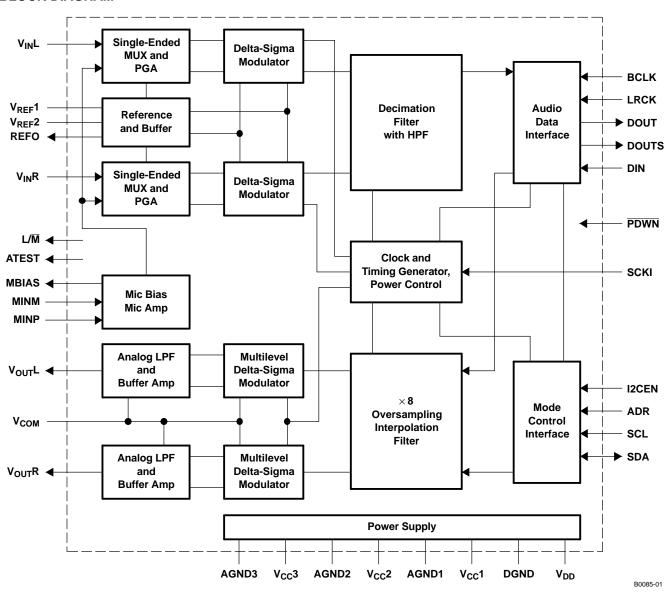

# **PIN ASSIGNMENTS**

#### **RTF PACKAGE** (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| TERM  | TERMINAL |     | DESCRIPTION                                                     |

|-------|----------|-----|-----------------------------------------------------------------|

| NAME  | NO.      | 1/0 | DESCRIPTION                                                     |

| ADR   | 20       | I   | Mode control address select input (1)                           |

| AGND1 | 8        |     | ADC analog ground                                               |

| AGND2 | 22       |     | DAC analog ground                                               |

| AGND3 | 30       |     | Microphone amplifier and bias analog ground                     |

| ATEST | 1        | 0   | Analog test, must be open                                       |

| DGND  | 15       |     | Digital ground                                                  |

| BCK   | 11       | 1   | Audio data bit clock input (2)                                  |

| DIN   | 12       | I   | Audio data digital input (3)                                    |

| DOUT  | 13       | 0   | Audio data digital output                                       |

| DOUTS | 14       | 0   | S/PDIF data digital output                                      |

| I2CEN | 21       | I   | Mode control enable/disable input, active HIGH (3)              |

| L/M   | 3        | 0   | ADC line/microphone select indicator                            |

| LRCK  | 10       | I   | Audio data latch enable input (2)                               |

| MBIAS | 27       | 0   | Microphone bias output/decoupling, 0.75 V <sub>CC</sub> 1       |

| MINM  | 28       | I   | Microphone amplifier input to ADC, inverting                    |

| MINP  | 29       | 1   | Microphone amplifier input to ADC, non-inverting                |

| PDWN  | 9        | I   | ADC and DAC power down control input, active LOW <sup>(1)</sup> |

| REFO  | 32       | 0   | Reference output / decoupling, 0.5 V <sub>CC</sub> 1            |

- Schimtt-trigger input with 50-k $\Omega$  typical internal pulldown resistor, 5-V tolerant

- Schimtt-trigger input with 50-kΩ typical internal pulldown resistor

- (2) (3) Schimtt-trigger input, 5-V tolerant

# DEVICE INFORMATION (continued) TERMINAL FUNCTIONS (continued)

| TERM               | /INAL | 1/0 | DESCRIPTION                                            |

|--------------------|-------|-----|--------------------------------------------------------|

| NAME               | NO.   | I/O | DESCRIPTION                                            |

| SCKI               | 17    | I   | System clock input, 256 f <sub>S</sub> <sup>(3)</sup>  |

| SCL                | 19    | I   | Mode control clock input (3)                           |

| SDA                | 18    | I/O | Mode control data input/output (4)                     |

| V <sub>CC</sub> 1  | 7     |     | ADC analog power supply, 5 V                           |

| V <sub>CC</sub> 2  | 23    |     | DAC analog power supply, 5 V                           |

| V <sub>CC</sub> 3  | 31    |     | Microphone amplifier and bias analog power supply, 5 V |

| $V_{COM}$          | 26    |     | DAC common voltage decoupling, 0.5 V <sub>CC</sub> 2   |

| $V_{DD}$           | 16    |     | Digital power supply, 3.3 V                            |

| V <sub>IN</sub> L  | 2     | I   | Line input to ADC, L-channel                           |

| V <sub>IN</sub> R  | 6     | I   | Line input to ADC, R-channel                           |

| V <sub>OUT</sub> L | 25    | 0   | Analog output from DAC, L-channel                      |

| $V_{OUT}R$         | 24    | 0   | Analog output from DAC, R-channel                      |

| V <sub>REF</sub> 1 | 4     |     | ADC reference 1 voltage output, 0.5 V <sub>CC</sub> 1  |

| V <sub>REF</sub> 2 | 5     |     | ADC reference 2 voltage decoupling, V <sub>CC</sub> 1  |

<sup>(4)</sup> Schimtt-trigger input/open-drain LOW output, 5-V tolerant

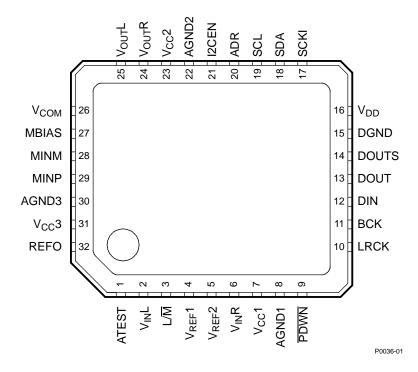

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (ADC SECTION)

All specifications at  $T_A = 25^{\circ}\text{C}$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5 \text{ V}$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , SCKI = 256 $f_S$ , 24-bit data, unless otherwise noted.

# **DIGITAL FILTER**

Figure 2.

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (ADC SECTION) (continued)

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz,  $SCKI = 256f_S$ , 24-bit data, unless otherwise noted.

G005

Figure 5.

Figure 6.

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (ADC SECTION) (continued)

All specifications at  $T_A = 25$ °C,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256 $f_S$ , 24-bit data, unless otherwise noted.

# **ANALOG FILTER (Line Input, PGA Gain = 0 dB)**

#### Figure 7.

# ANTIALIASING FILTER PASS-BAND CHARACTERISTICS

Figure 8.

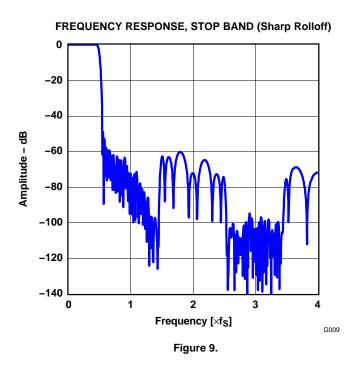

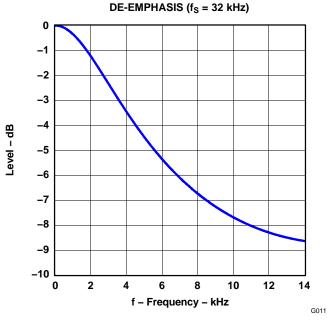

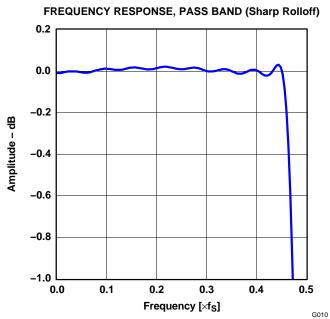

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (DAC SECTION)

All specifications at  $T_A = 25^{\circ}\text{C}$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5 \text{ V}$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , SCKI = 256 $f_S$ , 24-bit data, unless otherwise noted.

## **DIGITAL FILTER**

Figure 11.

Figure 10.

Figure 12.

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (DAC SECTION) (continued)

All specifications at  $T_A = 25$ °C,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256 $f_S$ , 24-bit data, unless otherwise noted.

# TYPICAL PERFORMANCE CURVES OF INTERNAL FILTER (DAC SECTION) (continued)

All specifications at  $T_A = 25^{\circ}\text{C}$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5 \text{ V}$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $f_S = 48 \text{ kHz}$ , SCKI = 256 $f_S$ , 24-bit data, unless otherwise noted.

## **ANALOG FILTER**

Figure 17.

Figure 18.

# **TYPICAL PERFORMANCE CURVES (ADC SECTION)**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted.

# LINE INPUT (at PGA Gain = 0 dB)

Figure 19.

Figure 21.

Figure 20.

Figure 22.

# **TYPICAL PERFORMANCE CURVES (ADC SECTION) (continued)**

All specifications at  $T_A$  = 25°C,  $V_{CC}1$  =  $V_{CC}2$  =  $V_{CC}3$  = 5 V,  $V_{DD}$  = 3.3 V,  $f_S$  = 48 kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted.

Figure 24.

# **TYPICAL PERFORMANCE CURVES (DAC SECTION)**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (DAC SECTION) (continued)**

All specifications at  $T_A$  = 25°C,  $V_{CC}1$  =  $V_{CC}2$  =  $V_{CC}3$  = 5 V,  $V_{DD}$  = 3.3 V,  $f_S$  = 48 kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted.

## **TYPICAL PERFORMANCE CURVES**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted.

# ADC OUTPUT SPECTRUM (Line Input, at PGA Gain = 0 dB)

Figure 32.

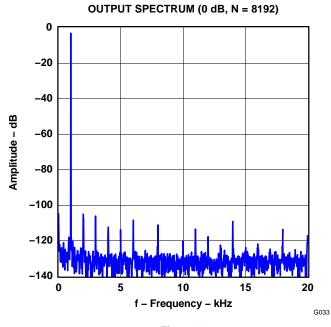

## DAC OUTPUT SPECTRUM

Figure 33.

Figure 34.

# TYPICAL PERFORMANCE CURVES (continued)

All specifications at  $T_A = 25$  °C,  $V_{CC}1 = V_{CC}2 = V_{CC}3 = 5$  V,  $V_{DD} = 3.3$  V,  $f_S = 48$  kHz, SCKI = 256  $f_S$ , 24-bit data, unless otherwise noted.

## **SUPPLY CURRENT**

#### THEORY OF OPERATION

#### ADC SECTION

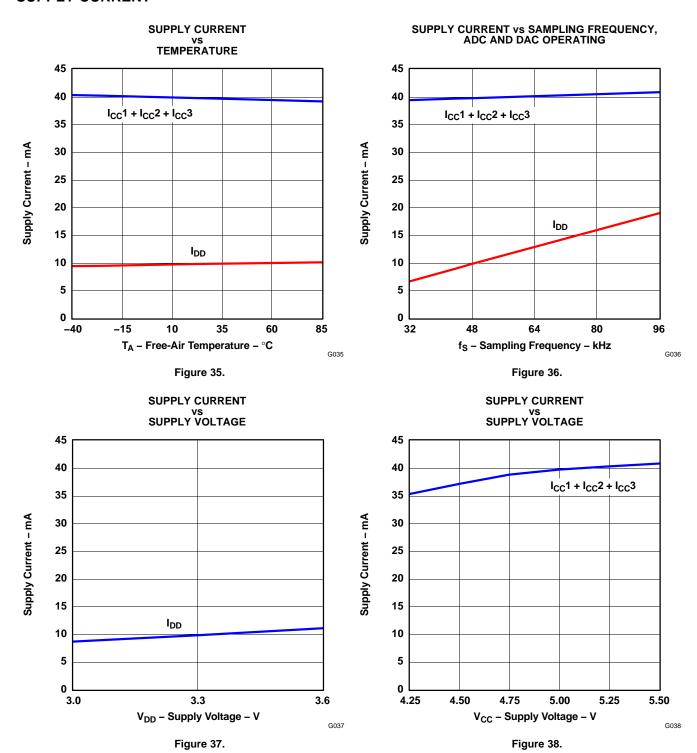

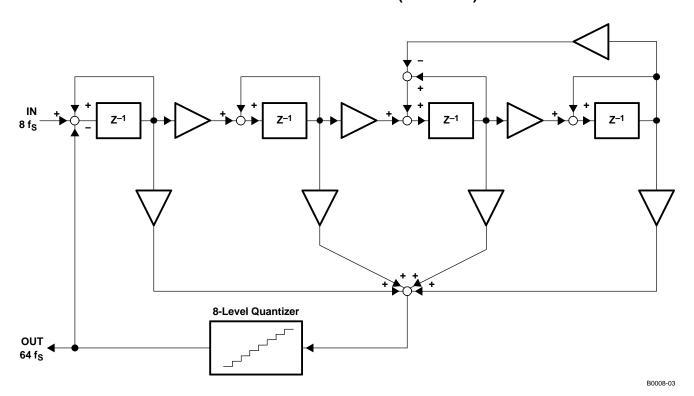

The ADC block consists of a reference circuit, two channels of single-ended to differential converter, a fifth-order delta-sigma modulator with fully differential architecture, a decimation filter with high-pass filter, and a serial interface circuit which is also used as the serial interface for the DAC input signal as shown in the block diagram.

Figure 39 is the block diagram of the fifth-order delta-sigma modulator and transfer function.

An on-chip reference circuit with two external capacitors provides all reference voltages that are needed in the ADC section, and defines the full-scale voltage range of both channels.

An on-chip, single-ended to differential signal converter saves the design, space, and extra parts cost of an external signal converter.

Full differential architecture provides a wide dynamic range and excellent power supply rejection performance.

The input signal is sampled at ×64 oversampling rate and an on-chip antialiasing filter eliminates the need for an external sample-hold amplifier. A fifth-order delta-sigma noise shaper, which consists of five integrators using the switched-capacitor technique and a comparator, shapes the quantization noise generated outside of audio signal band by the comparator and 1-bit DAC.

The high-order delta-sigma modulation randomizes the modulator outputs and reduces idle-tone level.

The 64  $f_S$ , 1-bit stream from the delta-sigma modulator is converted to a 1- $f_S$ , 24-bit digital signal by removing high-frequency noise components with the decimation filter.

The dc component of the signal is removed by the HPF, and the HPF output is converted to a time-multiplexed serial signal through the serial interface.

Figure 39. Block Diagram of Fifth-Order Delta-Sigma Modulator

## **DAC SECTION**

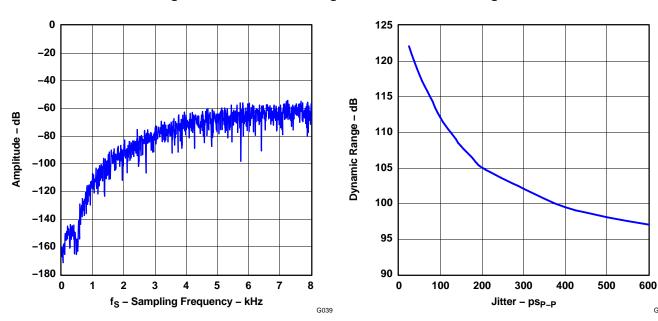

The DAC section is based on the delta-sigma modulator, which consists of an 8-level amplitude quantizer and a fourth-order noise shaper. This section converts the oversampled input data to 8-level delta-sigma format. A block diagram of the 8-level delta-sigma modulator is shown in Figure 40. This 8-level delta-sigma modulator has the advantage of stability and clock jitter over the typical one-bit (2-level) delta-sigma modulator. The combined oversampling rate of the delta-sigma modulator and the internal  $8\times$  interpolation filter is  $64\ f_S$  for all system clocks. The theoretical quantization-noise performance of the 8-level delta-sigma modulator is shown in Figure 41.

# **THEORY OF OPERATION (continued)**

Figure 40. 8-Level Delta-Sigma Modulator Block Diagram

Figure 41. Quantization Noise Spectrum

Figure 42. Clock Jitter

## THEORY OF OPERATION (continued)

#### SYSTEM CLOCK

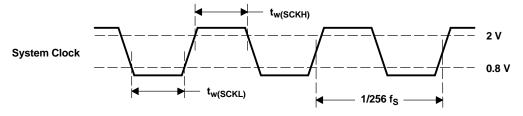

The system clock for the PCM3052A must be 256  $f_S$ , where  $f_S$  is the audio sampling rate, 16 kHz to 96 kHz. Table 1 lists typical system clock frequencies, and Figure 43 illustrates the system clock timing.

**Table 1. Typical System Clock**

| SAMPLING RATE                      | SYSTEM CLOCK FREQUENCY – MHz |

|------------------------------------|------------------------------|

| FREQUENCY (f <sub>S</sub> ) – LRCK | 256 f <sub>S</sub>           |

| 16 kHz                             | 4.096                        |

| 32 kHz                             | 8.192                        |

| 44.1 kHz                           | 11.2896                      |

| 48 kHz                             | 12.288                       |

| 96 kHz                             | 24.576                       |

T0005-10

| PARAMETE                                               | र | MIN | MAX | UNIT |

|--------------------------------------------------------|---|-----|-----|------|

| t <sub>w(SCKH)</sub> System clock pulse duration, HIGH |   | 16  |     | ns   |

| $t_{w(SCKL)}$ System clock pulse duration, LOW         |   | 16  |     | ns   |

Figure 43. System Clock Timing

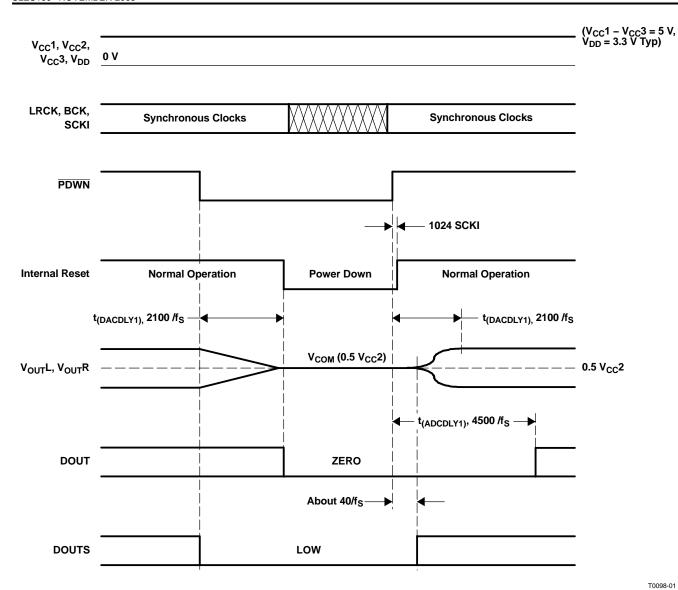

#### POWER SUPPLY ON, EXTERNAL RESET, AND POWER DOWN

The PCM3052A has both an internal power-on-reset circuit and an external reset circuit. The sequences for both resets are shown as follows.

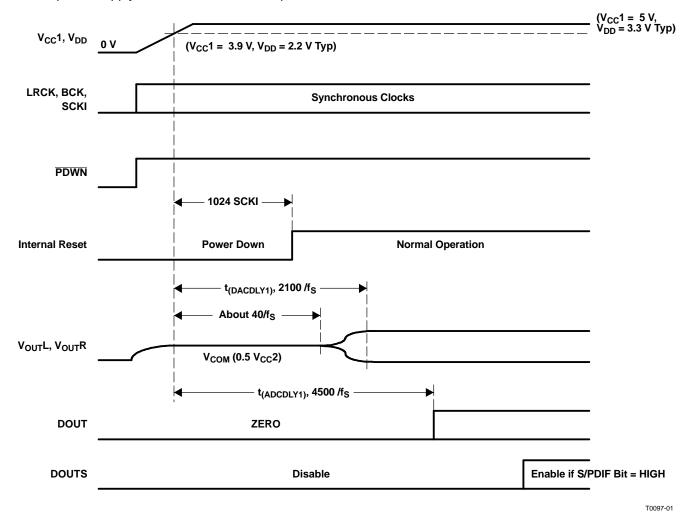

Figure 44 is the timing chart of the internal power-on reset. Two power-on-reset circuits are implemented, one each for for  $V_{CC}1$  and  $V_{DD}$ . Initialization (reset) is performed automatically at the time when  $V_{CC}1$  and  $V_{DD}$  exceed 3.9 V (typical) and 2.2 V (typical), respectively.

Internal reset is released after 1024 SCKI from power-on-reset release, and the PCM3052A begins normal operation.  $V_{OUT}L$  and  $V_{OUT}R$  from the DAC are forced to the  $V_{COM}$  (= 0.5  $V_{CC}2$ ) level as  $V_{CC}2$  rises. When synchronization between SCKI, BCK, and LRCK is maintained,  $V_{OUT}L$  and  $V_{OUT}R$  go into the fade-in sequence. Then  $V_{OUT}L$  and  $V_{OUT}R$  provide outputs corresponding to DIN after  $t_{(DACDLY1)} = 2100/f_S$  from power-on-reset release. On the other hand, DOUT from the ADC provides an output corresponding to  $V_{IN}L$  and  $V_{IN}R$  after  $t_{(ADCDLY1)} = 4500/f_S$  from power-on-reset release. If synchronization is not maintained, the internal reset is not released, and operation is kept in the power-down mode. After resynchronization, the DAC goes into the fade-in sequence, and the ADC goes into normal operation after internal initialization.

DOUTS can provide S/PDIF data after the power-on-reset release if the SPDIF bit is HIGH (see serial control port for mode control section).

Figure 45 shows timing chart for external reset. The PDWN pin (pin 9) initiates external forced reset when PDWN = LOW, and it provides the power-down mode, which is the lowest power-dissipation state in the PCM3052A.

When  $\overline{PDWN}$  transitions from HIGH to LOW while SCKI, BCK, and LRCK are synchronized,  $V_{OUT}L$  and  $V_{OUT}R$  are faded out and forced into  $V_{COM}$  (= 0.5  $V_{CC}2$ ) level after  $t_{DACDLY1}$  = 2100/f<sub>S</sub>. At the same time as the internal reset becomes LOW, DOUT becomes ZERO, the PCM3052A enters the power-down mode. To return to normal operation, set  $\overline{PDWN}$  to HIGH. Then the power-on reset sequence, Figure 44, is performed.

DOUTS is driven LOW immediately after PDWN is asserted and recovers about 40/f<sub>S</sub> following PDWN release.

#### Notes:

- 1. Large pop noises can be generated on  $V_{OUT}L$  and  $V_{OUT}R$  if the power supply is turned off during normal operation.

- 2. To switch PDWN during fade-in or fade-out causes an immediate change between fade-in and fade-out.

- 3. Changing mode controls during normal operation can degrade analog performance. It is recommended that mode controls be changed through the serial control port, and that changing or stopping the clock, switching the power supply off, etc., be done in the power-down mode.

Figure 44. DAC Output and ADC Output for Power-On Reset

Figure 45. DAC Output and ADC Output for External Reset (PDWN Pin)

24

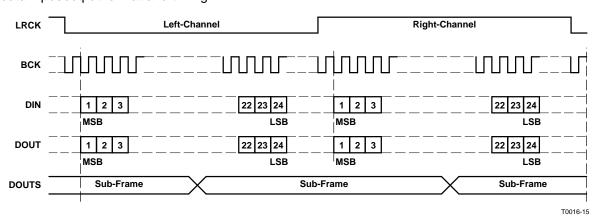

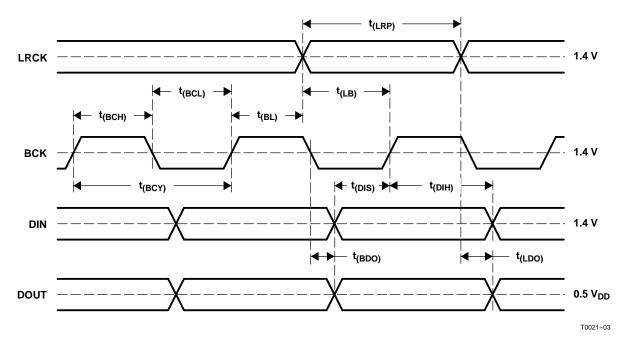

## **PCM AUDIO INTERFACE**

Digital audio data is interfaced to the PCM3052A on LRCK (pin 10), BCK (pin 11), DIN (pin 12), DOUT (pin 13), and DOUTS (pin 14). The PCM3052A can accept 24-bit I<sup>2</sup>S format only. In case of AC-3 type output data for DOUTS, bits 17 to 24 of DIN must be held LOW. See the *Digital Audio Interface Transmitter (DIT)* section of this data sheet.

**Table 2. Audio Data Format**

| DATA FORMAT                         |  |

|-------------------------------------|--|

| 24-bit, MSB-first, I <sup>2</sup> S |  |

The PCM3052A accepts only 64 clocks of BCK during one clock of LRCK. Figure 46 and Figure 47 illustrate audio data input/output format and timing.

Figure 46. Audio Data Input/Output Format

|                  | PARAMETER                             | MIN | MAX | UNIT |

|------------------|---------------------------------------|-----|-----|------|

| t <sub>BCY</sub> | BCK pulse cycle time                  | 160 |     | ns   |

| t <sub>BCH</sub> | BCK pulse duration, HIGH              | 70  |     | ns   |

| t <sub>BCL</sub> | BCK pulse duration, LOW               | 70  |     | ns   |

| t <sub>BL</sub>  | BCK rising edge to LRCK edge          | 20  |     | ns   |

| $t_{LB}$         | LRCK edge to BCK rising edge          | 20  |     | ns   |

| t <sub>LRP</sub> | LRCK pulse duration                   | 4.2 |     | μs   |

| t <sub>DIS</sub> | DIN setup time to BCK rising edge     | 20  |     | ns   |

| t <sub>DIH</sub> | DIN hold time to BCK rising edge      | 20  |     | ns   |

| $t_{BDO}$        | DOUT delay time from BCK falling edge |     | 20  | ns   |

| $t_{LDO}$        | DOUT delay time from LRCK edge        |     | 20  | ns   |

| t <sub>R</sub>   | Rising time of all signals            |     | 10  | ns   |

| t <sub>F</sub>   | Falling time of all signals           |     | 10  | ns   |

NOTE: Load capacitance at DOUT is 20 pF. Rising and falling time is measured from 10% to 90% of IN/OUT signal swing.

Figure 47. Audio Data Input/Output Timing

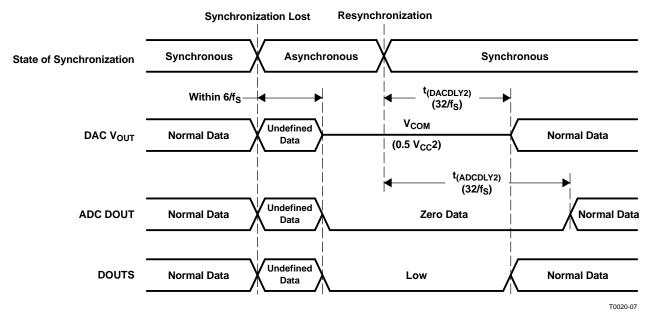

#### SYNCHRONIZATION WITH DIGITAL AUDIO SYSTEM

The PCM3052A operates with LRCK and BCK synchronized to the system clock in slave mode. The PCM3052A does not need specific phase relationship among LRCK, BCK, and the system clock, but does require the synchronization of LRCK, BCK, and the system clock.

If the relationship between system clock and LRCK changes more than  $\pm 6$  BCKs during one sample period due to LRCK jitter, etc., internal operation of DAC halts within  $6/f_S$ , and the analog output is forced to  $0.5~V_{CC}2$  until re-synchronization of the system clock to LRCK and BCK has completed and then the time of  $t_{(DACDLY2)}$  has elapsed.

DOUTS is also held LOW during the same period.

Internal operation of the ADC also halts within  $6/f_S$ , and digital output is forced into ZERO code until re-synchronization of the system clock to LRCK and BCK has completed and then the time of  $t_{(ADCDLY2)}$  has elapsed.

In case of changes less than  $\pm 5$  BCKs, re-synchronization does not occur and the previously described analog/digital output control and discontinuity does not occur.

Figure 48 illustrates the DAC analog output, ADC digital output, and DOUTS output for loss of synchronization.

During undefined data, the PCM3052A can generate some noise in audio signal. Also, the transition of normal to undefined data and undefined or zero data to normal creates a discontinuity of data on analog and digital outputs, which could generate some noise in audio signal.

Figure 48. DAC Output and ADC Output for Loss of Synchronization

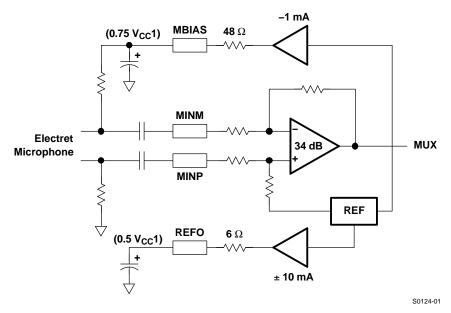

## MICROPHONE AMPLIFIER AND MICROPHONE BIAS GENERATOR

The PCM3052A has a built-in, high-performance differential-input microphone amplifier with 34-dB gain, 5-k $\Omega$  (minimum) input resistance, and 59-dB SNR at 100-mVrms output. Bandwidth is 20 kHz for -3-dB attenuation. The PCM3052A also has a low-noise microphone bias generator with 0.75-V<sub>CC</sub>1 and 1-mA current-source capability for electret microphones. Output impedance is 48  $\Omega$  for external noise reduction. The output of the microphone amplifier and the line input are connected as inputs to the multiplexer. The serial control port can be used to control which input the multiplexer selects (see Figure 50).

## REFERENCE OUTPUT

The PCM3052A has a reference output pin (RFFO, pin 32) to supply reference voltage (0.5  $V_{CC}1$ ) to external components. The pin has 10-mA sink/source capability with 6- $\Omega$  output impedance.

Figure 49. Microphone Amplifier, Microphone Bias Generator, and Reference Output

# LINE AND MICROPHONE INPUT SELECT INDICATOR

The PCM3052A employs an indicator pin ( $L/\overline{M}$ , pin 3) to show which analog input is selected, line or microphone.

**Table 3. Line and Microphone Select Indicator**

| L/M  | LINE/MIC SELECT<br>INDICATOR |

|------|------------------------------|

| LOW  | Microphone                   |

| HIGH | Line                         |

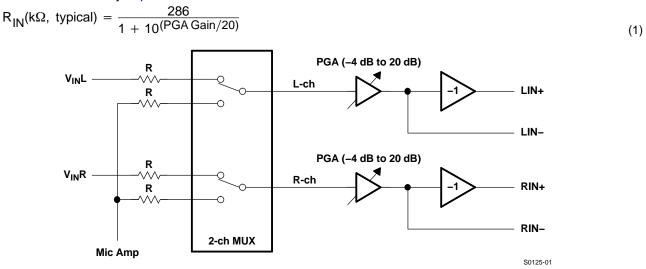

#### **MULTIPLEXER AND PGA**

The PCM3052A has built-in analog front-end circuit which is shown in Figure 50. Multiplexer input and PGA gain are selected by mode control via the serial port, as shown in the Serial Control Port for Mode Control section. The full-scale input voltage range is 0.1 Vrms to 1.5 Vrms, and it can be adjusted to an adequate level for following the ADC sections.

$V_{IN}L$  and  $V_{IN}R$  input resistance is maintained above 22 k $\Omega$  for all PGA gains. The input resistance value for each gain can be calculated by Equation 1.

Figure 50. Multiplexer and PGA

## **ANALOG OUTPUTS FROM DAC**

The PCM3052A has two independent output channels,  $V_{OUT}L$  and  $V_{OUT}R$ . These are unbalanced outputs, each capable of driving 4 Vp-p (typical) into a 5-k $\Omega$  ac-coupled load. The internal output amplifiers for  $V_{OUT}L$  and  $V_{OUT}R$  are biased to the dc common-mode (or bipolar zero) voltage, equal to 0.5  $V_{CC}2$

The output amplifiers include an RC continuous-time filter, which helps to reduce the out-of-band noise energy present at the DAC outputs due to the noise-shaping characteristics of the PCM3052A delta-sigma modulators. The frequency response of this filter is shown in the typical performance curves. By itself, this filter is not adequate to attenuate the out-of-band noise to an acceptable level for many applications. An external low-pass filter is required to provide sufficient out-of-band noise rejection. Further discussion of DAC post-filter circuits is provided in the PCM1742 data sheet (SBAS176).

#### **VCOM OUTPUT FOR DAC**

One unbuffered common-mode voltage output pin,  $V_{COM}$  (pin 26), is brought out for decoupling purposes. This pin is nominally biased to a dc voltage level equal to 0.5  $V_{CC}$ 2. This pin can be used to bias external circuits. Output resistance of this pin is 21 k $\Omega$  (typical).

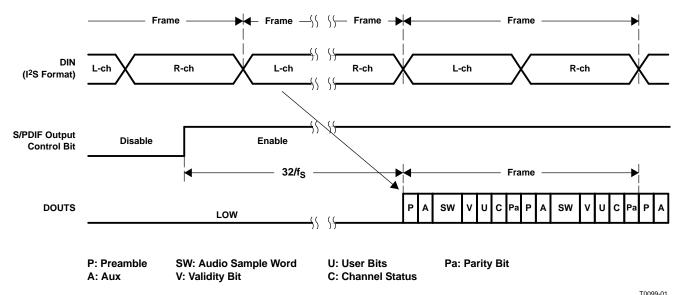

#### **DIGITAL AUDIO INTERFACE TRANSMITTER (DIT)**

The PCM3052A employs S/PDIF output from DOUTS (pin 14). The data (I<sup>2</sup>S format only) from DAC digital data input (DIN, pin 12) is encoded to S/PDIF format with preambles according to IEC958. S/PDIF output is controlled through the serial control port. The output data type (linear PCM or AC-3) can be also selected through the serial control port. For the output data type of AC-3, the word length is limited to 16 bits in the PCM3052A. Therefore, bits 17 to 24 in the I<sup>2</sup>S format data must be set to LOW.

Each bit after the audio sample word is assigned in the PCM3052A as follows.

Validity bit: Writable through serial control port

User data: Fixed to 0

Channel status [0]: Fixed to 0 (consumer use)

Channel status [1]: Writable through serial control port (audio sample word type)

Channel status [2]: Writable through serial control port (copyright flag)

Channel status [3:5]: Writable through serial control port (additional format information)

Channel status [6:7]: Fixed to 00 (mode 0)

Channel status [8:15]: Writable through serial control port (category code)

Channel status [16:19]: Fixed to 0000 (source number)

Channel status [20:23]: Fixed to 0000 (channel number)

Channel status [24:27]: Writable through serial control port (sampling frequency)

Channel status [28:29]: Writable through serial control port (clock accuracy)

Channel status [30:31]: Fixed to 00

Channel status [32:35]: Writable through serial control port (word length)

Channel status [36:191]: Fixed to all 0s

Parity bit: Even parity for preceding data from preamble to channel status bit

S/PDIF output timing is shown in Figure 51. The S/PDIF block starts with a preamble after 32/f<sub>S</sub> from the frame where S/PDIF output control bit becomes HIGH. The behavior of DOUTS for power-on reset, external reset, and loss of synchronization is shown in Figure 44, Figure 45, and Figure 48, respectively.

Figure 51. S/PDIF Output Timing

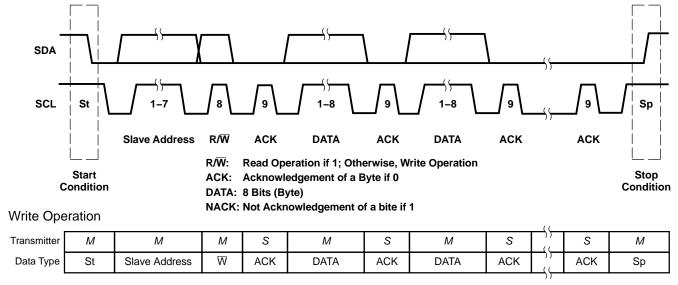

#### SERIAL CONTROL PORT FOR MODE CONTROL

The several built-in functions of the PCM3052A can be controlled through the I<sup>2</sup>C format serial-control port, SDA (pin 18) and SCL (pin 19). The PCM3052A supports the I<sup>2</sup>C serial bus and the data transmission protocol for standard mode as a slave device. This protocol is explained in I<sup>2</sup>C specification 2.0.

Serial control is available even during the power-down state and without a system clock, except when the MRST bit = 0 or I2CEN (pin 21) = LOW.

#### **Slave Address**

| MSB |   |   |   |   |   |     | LSB |

|-----|---|---|---|---|---|-----|-----|

| 1   | 0 | 0 | 0 | 1 | 1 | ADR | R/W |

The PCM3052A has seven bits for its own slave address. The first six bits (MSBs) of the slave address are factory preset to 100011. The next bit of the address byte is the device select bit which can be user-defined by ADR (pin 20). A maximum of two PCM3052As can be connected on the same bus at one time. Each PCM3052A responds when it receives its own slave address.

#### **Packet Protocol**

A master device must control packet protocol, which consists of start condition, slave address with read/write bit, data if write or acknowledgement if read, and stop condition. The PCM3052A supports slave receiver function.

M: Master Device S: Slave Device

St: Start Condition  $\overline{W}$ : Write Sp: Stop Condition

T0049-04

Figure 52. Basic I<sup>2</sup>C Framework

## **Write Operation**

The PCM3052A supports receiver function. A master can write to any PCM3052A registers using single or multiple accesses. The master sends a PCM3052A slave address with a write bit, a register address, and the data. If multiple access is required, the address is that of the starting register, followed by the data to be transferred. When the data are received properly, the index register is incremented by 1 automatically. When the index register reaches 50h, the next value is 41h. When undefined registers are accessed, the PCM3052A does not send an acknowledgement. Figure 53 is a diagram of the write operation. The register address and the write data are 8 bits and MSB-first format.

| Transmitter | М  | М             | М | S   | М           | S   | М            | S   | М            | S   | <b>-</b> √}- | S   | М  |

|-------------|----|---------------|---|-----|-------------|-----|--------------|-----|--------------|-----|--------------|-----|----|

| Data Type   | St | Slave Address | W | ACK | Reg Address | ACK | Write Data 1 | ACK | Write Data 2 | ACK | ( <u></u>    | ACK | Sp |

M: Master Device S: Slave Device

St: Start Condition ACK: Acknowledge W: Write Sp: Stop Condition

R0002-03

Figure 53. Framework for Write Operation

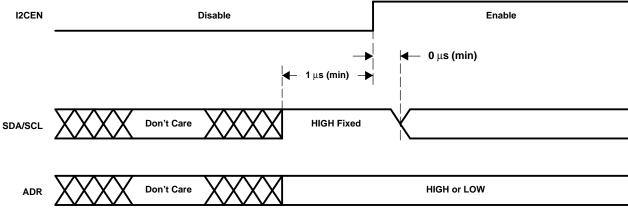

## Serial Control Enable/Disable

The PCM3052A supports I<sup>2</sup>C serial control enable/disable function by I2CEN (pin 21) to avoid an unstable start condition. When the I2CEN pin transitions from LOW to HIGH, both SDA (pin 18) and SCL (pin 19) must be HIGH stable and the ADR (pin 20) must be also stable.

While I2CEN = LOW, the write operation is disabled. A timing chart of I2CEN is shown in Figure 54.

Figure 54. I2CEN Timing Chart

T0100-01

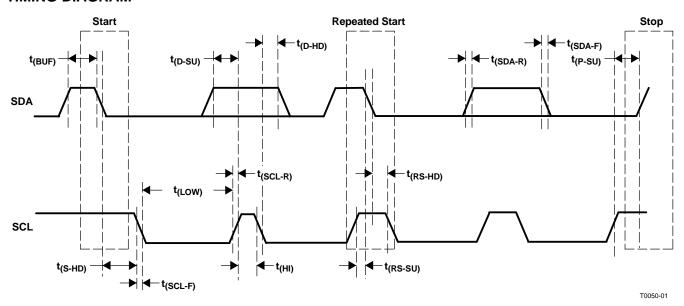

## **TIMING DIAGRAM**

|                                             | PARAMETER                                                                             | CONDITIONS    | MIN                     | MAX  | UNIT |

|---------------------------------------------|---------------------------------------------------------------------------------------|---------------|-------------------------|------|------|

| f <sub>(SCL)</sub>                          | SCL clock frequency                                                                   | Standard mode |                         | 100  | kHz  |

| t <sub>(BUF)</sub>                          | Bus free time between STOP and START condition                                        | Standard mode | 4.7                     |      | μs   |

| t <sub>(LOW)</sub>                          | Low period of the SCL clock                                                           | Standard mode | 4.7                     |      | μs   |

| t <sub>(HI)</sub>                           | High period of the SCL clock                                                          | Standard mode | 4                       |      | μs   |

| t <sub>RS-SU</sub>                          | Setup time for START/repeated START condition                                         | Standard mode | 4.7                     |      | μs   |

| t <sub>(S-HD)</sub><br>t <sub>(RS-HD)</sub> | Hold time for START/repeated START condition                                          | Standard mode | 4                       |      | μs   |

| t <sub>(D-SU)</sub>                         | Data setup time                                                                       | Standard mode | 250                     |      | ns   |

| t <sub>(D-HD)</sub>                         | Data hold time                                                                        | Standard mode | 0                       | 900  | ns   |

| t <sub>(SCL-R)</sub>                        | Rise time of SCL signal                                                               | Standard mode | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SCL-R1)</sub>                       | Rise time of SCL signal after a repeated START condition and after an acknowledge bit | Standard mode | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SCL-F)</sub>                        | Fall time of SCL signal                                                               | Standard mode | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SDA-R)</sub>                        | Rise time of SDA signal                                                               | Standard mode | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SDA-F)</sub>                        | Fall time of SDA signal                                                               | Standard mode | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(P-SU)</sub>                         | Setup time for STOP condition                                                         | Standard mode | 4                       |      | μs   |

| C <sub>B</sub>                              | Capacitive load for SDA and SCL line                                                  |               |                         | 400  | pF   |

| V <sub>NH</sub>                             | Noise margin at high level for each connected device (including hysteresis)           | Standard mode | 0.2 V <sub>DD</sub>     |      | V    |

Figure 55. Control Interface Timing

#### MODE CONTROL REGISTERS

## **User-Programmable Mode Controls**

The PCM3052A has several user programmable functions which are accessed via control registers. The registers are programmed using the I<sup>2</sup>C serial control port, which was previously discussed in this data sheet. Table 4 lists the available mode control functions, along with their reset default conditions and associated register addresses. The register map is shown in Table 5.

# **Table 4. User-Programmable Mode Controls**

| FUNCTION                                                          | RESET DEFAULT                           | REGISTER  | BIT(S)             |

|-------------------------------------------------------------------|-----------------------------------------|-----------|--------------------|

| Digital attenuation control, 0 dB to -63 dB in 0.5-dB steps (DAC) | 0 dB, no attenuation                    | 65 and 66 | AT1[7:0], AT2[7:0] |

| Mode control register reset (ADC and DAC)                         | Normal operation                        | 67        | MRST               |

| System reset (ADC and DAC)                                        | Normal operation                        | 67        | SRST               |

| ADC power-save control (ADC)                                      | Normal operation                        | 67        | ADPSV              |

| DAC Power Save Control (DAC)                                      | Normal operation                        | 67        | DAPSV              |

| Soft-mute control (DAC)                                           | Mute disabled                           | 68        | MUT[2:1]           |

| Oversampling rate control (DAC)                                   | 64-f <sub>S</sub> oversampling          | 68        | OVR1               |

| De-emphasis function control (DAC)                                | De-emphasis disabled                    | 69        | DM12               |

| De-emphasis sampling rate selection (DAC)                         | 48 kHz                                  | 69        | DMF[1:0]           |

| Digital filter rolloff control (DAC)                              | Sharp rolloff                           | 70        | FLT0               |

| Output phase select (DAC)                                         | Normal                                  | 71        | DREV               |

| Multiplexer input channel control (ADC)                           | LINE IN                                 | 72        | AML                |

| PGA gain control (ADC)                                            | -4 dB                                   | 72        | PG[4:0]            |

| HPF bypass control (ADC)                                          | HPF enabled                             | 75        | BYP                |

| DAC output control (DAC)                                          | Disabled                                | 77        | DACMSK             |

| Additional format information (DIT)                               | Two audio channels without pre-emphasis | 77        | AFI[5:3]           |

| Copyright flag (DIT)                                              | Asserted                                | 77        | COPY               |

| Audio sample word type (DIT)                                      | PCM                                     | 77        | AUDIO              |

| DIT output control (DIT)                                          | Disable                                 | 77        | DITMSK             |

| Category code (DIT)                                               | General                                 | 78        | CAT[15:8]          |

| Clock accuracy (DIT)                                              | Level II                                | 79        | CLK[29:28]         |

| Sampling frequency (DIT)                                          | 44.1kHz                                 | 79        | SF[27:24]          |

| Validity bit for L-channel (DIT)                                  | Valid                                   | 80        | VALIDL             |

| Validity bit for R-channel (DIT)                                  | Valid                                   | 80        | VALIDR             |

| S/PDIF output control (DIT)                                       | Disabled                                | 80        | SPDIF              |

| Word Length (DIT)                                                 | 24 bits                                 | 80        | WL[35:32]          |

# Table 5. Register Map

|                 |               | RE  | GISTE | R ADE | RESS | REGISTER ADDRESS |     |    |    |                    |                    |                    |                    |                    | DATA               |                    |                    |  |  |  |  |  |

|-----------------|---------------|-----|-------|-------|------|------------------|-----|----|----|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|--|

| IDX<br>(B8–B14) | REGIS-<br>TER | B15 | B14   | B13   | B12  | B11              | B10 | В9 | В8 | В7                 | В6                 | В5                 | В4                 | В3                 | B2                 | B1                 | В0                 |  |  |  |  |  |

| 41h             | 65            | 0   | 1     | 0     | 0    | 0                | 0   | 0  | 1  | AT17               | AT16               | AT15               | AT14               | AT13               | AT12               | AT11               | AT10               |  |  |  |  |  |

| 42h             | 66            | 0   | 1     | 0     | 0    | 0                | 0   | 1  | 0  | AT27               | AT26               | AT25               | AT24               | AT23               | AT22               | AT21               | AT20               |  |  |  |  |  |

| 43h             | 67            | 0   | 1     | 0     | 0    | 0                | 0   | 1  | 1  | MRST               | SRST               | ADPSV              | DAPSV              | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> |  |  |  |  |  |

| 44h             | 68            | 0   | 1     | 0     | 0    | 0                | 1   | 0  | 0  | RSV <sup>(1)</sup> | OVR1               | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | MUT2               | MUT1               |  |  |  |  |  |

| 45h             | 69            | 0   | 1     | 0     | 0    | 0                | 1   | 0  | 1  | RSV <sup>(1)</sup> | DMF1               | DMF0               | DM12               | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> |  |  |  |  |  |

| 46h             | 70            | 0   | 1     | 0     | 0    | 0                | 1   | 1  | 0  | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | FLT0               | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> | 1                  | RSV <sup>(1)</sup> | RSV <sup>(1)</sup> |  |  |  |  |  |

| 47h             | 71            | 0   | 1     | 0     | 0    | 0                | 1   | 1  | 1  | RSV <sup>(1)</sup> | DREV               |  |  |  |  |  |