SLOS331C - AUGUST 2000 - REVISED MARCH 2007

- Minimal External Components Required

- 1.6-V to 3.6-V Supply Voltage Range

- 50-mW Stereo Output

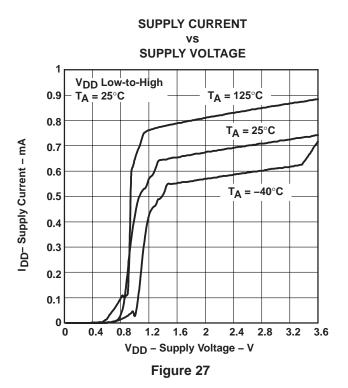

- Low Supply Current . . . 0.75 mA

- Low Shutdown Current . . . 50 nA

- Gain Set Internally to 2 dB

- Pop Reduction Circuitry

- Internal Mid-Rail Generation

- Thermal and Short-Circuit Protection

- Surface-Mount Packaging

- 3-mm × 5-mm MSOP Package (DGN)

- 5-mm × 6-mm SOIC Package (D)

- 2,5-mm × 2,5-mm MicroStar Junior™ BGA Package (ZQY)

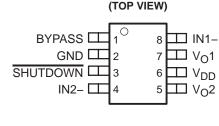

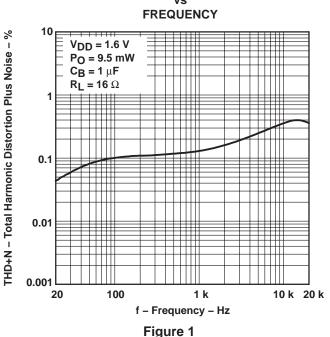

D or DGK PACKAGE

### description

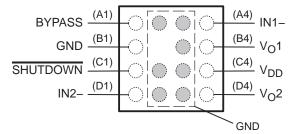

The TPA6101A2 is a stereo audio power amplifier packaged in an 8-pin SOIC package, an 8-pin MSOP package, or a 15-ball BGA package, capable of delivering 50 mW of continuous RMS power per channel into  $16-\Omega$  loads. Amplifier gain is internally set to 2 dB (inverting) to save board space by eliminating six external resistors.

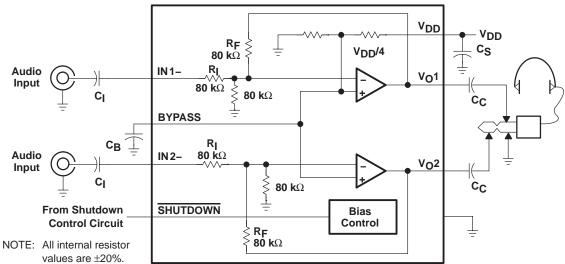

The TPA6101A2 is optimized for battery applications because of its low supply current, shutdown current, and THD+N. To obtain the low-supply-voltage range, the TPA6101A2 biases BYPASS to  $V_{DD}/4$ .

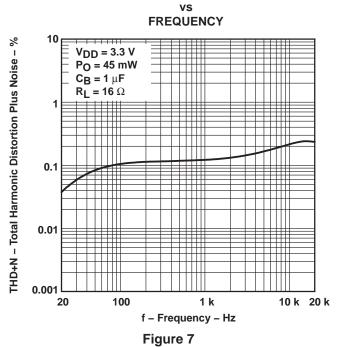

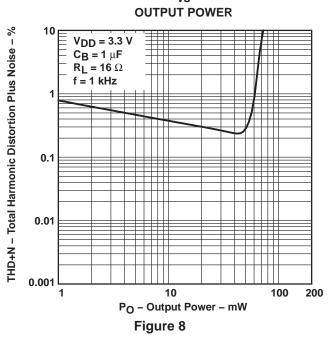

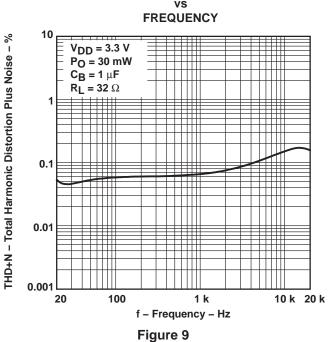

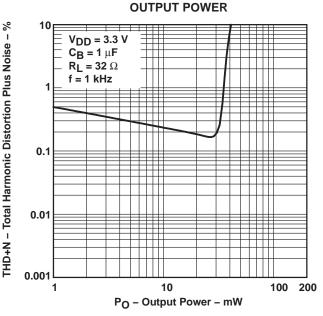

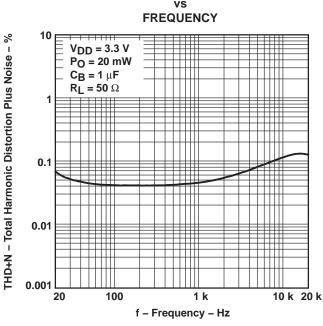

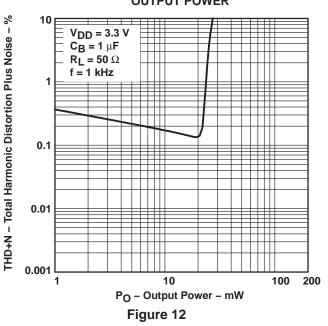

When driving a  $16-\Omega$  load with 40-mW output power from 3.3 V, THD+N is 0.08% at 1 kHz, and less than 0.2% across the audio band of 20 Hz to 20 kHz. For 30 mW into  $32-\Omega$  loads, the THD+N is reduced to less than 0.06% at 1 kHz, and is less than 0.3% across the audio band of 20 Hz to 20 kHz.

### typical application circuit

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

MicroStar BGA is a trademark of Texas Instruments.

#### **AVAILABLE OPTIONS**

| ı  | Τ.            | F                 | PACKAGED DEVICE |               | MSOP          | BGA           |

|----|---------------|-------------------|-----------------|---------------|---------------|---------------|

| TA |               | SMALL OUTLINE (D) | MSOP (DGK)      | BGA (ZQY)     | SYMBOLIZATION | SYMBOLIZATION |

| ı  | -40°C to 85°C | TPA6101A2D        | TPA6101A2DGK    | TPA6101A2ZQYR | AJM           | AAQI          |

### **Terminal Functions**

| TERM             | INAL          |    |     |                                                                                                                                                                           |  |

|------------------|---------------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  | N(            | 0. | 1/0 | DESCRIPTION                                                                                                                                                               |  |

| NAME             | D,<br>DGK ZQY |    | 20  |                                                                                                                                                                           |  |

| BYPASS           | 1             | A1 | I   | Tap to voltage divider for internal mid-supply bias supply. BYPASS is set at $V_{DD}/4$ . Connect to a 0.1- $\mu$ F to 1- $\mu$ F low-ESR capacitor for best performance. |  |

| GND              | 2             | B1 | -   | GND is the ground connection.                                                                                                                                             |  |

| IN1-             | 8             | A4 | _   | IN1- is the inverting input for channel 1.                                                                                                                                |  |

| IN2-             | 4             | D1 | _   | IN2- is the inverting input for channel 2.                                                                                                                                |  |

| SHUTDOWN         | 3             | C1 | _   | Active-low input. When held low, the device is placed in a low-supply-current mode.                                                                                       |  |

| $V_{DD}$         | 6             | C4 | ı   | V <sub>DD</sub> is the supply voltage terminal.                                                                                                                           |  |

| V <sub>O</sub> 1 | 7             | В4 | 0   | O1 is the audio output for channel 1.                                                                                                                                     |  |

| V <sub>O</sub> 2 | 5             | D4 | 0   | V <sub>O</sub> 2 is the audio output for channel 2.                                                                                                                       |  |

### absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage, V <sub>DD</sub>                              | 4 V                                       |

|--------------------------------------------------------------|-------------------------------------------|

| Input voltage, V <sub>I</sub>                                | $\dots$ -0.3 V to V <sub>DD</sub> + 0.3 V |

| Continuous total power dissipation                           | Internally Limited                        |

| Operating junction temperature range, T <sub>J</sub>         | –40°C to 150°C                            |

| Storage temperature range, T <sub>stq</sub>                  | –65°C to 150°C                            |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                                     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| D       | 710 mW                                             | 5.68 mW/°C                                     | 454 mW                                | 369 mW                                |

| DGK     | 469 mW                                             | 3.75 mW/°C                                     | 300 mW                                | 244 mW                                |

| ZQY     | 2 W                                                | 17.1 mW/°C                                     | 1.28 W                                | 1.04 W                                |

### recommended operating conditions

|                                                      | MIN                 | MAX                  | UNIT |

|------------------------------------------------------|---------------------|----------------------|------|

| Supply voltage, V <sub>DD</sub>                      | 1.6                 | 3.6                  | V    |

| High-level input voltage, V <sub>IH</sub> (SHUTDOWN) | 0.6 V <sub>DD</sub> |                      | V    |

| Low-level input voltage, V <sub>IL</sub> (SHUTDOWN)  |                     | 0.25 V <sub>DD</sub> | V    |

| Operating free-air temperature, T <sub>A</sub>       | -40                 | 85                   | °C   |

## dc electrical characteristics at $T_A$ = 25°C, $V_{DD}$ = 3.6 V (unless otherwise noted)

|                     | PARAMETER                           | TEST CONDITIONS                                | MIN | TYP  | MAX | UNIT |

|---------------------|-------------------------------------|------------------------------------------------|-----|------|-----|------|

| Voo                 | Output offset voltage               | $A_V = 2 dB$                                   |     | 5    | 40  | mV   |

| PSRR                | Power supply rejection ratio        | V <sub>DD</sub> = 3 V to 3.6 V                 |     | 72   |     | dB   |

| I <sub>DD</sub>     | Supply current                      | SHUTDOWN = 3.6 V                               |     | 0.75 | 1.5 | mA   |

| I <sub>DD(SD)</sub> | Supply current in SHUTDOWN mode     | SHUTDOWN = 0 V                                 |     | 50   | 250 | nA   |

| I <sub>IH</sub>     | High-level input current (SHUTDOWN) | $V_{DD} = 3.6 \text{ V},  V_I = V_{DD}$        |     |      | 1   | μΑ   |

| I <sub>IL</sub>     | Low-level input current (SHUTDOWN)  | $V_{DD} = 3.6 \text{ V},  V_{I} = 0 \text{ V}$ |     |      | 1   | μΑ   |

| Z <sub>I</sub>      | Input impedance                     |                                                |     | 80   |     | kΩ   |

## ac operating characteristics, $\rm V_{DD}$ = 3.3 V, $\rm T_A$ = 25°C, $\rm R_L$ = 16 $\Omega$

|       | PARAMETER                                        | TEST CONDITIONS                      | MIN | TYP  | MAX | UNIT    |

|-------|--------------------------------------------------|--------------------------------------|-----|------|-----|---------|

| G     | Gain                                             |                                      |     | 2    |     | dB      |

| PO    | Output power (each channel)                      | THD ≤ 0.1%, f = 1 kHz                |     | 50   |     | mW      |

| THD+N | Total harmonic distortion + noise                | P <sub>O</sub> = 45 mW, 20 Hz-20 kHz |     | 0.4% |     |         |

| Вом   | Maximum output power BW                          | THD < 0.5%                           |     | > 20 |     | kHz     |

| ksvr  | Supply ripple rejection ratio                    | f = 1 kHz                            |     | 47   |     | dB      |

| SNR   | Signal-to-noise ratio                            | P <sub>O</sub> = 50 mW               |     | 86   |     | dB      |

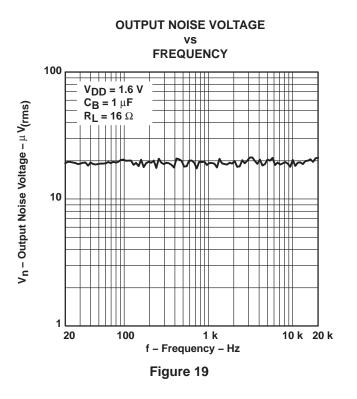

| Vn    | Noise output voltage (no-noise weighting filter) |                                      |     | 45   |     | μV(rms) |

## ac operating characteristics, $\rm V_{DD}$ = 3.3 V, $\rm T_A$ = 25°C, $\rm R_L$ = 32 $\rm \Omega$

|       | PARAMETER                                        | TEST CONDITIONS                                    |     | MIN | TYP  | MAX | UNIT    |

|-------|--------------------------------------------------|----------------------------------------------------|-----|-----|------|-----|---------|

| G     | Gain                                             |                                                    |     |     | 2    |     | dB      |

| PO    | Output power (each channel)                      | THD $\leq$ 0.1%, f = 1 kHz                         |     |     | 35   |     | mW      |

| THD+N | Total harmonic distortion + noise                | $P_O = 30 \text{ mW}, 20 \text{ Hz}-20 \text{ Hz}$ | кНz |     | 0.4% |     |         |

| Вом   | Maximum output power BW                          | THD < 0.4%                                         |     |     | >20  |     | kHz     |

| ksvr  | Supply ripple rejection ratio                    | f = 1 kHz                                          |     |     | 47   |     | dB      |

| SNR   | Signal-to-noise ratio                            | P <sub>O</sub> = 30 mW                             |     |     | 86   |     | dB      |

| Vn    | Noise output voltage (no-noise weighting filter) |                                                    |     |     | 50   |     | μV(rms) |

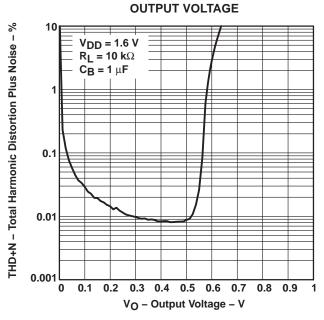

### dc electrical characteristics at $T_A = 25$ °C, $V_{DD} = 1.6$ V (unless otherwise noted)

|                     | PARAMETER                           | TEST CONDITIONS                                | MIN | TYP  | MAX | UNIT |

|---------------------|-------------------------------------|------------------------------------------------|-----|------|-----|------|

| Voo                 | Output offset voltage               | $A_V = 2 dB$                                   |     | 5    | 40  | mV   |

| PSRR                | Power supply rejection ratio        | V <sub>DD</sub> = 1.4 V to 1.8 V               |     | 80   |     | dB   |

| I <sub>DD</sub>     | Supply current                      | SHUTDOWN = 1.6 V                               |     | 0.65 | 1.2 | mA   |

| I <sub>DD(SD)</sub> | Supply current in SHUTDOWN mode     | SHUTDOWN = 0 V                                 |     | 50   | 250 | nA   |

| IIII                | High-level input current (SHUTDOWN) | $V_{DD} = 1.6 \text{ V},  V_I = V_{DD}$        |     |      | 1   | μΑ   |

| I <sub>IL</sub>     | Low-level input current (SHUTDOWN)  | $V_{DD} = 1.6 \text{ V},  V_{I} = 0 \text{ V}$ |     |      | 1   | μΑ   |

| Z <sub>l</sub>      | Input impedance                     |                                                |     | 80   |     | kΩ   |

### ac operating characteristics, V<sub>DD</sub> = 1.6 V, T<sub>A</sub> = 25°C, R<sub>L</sub> = 16 $\Omega$

|                | PARAMETER                                        | TEST CONDITIONS                                        | MIN TYP MAX | UNIT    |

|----------------|--------------------------------------------------|--------------------------------------------------------|-------------|---------|

| G              | Gain                                             |                                                        | 2           | dB      |

| PO             | Output power (each channel)                      | THD $\leq$ 0.5%, f = 1 kHz                             | 10          | mW      |

| THD+N          | Total harmonic distortion + noise                | $P_0 = 9.5 \text{ mW}, 20 \text{ Hz} - 20 \text{ kHz}$ | 0.06%       |         |

| ВОМ            | Maximum output power BW                          | THD < 1%                                               | > 20        | kHz     |

| ksvr           | Supply ripple rejection ratio                    | f = 1 kHz                                              | 47          | dB      |

| SNR            | Signal-to-noise ratio                            | $P_O = 10 \text{ mW}$                                  | 82          | dB      |

| V <sub>n</sub> | Noise output voltage (no-noise weighting filter) |                                                        | 32          | μV(rms) |

### ac operating characteristics, $V_{DD}$ = 1.6 V, $T_{A}$ = 25°C, $R_{L}$ = 32 $\Omega$

|                | PARAMETER                                        | TEST CONDITIONS                                      | MIN TYP MA | X UNIT  |

|----------------|--------------------------------------------------|------------------------------------------------------|------------|---------|

| G              | Gain                                             |                                                      | 2          | dB      |

| Po             | Output power (each channel)                      | THD ≤ 0.5%, f = 1 kHz                                | 7.5        | mW      |

| THD+N          | Total harmonic distortion + noise                | $P_O = 6.5 \text{ mW}, 20 \text{ Hz}-20 \text{ kHz}$ | 0.05%      |         |

| ВОМ            | Maximum output power BW                          | THD < 1%                                             | >20        | kHz     |

| ksvr           | Supply ripple rejection ratio                    | f = 1 kHz                                            | 47         | dB      |

| SNR            | Signal-to-noise ratio                            | $P_0 = 7.5 \text{ mW}$                               | 84         | dB      |

| V <sub>n</sub> | Noise output voltage (no-noise weighting filter) |                                                      | 32         | μV(rms) |

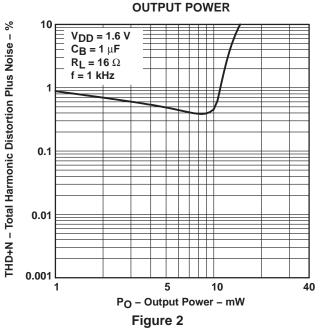

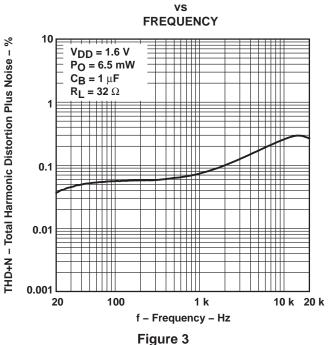

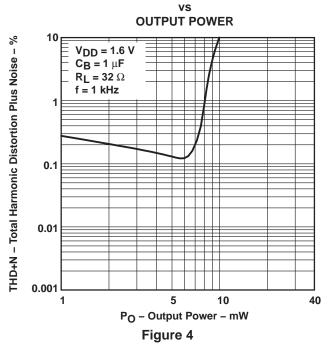

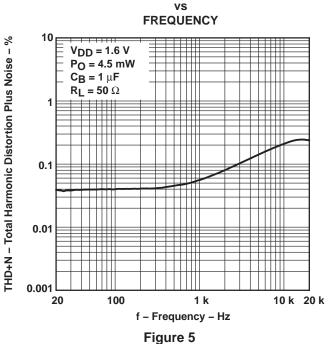

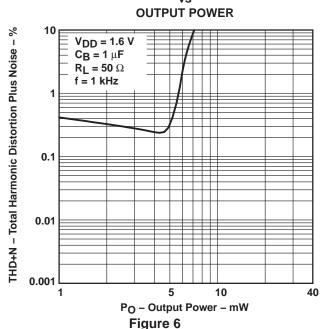

### TYPICAL CHARACTERISTICS

### **Table of Graphs**

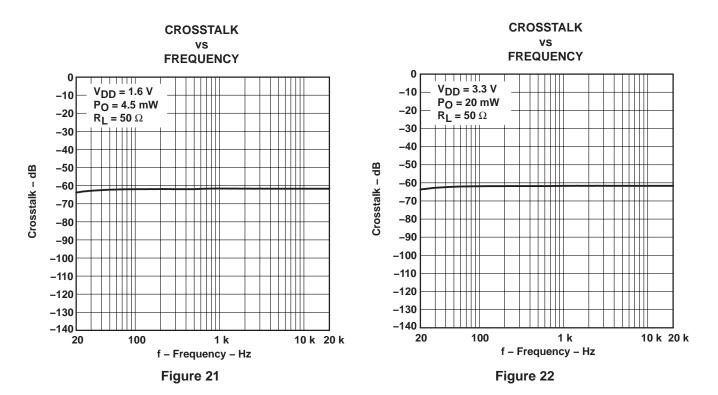

|                 |                                      |                    | FIGURE             |

|-----------------|--------------------------------------|--------------------|--------------------|

|                 |                                      | vs Frequency       | 1, 3, 5, 7, 9, 11  |

| THD+N           | Total harmonic distortion plus noise | vs Output power    | 2, 4, 6, 8, 10, 12 |

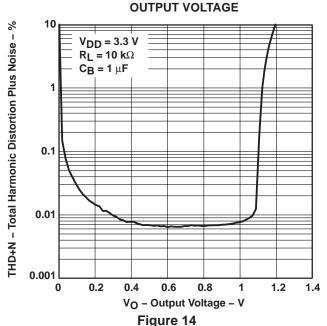

|                 |                                      | vs Output voltage  | 13, 14             |

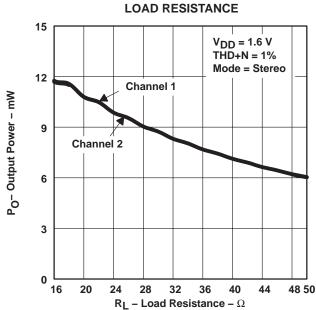

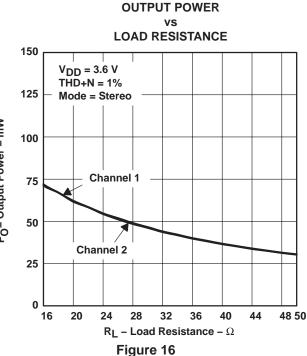

| PO              | Output power                         | vs Load resistance | 15, 16             |

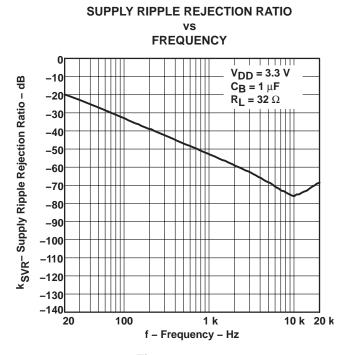

| kSVR            | Supply ripple rejection ratio        | vs Frequency       | 17, 18             |

| Vn              | Output noise voltage                 | vs Frequency       | 19, 20             |

|                 | Crosstalk                            | vs Frequency       | 21, 22             |

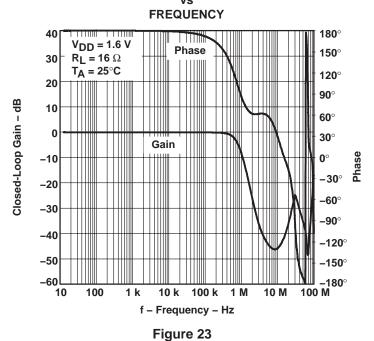

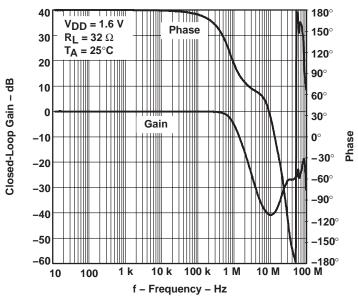

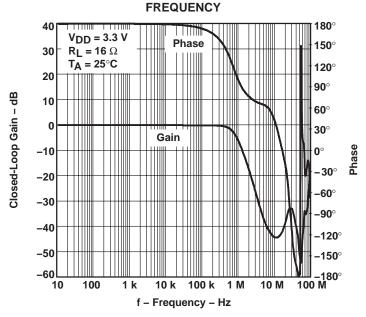

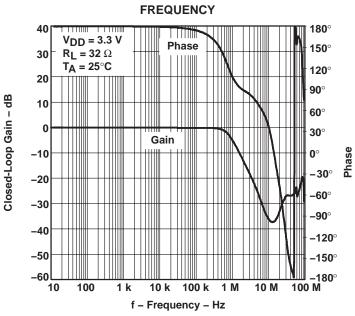

|                 | Closed-loop gain and phase           | vs Frequency       | 23, 24, 25, 26     |

| I <sub>DD</sub> | Supply current                       | vs Supply voltage  | 27                 |

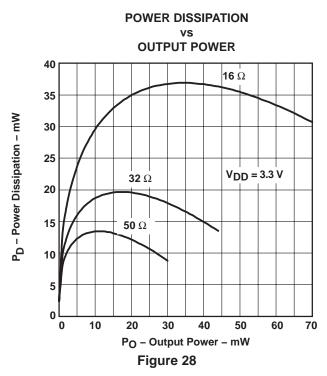

| $P_{D}$         | Power dissipation                    | vs Output power    | 28                 |

## TOTAL HARMONIC DISTORTION PLUS NOISE

## TOTAL HARMONIC DISTORTION PLUS NOISE vs

### TOTAL HARMONIC DISTORTION PLUS NOISE

### TOTAL HARMONIC DISTORTION PLUS NOISE

## TOTAL HARMONIC DISTORTION PLUS NOISE

## TOTAL HARMONIC DISTORTION PLUS NOISE

### TOTAL HARMONIC DISTORTION PLUS NOISE

## TOTAL HARMONIC DISTORTION PLUS NOISE

## TOTAL HARMONIC DISTORTION PLUS NOISE

## TOTAL HARMONIC DISTORTION PLUS NOISE vs

Figure 10

## TOTAL HARMONIC DISTORTION PLUS NOISE

Figure 11

# TOTAL HARMONIC DISTORTION PLUS NOISE vs OUTPUT POWER

## TOTAL HARMONIC DISTORTION PLUS NOISE

Figure 13

## TOTAL HARMONIC DISTORTION PLUS NOISE

### **OUTPUT POWER** vs

Figure 15

P<sub>O</sub>- Output Power - mW

### **SUPPLY RIPPLE REJECTION RATIO FREQUENCY** 0 $V_{DD} = 1.6 V$ -10 k<sub>SVR</sub>- Supply Ripple Rejection Ratio - dB $C_B = 1 \mu F$ -20 $R_L = 32 \Omega$ -30 -40 -50 -60 -70 -80 -90 -100 -110 -120 -130-140 20 100 1 k 10 k 20 k f - Frequency - Hz

Figure 17

Figure 18

**OUTPUT NOISE VOLTAGE**

f - Frequency - Hz

Figure 20

TEXAS INSTRUMENTS

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

10 k 20 k

## CLOSED-LOOP GAIN AND PHASE vs

## CLOSED-LOOP GAIN AND PHASE

FREQUENCY

Figure 24

### **CLOSED-LOOP GAIN AND PHASE**

VS

Figure 25

## CLOSED-LOOP GAIN AND PHASE vs

Figure 26

### APPLICATION INFORMATION

### input capacitor, CI

In the typical application, an input capacitor ( $C_I$ ) is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case,  $C_I$  and  $R_I$  form a high-pass filter with the corner frequency determined in equation 1.  $R_I$  is set internally and is fixed at 80 k $\Omega$ .

$$f_{C} = \frac{1}{2\pi R_{I}C_{I}} \tag{1}$$

The value of  $C_l$  is important to consider, as it directly affects the bass (low-frequency) performance of the circuit. Consider the example where the specification calls for a flat bass response down to 20 Hz. Equation 1 is reconfigured as equation 2.

$$C_{l} = \frac{1}{2\pi R_{l} f_{c}}$$

(2)

In this example,  $C_I$  is approximately 0.1  $\mu$ F. A further consideration for this capacitor is the leakage path from the input source through the input network ( $R_I$ ,  $C_I$ ) and the feedback resistor ( $R_F$ ) to the load. This leakage current creates a dc-offset voltage at the input to the amplifier that reduces useful headroom. For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications, as the dc level there is held at  $V_{DD}/4$ , which is likely higher than the source dc level. It is important to confirm the capacitor polarity in the application.

### power supply decoupling, CS

The TPA6101A2 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure that the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu$ F, placed as close as possible to the device  $V_{DD}$  lead, works best. For filtering lower-frequency noise signals, a larger, aluminum electrolytic capacitor of 10  $\mu$ F or greater placed near the power amplifier is recommended.

### midrail bypass capacitor, C<sub>B</sub>

The midrail bypass capacitor ( $C_B$ ) serves several important functions. During start-up,  $C_B$  determines the rate at which the amplifier starts up. This helps to push the start-up pop noise into the subaudible range (so low it can not be heard). The second function is to reduce noise produced by the power supply caused by coupling into the output drive signal. This noise is from the midrail generation circuit internal to the amplifier. The capacitor is fed from a  $55-k\Omega$  source inside the amplifier. To keep the start-up pop as low as possible, the relationship shown in Euation 3 should be maintained.

$$\frac{1}{\left(\mathsf{C}_{\mathsf{B}} \times 55 \,\mathsf{k}\Omega\right)} \le \frac{1}{\left(\mathsf{C}_{\mathsf{I}}\mathsf{R}_{\mathsf{I}}\right)} \tag{3}$$

As an example, consider a circuit where  $C_B$  is 1  $\mu$ F,  $C_I$  is 0.1  $\mu$ F, and  $R_I$  is 80  $k\Omega$ . Inserting these values into Euation 3 results in: 18.18  $\leq$  125 which satisfies the rule. Bypass capacitor ( $C_B$ ) values of 0.47  $\mu$ F to 1  $\mu$ F and ceramic or tantalum low-ESR capacitors are recommended for the best THD and noise performance.

### APPLICATION INFORMATION

### output coupling capacitor, CC

In the typical single-supply, single-ended (SE) configuration, an output coupling capacitor ( $C_C$ ) is required to block the dc bias at the output of the amplifier, thus preventing dc currents in the load. As with the input coupling capacitor, the output coupling capacitor and impedance of the load from a high-pass filter is governed by Equation 4.

$$f_{C} = \frac{1}{2\pi R_{I} C_{C}} \tag{4}$$

The main disadvantage, from a performance standpoint, is that the typically small load impedances drive the low-frequency corner higher. Large values of  $C_C$  are required to pass low-frequencies into the load. Consider the example where a  $C_C$  of 68  $\mu F$  is chosen and loads vary from 32  $\Omega$  to 47  $k\Omega$ . Table 1 summarizes the frequency response characteristics of each configuration.

Table 1. Common Load Impedances vs Low-Frequency Output Characteristics in SE Mode

| RL       | СС    | LOWEST FREQUENCY |

|----------|-------|------------------|

| 32 Ω     | 68 μF | 73 Hz            |

| 10,000 Ω | 68 μF | 0.23 Hz          |

| 47,000 Ω | 68 μF | 0.05 Hz          |

As Table 1 indicates, headphone response is adequate and drive into line-level inputs (a home stereo for example) is very good.

The output coupling capacitor required in single-supply SE mode also places additional constraints on the selection of other components in the amplifier circuit. With the rules described earlier still valid, add the following relationship:

$$\frac{1}{\left(C_{\mathsf{B}} \times 55 \,\mathsf{k}\Omega\right)} \le \frac{1}{\left(C_{\mathsf{I}}\mathsf{R}_{\mathsf{I}}\right)} \ll \frac{1}{\mathsf{R}_{\mathsf{L}}\mathsf{C}_{\mathsf{C}}} \tag{5}$$

### using low-ESR capacitors

Low-ESR capacitors are recommended throughout this application. A real capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor.

### 3.3-V versus 1.6-V operation

The TPA6101A2 was designed for operation over a supply range of 1.6 V to 3.6 V. There are no special considerations for 1.6-V versus 3.3-V operation as far as supply bypassing, gain setting, or stability. Supply current is slightly reduced from 0.75 mA (typical) to 0.65 mA (typical). The most important consideration is that of output power. Each amplifier can produce a maxium output voltage swing within a few hundred millivolts of the rails with a 10-k $\Omega$  load. However, this voltage swing decreases as the load resistance decreases, and the rDS(on) of the output stage transistors becomes more significant. For example, for a 32- $\Omega$  load, the maximum peak output voltage with VDD = 1.6 V is approximately 0.7 V with no clipping distortion. This reduced voltage swing effectively reduces the maximum undistorted output power.

11-Nov-2025 www.ti.com

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                |              |              |

| TPA6101A2D            | Active | Production    | SOIC (D)   8    | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 6101A2       |

| TPA6101A2D.A          | Active | Production    | SOIC (D)   8    | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 6101A2       |

| TPA6101A2DGKR         | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | AJM          |

| TPA6101A2DGKR.A       | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | AJM          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

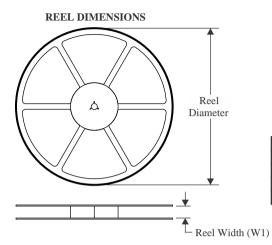

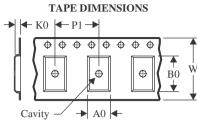

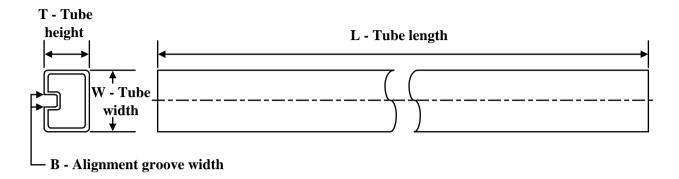

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

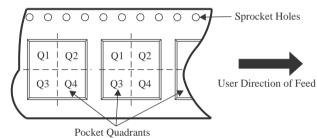

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA6101A2DGKR | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 23-May-2025

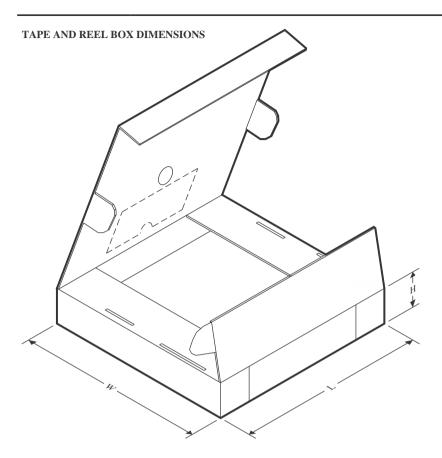

### \*All dimensions are nominal

| Ì | Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | TPA6101A2DGKR | VSSOP        | DGK             | 8    | 2500 | 358.0       | 335.0      | 35.0        |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

### **TUBE**

### \*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPA6101A2D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPA6101A2D.A | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

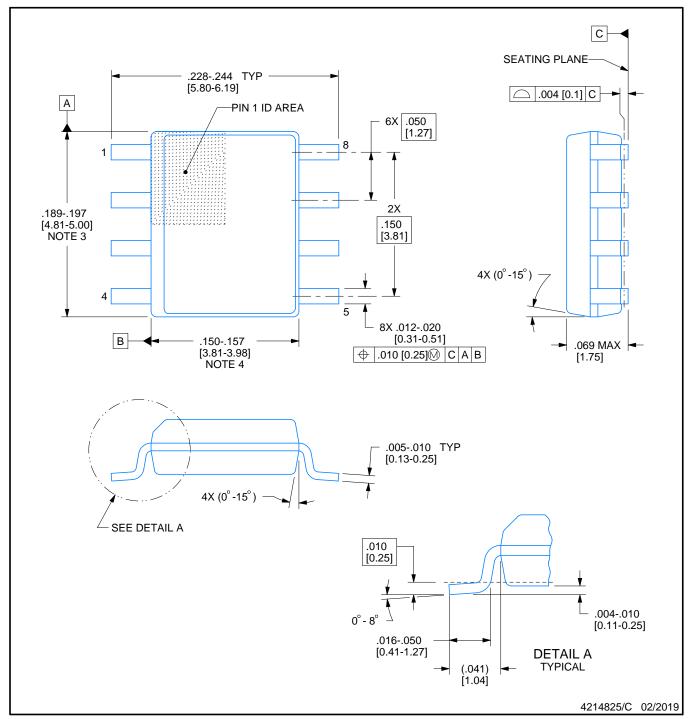

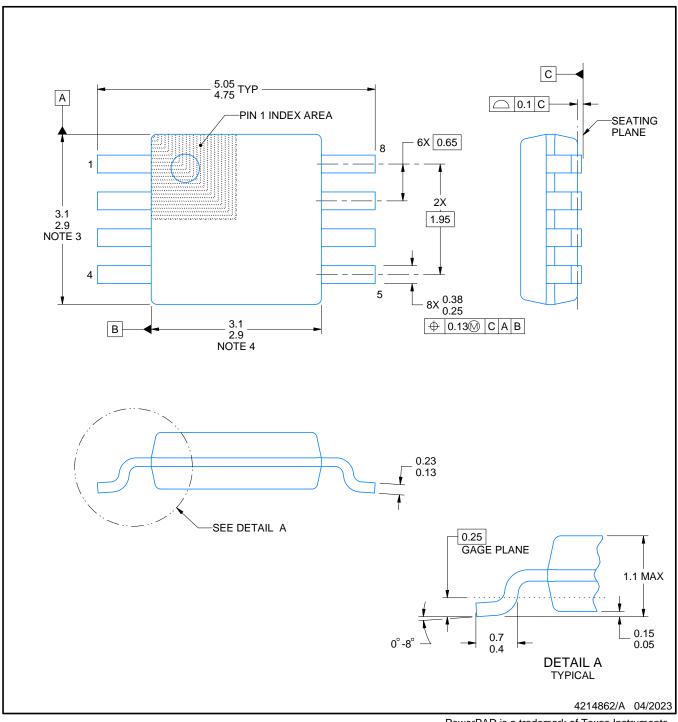

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

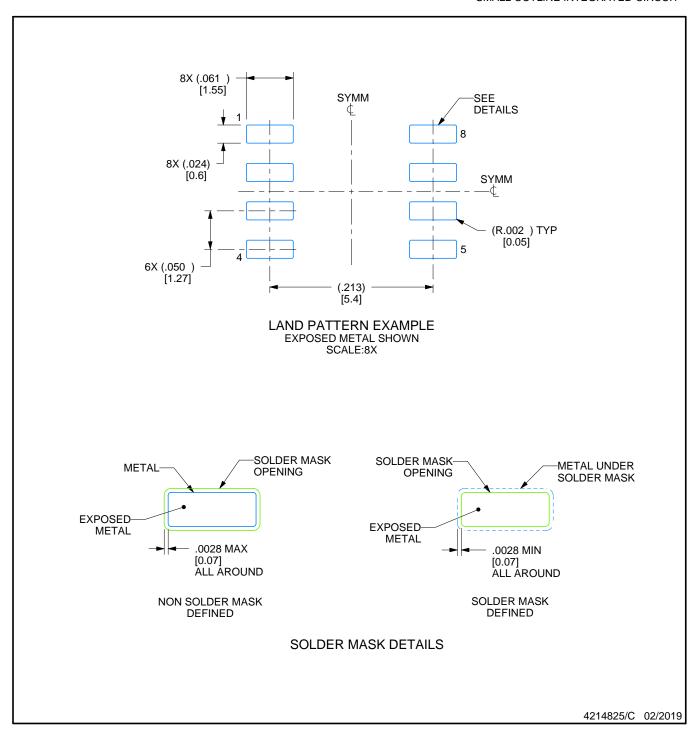

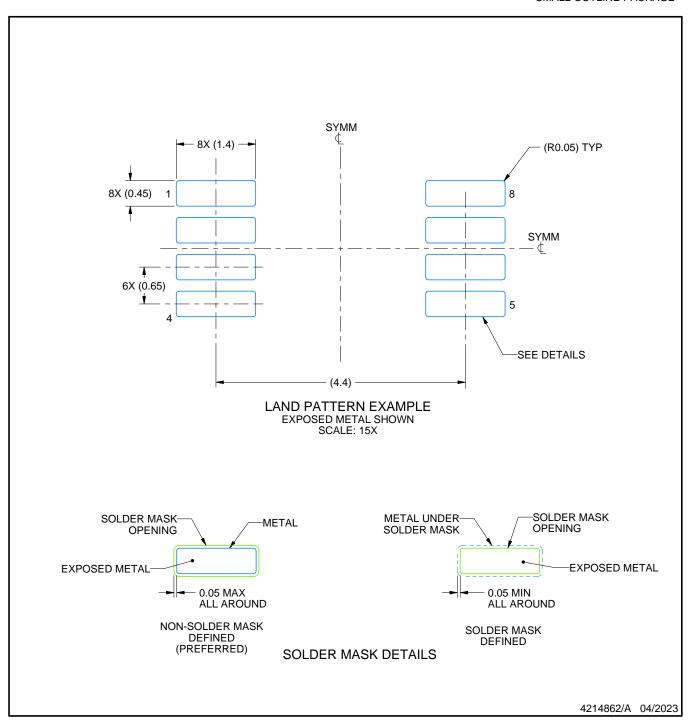

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

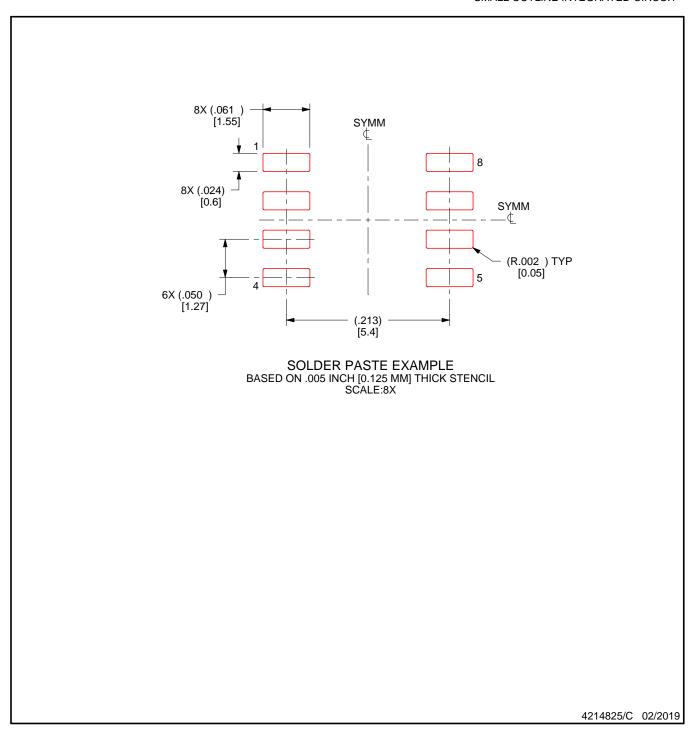

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

SMALL OUTLINE PACKAGE

### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

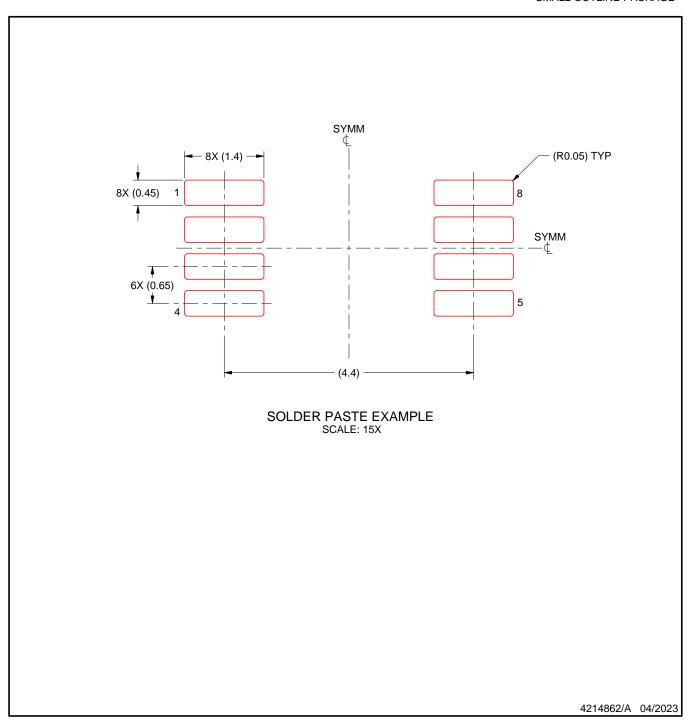

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025