**TPS3704**

SNVSBZ2E - MARCH 2021 - REVISED DECEMBER 2023

# TPS3704x Quad, Triple, Dual Window or Standard Voltage Supervisor

#### 1 Features

- Up to four independent voltage supervisor channels:

- Fixed and adjustable window, UV, or OV voltage options. See Table 4-1 for available

- Easy to use calculator tool for adjustable versions

- High threshold accuracy: ±0.25% (typical)

- Built-in precision hysteresis: 0.75% (typical)

- Fixed time delay options

- Open drain outputs

- Designed to support Arm-based processors such as TDA4, Sitara AM33xx, and advanced FPGAs and SOCs

- Low quiescent current: 15 µA (maximum)

- Temperature range: -40°C to +125°C

- **Functional Safety-Compliant**

- Systematic capability up to SIL 3

- Hardware capability up to SIL 1

## 2 Applications

- Factory automation

- **Building automation**

- Medical

- Motor drives

- Grid infrastructure

- Wireless infrastructure

- Data center & enterprise computing

## 3 Description

The TPS3704x is a low-power precision window or standard voltage supervisor that can be configured as a quad, triple, or dual channel. Each channel has a threshold accuracy of ±1% in an 8-pin

(1.6 mm x 2.9 mm) SOT-23 package offering a small solution size. The TPS3704x includes a very accurate threshold detection, with high resolution, that is ideal for systems that operate on low-voltage supply rails and have narrow margin supply tolerances. Built-in low threshold hysteresis and a fixed reset delay prevent false reset signals when monitoring multiple voltage rails.

The TPS3704x does not require any external resistors for setting the over and undervoltage reset thresholds, which further optimizes overall high accuracy, cost, solution size, and improves reliability for safety systems.

Separate VDD and SENSEx pins allow monitoring of rail voltages other than VDD or can be used as a push-button input. Optional use of external resistors are supported by the SENSEx pins. Each channel on the TPS3704x can be customized to its own over and undervoltage window detection with an upper and lower threshold tolerance that can be symmetric or asymmetric.

#### **Device Information**

| PART NUMBER | PACKAGE (1)        | BODY SIZE (NOM) |

|-------------|--------------------|-----------------|

| TPS3704x    | DDF (SOT-23 8-pin) | 1.6 mm × 2.9 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

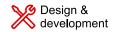

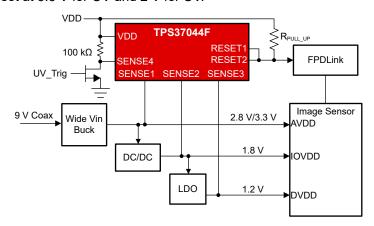

**Typical Application Circuit**

# **Table of Contents**

| 1 Features1                           | 7.3 Feature Description                              | 18 |

|---------------------------------------|------------------------------------------------------|----|

| 2 Applications1                       | 7.4 Device Functional Modes                          |    |

| 3 Description1                        | 8 Application and Implementation                     | 21 |

| 4 Device Nomenclature3                | 8.1 Application Information                          | 21 |

| 5 Pin Configuration and Functions5    | 8.2 Typical Application                              |    |

| 6 Specifications7                     | 8.3 Power Supply Recommendations                     |    |

| 6.1 Absolute Maximum Ratings7         | 8.4 Layout                                           |    |

| 6.2 ESD Ratings7                      | 9 Device and Documentation Support                   | 28 |

| 6.3 Recommended Operating Conditions7 | 9.1 Device Nomenclature                              |    |

| 6.4 Thermal Information7              | 9.2 Receiving Notification of Documentation Updates2 | 29 |

| 6.5 Electrical Characteristics8       | 9.3 Support Resources                                | 29 |

| 6.6 Timing Requirements9              | 9.4 Trademarks                                       |    |

| 6.7 Timing Diagrams10                 | 9.5 Electrostatic Discharge Caution                  | 29 |

| 6.8 Typical Characteristics12         | 9.6 Glossary                                         |    |

| 7 Detailed Description16              | 10 Revision History                                  |    |

| 7.1 Overview                          | 11 Mechanical, Packaging, and Orderable              |    |

| 7.2 Functional Block Diagram16        | Information                                          | 30 |

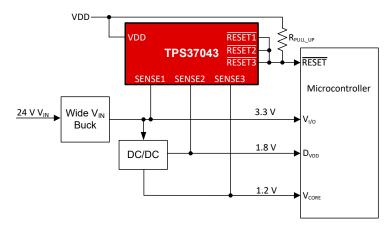

## **4 Device Nomenclature**

*Figure 4-1* shows the device naming nomenclature to compare the different device variants. See Table 9-1 for a more detailed explanation. See Table 4-1 or Table 9-2 for the available device variants.

**Table 4-1. Device Threshold Table**

| Table 4-1. Device Tilleshold Table |                        |                 |               |                           |                           |                           |                           |

|------------------------------------|------------------------|-----------------|---------------|---------------------------|---------------------------|---------------------------|---------------------------|

| ORDERABLE PART NAME                | VARIANT <sup>(3)</sup> | NUM OF<br>CHAN. | RESET<br>TIME | SENSE1 <sup>(1)</sup> (2) | SENSE2 <sup>(1)</sup> (2) | SENSE3 <sup>(1)</sup> (2) | SENSE4 <sup>(1)</sup> (2) |

| TPS37042BJOFDDFRQ1                 | ADJ                    | 2               | 10ms          | 0.8V (±4%)                | 0.8V (±4%)                | -                         | -                         |

| TPS37042A3OFDDFRQ1                 | Fixed                  | 2               | 10ms          | 3.3V (±5%)                | 1.2V (±5%)                | -                         | -                         |

| TPS37042ZJOFDDFRQ1                 | Fixed                  | 2               | 10ms          | 1.95V (±4%)               | 3.8V (±6%)                | -                         | -                         |

| TPS37043DJOFDDFR                   | ADJ/Fixed              | 3               | 10 ms         | 3.3V (-11%)               | 1.2V (-11%)               | 0.8V (-8%)                | -                         |

| TPS37043A4OFDDFRQ1                 | Fixed                  | 3               | 10ms          | 2.8V (±5%)                | 1.8V (±5%)                | 1.2V (±5%)                | -                         |

| TPS37043A8OFDDFRQ1                 | Fixed                  | 3               | 10ms          | 3.3V (±5%)                | 1.8V (±5%)                | 1.0V (±5%)                | -                         |

| TPS37043CPOFDDFRQ1                 | ADJ/Fixed              | 3               | 10ms          | 3.3V (±4%)                | 0.75V (±4%)               | 0.8V (±3%)                | -                         |

| TPS37043ZJOFDDFRQ1                 | Fixed                  | 3               | 10ms          | 0.95V (±4%)               | 1.35V (±4%)               | 1.8V (±4%)                | -                         |

| TPS37043LJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.4V (±5%)                | 0.4V (±5%)                | 0.8V (±5%)                | -                         |

| TPS37043CJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.8V (±6%)                | 0.8V (±6%)                | 0.8V (±6%)                | -                         |

| TPS37043MJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.4V (±7%)                | 0.4V (±7%)                | 0.8V (±7%)                | -                         |

| TPS37043A5OFDDFRQ1                 | Fixed                  | 3               | 10ms          | 3.3V (±4%)                | 1.8V (±4%)                | 1.2V (±4%)                | -                         |

| TPS37043BJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.8V (±4%)                | 0.8V (±4%)                | 0.8V (±4%)                | -                         |

| TPS37044BJOFDDFR                   | ADJ                    | 4               | 10 ms         | 0.8 V (±4%)               | 0.8 V (±4%)               | 0.8 V (±4%)               | 0.8 V (±4%)               |

| TPS37044LJOJDDFR                   | ADJ                    | 4               | 35ms          | 0.4V (±5%)                | 0.4V (±5%)                | 0.8V (±5%)                | 0.8V (±5%)                |

| TPS37044BJOFDDFRQ1                 | ADJ                    | 4               | 10ms          | 0.8V (±4%)                | 0.8V (±4%)                | 0.8V (±4%)                | 0.8V (±4%)                |

| TPS37044CJOFDDFRQ1                 | ADJ                    | 4               | 10ms          | 0.8V (±6%)                | 0.8V (±6%)                | 0.8V (±6%)                | 0.8V (±6%)                |

| TPS37044MJOFDDFRQ1                 | ADJ                    | 4               | 10ms          | 0.4V (±7%)                | 0.4V (±7%)                | 0.8V (±7%)                | 0.8V (±7%)                |

| TPS37044A4OGDDFRQ1                 | Fixed                  | 4               | 15ms          | 3.3V (±8%)                | 1.8V (±4%)                | 1.15V (±6%)               | 1.15V (±6%)               |

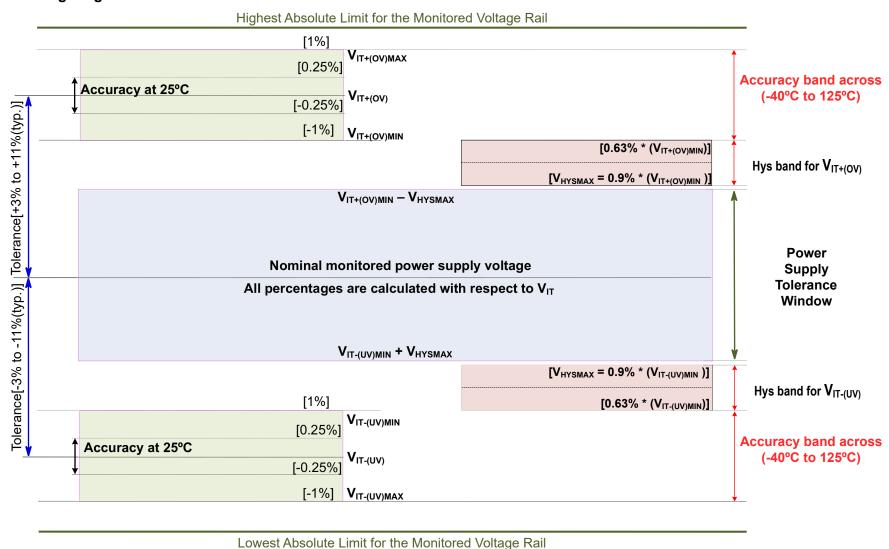

<sup>(1)</sup> Listed percentage denotes window tolerance, see Figure 6-1 for more information

<sup>(2)</sup> VIT threshold of 0.8V and 0.4V signifies an adjustable channel

<sup>(3)</sup> ADJ denotes an adjustable voltage threshold set by an external resistor divider, see Section 8.1.2 for more information

Figure 4-1. Device Naming Nomenclature

Product Folder Links: TPS3704

omit Document Feedback

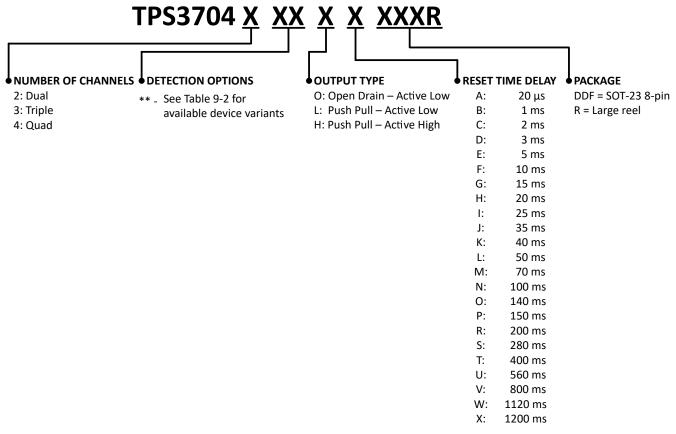

# **5 Pin Configuration and Functions**

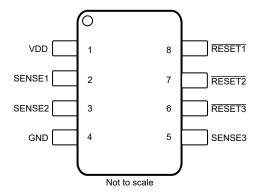

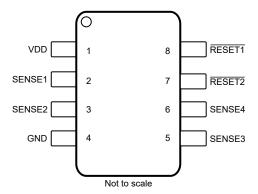

Figure 5-1. SOT-23 8-PIN DDF Package TPS37042 (Top View)

Figure 5-2. SOT-23 8-PIN DDF Package TPS37043 (Top View)

Figure 5-3. SOT-23 8-PIN DDF Package TPS37044 (Top View)

## **Table 5-1. Pin Functions**

|                       |            | PIN  |          | Tak      | ,,,,, | 5-1. PIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|------------|------|----------|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                  | TPS37041   |      | TPS37043 | TPS37044 | I/O   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD                   | 1          | 1    | 1        | 1        | ı     | Supply Input. Bypass with a 0.1 µF capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SENSE1                | 2          | 2    | 2        | 2        | Ι     | Connect directly to monitored voltage. RESET1/RESET1 is asserted when SENSE1 falls outside of window threshold. No external capacitor is required for this SENSE1 pin. For TPS37044 (quad version) RESET1/RESET1 asserts when either SENSE1 or SENSE2 falls outside of window threshold. For noisy applications, placing a 10 nF to 100 nF ceramic capacitor close to this pin may be needed for optimum performance. If the input pin is not being used, it can be left floating. |

| SENSE2                | -          | 3    | 3        | 3        | -     | Connect directly to monitored voltage. RESET2/RESET2 is asserted when SENSE2 falls outside of window threshold. No external capacitor is required for SENSE2 pin. For TPS37044 (quad version) RESET1/RESET1 asserts when either SENSE1 or SENSE2 falls outside of window threshold. For noisy applications, placing a 10 nF to 100 nF ceramic capacitor close to this pin may be needed for optimum performance. If the input pin is not being used, it can be left floating.      |

| SENSE3                | -          | -    | 5        | 5        | I     | Connect directly to monitored voltage. RESET3/RESET3 is asserted when SENSE3 falls outside of window threshold. No external capacitor is required for SENSE3 pin. For TPS37044 (quad version) RESET2/RESET2 asserts when either SENSE3 or SENSE4 falls outside of window threshold. For noisy applications, placing a 10 nF to 100 nF ceramic capacitor close to this pin may be needed for optimum performance. If the input pin is not being used, it can be left floating.      |

| SENSE4                | -          | -    | -        | 6        | I     | Connect directly to monitored voltage. For TPS37044 (quad version) RESET2/RESET2 asserts when either SENSE3 or SENSE4 falls outside of window threshold. For noisy applications, placing a 10 nF to 100 nF ceramic capacitor close to this pin may be needed for optimum performance. If the input pin is not being used, it can be left floating.                                                                                                                                 |

| RESET1 / RESET1       | 8          | 8    | 8        | 8        | 0     | RESET1/RESET1 asserts when SENSE1 falls outside of the overvoltage or undervoltage threshold window.  RESET1/RESET1 stays asserted for the reset timeout period after SENSE1 fall back within the window threshold. Active-low, open-drain reset output, requires an external pullup resistor. For TPS37044, RESET1/RESET1 asserts when either SENSE1 or SENSE2 fall outside of the window threshold. The pin can be left floating if it is unused.                                |

| RESET2<br>/<br>RESET2 | -          | 7    | 7        | 7        | 0     | RESET2/RESET2 asserts when SENSE2 falls outside of the overvoltage or undervoltage threshold window.  RESET2/RESET2 stays asserted for the reset timeout period after SENSE2 fall back within the window threshold. Active-low, open-drain reset output, requires an external pullup resistor. For TPS37044, RESET2/RESET2 asserts when either SENSE3 or SENSE4 fall outside of the window threshold. The pin can be left floating if it is unused.                                |

| RESET3<br>/<br>RESET3 | -          | -    | 6        | -        | 0     | RESET3/RESET3 asserts when SENSE3 falls outside of the overvoltage or undervoltage threshold window.  RESET3/RESET3 stays asserted for the reset timeout period after SENSE3 fall back within the window threshold. Active-low, open-drain reset output, requires an external pullup resistor. The pin can be left floating if it is unused.                                                                                                                                       |

| GND                   | 4          | 4    | 4        | 4        | -     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NC                    | 3, 5, 6, 7 | 5, 6 | -        | -        | •     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Submit Document Feedback Product Folder Links: TPS3704

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

Over operating free-air temperature range (unless otherwise noted) (1)

|                 |                                                                                       | MIN                         | MAX | UNIT |

|-----------------|---------------------------------------------------------------------------------------|-----------------------------|-----|------|

|                 | $V_{DD}$                                                                              | -0.3                        | 6.5 | V    |

| Voltage         | V <sub>RESET1</sub> , V <sub>RESET2</sub> , V <sub>RESET3</sub>                       | -0.3                        | 6.5 | V    |

|                 | V <sub>SENSE1</sub> , V <sub>SENSE2</sub> , V <sub>SENSE3</sub> , V <sub>SENSE4</sub> | -0.3                        | 6.5 | V    |

| Current         | I <sub>RESET1</sub> , I <sub>RESET2</sub> , I <sub>RESET3</sub> SINK                  |                             | ±20 | mA   |

|                 | Continuous total power dissipation                                                    | See the Thermal Information |     |      |

| Temperature (2) | Operating junction temperature, T <sub>J</sub>                                        | -40                         | 150 | °C   |

| Temperature (-) | Operating free-air temperature, T <sub>A</sub>                                        | -40                         | 150 | °C   |

|                 | Storage temperature, T <sub>stg</sub>                                                 | -65                         | 150 | °C   |

<sup>(1)</sup> Stresses beyond values listed under Absolute Maximum Ratings (AMR) may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to AMR-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                                                                       |                                                                     | VALUE | UNIT |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|-------|------|

| Electrostatic      | Human-body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup> | ±2000                                                               |       |      |

| V <sub>(ESD)</sub> | discharge                                                             | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | ±750  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process

## **6.3 Recommended Operating Conditions**

|                                                                      |                                | MIN | NOM MAX | UNIT |

|----------------------------------------------------------------------|--------------------------------|-----|---------|------|

| V <sub>DD</sub>                                                      | Supply pin voltage             | 1.7 | 6.0     | V    |

| V <sub>SENSE1,2,3,4</sub>                                            | Input pin voltage              | 0   | 6.0     | V    |

| V <sub>RESET1</sub> , V <sub>RESET2</sub> , V <sub>RESET3</sub>      | Output pin voltage             | 0   | 6.0     | V    |

| I <sub>RESET1</sub> , I <sub>RESET2</sub> , I <sub>RESET3</sub> SINK | Output pin current sink        | 0.3 | 5       | mA   |

| T <sub>A</sub>                                                       | Operating free air temperature | -40 | 125     | °C   |

### **6.4 Thermal Information**

|                       |                                              | TPS3704x |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC (1)                           | DDF      | UNIT |

|                       |                                              | PINS     |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 121.5    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 60.6     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 42.3     | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 2.2      | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 42.1     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> As a result of the low dissipated power in this device, it is assumed that  $T_J = T_A$ .

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process

### **6.5 Electrical Characteristics**

At 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  6.0 V,  $\overline{\text{RESETx}}$  Voltage (V<sub>RESETx</sub>) = 10 k $\Omega$  to V<sub>DD</sub>,  $\overline{\text{RESETx}}$  load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, typical conditions at V<sub>DD</sub> =

|                        | PARAMETER                                                                       | TEST CONDITIONS                                         | MIN  | TYP  | MAX  | UNIT      |

|------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------|------|------|------|-----------|

| $V_{DD}$               | Supply Voltage                                                                  |                                                         | 1.7  |      | 6.0  | V         |

| UVLO                   | Under Voltage Lockout (1)                                                       | V <sub>DD</sub> falling below 1.7 V                     | 1.2  | 1.4  | 1.6  | V         |

| UVLO <sub>(HYS)</sub>  | UVLO Hysteresis <sup>(2)</sup>                                                  | V <sub>DD</sub> rising below 1.7 V                      |      | 65   |      | mV        |

| V <sub>POR</sub>       | Power on reset voltage (3)                                                      | V <sub>OL (MAX)</sub> = 0.3 V, I <sub>OUT</sub> = 15 μA |      |      | 0.7  | V         |

| V <sub>IT</sub> Range  | Threshold Programming Range                                                     |                                                         | 0.4  |      | 5.55 | V         |

| V <sub>IT- (UV)</sub>  | UV accuracy (25°C)                                                              |                                                         |      | 0.1  |      | %         |

| V <sub>IT+ (OV)</sub>  | OV accuracy (25°C)                                                              |                                                         |      | 0.1  |      | %         |

| TOL_min                | Tolerance Programming minimum                                                   |                                                         |      | 3    |      | %         |

| TOL_max                | Tolerance Programming maximum                                                   |                                                         |      | 11   |      | %         |

| THR RES Low            | Threshold Programming Resolution Low                                            | V <sub>IT</sub> ≤ 0.8 V                                 |      | 20   |      | mV / step |

| THR RES Mid            | Threshold Programming Resolution Mid                                            | 0.8 V < V <sub>IT</sub> ≤ 4.0 V                         |      | 0.5  |      | % / step  |

| THR RES High           | Threshold Programming Resolution High                                           | V <sub>IT</sub> > 4.0 V                                 |      | 20   |      | mV / step |

| V <sub>IT</sub>        | Accuracy for absolute threshold including tolerance                             | V <sub>IT</sub> < 0.8 V                                 | -1.6 |      | 1.6  | %         |

| V <sub>IT</sub>        | Accuracy for absolute threshold including tolerance                             | V <sub>IT</sub> = 0.8 V - 5.55 V                        | -1   | -    | 1    | %         |

| V <sub>HYS</sub>       | V <sub>IT</sub> < 0.80V                                                         |                                                         | 1.1  | 1.4  | 1.7  | %         |

| V <sub>HYS</sub>       | V <sub>IT</sub> ≥ 0.80V                                                         |                                                         | 0.40 | 0.75 | 1    | %         |

| I <sub>DD</sub>        | TPS3704x                                                                        | V <sub>DD</sub> ≤ 6.0V                                  |      | 5.5  | 15   | μA        |

| I <sub>SENSEx</sub>    | Input current, SENSEx pin                                                       | V <sub>SENSEx</sub> = 5.5 V                             |      | 1    | 2.5  | μA        |

| I <sub>SENSE_ADJ</sub> | Input current, SENSE pin (Bypass internal resistor divider)- Adjustible version | V <sub>SENSEx</sub> = 5.5 V                             |      |      | 350  | nA        |

| V <sub>OL</sub>        | Low level output voltage                                                        | VDD = 1.7 V, I <sub>SINK</sub> = 0.4 mA                 |      |      | 300  | mV        |

| V <sub>OL</sub>        | Low level output voltage                                                        | VDD = 2 V, I <sub>SINK</sub> = 3 mA                     |      |      | 300  | mV        |

| V <sub>OL</sub>        | Low level output voltage                                                        | VDD = 6.0 V, I <sub>SINK</sub> = 5 mA                   |      |      | 300  | mV        |

| I <sub>(lkg)</sub>     | Open drain output leakage current                                               | V <sub>DD</sub> = V <sub>RESETx</sub> = 6.0 V           |      |      | 350  | nA        |

<sup>(1)</sup> RESETx pin is driven low when V<sub>DD</sub> falls below UVLO.

(2) Hysteresis is with respect of the tripoint (V<sub>IT-(UV)</sub>, V<sub>IT+(OV)</sub>).

(3) V<sub>POR</sub> is the minimum V<sub>DD</sub> voltage level for a controlled output state. Slew rate = 100 mV / μs.

## 6.6 Timing Requirements

At 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  6.0 V,  $\overline{\text{RESETx}}$  voltage (V<sub>RESETx</sub>) = 10 k $\Omega$  to V<sub>DD</sub>,  $\overline{\text{RESETx}}$  load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, typical conditions at V<sub>DD</sub> = 3.3 V.

|                       | PARAMETER                                       | TEST CONDITIONS                                           | MIN | NOM            | MAX | UNIT |

|-----------------------|-------------------------------------------------|-----------------------------------------------------------|-----|----------------|-----|------|

| t <sub>D</sub>        | Reset release time delay                        | Fixed delay option t <sub>D</sub> < 4 ms, overdrive = 10% | -40 | t <sub>D</sub> | 40  | %    |

| t <sub>D</sub>        | Reset release time delay                        | Fixed delay option t <sub>D</sub> > 5 ms, overdrive = 10% | -30 | t <sub>D</sub> | 30  | %    |

| t <sub>PD</sub>       | Propagation detect delay (1)                    | Fixed time delay t <sub>D</sub> > 1 ms, overdrive 10%     |     |                | 10  | μs   |

| t <sub>GI(VIT-)</sub> | Glitch Immunity Undervoltage (5% overdrive) (2) |                                                           |     | 2              |     | μs   |

| t <sub>GI(VIT+)</sub> | Glitch Immunity Overvoltage (5% overdrive) (2)  |                                                           |     | 2              |     | μs   |

| t <sub>R</sub>        | Ouptut rise (Push-Pull) (2) (3)                 |                                                           |     | 25             |     | ns   |

| t <sub>R</sub>        | Output rise time (Open-Drain) (2) (3)           |                                                           |     | 2.2            |     | μs   |

| t <sub>F</sub>        | Output fall time (2) (3)                        |                                                           |     | 0.2            |     | μs   |

| t <sub>STRT</sub>     | Startup delay <sup>(4)</sup>                    |                                                           |     | 1              |     | ms   |

- (2)

- $t_{PD} \ \ measured \ from \ threshold \ trip \ point \ (V_{IT-(UV)} \ or \ V_{IT+(OV)}) \ to \ \overline{RESETx} \ V_{OL} \ voltage \\ 5\% \ \ Overdrive \ from \ threshold. \ Overdrive \% = [(V_{SENSEx} V_{IT}) / V_{IT}]; \ Where \ V_{IT} \ stands \ for \ V_{IT-(UV)} \ or \ V_{IT+(OV)} \ Output \ transitions \ from \ V_{OL} \ to \ V_{OH} \ or \ (V_{RESETx}) \ for \ rise \ times \ and \ V_{OH} \ or \ (V_{RESETx}) \ to \ V_{OL} \ for \ fall \ times. \\ During \ the \ power-on \ sequence, \ V_{DD} \ must \ be \ at \ or \ above \ V_{DD(MIN)} \ for \ at \ least \ t_{STRT} + t_D \ before \ the \ output \ is \ in \ the \ correct \ state. \ when \ VDD \ is \ between \ V_{DD(MIN)} \ and \ VPOR \ the \ \overline{RESETx} \ pin \ will \ be \ engaged$

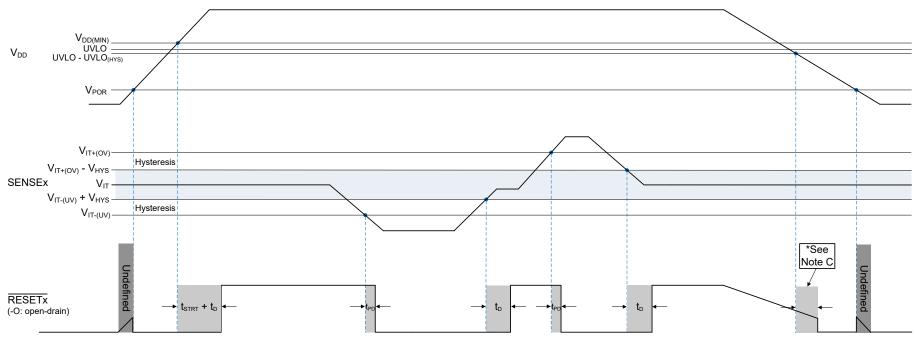

### 6.7 Timing Diagrams

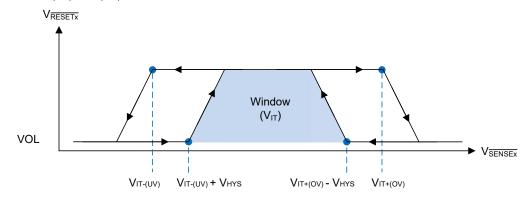

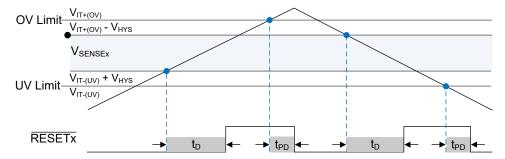

Figure 6-1. Voltage Threshold and Hysteresis Accuracy

Product Folder Links: TPS3704

Submit Document Feedback Copyright © 2023 Texas Instruments Incorporated

- A. Open-Drain timing diagram assumes the RESETx / RESETx pin is connected via an external pull-up resistor to VDD.

- B. Be advised that Figure 6-2 shows the VDD falling slew rate is slow or the VDD decay time is much larger than the propagation detect delay (tpD) time.

- C. RESETx/RESETx is asserted after a time delay, typical value of 100 µs, when VDD goes below the UVLO-UVLO<sub>(HYS)</sub> threshold.

Figure 6-2. SENSEx Timing Diagram

### **6.8 Typical Characteristics**

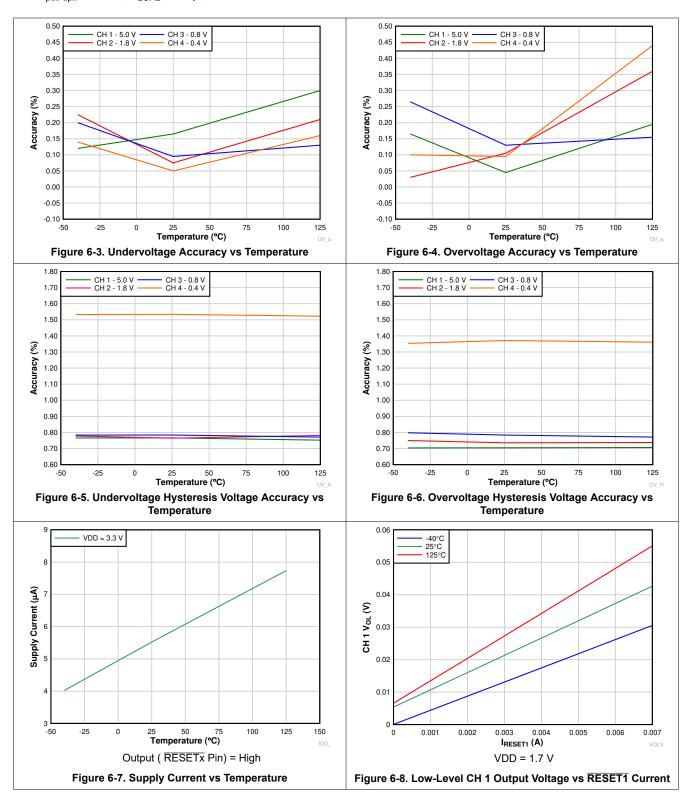

Typical characteristics show the typical performance of the TPS3704x device. Test conditions are  $T_A$  = 25°C,  $V_{DD}$  = 3.3 V, and  $R_{pull-upx}$  = 10 k $\Omega$ ,  $C_{LOAD}$  = 50 pF, unless otherwise noted.

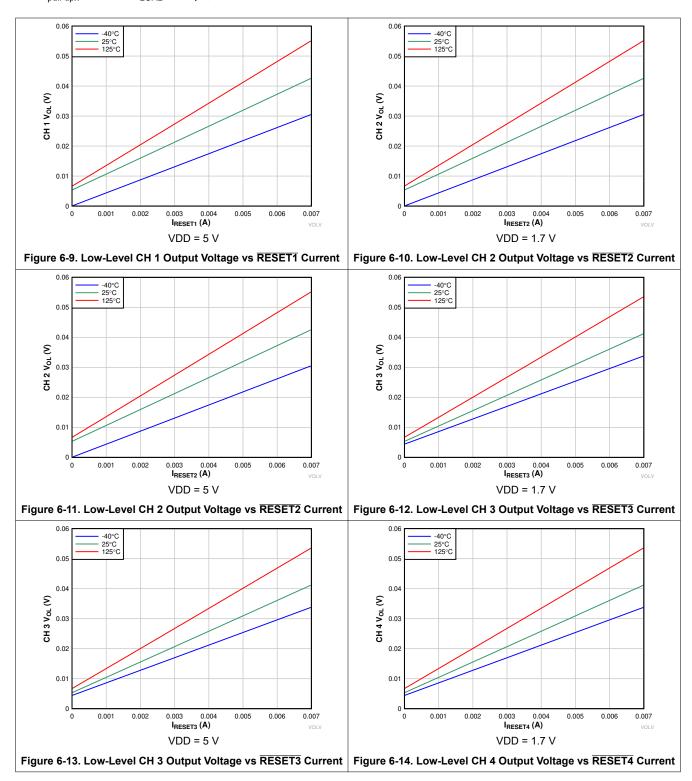

## **6.8 Typical Characteristics (continued)**

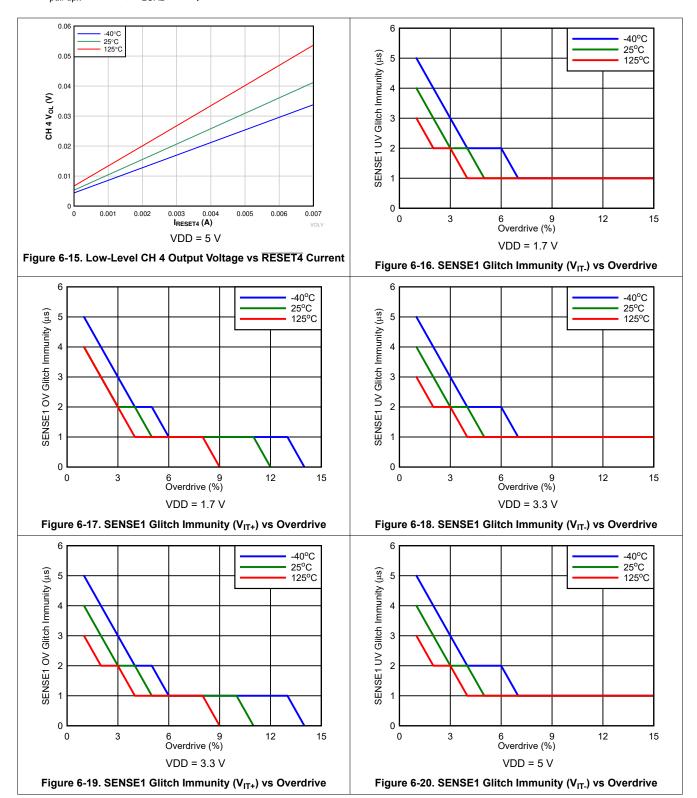

Typical characteristics show the typical performance of the TPS3704x device. Test conditions are  $T_A$  = 25°C,  $V_{DD}$  = 3.3 V, and  $R_{pull-upx}$  = 10 k $\Omega$ ,  $C_{LOAD}$  = 50 pF, unless otherwise noted.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

## 6.8 Typical Characteristics (continued)

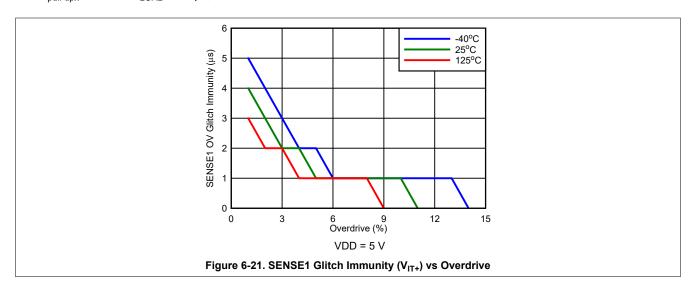

Typical characteristics show the typical performance of the TPS3704x device. Test conditions are  $T_A$  = 25°C,  $V_{DD}$  = 3.3 V, and  $R_{pull-upx}$  = 10 k $\Omega$ ,  $C_{LOAD}$  = 50 pF, unless otherwise noted.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# **6.8 Typical Characteristics (continued)**

Typical characteristics show the typical performance of the TPS3704x device. Test conditions are  $T_A$  = 25°C,  $V_{DD}$  = 3.3 V, and  $R_{pull-upx}$  = 10 k $\Omega$ ,  $C_{LOAD}$  = 50 pF, unless otherwise noted.

## 7 Detailed Description

## 7.1 Overview

TPS3704x is a family of quad, triple, and dual precision voltage supervisors where each channel has overvoltage and undervoltage detection capability. The TPS3704x features a highly accurate window threshold voltage where the upper and lower thresholds can be customized for symmetric or asymmetric tolerances. The reset signal for the TPS3704x is asserted, with a fault detection time delay ( $t_{PD}$  = 10  $\mu$ s maximum), when the sense voltage is outside of the overvoltage and undervoltage thresholds.

TPS3704x includes the resistors used to set the overvoltage and undervoltage thresholds internal to the device. These internal resistors allow for lower component counts and greatly simplifies the design because no additional margins are needed to account for the accuracy of external resistors. The level of integration in the TPS3704x enables a total small solution size for any application.

The TPS3704x is capable to monitor any voltage rail with high resolution ( $V_{IT} \le 0.8 \text{ V}$ : 20 mV steps /  $V_{IT} > 0.8 \text{ V}$ : 0.5% or 20 mV steps whichever is lower). Each channel in the TPS3704x can be configured independently as a window, OV or UV supervisor. Also, the  $V_{IT}$  threshold voltage for each channel can be asymmetric. For example, a channel that is configured as an overvoltage supervisor can be setup with a +5% tolerance whereas an undervoltage channel supervisor can be programmed with a -4% tolerance. If a window supervisor is configured, the voltage threshold tolerance can either be symmetrical or asymmetrical.

The TPS3704x includes fixed reset time delay ( $t_D$ ) options ranging from 20  $\mu$ s to 1200 ms and can monitor up to four channels while maintaining an ultra-low  $I_Q$  current of 15  $\mu$ A (maximum).

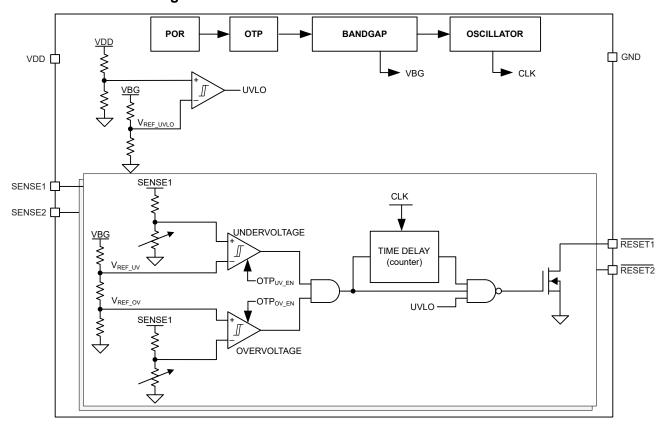

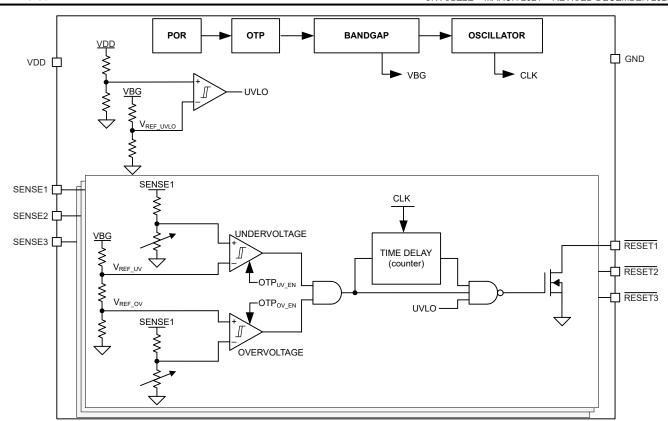

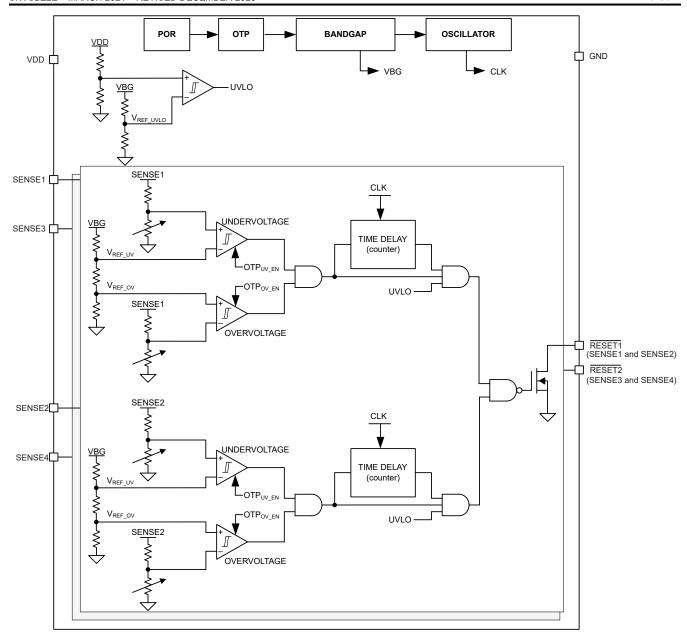

## 7.2 Functional Block Diagram

Figure 7-1. TPS37042 Dual-Channel Functional Block Diagram

Figure 7-2. TPS37043 Triple-Channel Functional Block Diagram

Figure 7-3. TPS37044 Quadruple-Channel Functional Block Diagram

\*For available voltages, window tolerance, time delays, and UV/OV threshold options, see Table 9-2.

## 7.3 Feature Description

#### 7.3.1 VDD

18

The TPS3704x is designed to operate from an input voltage supply range between 1.7 V to 6 V. The SENSEx pins is monitored by the internal comparator. VDD also functions as the supply for the internal bandgap, internal regulator, state machine, buffers and other control blocks. The reset signal is at a known state when VDD >  $V_{POR}$ . Undervoltage lockout forces the reset output to be asserted when VDD falls below the minimum VDD voltage.

VDD capacitor is not required for this device; however, if the input supply is noisy, then it is good design practice to place a 0.1  $\mu$ F to 1  $\mu$ F bypass capacitor between the VDD pin and the GND pin to ensure enough charge is available for the device to power up correctly. VDD needs to be at or above  $V_{DD(MIN)}$  for start-up delay

$(t_{STRT} + t_D)$  to begin and for the device to be fully functional.

## 7.3.2 SENSEx Input

The SENSEx input can monitor supply rails from 0 V to 5.55 V, regardless of the device supply voltage used. The SENSEx pins are used to monitor critical voltage rails or push-button inputs. If the voltage on this pin drops below  $V_{\text{IT-(UV)}}$  or goes above  $V_{\text{IT+(OV)}}$ , then  $\overline{\text{RESETx}}/\text{RESETx}$  is asserted. When the voltage on the SENSEx pin rises above the positive threshold voltage  $V_{\text{IT-(UV)}} + V_{\text{HYS}}$  or goes below the negative threshold voltage  $V_{\text{IT+(OV)}} - V_{\text{HYS}}$ ,

RESETx/RESETx deasserts after the set RESETx/RESETx delay time. The internal comparators have built-in hysteresis to ensure well-defined RESETx/RESETx assertions and deassertions even when there are small changes on the voltage rail being monitored.

The TPS3704x combines comparators with a precision reference voltage and a trimmed resistor divider. This configuration optimizes device accuracy because all resistor tolerances are accounted for in the accuracy and performance specifications. The TPS3704x device is relatively immune to short transients on the SENSEx pin. Although not required in most cases, for noisy applications, good analog design practice is to place a 10-nF to 100-nF bypass capacitor at the SENSEx inputs to reduce sensitivity to transient voltages on the monitored signals.

## 7.3.2.1 Immunity to SENSEx Pins Voltage Transients

The TPS3704x is immune to short voltage transient spikes on the input SENSEx pins. Sensitivity to transients depends on both transient duration and overdrive (amplitude) of the transient.

Overdrive is defined by how much the  $V_{SENSEx}$  exceeds the specified threshold, and is important to know because the smaller the overdrive, the slower the response of the ( $\overline{RESETx}/RESETx$ ) outputs. Threshold overdrive is calculated as a percent of the threshold in question, as shown in Equation 1:

Overdrive % =

$$|(V_{SENSEx} - (V_{IT-(UV)} \text{ or } V_{IT+(OV)})) / V_{IT} \text{ (Nominal)} \times 100\% |$$

(1)

#### where:

- V<sub>SENSEx</sub> is the voltage at the SENSEx pin

- V<sub>IT</sub> (Nominal) is the nominal threshold voltage

- V<sub>IT-(UV)</sub> and V<sub>IT+(OV)</sub> represent the actual undervoltage or overvoltage tripping voltage

### 7.3.2.1.1 SENSEx Hysteresis

Overvoltage and undervoltage comparators include built-in hysteresis that provides noise immunity and ensures stable operation. For example, if the voltage on the SENSEx pin falls below  $V_{\text{IT-(UV)}}$  or above  $V_{\text{IT+(OV)}}$ , then  $\overline{\text{RESETx}}/\text{RESETx}$  is asserted. When the voltage on the SENSEx pin is between the positive and negative threshold voltages,  $\overline{\text{RESETx}}/\text{RESETx}$  deasserts after the set  $\overline{\text{RESETx}}/\text{RESETx}$  delay time. Figure 7-4 shows the relation between  $V_{\text{IT-(UV)}}, V_{\text{IT+(OV)}}$  and the hysteresis voltage ( $V_{\text{HYS}}$ ).

Figure 7-4. SENSEx Pin Hysteresis

#### 7.3.3 RESETX/RESETX

In a typical TPS3704x application, the RESETx/RESETx output is connected to a reset or enable input of a processor [such as a digital signal processor (DSP), application-specific integrated circuit (ASIC), or other processor type] or the enable input of a voltage regulator [such as a DC-DC converter or low-dropout regulator (LDO)].

The TPS3704x has open drain active low outputs that requires an external pull-up resistor to hold these lines high to the required voltage logic. Connect the external pull-up resistor to the proper voltage rail to enable the output to be connected to other devices at the correct interface voltage levels. To ensure proper voltage levels, give some consideration when choosing the external pull-up resistor values. The external pull-up resistor value is determined by  $V_{OL}$ , output capacitive loading, and output leakage current. These values are specified in Section 6.5. The open drain output can be connected as a wired-OR logic with the other  $\overline{RESETx}/RESETx$  open drain pins.

Figure 7-5. RESETx output

#### 7.4 Device Functional Modes

**Table 7-1. Functional Mode Truth Table**

| DESCRIPTION                | CONDITION                                            | VDD PIN                                   | OUTPUT RESETx /<br>(RESETx) PIN |

|----------------------------|------------------------------------------------------|-------------------------------------------|---------------------------------|

| Normal Operation           | $V_{IT-(UV)}$ < SENSEx < $V_{IT+(OV)}$               | $V_{DD} > V_{DD(MIN)}$                    | High / (Low)                    |

| Normal Operation (UV Only) | SENSEx > V <sub>IT-(UV)</sub>                        | $V_{DD} > V_{DD(MIN)}$                    | High / (Low)                    |

| Overvoltage detection      | SENSEx > V <sub>IT+(OV)</sub>                        | $V_{DD} > V_{DD(MIN)}$                    | Low / (High)                    |

| Undervoltage detection     | SENSEx < V <sub>IT-(UV)</sub>                        | $V_{DD} > V_{DD(MIN)}$                    | Low / (High)                    |

| UVLO engaged               | V <sub>IT-(UV)</sub> < SENSEx < V <sub>IT+(OV)</sub> | V <sub>POR</sub> < V <sub>DD</sub> < UVLO | Low / (High)                    |

### 7.4.1 Normal Operation $(V_{DD} > V_{DD(MIN)})$

When the voltage on  $V_{DD}$  is greater than  $V_{DD(MIN)}$  for approximately ( $t_{STRT} + t_D$ ), the  $\overline{RESETx}/RESETx$  output state will correspond to the SENSEx pin voltage with respect to the threshold limits, when SENSEx voltage is outside of threshold limits the  $\overline{RESETx}/RESETx$  voltage will be asserted.

### 7.4.2 Undervoltage Lockout (V<sub>POR</sub> < V<sub>DD</sub> < UVLO)

When the voltage on  $V_{DD}$  is less than the device UVLO voltage but greater than the power-on reset voltage  $(V_{POR})$ , the  $\overline{RESETx}/RESETx$  pin will be asserted, regardless of the voltage on SENSEx pin.

### 7.4.3 Power-On Reset $(V_{DD} < V_{POR})$

When the voltage on  $V_{DD}$  is lower than the required voltage ( $V_{POR}$ ) to internally pull the asserted output to GND, RESETx/RESETx signal is undefined and is not to be relied upon for proper device function.

## 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 8.1 Application Information

### 8.1.1 Voltage Threshold Accuracy

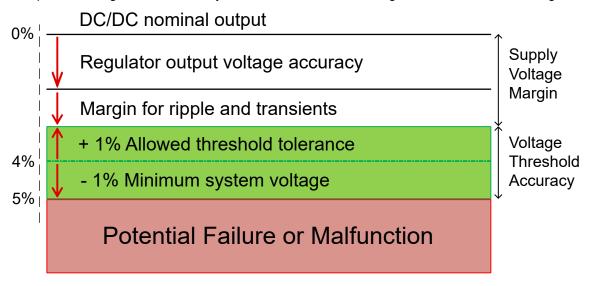

Voltage monitoring requirements vary depending on the voltage supply tolerance of the device being powered. Due to the high precision of the TPS3704x (±1% maximum), the device allows for a wider supply voltage margins and threshold headroom for tight tolerance applications.

For example, take a DC/DC regulator providing power to a core voltage rail of an MCU. The MCU has a tolerance of  $\pm 5\%$  of the nominal output voltage of the DC/DC. The user sets an ideal voltage threshold of  $\pm 4\%$  which allows for  $\pm 1\%$  of threshold accuracy. Since the TPS3704x threshold accuracy is  $\pm 1\%$ , the user has more supply voltage margin which can allow for a relaxed power supply design. This gives flexibility to the DC/DC to use a smaller output capacitor or inductor because of a larger voltage window for voltage ripple and transients. There is also headroom between the minimum system voltage and voltage tolerance of the MCU to ensure that the voltage supply will never be in the region of potential failure of malfunction without the TPS3704x asserting a reset signal.

Figure 8-1 illustrates the supply undervoltage margin and accuracy of the TPS3704x for the example explained above. Using a low accuracy supervisor will eat into the available budget for the power supply ripple and transient response. This gives less flexibility to the user and a more stringent DC/DC converter design.

Figure 8-1. TPS3704x Voltage Threshold Accuracy

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

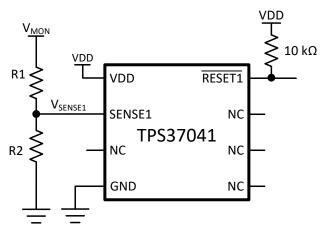

#### 8.1.2 Adjustable Voltage Thresholds

The TPS3704x maximum accuracy (1%) allows for adjustable voltage thresholds using external resistors without adding major inaccuracies to the device. In case that the desired monitored voltage is not available, external resistor dividers can be used to set the desired voltage thresholds. Figure 8-2 illustrates an example of how to adjust the voltage threshold with external resistor dividers. For assistance in calulating the external resistors access the TPS3704 adjustable threshold voltage resistor calculator in the Design Tools and Simulation section of the TPS3704 product page. The resistors can be calculated depending on the desired voltage threshold and device part number. TI recommends using an adjustable voltage threshold device variant because of the bypass mode of internal resistor ladder.

For example, consider a 2.0 V rail being monitored ( $V_{MON}$ ) using the TPS3704 0.8 V adjustable variant. Using Equation 2, R1 = 15 k $\Omega$  given that R2 = 10 k $\Omega$ ,  $V_{MON}$  = 2 V, and  $V_{SENSE1}$  = 0.8 V. This device is typically meant to monitor a 0.8 V rail with ±4% voltage thresholds. This means that the device undervoltage threshold ( $V_{IT+(DV)}$ ) and overvoltage threshold ( $V_{IT+(DV)}$ ) is 0.768 V and 0.832 V respectively. Using Equation 2,  $V_{MON}$  = 1.92 V when  $V_{SENSE1} = V_{IT-(UV)}$ . This can be denoted as  $V_{MON-}$ , the monitored undervoltage threshold where the device will assert a reset signal. Using Equation 2 again, the monitored overvoltage threshold ( $V_{MON+}$ ) = 2.08 V when  $V_{SENSE1} = V_{IT+(OV)}$ . If a wider tolerance or UV only threshold is desired, use a device variant shown on Table 9-2 to determine what device part number matches your application.

$$V_{SENSE1} = V_{MON} \times (R_2 / (R_1 + R_2))$$

(2)

There are inaccuracies that must be taken into consideration while adjusting voltage thresholds. Aside from the tolerance of the resistor divider, there is an internal resistance of the SENSE1 pin that may affect the accuracy of the resistor divider. Although expected to be very high impedance, users are recommended to calculate the values for design specifications. The internal sense resistance  $R_{SENSE1}$  can be calculated by the sense voltage  $V_{SENSE1}$  divided by the sense current  $I_{SENSE1}$  as shown in Equation 4.  $V_{SENSE1}$  can be calculated using Equation 2 depending on the resistor divider and monitored voltage.  $I_{SENSE1}$  can be calculated using Equation 3.

$$I_{SENSE1} = [(V_{MON} - V_{SENSE1}) / R_1] - (V_{SENSE1} / R_2)$$

(3)

Figure 8-2. Adjustable Voltage Threshold with External Resistor Dividers

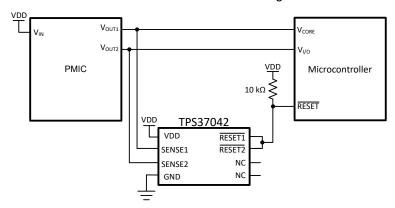

### 8.2 Typical Application

#### 8.2.1 Design 1: Multi-Rail Window Monitoring for Microcontroller Power Rails

A typical application for the TPS37042 is shown in Figure 8-3. The TPS37042 is used to monitor two PMIC voltage rails that powers the core and I/O voltage of the microcontroller that requires accurate reset delay and voltage supervision. It utilizes the TPS37042 to monitor the core voltage rail of a MCU similar to the circuit below.

Figure 8-3. TPS37042 Dual-Channel Monitoring Two Microcontroller Power Rails

### 8.2.1.1 Design Requirements

Table 8-1. Design Requirements

| PARAMETER                                      | DESIGN REQUIREMENT                                                                                                   | DESIGN RESULT                                                                                             |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Monitored rails                                | 3.3-V <sub>I/O</sub> nominal, with alerts if outside of ±8% of 3.3 V (including device accuracy), 10 ms reset delay  | Worst case V <sub>IT+(OV)</sub> = 3.533 V (7.06%)<br>Worst case V <sub>IT-(UV)</sub> = 3.071 V (-6.94%)   |

| Notificied fails                               | 1.2-V <sub>CORE</sub> nominal, with alerts if outside of ±5% of 1.2 V (including device accuracy), 10 ms reset delay | Worst case V <sub>IT+(OV)</sub> = 1.2484 V (4.03%)<br>Worst case V <sub>IT-(UV)</sub> = 1.1524 V (-3.97%) |

| Output logic voltage                           | 5-V CMOS                                                                                                             | 5-V CMOS                                                                                                  |

| Maximum system supervision current consumption | 25 μΑ                                                                                                                | 5.5 μA (15 μA max)                                                                                        |

#### 8.2.1.2 Detailed Design Procedure

Determine which version of the TPS3704x best suits the monitored rail ( $V_{MON}$ ) and window tolerances found on Table 9-2. The TPS3704x allows overvoltage and undervoltage monitoring for precise voltage supervision of common rails between 0.4 V and 5.55 V. This application calls for very tight monitoring of the rail with only  $\pm 5\%$  of variation allowed on the 1.2- $V_{CORE}$  rail. To ensure this requirement is met, the TPS37042 was chosen for its  $\pm 3\%$  thresholds. The 3.3- $V_{I/O}$  is more flexible and can operate up to 8% variance. Since the TPS3704x comes in various tolerance options, the  $\pm 6\%$  thresholds can be chosen for this voltage rail. To calculate the worst-case for  $V_{IT+(OV)}$  and  $V_{IT-(UV)}$ , the accuracy must also be taken into account. The worst-case for  $V_{IT+(OV)}$  and  $V_{IT-(UV)}$  can be calculated shown in Equation 5 and Equation 6 respectively:

$$V_{\text{IT+(OV-Worst Case)}} = V_{\text{MON}} \times (1 + \text{\%Threshold}) \times (1 + \text{\%Accuracy}) = 1.2 \times (1.03) \times (1.01) = 1.2484 \text{ V}$$

(5)

$$V_{\text{IT-(UV-Worst Case)}} = V_{\text{MON}} \times (1 - \text{\%Threshold}) \times (1 - \text{\%Accuracy}) = 1.2 \times (0.97) \times (0.99) = 1.1524V$$

(6)

Hysteresis is also needed to be taken into account when determining the OV and UV thresholds such that the release point after the fault is higher than the power supply tolerance limits. Refer to Figure 6-1 for more details.

When the outputs switch to a high impedance state, the rise time of the RESETx/RESETx pin depends on the pull-up resistance and the capacitance on that node. Choose pull-up resistors that satisfy both the downstream timing requirements and the sink current required to have a  $V_{OL}$  low enough for the application; 10 k $\Omega$  to 1 M $\Omega$  resistors are a good choice for low-capacitive loads.

## 8.2.2 Design 2: Manual Self-Test Option for Enhanced Functional Safety Use Cases

Figure 8-4 displays a self-test scheme where a manual self-test function can be implemented. Any SENSEx pin can be reserved and used to trigger a fault to be observed at the output, thus pre-checking the TPS3704 for fault detection. TPS3704 is a functional safety compliant multichannel supervisor and enables applications such as factory automation and motor drive achieve IEC 61508 requirements and industrial safety integrity levels. This example uses a TPS37044F, configured for separate undervoltage and overvoltage (UV/OV) outputs where the SENSE4 thresholds are set at 5.5 V for OV and 2 V for UV.

Figure 8-4. TPS37044F Quad-Channel Monitoring With Manual Self-Test Option for Functional Safety

#### 8.2.2.1 Design Requirements

Table 8-2. Design Requirements

| PARAMETER                    | DESIGN REQUIREMENT                                                                                              | DESIGN RESULT                                                                                      |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Monitored rails              | 3.3-V AVDD nominal, with alerts if outside of $\pm 4\%$ of 3.3 V (including device accuracy), 10-ms reset delay | Worst case V <sub>IT+(OV)</sub> = 3.432 V (+4%)<br>Worst case V <sub>IT-(UV)</sub> = 3.168 V (-4%) |

|                              | 1.8-V IOVDD nominal, with alerts if outside of ±4% of 1.8 V (including device accuracy), 10-ms reset delay      | Worst case V <sub>IT+(OV)</sub> = 1.872 V (+4%)<br>Worst case V <sub>IT-(UV)</sub> = 1.728 V (-4%) |

|                              | 1.2-V DVDD nominal, with alerts if outside of ±4% of 1.2 V (including device accuracy), 10-ms reset delay       | Worst case V <sub>IT+(OV)</sub> = 1.248 V (+4%)<br>Worst case V <sub>IT-(UV)</sub> = 1.152 V (-4%) |

| SENSE4<br>(Self-test Option) | 100-kΩ pullup resistor to VDD with NFET pulldown transistor to GND                                              | UV_Trig = High - causing SENSE4 pin going low UV_Trig = Low - in normal operation                  |

| Output logic voltage         | 5-V CMOS                                                                                                        | 5-V CMOS                                                                                           |

| Max system<br>IDD current    | 25 μΑ                                                                                                           | 5.5 μA (20 μA maximum)                                                                             |

#### 8.2.2.2 Detailed Design Procedure

Figure 8-4 shows a self-test scheme where a manual self-test function can be implemented. SENSE4 has an overvoltage (OV) threshold that is set at 5.5 V and the undervoltage (UV) threshold set at 2 V. SENSE4 can be connected via a  $100\text{-k}\Omega$  resistor to VDD. The self-test setup gives the added benefit of a built-in overvoltage detector for the rail powering the TPS37044F. From a functional safety perspective, a voltage supervisor cannot be considered reliable if the supervisor is operating outside its recommended operated limits.

To trigger a manual self-test, pull UV\_Trig high to cause SENSE4 to be logic low, therefore triggering an undervoltage (UV) fault. The UV fault appears at RESET2 as an asserted low signal. By tying both reset outputs to an NMI or interrupt input of the processor, this self-test option scheme serves as a purpose to ensure that RESET2, of the TPS37044F is operating properly. For more information on functional safety, see the Functional Safety Manual.

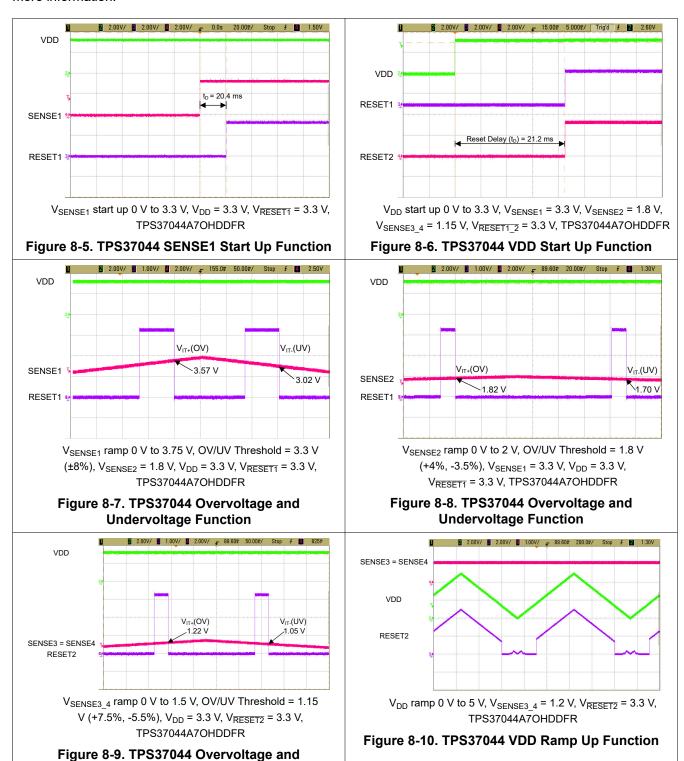

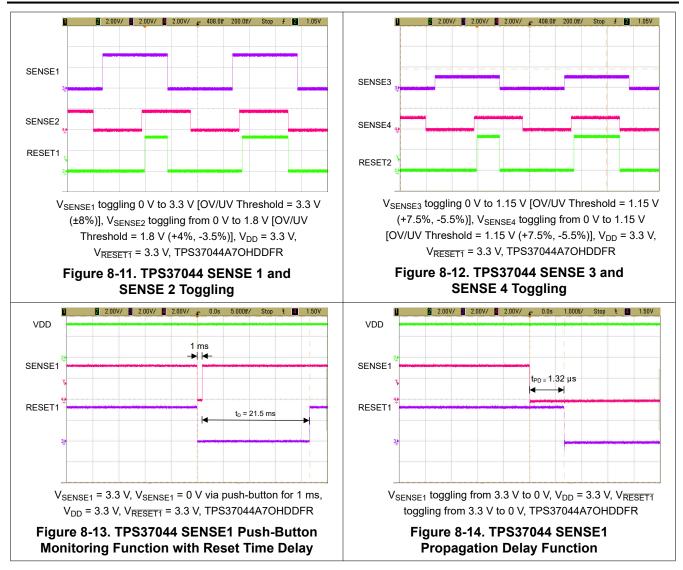

#### 8.2.3 Application Curves

These application curves were taken with the TPS3704Q1EVM. Please see the TPS3704Q1EVM User Guide for more information.

**Undervoltage Function**

### 8.3 Power Supply Recommendations

#### 8.3.1 Power Supply Guidelines

This device is designed to operate from an input supply with a voltage range between 1.7 V to 6 V. It has a 6.5 V absolute maximum rating on the VDD pin. It is good analog practice to place a 0.1  $\mu$ F to 1  $\mu$ F capacitor between the VDD pin and the GND pin depending on the input voltage supply noise. If the voltage supply providing power to VDD is susceptible to any large voltage transient that exceed maximum specifications, additional precautions must be taken. See SNVA849 for more information.

Product Folder Links: TPS3704

Copyright © 2023 Texas Instruments Incorporated

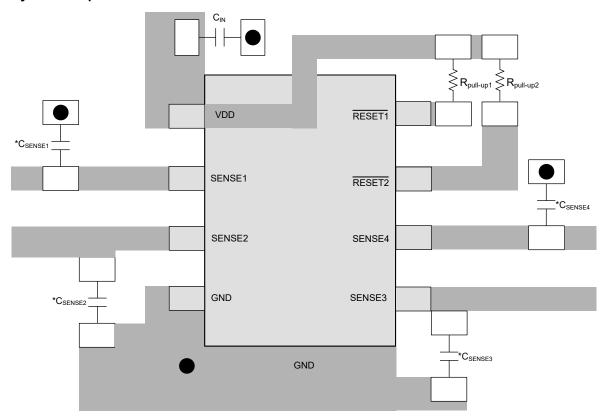

### 8.4 Layout

#### 8.4.1 Layout Guidelines

- Place the external components as close to the device as possible. This configuration prevents parasitic errors from occurring.

- Avoid using long traces for the VDD supply node. The VDD capacitor, along with parasitic inductance from the supply to the capacitor, can form an LC circuit and create ringing with peak voltages above the maximum VDD voltage.

- Avoid using long traces of voltage to the sense pin. Long traces increase parasitic inductance and cause inaccurate monitoring and diagnostics.

- If SENSEx capacitors (C<sub>SENSEx</sub>) are used, place the capacitors as close as possible to the SENSEx pins to further improve the noise immunity on the SENSEx pins. Placing a 10 nF to 100 nF capacitors between the SENSEx pins and GND can reduce the sensitivity to transient voltages on the monitored signal.

- Do not run sensitive analog traces in parallel with digital traces. Avoid crossing digital and analog traces if

possible, and only make perpendicular crossings when absolutely necessary.

#### 8.4.2 Layout Example

Vias used to connect pins for application-specific connections

\*C<sub>SENSEx</sub> capacitors can be added for improve noise immunity

Figure 8-15. Recommended Layout

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# 9 Device and Documentation Support

## 9.1 Device Nomenclature

Figure 4-1 in Section 4 and Table 9-1 shows how to decode the function of the device based on its part number shown in Table 9-2.

**Table 9-1. Device Naming Convention**

| DESCRIPTION                    | NOMENCLATURE | VALUE                          |

|--------------------------------|--------------|--------------------------------|

| Generic Part number            | TPS3704x     | TPS3704x                       |

| Channel Option                 | 1            | One-channel option             |

|                                | 2            | Dual-channel option            |

|                                | 3            | Triple-channel option          |

|                                | 4            | Quad-channel option            |

| Detection Options              | Ax, Bx, Cx,  | Please refer to Table 9-2      |

| Variant code (Output Topology) | 0            | Open-Drain, Active-Low         |

|                                | L            | Push-Pull, Active-Low          |

|                                | Н            | Push-Pull, Active-High         |

| Reset Time Delay Option        | A            | 20 μs reset time delay         |

|                                | В            | 1 ms reset time delay          |

|                                | С            | 2 ms reset time delay          |

|                                | D            | 3 ms reset time delay          |

|                                | E            | 5 ms reset time delay          |

|                                | F            | 10 ms reset time delay         |

|                                | G            | 15 ms reset time delay         |

|                                | Н            | 20 ms reset time delay         |

|                                | I            | 25 ms reset time delay         |

|                                | J            | 35 ms reset time delay         |

|                                | К            | 40 ms reset time delay         |

|                                | L            | 50 ms reset time delay         |

|                                | M            | 70 ms reset time delay         |

|                                | N            | 100 ms reset time delay        |

|                                | 0            | 140 ms reset time delay        |

|                                | P            | 150 ms reset time delay        |

|                                | R            | 200 ms reset time delay        |

|                                | S            | 280 ms reset time delay        |

|                                | Т            | 400 ms reset time delay        |

|                                | U            | 560 ms reset time delay        |

|                                | V            | 800 ms reset time delay        |

|                                | W            | 1120 ms reset time delay       |

|                                | Х            | 1200 ms reset time delay       |

| Package                        | DDF          | SOT-23 8-pin (1.6 mm × 2.9 mm) |

| Reel                           | R            | Large Reel                     |

#### Table 9-2. Device Threshold Table

| Table 5-2. Device Tilleshold Table |                        |                 |               |                           |                           |                           |                           |  |  |  |  |

|------------------------------------|------------------------|-----------------|---------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| ORDERABLE PART NAME                | VARIANT <sup>(3)</sup> | NUM OF<br>CHAN. | RESET<br>TIME | SENSE1 <sup>(1)</sup> (2) | SENSE2 <sup>(1)</sup> (2) | SENSE3 <sup>(1)</sup> (2) | SENSE4 <sup>(1)</sup> (2) |  |  |  |  |

| TPS37042BJOFDDFRQ1                 | ADJ                    | 2               | 10ms          | 0.8V (±4%)                | 0.8V (±4%)                | -                         | -                         |  |  |  |  |

| TPS37042A3OFDDFRQ1                 | Fixed                  | 2               | 10ms          | 3.3V (±5%)                | 1.2V (±5%)                | -                         | -                         |  |  |  |  |

| TPS37042ZJOFDDFRQ1                 | Fixed                  | 2               | 10ms          | 1.95V (±4%)               | 3.8V (±6%)                | -                         | -                         |  |  |  |  |

| TPS37043DJOFDDFR                   | ADJ/Fixed              | 3               | 10 ms         | 3.3V (-11%)               | 1.2V (-11%)               | 0.8V (-8%)                | -                         |  |  |  |  |

| TPS37043A4OFDDFRQ1                 | Fixed                  | 3               | 10ms          | 2.8V (±5%)                | 1.8V (±5%)                | 1.2V (±5%)                | -                         |  |  |  |  |

| TPS37043A8OFDDFRQ1                 | Fixed                  | 3               | 10ms          | 3.3V (±5%)                | 1.8V (±5%)                | 1.0V (±5%)                | -                         |  |  |  |  |

| TPS37043CPOFDDFRQ1                 | ADJ/Fixed              | 3               | 10ms          | 3.3V (±4%)                | 0.75V (±4%)               | 0.8V (±3%)                | -                         |  |  |  |  |

| TPS37043ZJOFDDFRQ1                 | Fixed                  | 3               | 10ms          | 0.95V (±4%)               | 1.35V (±4%)               | 1.8V (±4%)                | -                         |  |  |  |  |

| TPS37043LJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.4V (±5%)                | 0.4V (±5%)                | 0.8V (±5%)                | -                         |  |  |  |  |

| TPS37043CJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.8V (±6%)                | 0.8V (±6%)                | 0.8V (±6%)                | -                         |  |  |  |  |

| TPS37043MJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.4V (±7%)                | 0.4V (±7%)                | 0.8V (±7%)                | -                         |  |  |  |  |

| TPS37043A5OFDDFRQ1                 | Fixed                  | 3               | 10ms          | 3.3V (±4%)                | 1.8V (±4%)                | 1.2V (±4%)                | -                         |  |  |  |  |

| TPS37043BJOFDDFRQ1                 | ADJ                    | 3               | 10ms          | 0.8V (±4%)                | 0.8V (±4%)                | 0.8V (±4%)                | -                         |  |  |  |  |

| TPS37044BJOFDDFR                   | ADJ                    | 4               | 10 ms         | 0.8 V (±4%)               | 0.8 V (±4%)               | 0.8 V (±4%)               | 0.8 V (±4%)               |  |  |  |  |

| TPS37044LJOJDDFR                   | ADJ                    | 4               | 35ms          | 0.4V (±5%)                | 0.4V (±5%)                | 0.8V (±5%)                | 0.8V (±5%)                |  |  |  |  |

| TPS37044BJOFDDFRQ1                 | ADJ                    | 4               | 10ms          | 0.8V (±4%)                | 0.8V (±4%)                | 0.8V (±4%)                | 0.8V (±4%)                |  |  |  |  |

| TPS37044CJOFDDFRQ1                 | ADJ                    | 4               | 10ms          | 0.8V (±6%)                | 0.8V (±6%)                | 0.8V (±6%)                | 0.8V (±6%)                |  |  |  |  |

| TPS37044MJOFDDFRQ1                 | ADJ                    | 4               | 10ms          | 0.4V (±7%)                | 0.4V (±7%)                | 0.8V (±7%)                | 0.8V (±7%)                |  |  |  |  |

| TPS37044A4OGDDFRQ1                 | Fixed                  | 4               | 15ms          | 3.3V (±8%)                | 1.8V (±4%)                | 1.15V (±6%)               | 1.15V (±6%)               |  |  |  |  |

- (1) Listed percentage denotes window tolerance, see Figure 6-1 for more information

- (2) VIT threshold of 0.8V and 0.4V signifies an adjustable channel

- (3) ADJ denotes an adjustable voltage threshold set by an external resistor divider, see Section 8.1.2 for more information

### 9.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Notifications* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 9.3 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 9.4 Trademarks

TI E2E™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

## 9.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 9.6 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

## **10 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (September 2022) to Revision E (December 2023)   | Page |

|--------------------------------------------------------------------------|------|

| Remove TPS37044UJOFDDFR and TPS37044GJONDDFR from Device Threshold Table | e3   |

| Remove single channel pin-out                                            |      |

| Remove TPS37044UJOFDDFR and TPS37044GJONDDFR from Device Threshold Table |      |

| Changes from Revision C (September 2022) to Revision D (September 2023)  | Page |

| Clarifying text added to window tolerance specification                  |      |

| Highlighted presence of device threshold table and calculator tool       |      |

| Removed reference to single channel and condenced verbiage               |      |

| Addition of Table 4-1                                                    |      |

| Clarifying text added to window tolerance specification in Figure 6-1    |      |

| Removed reference to single channel supervisor                           |      |

| Removed single channel block diagram                                     | 16   |

| Addition of reference to adjustable threshold resistor calculator        | 22   |

| Orderable part name additions to Table 9-2                               | 28   |

| Changes from Revision B (November 2021) to Revision C (September 2022)   | Page |

| Added Functional Safety information                                      | 1    |

| Added Manual Self-Test Option Section                                    |      |

| Changes from Revision A (July 2021) to Revision B (November 2021)        | Page |

| Change from Advance Information to Production Data                       |      |

## 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins        | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       | . ,    | . ,           |                       |                       | (-)  | (4)                           | (5)                        |              | (-,              |

| TPS37043DJOFDDFR      | Active | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 3DJOF            |

| TPS37043DJOFDDFR.A    | Active | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 3DJOF            |

| TPS37044BJOFDDFR      | Active | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 4BJOF            |

| TPS37044BJOFDDFR.A    | Active | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 4BJOF            |

| TPS37044LJOJDDFR      | Active | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 4LJOJ            |

| TPS37044LJOJDDFR.A    | Active | Production    | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 4LJOJ            |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# PACKAGE OPTION ADDENDUM

www.ti.com 9-Nov-2025

#### OTHER QUALIFIED VERSIONS OF TPS3704:

Automotive: TPS3704-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 7-Dec-2023

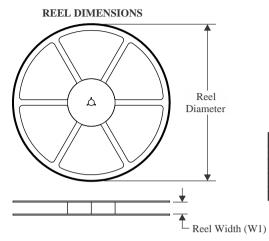

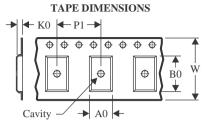

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

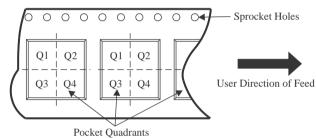

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS37043DJOFDDFR | SOT-23-<br>THIN | DDF                | 8 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS37044BJOFDDFR | SOT-23-<br>THIN | DDF                | 8 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| TPS37044LJOJDDFR | SOT-23-<br>THIN | DDF                | 8 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

www.ti.com 7-Dec-2023

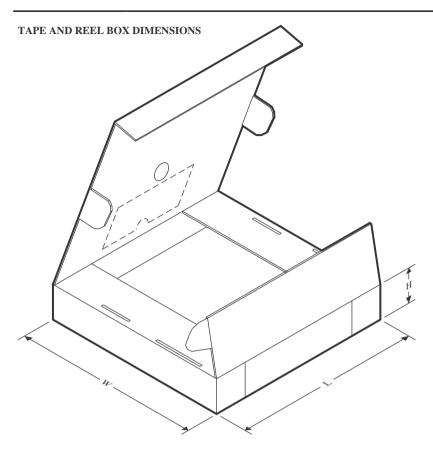

## \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS37043DJOFDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS37044BJOFDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS37044LJOJDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

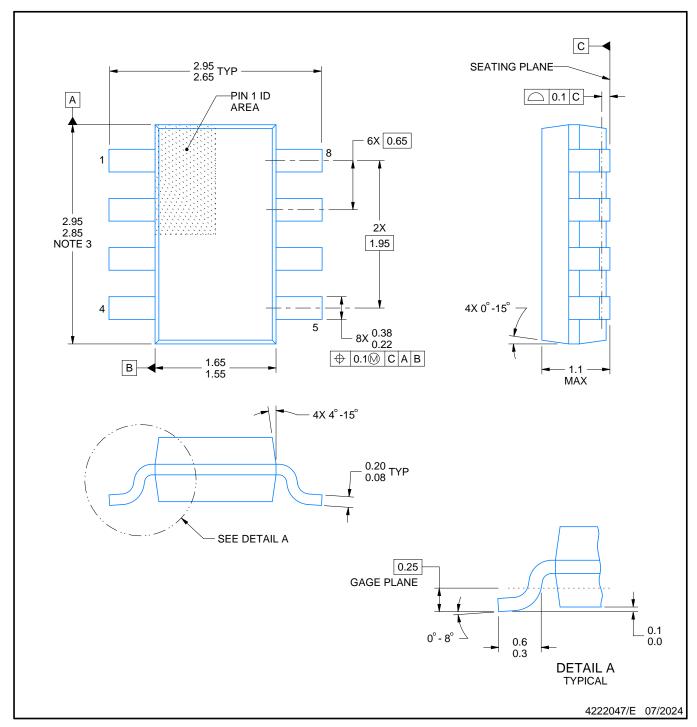

PLASTIC SMALL OUTLINE

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

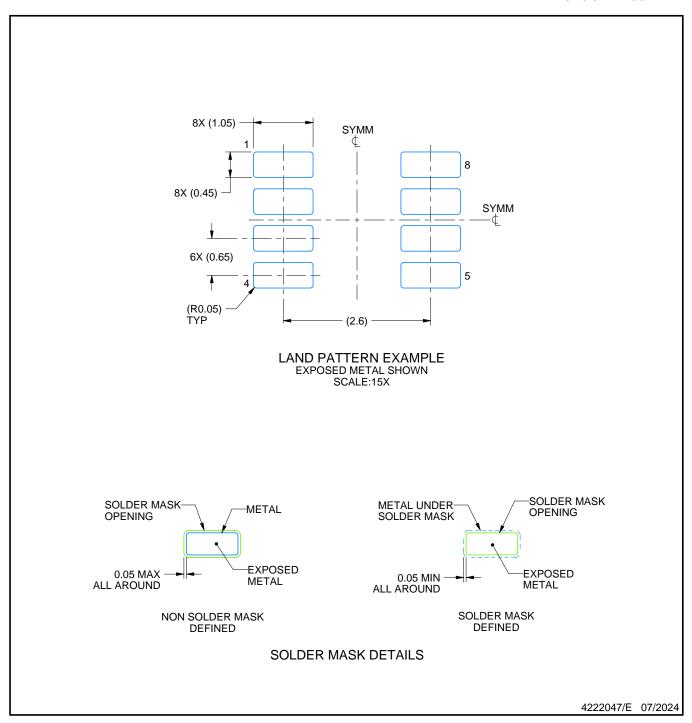

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 4. Publication IPC-7351 may have alternate designs.

- 5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

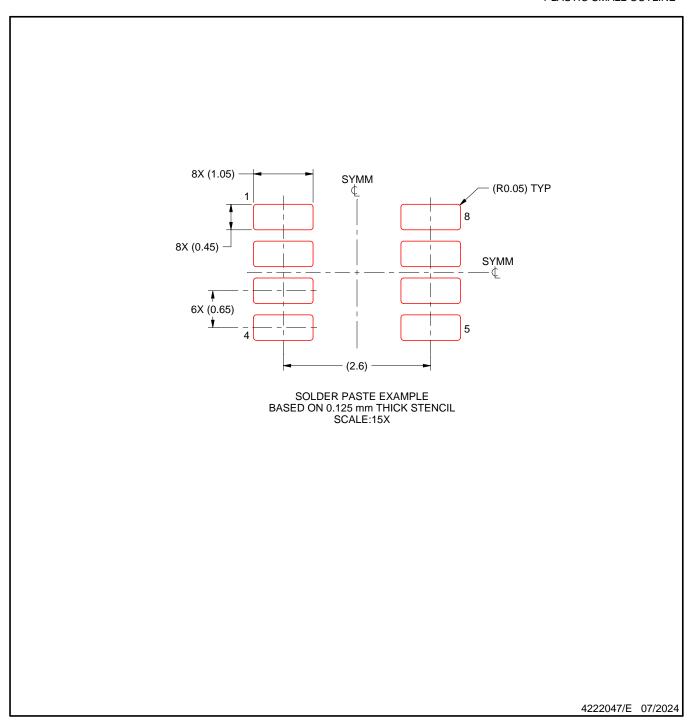

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 7. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER