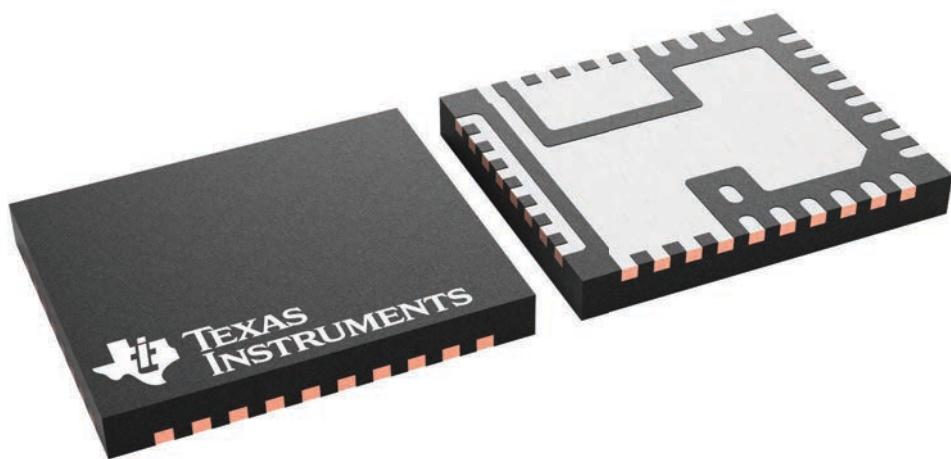

# TPS544C26 4-V to 16-V Input, 35-A Synchronous Buck Converter With SVID And I<sup>2</sup>C Interfaces

## 1 Features

- Single chip power supply for SVID rails

- Intel® VR13 SVID compliant

- I<sup>2</sup>C interface with NVM for configuration, telemetry (V/I/T) and fault reporting

- Input power monitoring for DDR5 memory RAPL

- Integrated 4.0-mΩ and 1.0-mΩ MOSFETs for 35-A continuous current operation

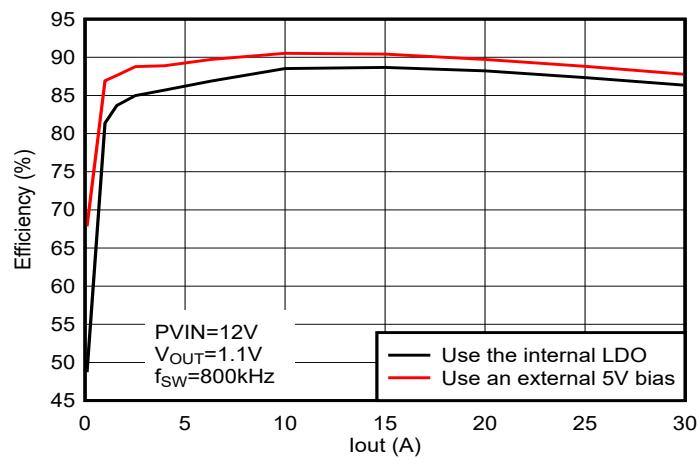

- Supports external 5-V bias improving efficiency and enabling 2.7-V minimum input voltage

- V<sub>OUT</sub> programmable from 0.25 V to 3.04 V

- Precision voltage reference and differential remote sense for high output accuracy

- ±0.5% V<sub>OUT</sub> tolerance from 0°C to 85°C T<sub>J</sub>

- ±1% V<sub>OUT</sub> tolerance from -40°C to 125°C T<sub>J</sub>

- D-CAP+™ control topology with fast transient response, supporting all ceramic output capacitors

- Programmable internal loop compensation including droop

- Selectable cycle-by-cycle valley current limit

- Selectable operation frequency 0.6 MHz to 1.2 MHz with DCM or FCCM operation

- Safe start-up into pre-biased outputs

- Programmable soft-start time from 1 ms to 16 ms

- Programmable soft-stop time from 0.5 ms to 4 ms

- Open-drain power-good output (VRRDY) and Catastrophic fault indicator (CAT\_FAULT#)

- Programmable overcurrent, overvoltage, undervoltage, overtemperature protections

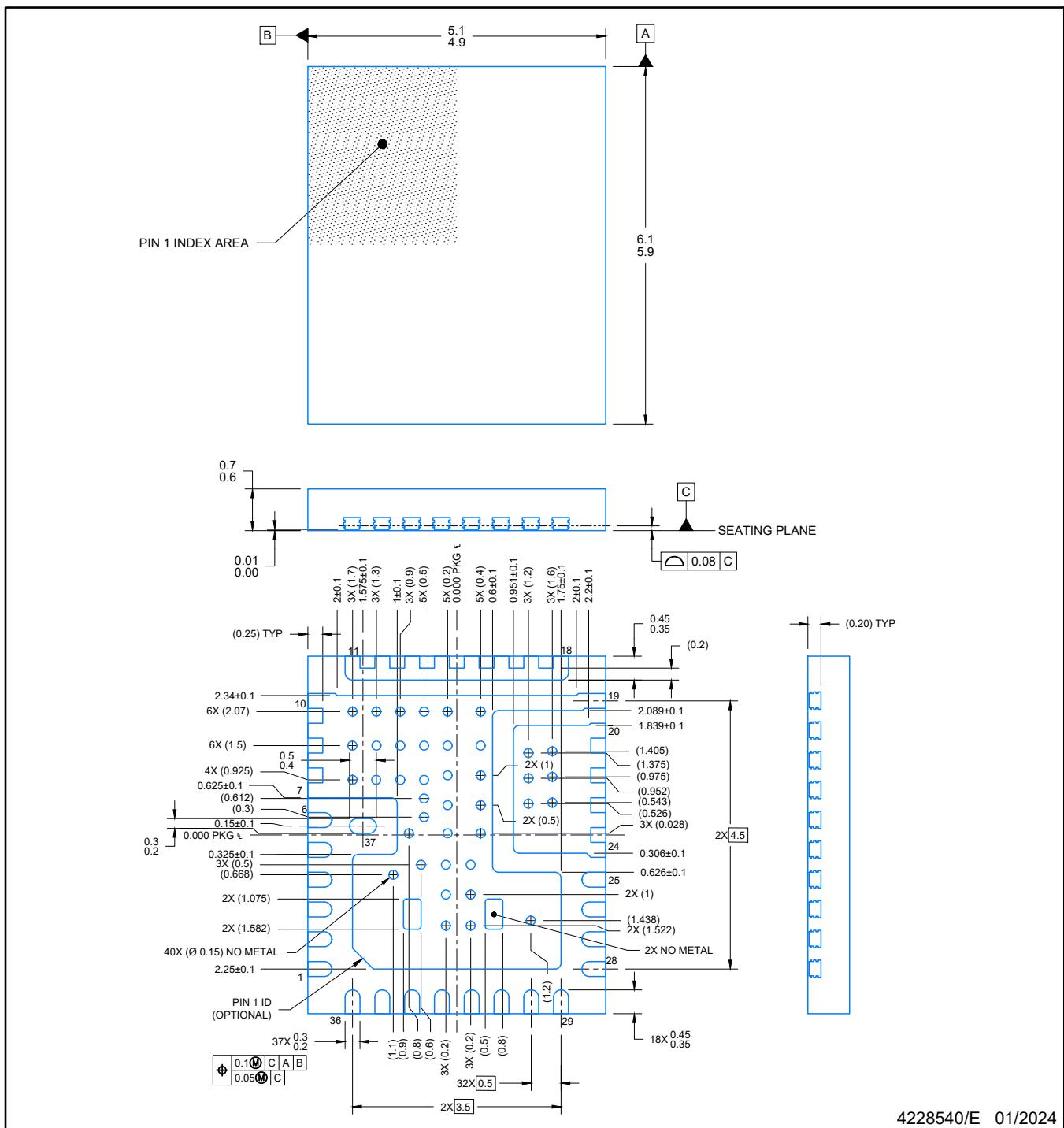

- 5 mm × 6 mm, 37-pin WQFN-FCRLF package

- TPS548C26 non-SVID/I<sup>2</sup>C analog converter in the same package available soon

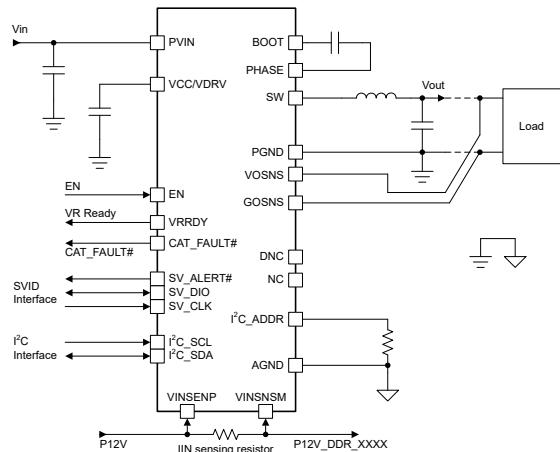

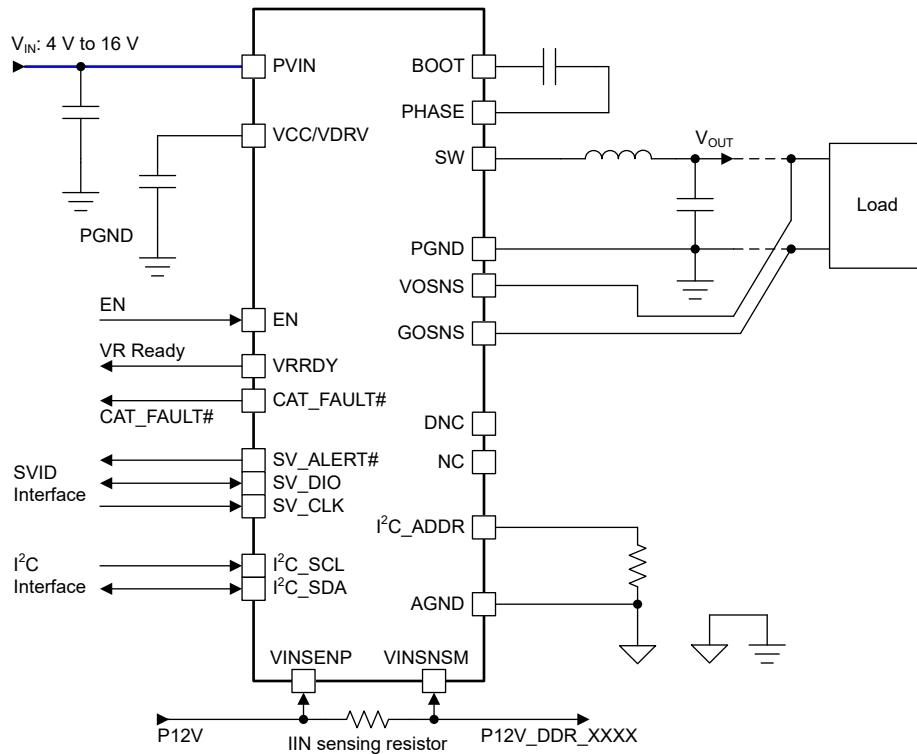

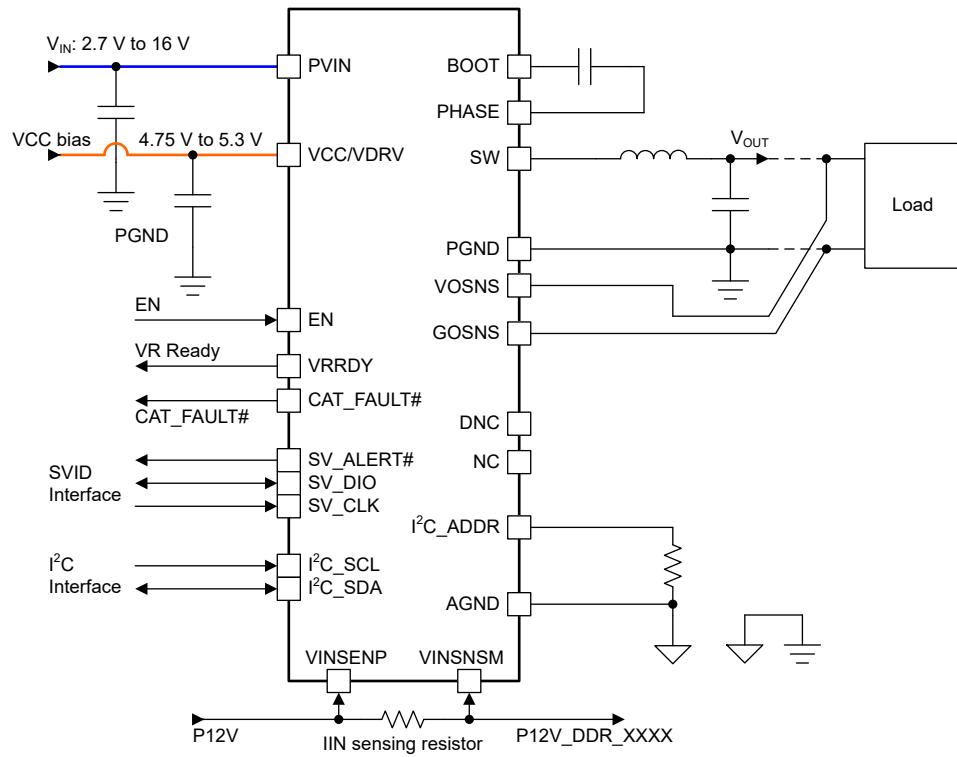

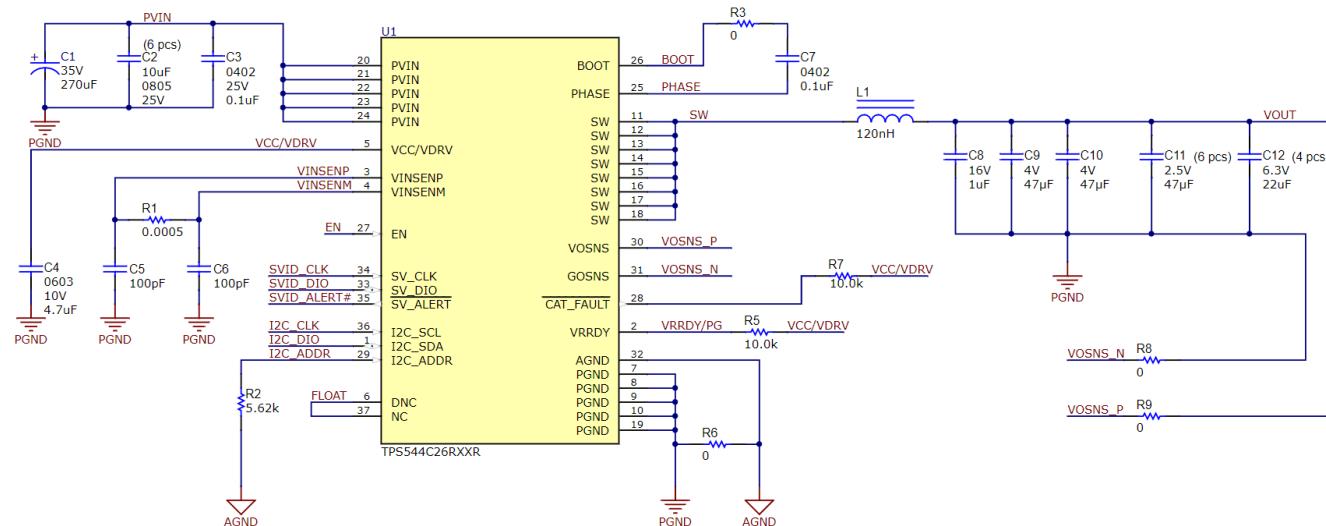

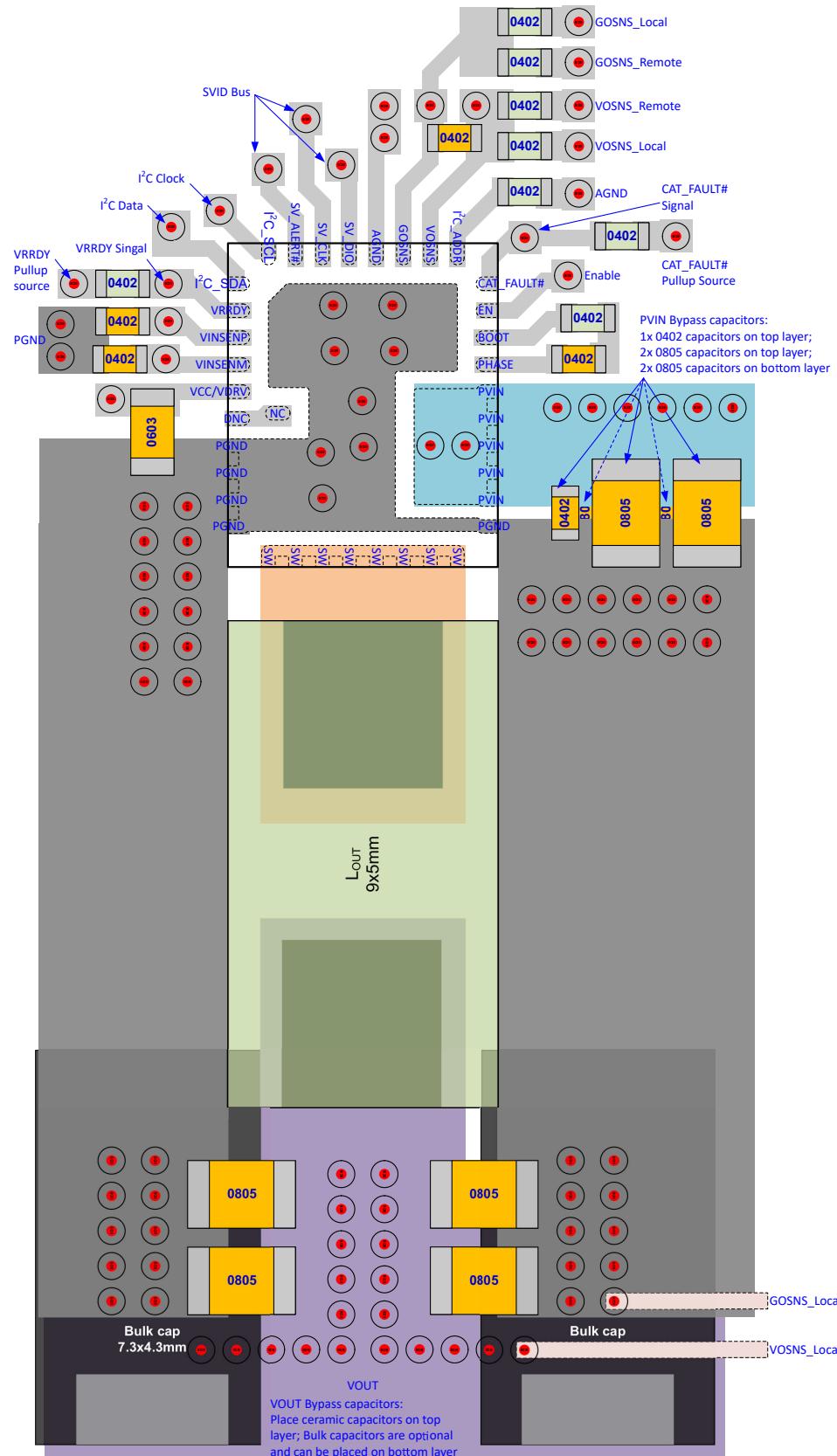

**Simplified Schematic**

## 2 Applications

- Server and cloud-computing POLs

- Hardware accelerator

- Network interface card

## 3 Description

The TPS544C26 device is a highly integrated buck converter with D-CAP+ control topology for the fast transient response. All programmable parameters can be configured by the I<sup>2</sup>C interface and stored in NVM as the new default values to minimize the external component count. These features make the device well-suited for space-constrained applications.

The TPS544C26 device is designed to work with Intel CPUs and fits well for single-phase, low-to-mid current SVID rails in Intel's server and SoC platforms.

Fault management and status reports for the Overcurrent limit, V<sub>OUT</sub> OVF/UVF, and OTF are provided on the device. The TPS544C26 device provides a full set of telemetry, including V<sub>OUT</sub>, I<sub>OUT</sub>, and IC temperature. Additionally, input power monitoring through an external sensing resistor is provided for board-level power management.

The TPS544C26 device is a lead-free device and is RoHS compliant without exemption.

## Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| TPS544C26   | RXX (WQFN-FCRLF, 37)   | 5.00 mm × 6.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

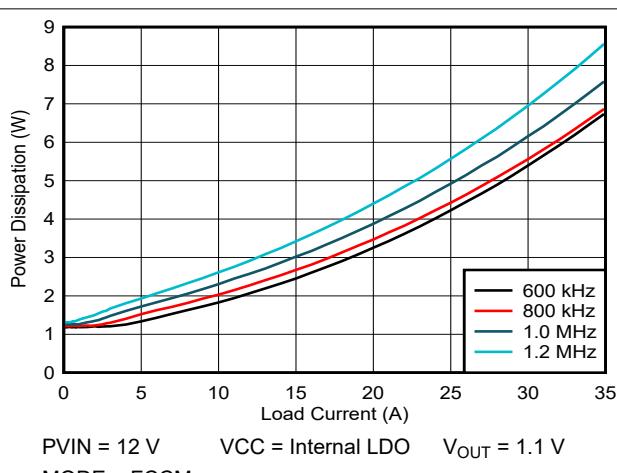

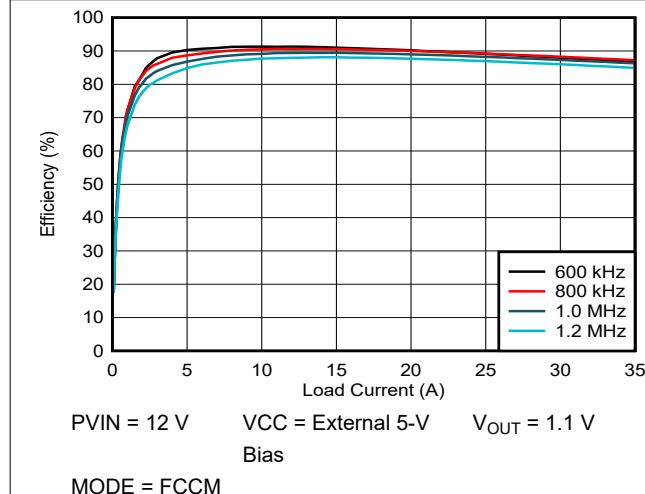

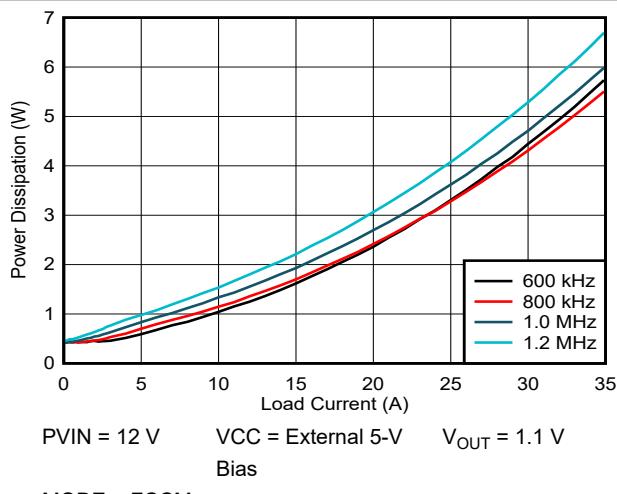

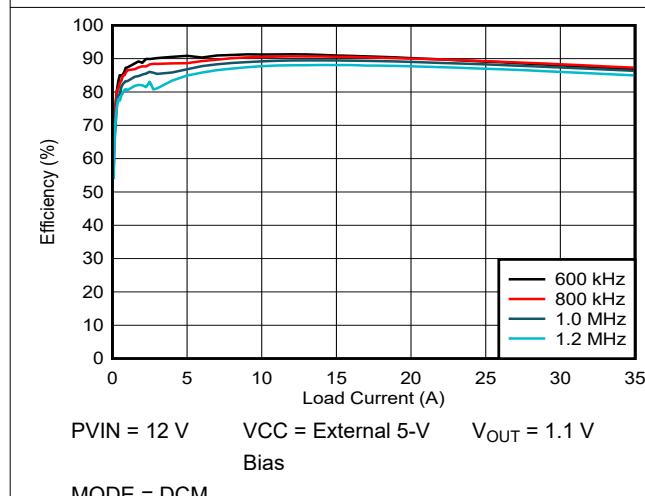

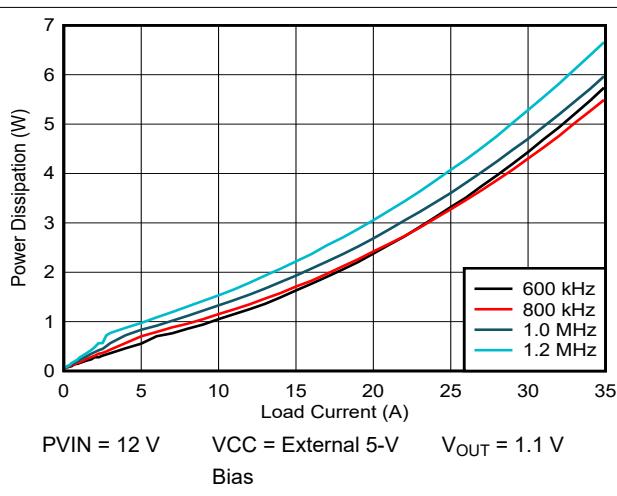

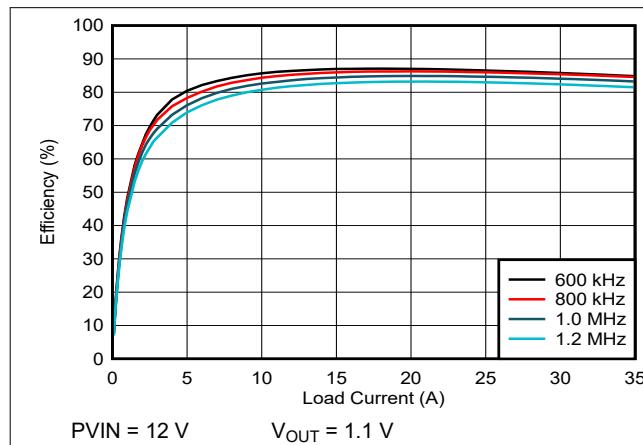

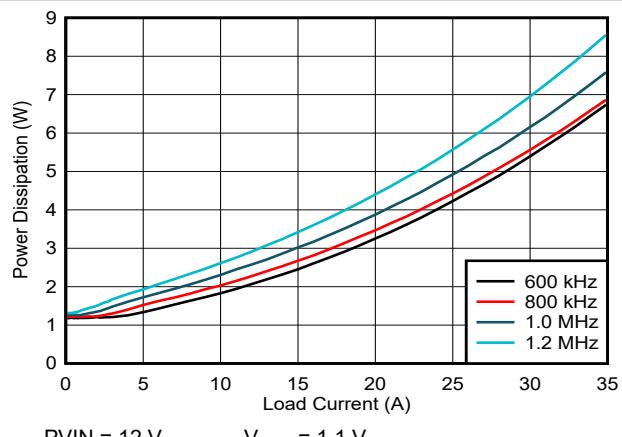

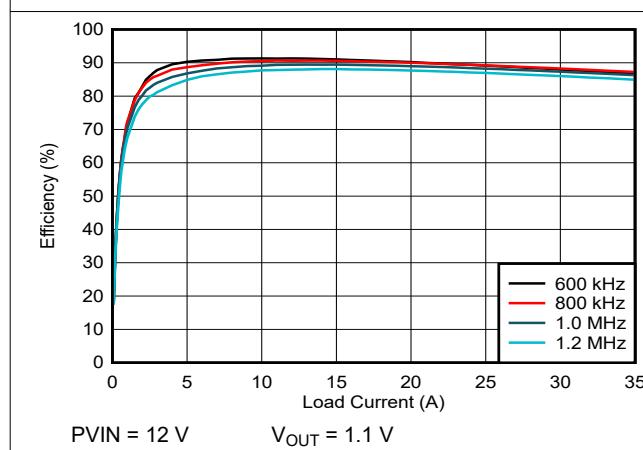

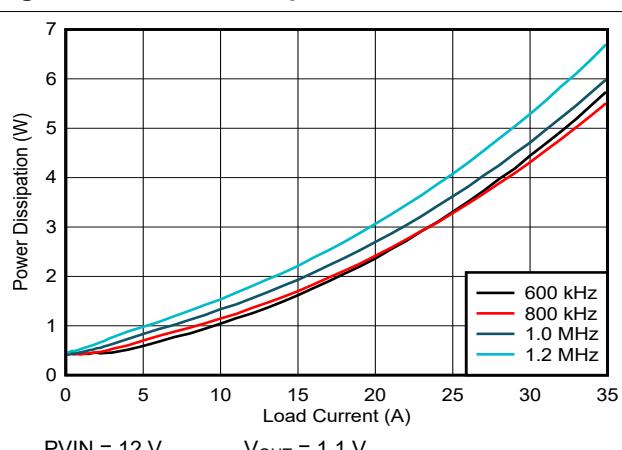

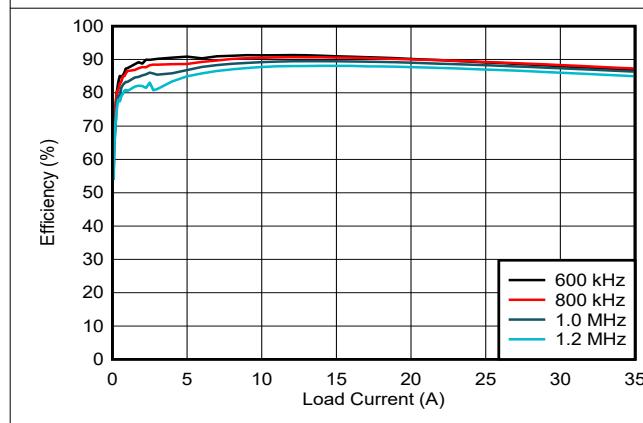

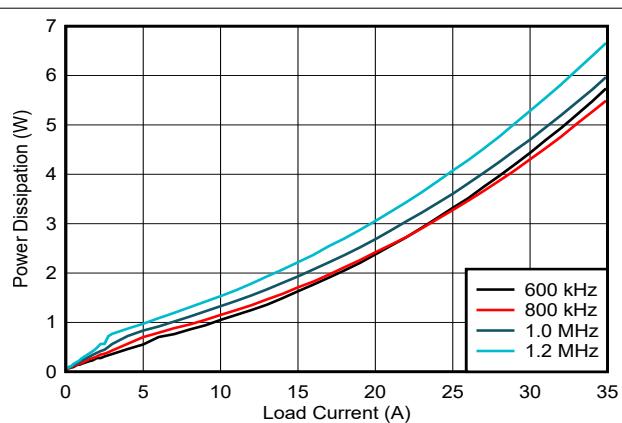

**Typical Efficiency**

## Table of Contents

|                                                |           |                                                                            |            |

|------------------------------------------------|-----------|----------------------------------------------------------------------------|------------|

| <b>1 Features</b> .....                        | <b>1</b>  | 7.5 Programming.....                                                       | <b>37</b>  |

| <b>2 Applications</b> .....                    | <b>1</b>  | 7.6 Register Maps.....                                                     | <b>42</b>  |

| <b>3 Description</b> .....                     | <b>1</b>  | <b>8 Application and Implementation</b> .....                              | <b>116</b> |

| <b>4 Revision History</b> .....                | <b>2</b>  | 8.1 Application Information.....                                           | <b>116</b> |

| <b>5 Pin Configuration and Functions</b> ..... | <b>3</b>  | 8.2 Typical Application.....                                               | <b>116</b> |

| <b>6 Specifications</b> .....                  | <b>5</b>  | 8.3 Power Supply Recommendations.....                                      | <b>120</b> |

| 6.1 Absolute Maximum Ratings.....              | 5         | 8.4 Layout.....                                                            | <b>121</b> |

| 6.2 ESD Ratings.....                           | 5         | <b>9 Device and Documentation Support</b> .....                            | <b>124</b> |

| 6.3 Recommended Operating Conditions.....      | 5         | 9.1 Documentation Support.....                                             | <b>124</b> |

| 6.4 Thermal Information.....                   | 6         | 9.2 Receiving Notification of Documentation Updates.....                   | <b>124</b> |

| 6.5 Electrical Characteristics.....            | 6         | 9.3 Support Resources.....                                                 | <b>124</b> |

| 6.6 Typical Characteristics.....               | 15        | 9.4 Trademarks.....                                                        | <b>124</b> |

| <b>7 Detailed Description</b> .....            | <b>16</b> | 9.5 Electrostatic Discharge Caution.....                                   | <b>124</b> |

| 7.1 Overview.....                              | 16        | 9.6 Glossary.....                                                          | <b>124</b> |

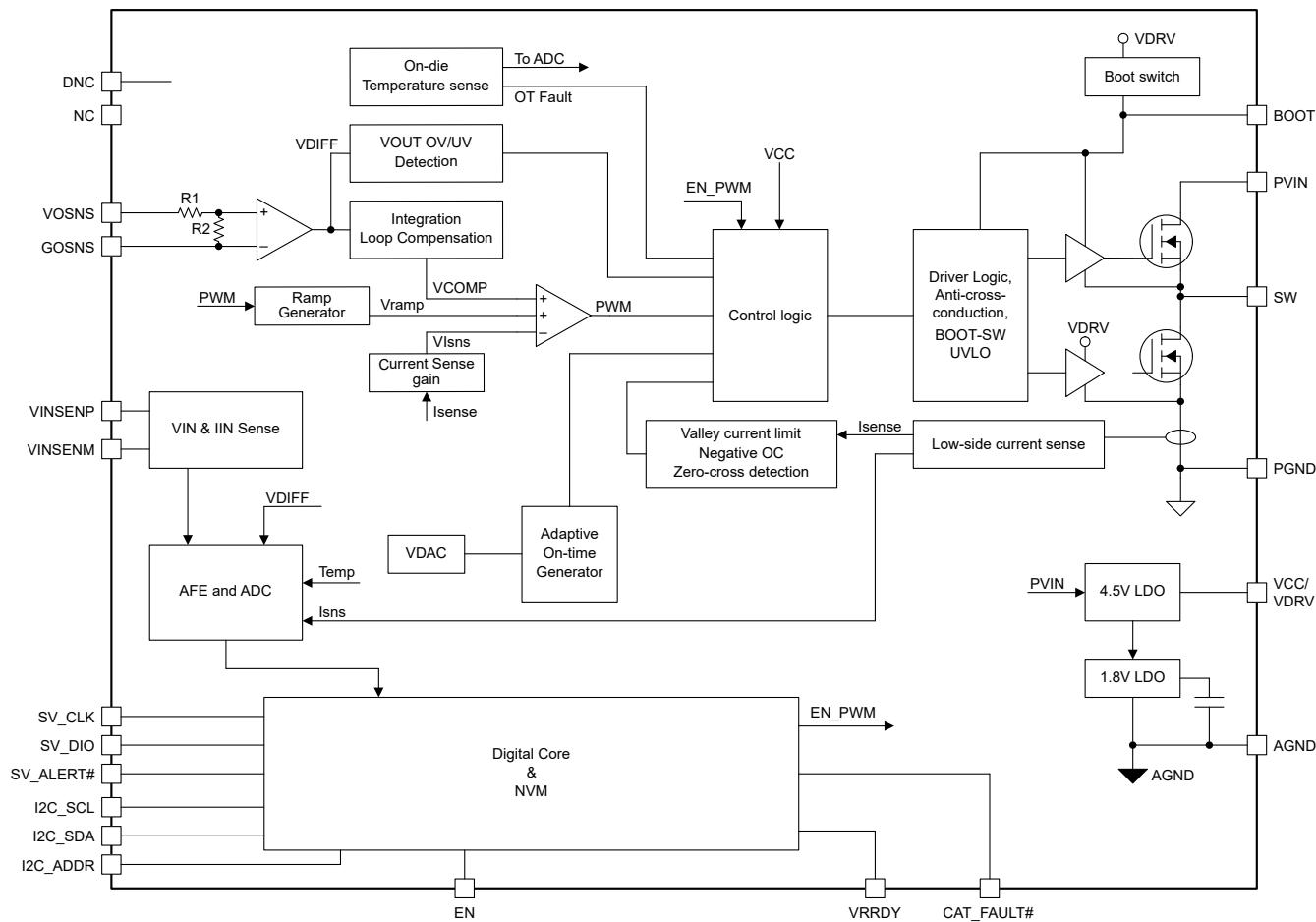

| 7.2 Functional Block Diagram.....              | 16        | <b>10 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>125</b> |

| 7.3 Feature Description.....                   | 16        |                                                                            |            |

| 7.4 Device Functional Modes.....               | 35        |                                                                            |            |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2022 | *        | Initial release |

## 5 Pin Configuration and Functions

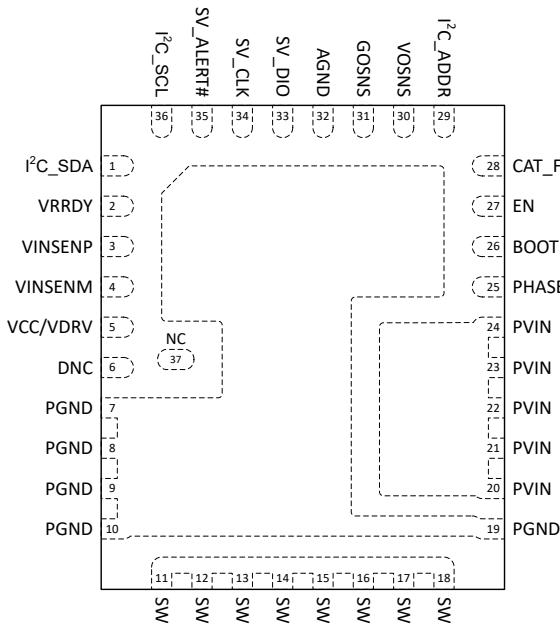

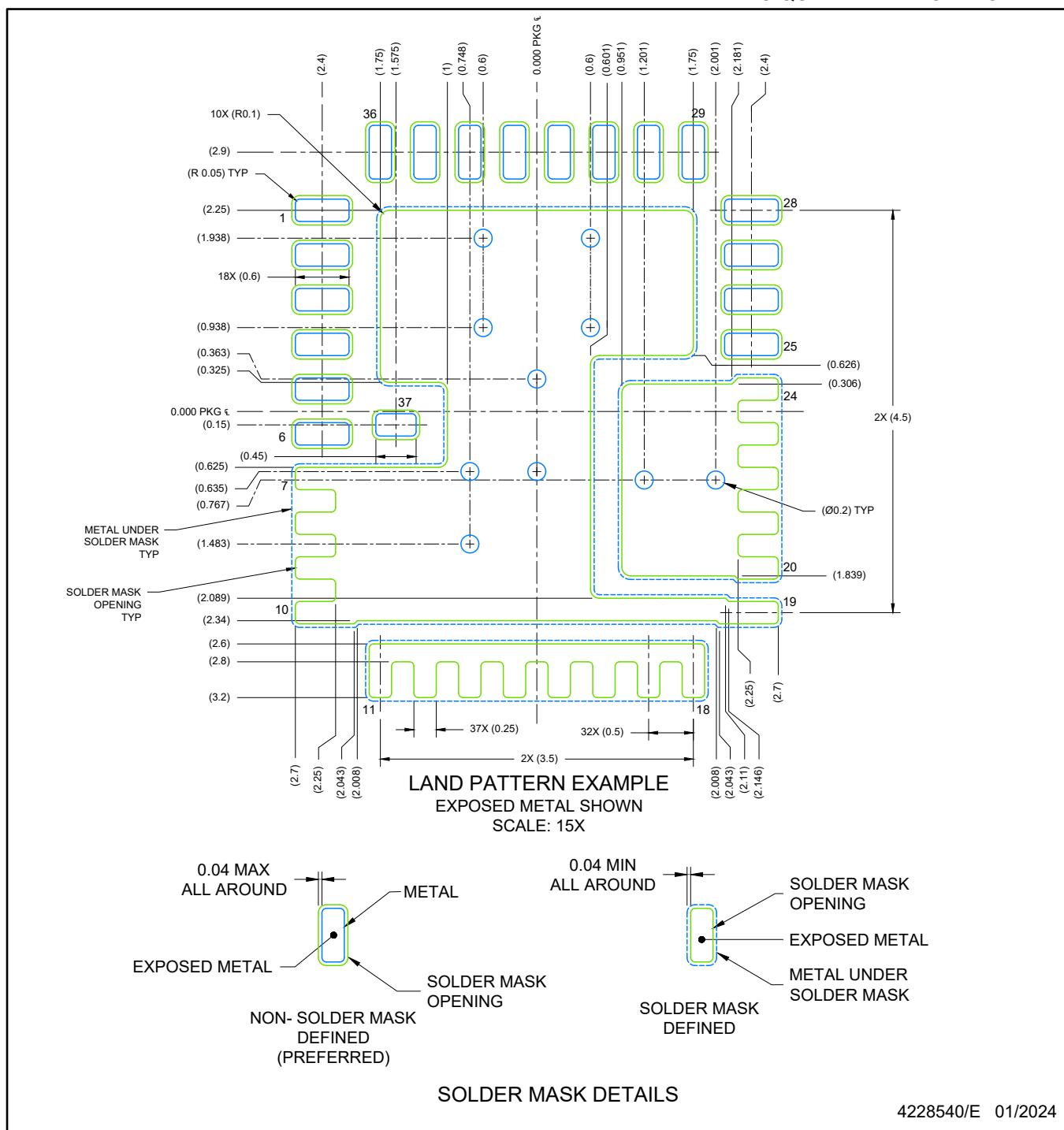

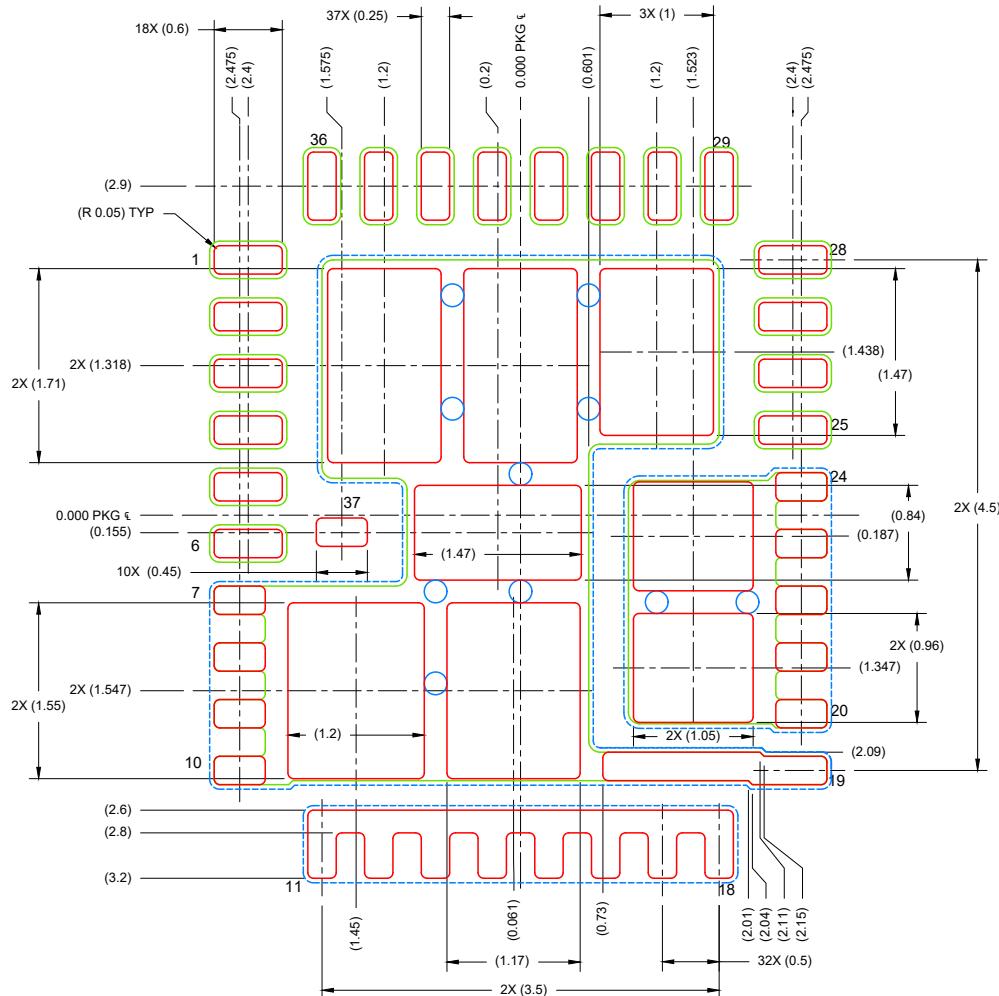

Figure 5-1. RXX 37-pin WQFN-FCRLF Package (Top View)

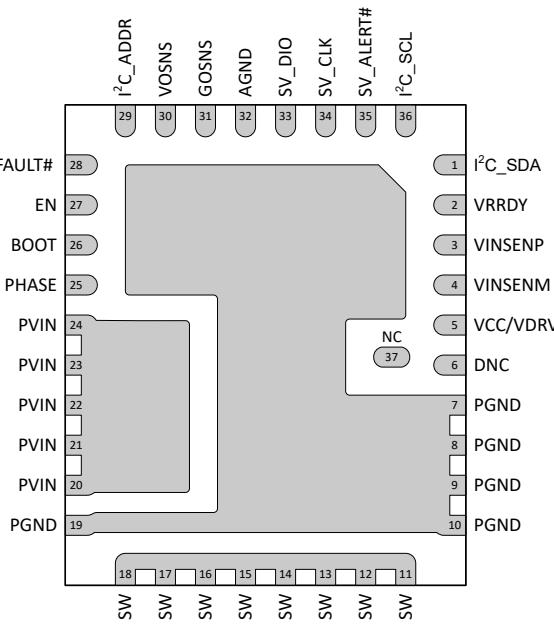

Figure 5-2. RXX 37-pin WQFN-FCRLF Package (Bottom View)

Table 5-1. Pin Functions

| PIN        |          | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                       |

|------------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.      |                    |                                                                                                                                                                                                                                                                                                   |

| AGND       | 32       | G                  | Ground pin, reference point for internal control circuitry.                                                                                                                                                                                                                                       |

| BOOT       | 26       | P                  | Supply rail for the high-side gate driver (boost terminal). Connect the bootstrap capacitor from this pin to PHASE pin. A high temperature (X7R) 0.1 $\mu$ F or greater value ceramic capacitor is recommended.                                                                                   |

| CAT_FAULT# | 28       | O                  | Catastrophic Fault indicator, open-drain. The CAT_FAULT# indicator asserts low when any catastrophic fault event (over-voltage, under-voltage and over-temperature) happens. During nominal operation, the CAT_FAULT# indicator holds high.                                                       |

| DNC        | 6        | —                  | Do Not Connect (DNC) pin. This pin is the output of internal circuitry and must be floating. Pin 6 and pin 37 can be shorted together but NO any other PCB connection is allowed on pin 6.                                                                                                        |

| EN         | 27       | I                  | Enable pin, an active-high input pin that, when asserted high, causes the converter to begin its soft-start sequence for its output voltage rail. When de-asserted low, the converter must de-assert VRRDY and begin the shutdown sequence of the output voltage rail and continue to completion. |

| GOSNS      | 31       | I                  | Negative input of the differential remote sense circuit, connect to the ground sense point on the load side.                                                                                                                                                                                      |

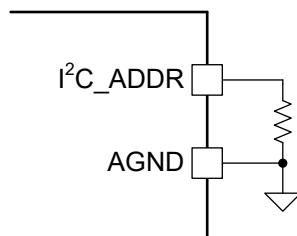

| I2C_ADDR   | 29       | I                  | The I2C address of the device is set by tying an external resistor between this pin and AGND.                                                                                                                                                                                                     |

| I2C_SCL    | 36       | I                  | I2C serial clock pin, open drain.                                                                                                                                                                                                                                                                 |

| I2C_SDA    | 1        | I/O                | I2C bi-directional serial data pin, open drain.                                                                                                                                                                                                                                                   |

| NC         | 37       | —                  | Not connected. This pin is floating internally. Pin 37 and pin 6 can be shorted together.                                                                                                                                                                                                         |

| PGND       | 7-10, 19 | G                  | Power ground for the internal power stage.                                                                                                                                                                                                                                                        |

| PHASE      | 25       | —                  | Return for high-side MOSFET driver. Shorted to SW internally. Connect the bootstrap capacitor from BOOT pin to this pin.                                                                                                                                                                          |

| PVIN       | 20-24    | P                  | Power input for both the power stage. PVIN is the input of the internal VCC LDO as well.                                                                                                                                                                                                          |

| SV_ALERT#  | 35       | O                  | SVID active low ALERT# signal, open drain. This output is asserted to indicate the status of the converter has changed.                                                                                                                                                                           |

**Table 5-1. Pin Functions (continued)**

| PIN      |       | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.   |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SV_CLK   | 34    | I                  | SVID clock pin, open drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SV_DIO   | 33    | I/O                | SVID bi-directional data pin, open drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SW       | 11–18 | O                  | Output switching terminal of the power converter. Connect these pins to the output inductor.                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC/VDRV | 5     | P                  | Internal VCC LDO output and also the input for gate driver circuit. An external 5-V bias can be connected to this pin to save the power losses on the internal LDO. The voltage source on this pin powers both the internal control circuitry and the gate driver. A 2.2 $\mu$ F (or 4.7 $\mu$ F), at least 6.3 V rating ceramic capacitor is required to be placed from VCC/VDRV pin to PGND pins to decouple the noise generated by driver circuitry. Check layout guidelines for more details. |

| VINSENM  | 4     | I                  | Negative input for the input power telemetry. Connect to the negative side of the input power sense resistor. Input voltage is also sensed at this pin. To minimize the impact from switching noise, a ceramic decoupling capacitor with at least 100 pF capacitance is required from this pin to PGND. Check layout guidelines for more details.                                                                                                                                                 |

| VINSENP  | 3     | I                  | Positive input for the input power telemetry. Connect to the positive side of the input power sense resistor. To minimize the impact from switching noise, a ceramic decoupling capacitor with at least 100-pF capacitance is required from this pin to PGND. Check layout guidelines for more details.                                                                                                                                                                                           |

| VOSNS    | 30    | I                  | Positive input of the differential remote sense circuit, connect to the Vout sense point on the load side.                                                                                                                                                                                                                                                                                                                                                                                        |

| VRRDY    | 2     | O                  | Voltage regulator "Ready" output signal. The VRRDY indicator is asserted when the controller is ready to accept SVID commands after the EN is asserted. VRRDY also de-asserts low when a shutdown fault occurs. This open-drain output requires an external pullup resistor.                                                                                                                                                                                                                      |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating junction temperature range (unless otherwise noted) <sup>(1)</sup>

|                  |                                                                       | MIN  | MAX  | UNIT |

|------------------|-----------------------------------------------------------------------|------|------|------|

| Pin voltage      | PVIN                                                                  | -0.3 | 18   | V    |

| Pin voltage      | PVIN – SW, DC                                                         | -0.3 | 18   | V    |

| Pin voltage      | PVIN – SW, transient < 10 ns                                          | -1.5 | 26   | V    |

| Pin voltage      | SW – PGND, DC                                                         | -0.3 | 18   | V    |

| Pin voltage      | SW – PGND, transient < 10 ns                                          | -3.0 | 21.5 | V    |

| Pin voltage      | BOOT – PGND                                                           | -0.3 | 23.5 | V    |

| Pin voltage      | BOOT – SW                                                             | -0.3 | 5.5  | V    |

| Pin voltage      | VCC/VDRV                                                              | -0.3 | 5.5  | V    |

| Pin voltage      | PHASE                                                                 | -0.3 | 18   | V    |

| Pin voltage      | VINSENP, VINSENM                                                      | -0.3 | 20   | V    |

| Pin voltage      | EN, VOSNS, I <sup>2</sup> C_ADDR, VRRDY, CAT_FAULT#                   | -0.3 | 5.5  | V    |

| Pin voltage      | SV_CLK, SV_DIO, SV_ALERT#, I <sup>2</sup> C_SCL, I <sup>2</sup> C_SDA | -0.3 | 5.5  | V    |

| Pin voltage      | GOSNS – AGND                                                          | -0.3 | 0.3  | V    |

| Pin voltage      | DNC, NC                                                               | -0.3 | 1.9  | V    |

| Sink current     | VRRDY                                                                 | 0    | 10   | mA   |

| T <sub>J</sub>   | Operating junction temperature                                        | -40  | 150  | °C   |

| T <sub>stg</sub> | Storage temperature                                                   | -55  | 150  | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |                         | VALUE                                                                 | UNIT  |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 |

|                    |                         | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating junction temperature range (unless otherwise noted)

|                    |                                   | MIN                                                   | NOM  | MAX | UNIT |

|--------------------|-----------------------------------|-------------------------------------------------------|------|-----|------|

| V <sub>OUT</sub>   | Programmable output voltage range | 0.25                                                  | 3.04 |     | V    |

| V <sub>IN</sub>    | Input voltage                     | PVIN when VCC/VDRV is powered by the internal LDO     | 4.0  | 16  | V    |

|                    |                                   | PVIN when VCC/VDRV is powered by an external 5 V bias | 2.7  | 16  | V    |

| V <sub>BIAS</sub>  | Input voltage                     | VCC/VDRV external bias                                | 4.75 | 5.3 | V    |

| I <sub>OUT</sub>   | Output current range              |                                                       |      | 35  | A    |

|                    | Pin voltage                       | VINSENP, VINSENM                                      | 8    | 16  | V    |

|                    | Pin voltage                       | EN, VRRDY, CAT_FAULT#                                 | -0.1 | 5.3 | V    |

|                    | Pin voltage                       | SV_CLK, SV_DIO, SV_ALERT#                             | -0.1 | 1.5 | V    |

|                    | Pin voltage                       | I <sup>2</sup> C_SCL, I <sup>2</sup> C_SDA            | -0.1 | 5.3 | V    |

| I <sub>VRRDY</sub> | VRRDY input current capability    |                                                       |      | 10  | mA   |

| T <sub>J</sub>     | Operating junction temperature    | -40                                                   | 125  |     | °C   |

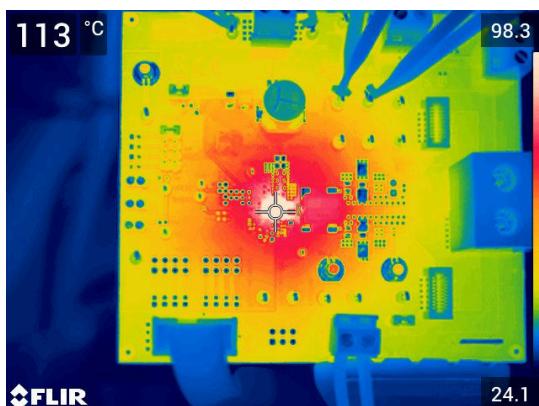

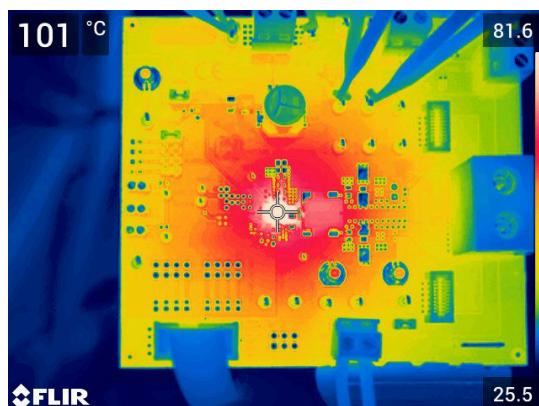

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | DEVICE           |                               | UNIT |

|-------------------------------|----------------------------------------------|------------------|-------------------------------|------|

|                               |                                              | RXX (QFN, JEDEC) | RXX (QFN, TI EVM)             |      |

|                               |                                              | 37 PINS          | 37 PINS                       |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 26.0             | 16.0                          | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 7.4              | Not applicable <sup>(2)</sup> | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 3.6              | Not applicable <sup>(2)</sup> | °C/W |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 0.2              | 0.2                           | °C/W |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 3.6              | 5.7                           | °C/W |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 3.3              | Not applicable <sup>(2)</sup> | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

(2) The thermal test or simulation setup is not applicable to a TI EVM layout.

## 6.5 Electrical Characteristics

T<sub>J</sub> = –40°C to +125°C. PVIN = 4 V to 16 V, V<sub>VCC</sub> = 4.5 V to 5.0 V (unless otherwise noted). Typical values are at T<sub>J</sub> = 25°C, PVIN = 12 V and V<sub>VCC</sub> = 4.5 V.

| PARAMETER            | TEST CONDITIONS                      | MIN                                                                                                                                                                 | TYP  | MAX  | UNIT   |

|----------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|

| <b>SUPPLY</b>        |                                      |                                                                                                                                                                     |      |      |        |

|                      | PVIN operating input range           | 4                                                                                                                                                                   | 16   |      | V      |

| I <sub>Q(PVIN)</sub> | PVIN quiescent current               | Non-switching, PVIN = 12 V, V <sub>EN</sub> = 0 V, no bias on VCC/VDRV pin                                                                                          | 6    | 7.9  | 9 mA   |

| I <sub>VCC</sub>     | VCC/VDRV external bias current       | External 5 V bias on VCC/VDRV pin, regular switching. T <sub>J</sub> = 25°C, PVIN = 12 V, I <sub>OUT</sub> = 35 A, V <sub>EN</sub> = 2 V, f <sub>SW</sub> = 0.6 MHz |      | 32.7 | mA     |

| I <sub>VCC</sub>     | VCC/VDRV external bias current       | External 5 V bias on VCC/VDRV pin, regular switching. T <sub>J</sub> = 25°C, PVIN = 12 V, I <sub>OUT</sub> = 35 A, V <sub>EN</sub> = 2 V, f <sub>SW</sub> = 0.8 MHz |      | 39.7 | mA     |

| I <sub>VCC</sub>     | VCC/VDRV external bias current       | External 5 V bias on VCC/VDRV pin, regular switching. T <sub>J</sub> = 25°C, PVIN = 12 V, I <sub>OUT</sub> = 35 A, V <sub>EN</sub> = 2 V, f <sub>SW</sub> = 1.0 MHz |      | 48.7 | mA     |

| I <sub>VCC</sub>     | VCC/VDRV external bias current       | External 5 V bias on VCC/VDRV pin, regular switching. T <sub>J</sub> = 25°C, PVIN = 12 V, I <sub>OUT</sub> = 35 A, V <sub>EN</sub> = 2 V, f <sub>SW</sub> = 1.2 MHz |      | 57.3 | mA     |

| I <sub>Q(VCC)</sub>  | VCC/VDRV quiescent current           | External 5 V bias on VCC/VDRV pin, non-switching. PVIN = 12V, V <sub>EN</sub> = 2 V, V <sub>VOSNS</sub> = V <sub>O_Setting</sub> + 50 mV                            | 6    | 7.9  | 9 mA   |

| <b>UVLO</b>          |                                      |                                                                                                                                                                     |      |      |        |

| PVIN <sub>OV</sub>   | PVIN overvoltage rising threshold    | PVIN rising, register (55h) VIN_OV_FAULT_LIMIT = 00h                                                                                                                | 16.3 | 16.9 | 17.5 V |

| PVIN <sub>OV</sub>   | PVIN overvoltage rising threshold    | PVIN rising, register (55h) VIN_OV_FAULT_LIMIT = 01h                                                                                                                | 18.0 | 18.6 | 19.2 V |

| PVIN <sub>OV</sub>   | PVIN overvoltage falling threshold   | PVIN falling. PVIN_OVF status bit, once it is set, cannot be cleared unless PVIN falls below the PVIN overvoltage falling threshold                                 | 12.9 | 13.4 | 13.9 V |

| VIN_ON               | PVIN turn-on voltage                 | PVIN rising, register (35h) VIN_ON = 00h                                                                                                                            | 9.7  | 10   | 10.2 V |

| VIN_ON               | PVIN turn-on voltage <sup>(1)</sup>  | PVIN rising, register (35h) VIN_ON = 01h                                                                                                                            |      | 9    | V      |

| VIN_ON               | PVIN turn-on voltage                 | PVIN rising, register (35h) VIN_ON = 02h                                                                                                                            | 7.8  | 8    | 8.2 V  |

| VIN_ON               | PVIN turn-on voltage                 | PVIN rising, register (35h) VIN_ON = 03h, V <sub>VCC</sub> = Internal LDO                                                                                           | 3.6  | 3.8  | 4.0 V  |

| VIN_OFF              | PVIN turn-off voltage                | PVIN falling, register (36h) VIN_OFF = 00h                                                                                                                          | 4.0  | 4.2  | 4.4 V  |

| VIN_OFF              | PVIN turn-off voltage                | PVIN falling, register (36h) VIN_OFF = 01h                                                                                                                          | 9.1  | 9.5  | 9.8 V  |

| VIN_OFF              | PVIN turn-off voltage <sup>(1)</sup> | PVIN falling, register (36h) VIN_OFF = 02h                                                                                                                          |      | 8.5  | V      |

| VIN_OFF              | PVIN turn-off voltage <sup>(1)</sup> | PVIN falling, register (36h) VIN_OFF = 03h                                                                                                                          |      | 7.5  | V      |

| VIN_OFF              | PVIN turn-off voltage <sup>(1)</sup> | PVIN falling, register (36h) VIN_OFF = 04h                                                                                                                          |      | 6.5  | V      |

| VIN_OFF              | PVIN turn-off voltage <sup>(1)</sup> | PVIN falling, register (36h) VIN_OFF = 05h                                                                                                                          |      | 5.5  | V      |

| VIN_OFF              | PVIN turn-off voltage                | PVIN falling, register (36h) VIN_OFF = 06h                                                                                                                          | 4.0  | 4.2  | 4.4 V  |

## 6.5 Electrical Characteristics (continued)

$T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ .  $\text{PVIN} = 4\text{ V}$  to  $16\text{ V}$ ,  $\text{V}_{\text{VCC}} = 4.5\text{ V}$  to  $5.0\text{ V}$  (unless otherwise noted). Typical values are at  $T_J = 25^\circ\text{C}$ ,  $\text{PVIN} = 12\text{ V}$  and  $\text{V}_{\text{VCC}} = 4.5\text{ V}$ .

| PARAMETER                    |                                                                           | TEST CONDITIONS                                                                                                             | MIN   | TYP  | MAX  | UNIT  |

|------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| VIN_OFF                      | PVIN turn-off voltage                                                     | PVIN falling, register (36h) VIN_OFF = 07h, $\text{V}_{\text{VCC}} = \text{Internal LDO}$                                   | 3.2   | 3.4  | 3.6  | V     |

| PVIN <sub>UVLO(R)</sub>      | PVIN UVLO rising threshold                                                | PVIN rising, external 5 V bias on VCC/VDRV pin                                                                              | 2.35  | 2.55 | 2.75 | V     |

| PVIN <sub>UVLO(F)</sub>      | PVIN UVLO falling threshold                                               | PVIN falling, external 5 V bias on VCC/VDRV pin                                                                             | 2.10  | 2.30 | 2.50 | V     |

| PVIN <sub>UVLO(H)</sub>      | PVIN UVLO hysteresis                                                      |                                                                                                                             |       | 0.25 |      | V     |

| <b>ENABLE</b>                |                                                                           |                                                                                                                             |       |      |      |       |

| V <sub>EN(R)</sub>           | EN voltage rising threshold                                               | EN rising, enable switching                                                                                                 | 1.14  | 1.19 | 1.24 | V     |

| V <sub>EN(F)</sub>           | EN voltage falling threshold                                              | EN falling, disable switching                                                                                               | 0.94  | 0.98 | 1.02 | V     |

| V <sub>EN(H)</sub>           | EN voltage hysteresis                                                     |                                                                                                                             |       | 0.21 |      | V     |

| t <sub>EN(DIG)</sub>         | EN Deglitch Time                                                          |                                                                                                                             | 0.2   |      |      | μs    |

|                              | EN internal pulldown resistor                                             | $\text{V}_{\text{EN}} = 2\text{ V}$ , EN pin to AGND                                                                        | 110   | 125  | 140  | kΩ    |

| <b>INTERNAL VCC LDO</b>      |                                                                           |                                                                                                                             |       |      |      |       |

| t <sub>delay(uvlo_I2C)</sub> | Delay from VCC_OK to I <sup>2</sup> C ready to communicate <sup>(1)</sup> | VCC/VDRV $\geq 3\text{ V}$                                                                                                  |       | 300  |      | μs    |

|                              | Internal VCC LDO output voltage                                           | PVIN = 4 V, I <sub>VCC(load)</sub> = 5 mA                                                                                   | 3.925 | 3.97 | 4.0  | V     |

|                              | Internal VCC LDO output voltage                                           | PVIN = 5 V to 16 V, I <sub>VCC(load)</sub> = 5 mA                                                                           | 4.28  | 4.44 | 4.55 | V     |

|                              | VCC_OK rising threshold                                                   | $T_J = -40^\circ\text{C}$ to $85^\circ\text{C}$ . VCC rising, enabling initial power-on including digital communication     | 3.0   | 3.15 | 3.3  | V     |

|                              | VCC_OK falling threshold                                                  | $T_J = -40^\circ\text{C}$ to $85^\circ\text{C}$ . VCC falling, disabling controller circuit including digital communication | 2.95  | 3.10 | 3.25 | V     |

|                              | VCC LDO dropout voltage                                                   | PVIN – $\text{V}_{\text{VCC}}$ , PVIN = 4 V, I <sub>VCC(load)</sub> = 50 mA                                                 |       | 184  | 300  | mV    |

|                              | VCC LDO short-circuit current limit                                       |                                                                                                                             | 150   |      |      | mA    |

| <b>VOUT VOLTAGE</b>          |                                                                           |                                                                                                                             |       |      |      |       |

|                              | Output Voltage controlled through SVID interface                          | Output voltage range by SetVID & SetWP commands                                                                             | 0.5   |      | 3.04 | V     |

|                              | Output Voltage controlled through SVID interface                          | Output voltage resolution by SetVID & SetWP commands                                                                        |       | 5    |      | mV    |

|                              | Output Voltage controlled through SVID interface                          | SVID fast slew rate, register (AFh) DVS_CFG = 02h                                                                           | 2.5   | 2.78 | 3.06 | mV/μs |

|                              | Output Voltage controlled through SVID interface                          | SVID fast slew rate, register (AFh) DVS_CFG = 04h                                                                           | 5     | 5.5  | 6.1  | mV/μs |

|                              | Output Voltage controlled through SVID interface                          | SVID fast slew rate, register (AFh) DVS_CFG = 06h                                                                           | 10    | 11.1 | 12.2 | mV/μs |

|                              | Output Voltage controlled through SVID interface                          | SVID OFFSET range                                                                                                           | -128  |      | 127  | Step  |

|                              | Output Voltage controlled through SVID interface                          | SVID OFFSET resolution                                                                                                      |       | 1    |      | Step  |

|                              | Output Voltage controlled through I <sup>2</sup> C interface              | Output voltage range by register (A6h) VOUT_CMD                                                                             | 0.5   |      | 3.04 | V     |

|                              | Output Voltage controlled through I <sup>2</sup> C interface              | Output voltage resolution by register (A6h) VOUT_CMD                                                                        |       | 5    |      | mV    |

|                              | Output Voltage controlled through I <sup>2</sup> C interface              | Output voltage transition slew rate by register (A6h) VOUT_CMD, register (AFh) DVS_CFG = 02h                                | 0.625 |      |      | mV/μs |

|                              | Output Voltage controlled through I <sup>2</sup> C interface              | Output voltage transition slew rate by register (A6h) VOUT_CMD, register (AFh) DVS_CFG = 04h                                | 1.25  |      |      | mV/μs |

|                              | Output Voltage controlled through I <sup>2</sup> C interface              | Output voltage transition slew rate by register (A6h) VOUT_CMD, register (AFh) DVS_CFG = 06h                                | 2.5   |      |      | mV/μs |

|                              | Output Voltage controlled through I <sup>2</sup> C interface              | I <sup>2</sup> C offset (register A8h) range, $\text{V}_{\text{OUT}}$ step = 5 mV                                           | -64   |      | 63   | mV    |

## 6.5 Electrical Characteristics (continued)

$T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ .  $\text{PVIN} = 4\text{ V}$  to  $16\text{ V}$ ,  $\text{V}_{\text{VCC}} = 4.5\text{ V}$  to  $5.0\text{ V}$  (unless otherwise noted). Typical values are at  $T_J = 25^\circ\text{C}$ ,  $\text{PVIN} = 12\text{ V}$  and  $\text{V}_{\text{VCC}} = 4.5\text{ V}$ .

| PARAMETER                                                    | TEST CONDITIONS                                                                                 | MIN                                                                                                                                                       | TYP    | MAX  | UNIT        |               |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------------|---------------|

| Output Voltage controlled through I <sup>2</sup> C interface | I <sup>2</sup> C offset (register A8h) resolution, $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ |                                                                                                                                                           | 0.5    |      | $\text{mV}$ |               |

| Output Voltage controlled through I <sup>2</sup> C interface | I <sup>2</sup> C offset (register A8h) range, $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$     | -128                                                                                                                                                      |        | 127  | $\text{mV}$ |               |

| Output Voltage controlled through I <sup>2</sup> C interface | I <sup>2</sup> C offset (register A8h) resolution, $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ |                                                                                                                                                           | 1.0    |      | $\text{mV}$ |               |

| $\text{V}_{\text{OUT(ACC)}}$                                 | Output voltage accuracy                                                                         | $T_J = 0^\circ\text{C}$ to $85^\circ\text{C}$ , $\text{V}_{\text{OUT\_Setting}} = 0.75\text{ V}$ , $\text{V}_{\text{VOSNS}} - \text{V}_{\text{GOSNS}}$    | 0.7425 | 0.75 | 0.7575      | $\text{V}$    |

| $\text{V}_{\text{OUT(ACC)}}$                                 | Output voltage accuracy                                                                         | $T_J = 0^\circ\text{C}$ to $85^\circ\text{C}$ , $\text{V}_{\text{OUT\_Setting}} = 1.1\text{ V}$ , $\text{V}_{\text{VOSNS}} - \text{V}_{\text{GOSNS}}$     | 1.0945 | 1.1  | 1.1055      | $\text{V}$    |

| $\text{V}_{\text{OUT(ACC)}}$                                 | Output voltage accuracy                                                                         | $T_J = 0^\circ\text{C}$ to $85^\circ\text{C}$ , $\text{V}_{\text{OUT\_Setting}} = 1.8\text{ V}$ , $\text{V}_{\text{VOSNS}} - \text{V}_{\text{GOSNS}}$     | 1.791  | 1.8  | 1.809       | $\text{V}$    |

| $\text{V}_{\text{OUT(ACC)}}$                                 | Output voltage accuracy                                                                         | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{V}_{\text{OUT\_Setting}} = 0.75\text{ V}$ , $\text{V}_{\text{VOSNS}} - \text{V}_{\text{GOSNS}}$ | 0.739  | 0.75 | 0.761       | $\text{V}$    |

| $\text{V}_{\text{OUT(ACC)}}$                                 | Output voltage accuracy                                                                         | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{V}_{\text{OUT\_Setting}} = 1.1\text{ V}$ , $\text{V}_{\text{VOSNS}} - \text{V}_{\text{GOSNS}}$  | 1.089  | 1.1  | 1.111       | $\text{V}$    |

| $\text{V}_{\text{OUT(ACC)}}$                                 | Output voltage accuracy                                                                         | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{V}_{\text{OUT\_Setting}} = 1.8\text{ V}$ , $\text{V}_{\text{VOSNS}} - \text{V}_{\text{GOSNS}}$  | 1.782  | 1.8  | 1.818       | $\text{V}$    |

| $\text{I}_{\text{VOS}}$                                      | VOSNS input current                                                                             | $\text{V}_{\text{VOSNS}} = 1.8\text{ V}$                                                                                                                  |        | 120  | 130         | $\mu\text{A}$ |

### SWITCHING FREQUENCY

|                       |                                     |                                                                                                                                                                          |      |      |      |              |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------|

| $f_{\text{SW(FCCM)}}$ | Switching frequency, FCCM operation | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{OUT}} = 1.1\text{ V}$ , no load, register (33h) FREQUENCY_SWITCH = 00h | 510  | 600  | 660  | $\text{kHz}$ |

| $f_{\text{SW(FCCM)}}$ | Switching frequency, FCCM operation | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{OUT}} = 1.1\text{ V}$ , no load, register (33h) FREQUENCY_SWITCH = 01h | 680  | 800  | 920  | $\text{kHz}$ |

| $f_{\text{SW(FCCM)}}$ | Switching frequency, FCCM operation | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{OUT}} = 1.1\text{ V}$ , no load, register (33h) FREQUENCY_SWITCH = 02h | 850  | 1000 | 1150 | $\text{kHz}$ |

| $f_{\text{SW(FCCM)}}$ | Switching frequency, FCCM operation | $T_J = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{OUT}} = 1.1\text{ V}$ , no load, register (33h) FREQUENCY_SWITCH = 03h | 1020 | 1200 | 1440 | $\text{kHz}$ |

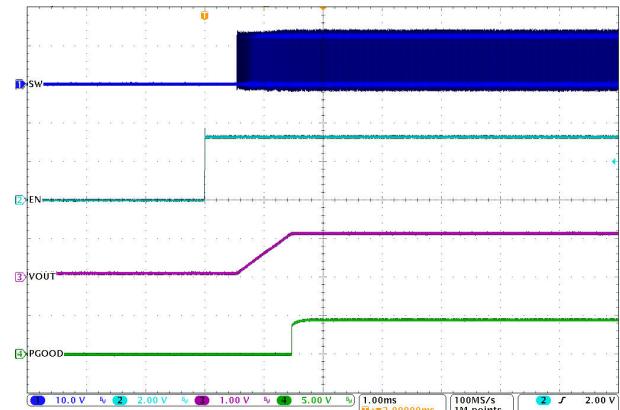

### STARTUP

|                       |                          |                                                                          |  |     |      |             |

|-----------------------|--------------------------|--------------------------------------------------------------------------|--|-----|------|-------------|

| $t_{\text{ON(DLY)}}$  | Power on sequence delay  | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (60h) TON_DELAY = 00h  |  | 0.5 | 0.55 | $\text{ms}$ |

| $t_{\text{ON(DLY)}}$  | Power on sequence delay  | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (60h) TON_DELAY = 01h  |  | 1.0 | 1.1  | $\text{ms}$ |

| $t_{\text{ON(DLY)}}$  | Power on sequence delay  | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (60h) TON_DELAY = 02h  |  | 1.5 | 1.65 | $\text{ms}$ |

| $t_{\text{ON(DLY)}}$  | Power on sequence delay  | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (60h) TON_DELAY = 03h  |  | 2.0 | 2.2  | $\text{ms}$ |

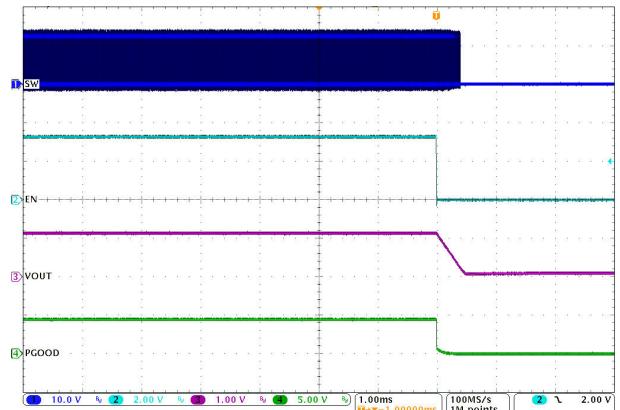

| $t_{\text{OFF(DLY)}}$ | Power off sequence delay | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (64h) TOFF_DELAY = 00h |  | 0   | 0.02 | $\text{ms}$ |

| $t_{\text{OFF(DLY)}}$ | Power off sequence delay | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (64h) TOFF_DELAY = 01h |  | 1.0 | 1.1  | $\text{ms}$ |

| $t_{\text{OFF(DLY)}}$ | Power off sequence delay | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (64h) TOFF_DELAY = 02h |  | 1.5 | 1.65 | $\text{ms}$ |

| $t_{\text{OFF(DLY)}}$ | Power off sequence delay | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (64h) TOFF_DELAY = 03h |  | 2.0 | 2.2  | $\text{ms}$ |

| $t_{\text{ON(Rise)}}$ | Soft-start time          | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (61h) TON_RISE = 00h   |  | 1.0 | 1.1  | $\text{ms}$ |

| $t_{\text{ON(Rise)}}$ | Soft-start time          | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (61h) TON_RISE = 01h   |  | 2.0 | 2.2  | $\text{ms}$ |

| $t_{\text{ON(Rise)}}$ | Soft-start time          | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (61h) TON_RISE = 02h   |  | 4.0 | 4.4  | $\text{ms}$ |

| $t_{\text{ON(Rise)}}$ | Soft-start time          | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (61h) TON_RISE = 03h   |  | 8.0 | 8.8  | $\text{ms}$ |

## 6.5 Electrical Characteristics (continued)

$T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ .  $\text{PVIN} = 4\text{ V}$  to  $16\text{ V}$ ,  $\text{V}_{\text{VCC}} = 4.5\text{ V}$  to  $5.0\text{ V}$  (unless otherwise noted). Typical values are at  $T_J = 25^\circ\text{C}$ ,  $\text{PVIN} = 12\text{ V}$  and  $\text{V}_{\text{VCC}} = 4.5\text{ V}$ .

| PARAMETER                     |                                                                             | TEST CONDITIONS                                                                                                                                                                                                                          | MIN | TYP   | MAX  | UNIT             |

|-------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------------------|

| $t_{\text{ON}}(\text{Rise})$  | Soft-start time                                                             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (61h) $\text{TON\_RISE} = 04\text{h}$ to $07\text{h}$                                                                                                                                  |     | 16.0  | 17.6 | ms               |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 00\text{h}$ , $\text{V}_{\text{boot}} = 1.1\text{V}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )  |     | 2.2   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 01\text{h}$ , $\text{V}_{\text{boot}} = 1.1\text{V}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )  |     | 1.1   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 02\text{h}$ , $\text{V}_{\text{boot}} = 1.1\text{V}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )  |     | 0.55  |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 03\text{h}$ , $\text{V}_{\text{boot}} = 1.1\text{V}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )  |     | 0.275 |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 00\text{h}$ , $\text{V}_{\text{boot}} = 1.8\text{V}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ ) |     | 3.6   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 01\text{h}$ , $\text{V}_{\text{boot}} = 1.8\text{V}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ ) |     | 1.8   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 02\text{h}$ , $\text{V}_{\text{boot}} = 1.8\text{V}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ ) |     | 0.9   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by SVID             | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 03\text{h}$ , $\text{V}_{\text{boot}} = 1.8\text{V}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ ) |     | 0.45  |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 00\text{h}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )                                           |     | 2.2   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 01\text{h}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )                                           |     | 1.1   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 02\text{h}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )                                           |     | 0.55  |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 03\text{h}$ , $\text{PROTOCOL\_ID} = 01\text{b}$ or $10\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $5\text{ mV}$ )                                           |     | 0.275 |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 00\text{h}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ )                                          |     | 3.6   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 01\text{h}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ )                                          |     | 1.8   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 02\text{h}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ )                                          |     | 0.9   |      | V/ms             |

| $t_{\text{OFF}}(\text{Fall})$ | Soft-stop slew rate, $\text{V}_{\text{OUT}}$ controlled by I <sup>2</sup> C | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , register (65h) $\text{TOFF\_FALL} = 03\text{h}$ , $\text{PROTOCOL\_ID} = 00\text{b}$ or $11\text{b}$ ( $\text{V}_{\text{OUT}}$ step = $10\text{ mV}$ )                                          |     | 0.45  |      | V/ms             |

| <b>POWER STAGE</b>            |                                                                             |                                                                                                                                                                                                                                          |     |       |      |                  |

| $R_{\text{DSON(HS)}}$         | High-side MOSFET on-resistance                                              | $T_J = 25^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{BOOT-SW}} = 4.5\text{ V}$                                                                                                                                      |     | 4     |      | $\text{m}\Omega$ |

| $R_{\text{DSON(HS)}}$         | High-side MOSFET on-resistance                                              | $T_J = 25^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{BOOT-SW}} = 5.0\text{ V}$                                                                                                                                      |     | 3.91  |      | $\text{m}\Omega$ |

| $R_{\text{DSON(LS)}}$         | Low-side MOSFET on-resistance                                               | $T_J = 25^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{VCC}} = 4.5\text{ V}$                                                                                                                                          |     | 1     |      | $\text{m}\Omega$ |

| $R_{\text{DSON(LS)}}$         | Low-side MOSFET on-resistance                                               | $T_J = 25^\circ\text{C}$ , $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{VCC}} = 5\text{ V}$                                                                                                                                            |     | 0.98  |      | $\text{m}\Omega$ |

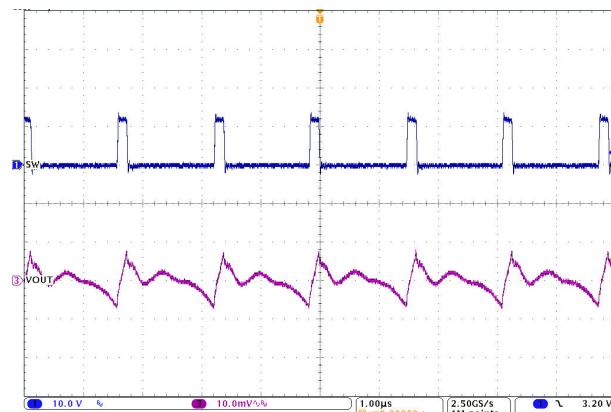

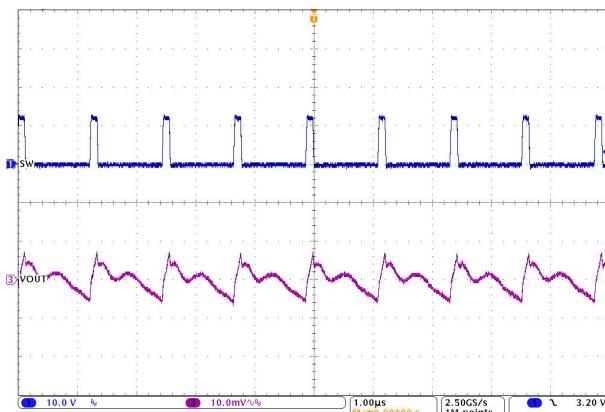

| $t_{\text{ON}}(\text{min})$   | Minimum ON pulse width                                                      | $\text{V}_{\text{VCC}} = 4.5\text{ V}$                                                                                                                                                                                                   |     | 60    |      | ns               |

| $t_{\text{OFF}}(\text{min})$  | Minimum OFF pulse width                                                     | $\text{V}_{\text{VCC}} = 4.5\text{ V}$ , $I_{\text{O}}=1.5\text{A}$ , $\text{V}_{\text{VOSNS}} = \text{V}_{\text{OUT\_Setting}} - 20\text{ mV}$ , SW falling edge to rising edge                                                         |     | 210   | 250  | ns               |

| <b>BOOT CIRCUIT</b>           |                                                                             |                                                                                                                                                                                                                                          |     |       |      |                  |

## 6.5 Electrical Characteristics (continued)

$T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ .  $\text{PVIN} = 4\text{ V}$  to  $16\text{ V}$ ,  $\text{V}_{\text{VCC}} = 4.5\text{ V}$  to  $5.0\text{ V}$  (unless otherwise noted). Typical values are at  $T_J = 25^\circ\text{C}$ ,  $\text{PVIN} = 12\text{ V}$  and  $\text{V}_{\text{VCC}} = 4.5\text{ V}$ .

| PARAMETER                  | TEST CONDITIONS                                                                                                 | MIN                                                                                                                         | TYP   | MAX   | UNIT          |               |

|----------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------|---------------|

| $I_{\text{BOOT(LKG)}}$     | $\text{BOOT}$ leakage current<br>$\text{V}_{\text{EN}} = 2\text{ V}$ , $\text{V}_{\text{BOOT-SW}} = 5\text{ V}$ |                                                                                                                             |       | 150   | $\mu\text{A}$ |               |

| $V_{\text{BOOT-SW(UV_F)}}$ | $\text{BOOT-SW UVLO}$ falling threshold                                                                         | 2.60                                                                                                                        | 2.76  |       | V             |               |

| <b>OVERCURRENT LIMIT</b>   |                                                                                                                 |                                                                                                                             |       |       |               |               |

| $I_{\text{LS(OC)}}$        | Low-side valley overcurrent limit<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 00\text{h}$                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 00\text{h}$                              | 8.5   | 10    | 11.5          | A             |

| $I_{\text{LS(OC)}}$        | Low-side valley overcurrent limit <sup>(1)</sup>                                                                | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 01\text{h}$                              | 10.2  | 12    | 13.8          | A             |

| $I_{\text{LS(OC)}}$        | Low-side valley overcurrent limit                                                                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 02\text{h}$                              | 13.5  | 15    | 16.5          | A             |

| $I_{\text{LS(OC)}}$        | Low-side valley overcurrent limit <sup>(1)</sup>                                                                | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 03\text{h}$                              | 17.1  | 19    | 20.9          | A             |

| $I_{\text{LS(OC)}}$        | Low-side valley overcurrent limit                                                                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 04\text{h}$                              | 18    | 20    | 22            | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit                                                                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 05\text{h}$                              | 22.5  | 25    | 27.5          | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit <sup>(1)</sup>                                                                | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 06\text{h}$                              | 23.4  | 26    | 28.6          | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit                                                                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 07\text{h}$                              | 27    | 30    | 33            | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit <sup>(1)</sup>                                                                | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 08\text{h}$                              | 29.7  | 33    | 36.3          | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit                                                                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 09\text{h}$                              | 31.5  | 35    | 38.5          | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit <sup>(1)</sup>                                                                | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 0Ah$                                     | 35.1  | 39    | 42.9          | A             |

| $I_{\text{LS(OCL)}}$       | Low-side valley overcurrent limit                                                                               | Valley current limit on LS FET, register (46h)<br>$\text{IOUT\_OC\_FAULT\_LIMIT} = 0B\text{h}$ to $0F\text{h}$              | 36    | 40    | 44            | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit                                                                             | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 00\text{h}$ , $I_{\text{CCMAX}} \geq 15\text{A}$ | -24   | -21   | -18           | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit                                                                             | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 01\text{h}$ , $I_{\text{CCMAX}} \geq 15\text{A}$ | -18   | -16   | -14           | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit                                                                             | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 02\text{h}$ , $I_{\text{CCMAX}} \geq 15\text{A}$ | -14.5 | -12.8 | -11           | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit                                                                             | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 03\text{h}$ , $I_{\text{CCMAX}} \geq 15\text{A}$ | -12.5 | -10.8 | -9            | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit <sup>(1)</sup>                                                              | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 00\text{h}$ , $I_{\text{CCMAX}} \leq 10\text{A}$ | -14   | -11.3 | -9            | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit <sup>(1)</sup>                                                              | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 01\text{h}$ , $I_{\text{CCMAX}} \leq 10\text{A}$ | -12   | -8.7  | -6            | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit <sup>(1)</sup>                                                              | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 02\text{h}$ , $I_{\text{CCMAX}} \leq 10\text{A}$ | -10   | -7.2  | -4.5          | A             |

| $I_{\text{LS(NOC)}}$       | Low-side negative overcurrent limit <sup>(1)</sup>                                                              | Sinking current limit on LS FET, register (B4h) $\text{IOUT\_NOC\_LIMIT} = 03\text{h}$ , $I_{\text{CCMAX}} \leq 10\text{A}$ | -8.5  | -6.2  | -3.9          | A             |

| $I_{\text{ZC}}$            | Zero-cross detection current threshold                                                                          | ZC comparator threshold, enter DCM. $\text{PVIN} = 12\text{ V}$ , $\text{V}_{\text{VCC}} = 4.5\text{ V}$ ,                  |       | 900   |               | mA            |

|                            | Response delay before entering Hiccup                                                                           | UVF RESPONSE_DELAY = 00b                                                                                                    |       | 2     | 4             | $\mu\text{s}$ |

|                            | Response delay before entering Hiccup                                                                           | UVF RESPONSE_DELAY = 01b                                                                                                    |       | 16    | 20            | $\mu\text{s}$ |

|                            | Response delay before entering Hiccup                                                                           | UVF RESPONSE_DELAY = 10b                                                                                                    |       | 64    | 80            | $\mu\text{s}$ |

|                            | Response delay before entering Hiccup                                                                           | UVF RESPONSE_DELAY = 11b                                                                                                    |       | 256   | 320           | $\mu\text{s}$ |

|                            | Hiccup sleep time before a restart                                                                              |                                                                                                                             | 49    | 56    | 59            | ms            |

## 6.5 Electrical Characteristics (continued)

$T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$ .  $\text{PVIN} = 4\text{ V}$  to  $16\text{ V}$ ,  $\text{V}_{\text{VCC}} = 4.5\text{ V}$  to  $5.0\text{ V}$  (unless otherwise noted). Typical values are at  $T_J = 25^\circ\text{C}$ ,  $\text{PVIN} = 12\text{ V}$  and  $\text{V}_{\text{VCC}} = 4.5\text{ V}$ .

| PARAMETER                              | TEST CONDITIONS                                                                                                                                                                                          | MIN   | TYP  | MAX   | UNIT          |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|---------------|

| <b>OUTPUT OVP AND UVW</b>              |                                                                                                                                                                                                          |       |      |       |               |

| $V_{\text{OVF}}$                       | $V_{\text{OUT}}$ tracking overvoltage fault (OVF) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (40h)<br>$V_{\text{OUT\_OV\_FAULT\_LIMIT}} = 00\text{h}$    | 80    | 100  | 120   | mV            |

| $V_{\text{OVF}}$                       | $V_{\text{OUT}}$ tracking overvoltage fault (OVF) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (40h)<br>$V_{\text{OUT\_OV\_FAULT\_LIMIT}} = 01\text{h}$    | 120   | 150  | 180   | mV            |

| $V_{\text{OVF}}$                       | $V_{\text{OUT}}$ tracking overvoltage fault (OVF) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (40h)<br>$V_{\text{OUT\_OV\_FAULT\_LIMIT}} = 02\text{h}$    | 160   | 200  | 240   | mV            |

| $V_{\text{OVF}}$                       | $V_{\text{OUT}}$ tracking overvoltage fault (OVF) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (40h)<br>$V_{\text{OUT\_OV\_FAULT\_LIMIT}} = 03\text{h}$    | 240   | 300  | 360   | mV            |

| $V_{\text{OVW}}$                       | $V_{\text{OUT}}$ tracking overvoltage warning (OVW) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (42h)<br>$V_{\text{OUT\_OV\_WARN\_LIMIT}} = 00\text{h}$   | 80    | 100  | 120   | mV            |

| $V_{\text{OVW}}$                       | $V_{\text{OUT}}$ tracking overvoltage warning (OVW) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (42h)<br>$V_{\text{OUT\_OV\_WARN\_LIMIT}} = 01\text{h}$   | 120   | 150  | 180   | mV            |

| $V_{\text{OVW}}$                       | $V_{\text{OUT}}$ tracking overvoltage warning (OVW) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (42h)<br>$V_{\text{OUT\_OV\_WARN\_LIMIT}} = 02\text{h}$   | 160   | 200  | 240   | mV            |

| $V_{\text{OVW}}$                       | $V_{\text{OUT}}$ tracking overvoltage warning (OVW) threshold, offset above $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) rising. Register (42h)<br>$V_{\text{OUT\_OV\_WARN\_LIMIT}} = 03\text{h}$   | 240   | 300  | 360   | mV            |

| $V_{\text{FixOVF}}$                    | $V_{\text{OUT}}$ fixed OVF threshold, $V_{\text{OUT}}$ step = 5 mV<br>(VOSNS – GOSNS) rising. SEL_FIX_OVF = 0b, PROTOCOL_ID = 01b or 10b ( $V_{\text{OUT}}$ step = 5 mV)                                 | 1.425 | 1.5  | 1.575 | V             |

| $V_{\text{FixOVF}}$                    | $V_{\text{OUT}}$ fixed OVF threshold, $V_{\text{OUT}}$ step = 5 mV<br>(VOSNS – GOSNS) rising. SEL_FIX_OVF = 1b, PROTOCOL_ID = 01b or 10b ( $V_{\text{OUT}}$ step = 5 mV)                                 | 1.71  | 1.8  | 1.89  | V             |

| $V_{\text{FixOVF}}$                    | $V_{\text{OUT}}$ fixed OVF threshold, $V_{\text{OUT}}$ step = 10 mV<br>(VOSNS – GOSNS) rising. SEL_FIX_OVF = 0b, PROTOCOL_ID = 00b or 11b ( $V_{\text{OUT}}$ step = 10 mV)                               | 2.3   | 2.4  | 2.47  | V             |

| $V_{\text{FixOVF}}$                    | $V_{\text{OUT}}$ fixed OVF threshold, $V_{\text{OUT}}$ step = 10 mV<br>(VOSNS – GOSNS) rising. SEL_FIX_OVF = 1b, PROTOCOL_ID = 00b or 11b ( $V_{\text{OUT}}$ step = 10 mV)                               | 2.85  | 3.0  | 3.07  | V             |

| $V_{\text{UVF}}$                       | $V_{\text{OUT}}$ tracking undervoltage fault (UVF) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (44h)<br>$V_{\text{OUT\_UV\_FAULT\_LIMIT}} = 00\text{h}$  | -180  | -150 | -120  | mV            |

| $V_{\text{UVF}}$                       | $V_{\text{OUT}}$ tracking undervoltage fault (UVF) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (44h)<br>$V_{\text{OUT\_UV\_FAULT\_LIMIT}} = 01\text{h}$  | -240  | -200 | -160  | mV            |

| $V_{\text{UVF}}$                       | $V_{\text{OUT}}$ tracking undervoltage fault (UVF) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (44h)<br>$V_{\text{OUT\_UV\_FAULT\_LIMIT}} = 02\text{h}$  | -240  | -200 | -160  | mV            |

| $V_{\text{UVF}}$                       | $V_{\text{OUT}}$ tracking undervoltage fault (UVF) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (44h)<br>$V_{\text{OUT\_UV\_FAULT\_LIMIT}} = 03\text{h}$  | -360  | -300 | -240  | mV            |

| $V_{\text{UVW}}$                       | $V_{\text{OUT}}$ tracking undervoltage warning (UVW) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (43h)<br>$V_{\text{OUT\_UV\_WARN\_LIMIT}} = 00\text{h}$ | -120  | -100 | -80   | mV            |

| $V_{\text{UVW}}$                       | $V_{\text{OUT}}$ tracking undervoltage warning (UVW) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (43h)<br>$V_{\text{OUT\_UV\_WARN\_LIMIT}} = 01\text{h}$ | -180  | -150 | -120  | mV            |

| $V_{\text{UVW}}$                       | $V_{\text{OUT}}$ tracking undervoltage warning (UVW) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (43h)<br>$V_{\text{OUT\_UV\_WARN\_LIMIT}} = 02\text{h}$ | -240  | -200 | -160  | mV            |

| $V_{\text{UVW}}$                       | $V_{\text{OUT}}$ tracking undervoltage warning (UVW) threshold, offset below $V_{\text{OUT}}$ setting value<br>(VOSNS – GOSNS) falling. Register (43h)<br>$V_{\text{OUT\_UV\_WARN\_LIMIT}} = 03\text{h}$ | -360  | -300 | -240  | mV            |

|                                        | $V_{\text{OUT}}$ tracking UVF response delay time<br>UVF RESPONSE_DELAY = 00b. From UVF detection to tri-state of the power FETs                                                                         | 2     | 4    |       | $\mu\text{s}$ |

|                                        | $V_{\text{OUT}}$ tracking UVF response delay time<br>UVF RESPONSE_DELAY = 01b. From UVF detection to tri-state of the power FETs                                                                         | 16    | 20   |       | $\mu\text{s}$ |