# TSB82AF15-EP PCI Express-Based IEEE 1394b OHCI Host Controller

#### 1 Features

- PCI Express<sup>™</sup> based 1394b Open Host Controller Interface (OHCI) link layer controller

- TQFP package simplifies board routing and eases board inspection

- Stand-alone link laver controller provides flexibility to interface with a 1394b s400 or a 1394b s800 physical layer controller

- Fully compliant with 1394 OHCI specification. revision 1.1 and revision 1.2 draft

- Compliant with PCI Express<sup>™</sup> (PCIe) base specification, revision 1.1. See Section 11.1

- Fully supports provisions of IEEE Std P1394b-2002, IEEE Std 1394-1995 and IEEE Std 1394a-2000

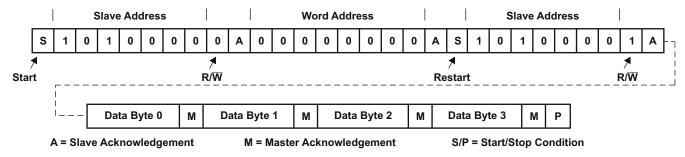

- EEPROM configuration support to load Global Unique ID for 1394 fabric

- Utilizes 100-MHz differential PCI Express™ common reference clock

- Support for D1, D2, D3<sub>hot</sub>

- Active-state link power management saves power when packet activity on the PCI Express<sup>™</sup> link is idle, using both L0s and L1 states

- Eight 3.3-V multifunction General-Purpose I/O (GPIO) terminals

- Supports defense, aerospace, and medical applications:

- Controlled baseline

- One assembly/test site and one fabrication site

- Extended product life cycle and product-change notification

### 2 Applications

- Avionics and defense

- Factory automation & control

- Medical

## 3 Description

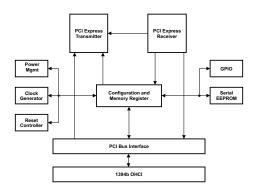

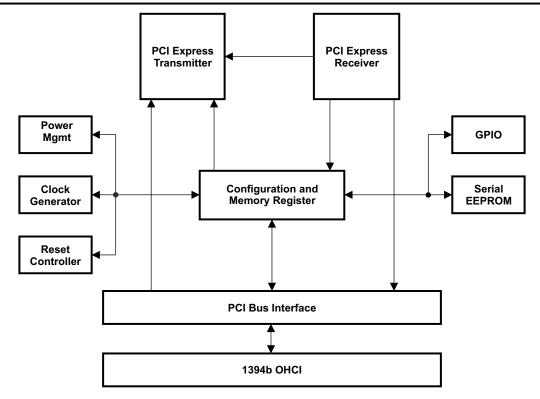

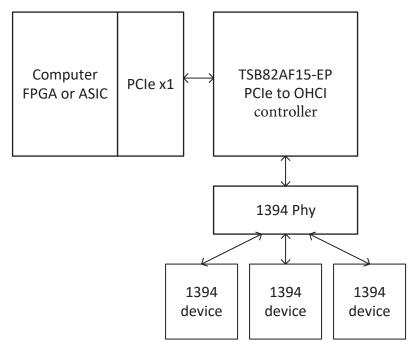

The Texas Instruments TSB82AF15-EP is a singlefunction PCI Express™ (PCIe) to PCI local bus translation bridge, where the PCI bus interface is internally connected to a 1394b open host controller/ link-layer controller. When the TSB82AF15-EP is properly configured, this solution provides full PCIe to 1394 link layer controller.

The TSB82AF15-EP simultaneously supports up to four posted write transactions, four nonposted transactions, and four completion transactions pending in each direction at any time. Each posted write data queue and completion data queue can store up to 8K bytes of data. The non-posted data queues can store up to 128 bytes of data.

#### Device Information (1)

| PART NUMBER  | PACKAGE     | BODY SIZE (NOM)        |

|--------------|-------------|------------------------|

| TSB82AF15-EP | 100 pin PZT | 14.00 mm × 14.00<br>mm |

For all available packages, see the orderable addendum at the end of the data sheet.

Simplified Block Diagram

## **Table of Contents**

| 1 Features1                                           | 10.3 Feature Description18                               |

|-------------------------------------------------------|----------------------------------------------------------|

| 2 Applications1                                       | 10.4 Device Functional Modes30                           |

| 3 Description1                                        | 10.5 Programming32                                       |

| 4 Revision History2                                   | 10.6 Register Maps33                                     |

| 5 Pin Configuration and Functions3                    | 11 Application and Implementation 164                    |

| 6 Specifications8                                     | 11.1 Known exceptions to functional specification        |

| 6.1 Absolute Maximum Ratings8                         | (errata)164                                              |

| 6.2 ESD Ratings 8                                     | 11.2 Application Information165                          |

| 6.3 Recommended Operating Conditions8                 | 12 Power Supply Recommendations167                       |

| 6.4 Thermal Information8                              | 13 Layout168                                             |

| 6.5 PCIe Differential Transmitter Output Ranges8      | 13.1 Layout Guidelines168                                |

| 6.6 PCIe Differential Receiver Input Ranges11         | 14 Device and Documentation Support169                   |

| 6.7 PCIe Differential Reference Clock Input Ranges 13 | 14.1 Device Support                                      |

| 6.8 Electrical Characteristics Over Recommended       | 14.2 Documentation Support169                            |

| Operating Conditions (3.3-V I/O)13                    | 14.3 Receiving Notification of Documentation Updates 169 |

| 6.9 Switching Characteristics13                       | 14.4 Support Resources169                                |

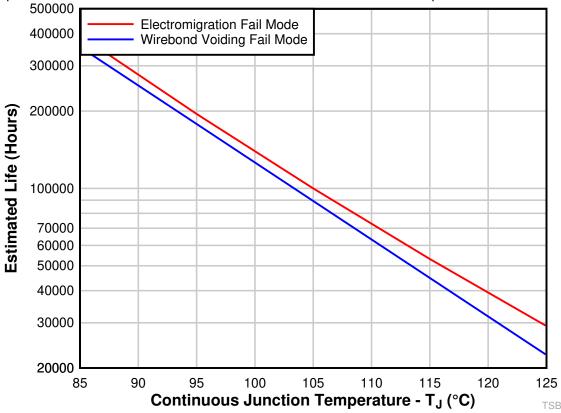

| 7 Operating Life Deration14                           | 14.5 Trademarks169                                       |

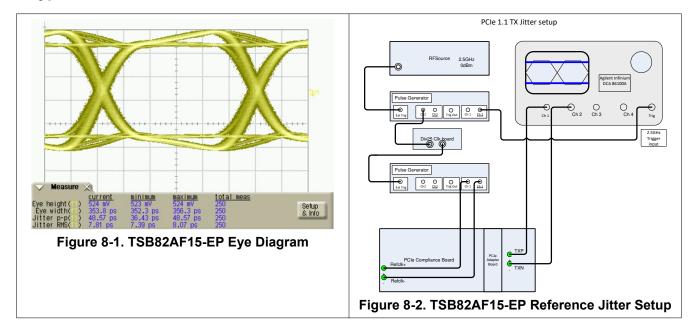

| 8 Typical Characteristics15                           | 14.6 Electrostatic Discharge Caution170                  |

| 9 Parameter Measurement Information16                 | 14.7 Glossary170                                         |

| 10 Detailed Description17                             | 15 Mechanical, Packaging, and Orderable                  |

| 10.1 Overview17                                       | Information171                                           |

| 10.2 Functional Block Diagram17                       | 15.1 Mechanical Data172                                  |

|                                                       |                                                          |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE           | REVISION | NOTES            |

|----------------|----------|------------------|

| September 2020 | *        | Initial release. |

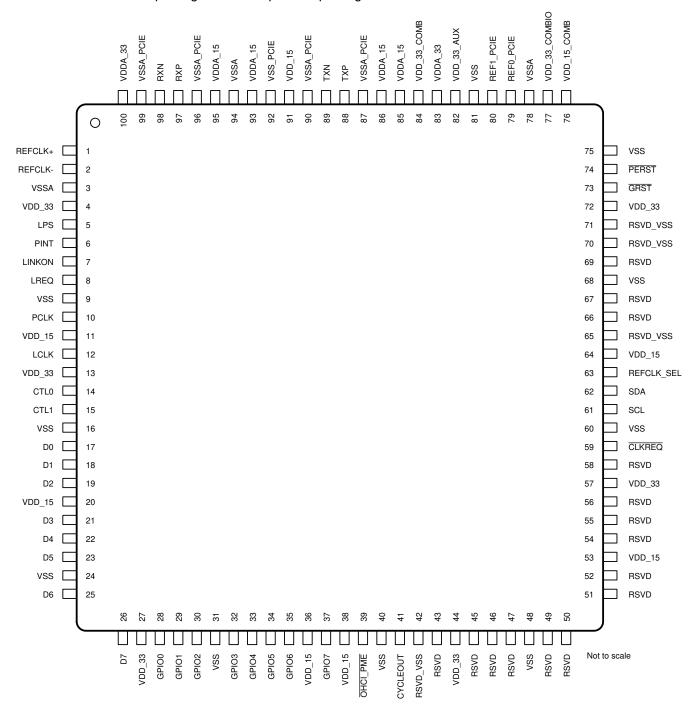

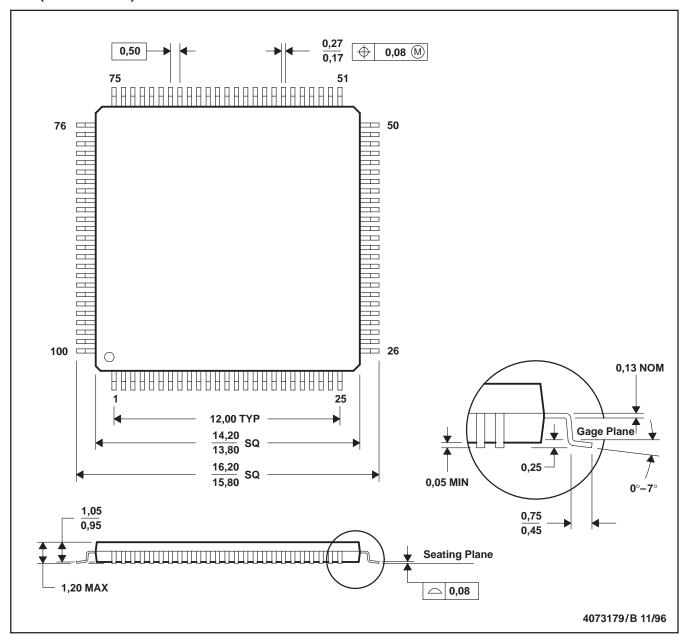

## 5 Pin Configuration and Functions

The TSB82AF15-EP is packaged in a 100-pin PZT package.

Figure 5-1. PZT Package 100-Pin QFP Top View

## **Pin Functions**

| PIN     |     | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | NO. | TYPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| REFCLK+ | 1   | DI      | Reference clock positive. REFCLK+ and REFCLK- comprise the differential input pair for the 100-MHz system reference clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| REFCLK- | 2   | DI      | Reference clock negative. REFCLK+ and REFCLK- comprise the differential input pair for th 100-MHz system reference clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| VSSA    | 3   | Р       | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| VDD_33  | 4   | Р       | 3.3-V digital I/O power. Filter from VDDA_33 supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| LPS     | 5   | 0       | Link power status. This terminal must be connected to the LPS input terminal of the connected PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| PINT    | 6   | I       | PHY interrupt. The connected PHY uses this signal to transfer status and interrupt information serially to the LLC. This terminal must be connected to the PINT output of the connected PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| LINKON  | 7   | I/O     | Link-on notification. LINKON is an input to the LLC from the connected PHY that is used to provide notification that a link-on packet has been received or an event, such as a port connection, has occurred. This I/O only has meaning when LPS is disabled. This includes the D0 (uninitialized), D2, and D3 power states. If LINKON becomes active in the D0 (uninitialized), D2, or D3 power state, the TSB82AF15-EP device sets bit 15 (PME_STS) in the power-management control and status register in the PCI configuration space at offset 48h. This terminal must be connected to the LKON output terminal of the connected PHY. |  |  |  |

| LREQ    | 8   | 0       | LLC request. The LLC uses this output to initiate a service request to the connected PHY. This terminal must be connected to the LREQ input of the connected PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VSS     | 9   | Р       | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PCLK    | 10  | 1       | PHY clock. This terminal must be connected to the PCLK output of the connected PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| VDD_15  | 11  | Р       | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| LCLK    | 12  | 0       | LLC clock. This terminal must be connected to the LCLK input terminal of the connected PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| VDD_33  | 13  | Р       | 3.3-V digital I/O power. Filter from VDDA_33 supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CTL0    | 14  | I/O     | Control. CTL[1:0] are bidirectional control bus signals that are used to indicate the phase of operation of the PHY link interface. Upon a reset of the interface, this bus is driven by the PHY. When driven by the PHY, information on CTL[1:0] is synchronous to PCLK. When driven by the link, information on CTL[1:0] is synchronous to LCLK. If not implemented, these terminals should be left unconnected.                                                                                                                                                                                                                        |  |  |  |

| CTL1    | 15  | I/O     | Control. CTL[1:0] are bidirectional control bus signals that are used to indicate the phase of operation of the PHY link interface. Upon a reset of the interface, this bus is driven by the PHY. When driven by the PHY, information on CTL[1:0] is synchronous to PCLK. When driven by the link, information on CTL[1:0] is synchronous to LCLK. If not implemented, these terminals should be left unconnected.                                                                                                                                                                                                                        |  |  |  |

| VSS     | 16  | Р       | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| D0      | 17  | I/O     | Data. D[7:0] comprise a bidirectional data bus that is used to carry 1394 packet data, packet speed, and grant type information between the PHY and the link. Upon a reset of the interface, this bus is driven by the PHY. When driven by the PHY, information on D[7:0] is synchronous to PCLK. When driven by the link, information on D[7:0] is synchronous to LCLK. If not implemented, these terminals should be left unconnected.                                                                                                                                                                                                  |  |  |  |

| D1      | 18  | I/O     | D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D2      | 19  | I/O     | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VDD_15  | 20  | Р       | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D3      | 21  | I/O     | D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D4      | 22  | I/O     | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D5      | 23  | I/O     | D5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VSS     | 24  | Р       | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| D6      | 25  | I/O     | D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| D7      | 26  | I/O     | D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VDD_33  | 27  | Р       | 3.3-V digital I/O power. Filter from VDDA 33 supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| PIN       |          | TVDE(1)             | DESCRIPTION                                                                                                                                                                                                |  |  |  |

|-----------|----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NO.      | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                |  |  |  |

| GPIO0     | 28       | I/O                 | General-purpose I/O 0. This terminal functions as a GPIO controlled by bit 0 (GPIO0_DIR) in the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal active pullup resistor. |  |  |  |

| GPIO1     | 29       | I/O                 | General-purpose I/O 1. This terminal functions as a GPIO controlled by bit 1 (GPIO1_DIR) the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal activity pullup resistor.  |  |  |  |

| GPIO2     | 30       | I/O                 | General-purpose I/O 2. This terminal functions as a GPIO controlled by bit 2 (GPIO2_DIR the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal actipullup resistor.        |  |  |  |

| VSS       | 31       | Р                   | Digital ground.                                                                                                                                                                                            |  |  |  |

| GPIO3     | 32       | I/O                 | General-purpose I/O 3. This terminal functions as a GPIO controlled by bit 3 (GPIO3_DIR) in the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal active pullup resistor. |  |  |  |

| GPIO4     | 33       | I/O                 | General-purpose I/O 4. This terminal functions as a GPIO controlled by bit 4 (GPIO4_DIR) in the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal active pullup resistor. |  |  |  |

| GPIO5     | 34       | I/O                 | General-purpose I/O 5. This terminal functions as a GPIO controlled by bit 5 (GPIO5_DIR) in the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal active pullup resistor. |  |  |  |

| GPIO6     | 35       | I/O                 | General-purpose I/O 6. This terminal functions as a GPIO controlled by bit 6 (GPIO6_DIR) in the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal active pullup resistor. |  |  |  |

| VDD_15    | 36       | Р                   | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                         |  |  |  |

| GPIO7     | 37       | I/O                 | General-purpose I/O 7. This terminal functions as a GPIO controlled by bit 7 (GPIO7_DIR) in the GPIO control register (See Section 10.6.1.60). Note: This terminal has an internal active pullup resistor. |  |  |  |

| VDD_15    | 38       | Р                   | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                         |  |  |  |

| OHCI_PME# | 39       | 0                   | OHCI power-management event. This is an optional signal that can be used by a device to request a change in the device or system power state. This signal must be enabled by software.                     |  |  |  |

| VSS       | 40       | Р                   | Digital ground.                                                                                                                                                                                            |  |  |  |

| CYCLEOUT  | 41       | 0                   | Cycle out. This terminal provides an 8-kHz cycle timer synchronization signal. If not implemented, this terminal should be left unconnected.                                                               |  |  |  |

| RSVD_VSS  | 42       | I                   | Reserved pin, connect to VSS.                                                                                                                                                                              |  |  |  |

| RSVD      | 43       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| VDD_33    | 44       | Р                   | 3.3-V digital I/O power. Filter from VDDA_33 supply.                                                                                                                                                       |  |  |  |

| RSVD      | 45       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 46       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 47       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| VSS       | 48       | Р                   | Digital ground.                                                                                                                                                                                            |  |  |  |

| RSVD      | 49       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 50       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 51       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 52       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| VDD_15    | 53       | Р                   | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                         |  |  |  |

| RSVD      | 54       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 55       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| RSVD      | 56       | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                           |  |  |  |

| VDD_33    | 57       | P                   | 3.3-V digital I/O power. Filter from VDDA_33 supply.                                                                                                                                                       |  |  |  |

|           | <u> </u> |                     | 1                                                                                                                                                                                                          |  |  |  |

| PIN           |     |                     |                                                                                                                                                                                                                                                                                    |  |  |

|---------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                        |  |  |

| CLKREQ        | 59  | 0                   | Clock request. This terminal is used to support the clock request protocol. <b>Note</b> : CLKREQ is an open-drain output buffer. An external pullup resistor is required, even if CLKREQ functionality is unused.                                                                  |  |  |

| VSS           | 60  | Р                   | Digital ground.                                                                                                                                                                                                                                                                    |  |  |

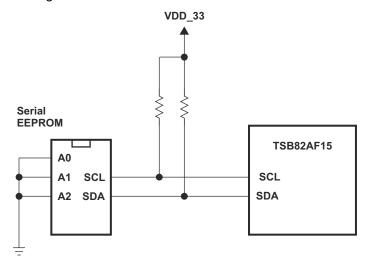

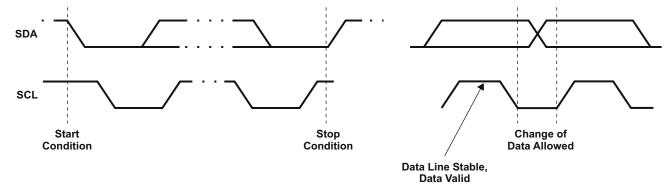

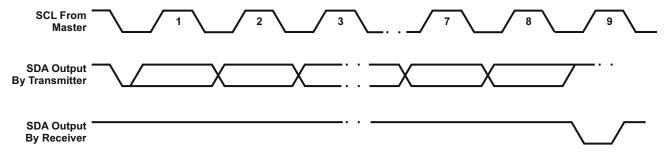

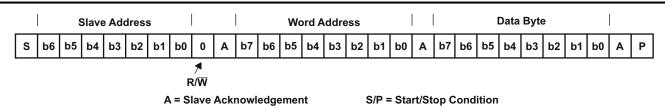

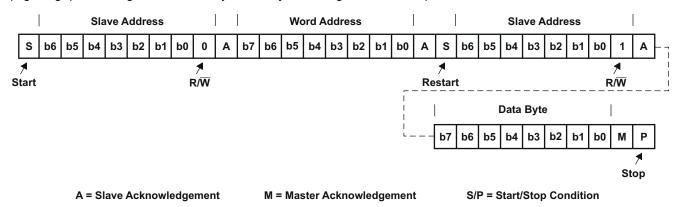

| SCL           | 61  | I/O                 | Serial-bus clock. This signal is used as a serial bus clock when a pullup is detected on SDA owhen the SBDETECT bit is set in the serial bus control and status register. Note: This terminal has an internal active pullup resistor.                                              |  |  |

| SDA           | 62  | I/O                 | Serial-bus data. This signal is used as serial bus data when a pullup is detected on SDA or when the SBDETECT bit is set in the serial bus control and status register. Note: In serial-bus mode, an external pullup resistor is required to prevent the SDA signal from floating. |  |  |

| REFCLK_SEL    | 63  | I                   | Reference clock select. This terminal selects the reference clock input. 0 = 100-MHz differential common reference clock used. REFCLK_SEL must be driven logic low to enable 100Mhz differential clock. 125Mhz single ended clocking is not supported.                             |  |  |

| VDD_15        | 64  | Р                   | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                                                                                                 |  |  |

| RSVD_VSS      | 65  | 1                   | Reserved Pin, connect to VSS.                                                                                                                                                                                                                                                      |  |  |

| RSVD          | 66  | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                                                                                                   |  |  |

| RSVD          | 67  | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                                                                                                   |  |  |

| VSS           | 68  | Р                   | Digital ground.                                                                                                                                                                                                                                                                    |  |  |

| RSVD          | 69  | 0                   | Reserved pin, leave unconnected.                                                                                                                                                                                                                                                   |  |  |

| RSVD_VSS      | 70  | ı                   | Reserved Pin, connect to VSS.                                                                                                                                                                                                                                                      |  |  |

| RSVD_VSS      | 71  | 1                   | Reserved Pin, connect to VSS.                                                                                                                                                                                                                                                      |  |  |

| VDD_33        | 72  | Р                   | 3.3-V digital I/O power. Filter from VDDA_33 supply.                                                                                                                                                                                                                               |  |  |

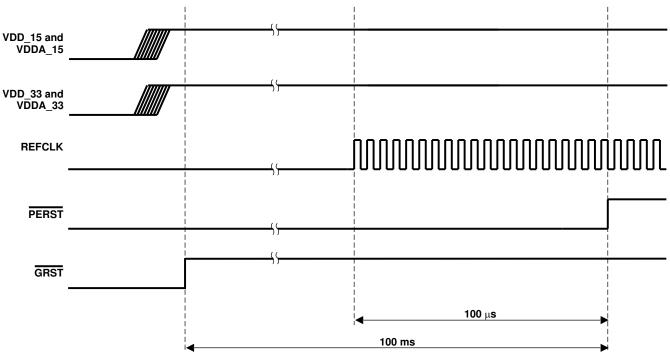

| GRST          | 73  | I                   | Global power reset. This reset brings all of the TSB82AF15-EP internal link registers to thei default states. This should be a one-time power-on reset. This terminal has hysteresis and integrated pullup resistor.                                                               |  |  |

| PERST         | 74  | I                   | PCI Express reset. PERST identifies when the system power is stable and generates an internal power-on reset. <b>Note</b> : The PERST input buffer has hysteresis.                                                                                                                 |  |  |

| VSS           | 75  | Р                   | Digital ground.                                                                                                                                                                                                                                                                    |  |  |

| VDD_15_COMB   | 76  | Р                   | Internal 1.5-V main power output for external bypass capacitor filtering. Caution: Do not use this terminal to supply external power to other devices.                                                                                                                             |  |  |

| VDD_33_COMBIO | 77  | Р                   | Internal 3.3-V IO power output for external bypass capacitor filtering. Caution: Do not use this terminal to supply external power to other devices.                                                                                                                               |  |  |

| VSSA          | 78  | Р                   | Analog ground.                                                                                                                                                                                                                                                                     |  |  |

| REF0_PCIE     | 79  | I/O                 | External reference resistor + and – terminals for setting TX driver current. An external                                                                                                                                                                                           |  |  |

| REF1_PCIE     | 80  | I/O                 | resistance of 14.532k $\Omega$ is connected between REF0_PCIE and REF1_PCIE terminals. To eliminate the need for a custom resistor, two series resistors are recommended: a 14.3k $\Omega$ , 1% resistor and a 232 $\Omega$ , 1% resistor.                                         |  |  |

| VSS           | 81  | Р                   | Digital ground.                                                                                                                                                                                                                                                                    |  |  |

| VDD_33_AUX    | 82  | Р                   | This terminal is connected to VSS through a $10k\Omega$ pulldown resistor. The TSB82AF15-EP does not support auxiliary power.                                                                                                                                                      |  |  |

| VDDA_33       | 83  | Р                   | 3.3-V digital I/O power for the link. Filter from VDD_33 supply.                                                                                                                                                                                                                   |  |  |

| VDD_33_COMB   | 84  | Р                   | Internal 3.3-V main power output for external bypass capacitor filtering. Caution: Do not use this terminal to supply external power to other devices.                                                                                                                             |  |  |

| VDDA_15       | 85  | Р                   | 1.5-V analog power for the link. Filter from VDD_15 supply.                                                                                                                                                                                                                        |  |  |

| VDDA_15       | 86  | Р                   | 1.5-V analog power for the link. Filter from VDD_15 supply.                                                                                                                                                                                                                        |  |  |

| VSSA_PCIE     | 87  | Р                   | Analog ground for PCIe function.                                                                                                                                                                                                                                                   |  |  |

| TXP           | 88  | DO                  | High-speed transmit pair. TXP and TXN comprise the differential transmit pair for the single PCIe lane.                                                                                                                                                                            |  |  |

| TXN           | 89  | DO                  | High-speed transmit pair. TXP and TXN comprise the differential transmit pair for the single PCIe lane                                                                                                                                                                             |  |  |

| VSSA_PCIE     | 90  | Р                   | Analog ground for PCIe function.                                                                                                                                                                                                                                                   |  |  |

| VDD_15        | 91  | Р                   | 1.5-V digital core power for the link. Filter from VDDA_15 supply.                                                                                                                                                                                                                 |  |  |

| PIN       |     | TYPE(1) | DESCRIPTION                                                                                           |  |

|-----------|-----|---------|-------------------------------------------------------------------------------------------------------|--|

| NAME      | NO. | ITPE    | DESCRIPTION                                                                                           |  |

| VSS_PCIE  | 92  | Р       | Digital ground for PCIe function.                                                                     |  |

| VDDA_15   | 93  | Р       | 1.5-V analog power for the link. Filter from VDD_15 supply.                                           |  |

| VSSA      | 94  | Р       | Analog ground.                                                                                        |  |

| VDDA_15   | 95  | Р       | 1.5-V analog power for the link. Filter from VDD_15 supply.                                           |  |

| VSSA_PCIE | 96  | Р       | Analog ground for PCle function.                                                                      |  |

| RXP       | 97  | DI      | High-speed receive pair. RXP and RXN comprise the differential receive pair for the single PCIe lane. |  |

| RXN       | 98  | DI      | High-speed receive pair. RXP and RXN comprise the differential receive pair for the single PCIe lane. |  |

| VSSA_PCIE | 99  | Р       | Analog ground for PCIe function.                                                                      |  |

| VDDA_33   | 100 | Р       | 3.3-V digital I/O power for the link. Filter from VDD_33 supply.                                      |  |

### (1) • Pin Type Legend:

- DI: Differential Input

- DO: Differential Output

- I: Input pin

- O: Output pin

- I/O: Pin can be Input or Output depending on configuration

- P: Power Supply or Ground

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating temperature range (unless otherwise noted)

|                     |                                       |                                                                    | MIN  | MAX                       | UNIT |  |

|---------------------|---------------------------------------|--------------------------------------------------------------------|------|---------------------------|------|--|

| V <sub>SUP_33</sub> | Supply voltage range                  | V <sub>DD_33</sub> , V <sub>DDA_33</sub> , V <sub>DD_33_COMB</sub> | -0.5 | 4.2                       | V    |  |

| V <sub>SUP_15</sub> | Supply voltage range                  | $V_{DD\_15}, V_{DDA\_15}, V_{DD\_15\_COMB}$                        | -0.5 | 2.1                       | V    |  |

|                     |                                       | PCIe (RX)                                                          | -0.6 | 1.2                       |      |  |

| VI                  | V <sub>I</sub> Input voltage range    | PCIe REFCLK                                                        | -0.5 | 1.2                       | V    |  |

|                     |                                       | Miscellaneous 3.3-V I/O                                            | -0.5 | V <sub>SUP_33</sub> + 0.5 |      |  |

| V                   | Output voltage range                  | PCIe (TX)                                                          | -0.5 | V <sub>SUP_15</sub> + 0.5 | V    |  |

| Vo                  |                                       | Miscellaneous 3.3-V I/O                                            | -0.5 | V <sub>SUP_33</sub> + 0.5 | V    |  |

|                     | Input clamp current (V                | < 0 or V <sub>I</sub> > VDD) <sup>(1)</sup>                        |      | 20                        | mA   |  |

|                     | Output clamp current (                | $V_{\rm O} < 0 \text{ or } V_{\rm O} > VDD)^{(2)}$                 |      | 20                        | mA   |  |

| TJ                  | Absolute maximum junction temperature |                                                                    |      | 150                       | °C   |  |

| T <sub>stg</sub>    | Storage temperature ra                | ange                                                               | -65  | 150                       | °C   |  |

<sup>(1)</sup> Applies for external input and bidirectional buffers.  $V_1 < 0$  or  $V_1 > V_{SUP\_33}$

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

|                     |                                  | OPERATION | MIN | NOM | MAX | UNIT |

|---------------------|----------------------------------|-----------|-----|-----|-----|------|

| V <sub>SUP_15</sub> | Supply voltage                   | 1.5 V     | 1.4 | 1.5 | 1.6 | V    |

| V <sub>SUP_33</sub> | Supply voltage (I/O)             | 3.3 V     | 3   | 3.3 | 3.6 | V    |

| T <sub>A</sub>      | Operating Temperature (free-air) |           | -40 | 25  | 110 | °C   |

| TJ                  | Junction temperature             |           | -40 | 25  | 125 | °C   |

#### **6.4 Thermal Information**

|                      | THERMAL METRIC <sup>(1)</sup>                | TQFP (PZT) | UNIT |

|----------------------|----------------------------------------------|------------|------|

|                      | THERWAL WETRICKY                             | 100 PINS   | UNII |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 46.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 7.0        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 25.1       | °C/W |

| Ψ <sub>JT</sub>      | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 24.6       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

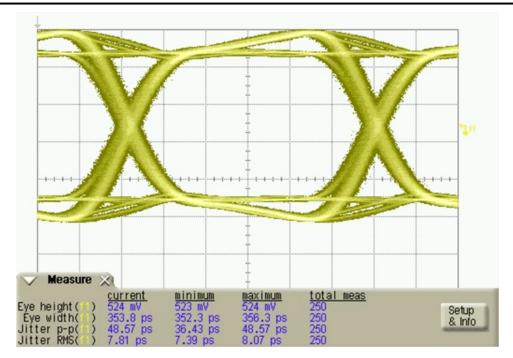

### 6.5 PCIe Differential Transmitter Output Ranges

TXP and TXN. At  $T_J = -40^{\circ}$ C to 125°C, unless otherwise noted.

| PARAMETER |               | MIN    | NOM | MAX    | UNIT | COMMENTS                                                                                   |

|-----------|---------------|--------|-----|--------|------|--------------------------------------------------------------------------------------------|

| UI        | Unit interval | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps 300 ppm. UI does not account for SSC dictated variations. <sup>(1)</sup> |

<sup>(2)</sup> Applies for external output and bidirectional buffers.  $V_O < 0$  or  $V_O > V_{SUP\_33}$

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

TXP and TXN. At  $T_J = -40^{\circ}$ C to 125°C, unless otherwise noted.

| PARAMI                                       | ETER                                                                                               | MIN   | NOM | MAX  | UNIT | COMMENTS                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|----------------------------------------------------------------------------------------------------|-------|-----|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-DIFFp-p</sub>                      | Differential peak-to-peak output voltage                                                           | 0.8   |     | 1.2  | V    | $V_{TX-DIFFp-p} = 2* V_{TXP} - V_{TXN} ^{(2)}$                                                                                                                                                                                                                                                                                                             |

| V <sub>TX-DE-RATIO</sub>                     | Deemphasized<br>differential output voltage<br>(ratio)                                             | 3.0   | 3.5 | 4.0  | dB   | This is the ratio of the V <sub>TX-DIFFp-p</sub> of the second and following bits after a transition divided by the V <sub>TX-DIFFp-p</sub> of the first bit after a transition. (2)                                                                                                                                                                       |

| TTX-EYE                                      | Minimum TX eye width                                                                               | 0.75  |     |      | UI   | The maximum transmitter jitter can be derived as $T_{TXMAX-JITTER} = 1 - T_{TX-EYE} = 0.3$ UI. (2) (3)                                                                                                                                                                                                                                                     |

| T <sub>TX-EYE-MEDIAN-to-MAX-</sub> JITTER    | Maximum time between jitter median and maximum deviation from the median                           |       |     | 0.15 | UI   | Jitter is defined as the measurement variation of the crossing points (V <sub>TX-DIFFp-p</sub> = 0 V) in relation to recovered TX UI. A recovered TX UI is calculated over 3500 consecutive UIs of sample data. Jitter is measured using all edges of the 250 consecutive UIs in the center of the 3500 UIs used for calculating the TX UI. <sup>(2)</sup> |

| T <sub>TX-RISE</sub><br>T <sub>TX-FALL</sub> | P/N TX output rise/fall time                                                                       | 0.125 |     |      | UI   | (2) (3)                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>TX-CM-ACp</sub>                       | RMS ac peak common-<br>mode output voltage                                                         |       |     | 20   | mV   | $ \begin{vmatrix} V_{\text{TX-CM-ACp}} = \text{RMS}( V_{\text{TX}}P + V_{\text{TXN}} /2 - V_{\text{TX-CM-DC}}) \\  V_{\text{TX-CM-DC}} =  V_{\text{TX-CM-DC}}  \end{vmatrix} $                                                                                                                                                                             |

| VTX-CM-DC-ACTIVE-IDLE-DELTA                  | Absolute delta of dc<br>common-mode voltage<br>during L0 and electrical<br>idle                    |       |     | 100  | mV   |                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>TX-CM-DC-LINE-DELTA</sub>             | Absolute delta of dc<br>common-mode voltage<br>between P and N                                     |       |     | 25   | mV   | $\begin{split}  V_{TXP\text{-}CM\text{-}DC} - V_{TXN\text{-}CM\text{-}DC}  &\leq 25 \text{ mV when} \\ V_{TXP\text{-}CM\text{-}DC} &= DC_{(avg)} \text{ of }  V_{TXP}  \\ V_{TXN\text{-}CM\text{-}DC} &= DC_{(avg)} \text{ of }  V_{TXN} ^{(2)} \end{split}$                                                                                               |

| $V_{TX	ext{-}IDLE	ext{-}DIFFp}$              | Electrical idle differential peak output voltage                                                   |       |     | 20   | mV   | $V_{TX-IDLE-DIFFp} =  V_{TXP-Idle} - V_{TXN-Idle}  \le 20$<br>$mV^{(2)}$                                                                                                                                                                                                                                                                                   |

| V <sub>TX-RCV-DETECT</sub>                   | Amount of voltage change allowed during receiver detection                                         |       |     | 600  | mV   | The total amount of voltage change that a transmitter can apply to sense whether a low impedance receiver is present                                                                                                                                                                                                                                       |

| V <sub>TX-DC-CM</sub>                        | TX dc common-mode voltage                                                                          | 0     |     | 3.6  | V    | The allowed dc common-mode voltage under any condition                                                                                                                                                                                                                                                                                                     |

| I <sub>TX-SHORT</sub>                        | TX short-circuit current limit                                                                     |       |     | 90   | mA   | The total current the transmitter can provide when shorted to its ground                                                                                                                                                                                                                                                                                   |

| T <sub>TX-IDLE-MIN</sub>                     | Minimum time spent in electrical idle                                                              | 50    |     |      | UI   | Minimum time a transmitter must be in electrical Idle. Utilized by the receiver to start looking for an electrical idle exit after successfully receiving an electrical idle ordered set.                                                                                                                                                                  |

| T <sub>TX-IDLE-SET-to-IDLE</sub>             | Maximum time to transition to a valid electrical idle after sending an electrical idle ordered set |       |     | 20   | UI   | After sending an electrical idle ordered set, the transmitter must meet all electrical idle specifications within this time. This is considered a debounce time for the transmitter to meet electrical idle after transitioning from L0.                                                                                                                   |

| T <sub>TX-IDLE-to-</sub> DIFF-DATA           | Maximum time to transition to valid TX specifications after leaving an electrical idle condition   |       |     | 20   | UI   | Maximum time to meet all TX specifications when transitioning from electrical idle to sending differential data. This is considered a debounce time for the TX to meet all TX specifications after leaving electrical idle.                                                                                                                                |

| RL <sub>TX-DIFF</sub>                        | Differential return loss                                                                           | 10    |     |      | dB   | Measured over 50 MHz to 1.25 GHz <sup>(4)</sup>                                                                                                                                                                                                                                                                                                            |

| RL <sub>TX-CM</sub>                          | Common-mode return loss                                                                            | 6     |     |      | dB   | Measured over 50 MHz to 1.25 GHz <sup>(4)</sup>                                                                                                                                                                                                                                                                                                            |

#### TXP and TXN. At $T_{J} = -40^{\circ}$ C to 125°C, unless otherwise noted.

| PARAMETER               |                              |    | NOM | MAX | UNIT | COMMENTS                                                     |

|-------------------------|------------------------------|----|-----|-----|------|--------------------------------------------------------------|

| Z <sub>TX-DIFF-DC</sub> | DC differential TX impedance | 80 | 100 | 120 | Ω    | TX dc differential mode low impedance                        |

| Z <sub>TX-DC</sub>      | Transmitter dc impedance     | 40 |     |     | Ω    | Required TXP as well as TXN dc impedance during all states   |

| C <sub>TX</sub>         | AC coupling capacitor        | 75 |     | 200 | nF   | All transmitters are ac coupled and are required on the PWB. |

- (1) No test load is necessarily associated with this value.

- (2) Specified at the measurement point into a timing and voltage compliance test load and measured over any 250 consecutive TX UIs.

- (3) A T<sub>TX-EYE</sub> = 0.75 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.25 UI for the transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It must be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- (4) The transmitter input impedance results in a differential return loss greater than or equal to 10 dB and a common-mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50 to ground for both the P and N lines. Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

Product Folder Links: TSB82AF15-EP

## 6.6 PCIe Differential Receiver Input Ranges

RXP and RXN. At  $T_J = -40^{\circ}$ C to 125°C, unless otherwise noted.

| PARAMETER                                 |                                                                      | MIN    | NOM | MAX    | UNIT | COMMENTS                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|----------------------------------------------------------------------|--------|-----|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                        | Unit interval                                                        | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps 300 ppm. UI does not account for SSC dictated variations <sup>(1)</sup>                                                                                                                                                                                                                                                                  |

| V <sub>RX-DIFFp-p</sub>                   | Differential input peak-to-<br>peak voltage                          | 0.175  |     | 1.200  | >    | $V_{RX-DIFFp-p} = 2* V_{RXP} - V_{RXN},  ^{(2)}$                                                                                                                                                                                                                                                                                                           |

| T <sub>RX-EYE</sub>                       | Minimum receiver eye width                                           | 0.4    |     |        | UI   | The maximum interconnect media and transmitter jitter that can be tolerated by the receiver is derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6 \ UI^{(2)}$ (3)                                                                                                                                                                                        |

| T <sub>RX-EYE-MEDIAN-to-MAX-</sub> JITTER | Maximum time between jitter median and maximum deviation from median |        |     | 0.3    | UI   | Jitter is defined as the measurement variation of the crossing points (V <sub>RX-DIFFp-p</sub> = 0 V) in relation to recovered TX UI. A recovered TX UI is calculated over 3500 consecutive UIs of sample data. Jitter is measured using all edges of the 250 consecutive UIs in the center of the 3500 UIs used for calculating the TX UI. <sup>(2)</sup> |

| V <sub>RX-CM-ACp</sub>                    | AC peak common-mode input voltage                                    |        |     | 150    | mV   | $\begin{aligned} V_{\text{RX-CM-ACp}} &= \text{RMS}( V_{\text{RXP}} + V_{\text{RXN}} /2 - V_{\text{RX-}} \\ &                  $                                                                                                                                                                                                                           |

| RL <sub>RX-DIFF</sub>                     | Differential return loss                                             | 10     |     |        | dB   | Measured over 50 MHz to 1.25 GHz with the P and N lines biased at +300 mV and - 300 mV, respectively <sup>(4)</sup>                                                                                                                                                                                                                                        |

| RL <sub>RX-CM</sub>                       | Common-mode return loss                                              | 6      |     |        | dB   | Measured over 50 MHz to 1.25 GHz with the P and N lines biased at +300 mV and 300 mV, respectively <sup>(4)</sup>                                                                                                                                                                                                                                          |

| Z <sub>RX-DIFF-DC</sub>                   | DC differential input impedance                                      | 80     | 100 | 120    | Ω    | RX dc differential mode impedance <sup>(4)</sup>                                                                                                                                                                                                                                                                                                           |

| Z <sub>RX-DC</sub>                        | DC input impedance                                                   | 40     | 50  | 60     | Ω    | Required RXP as well as RXN dc impedance (50 Ω 20% tolerance) <sup>(2) (5)</sup>                                                                                                                                                                                                                                                                           |

| Z <sub>RX-HIGH-IMP-D</sub>                | Powered down dc input impedance                                      | 200    |     |        | kΩ   | Required RXP as well as RXN dc impedance when the receiver terminations do not have power <sup>(6)</sup>                                                                                                                                                                                                                                                   |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>          | Electrical idle detect threshold                                     | 65     |     | 175    | mV   | V <sub>RX-IDLE-DET-DIFFp-p</sub> = 2* V <sub>RXP</sub> - V <sub>RXN</sub>  <br>measured at the receiver package<br>terminals                                                                                                                                                                                                                               |

| T <sub>RX-IDLE-DET-DIFF-ENTER-TIME</sub>  | Unexpected electrical idle enter detect threshold integration time   |        |     | 10     | ms   | An unexpected electrical idle  (V <sub>RX-DIFFp-p</sub> < V <sub>RX-IDLE-DET-DIFFp-p</sub> ) must be recognized no longer than  T <sub>RX-IDLE-DET-DIFF-ENTER-TIME</sub> to signal an unexpected idle condition.                                                                                                                                           |

- (1) No test load is necessarily associated with this value.

- (2) Specified at the measurement point and measured over any 250 consecutive UIs. A test load must be used as the RX device when taking measurements. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI is used as a reference for the eye diagram.

- (3) A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total UI jitter budget collected over any 250 consecutive TX UIs. It must be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UIs must be used as the reference for the eye diagram.

- (4) The receiver input impedance results in a differential return loss greater than or equal to 15 dB with the P line biased to 300 mV and the N line biased to 300 mV and a common-mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50Ω to ground for both the P and N line (i.e., as measured by a vector network analyzer with 50Ω probes). The series capacitors CTX is optional for the return loss measurement.

#### TSB82AF15-EP

SCPS271 - JULY 2020

- (5) Impedance during all link training status state machine (LTSSM) states. When transitioning from a PCIe reset to the detect state (the initial state of the LTSSM) there is a 5-ms transition time before receiver termination values must be met on the unconfigured lane of a port.

- (6) The RX dc common-mode impedance that exists when no power is present or PCIe reset is asserted. This helps ensure that the receiver detect circuit does not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

Product Folder Links: TSB82AF15-EP

## 6.7 PCle Differential Reference Clock Input Ranges

REFCLK+ and REFCLK-. At  $T_J = -40^{\circ}$ C to 125°C, unless otherwise noted.

|                         | PARAMETER                               | MIN   | NOM | MAX   | UNIT | COMMENTS                                                                                                                                                                                                                                    |

|-------------------------|-----------------------------------------|-------|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>IN-DIFF</sub>    | Differential input frequency            |       | 100 |       | MHz  | The input frequency is 100 MHz + 300 ppm and 2800 ppm including SSC-dictated variations.                                                                                                                                                    |

| V <sub>RX-DIFFp-p</sub> | Differential input peak-to-peak voltage | 0.175 |     | 1.200 | V    | V <sub>RX-DIFFp-p</sub> = 2* V <sub>REFCLK+</sub> V <sub>REFCLK-</sub>                                                                                                                                                                      |

| V <sub>RX-CM-ACp</sub>  | AC peak common-mode input voltage       |       |     | 140   | mV   | $\begin{aligned} V_{\text{RX-CM-ACp}} &= \text{RMS}( V_{\text{REFCLK+}} + V_{\text{REFCLK-}} /2\\ V_{\text{RX-CM-DC}}) \ V_{\text{RX-CM-DC}} &= DC_{(\text{avg})} \ \text{of} \\  V_{\text{REFCLK+}} + V_{\text{REFCLK-}} /2 \end{aligned}$ |

| Duty cycle              |                                         | 40%   |     | 60%   |      | Differential waveform input duty cycle                                                                                                                                                                                                      |

| Z <sub>RX-DIFF-DC</sub> | DC differential input impedance         |       | 20  |       | kΩ   | REFCLK dc differential mode impedance                                                                                                                                                                                                       |

## 6.8 Electrical Characteristics Over Recommended Operating Conditions (3.3-V I/O)

All signals (I) Input, (O) Output, (I/O) pins excluding the differential Inputs (DI), Differential Outputs (DO) pins. At  $T_{\perp} = -40$ °C to 125°C, unless otherwise noted.

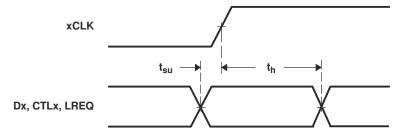

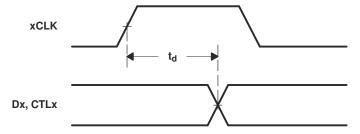

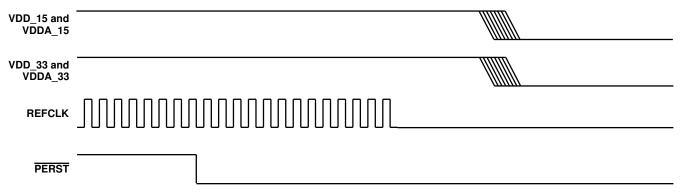

|                  | PARAMETER                                                                               | OPERATION           | TEST CONDITIONS                           | MIN                     | MAX                      | UNIT |