# Resonant-Mode Power Supply Controllers

### **FEATURES**

- Controls Zero Current Switched (ZCS) or Zero Voltage Switched (ZVS) Quasi-Resonant Converters

- Zero-Crossing Terminated One-Shot Timer

- Precision 1%, Soft-Started 5V Reference

- Programmable Restart Delay Following Fault

- Voltage-Controlled Oscillator (VCO) with Programmable Minimum and Maximum Frequencies from 10kHz to 1MHz

- Low Start-Up Current (150μA typical)

- Dual 1 Amp Peak FET Drivers

- UVLO Option for Off-Line or DC/DC Applications

#### DESCRIPTION

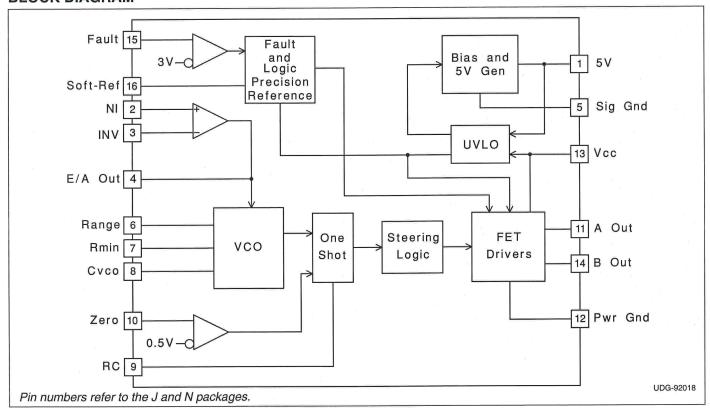

The UC1861-1868 family of ICs is optimized for the control of Zero Current Switched and Zero Voltage Switched quasi-resonant converters. Differences between members of this device family result from the various combinations of UVLO thresholds and output options. Additionally, the one-shot pulse steering logic is configured to program either on-time for ZCS systems (UC1865-1868), or off-time for ZVS applications (UC1861-1864).

The primary control blocks implemented include an error amplifier to compensate the overall system loop and to drive a voltage controlled oscillator (VCO), featuring programmable minimum and maximum frequencies. Triggered by the VCO, the one-shot generates pulses of a programmed maximum width, which can be modulated by the Zero Detection comparator. This circuit facilitates "true" zero current or voltage switching over various line, load, and temperature changes, and is also able to accommodate the resonant components' initial tolerances.

Under-Voltage Lockout is incorporated to facilitate safe starts upon power-up. The supply current during the under-voltage lockout period is typically less than  $150\mu A$ , and the outputs are actively forced to the low state. (continued)

| Device  | 1861        | 1862      | 1863        | 1864     | 1865        | 1866      | 1867        | 1868     |

|---------|-------------|-----------|-------------|----------|-------------|-----------|-------------|----------|

| UVLO    | 16.5/10.5   | 16.5/10.5 | 8/7         | 8/7      | 16.5/10.5   | 16.5/10.5 | 8/7         | 8/7      |

| Outputs | Alternating | Parallel  | Alternating | Parallel | Alternating | Parallel  | Alternating | Parallel |

| "Fixed" | Off Time    | Off Time  | Off Time    | Off Time | On Time     | On Time   | On Time     | On Time  |

#### **BLOCK DIAGRAM**

## **DESCRIPTION** (cont.)

UVLO thresholds for the UC1861/62/65/66 are 16.5V (ON) and 10.5V (OFF), whereas the UC1863/64/67/68 thresholds are 8V (ON) and 7V (OFF). After  $V_{\rm CC}$  exceeds the UVLO threshold, a 5V generator is enabled which provides bias for the internal circuits and up to 10mA for external usage.

A Fault comparator serves to detect fault conditions and set a latch while forcing the output drivers low. The Soft-Ref pin serves three functions: providing soft start, restart delay, and the internal system reference.

Each device features dual 1 Amp peak totem pole output drivers for direct interface to power MOSFETS. The outputs are programmed to alternate in the UC1861/63/65/67 devices. The UC1862/64/66/68 outputs operate in unison alllowing a 2 Amp peak current.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> 22V                            |

|------------------------------------------------|

| Output Current                                 |

| Source or Sink (Pins 11 & 14) 0.5A             |

| DC Pulse (0.5μs)                               |

| Power Ground Voltage                           |

| Inputs (Pins 2, 3, 10, & 15)0.4 to 7V          |

| Error Amp Output Current±2mA                   |

| Power Dissipation1W                            |

| Junction Temperature (Operating)150°C          |

| Lead Temperature (Soldering, 10 seconds) 300°C |

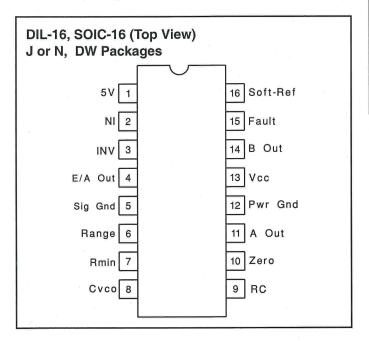

All voltages are with respect to signal ground and all currents are positive into the specified terminal. Pin numbers refer to the J and N packages. Consult Unitrode Integrated Circuits databook for information regarding thermal specifications and limitations of packages.

#### CONNNECTION DIAGRAMS

PLCC-20 & LCC-20 (Top View)

Q & L Package

| PACKAGE PIN FUNCTION |     |  |  |  |  |  |  |

|----------------------|-----|--|--|--|--|--|--|

| FUNCTION             | PIN |  |  |  |  |  |  |

| Soft Ref             | 11  |  |  |  |  |  |  |

| 5V                   | 2   |  |  |  |  |  |  |

| NI                   | 3   |  |  |  |  |  |  |

| INV                  | 4   |  |  |  |  |  |  |

| E/A Out              | 5   |  |  |  |  |  |  |

| Sig Gnd              | 6   |  |  |  |  |  |  |

| Range                | 7   |  |  |  |  |  |  |

| RMIN                 | 8   |  |  |  |  |  |  |

| Cvco                 | 9   |  |  |  |  |  |  |

| RC                   | 10  |  |  |  |  |  |  |

| Zero                 | 11  |  |  |  |  |  |  |

| NC                   | 12  |  |  |  |  |  |  |

| NC                   | 13  |  |  |  |  |  |  |

| A Out                | 14  |  |  |  |  |  |  |

| Pwr Gnd              | 15  |  |  |  |  |  |  |

| Pwr Gnd              | 16  |  |  |  |  |  |  |

| Vcc                  | 17  |  |  |  |  |  |  |

| B Out                | 18  |  |  |  |  |  |  |

| NC                   | 19  |  |  |  |  |  |  |

| Fault                | 20  |  |  |  |  |  |  |

|                      | 1   |  |  |  |  |  |  |

|                      |     |  |  |  |  |  |  |

**ELECTRICAL CHARACTERISTICS** Unless otherwise stated, all specifications apply for −55°C≤Ta≤125°C for the UC186x, −25°C≤Ta≤85°C for the UC286x, and 0°C≤Ta≤70°C for the UC386x, Vcc=12V, Cvco=1nF, Range=7.15k, RMIN=86.6k, C=200pF, R=4.02k, and Csr=0.1µF. Ta=TJ

| PARAMETER                        | TEST CONDITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|----------------------------------|---------------------------------------------------------|------|------|------|-------|

| 5V Generator                     |                                                         |      |      |      |       |

| Output Voltage                   | $12V \le Vcc \le 20V$ , $-10mA \le Io \le 0mA$          | 4.8  | 5.0  | 5.2  | V     |

| Short Circuit Current            | Vo = 0V                                                 | -150 |      | -15  | mA    |

| Soft-Reference                   |                                                         |      |      |      | •     |

| Restart Delay Current            | V = 2V                                                  | 10   | 20   | 35   | μΑ    |

| Soft Start Current               | V = 2V                                                  | -650 | -500 | -350 | μΑ    |

| Reference Voltage                | $T_J = 25$ °C, $I_O = 0$ A                              | 4.95 | 5.00 | 5.05 | V     |

|                                  | $12V \le Vcc \le 20V$ , $-200\mu A \le Io \le 200\mu A$ | 4.85 |      | 5.15 | V     |

| Line Regulation                  | 12V ≤ Vcc ≤ 20V                                         |      | 2    | 20   | mV    |

| Load Regulation                  | –200μA ≤ Io ≤ 200μA                                     |      | 10   | 30   | mV    |

| Error Amplifier (Note 3)         |                                                         |      |      |      |       |

| Input Offset Voltage             | VCM = 5V, $Vo = 2V$ , $IO = 0A$                         | -10  |      | 10   | mV    |

| Input Bias Current               | Vcm = 0V                                                | -2.0 | -0.3 |      | μΑ    |

| Voltage Gain                     | $Vcm = 5V, 0.5V \le Vo \le 3.7V, Io = 0A$               | 70   | 100  | 1    | dB    |

| Power Supply Rejection Ratio     | $Vcm = 5V$ , $Vo = 2V$ , $12V \le Vcc \le 20V$          | 70   | 100  | 1    | dB    |

| Error Amplifier (Note 3) (cont.) |                                                         |      |      |      |       |

| Common Mode Rejection Ratio      | $0V \le Vcm \le 6V, Vo = 2V$                            | 65   | 100  |      | dB    |

| Vout Low                         | $VID = -100 \text{mV}, IO = 200 \mu \text{A}$           |      | 0.17 | 0.25 | V     |

| Vout High                        | $VID = 100 mV$ , $IO = -200 \mu A$                      | 3.9  | 4.2  |      | V     |

| Unity Gain Bandwidth             | (Note 4)                                                | 0.5  | 0.8  |      | MHz   |

| Voltage Controlled Oscillator    |                                                         |      |      |      |       |

| Maximum Frequency                | VID (Error Amp) = 100mV, TJ = 25°C                      | 450  | 500  | 550  | kHz   |

|                                  | VID (Error Amp) = 100mV                                 | 425  |      | 575  | kHz   |

| Minimum Frequency                | VID (Error Amp) = $-100$ mV, TJ = $25$ °C               | 45   | 50   | 55   | kHz   |

|                                  | VID (Error Amp) = -100mV                                | 42   |      | 58   | kHz   |

| One Shot                         |                                                         |      |      |      |       |

| Zero Comparator Vth              |                                                         | 0.45 | 0.50 | 0.55 | V     |

| Propagation Delay                | (Note 4)                                                | u .  | 120  | 200  | ns    |

| Maximum Pulse Width              | VZERO = 1V                                              | 850  | 1000 | 1150 | ns    |

| Maximum to Minimum Pulse         | Vzero = 0V UCx861 - UCx864                              | 2.5  | 4    | 5.5  |       |

| Width Ratio                      | Vzero = 0V UCx865 - UCx86855°C to +85°C                 | 4    | 5.5  | 7    |       |

|                                  | Vzero = 0V UCx865 - UCx868, +125°C                      | 3.8  | 5.5  | 7    | 11    |

| Output Stage                     |                                                         |      |      |      |       |

| Rise and Fall Time               | CLOAD = 1nF (Note 4)                                    | 1    | 25   | 45   | ns    |

| Output Low Saturation            | Io = 20mA                                               |      | 0.2  | 0.5  | V     |

|                                  | Io = 200mA                                              |      | 0.5  | 2.2  | V     |

| Output High Saturation           | Io = -200mA, down from Vcc                              |      | 1.7  | 2.5  | V     |

| UVLO Low Saturation              | Io = 20mA                                               |      | 0.8  | 1.5  | V     |

| Fault Comparator                 |                                                         | 1    |      |      |       |

| Fault Comparator Vth             |                                                         | 2.85 | 3.00 | 3.15 | V     |

| Delay to Output                  | (Note 4) (Note 5)                                       |      | 100  | 200  | ns    |

**ELECTRICAL CHARACTERISTICS** Unless otherwise stated, all specifications apply for –55°C≤Ta≤125°C for the UC186x, –25°C≤Ta≤85°C for the UC286x, and 0°C≤Ta≤70°C for the UC386x, Vcc=12V, Cvco=1nF, Range=7.15k, Rmin=86.6k, C=200pF, R=4.02k, and Csr=0.1μF. Ta=TJ.

| PARAMETER              | PARAMETER TEST CONDITIONS      |     |      | MAX  | UNITS |

|------------------------|--------------------------------|-----|------|------|-------|

| UVLO                   |                                |     |      |      | 1     |

| Vcc Turn-on Threshold  | UCx861, UCx862, UCx865, UCx866 | 15  | 16.5 | 18   | V     |

|                        | UCx863, UCx864, UCx867, UCx868 | 7   | 8.0  | 9    | V     |

| Vcc Turn-off Threshold | UCx861, UCx862, UCx865, UCx866 | 9.5 | 10.5 | 11.5 | V     |

|                        | UCx863, UCx864, UCx867, UCx868 | 6   | 7.0  | 8    | V     |

| Icc Start              | Vcc = Vcc(on) - 0.3V           |     | 150  | 300  | μΑ    |

| Icc Run                | VID = 100mV                    |     | 25   | 32   | mA    |

Note 1: Currents are defined as positive into the pin.

Note 2: Pulse measurement techniques are used to insure that TJ = TA.

Note 3: VID = V(NI) - V(INV).

Note 4: This parameter is not 100% tested in production but guaranteed by design.

Note 5: Vi = 0 to 4V

tr(Vi) 10ns

tpd = t(Vo = 6V) - t(Vi = 3V)

#### APPLICATION INFORMATION

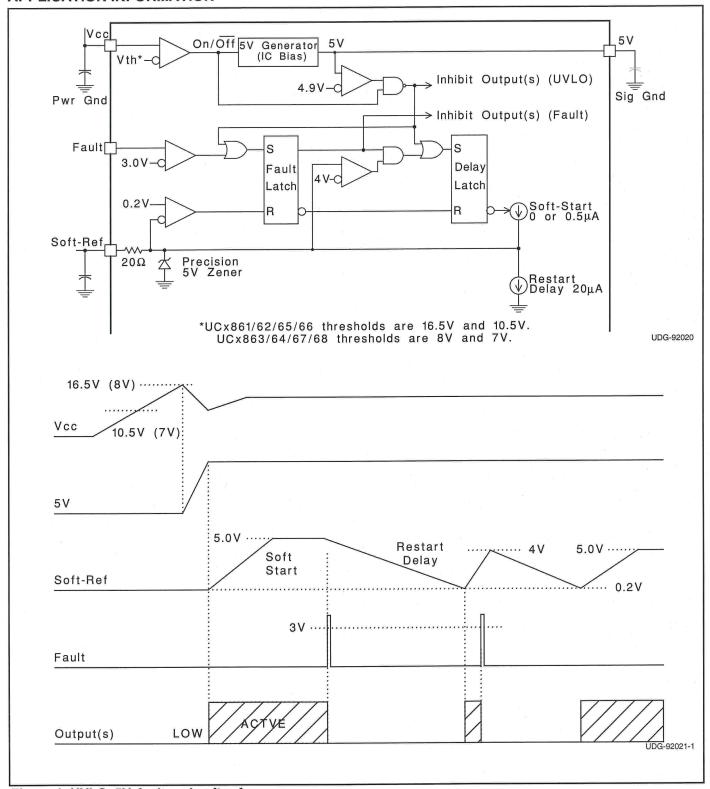

UVLO & 5V GENERATOR (See Figure 1): When power is applied to the chip and Vcc is less than the upper UVLO threshold, lcc will be less than  $300\mu A$ , the 5V generator will be off, and the outputs will be actively held low.

When Vcc exceeds the upper UVLO threshold, the 5V generator turns on. Until the 5V pin exceeds 4.9V, the outputs will still remain low.

The 5V pin should be bypassed to signal ground with a  $0.1\mu F$  capacitor. The capacitor should have low equivalent series resistance and inductance.

**FAULT AND SOFT-REFERENCE (See Figure 1):** The Soft-Ref pin serves three functions: system reference, restart delay, and soft-start. Designed to source or sink 200 $\mu$ A, this pin should be used as the input reference for the error amplifier circuit. This pin requires a bypass capacitor of at least 0.1 $\mu$ F. This yields a minimum soft-start time of 1ms.

Under-Voltage Lockout sets both the fault and restart delay latches. This holds the outputs low and discharges the Soft-Ref pin. After UVLO, the fault latch is reset by the low voltage on the Soft-Ref pin. The reset fault latch resets the delay latch and Soft-Ref charges via the 0.5mA current source. The fault pin is input to a high speed comparator with a threshold of 3V. In the event of a detected fault, the fault latch is set and the outputs are driven low. If Soft-Ref is above 4V, the delay latch is set. Restart delay is timed as Soft-Ref is discharged by 20µA. When Soft-Ref is fully discharged, the fault latch is reset if the fault input signal is low. The Fault pin can be used as a system shutdown pin.

If a fault is detected during soft-start, the fault latch is set and the outputs are driven low. The delay latch will remain reset until Soft-Ref charges to 4V. This sets the delay latch, and restart delay is timed. Note that restart delay for a single fault event is longer than for recurring faults since Soft-Ref must be discharged from 5V instead of 4V.

The restart delay to soft-start time ratio is 24:1 for a fault occurring during normal operation and 19:1 for faults occurring during soft-start. Shorter ratios can be programmed down to a limit of approximately 3:1 by the addition of a  $20k\Omega$  or larger resistor from Soft-Ref to ground.

A  $100k\Omega$  resistor from Soft-Ref to 5V will have the effect of permanent shut down after a fault since the internal  $20\mu$ A current source can't pull Soft-Ref low. This feature can be used to require recycling Vcc after a fault. Care must be taken to insure Soft-Ref is indeed low at start up, or the fault latch will never be reset.

## APPLICATION INFORMATION

Figure 1. UVLO, 5V, fault and soft-ref.

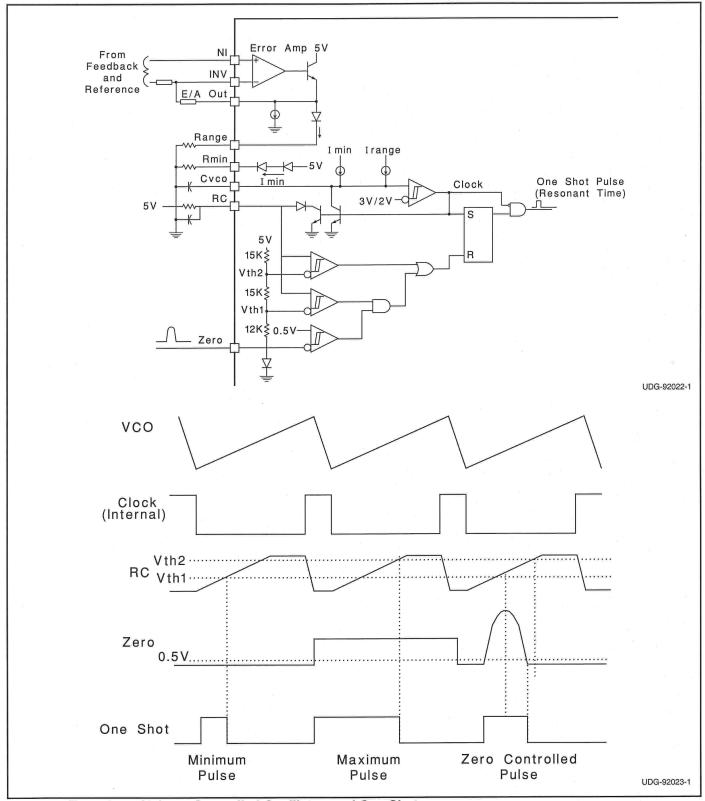

Figure 2. Error Amp, Voltage Controlled Oscillator, and One Shot

#### APPLICATION INFORMATION

Minimum oscillator frequency is set by Rmin and Cvco. The minimum frequency is approximately given by the equation:

$$F_{MIN} \cong \frac{3.6}{R_{MIN} \bullet C_{VCO}}$$

Maximum oscillator frequency is set by Rmin, Range & Cvco. The maximum frequency is approximately given by the equation:

$$F_{MAX} \cong \frac{3.6}{(R_{MIN} / / Range) \cdot C_{VCO}}$$

The Error Amplifier directly controls the oscillator frequency. E/A output low corresponds to minimum frequency and output high corresponds to maximum frequency. At the end of each oscillator cycle, the RC pin is discharged to one diode drop above ground. At the beginning of the oscillator cycle, V(RC) is less than Vth1 and so the output of the zero detect comparator is ignored. After V(RC) exceeds Vth1, the one shot pulse will be terminated as soon as the zero pin falls below 0.5V or V(RC) exceeds Vth2. The minimum one shot pulse width is approximately given by the equation:

The maximum pulse width is approximately given by:

Tpw(max) 1.2 R C.

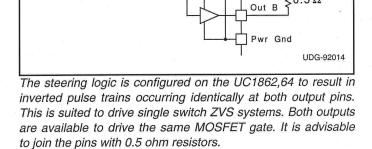

UCx862, 64

One Shot-

Fault Latch-UVLO- VCC

Out A

{0.5 Ω | → Output {0.5 Ω

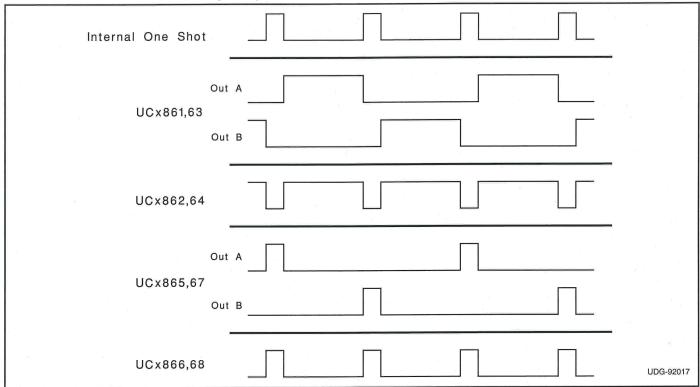

## STEERING LOGIC

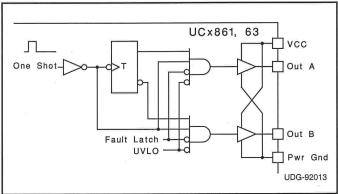

The steering logic is configured on the UC1861,63 to result in dual non-overlapping square waves at outputs A & B. This is suited to drive dual switch ZVS systems.

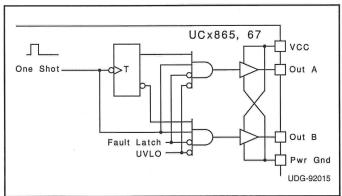

The steering logic is configured on the UC1865,67 to result in alternating pulse trains at outputs A & B. This is suited to drive dual switch ZCS systems.

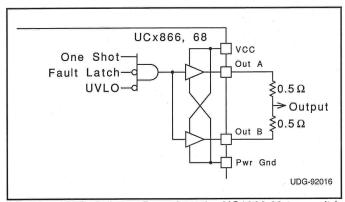

The steering logic is configured on the UC1866,68 to result in non-inverted pulse trains occurring identically at both output pins. This is suited to drive single switch ZCS systems. Both outputs are available to drive the same MOSFET gate. It is advisable to join the pins with 0.5 ohm resistors.

## **APPLICATION INFORMATION (cont.)**

Figure 3. Current waveforms.

29-May-2024 www.ti.com

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C)                  | Device Marking<br>(4/5)                 | Samples                                |  |

|------------------|--------|--------------|--------------------|------|----------------|---------------------|-------------------------------|---------------------|-------------------------------|-----------------------------------------|----------------------------------------|--|

| 5962-9203103Q2A  | ACTIVE | LCCC         | FK                 | 20   | 55             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | -55 to 125                    | 5962-<br>9203103Q2A<br>UC1863L/<br>883B | Samples                                |  |

| 5962-9203103QEA  | ACTIVE | CDIP         | J                  | 16   | 25             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | -55 to 125                    | 5962-9203103QE<br>A<br>UC1863J/883B     | Samples                                |  |

| 5962-9203103V2A  | ACTIVE | LCCC         | FK                 | 20   | 55             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | N / A for Pkg Type -55 to 125 |                                         | 5962-<br>9203103V2A<br>UC1863L<br>QMLV |  |

| UC1863J          | ACTIVE | CDIP         | J                  | 16   | 25             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | -55 to 125                    | UC1863J                                 | Samples                                |  |

| UC1863J883B      | ACTIVE | CDIP         | J                  | 16   | 25             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | -55 to 125                    | 5962-9203103QE<br>A<br>UC1863J/883B     | Samples                                |  |

| UC1863L          | ACTIVE | LCCC         | FK                 | 20   | 55             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | -55 to 125                    | UC1863L                                 | Samples                                |  |

| UC1863L883B      | ACTIVE | LCCC         | FK                 | 20   | 55             | Non-RoHS<br>& Green | SNPB                          | N / A for Pkg Type  | -55 to 125                    | 5962-<br>9203103Q2A<br>UC1863L/<br>883B | Samples                                |  |

| UC2861DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | RoHS & Green        | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85                     | UC2861DW                                | Samples                                |  |

| UC2863DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | RoHS & Green        | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85                     | UC2863DW                                | Samples                                |  |

| UC2864DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | RoHS & Green        | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85                     | UC2864DW                                | Samples                                |  |

| UC3861DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | RoHS & Green        | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70                       | UC3861DW                                | Samples                                |  |

| UC3861DWG4       | ACTIVE | SOIC         | DW                 | 16   | 40             | RoHS & Green        | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70                       | UC3861DW                                | Samples                                |  |

| UC3861N          | ACTIVE | PDIP         | N                  | 16   | 25             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type  | 0 to 70                       | UC3861N                                 | Samples                                |  |

| UC3863DW         | ACTIVE | SOIC         | DW                 | 16   | 40             | RoHS & Green        | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70                       | UC3863DW                                | Samples                                |  |

www.ti.com 29-May-2024

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| UC3865DW         | ACTIVE     | SOIC         | DW                 | 16   | 40             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3865DW                | Samples |

| UC3867DW         | ACTIVE     | SOIC         | DW                 | 16   | 40             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3867DW                | Samples |

| UC3867DWTR       | ACTIVE     | SOIC         | DW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3867DW                | Samples |

| UC3867N          | ACTIVE     | PDIP         | N                  | 16   | 25             | RoHS & Green | NIPDAU                        | N / A for Pkg Type  | 0 to 70      | UC3867N                 | Samples |

| UC3867NG4        | ACTIVE     | PDIP         | N                  | 16   | 25             | RoHS & Green | NIPDAU                        | N / A for Pkg Type  | 0 to 70      | UC3867N                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

## **PACKAGE OPTION ADDENDUM**

www.ti.com 29-May-2024

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC1863, UC1863-SP, UC3863:

• Catalog : UC3863, UC1863

Military: UC1863

■ Space : UC1863-SP

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Military QML certified for Military and Defense Applications

- Space Radiation tolerant, ceramic packaging and qualified for use in Space-based application

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Dec-2023

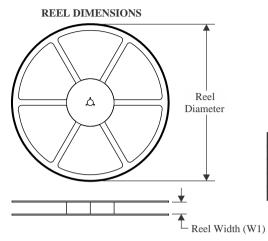

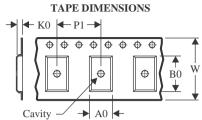

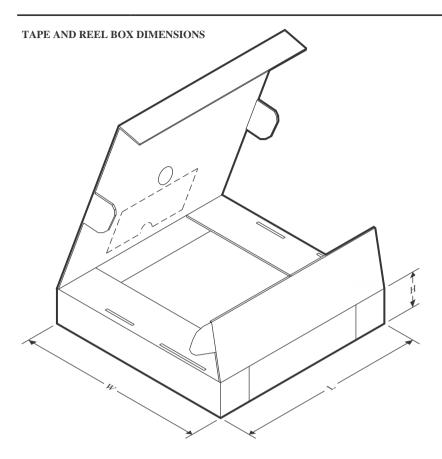

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

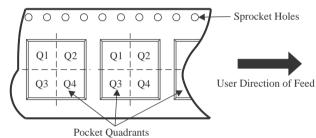

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UC3867DWTR | SOIC            | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

PACKAGE MATERIALS INFORMATION

www.ti.com 10-Dec-2023

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC3867DWTR | SOIC         | DW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

www.ti.com 10-Dec-2023

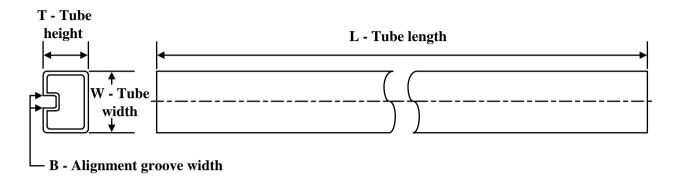

## **TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| 5962-9203103Q2A | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| 5962-9203103V2A | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| UC1863L         | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| UC1863L883B     | FK           | LCCC         | 20   | 55  | 506.98 | 12.06  | 2030   | NA     |

| UC2861DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC2863DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC2864DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC3861DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC3861DWG4      | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC3861N         | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| UC3863DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC3865DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC3867DW        | DW           | SOIC         | 16   | 40  | 507    | 12.83  | 5080   | 6.6    |

| UC3867N         | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| UC3867NG4       | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated