# UCG2882x Self-Biased High Frequency QR Flyback Converter With Integrated GaN

## 1 Features

- Integrated 750V GaN with 170mΩ  $R_{ds(on)}$  option

- Dynamic QR/DCM/CCM modes of operation

- High power density: up to 500kHz switching frequency

- Enable low BoM cost by integration

- Remove auxiliary winding with self bias

- Integrated input and output voltage sensing

- Integrated current sense

- Integrated HV start-up

- Integrated X-cap discharge

- High efficiency and low EMI performance

- Ultra-low standby power: <30mW

- Frequency foldback and burst mode

- Valley locking

- Frequency dithering

- Switching slew rate control

- Comprehensive protection features

- Overtemperature protection

- Overvoltage protection

- Short-circuit protection

- Cycle-by-cycle current limit

- Two-level over power protection with LPS

- Brownin and brownout protection

- Open feedback protection

- Flexible configurability through external resistors

- X-cap discharge and CCM mode disable

- Selectable switching slew rate

- Multiple clamping frequency settings

- Fault latch or auto-restart

- Maximum and minimum peak current ratio

- Dithering amplitude

## 2 Applications

- USB-PD adapter for portable electronics

- USB wall outlets and docking stations

- Industrial DIN rail power supplies

- Server aux power supplies

## 3 Description

UCG2882x is a high frequency, quasi-resonant flyback converter with a built-in 750V GaN high electron mobility transistor (HEMT) with as low as 170mΩ  $R_{ds(on)}$  for AC to DC power conversion. The UCG2882x is designed for high power density applications, such as cell phone fast chargers and notebook adapters. The key feature of this device is the self-bias and auxless sensing scheme which eliminates the need of the auxiliary winding and simplifies the system design with higher efficiency.

The UCG2882x also features intelligent mode transition (CCM/QR/DCM) to enable high efficiency across wide power range and <30mW standby power consumption. In addition, UCG2882x includes a full list of protections, such as brownin and brownout protection, SCP, OVP, OPP, LPS, OFB and OTP. The cycle-by-cycle current limit allows for fast response to the fault conditions to safeguard the system and improve the reliability. In a small 5 × 5mm package, the UCG2882x has dedicated configuration pins to offer more flexibility. Only resistors are needed to tune certain parameters for each system, enabling a platform design with a single device.

## Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| UCG28824    | REZ (QFN, 12)          | 5mm × 5mm                   |

| UCG28826    |                        |                             |

| UCG28828    |                        |                             |

(1) For all available packages, see [Section 11](#) at the end of the data sheet.

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

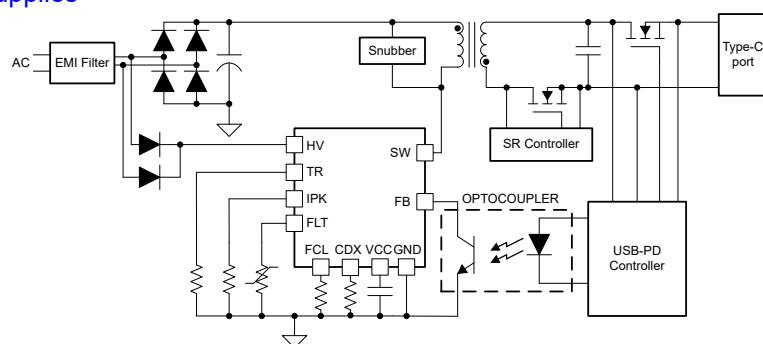

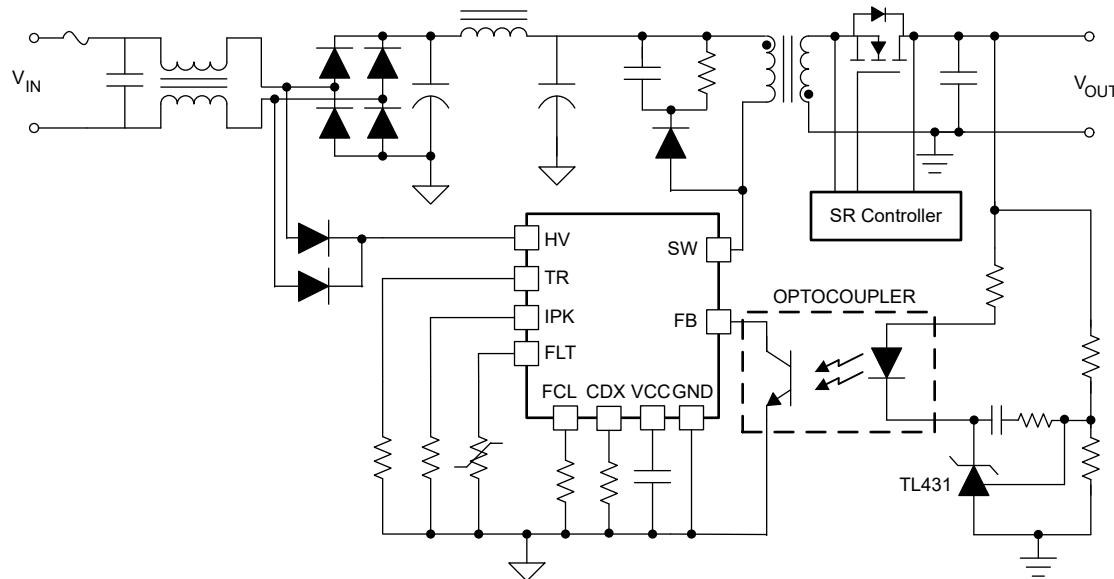

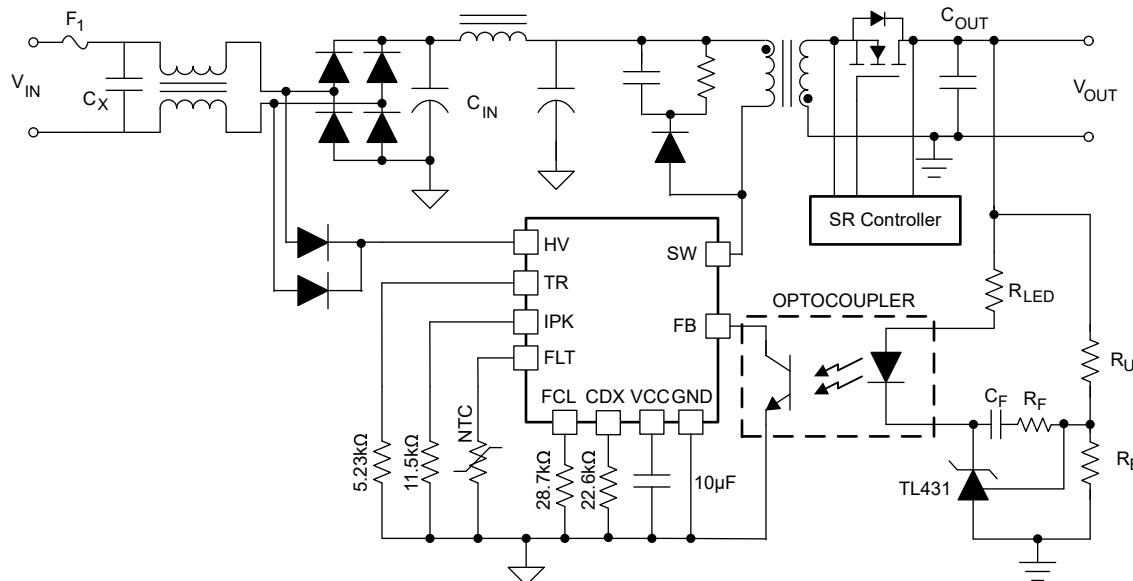

**Simplified Schematic of AC/DC Flyback Converter Using UCG2882x**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                |           |                                                          |           |

|------------------------------------------------|-----------|----------------------------------------------------------|-----------|

| <b>1 Features</b> .....                        | <b>1</b>  | 7.4 Feature Description.....                             | <b>18</b> |

| <b>2 Applications</b> .....                    | <b>1</b>  | <b>8 Application and Implementation</b> .....            | <b>30</b> |

| <b>3 Description</b> .....                     | <b>1</b>  | 8.1 Application Information.....                         | <b>30</b> |

| <b>4 Device Comparison</b> .....               | <b>3</b>  | 8.2 Typical Application.....                             | <b>30</b> |

| <b>5 Pin Configuration and Functions</b> ..... | <b>4</b>  | 8.3 Power Supply Recommendations.....                    | <b>33</b> |

| <b>6 Specifications</b> .....                  | <b>5</b>  | 8.4 Layout.....                                          | <b>34</b> |

| 6.1 Absolute Maximum Ratings.....              | 5         | <b>9 Device and Documentation Support</b> .....          | <b>36</b> |

| 6.2 ESD Ratings.....                           | 5         | 9.1 Receiving Notification of Documentation Updates..... | 36        |

| 6.3 Recommended Operating Conditions.....      | 5         | 9.2 Support Resources.....                               | 36        |

| 6.4 Thermal Information.....                   | 6         | 9.3 Trademarks.....                                      | 36        |

| 6.5 Electrical Characteristics.....            | 7         | 9.4 Electrostatic Discharge Caution.....                 | 36        |

| 6.6 Typical Characteristics.....               | 10        | 9.5 Glossary.....                                        | 36        |

| <b>7 Detailed Description</b> .....            | <b>12</b> | <b>10 Revision History</b> .....                         | <b>36</b> |

| 7.1 Overview.....                              | 12        | <b>11 Mechanical, Packaging, and Orderable</b>           |           |

| 7.2 Functional Block Diagram.....              | 13        | <b>Information</b> .....                                 | <b>36</b> |

| 7.3 Detailed Pin Descriptions.....             | 13        |                                                          |           |

## 4 Device Comparison

**Table 4-1. Related Products**

| DEVICE NAME | DESCRIPTION                                                                                 |

|-------------|---------------------------------------------------------------------------------------------|

| UCG28824    | Self-biased QR flyback converter with 750V, 270mΩ GaN FET for 45W designs                   |

| UCG28826    | Self-biased QR flyback converter with 750V, 170mΩ GaN FET for 65W designs                   |

| UCG28828    | Self-biased QR flyback converter with 750V, 170mΩ GaN FET for 120W designs (with PFC input) |

| UCC28881    | 4.5W, 700V AC/DC flyback converter with integrated FET                                      |

| UCC28910    | 6W and 7.5W, 700V primary side regulated flyback converter                                  |

**Table 4-2. UCG2882x Device Options**

|                         | UCG28826-1  | UCG28826-3  | UCG28826-4  | UCG28826-5  | UCG28828-1  | UCG28828-2 <sup>(1)</sup> | UCG28824-1  |

|-------------------------|-------------|-------------|-------------|-------------|-------------|---------------------------|-------------|

| Power Level             | 65W         | 65W         | 65W         | 65W         | 120W        | 120W                      | 45W         |

| Rdson                   | 170mΩ       | 170mΩ       | 170mΩ       | 170mΩ       | 170mΩ       | 170mΩ                     | 270mΩ       |

| OPPL                    | 100W        | 100W        | 80W         | Disabled    | Disabled    | Disabled                  | 69W         |

| OPPH                    | 140W        | 140W        | 140W        | 140W        | 190W        | 190W                      | 97W         |

| LPS                     | 7.5A        | 7.5A        | 7.5A        | Disabled    | Disabled    | Disabled                  | 5.2A        |

| Brownout/in             | 80VAC/70VAC | 80VAC/70VAC | 80VAC/70VAC | 67VAC/57VAC | 80VAC/70VAC | 80VAC/70VAC               | 80VAC/70VAC |

| Output OVP              | 25V         | 25V         | 16V         | 25V         | 25V         | 25V                       | 25V         |

| Input OVP               | No          | No          | No          | No          | No          | 315VAC                    | No          |

| High Line CCM           | No          | No          | No          | No          | No          | Yes                       | No          |

| EMI Dithering Frequency | 6.25kHz     | 390Hz       | 6.25kHz     | 6.25kHz     | 6.25kHz     | 6.25kHz                   | 6.25kHz     |

(1) Contact TI before ordering

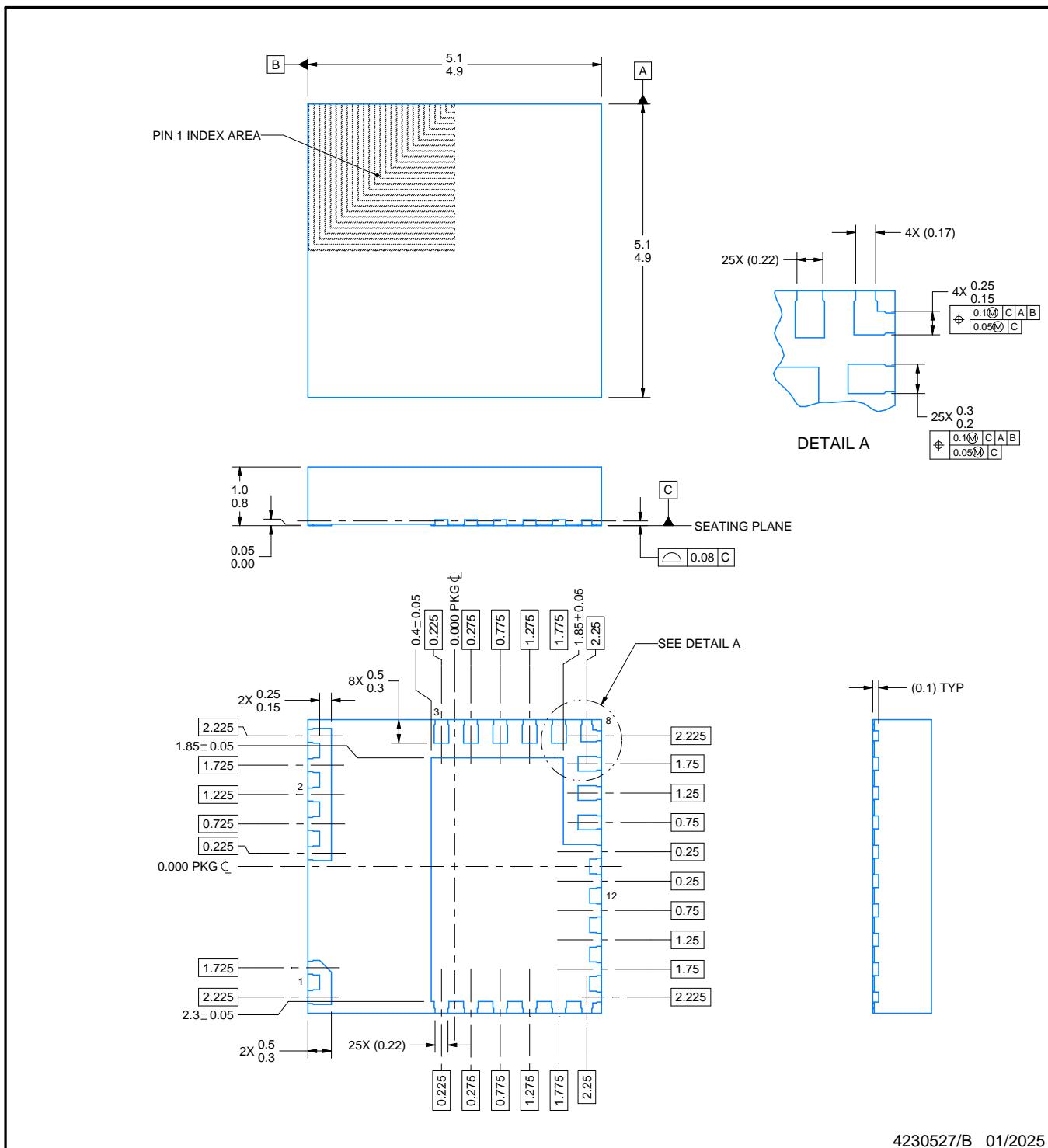

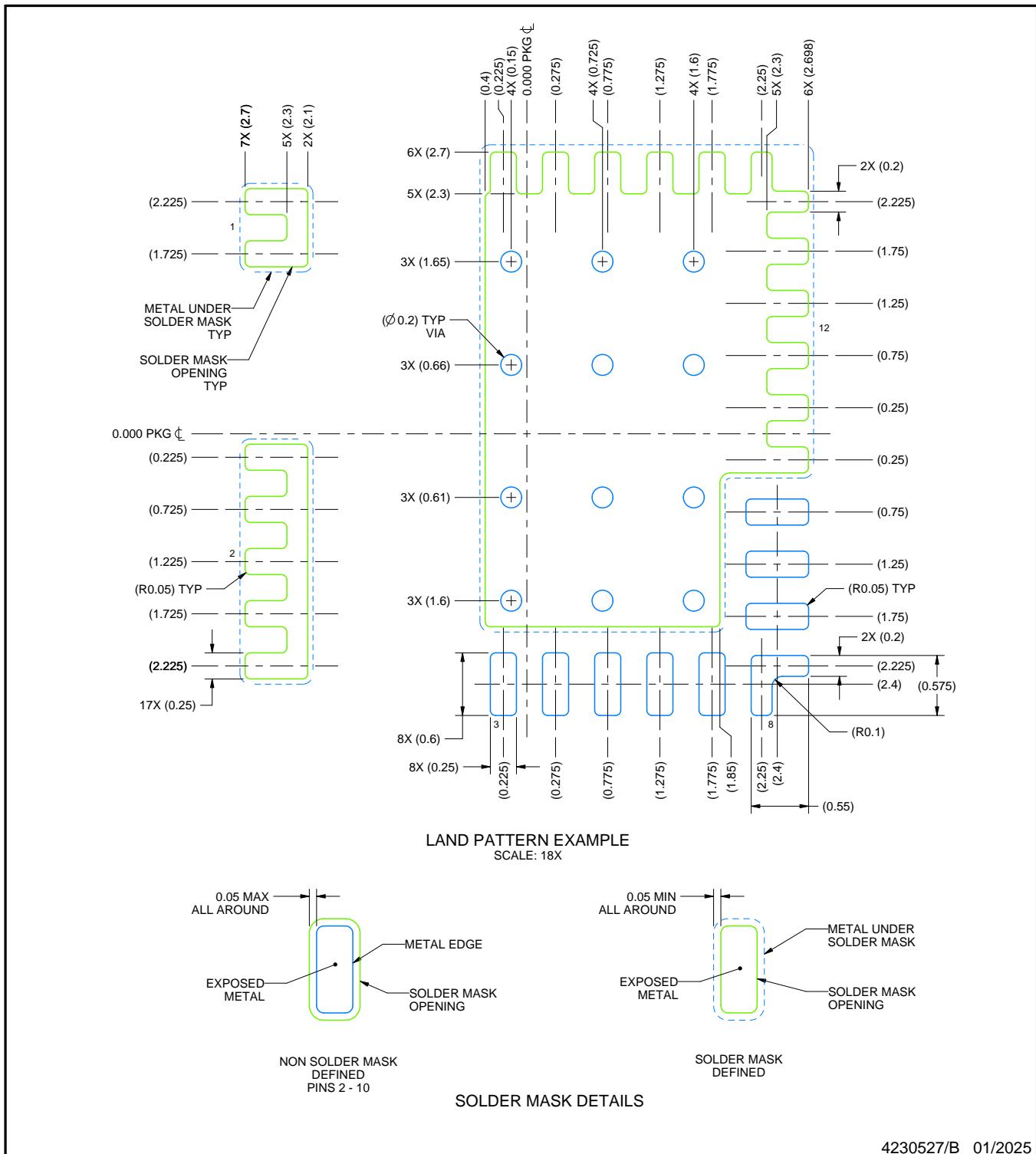

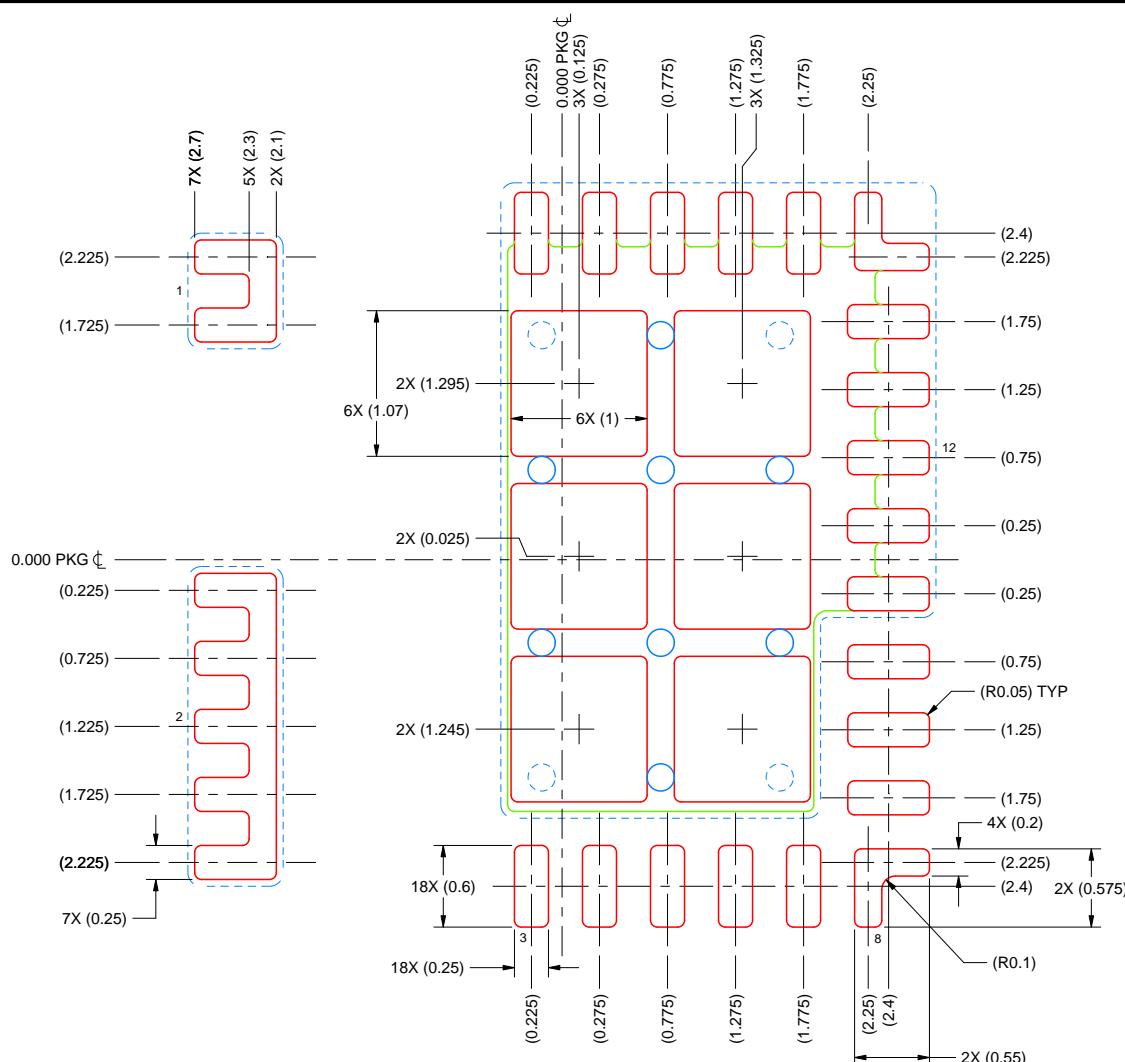

## 5 Pin Configuration and Functions

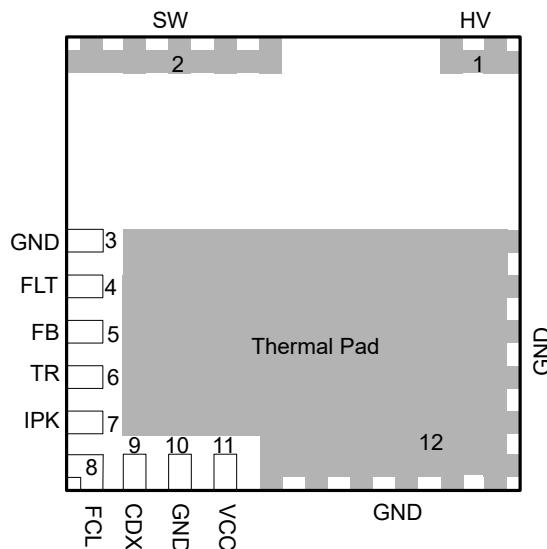

**Figure 5-1. UCG2882x 5mm × 5mm Package, 12-Pin QFN (Top View)**

**Table 5-1. Pin Functions**

| PIN  |       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                         |

|------|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO.   |                     |                                                                                                                                                                                                                                     |

| CDX  | 9     | I                   | Multifunction pin to enable and disable CCM mode, switching slew rate setting and X-cap discharge enable and disable.                                                                                                               |

| FB   | 5     | I                   | Feedback signal. Connect this pin to the collector of an optocoupler.                                                                                                                                                               |

| FCL  | 8     | I                   | Switching frequency clamp and fault behavior setting.                                                                                                                                                                               |

| FLT  | 4     | O                   | Fault pin for external overtemperature protection. Connect an NTC from this pin to GND.                                                                                                                                             |

| GND  | 3, 10 | G                   | Signal ground. Internally connected to power ground.                                                                                                                                                                                |

| GND  | 12    | G                   | Power ground. Connect to negative terminal of input bulk capacitor. Add a ground plane with sufficient copper area below the thermal pad for efficient heat conduction to the PCB.                                                  |

| HV   | 1     | P                   | HV start-up, AC line input presence detection and X-cap discharge.                                                                                                                                                                  |

| IPK  | 7     | I                   | Peak current and frequency dither setting pin. A resistor from this pin to GND sets the maximum and minimum primary-side peak current and dithering depth.                                                                          |

| SW   | 2     | P                   | Drain pin of integrated high-voltage GaN HEMT. This is also the sensing pin for valley switching and protections.                                                                                                                   |

| TR   | 6     | I                   | Turns ratio setting. A resistor from this pin to GND sets the transformer turns ratio Np/Ns.                                                                                                                                        |

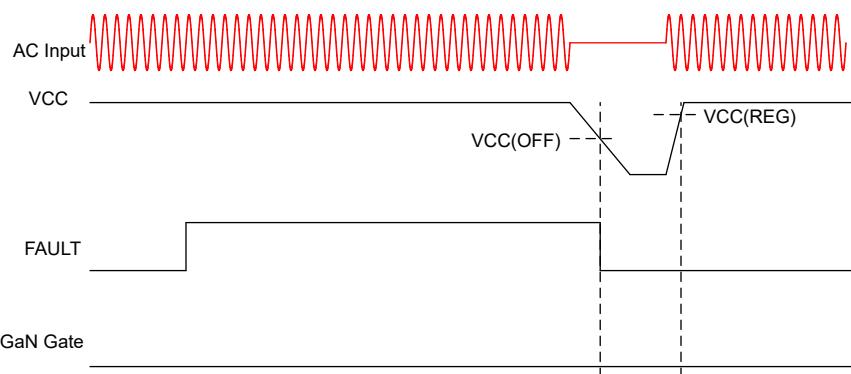

| VCC  | 11    | P                   | IC bias supply. Connect an external capacitor (at least 10V rated) from this pin to GND. Verify that the capacitor value is from 15µF to 47µF. The capacitor value is determined by the hold up time for missing input line cycles. |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                   |                                                                                        |                            | MIN                | MAX | UNIT |

|-----------------------------------|----------------------------------------------------------------------------------------|----------------------------|--------------------|-----|------|

| $V_{HV(\text{surge})}$            | GaN HEMT drain-source voltage, surge condition                                         |                            | 800                |     | V    |

| $V_{SW(\text{tr})(\text{surge})}$ | GaN power HEMT transient drain-source voltage, surge condition <sup>(2) (4)</sup>      |                            | 800                |     | V    |

| $V_{SW(\text{tr})}$               | GaN power HEMT drain-source transient voltage, each switching cycle <sup>(3) (4)</sup> |                            | 750                |     | V    |

| $V_{SW}$                          | GaN power HEMT continuous drain-source voltage, FET off                                |                            | 700                |     | V    |

| $I_{DS}$                          | GaN power HEMT continuous current, FET on                                              |                            | Internally limited |     | A    |

|                                   | Pin voltage                                                                            | FLT, TR, IPK, FCL, CDX, FB | -0.3               | 5.5 | V    |

|                                   |                                                                                        | VCC                        | -0.3               | 6.5 |      |

| $T_J$                             | Junction temperature                                                                   |                            | -40                | 150 | °C   |

| $T_{\text{stg}}$                  | Storage temperature                                                                    |                            | -65                | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) One time event with duration limited to <100μs

(3) Damped to  $V_{SW(\text{Plateau})}$ =600V in <900ns

(4) See [GaN HEMT Switching Capability](#) for more information on the GaN power FET switching capability.

### 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| $V_{(\text{ESD})}$ | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| $V_{(\text{ESD})}$ | Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±750  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|           |                                          | MIN                | NOM | MAX | UNIT |

|-----------|------------------------------------------|--------------------|-----|-----|------|

| $I_{SW}$  | SW pin current, continuous               | Internally limited |     |     | A    |

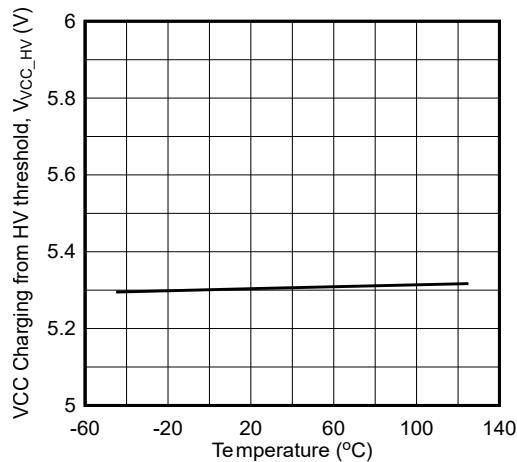

| $V_{VCC}$ | VCC supply, self-regulating              | 5.2                | 6   |     | V    |

| $C_{VCC}$ | Capacitance on VCC pin                   | 15                 | 47  |     | μF   |

| $C_{X2}$  | X2 capacitance                           | 0.1                | 1   |     | μF   |

| $L_{MAG}$ | Primary magnetising inductance, UCG28824 | 190                | 550 |     | μH   |

| $L_{MAG}$ | Primary magnetising inductance, UCG28826 | 130                | 400 |     | μH   |

| $L_{MAG}$ | Primary magnetising inductance, UCG28828 | 130                | 400 |     | μH   |

| $L_{LK}$  | Primary winding leakage inductance       |                    | 3   |     | %    |

| $C_{SW}$  | SW pin capacitance (GaN HEMT excluded)   |                    | 300 |     | pF   |

| $C_{HV}$  | HV pin parasitic capacitance             | 50                 | 100 |     | pF   |

| $T_A$     | Ambient temperature                      | -40                | 105 |     | °C   |

| $T_J$     | Junction temperature                     | -40                | 125 |     | °C   |

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | UCG28826  | UNIT |

|-------------------------------|----------------------------------------------|-----------|------|

|                               |                                              | REZ (QFN) |      |

|                               |                                              | 12 PINS   |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 28.5      | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 28        | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 5.7       | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 2         | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 5.6       | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 1.6       | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                   | TEST CONDITIONS                               | MIN                                                                                  | TYP  | MAX  | UNIT             |    |

|-----------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|------|------|------------------|----|

| <b>BIAS SUPPLY</b>          |                                               |                                                                                      |      |      |                  |    |

| $V_{VCCSHORT}$              | Threshold for reduced VCC startup current     | 0.65                                                                                 | 0.9  | 1.2  | V                |    |

| $I_{HVLO}$                  | Reduced HV startup current                    | Before VCC reaches $V_{VCCSHORT}$                                                    | 0.55 | 1    | 1.6              | mA |

| $I_{HVHI}$                  | Full HV startup current                       | After VCC exceeds $V_{VCCSHORT}$                                                     | 2.2  | 4    | 5.65             | mA |

| $V_{VCC(OFF)}$              | VCC under voltage lock out threshold          | Tracking with variation in other thresholds                                          | 4.9  | 5.1  | 5.3              | V  |

| $V_{VCC(REG)}$              | VCC regulation voltage and start-up threshold | Tracking with variation in other thresholds                                          | 5.6  | 5.8  | 6                | V  |

| $V_{VCC(CHG)}$              | VCC charging trigger threshold                | Trigger VCC charging to $V_{VCC(REG)}$ , Tracking with variation in other thresholds | 5.4  | 5.6  | 5.8              | V  |

| $I_{VCC}$                   | Operating supply current                      | No switching                                                                         | 700  |      | $\mu$ A          |    |

| $I_{VCCSLEEP}$              | Supply current in burst mode                  | No switching                                                                         | 260  | 310  | $\mu$ A          |    |

| $I_{VCCFAULT}$              | Supply current when a protection is triggered |                                                                                      | 260  |      | $\mu$ A          |    |

| <b>GAN POWER TRANSISTOR</b> |                                               |                                                                                      |      |      |                  |    |

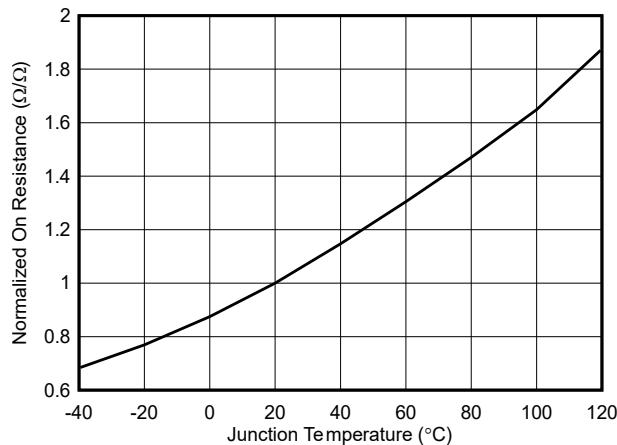

| $R_{DSON}$                  | Drain-source on-resistance                    | $T_J = 25^\circ\text{C}$ , UCG28824                                                  | 270  | 350  | $\text{m}\Omega$ |    |

| $R_{DSON}$                  | Drain-source on-resistance                    | $T_J = 25^\circ\text{C}$ , UCG28826, UCG28828                                        | 170  | 220  | $\text{m}\Omega$ |    |

| $C_{OSS}$                   | Output capacitance                            | $V_{SW} = 400\text{V}$ , UCG28824                                                    | 28   |      | $\text{pF}$      |    |

| $C_{OSS}$                   | Output capacitance                            | $V_{SW} = 400\text{V}$ , UCG28826, UCG28828                                          | 40   |      | $\text{pF}$      |    |

| <b>GAN GATE DRIVER</b>      |                                               |                                                                                      |      |      |                  |    |

|                             | Turn-on dV/dt                                 | For SW node, $V_{DS} = 325\text{V}$ , Option 1                                       | 10   |      | V/ns             |    |

|                             | Turn-on dV/dt                                 | For SW node, $V_{DS} = 325\text{V}$ , Option 2                                       | 7    |      | V/ns             |    |

|                             | Turn-on dV/dt                                 | For SW node, $V_{DS} = 325\text{V}$ , Option 3                                       | 5    |      | V/ns             |    |

| <b>PEAK CURRENT CONTROL</b> |                                               |                                                                                      |      |      |                  |    |

| $I_{PKMAX}$                 | Maximum peak current, UCG28824                | Option 1                                                                             | 1.9  | 2.05 | A                |    |

|                             |                                               | Option 2                                                                             | 2.1  | 2.25 |                  |    |

|                             |                                               | Option 3                                                                             | 2.4  | 2.55 |                  |    |

| $I_{PKMAX}$                 | Maximum peak current, UCG28826, UCG28828      | Option 1                                                                             | 2.65 | 2.8  | A                |    |

|                             |                                               | Option 2                                                                             | 2.95 | 3.1  |                  |    |

|                             |                                               | Option 3                                                                             | 3.35 | 3.5  |                  |    |

| $I_{PKMAX}/I_{PKMIN}$       | Maximum to minimum peak current ratio         | Option 1                                                                             | 4    |      |                  |    |

|                             |                                               | Option 2                                                                             | 3    |      |                  |    |

| $T_{SS}$                    | Soft start time                               |                                                                                      | 4    |      | ms               |    |

| <b>FEEDBACK CONTROL</b>     |                                               |                                                                                      |      |      |                  |    |

| $R_{FB}$                    | FB pull-up resistor                           |                                                                                      | 60   |      | $\text{k}\Omega$ |    |

| $V_{FBOPEN}$                | Open FB Pin voltage                           |                                                                                      | 3.3  | 3.45 | V                |    |

| $V_{BST\_OFF}$              | Burst-off threshold                           | Turn-off switching                                                                   | 250  |      | $\text{mV}$      |    |

| $V_{BST\_ON}$               | Burst-on threshold                            | Resume burst switching                                                               | 300  |      | $\text{mV}$      |    |

| $V_{BST\_EX}$               | Burst mode exit threshold                     | Exit to frequency foldback                                                           | 500  |      | $\text{mV}$      |    |

| $f_{MIN,CLAMP}$             | Minimum frequency clamp                       | During normal operation                                                              | 23   | 25   | $\text{kHz}$     |    |

|                             |                                               | During soft start                                                                    | 10   |      |                  |    |

| $T_{SWMAX}$                 | Maximum time period                           |                                                                                      | 40   | 43   | $\mu\text{s}$    |    |

| $T_{ONMAX}$                 | Maximum on time                               |                                                                                      | 17   | 19   | $\mu\text{s}$    |    |

## 6.5 Electrical Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER            |                                                         | TEST CONDITIONS                                                                                    | MIN  | TYP   | MAX  | UNIT |

|----------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|-------|------|------|

| $f_{MAX,CLAMP}$      | Frequency clamp                                         | Option 1                                                                                           |      | 140   |      | kHz  |

|                      |                                                         | Option 2                                                                                           |      | 100   |      |      |

|                      |                                                         | Option 3                                                                                           |      | 250   |      |      |

|                      |                                                         | Option 4                                                                                           |      | 500   |      |      |

| $T_{DDCM}$           | DCM ring fixed timer                                    | From last seen DCM ring valley, UCG28826, UCG28828                                                 |      | 3.75  |      | μs   |

| <b>EMI DITHERING</b> |                                                         |                                                                                                    |      |       |      |      |

| $f_c$                | Carrier frequency                                       | UCG28826-3 only                                                                                    |      | 390   |      | Hz   |

| $f_c$                | Carrier frequency                                       |                                                                                                    |      | 6.25  |      | kHz  |

| $I_{Dither,max}$     | Carrier amplitude                                       | % of instantaneous peak currents, Option 1                                                         |      | ±6.25 |      | %    |

|                      |                                                         | % of instantaneous peak currents, Option 2                                                         |      | ±12.5 |      |      |

| <b>PROTECTIONS</b>   |                                                         |                                                                                                    |      |       |      |      |

| $V_{TH\_BI}$         | Brown-in threshold                                      | UCG28826-1 , UCG28826-3 , UCG28826-4 , UCG28828-1 , UCG28828-2 , UCG28824-1 DC level               | 106  | 112   | 118  | V    |

| $V_{TH\_BI}$         | Brown-in threshold                                      | UCG28826-5 DC level                                                                                | 89   | 94    | 99   | V    |

| $V_{TH\_BO}$         | Brown-out threshold                                     | UCG28826-1 , UCG28826-3 , UCG28826-4 , UCG28828-1 , UCG28828-2 , UCG28824-1 DC level               | 93   | 98    | 103  | V    |

| $V_{TH\_BO}$         | Brown-out threshold                                     | UCG28826-5 DC level                                                                                | 76   | 80    | 84   | V    |

| $T_{DBO}$            | Brown-out delay time                                    |                                                                                                    |      | 60    |      | ms   |

| $I_{FLT}$            | FLT pin source current                                  |                                                                                                    |      | 75    |      | μA   |

| $V_{TH\_OTP}$        | FLT threshold voltage                                   | Triggers external overtemperature fault                                                            | 0.58 | 0.6   | 0.62 | V    |

| $T_{IFLTTON}$        | $I_{FLT}$ on time                                       |                                                                                                    |      | 260   |      | μs   |

| $T_{IFLTperiod}$     | $I_{FLT}$ time period                                   |                                                                                                    |      | 10    |      | ms   |

| $N_{FLTTSD}$         | Number of external $I_{FLT}$ cycles                     | Before fault is triggered                                                                          |      | 3     |      |      |

| $R_{SW}$             | SW pin impedance                                        |                                                                                                    | 8.2  | 9.5   |      | MΩ   |

| $V_{OVP}$            | OVP detection threshold                                 | UCG28826-4<br>$V_{OUT}$ threshold                                                                  | 14.5 | 16    | 17.5 | V    |

| $V_{OVP}$            | OVP detection threshold                                 | UCG28826-1 , UCG28826-3 , UCG28826-5 , UCG28828-1 , UCG28828-2 , UCG28824-1<br>$V_{OUT}$ threshold | 23   | 25    | 27   | V    |

|                      | Internal overtemperature protection shut down threshold | Temperature increasing                                                                             |      | 150   |      | °C   |

|                      | Internal overtemperature protection hysteresis          | Temperature reducing                                                                               |      | 10    |      | °C   |

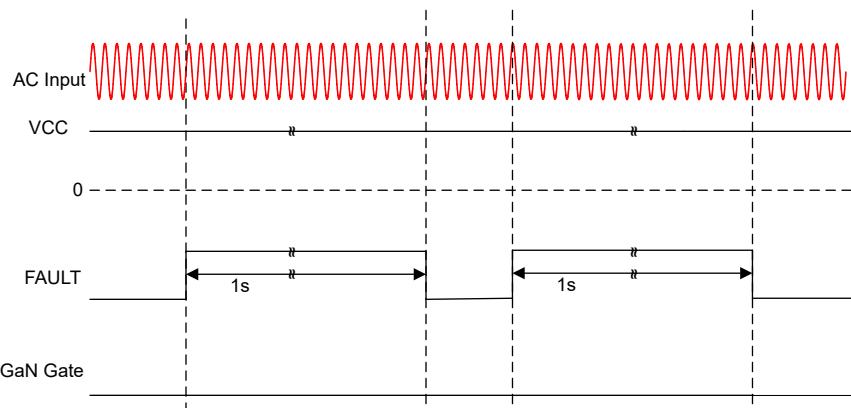

| $T_{RETRY}$          | Auto-retry time                                         |                                                                                                    |      | 1     |      | s    |

| $P_{OPPL}$           | Over power protection threshold, low                    | UCG28824-1, triggers after 4.2s                                                                    | 61   | 69    | 78   | W    |

| $P_{OPPL}$           | Over power protection threshold, low                    | UCG28826-1, UCG28826-3, triggers after 4.2s                                                        | 89   | 100   | 114  | W    |

| $P_{OPPL}$           | Over power protection threshold                         | UCG28826-4, triggers after 4.2s                                                                    | 71   | 80    | 92   | W    |

| $P_{OPPL}$           | Over power protection threshold, low                    | UCG28826-5 , UCG28828-1 , UCG28828-2<br>Disabled                                                   |      |       |      | W    |

| $P_{OPPH}$           | Over power protection threshold, high                   | UCG28824-1, triggers after 120ms                                                                   | 87   | 97.5  | 111  | W    |

| $P_{OPPH}$           | Over power protection threshold, high                   | UCG28826-1 , UCG28826-3 , UCG28826-4 , UCG28826-5<br>Triggers after 120ms                          | 125  | 140   | 160  | W    |

## 6.5 Electrical Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER          |                                       | TEST CONDITIONS                                                             | MIN | TYP | MAX  | UNIT |

|--------------------|---------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|------|

| P <sub>OPPH</sub>  | Over power protection threshold, high | UCG28828-1 , UCG28828-2<br>Triggers after 120ms                             | 169 | 190 | 216  | W    |

| I <sub>LPS</sub>   | LPS fault output current threshold    | UCG28824-1, input referred, triggers after 4.2s                             | 4.4 | 5.2 | 6    | A    |

| I <sub>LPS</sub>   | LPS fault output current threshold    | UCG28826-1 , UCG28826-3 , UCG28826-4<br>Input referred, triggers after 4.2s | 6.3 | 7.5 | 8.65 | A    |

| I <sub>LPS</sub>   | LPS fault output current threshold    | UCG28826-5 , UCG28828-1 , UCG28828-2<br>Disabled                            |     |     |      | A    |

| I <sub>SCP</sub>   | Short Circuit Protection              | Primary current threshold, UCG28824                                         |     | 3.1 |      | A    |

| I <sub>SCP</sub>   | Short Circuit Protection              | Primary current threshold, UCG28826 ,<br>UCG28828                           |     | 4.5 |      | A    |

|                    | Short Circuit Protection              | Number of cycles                                                            |     | 3   |      |      |

| t <sub>SCP</sub>   | Short-circuit response time           |                                                                             |     | 140 |      | ns   |

| V <sub>INOVF</sub> | Input OVP trigger threshold           | UCG28828-2, trigger protection and stop switching, AC input                 |     | 315 |      | V    |

### X CAP DISCHARGE

|                    |                                |                          |     |   |     |    |

|--------------------|--------------------------------|--------------------------|-----|---|-----|----|

| I <sub>ACDET</sub> | Line removal detection current | Current sink from HV pin | 1.5 | 2 | 2.5 | mA |

| I <sub>XDIS</sub>  | X-cap discharge Current        |                          | 3.8 | 5 | 6.2 | mA |

| T <sub>XDIS</sub>  | X-cap discharge Time           | C <sub>XCAP</sub> = 1μF  |     |   | 1   | s  |

## 6.6 Typical Characteristics

Figure 6-1. Normalized On-Resistance vs Junction Temperature

Figure 6-2. VCC Threshold for Charging From HV Pin vs Junction Temperature

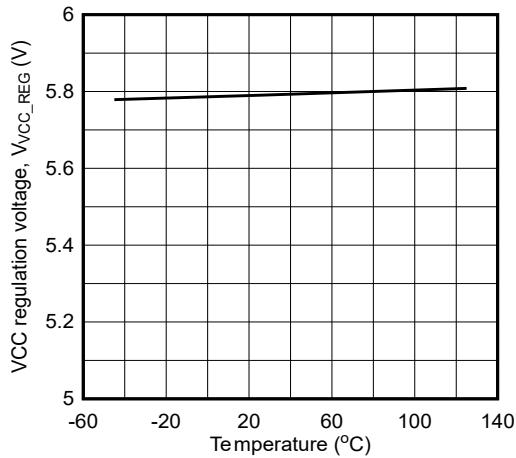

Figure 6-3. VCC Regulation Voltage vs Junction Temperature

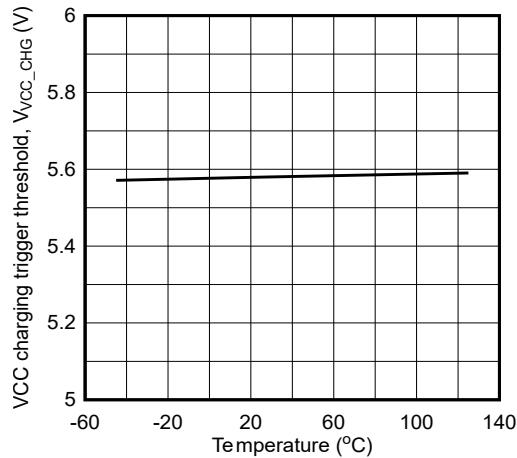

Figure 6-4. VCC Charging Trigger Voltage vs Junction Temperature

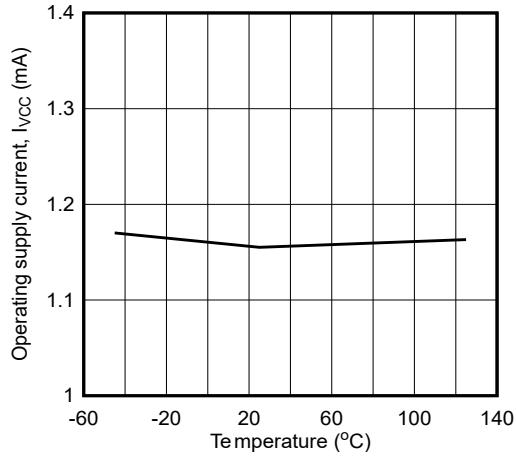

100KHz switching frequency

Figure 6-5. Operating Supply Current vs Junction Temperature

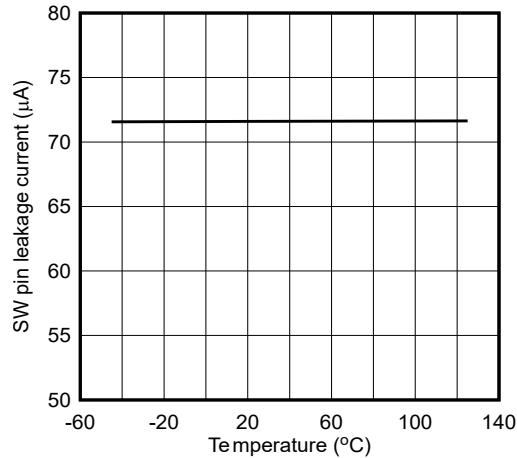

$V_{SW} = 650V$

Figure 6-6. SW Pin Leakage Current vs Junction Temperature

## 6.6 Typical Characteristics (continued)

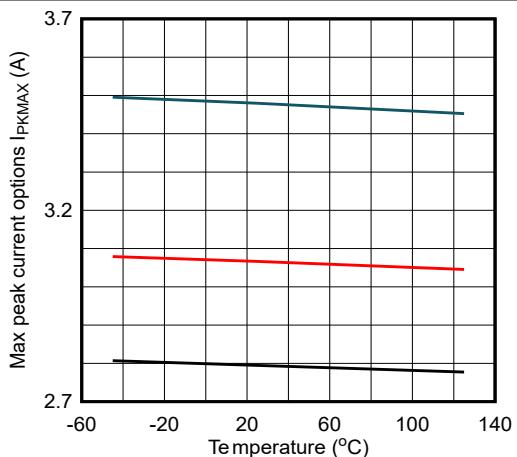

Peak current options centered around 2.8A, 3.1A, and 3.5A

**Figure 6-7. Maximum Primary Peak Current vs Junction Temperature**

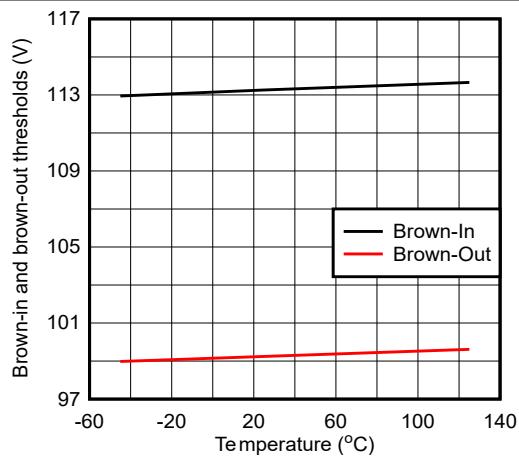

**Figure 6-8. Brownin and Brownout Thresholds vs Junction Temperature**

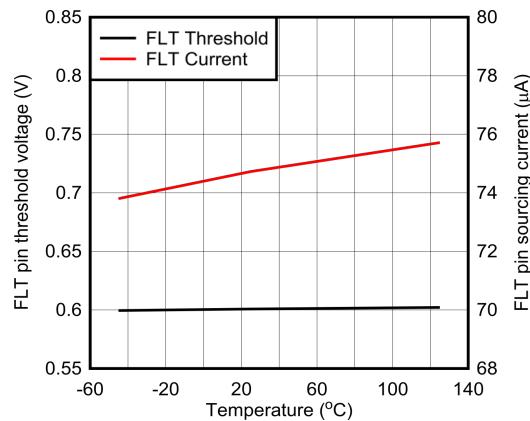

**Figure 6-9. FLT Pin Voltage and Current vs Junction Temperature**

## 7 Detailed Description

### 7.1 Overview

The UCG2882x is a high frequency, quasi-resonant (QR) AC/DC flyback converter with integrated 750V primary-side GaN high electron mobility transistor (HEMT), referred to as GaN HEMT, designed for use in AC-to-DC power supplies up to 120W. This device gives benefit of GaN integration to achieve high power density designs with high switching frequency up to 500kHz.

The UCG2882x features the industry's first auxless flyback architecture with self-bias to give a compact and low cost power supply design without the need for an auxiliary winding in the transformer. The self bias feature reduces losses to improve efficiency in wide output voltage applications like USB-PD chargers by eliminating the need for a low dropout regulator (LDO) and the associated losses to generate the device bias.

The UCG2882x supports continuous conduction mode (CCM) operation for up to 10msec for transient output power conditions of minimum 130W (two times the 65W nominal output power) in low-line input conditions without increase in transformer size, saving space and lowering cost. This device also includes frequency foldback and burst modes for higher efficiency operation during light load and no-load conditions, respectively. The X-cap discharge circuit discharges the X-capacitor in the input EMI filter to 0V in less than 1s to prevent the user from an electric shock at the time of unplugging the power supply from the wall socket, meeting different safety standard requirements.

The UCG2882x overcomes the system design limitations of integrated converters by offering resistor programmable options to the user for maximum flexibility to optimize performance at the desired operating point. The device also includes many built-in protections such as output over-voltage protection (OVP), short-circuit protection (SCP), two-level over power protection (OPPH and OPPL) and over-temperature protections (OTP) with auto-restart and latch response for a robust power supply design preventing any damage during such fault conditions.

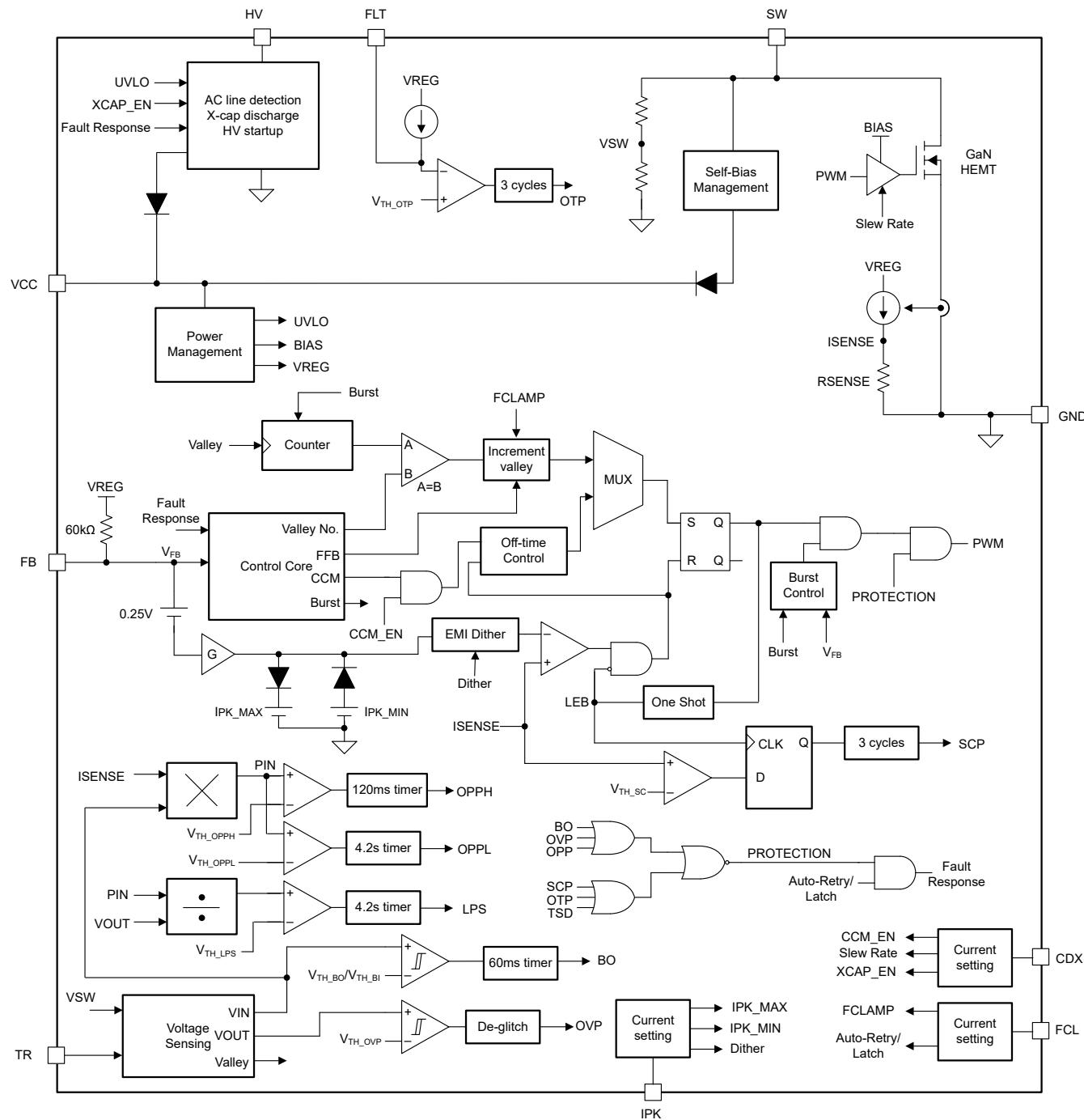

Figure 7-1. AC/DC Flyback Converter Schematic Using UCG2882x

## 7.2 Functional Block Diagram

## 7.3 Detailed Pin Descriptions

The UCG2882x is a QR flyback converter with integrated 750V GaN HEMT with self bias and auxless sensing. UCG2882x includes HV, SW and GND pins for interface with the flyback power stage components. Additionally, the device has a bias supply and a feedback pin for secondary side regulation. There are several programmable setting pins for the user to configure the device for an optimized power supply design. These programming pins require a resistor to ground and offer the flexibility to optimize various parameters during power stage design, enabling a platform design with a single device. The resistor values on the programming pins are detected at the

UVLO turn-on event and recorded inside the IC to improves the IC noise immunity. The resistor setting can not undergo dynamic change during operation.

### **7.3.1 HV - High Voltage Input**

Connect the high voltage (HV) pin to the two ends of the X-capacitor at the line input, through two diodes as shown in [Figure 7-1](#). HV pin charges the bias supply (VCC) capacitor at start-up. The HV pin also discharges the X-capacitor when the input line voltage is removed. When X-cap discharge is not needed, this connection is still required to minimize standby power consumption. When designing for DC input applications, the HV pin can be directly connected to the input bulk capacitor with corresponding resistor setting on the CDX pin to disable the X-cap discharge feature. The standby power consumption is slightly increased in DC input applications.

### **7.3.2 SW - Switch Node**

The SW pin is connected to the switch node on the primary side of the flyback converter. SW pin is the drain of the integrated 750V GaN HEMT. SW pin is also the sensing pin for valley switching and OVP, OPP and LPS protections. To keep the switching losses low, minimize the maximum total switch node capacitance at this pin. The capacitance at the SW pin includes the transformer parasitic capacitance, GaN HEMT drain-source capacitance, reflected capacitance from secondary side and any additional capacitance which are added to slow down the switch node turn-on and turn-off slew rates.

### **7.3.3 GND – Ground Return**

The GND pin is the external return pin, and provides a reference point for the internal circuitry and the gate drive of the device. This is the return pin for the power stage and must be connected to the negative terminal of the input bulk capacitors. Connect the thermal pad to the GND and verify sufficient copper area to dissipate the heat.

Connect pin 10 GND to pin 3 and 12 in the shortest trace possible. VCC bypassing capacitor must return to pin 10.

### **7.3.4 FLT - External Overtemperature Fault**

Connect a negative temperature coefficient (NTC) resistor from this pin to GND for monitoring the temperature of a critical point on the power supply external to the device, and trigger overtemperature protection to avoid damage to components. The device sources 75 $\mu$ A current into the NTC. As the NTC resistance reduces with increase in sensed temperature, the external over-temperature fault is triggered when the voltage on the FLT pin reduces to less than 0.6V. See [Section 7.4.10.5](#) for details of overtemperature protection. Pull the FLT pin low to trigger a fault implemented with external discrete circuits. Other than the FLT pin, the device also includes internal over temperature protection to prevent the device from exceeding the maximum allowable junction temperature.

### **7.3.5 FB – Feedback**

Connect the feedback (FB) pin to the collector of the optocoupler for output regulation. This pin has an internal 60 $k\Omega$  pull up for optocoupler bias. The instantaneous voltage on this pin determines the switching frequency, peak current and mode of operation (burst, foldback, valley switching or CCM) as per the control law in [Figure 7-3](#) to deliver the required output power. Connect a 100pF or 220pF capacitor from this pin to ground for high frequency noise filtering.

### 7.3.6 TR - Turns Ratio

Set the transformer turns ratio information with a resistor from this pin to GND as per values in [Table 7-1](#) or [Table 7-2](#). The turns ratio information is used for output voltage sensing. The resistor must be 1% accurate.

**Table 7-1. Turns Ratio Setting Resistor Values**

| TR Pin Resistor (kΩ) | Turns Ratio | V <sub>OUT</sub> OVP Threshold (V, Reflected to Primary) |

|----------------------|-------------|----------------------------------------------------------|

| 0                    | 7.875       | 196.9                                                    |

| 5.23                 | 6           | 150                                                      |

| 6.34                 | 6.125       | 153.1                                                    |

| 7.68                 | 6.25        | 156.2                                                    |

| 9.31                 | 6.375       | 159.4                                                    |

| 11.3                 | 6.5         | 162.5                                                    |

| 13.7                 | 6.625       | 165.6                                                    |

| 16.9                 | 6.75        | 168.7                                                    |

| 20.5                 | 6.875       | 171.9                                                    |

| 25.5                 | 7           | 175                                                      |

| 31.6                 | 7.125       | 178.1                                                    |

| 39.2                 | 7.25        | 181.2                                                    |

| 51.1                 | 7.375       | 184.4                                                    |

| 66.5                 | 7.5         | 187.5                                                    |

| 84.5                 | 7.625       | 190.6                                                    |

| 113                  | 7.75        | 193.7                                                    |

| 174                  | 7.875       | 196.9                                                    |

**Table 7-2. Turns Ratio Setting Resistor Values for UCG28826-4**

| TR Pin Resistor (kΩ) | Turns Ratio | V <sub>OUT</sub> OVP Threshold (V, Reflected to Primary) |

|----------------------|-------------|----------------------------------------------------------|

| 0                    | 7.875       | 126                                                      |

| 5.23                 | 6           | 96                                                       |

| 6.34                 | 6.125       | 98                                                       |

| 7.68                 | 6.25        | 100                                                      |

| 9.31                 | 6.375       | 102                                                      |

| 11.3                 | 6.5         | 104                                                      |

| 13.7                 | 6.625       | 106                                                      |

| 16.9                 | 6.75        | 108                                                      |

| 20.5                 | 6.875       | 110                                                      |

| 25.5                 | 7           | 112                                                      |

| 31.6                 | 7.125       | 114                                                      |

| 39.2                 | 7.25        | 116                                                      |

| 51.1                 | 7.375       | 118                                                      |

| 66.5                 | 7.5         | 120                                                      |

| 84.5                 | 7.625       | 122                                                      |

| 113                  | 7.75        | 124                                                      |

| 174                  | 7.875       | 126                                                      |

The TR pin sets up the transformer turns ratio assuming the design is used for USB-PD application. When used for other applications, the TR pin setting follows different principle. In reality, the TR pin is used to set the output OVP level. The UCG2882x uses the auxless sensing technology and can't directly tell the output voltage level. The TR pin sets the output OVP level based on the output voltage reflected to the primary side. Basically, in

those applications, choose the TR pin resistor value based on the  $V_{OUT}$  OVP Threshold (V, Reflected to Primary) column in [Table 7-1](#) and [Table 7-2](#). Refer to the [application note](#) for more details.

### 7.3.7 IPK - Peak Current and Dithering

This pin offers settings for peak current thresholds and dithering. Connect a resistor from this pin to GND as per values in [Table 7-3](#) to select the preferred option for the following specifications:

- Maximum peak current

- Ratio of maximum to minimum peak current

- EMI dithering depth

**Table 7-3. IPK Pin Programming Resistor Values**

| IPK Pin Resistor (kΩ) | Maximum Peak Current (A) | $I_{PK,MAX}/I_{PK,MIN}$ | EMI Dithering Depth (%) |

|-----------------------|--------------------------|-------------------------|-------------------------|

| 0                     | 3.1                      | 4                       | 6.25                    |

| 5.23                  | 2.8                      | 4                       | 12.5                    |

| 6.34                  | 3.1                      | 4                       | 12.5                    |

| 7.68                  | 3.5                      | 4                       | 12.5                    |

| 9.31                  | 2.8                      | 3                       | 12.5                    |

| 11.5                  | 3.1                      | 3                       | 12.5                    |

| 14.3                  | 3.5                      | 3                       | 12.5                    |

| 17.8                  | 2.8                      | 4                       | 6.25                    |

| 22.6                  | 3.1                      | 4                       | 6.25                    |

| 28.7                  | 3.5                      | 4                       | 6.25                    |

| 36.5                  | 2.8                      | 3                       | 6.25                    |

| 51.1                  | 3.1                      | 3                       | 6.25                    |

| 75                    | 3.5                      | 3                       | 6.25                    |

### 7.3.8 FCL - Frequency Clamp and Fault Response

Use the FCL pin to select the maximum switching frequency clamp value and fault response behavior. [Table 7-4](#) lists the resistor values to be used for the given operating conditions. The resistor must be 1% accurate.

**Table 7-4. FCL Pin Programming Resistor Values**

| FCL Pin Resistor (kΩ) | Frequency Clamp (kHz) | Fault Response                                |

|-----------------------|-----------------------|-----------------------------------------------|

| 0                     | 140                   | EXTOTP and OVP Latched, rest Auto retry       |

| 5.23                  | 140                   | All latched                                   |

| 6.34                  | 100                   | All latched                                   |

| 7.68                  | 250                   | All latched                                   |

| 9.31                  | 500                   | All latched                                   |

| 11.5                  | 140                   | All auto retry                                |

| 14.3                  | 100                   | All auto retry                                |

| 17.8                  | 250                   | All auto retry                                |

| 22.6                  | 500                   | All auto retry                                |

| 28.7                  | 140                   | EXTOTP fault and OVP latched, rest auto retry |

| 36.5                  | 100                   | EXTOTP fault and OVP latched, rest auto retry |

| 51.1                  | 250                   | EXTOTP fault and OVP latched, rest auto retry |

| 75                    | 500                   | EXTOTP fault and OVP latched, rest auto retry |

### 7.3.9 CDX - CCM, Drive Strength, and X-cap Discharge

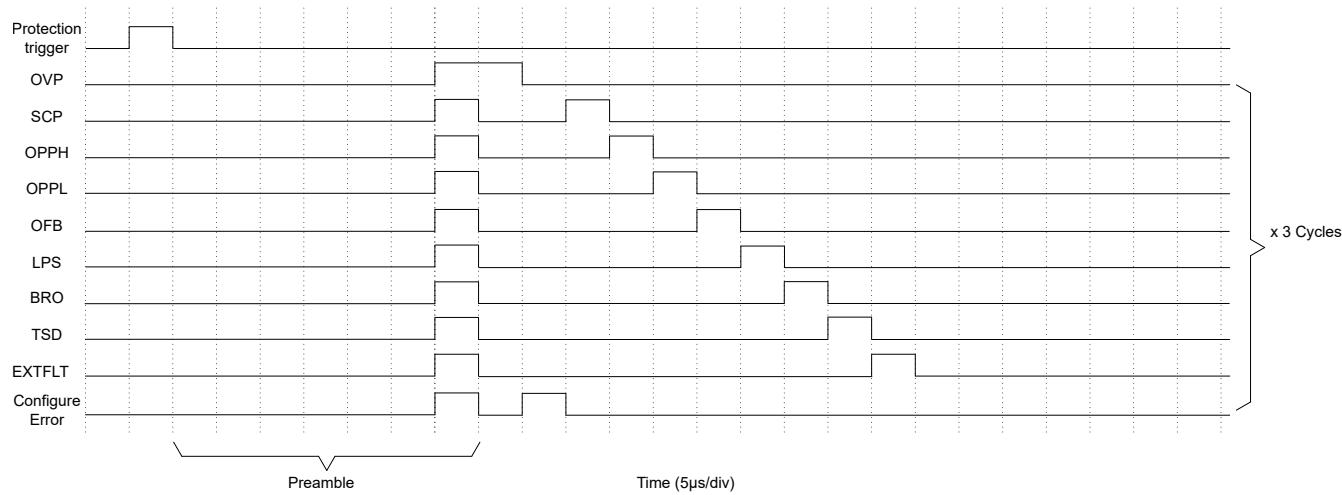

Use the CDX pin to enable and disable CCM mode and X-cap discharge. Select the SW node slew rate when turning on the GaN HEMT. Refer to [Table 7-5](#) for values of resistors to connect from CDX pin to GND for the given operating points. The resistor must be 1% accurate. The CDX pin is also used for fault reporting for easy debugging during design. Refer to [Section 7.4.10.7](#) for details. Do not connect this pin to GND.

**Table 7-5. CDX Pin Programming Resistor Values**

| CDX Pin Resistor (kΩ) | CCM      | SW Node Turn-On Slew Rate | X-cap Discharge |

|-----------------------|----------|---------------------------|-----------------|

| 5.23                  | Disabled | 10V/ns                    | Enabled         |

| 6.34                  | Disabled | 7V/ns                     | Enabled         |

| 7.68                  | Disabled | 5V/ns                     | Enabled         |

| 9.31                  | Disabled | 10V/ns                    | Disabled        |

| 11.5                  | Disabled | 7V/ns                     | Disabled        |

| 14.3                  | Disabled | 5V/ns                     | Disabled        |

| 17.8                  | Enabled  | 10V/ns                    | Enabled         |

| 22.6                  | Enabled  | 7V/ns                     | Enabled         |

| 28.7                  | Enabled  | 5V/ns                     | Enabled         |

| 36.5                  | Enabled  | 10V/ns                    | Disabled        |

| 51.1                  | Enabled  | 7V/ns                     | Disabled        |

| 75                    | Enabled  | 5V/ns                     | Disabled        |

### 7.3.10 VCC - Input Bias

The VCC pin provides the bias to the device, powering the internal references, gate driver, regulators, control circuits and protection features. Use a minimum of 10µF capacitance from this pin to GND for maintaining VCC voltage regulation with self-bias feature. Use of an additional 10nF ceramic capacitor in parallel is recommended

for low ESR and minimum overshoot and undershoot on this pin. Use  $30\mu\text{F}$  capacitance at this pin for holdup without reset in the event of two missing line cycles at the input.

## 7.4 Feature Description

### 7.4.1 Self Bias and Auxless Sensing

The UCG2882x includes self bias and auxless sensing to eliminate the transformer auxiliary winding. Removing the auxiliary winding and associated components makes the system design simpler, smaller and cheaper.

The self bias feature is especially useful in applications like USB-PD chargers with wide output voltage range. Typically in wide output voltage range designs, the aux winding generates device supply voltage (VCC) greater than the UVLO threshold at the minimum  $V_{\text{OUT}}$  which is 3.3V. In such case, the voltage on aux winding increases six times when  $V_{\text{OUT}} = 20\text{V}$  which needs an internal and external power conversion stage to reduce to VCC range, increasing external components and reducing efficiency. The UCG2882x self bias eliminates the need for the additional power conversion stage at the VCC pin thus reducing the number of components and recovering power losses. The self bias circuit is designed to keep VCC higher than the UVLO threshold throughout the range of operation of the device, given the components around the device are used within the range recommended in the data sheet. Auxless sensing circuits are connected to the SW pin. The device senses the voltage on SW for valley sensing and various protections. The input bulk capacitor voltage and output voltage are derived from the SW pin voltage.

### 7.4.2 Control Law

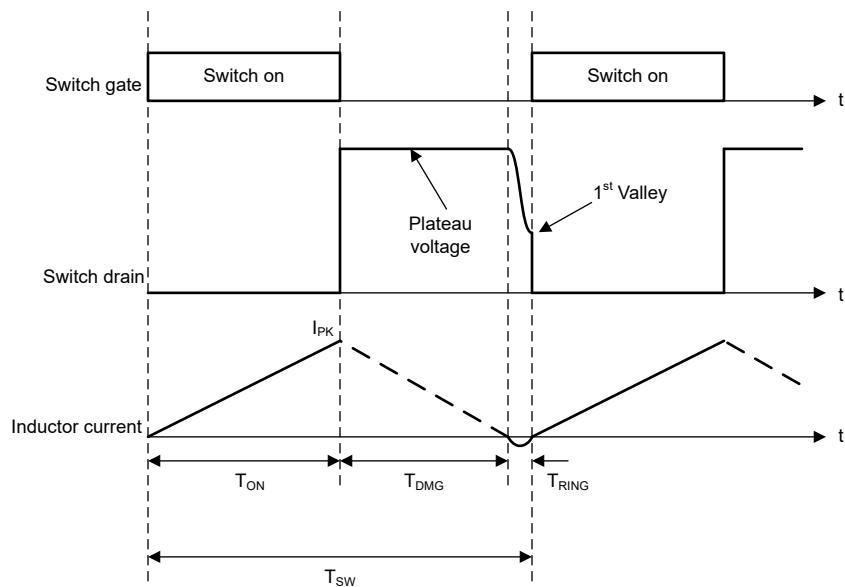

The UCG2882x is a peak current mode control QR flyback converter. The converter starts by turning on the primary-side integrated GaN HEMT. The current in the transformer primary side winding  $I_{\text{PRI}}$  increases with a slope dependent on  $V_{\text{IN}}$  and primary magnetizing inductance  $L_M$  and equals  $V_{\text{IN}}/L_M$ . Once  $I_{\text{PRI}}$  reaches the peak value  $I_{\text{PK,PRI}}$ , the GaN HEMT turns off. By flyback action, the secondary winding voltage increases and turns on the synchronous rectifier (SR) FET body diode to clamp to output voltage  $V_{\text{OUT}}$ . During this time, the secondary winding current reduces from secondary peak current  $I_{\text{PK,SEC}}$  with a slope  $V_{\text{OUT}}/L_S$ , where  $L_S$  is the secondary winding inductance. The switch node voltage is equal to the sum of  $V_{\text{IN}}$  and primary to secondary turns ratio  $N$  times  $V_{\text{OUT}}$ , called the plateau voltage. Once the secondary current reduces to zero,  $L_M$  and total switch node capacitance  $C_{\text{SW}}$  begin to resonate to cause magnetizing ring. The UCG28826 turns on the primary GaN HEMT at a valley in this magnetizing ring to reduce the turn-on switching losses.

Figure 7-2. Flyback Converter Waveforms

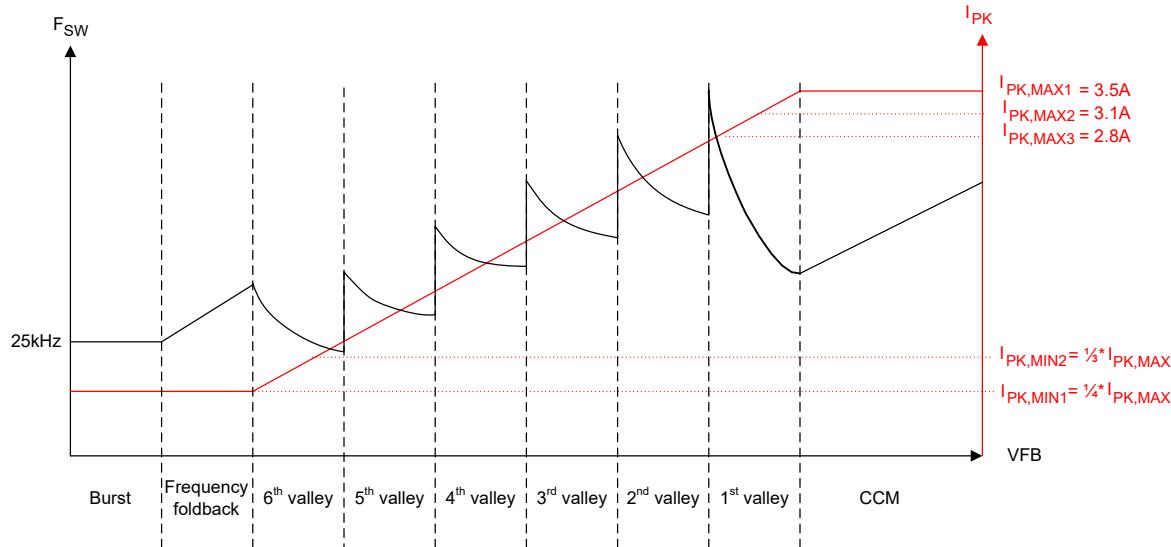

Hence, in UCG2882x, in every switching cycle, the primary GaN HEMT turns off after reaching the peak current threshold and turns on next at a target valley in magnetizing ring during discontinuous mode (DCM) operation. The instantaneous primary peak current and target valley is determined by the feedback (FB) pin voltage as per the control law of [Figure 7-3](#). Connect the FB pin to the optocoupler collector. The negative feedback loop sets FB pin voltage to the required value to support a certain  $V_{OUT}$  and  $P_{OUT}$  on the output. The device can operate in one of the four modes of operation: burst, frequency foldback, valley switching or continuous conduction mode, as described later.

**Figure 7-3. UCG2882x Control Law**

In the control law shown in [Figure 7-3](#), the UCG2882x offers flexibility to select a max peak current  $I_{PK,MAX}$  to optimize for the switching frequency at rated load and transformer size. For each  $I_{PK,MAX}$  setting, a scaling ratio of 1/3rd or 1/4th is available for the minimum peak current  $I_{PK,MIN}$ . This  $I_{PK,MIN}$  value determines the switching frequency and losses in light load conditions when the flyback converter is operating in frequency foldback or burst modes. For all values of  $I_{PK,MAX}$  and  $I_{PK,MIN}$ , the slope of control law peak current vs feedback voltage remains the same, as per [Equation 1](#). [Table 7-6](#) shows the threshold voltages for transition between different modes and between valleys for different peak current settings of [Table 7-3](#).

**Table 7-6. FB Pin Voltage Thresholds for Various Peak Current Settings**

|                | PARAMETER                                  | TEST CONDITIONS | $I_{PK,MAX} = 2.8A$                  | $I_{PK,MAX} = 3.1A$ | $I_{PK,MAX} = 3.5A$ | UNIT |

|----------------|--------------------------------------------|-----------------|--------------------------------------|---------------------|---------------------|------|

| $V_{FBOPEN}$   | Open FB pin voltage                        | VFB decreasing  | 3.3                                  | 3.45                | 3.65                | V    |

| $V_{THCCMto1}$ | CCM to 1st valley threshold                |                 | 2.18                                 | 2.4                 | 2.65                |      |

| $V_{TH12}$     | 1st to 2nd valley threshold                |                 | 1.09                                 | 1.19                | 1.31                |      |

| $V_{TH23}$     | 2nd to 3rd valley threshold                |                 | 0.97                                 | 1.05                | 1.16                |      |

| $V_{TH34}$     | 3rd to 4th valley threshold                |                 | 0.91                                 | 0.98                | 1.08                |      |

| $V_{TH45}$     | 4th to 5th valley threshold                |                 | 0.85                                 | 0.92                | 1.0                 |      |

| $V_{TH56}$     | 5th to 6th valley threshold                |                 | 0.79                                 | 0.85                | 0.93                |      |

| $V_{TH65}$     | 6th to 5th valley threshold                |                 | 1.16                                 | 1.25                | 1.38                |      |

| $V_{TH54}$     | 5th to 4th valley threshold                |                 | 1.22                                 | 1.32                | 1.46                |      |

| $V_{TH43}$     | 4th to 3rd valley threshold                |                 | 1.28                                 | 1.39                | 1.53                |      |

| $V_{TH32}$     | 3rd to 2nd valley threshold                |                 | 1.34                                 | 1.45                | 1.61                |      |

| $V_{TH21}$     | 2nd to 1st valley threshold                |                 | 1.46                                 | 1.59                | 1.76                |      |

| $V_{TH1toCCM}$ | 1st valley to CCM threshold                |                 | 2.18                                 | 2.4                 | 2.65                |      |

| $V_{THFF}$     | 6th valley to frequency foldback threshold |                 | $I_{PK,MIN} = 1/4 \times I_{PK,MAX}$ | 0.73                | 0.78                | 0.85 |

|                |                                            |                 | $I_{PK,MIN} = 1/3 \times I_{PK,MAX}$ | 0.89                | 0.96                | 1.05 |

#### 7.4.2.1 Valley Switching

The UCG2882x is designed to operate with soft switching and primary FET turn-on at a valley to reduce switching losses. The converter operates in valley switching except during peak load transients during which control can transition to CCM mode (if enabled using CDX pin). During valley switching mode, the target valley and peak current threshold are governed by the control law of [Figure 7-3](#) and [Equation 1](#):

$$I_{PK} = 1.45 \times (V_{FB} - 0.25) \quad (1)$$

During valley switching, with increasing output power, the peak current threshold continues to increase linearly as per above equation. The switching frequency also varies based on  $I_{PK}$  and valley targets corresponding to the instantaneous FB pin voltage. When output power is increasing from light loads to rated power, the control transitions from 6th valley till 1st valley with corresponding linear increase in  $I_{PK}$  threshold. As output power continues to increase further to take FB voltage to the edge of 1st valley operation, the converter transitions into CCM mode operation with  $I_{PK}$  clamped to the maximum value  $I_{PK,MAX}$  and increase in switching frequency  $F_{sw}$  with further increase in output load. This clamp on  $I_{PK,MAX}$  limits the transformer size in a high density power supply design. See [Section 7.4.2.4](#) for details of CCM mode of operation. If output power reduces while operating in the 6th valley, the control transitions to frequency foldback mode to operate at higher valleys and lower frequency to reduce switching losses further.

The FB pin voltage thresholds for valley transitions include a hysteresis and vary depending on increasing or decreasing  $P_{OUT}$  to enable valley locking and prevent any audible noise due to hopping between valleys. Refer to the Electrical Characteristics table for FB pin voltage thresholds which determine the mode of operation for UCG2882x. For zero optocoupler collector current with large  $P_{OUT}$ , the FB pin is pulled up to  $V_{FBOPEN}$  through a  $60k\Omega$  resistor.

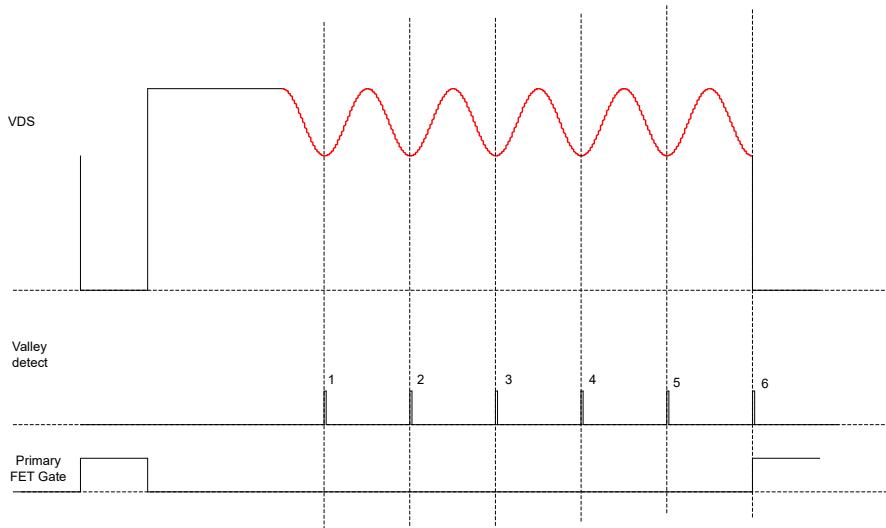

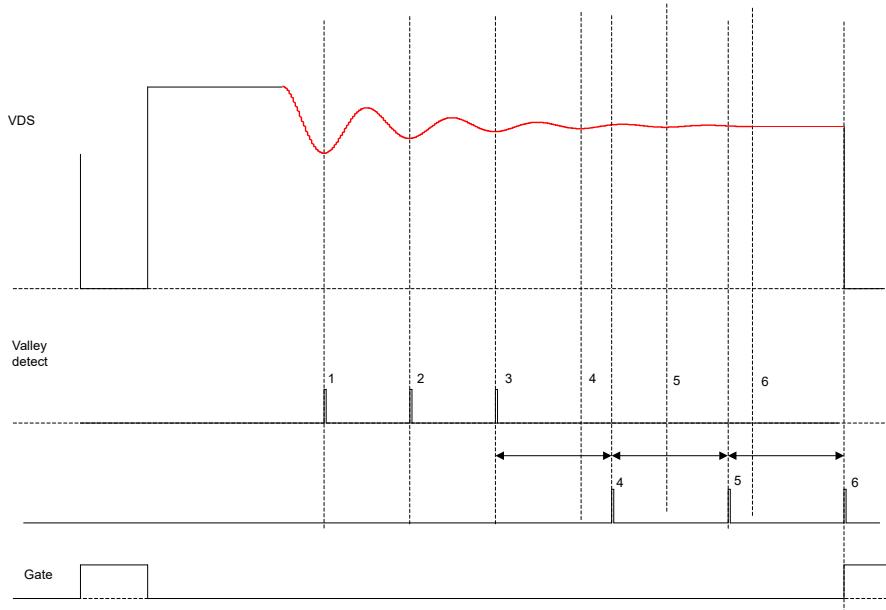

**Figure 7-4. Valley Counter With Continuous Valley Occurrence**

Typically, the control counts the valleys and turns on the primary GaN HEMT once the target valley is reached, shown in [Figure 7-4](#). For the case when SW node waveform is damped so the valleys disappear before reaching the target valley, a DCM ring fixed timer of  $3.75\mu\text{s}$  starts to continue counting valleys and turn on the primary GaN HEMT once the valley target is reached, shown in [Figure 7-5](#). During start-up (soft start) when  $V_{\text{OUT}}$  is small, if the valleys do not appear, the controller turns on the primary GaN HEMT after  $100\mu\text{s}$  from last turn on, to switch at  $10\text{kHz}$  (the minimum frequency clamp during soft start) for initial few cycles to avoid latch up condition.

**Figure 7-5. Valley Counter With Missing Valleys**

The device operates in CCM mode for maximum 10ms to support any transient output load conditions, as seen in notebook chargers and other applications. The converter returns to the 1st valley QR operation after expiry of this 10ms CCM timer. CCM mode can be entered again only after the FB pin voltage reduces below the  $V_{\text{TH1toCCM}}$  threshold. At all times during operation of UCG2882x, the maximum switching frequency can be limited with a frequency clamp setting programmable with a resistor from FCL pin to GND, as detailed in [Section 7.3.8](#).

#### 7.4.2.2 Frequency Foldback

If output power reduces while operating in 6th valley to reduce FB pin voltage below  $V_{THFF}$ , the converter transitions to frequency foldback mode and abandons valley switching. The peak current threshold is clamped to  $I_{PK,MIN}$  and converter operates at higher valleys after 6th valley, depending on FB pin voltage. This causes the switching frequency to reduce further with increase in target valley number, until switching frequency reduces to 25kHz and is clamped at 25kHz. Minimum switching frequency is clamped to 25kHz to prevent any audible noise, with a total switching cycle time of 40 $\mu$ s. Further reduction in output power takes the converter to burst mode to reduce unnecessary switching losses from periodic switching and achieve very low standby power consumption.

#### 7.4.2.3 Burst Mode

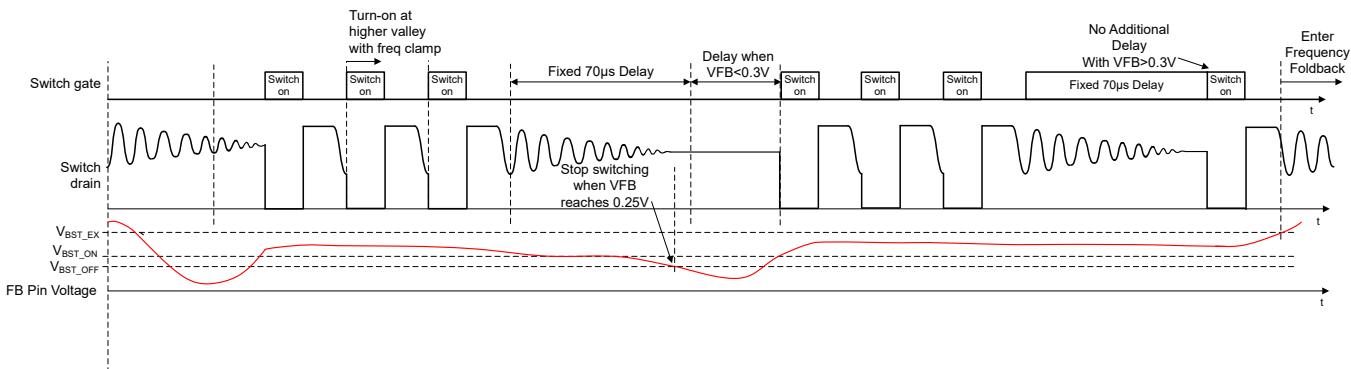

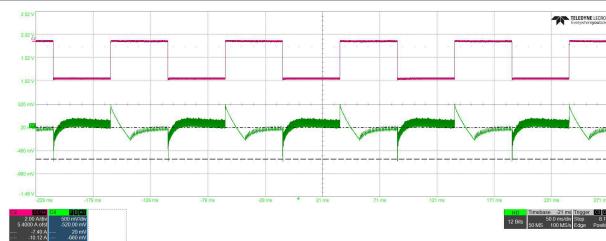

If output power continues to reduce while in frequency foldback mode, the device enters burst mode when FB pin voltages reaches 0.25V for the first time and the device stops switching. Depending on the output power, once FB pin voltage recovers to 0.3V is when device resumes switching in burst mode.

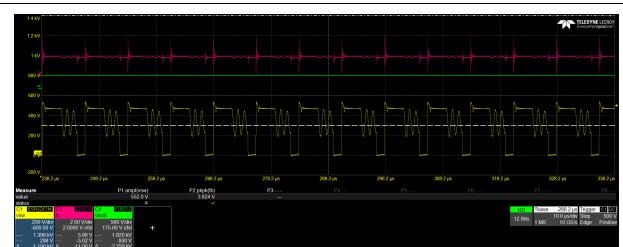

The UCG2882x's burst mode offers three 1st valley QR switching cycles followed by a minimum 70 $\mu$ s delay before the start of next burst packet. Valley switching reduces switching losses while the delay limits power delivery in burst mode and device transitions to other modes of operation at higher power to maintain high efficiency in the range of output power. In burst mode, frequency clamp is fixed at 250kHz and the primary GaN HEMT turns on at next valley after the expiration of the clamp timer. With burst mode operation, switching losses are kept low with valley switching with limit on electromagnetic emissions with minimum peak current to pass emission standards. Burst mode switching waveforms are shown in Figure 7-6.

**Figure 7-6. Burst Mode Entry and Exit Waveforms**

#### 7.4.2.4 Continuous Conduction Mode (CCM)

As shown in Figure 7-3, once the boundary of 1st valley QR operation is reached with increasing output power, the control clamps  $I_{PK}$  to the maximum selected value  $I_{PK,MAX}$ , and begins to reduce the secondary conduction time  $T_{OFF}$  in CCM mode. This reduction in  $T_{OFF}$  is proportional to increase in FB pin voltage, until 50% of the QR mode off-time to reach maximum 1.5 $\times$  the QR mode output power delivery capability. Use a primary magnetizing inductance  $L_M$  large enough to not hit the frequency clamp during CCM mode and avoid any subharmonic oscillations which can increase output voltage ripple, depending on application requirements. For long duration output power transients, the converter returns to 1st valley QR mode after expiry of the 10ms CCM timer and continues to deliver the largest possible output power at the transition point of QR and CCM modes, while operating in QR mode. The device offers flexibility to enable or disable CCM mode operation with a resistor from the CDX pin to GND, as per values in Table 7-5.

#### 7.4.3 GaN HEMT Switching Capability

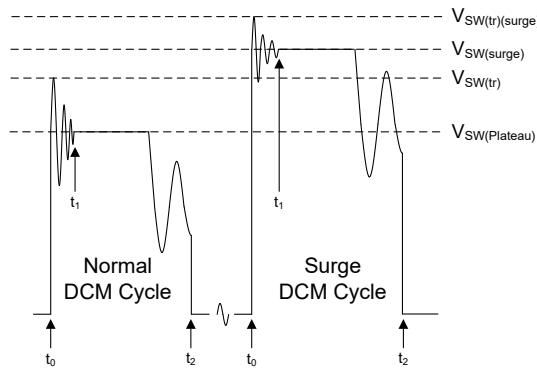

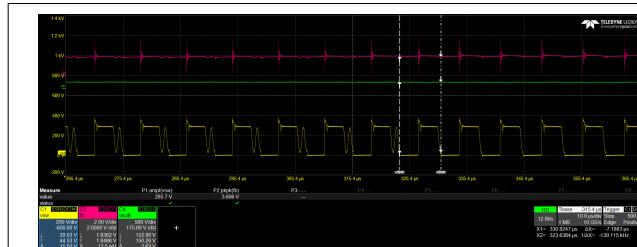

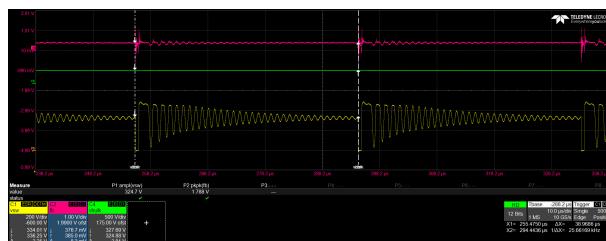

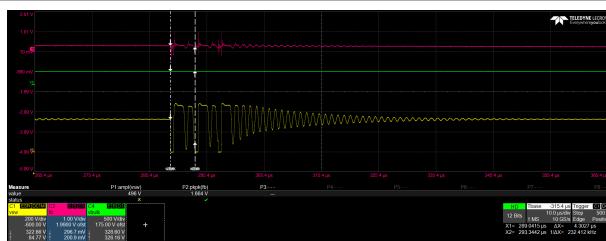

The UCG2882x primary-side integrated GaN HEMT switching capability is explained with the help of Figure 7-7. Figure 7-7 shows the drain-source voltage (same as SW pin voltage) for the UCG2882x for two distinct switching cycles in a flyback application. The first switching cycle is a normal switching cycle followed by a surge switching cycle in DCM/valley switching condition.

**Figure 7-7. GaN HEMT Switching Capability**

Each cycle starts before  $t_0$  with the GaN HEMT in *on* state. At  $t_0$ , the GaN HEMT turns off and the parasitic elements cause the drain-source voltage to ring at a high frequency. The high frequency ringing is damped out by  $t_1$ . Between  $t_1$  and  $t_2$ , the HEMT drain-source is at a flat plateau voltage with reducing secondary winding current in a flyback design. At  $t_2$ , the GaN HEMT turns on at a valley. During normal operation, the device safely operates up to 750V leakage transient voltage ( $V_{SW(tr)}$ ) in every switching cycle. For rare surge events, the transient ring voltage is limited to 800V and the plateau is limited to 750V.

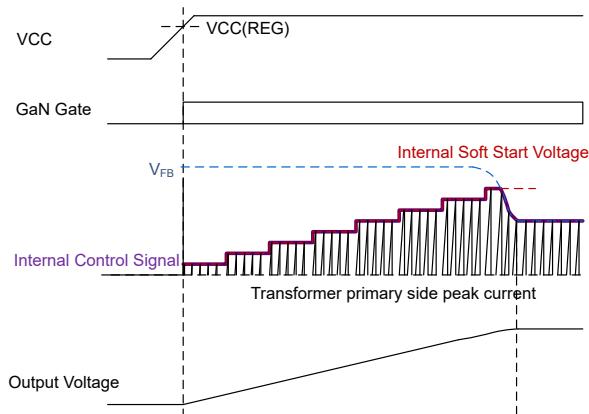

#### 7.4.4 Soft Start

When turned on, a flyback converter starts with 0V output voltage. The low voltage can cause the feedback voltage FB to clamp the maximum value and trigger overload protections. To prevent the clamping from happening, the UCG2882x starts in soft start mode. As Figure 7-8 shows, during this time, an internal FB voltage ramp increases in eight steps from 0V to its maximum value in 4ms. The maximum value of internal FB ramp at FB pin voltage is equivalent to 80% of the  $I_{PK,MAX}$  setting and changes for different resistor settings on the IPK pin. During soft start, the smaller of internal ramp voltage and actual FB pin voltage is used to determine the device operating point in the control law of Figure 7-3. Once the internal FB ramp voltage reaches the maximum value at the end of 4ms is when control is transferred to FB pin voltage for output regulation. Soft start sequence is executed every time at start up or when recovering from fault (auto-retry or latch) and brown-out conditions. The minimum frequency clamp is changed to 10kHz only during soft start (which is otherwise at 25kHz during normal operation). The 10kHz minimum frequency clamp helps at start-up when valleys are missing and the control law forces turn-on of primary GaN HEMT every 100 $\mu$ s from the last turn-on edge (if valleys are missing), to charge the output capacitor.

**Figure 7-8. Soft Start Sequence**

#### 7.4.5 Frequency Clamp

The UCG2882x includes frequency clamp to limit the maximum switching frequency. Frequency clamps are useful during design optimizations to pass emissions standards and reduce switching losses by limiting the

switching frequency to a certain value. The device offers four maximum frequency clamp settings at 100kHz, 140kHz, 250kHz, and 500kHz which are selected with a resistor from FCL pin to ground as per values in [Table 7-4](#). There are no condition where the switching frequency exceeds the chosen value of clamp frequency, except in burst mode when the clamp frequency is set to 250kHz. The minimum switching frequency is also clamped to a fixed 25kHz to prevent switching in the audible frequency range and noise from the flyback converter. Low switching frequency can occur during operation in higher valleys or frequency foldback mode.

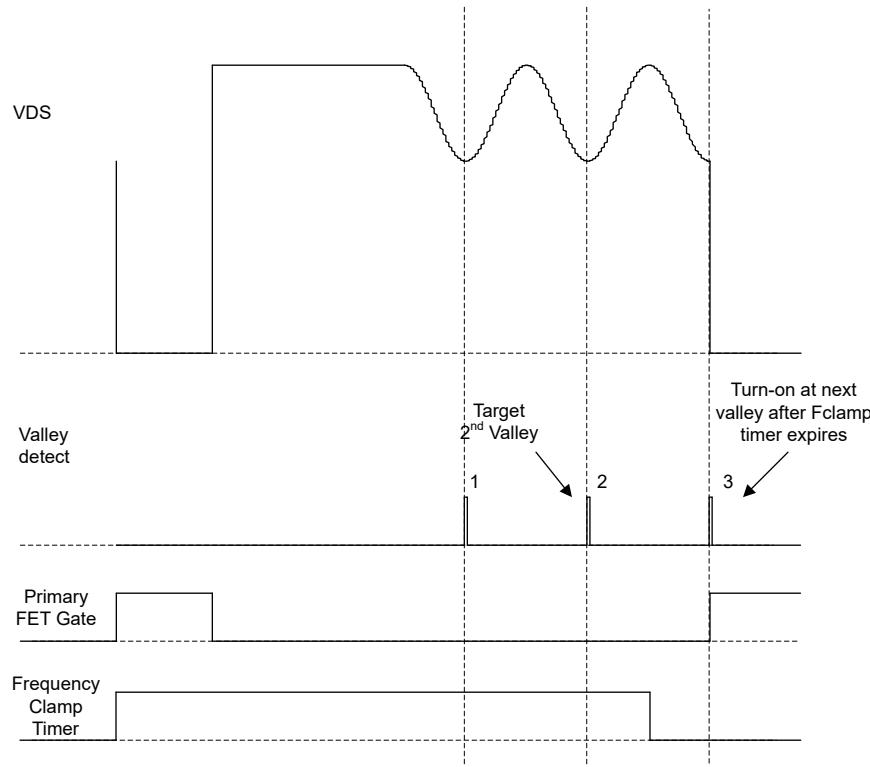

[Figure 7-9](#) illustrates example waveforms that demonstrate the operation of the frequency clamp. In this case, the valley target based on the FB pin voltage at the 2nd valley. After the secondary winding current reduces to zero, the VDS voltage on SW pin begins to resonate and valleys are counted by the valley detection block. The primary-side GaN HEMT does not turn-on at the 2nd valley because the frequency clamp timer is still counting. Only after the expiration of the frequency clamp timer that the primary GaN HEMT turns-on at the next valley, which is the 3rd valley in this case. Based on this logic, the turn-on of the primary GaN HEMT happens only at the next valley post expiration of the frequency clamp timer.

**Figure 7-9. Primary GaN HEMT Turn-On Delay Due to Frequency Clamp**

#### 7.4.6 Frequency Dithering

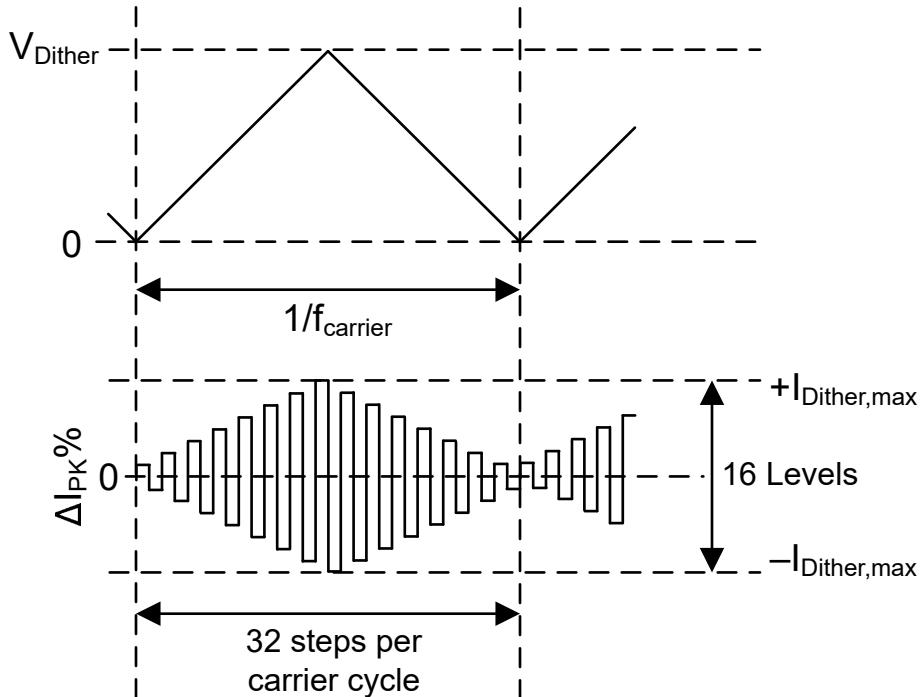

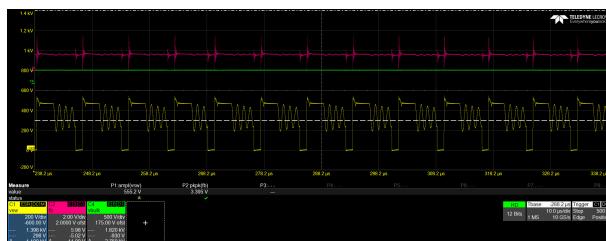

The UCG2882x includes frequency dithering to spread the energy in the spectrum around the switching frequency to reduce electromagnetic emissions, making qualifying for various emissions standards easier. Since this device uses peak current mode control to turn-off the primary GAN HEMT and there is no fixed clock signal to set the switching frequency, the dithering in frequency is achieved with small change to the value of peak current threshold in every switching cycle, changing the peak current, and thus the on-time, off-time and switching frequency, in every cycle. The per cent change to peak current threshold varies based on a fixed 6.25kHz triangular carrier signal with 32 steps alternating in sign at every transition from minimum (0%) to maximum value (called dithering depth,  $\pm 6.25\%$  or  $\pm 12.5\%$ ) in every carrier cycle. The alternating sign of dither perturbation at each step and the low frequency output pole of flyback converter topology averages the cycle-to-cycle power delivery, causing small impact in output ripple due to dithering. The dither perturbation to peak current is asynchronous with the switching frequency and the instantaneous change in peak current is calculated based on the dithering signal during the primary GAN HEMT turn-on time.

The dithering depth can be chosen with a resistor from IPK pin to GND as given in [Table 7-3](#). [Figure 7-10](#) shows the dithering carrier and peak current perturbation waveforms to dither the switching frequency.

**Figure 7-10. Frequency Dithering to Reduce Emissions**

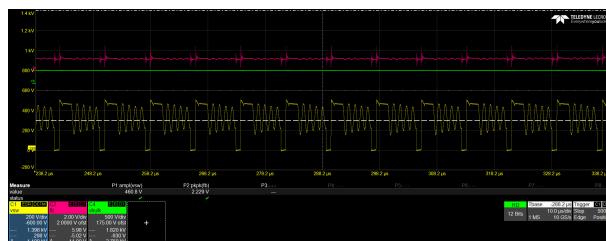

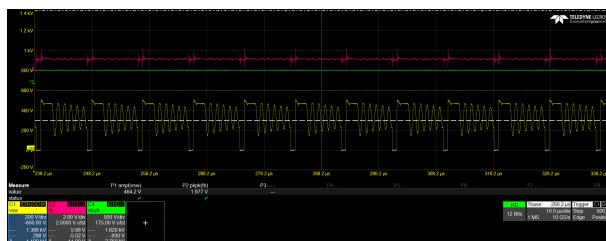

#### 7.4.7 Slew Rate Control

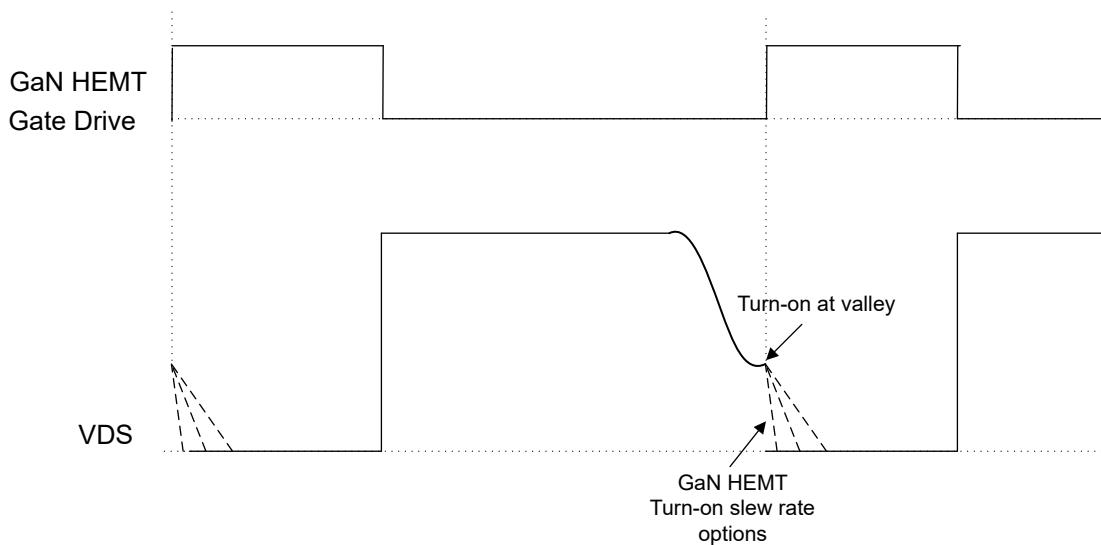

The UCG2882x includes slew rate options for drain voltage reduction from switch node valley voltage to ground at the time of primary GaN HEMT turn-on. This GaN HEMT turn-on during valley switching happens at nearly zero current and incurs negligible additional losses with the slower turn-on due to slew rate control helping to meet various electromagnetic emission standards. Three slew rate options are available at 5V/ns, 7V/ns, and 10V/ns, which vary marginally based on the valley voltage, as shown in [Figure 7-11](#).

**Figure 7-11. GaN HEMT Turn-On Slew Rate Control**

Select the required slew rate value using a resistor from CDX pin to GND as per values in [Table 7-5](#). At the primary GaN HEMT turn-off instant, the increase in SW node voltage depends on  $I_{PK}$  and total switch node capacitance  $C_{SW}$ . A gate drive current controlled reduction in this turn-off slew rate can increase losses significantly. If a reduction in GaN HEMT turn-off slew rate is needed, add an additional capacitor from GaN HEMT drain (switch node) to GND to reduce the rate of increase in switch node voltage at this turn-off instant.

#### 7.4.8 Transient Peak Power Capability

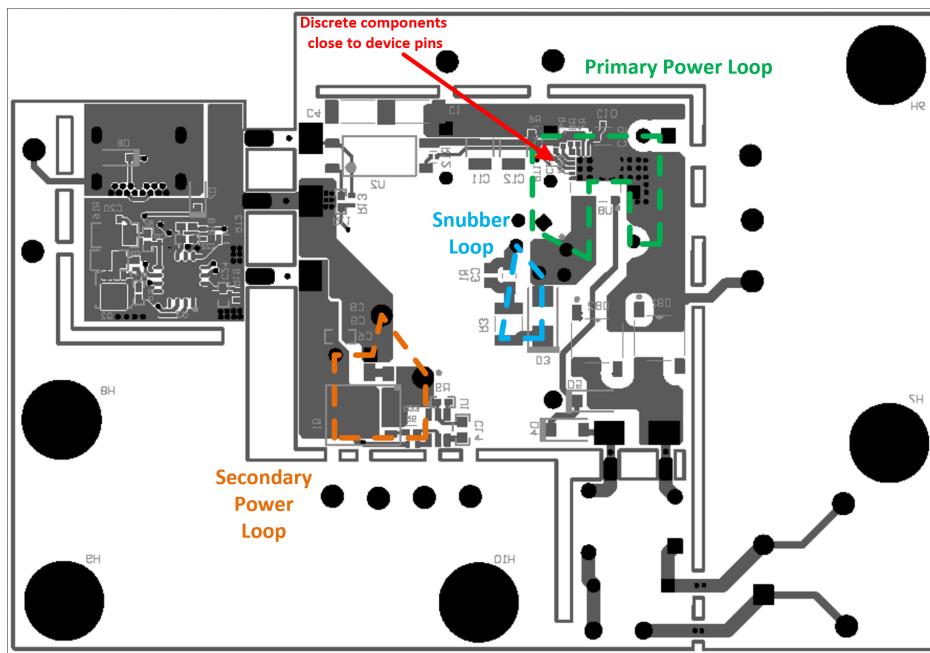

The UCG2882x supports minimum 2 $\times$  transient peak output power capability for applications which require bursts of high power for short durations of time. The peak power is achieved without the need for oversizing the various components such as the transformer, power FETs, and so forth, and the same flyback design is usable for minimum 2 $\times$  the continuous output power rating for short durations. With the peak power handling capability, a 65W flyback converter designed with UCG28826 can deliver a minimum 130W transient peak output power for a maximum 120ms duration during high line and 10ms during low line operating conditions.