# TI Live! BATTERY MANAGEMENT SYSTEMS SEMINAR

TIGER ZHOU

SWITCHING CHARGER PCB LAYOUT TIPS AND EXAMPLE

#### Content

- Switching charger layout key considerations

- Optimize electrical performance with minimized circuit noise

- Noise sources and parasitics

- di/dt loop, dv/dt coupling

- Solutions:

- Components placement, shielding, bypassing, ground partition, routing sensitive signal

- Optimize thermal performance

- Layout optimization examples

- Buck-boost EVM, 5S power tools, notebook charger

- Summary

#### Key considerations of switching chargers

Layout is key to achieve the optimal electrical and thermal performance:

Goals: low noise operation, low EMI, high accuracy, high efficiency, low temp

Issues: high slew rate of di/dt or dv/dt, parasitic, noise, etc.

Solutions: minimize coupling, optimize ground and improve the accuracy

Key to a successful layout is to understand the circuit, including the parasitic components.

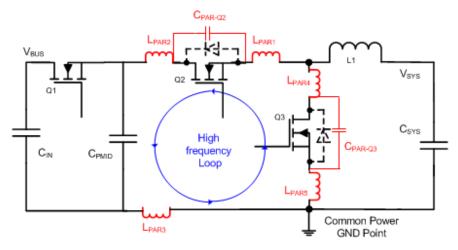

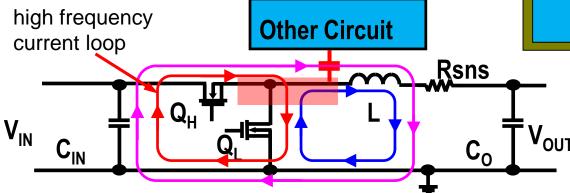

#### Noise source -high di/dt loop

- Identify high di/dt loops

- Prioritize component placement to reduce high di/dt loop area

#### Components placement example

Small high frequency current loop

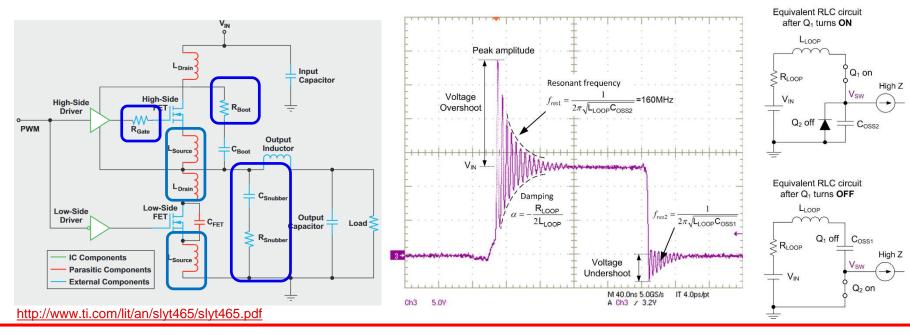

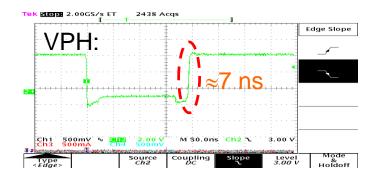

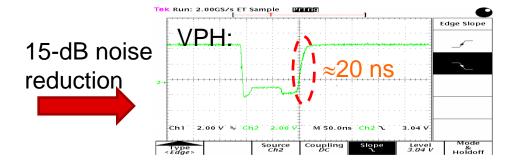

### Noise source -dv/dt coupling

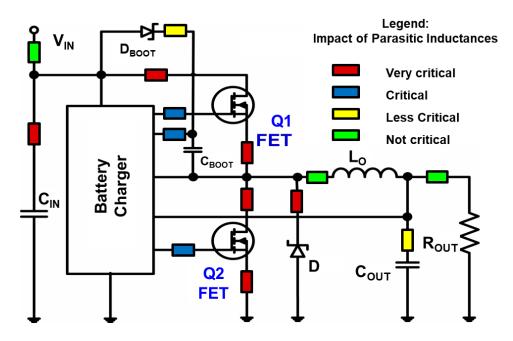

The buck converter switch node rising edge ringing is related to L<sub>Drain</sub>, L<sub>Source,</sub> low side C<sub>FET</sub> and input capacitor. The falling edge ringing is related to high side FET's Coss and low side FET's parasitic inductance.

#### Reduce EMI noise by suppressing switch node ringing

- Suppress switch node ringing

- Add Rboot

- Add RC snubber

- Add Rgate

- Reduce parasitic inductance

#### Parasitic resistance

All conductors exhibit resistance – (except superconductors)

- Simple formulae exist for specific geometries

- Sheet Resistivity:  $R_{sheet} = \rho \frac{l}{A}$

- ≈ 500 μΩ per square for 1 oz (34 μm) copper

This is important where currents are high

Current sensing resistors – 10 m $\Omega$  typical

Copper has a large temperature co-efficient of resistance  $TCR_{cu} \approx 4000 \ ppm \ ^{\circ}C^{-1}$  (+40% for 100  $^{\circ}C$  rise)

| Copper Weight (Oz.) | Thickness<br>(mm/mils) | mΩ per<br>Square<br>(25 °C) |

|---------------------|------------------------|-----------------------------|

| 1/2                 | 0.02/0.7               | 1.0                         |

| 1                   | 0.04/1.4               | 0.5                         |

| 2                   | 0.07/2.8               | 0.2                         |

$4*500 \mu\Omega = 2 m\Omega$

# **Layout tips**

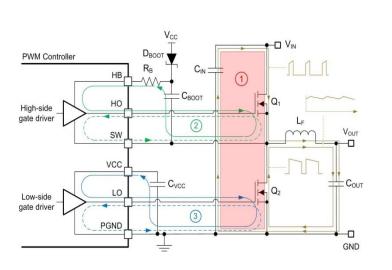

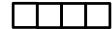

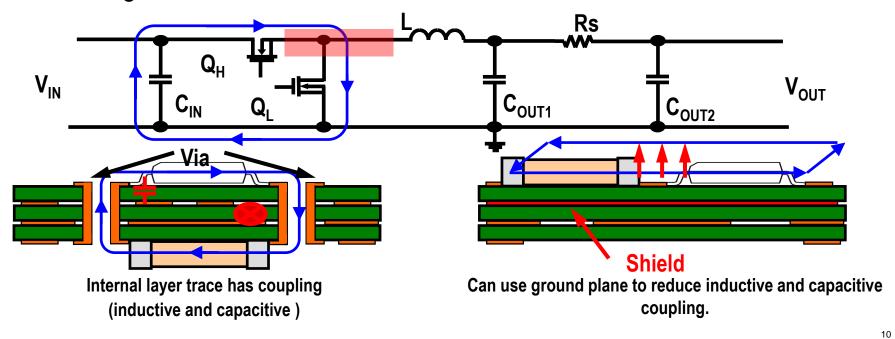

#### 1. Same layer components placement reduces parasitic

Put power components on the same layer and use ground layer to shield switching noise

#### 2. Noise shielding with ground layer

- Ground layer near power component layer can reduce:

- Inductive and capacitive coupling noise

- High frequency current loop area

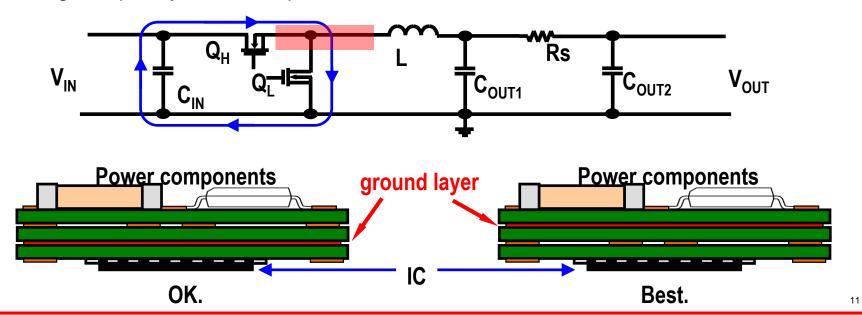

#### 3. Coupling minimization with ceramic capacitors

- A small capacitor can provide lower impedance at high frequency

- Put 10-nF ceramic capacitor between HS FET's drain and LS FET's source

[\*] Murata Simsurfing tool, <a href="http://ds.murata.co.jp/software/simsurfing/en-us/index.html">http://ds.murata.co.jp/software/simsurfing/en-us/index.html</a>

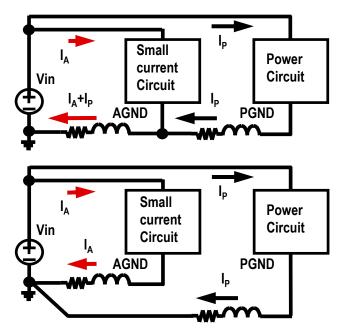

#### 4. Grounding – separate PGND and AGND

AGND and PGND single connection point

Analog ground copper pour

- Separate PGND (high current ground) and AGND (small current ground) first to avoid small signal ground coupling high current (high di/dt) ground noise

- Make PGND and AGND joint together near charger IC

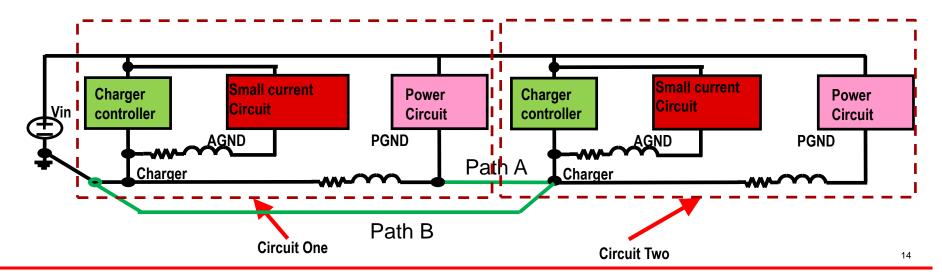

#### 5. Grounding – PGND as common ground

- Separate PGND and AGND first to avoid small signal ground coupling high current (high di/dt) ground noise.

- Make PGND and AGND joint together near charger IC.

- Use PGND as common ground for different sub-circuit, such as: pathA or pathB.

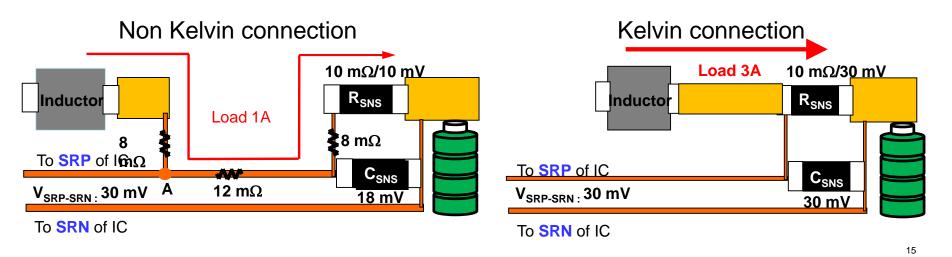

#### 6. High accuracy with Kelvin sensing circuit

- The thin trace causes an unexpected voltage drop on the board.

- Non-Kelvin connector causes the SRP-SRN is different than V<sub>RSNS</sub>.

- Kelvin connection is needed for current sensing.

- Voltage sensing trace doesn't allow high current path.

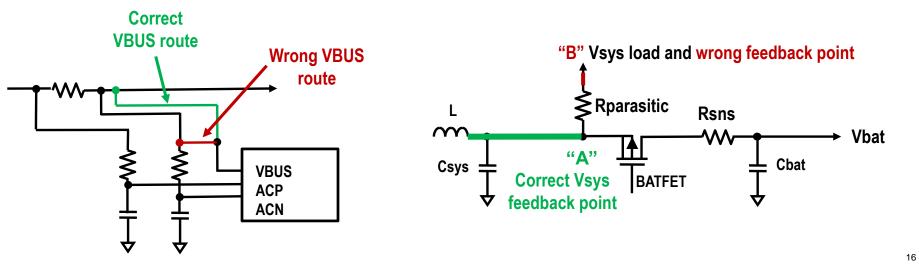

### 7. High accuracy with minimization of parasitic impact

- Avoid  $V_{BUS}$  share same trace with  $V_{ACN}$  (Separate  $V_{ACN}$  trace and  $V_{BUS}$  trace)

- Avoid high parasitic resistance from the BATFET to VSYS load and feedback point (separate VSYS trace from IC VSYS pin to BATFET's source or on the green trace)

#### Thermal performance optimize - FETs

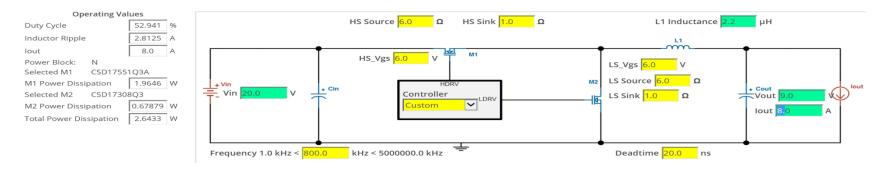

- Use Webench tool customize setup to estimate the power loss.

- Check the FET's thermal resistance in 3x3-mm and 5x6-mm package.

- Check the thermal performance at the worst case.

- If single FET cannot meet the thermal performance, we may have to use two FETs in parallel.

#### Thermal performance optimize - FETs

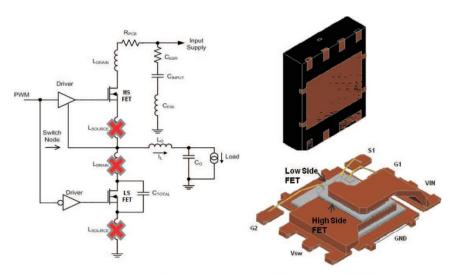

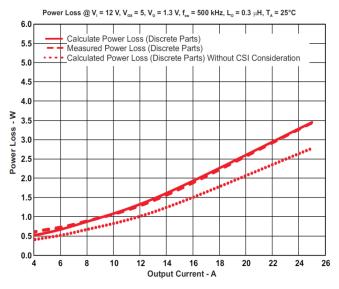

- TI app note-power loss calculation considering the FET parasitic inductance.4

- Dual FET reduces the parasitic inductance between top FET and bottom FET.

Figure 7. Schematic for Converter 2 - TI Power Block Solution

Figure 9. Power Loss Calculation Comparisons With/Without CSI Consideration

#### Thermal performance optimize - inductor

Use vendor calculation tool<sup>5</sup> to estimate the power loss and thermal performance.

| Choose Calculator Type       |                                                   |                     |        |         |        |                            |              | F           | Ratings                      |               |        |

|------------------------------|---------------------------------------------------|---------------------|--------|---------|--------|----------------------------|--------------|-------------|------------------------------|---------------|--------|

| Buck                         | IHLP-5050CE-01 - 2.2 Buck μH Ind. Loss Calculator |                     |        |         |        |                            |              | Inductance  | 2.2                          | μH            |        |

|                              |                                                   |                     |        |         |        |                            | 25° C DC Res | 0.0072      | Ohms                         |               |        |

| Choose Available Series Inpu |                                                   |                     | nputs: |         |        | Outnuta                    |              | Isat        | 29                           | Amps          |        |

| IHLP-5050CE-01 ✓             | Enter data into yellow fields                     |                     |        | Outputs |        |                            | I(Heat)      | 16          | Amps                         |               |        |

| Calcat Industance            | Frequ                                             | ency = 800000       |        | 0000    | Hz     | ET <sub>ckt</sub>          | 6.19         | V-usec      |                              |               |        |

| Select Inductance:  0.1 µH   |                                                   | I <sub>ind</sub> =  |        | 8       | Amps   | F(eff)                     | 514183.8     | Hertz       | Inductor Current (One Cycle) |               | )      |

|                              | Ambient T                                         | emp =               | 5      | 55      | °C     | Res                        | 0.009142     | Ohms        | 9.4                          | $\overline{}$ |        |

| 0.15 μH<br>0.22 μH           | Vo                                                | lts In =            | 2      | 20      | Volts  | I <sub>max</sub>           | 9.41         | Amps        |                              |               |        |

| 0.22 μΠ O                    |                                                   | out =               |        | 9       | Volts  | I <sub>min</sub>           | 6.59         | Amps        | 8.0                          |               |        |

| 0.47 µH                      |                                                   | V <sub>SW</sub> =   | 0.0    | 025     | Volts  | I <sub>ripple</sub>        | 2.81         | Amps        | 7.0                          |               |        |

| 0.6 μH 🔾                     |                                                   | V <sub>D</sub> =    | 0.0    | 025     | Volts  | Duty                       | 0.45         |             | 6.0                          |               |        |

| 0.68 μH<br>0.82 μH<br>1 μH   |                                                   |                     |        |         |        | P <sub>core</sub>          | 0.345        | Watts       |                              |               |        |

|                              |                                                   | ET <sub>100</sub> = | 2.10   |         | V-usec | P <sub>dc</sub>            | 0.585        | Watts       | 5.0                          |               |        |

| 1.5 µH                       |                                                   | B <sub>pk</sub> =   |        | 294.8   |        | Pac                        | 0.641        | Watts       | 4.0                          |               |        |

| 1.8 µH                       |                                                   |                     |        |         | G      |                            |              |             | 3.0                          |               |        |

| 2.2 µH                       | A                                                 | 0.520               | Inch   | 13.2    | mm     | P <sub>tot</sub>           | 1.571        | Watts       | 3.0                          |               |        |

| 3.3 μH<br>4.7 μH             | В                                                 | 0.508               | Inch   | 12.9    | mm     | Temp.<br>Coeff.            | 18.8         | °C/W        | 2.0                          |               |        |

| 5.6 µH                       |                                                   | 0.138               | Inch   | 3.5     | mm     | Temp Rise                  | 29.5         | °C          | 1.0                          |               |        |

| 6.8 µH                       |                                                   | 0.700               |        | 0.0     |        | Comp                       |              |             |                              |               |        |

| 8.2 µH O                     |                                                   |                     |        |         |        | Temp                       | 84.5         | °C          | 0.0                          | ).5           | 1 1.25 |

| 10 μH 🔘                      | Reference<br>Cost                                 | ce 1.5              |        |         |        | Compared to IHLP-2525CZ-01 |              | Time (μSec) |                              |               |        |

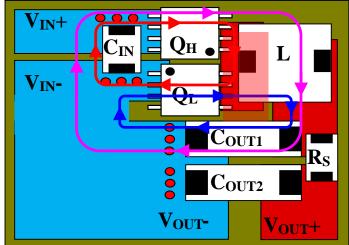

# **Layout examples**

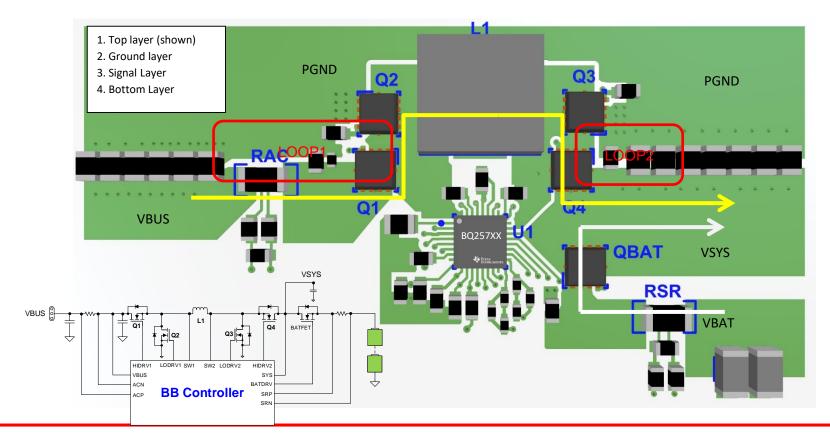

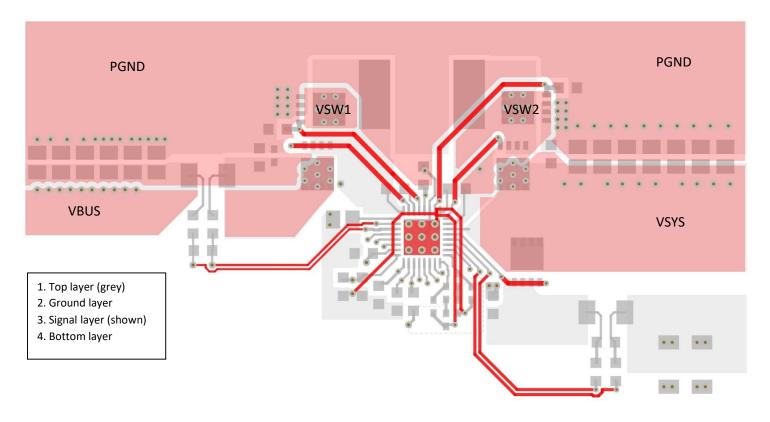

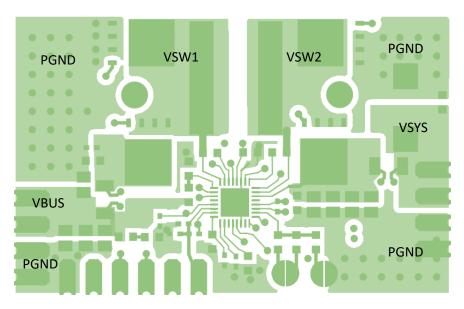

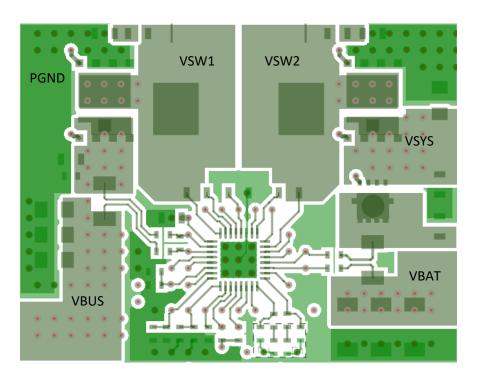

### **Example: A buck-boost charger EVM layout**

21

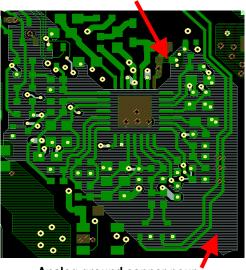

## **Example: Inner traces and single point grounding**

#### 24-Vin, 240-W, 5S power tool

PMP22085

- High power 5 to 24 VIN and 240 W

- High efficiency of 98%

- Compact size of 1.08 inches x 1.68 inches (27.4 mm x 42.7 mm)

- USB on-the-go power bank

- Supports 1 to 5S battery

- Wide input range USB Type-C PD compliance

#### 130-W high density notebook charger

- High power 5 to 24 VIN and 130 W

- Dual-FET for high density

- Compact size of 1.01 inches x 1.30 inches

- Supports 1 to 4S battery

- Wide input range USB Type-C PD compliance

## **Summary**

- Switching charger layout key considerations

- Optimize electrical performance with minimized circuit noise

- Minimize the noise source, reduce or shield coupling

- AGND and PGND design considerations

- Achieve high accuracy signal sensing

- Optimize thermal performance

- Loss estimation with modeling

- Component selection

- Layout design with thermal performance

#### **Details on the layout guideline**

| Priority | Components         | Function           | Impact                                                                | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|--------------------|--------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        |                    | PCB layer stack up | Thermal, efficiency, signal integrity                                 | Multi- layer PCB is suggested. Allocate at least one ground layer. The BQ257XXEVM uses a 4-layer PCB (top layer, ground layer, signal layer and bottom layer).                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2        | CBUS, RAC, Q1, Q2  | input loop         | High frequency noise, ripple                                          | VBUS capacitors, RAC, Q1 and Q2 form a small loop 1. It is best to put them on the same side. Connect them with large copper to reduce the parasitic resistance. Move part of CBUS to the other side of PCB for high density design. After RAC and before Q1 and Q2 power stage, it is recommended to put two decoupling capacitors (10 nF, 1 nF, 0402 package) as close as possible to IC to decouple switching loop high frequency noise.                                                                                                                                   |

| 3        | RAC, Q1, L1, Q4    | current path       | Efficiency                                                            | The current path from VBUS to VSYS, through RAC, Q1, L1, Q4, has low impedance. Please pay attention to via resistance if they are not on the same side. The number of vias can be estimated as 1 to 2A/via for a 10mil via with 1 oz copper thickness.                                                                                                                                                                                                                                                                                                                       |

| 4        | CSYS, Q3, Q4       | output loop        | High frequency noise, ripple                                          | VSYS capacitors, Q3 and Q4 form a small loop 2. It is best to put them on the same side. Connect them with large copper to reduce the parasitic resistance. Move part of CSYS to the other side of PCB for high density design.                                                                                                                                                                                                                                                                                                                                               |

| 5        | QBAT, RSR          | current path       | Efficiency, battery voltage detection                                 | Place QBAT and RSR near the battery terminal. The current path from VBAT to VSYS, through RSR and QBAT, has low impedance. Please pay attention to via resistance if they are not on the same side. The device detects the battery voltage through SRN near battery terminal.                                                                                                                                                                                                                                                                                                 |

| 6        | Q1, Q2, L1, Q3, Q4 | power stage        | Thermal, efficiency                                                   | Place Q1, Q2, L1, Q3 and Q4 next to each other. Please allow enough copper area for thermal dissipation. The copper area is suggested to be 2x-4x of the pad size. Multiple thermal vias can be used to connect more copper layers together and dissipate more heat.                                                                                                                                                                                                                                                                                                          |

| 7        | RAC, RSR           | current sense      | Regulation accuracy                                                   | Use Kelvin-sensing technique for RAC and RSR current sense resistors. Connect the current sense traces to the center of the pads, and run current sense traces as differential pairs.                                                                                                                                                                                                                                                                                                                                                                                         |

| 8        | small caps         | IC bypass caps     | Noise, jittering, ripple                                              | Place VBUS cap, VCC cap, REGN caps near IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9        |                    | ground partition   | Measurement<br>accuracy, regulation<br>accuracy, jittering,<br>ripple | Separate analog ground(AGND) and power grounds(PGND) is preferred. PGND should be used for all power stage related ground net. AGND should be used for all sensing, compensation and control network ground for example ACP/ACN/COMP1/COMP2/CMPIN/ CMPOUT/IADPT/IBAT/PSYS. Connect all analog grounds to a dedicated low-impedance copper plane, which is tied to the power ground underneath the IC exposed pad. If possible, use dedicated COMP1, COMP2 AGND traces. Connect analog ground and power ground together using power pad as the single ground connection point. |

Priority, the function in the circuit, the impact and explanations

© Copyright 2022 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated