## PLL Performance, Simulation, and Design

## 5<sup>th</sup> Edition

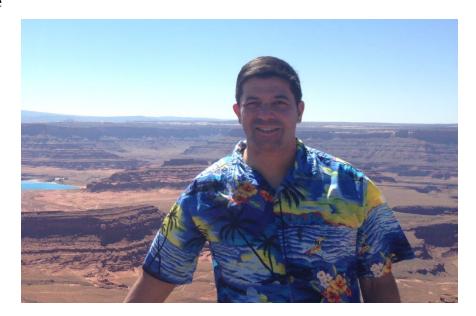

### Dean Banerjee

"Make Everything as Simple as Possible, but not Simpler."

Albert Einstein

To my wife, Nancy, and my children, Caleb, Olivia, and Anabelle

#### **Preface**

I first became familiar with PLLs by working for National Semiconductor (now acquired by Texas Instruments) as an applications engineer. While supporting customers, I noticed that there were many repeat questions. Instead of creating the same response over and over, it made more sense to create a document, worksheet, or program to address these recurring questions in greater detail and just re-send the file. From all of these documents, worksheets, and programs, this book was born.

Many questions concerning PLLs can be answered through a greater understanding of the underlying concepts and the mathematics involved. By approaching problems in a rigorous mathematical way one gains a greater level of understanding, a greater level of satisfaction, and the ability to extend the learnings to other problems.

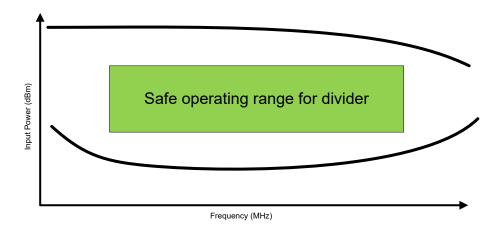

Many of the formulas that are commonly used for PLL design and simulation contain gross approximations with no or little justification of how they were derived. Others may be rigorously derived, but are from outdated concepts or are not compared to measured results to ensure they account for all relevant factors. It is therefore no surprise that there are so many rules of thumb which yield unreliable results.

There is also the approach of not trusting formulas enough and relying on only measured results. The fault with this is that many great insights are lost and it is difficult to learn and grow in PLL knowledge this way. By knowing what a result should theoretically be, it makes it easier to spot and diagnose problems with a PLL circuit. This book takes a unique approach to PLL design by combining rigorous mathematical derivations for formulas with actual measured data. When there is agreement between these two, then one can feel much more confident with the results.

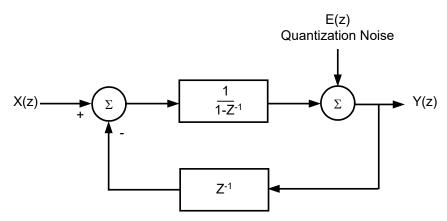

Although PLL technology is evolving, many concepts are timeless and will never become outdated. The fifth edition adds substantial content from the fourth edition regarding many topics including fractional spurs, VCO calibration, delta sigma PLLs, and many other topics.

## **Table of Contents**

| PLL BASICS                                                         | 1   |

|--------------------------------------------------------------------|-----|

| CHAPTER 1 BASIC PLL OVERVIEW                                       | 3   |

| CHAPTER 2 A BRIEF OVERVIEW OF PLL PERFORMANCE CHARACTERISTICS      | 9   |

| CHAPTER 3 IMPACT OF THE PLL PERFORMANCE ON THE SYSTEM              | 14  |

| PLL BUILDING BLOCKS                                                | 19  |

| PLL BUILDING BLOCKS                                                | 21  |

| CHAPTER 5 THE INPUT PATH AND R DIVIDER                             |     |

| CHAPTER 6 THE PHASE DETECTOR AND CHARGE PUMP                       | 30  |

| CHAPTER 7 THE LOOP FILTER                                          | 41  |

| CHAPTER 8 VOLTAGE CONTROLLED OSCILLATORS                           | 45  |

| CHAPTER 9 PRESCALERS AND HIGH FREQUENCY DIVIDERS                   | 61  |

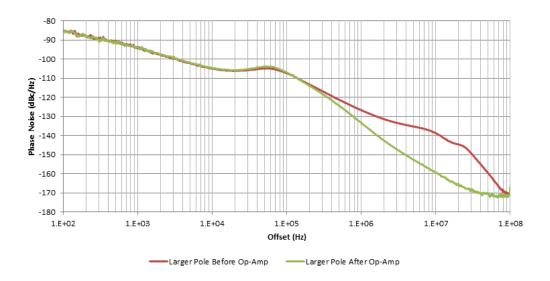

| CHAPTER 10 FUNDAMENTALS OF FRACTIONAL DIVIDERS                     | 71  |

| PLL LOOP THEORY                                                    | 79  |

| PLL LOOP THEORYCHAPTER 11 INTRODUCTION TO LOOP FILTER COEFFICIENTS | 81  |

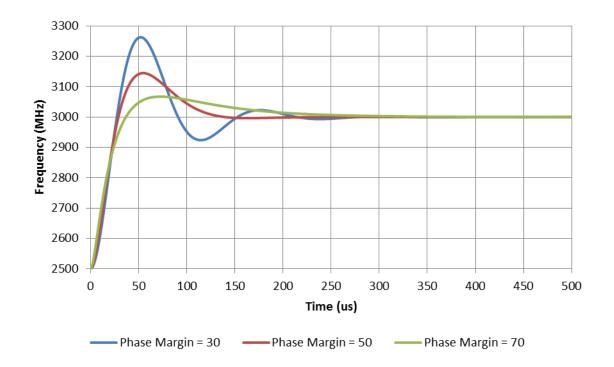

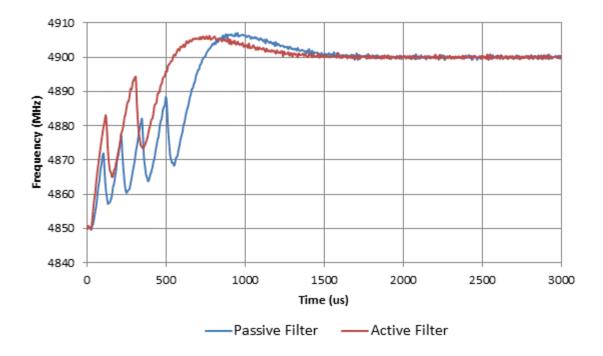

| CHAPTER 12 INTRODUCTION TO PLL TRANSFER FUNCTIONS AND NOTATION     |     |

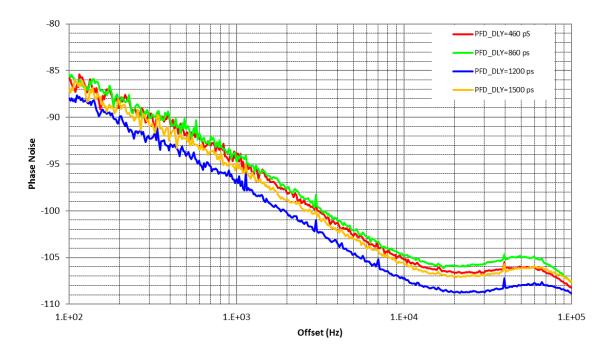

| CHAPTER 13 PLL MODULATION, DEMODULATION, AND CLOCK CLEANING        |     |

| CHAPTER 14 STABILITY OF PLL LOOP FILTERS                           |     |

| CHAPTER 15 A SAMPLE LOOP FILTER ANALYSIS                           |     |

| SPURS                                                              | 110 |

| CHAPTER 16 DIRECT SPURS                                            | 121 |

| CHAPTER 17 MODULATED SPURS                                         |     |

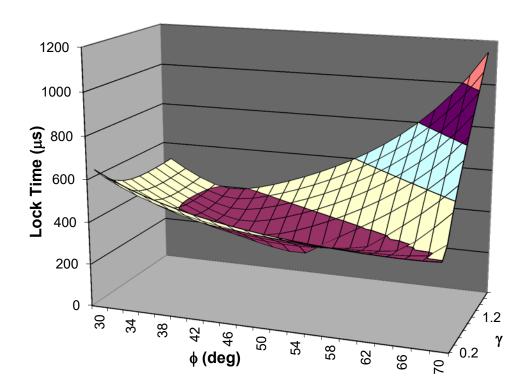

| CHAPTER 18 MODULATED CROSSTALK SPURS                               |     |

| CHAPTER 19 PHASE DETECTOR SPURS AND THEIR CAUSES                   |     |

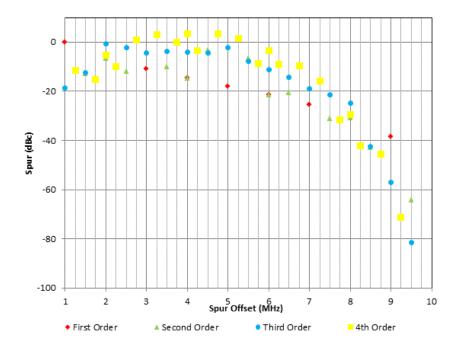

| CHAPTER 20 FUNDAMENTALS OF FRACTIONAL SPURS                        |     |

| CHAPTER 21 DELTA SIGMA FRACTIONAL SPURS                            |     |

|                                                                    |     |

| PHASE NOISE                                                        | 183 |

| CHAPTER 22 OSCILLATOR PHASE NOISE                                  | 185 |

| CHAPTER 23 PHASE NOISE OF INPUT PATH, CHARGE PUMP, AND DIVIDERS    |     |

| CHAPTER 24 PHASE NOISE OF PASSIVE LOOP FILTERS                     |     |

| CHAPTER 25 PHASE NOISE OF ACTIVE LOOP FILTERS                      |     |

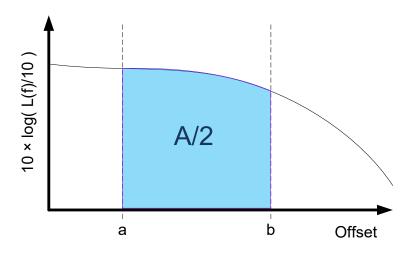

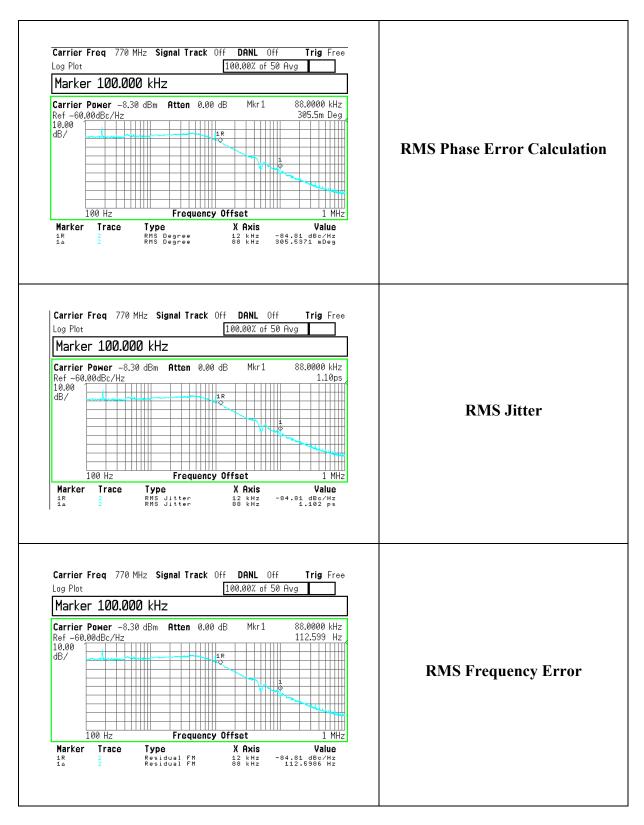

| CHAPTER 26 INTEGRATED PHASE NOISE QUANTITIES                       |     |

| CHAPTER 27 A SAMPLE PLI. PHASE NOISE ANALYSIS                      | 236 |

| TRANSIENT RESPONSE                                                        | <u> 245</u> |

|---------------------------------------------------------------------------|-------------|

| CHAPTER 28 TRANSIENT RESPONSE OF PLL FREQUENCY SYNTHESIZERS               | 247         |

| CHAPTER 29 IMPACT OF PFD DISCRETE SAMPLING EFFECTS ON THE TR              |             |

| RESPONSE                                                                  | 267         |

| CHAPTER 30 VCO DIGITAL CALIBRATION TIME FOR INTEGRATED VCOs               | 278         |

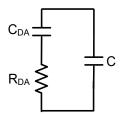

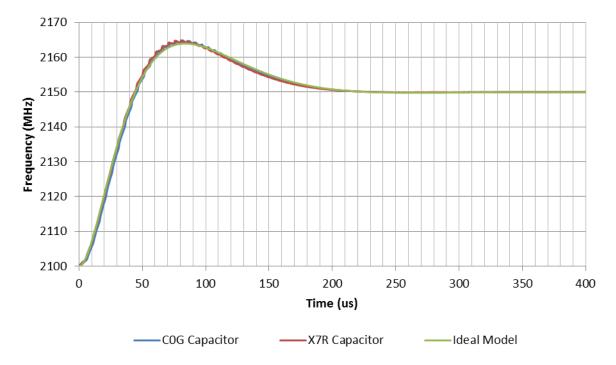

| CHAPTER 31 IMPACT OF CAPACITOR DIELECTRIC ABSORPTION AND RAILING          | ON THE      |

| TRANSIENT RESPONSE                                                        | 286         |

| CHAPTER 32 USING FASTLOCK AND CYCLE SLIP REDUCTION                        | 290         |

|                                                                           |             |

|                                                                           |             |

| LOOP FILTER DESIGN FUNDAMENTALS CHAPTER 33 CONCEPTS OF LOOP FILTER DESIGN | 297         |

| CHAPTER 33 CONCEPTS OF LOOP FILTER DESIGN                                 | 299         |

| CHAPTER 34 CHOOSING THE LOOP BANDWIDTH                                    |             |

| CHAPTER 35 OPTIMAL CHOICES FOR PHASE MARGIN                               |             |

| CHAPTER 36 OPTIMAL CHOICES FOR GAMMA OPTIMIZATION PARAMETER               | 314         |

| CHAPTER 37 CHOOSING FILTER ORDER AND POLE RATIOS                          | 322         |

|                                                                           |             |

|                                                                           |             |

| EQUATIONS FOR PLL DESIGN                                                  |             |

| CHAPTER 38 EQUATIONS FOR A PASSIVE SECOND ORDER LOOP FILTER               |             |

| CHAPTER 39 EQUATIONS FOR A PASSIVE THIRD ORDER LOOP FILTER                |             |

| CHAPTER 40 EQUATIONS FOR A PASSIVE FOURTH ORDER LOOP FILTER               |             |

| CHAPTER 41 FUNDAMENTALS OF PLL ACTIVE LOOP FILTER DESIGN                  |             |

| CHAPTER 42 ACTIVE FILTER FROM DIFFERENTIAL PHASE DETECTOR OUTPUTS         |             |

| CHAPTER 43 PARTIALLY INTEGRATED LOOP FILTERS                              |             |

| CHAPTER 44 SWITCHED AND MULTIMODE LOOP FILTER DESIGN                      |             |

| CHAPTER 45 ROUNDING TECHNIQUES FOR LOOP FILTER COMPONENTS                 | 426         |

|                                                                           |             |

|                                                                           |             |

| ADDITIONAL TOPICS                                                         |             |

| CHAPTER 46 PLL LOCK DETECT                                                |             |

| CHAPTER 47 IMPEDANCE MATCHING ISSUES AND TECHNIQUES FOR PLLS              |             |

| CHAPTER 48 PLL DEBUGGING TECHNIQUES                                       | 461         |

| CHAPTER 49 SOLUTIONS TO HIGHER ORDER POLYNOMIAL EQUATIONS                 | 467         |

|                                                                           |             |

| CURRY EMENTAL INFORMATION                                                 | 455         |

| SUPPLEMENTAL INFORMATION                                                  |             |

| GLOSSARY                                                                  |             |

| SYMBOLS AN ABBREVIATIONS                                                  |             |

| SOFTWARE RECOMMENDATIONS                                                  |             |

| OTHER WEBSITES                                                            |             |

| COMMONLY USED REFERENCES                                                  |             |

| I PRINTS                                                                  | 44          |

## **PLL Basics**

#### Chapter 1 Basic PLL Overview

#### Introduction

The *PLL* (Phased Locked Loop) has been around for many decades. Some of its earliest applications included keeping power generators in phase and synchronizing to the sync pulse in a TV set. Other applications include recovering a clock from asynchronous data and demodulating an FM modulated signal. Although these are legitimate applications of the PLL, this book focuses mainly on the use of a PLL to generate a stable output frequency. In this situation, the PLL starts with a fixed and stable input frequency and this is used to generate one or more output frequencies. Components that generate a tunable output frequency directly typically are not as stable or low noise as a fixed frequency input, so by using negative feedback as is employed in a PLL, it is possible to get a tunable frequency that has both good accuracy and good noise performance.

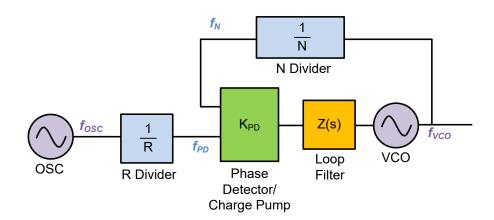

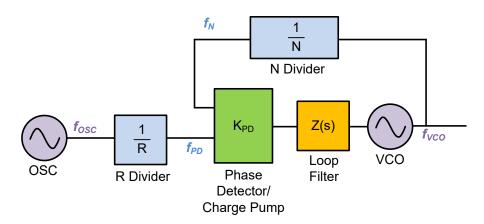

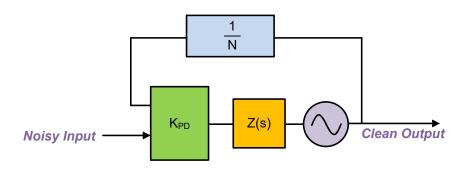

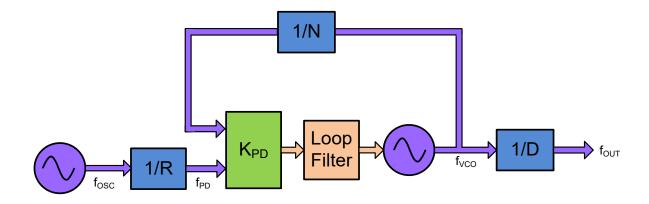

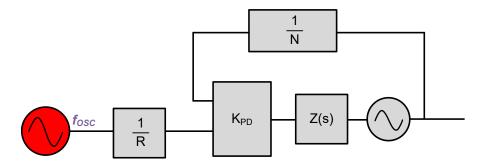

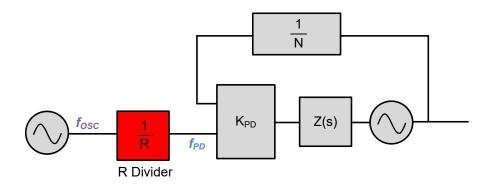

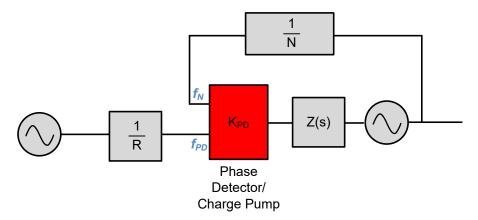

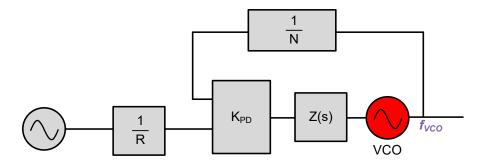

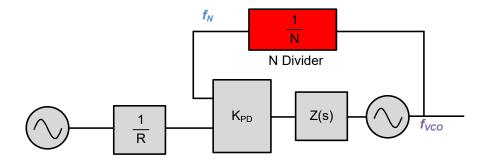

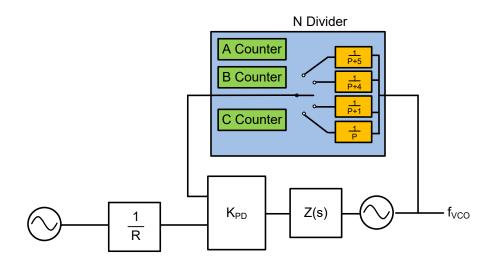

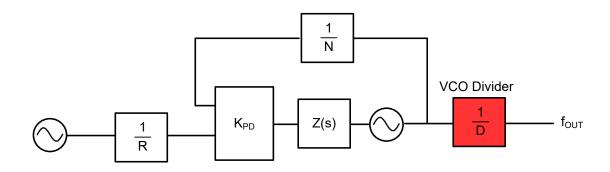

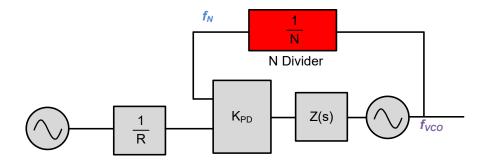

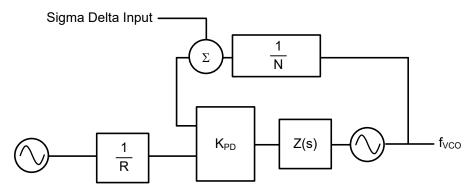

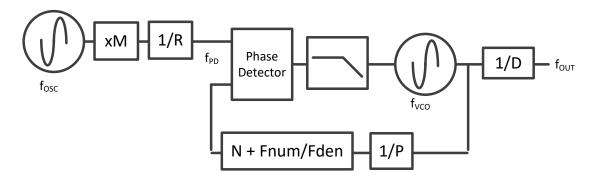

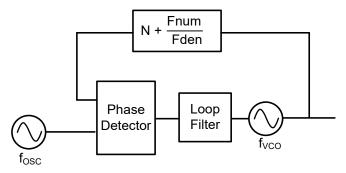

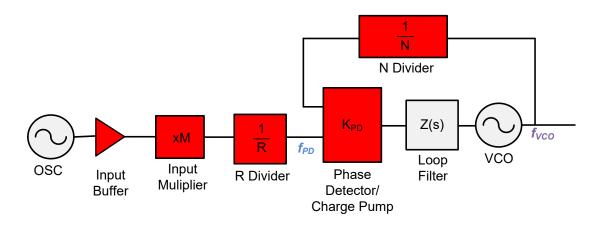

**Figure 1.1** *The Basic PLL*

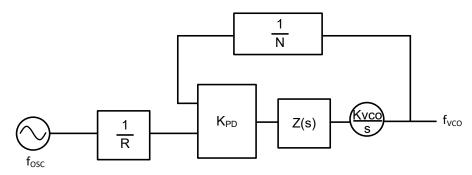

#### **PLL Structure and Frequencies**

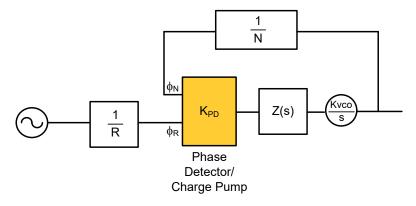

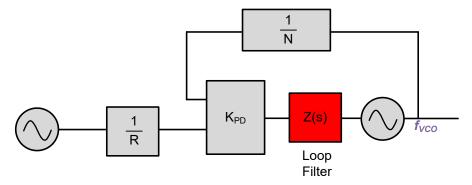

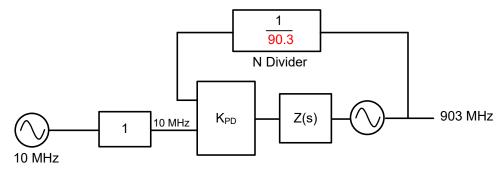

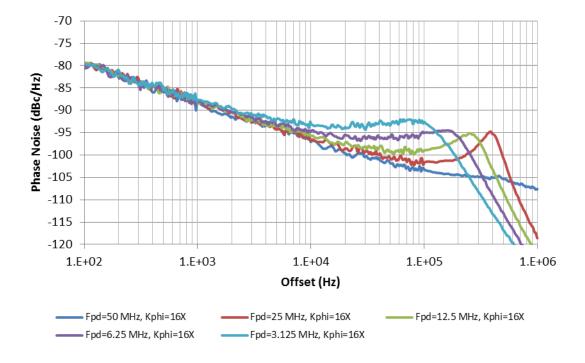

The PLL starts with a stable input frequency ( $f_{OSC}$ ). This frequency is typically fixed and very stable over temperature and process. The R divider reduces this frequency to the phase detector frequency ( $f_{PD}$ ). The phase-frequency detector then compares the phase of the R divider ( $f_{PD}$ ) with the phase of the N divider ( $f_N$ ) and produces current correction pulses that have a duty cycle that is proportional to the phase error between the two inputs to the phase detector. These pulses can be sourcing  $K_{PD}$  current, sinking  $K_{PD}$  current, or off (tri-state). In later chapters, the charge pump is discussed in more depth, but for most practical purposes, it can be treated as an analog current source that outputs a current of magnitude  $K_{PD}$  times the phase error as presented to the phase detector. These current correction pulses then go through a low pass filter called the loop filter, which has a current to voltage transfer function Z(s). The loop filter is typically implemented with discrete components, but can also be integrated on silicon or in the digital domain. The loop filter is application specific and much of this book is devoted to the art of loop filter design. The output voltage of the

loop filter then is used to steer the output frequency of the VCO (Voltage Controlled Oscillator). The VCO is a voltage to frequency converter and has a proportionality constant of  $K_{VCO}$ . The output of the VCO then goes through the N divider and is divided down to an input of the phase detector,  $f_N$ . The phase detector compares the input phases and will cause both inputs to be the same frequency and phase in the steady state and the VCO frequency will be as follows:

$$f_{VCO} = \frac{N}{R} \cdot f_{OSC} \tag{1.1}$$

The N divider value can be changed in order to produce a range of VCO frequencies that have the same frequency accuracy as the crystal. In some applications, there is no need for a VCO divider and one can use the direct VCO output. When a range is specified, one typically specifies a channel spacing  $f_{CH}$  for the spacing between the frequencies. It is usually desirable to maximize the phase detector frequency, which means that it would be chosen equal to the channel spacing in this case, unless there were some other restrictions with the device that would cause it to be chosen to be lower.

In the case that the output frequency of the PLL is to be fixed, the choice of the N divider value may not be intuitively obvious as there are many choices. In this case, it is typically best to choose the N divider as small as possible to maximize the phase detector frequency in order get the best noise performance.

$$\frac{N}{R} = \frac{f_{VCO}}{f_{OSC}} \tag{1.2}$$

Since the output frequency and input frequency are both known quantities, the right hand side of this equation is known and can be reduced to a lowest terms fraction. Once this lowest terms fraction is known, the numerator is the N value and the denominator is the R value. If this solution results in an N divider ratio that the PLL cannot do or phase detector frequency that is too high for the PLL to handle, then multiply both N and R by some integer until it is not an issue. In the case where there is freedom to choose the input reference frequency, it is best to choose it so that it has a lot of common factors with the output frequency so that the N value is as small as possible.

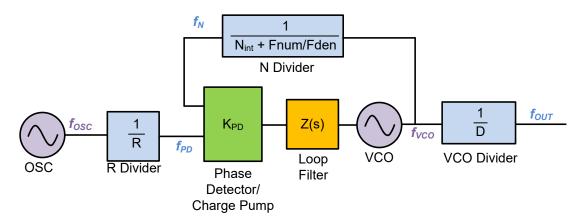

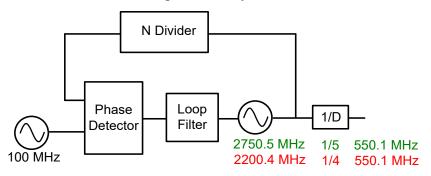

It is also possible for the dividers to be fractional. Fractional N dividers are somewhat common and fractional values for the R and D divider could arise in a situation if there was a frequency doubler at the input or output. In general, the output frequency is as follows.

$$f_{OUT} = \frac{f_{VCO}}{D} = \frac{N}{R \cdot D} \cdot f_{OSC} \tag{1.3}$$

#### Using an Output Divider to Extend the Frequency Range

Fractional synthesizers with output dividers are commonplace in today's market. The broad host of applications for PLLs makes it desirable for the VCO to be able to tune over a wide frequency. However, there is a trade-off for VCOs between tuning range and noise performance. A common technique used is to combine the VCO with the output divider to produce this wide range.

For instance, one can combine an octave VCO with a divider that does powers of 2 to cover a continuous range. For instance, consider a VCO that can tune 2-4 GHz combined with a divider that can divide by 1, 2, 4, 8, 16, and 32. The divide by 1 can create 2-4 GHz, the divide by 2 can create 1-2 GHz, and the divide by 4 can create 0.5-1 GHz, and so on until the entire range of 62.5 – 4000 MHz is covered.

An alternative approach is to use a higher frequency divider of lesser tuning range and accept a small frequency hole to get continuous coverage. For instance, one could take a divider that can do 1, 2, 3, 4, 5, ... 20 and combine with a VCO that tunes from 4-5 GHz to get frequency coverage from 200 MHz - 1 GHz, then with a divide by one and divide by 2, this can be extended to 0.5 - 2 GHz. Extending on this concept, one could take a programmable divider of 1, 2, 4, 8, 16, and 32 to extend this tuning range to 31.25 - 2000 MHz with no gaps in coverage for VCO.

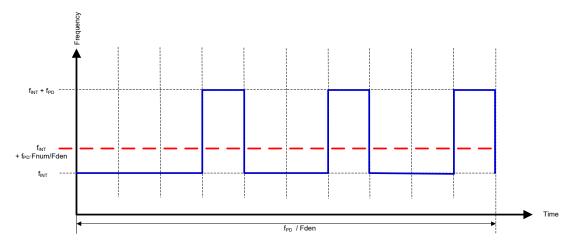

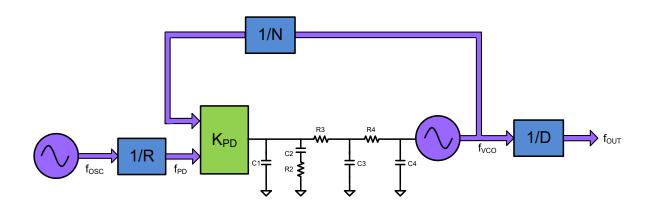

#### Fractional PLL N Example with VCO Divider

The model in Figure 1.3 is sufficient for understanding the fundamentals of PLLs, but for a more complete model, one also needs to allow for a VCO divider as shown in Figure 1.2. The VCO divider is often used in cases where it is easier to integrate a higher frequency VCO and then divide down the frequency.

**Figure 1.2** Fractional N PLL with VCO Divider

#### Industry Impact on PLL Terminology

The term PLL technically refers to the entire system shown in Figure 1.1; however, challenges with integrating the VCO and input signal have caused industry to redefine the term. In industry, often times when one buys a "PLL" chip from semiconductor manufacturers, it only includes the dividers and charge pump. When capability to integrate VCOs came along, semiconductor vendors did not want to call this a PLL because they wanted it clear that the VCO was also included, so this is often called a *frequency synthesizer*. Integration of the input reference is less common at the time of writing this book and is assumed that this is supplied external to the PLL chip.

#### **PLL Applications**

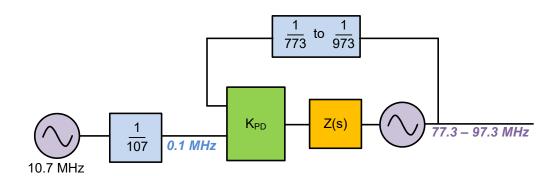

#### Integer PLL FM Radio

Starting with a more basic example, consider an FM radio receiver where we want to generate a range of frequencies of 88, 88.1, 88.2, ... to 108 MHz. Assume that this is done by down converting the received signal to 10.7 MHz. This means that the PLL frequency would be 77.3 to 97.3 MHz with a channel spacing of 0.1 MHz.

Figure 1.3 Integer PLL Example

#### Clock Recovery Applications

One variation of a jitter cleaning application is a clock recovery application. In wired communications, a clock is typically used to send data. It is undesirable to require an extra wire to just send the clock. In addition to this, skew between the data and clock wires becomes a concern. One approach that can be used is to embed the clock with the data and then use a PLL to recover the clock. The data should have a sufficient number of transitions in order to get the PLL to lock to the clock frequency and there are encoding methods that are designed to do this. This also may put some special requirements on the phase detector. The approach is to feed the data with embedded clock into the input reference of the PLL and then the recovered clock is attained at the VCO output.

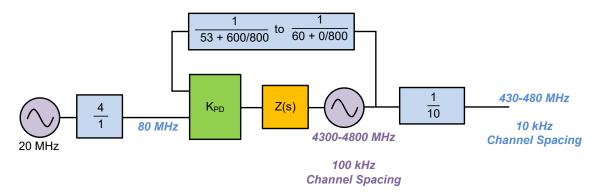

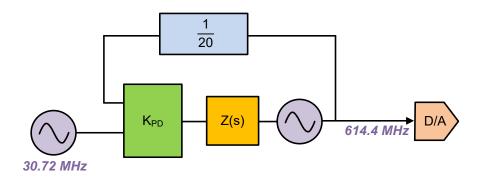

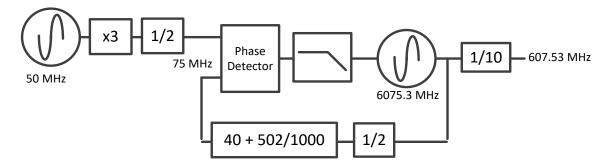

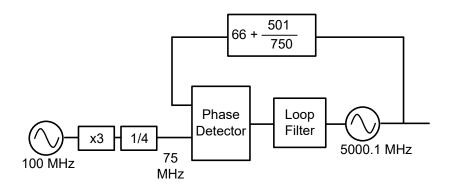

#### Fractional PLL Two Way Radio

One example of a PLL synthesizer in fractional mode using the VCO divider could be a two way radio that generates 430-480 MHz with a channel spacing of 10 kHz from a 20 MHz input frequency. Assume that the device chosen has an input multiplier of four and an integrated VCO that tunes from 4300-5300 MHz. Also assume that this VCO has a divider of ten after it. Figure 1.4 shows how this can be done.

Figure 1.4 Two Way Radio Example

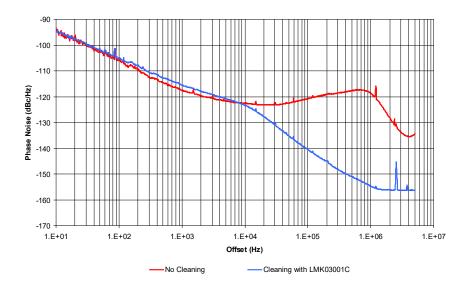

#### Jitter Cleaner Applications

In this type of applications, the PLL can be used to improve the noise of a noisy input signal. This clock may be noisy for intentional reasons or for non-intentional reasons. For instance, sometimes the clock is intentionally made noisy in order to reduce the radiated energy for EMI requirements.

For whatever reason that the clock is dirty, the idea is to use this as the input reference for the PLL and configure the PLL such that it filters out this noise and replaces it with just the noise of the PLL. The PLL can be used to scale the input frequency as well.

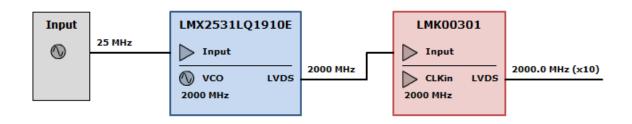

**Figure 1.5** Example of a PLL used to clean a Noisy Input

#### Clocking Applications

In some cases, all that is required is a fixed output frequency, such as the case of clocking an A/D converter. Even though there might be fixed crystal frequencies that have pretty good performance, they tend to be at lower frequency. By using a PLL, one can generate much higher fixed frequencies.

**Figure 1.6** Example of PLL Clocking an A/D Converter

#### **Conclusion**

The PLL can be used to generate a stable output frequency from a fixed input frequency using a phase detector, charge pump, VCO, and dividers. The output frequency can be adjusted by changing the divider values. The output frequency can be a fixed frequency or a tunable range of frequencies. There is a broad range of applications for the PLL.

#### **Chapter 2** A Brief Overview of PLL Performance Characteristics

#### Introduction

The performance characteristics of the PLL are involved and optimizing them involves many trade-offs. This chapter is intended to give the reader a simplified high level overview of some of these key concepts. Among these concepts are the loop characteristics, phase noise, spurs, and transient response.

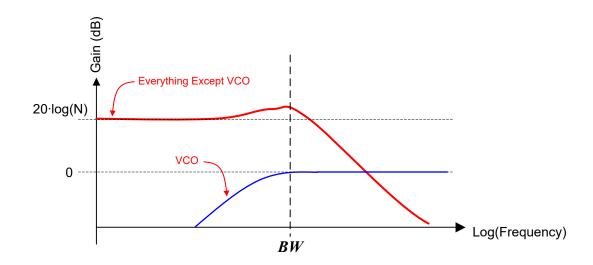

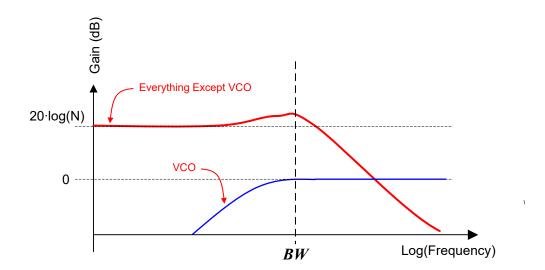

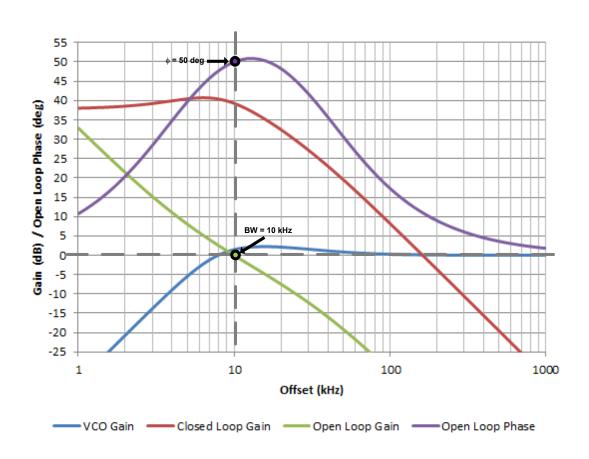

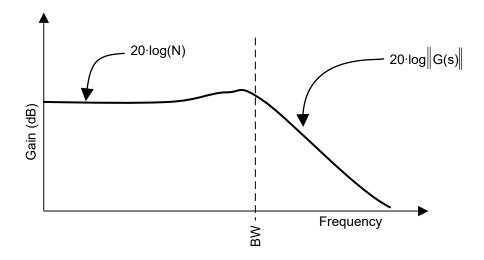

#### **Loop Characteristics**

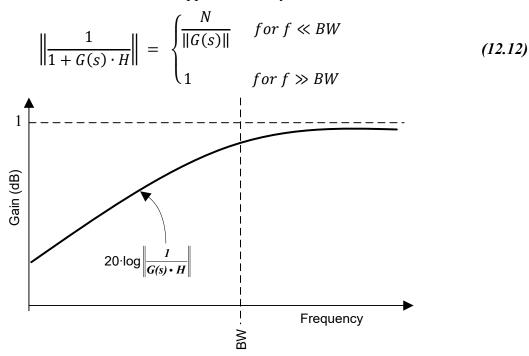

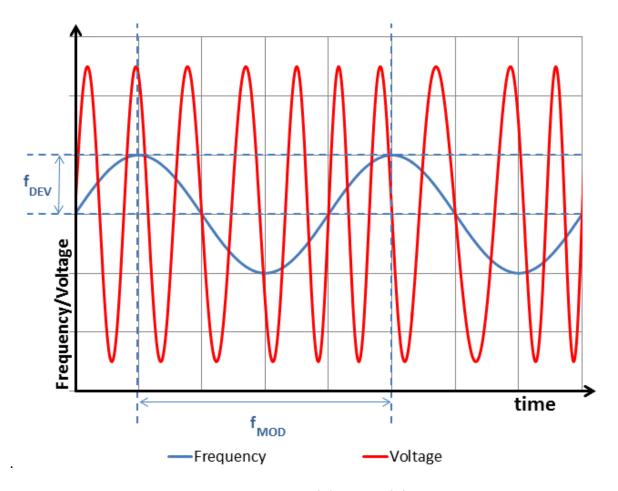

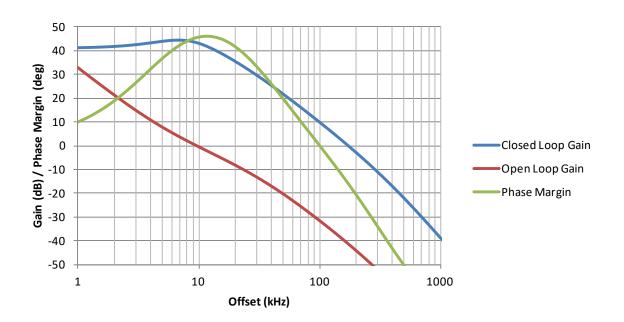

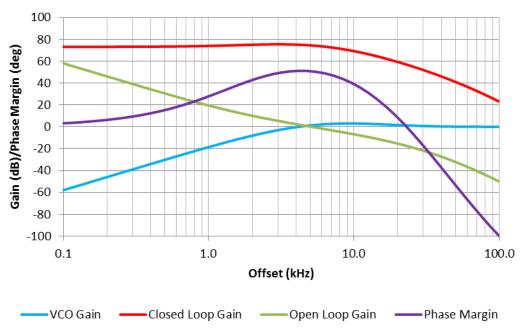

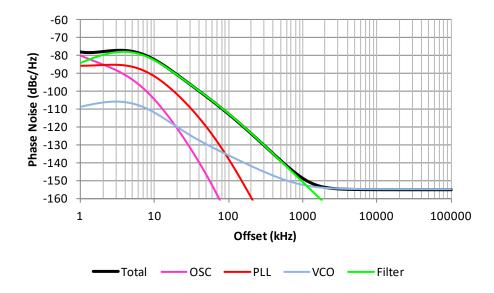

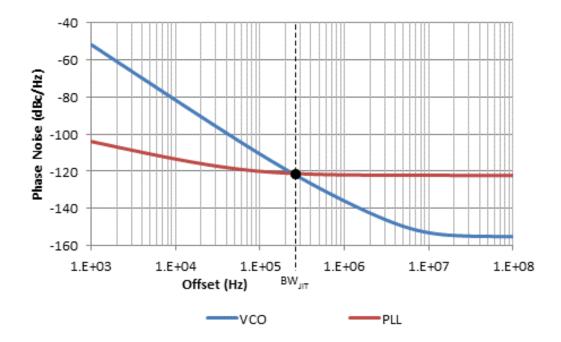

The closed loop transfer function from the input of the phase detector to the VCO output is determined by the N divider, VCO gain, charge pump gain, and the loop filter. This is a low pass function with a cutoff frequency called the loop bandwidth (BW). The choice of the loop bandwidth is the most critical design parameter and has a significant impact on phase noise, spurs, and the switching speed of a PLL. For all noise and spurs not coming from the VCO, this transfer function multiplies up the phase noise within the loop bandwidth and then suppresses then the filter attenuation begins to kick in after the loop bandwidth. For the VCO, the noise is suppressed below the loop bandwidth frequency and unshaped above the loop bandwidth frequency.

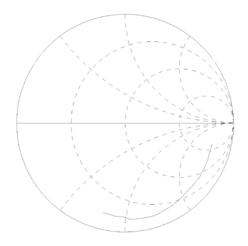

**Figure 2.1** *PLL Noise Transfer Functions*

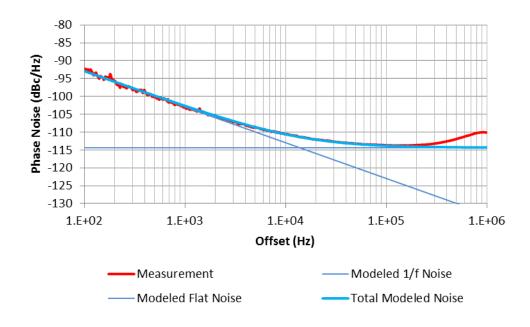

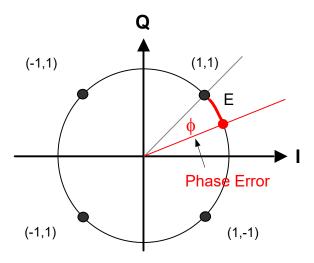

#### **PLL Phase Noise**

In addition to the desired signal, a PLL will also produce undesired noise. This noise can be thought of as noise on the phase of the output and is therefore called *phase noise*. In the frequency domain, this is more commonly thought of as the density of the noise power relative to the carrier power and measured in dBc/Hz.

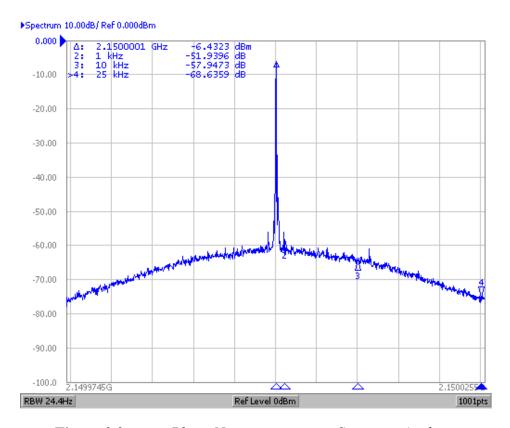

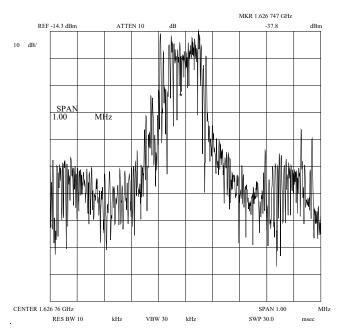

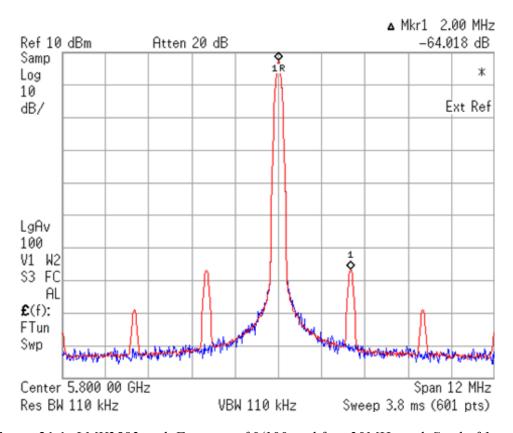

Figure 2.2 Phase Noise as seen on a Spectrum Analyzer

A spectrum analyzer is a piece of test equipment that can be used to measure phase noise and displays noise power vs. frequency as shown in Figure 2.2. In this case, the measurement needs to be adjusted by  $10 \cdot \log(Resolution Bandwidth)$ , which would be  $10 \cdot \log(24.4) = 13.8$  dB. For instance, the phase noise at 10 kHz would be -57.9 - 13.8 = -71.7 dBc/Hz. Sometimes spectrum analyzers have correction factors that can account for a few dB. Sometimes there is a marker noise function to help account for this.

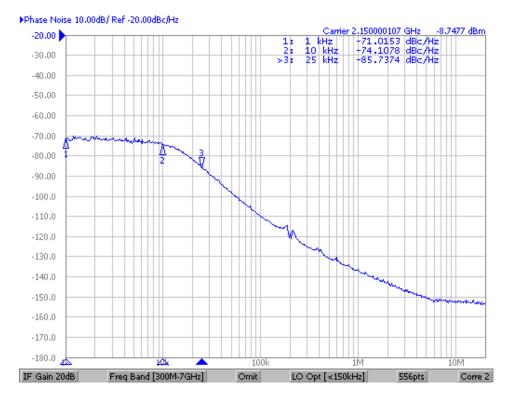

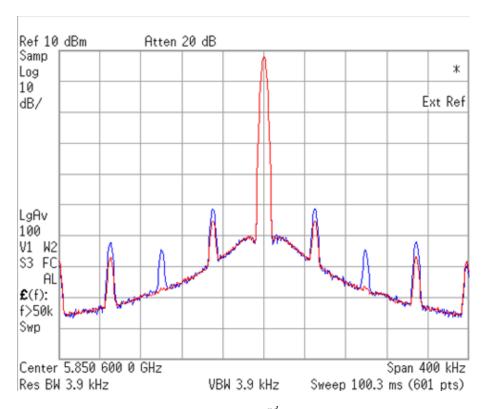

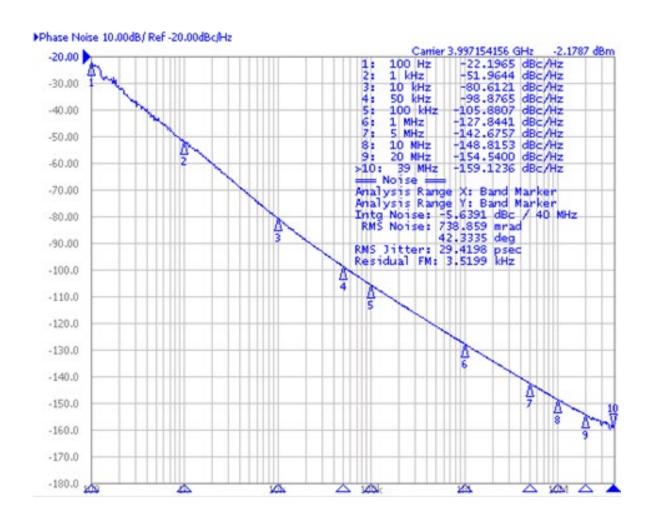

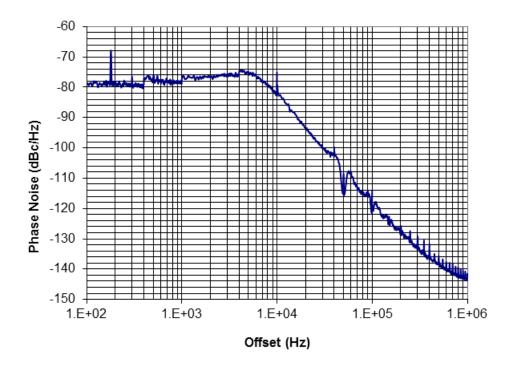

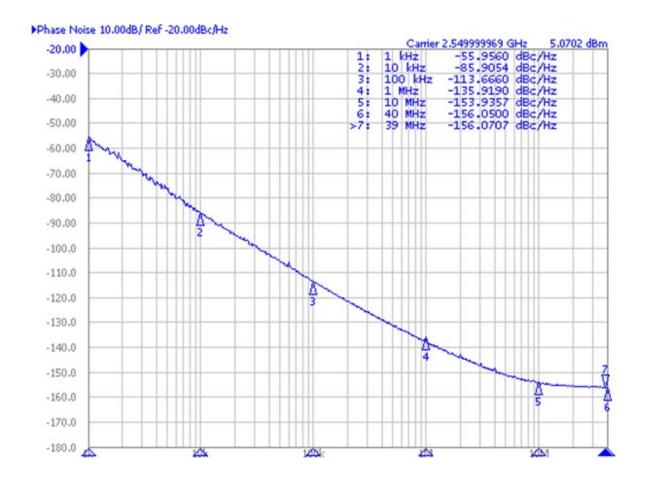

The *phase noise analyzer* tracks the VCO frequency and then plots the phase noise as a function of offset. Figure 2.3 shows the same frequency and setup condition as shown in Figure 2.2 with the exception that the instrument was switched from spectrum analyzer mode to phase noise analyzer mode. Note that the phase noise at 10 kHz is -74.1 dBc/Hz, which is better and more accurate than the measurement in spectrum analyzer mode. Part of this reason could be due to the spectrum analyzer correction factor.

**Figure 2.3** Phase Noise as Seen on a Phase Noise Analyzer

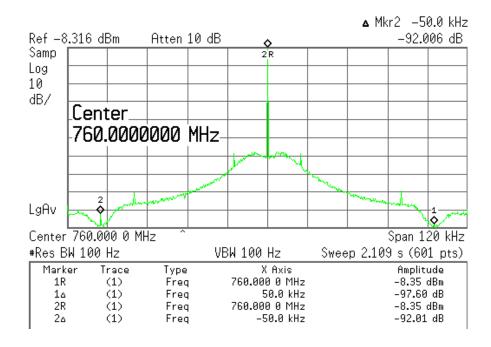

#### **Spurs**

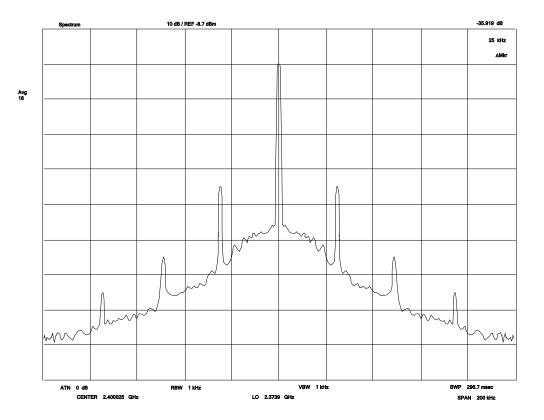

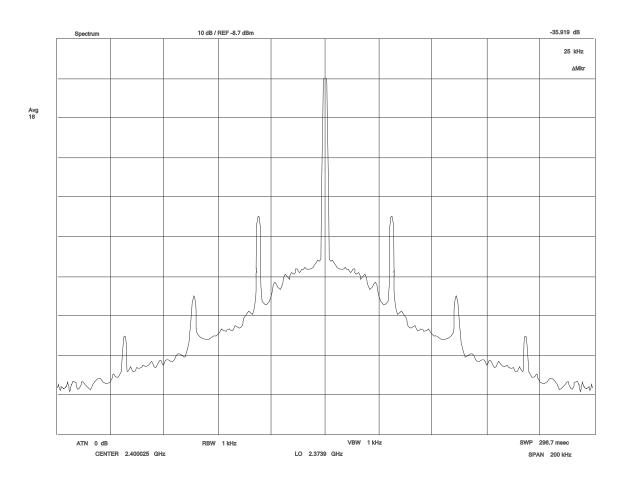

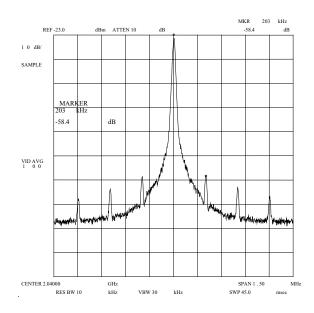

Spurs can be thought of as noise that is concentrated at a specific offset from the carrier as shown in Figure 2.4. These are typically measured in dBc with a spectrum analyzer. There are many kinds of spurs and they can have multiple causes, but most of them occur at very predictable offsets. Spurs have a tendency to occur at multiples of the phase detector frequency, input reference frequency, channel spacing, and fractions of the channel spacing.

Figure 2.4 Spurs as seen on a Spectrum Analyzer

#### **Impact of Dividers on Phase Noise and Spurs**

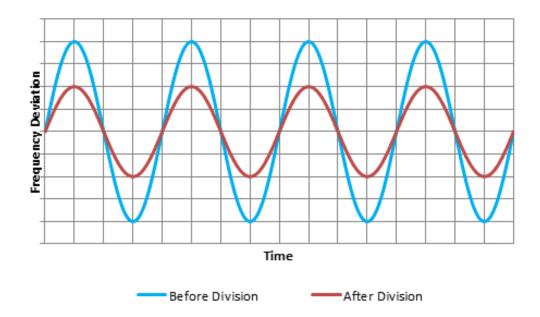

It is getting more common, especially with devices that include the integrated VCO, to have a divider after the VCO to extend the frequency range. This divider has a significant impact on the phase noise and spurs. For the phase noise going through a divider of value D, the phase noise is reduced by  $20 \cdot \log(D)$ . So a divide by two translates to a theoretical 6 dB improvement in phase noise. In practice, this 6 dB is typically realized for closer in offsets, but at farther out offsets, the noise improvement may be less due to the divider noise and the fact that some of the noise far-out might not be correlated to the carrier frequency. In regards to spurs, a divider does not change the offset frequency and theoretically reduces the magnitude by  $20 \cdot \log(D)$ . Furthermore, because the offset frequency is not changed, this often allows the user to increase the channel spacing at the VCO by a factor of D to achieve the same channel spacing, which theoretically pushes the spurs to farther offsets, making them easier to filter. This benefit is seen in practice, although there are certain spurs that are not improved as much as theoretically predicted due to crosstalk.

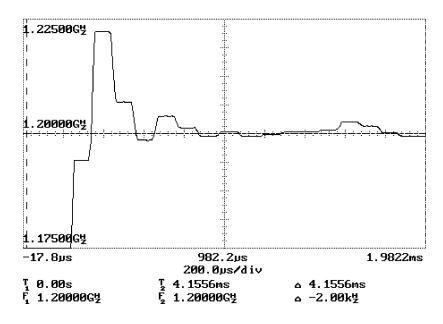

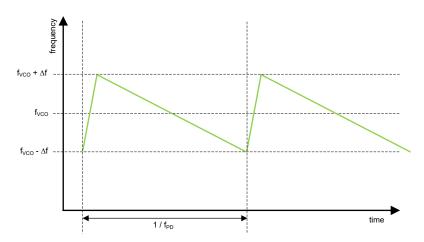

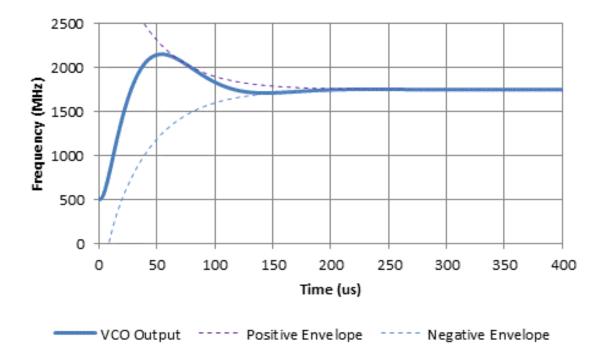

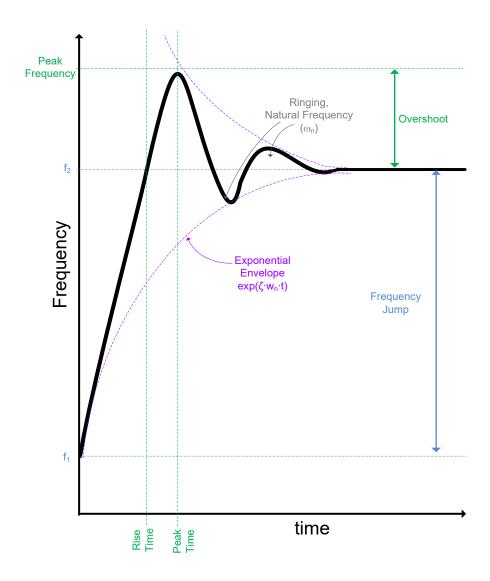

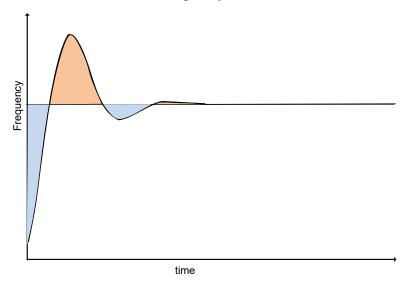

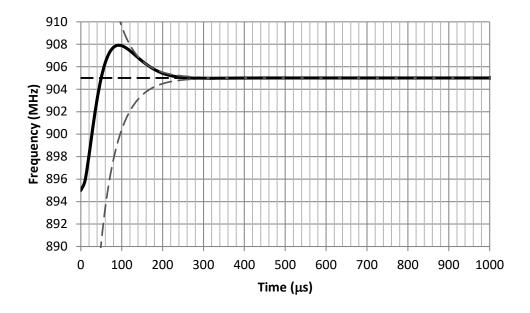

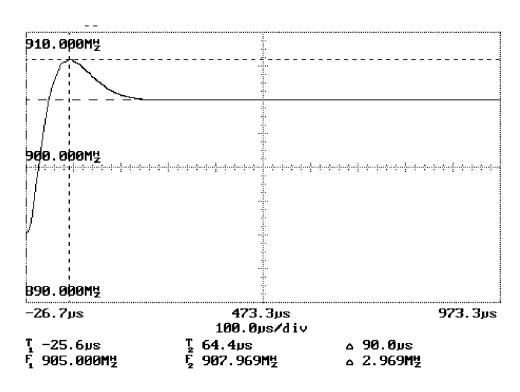

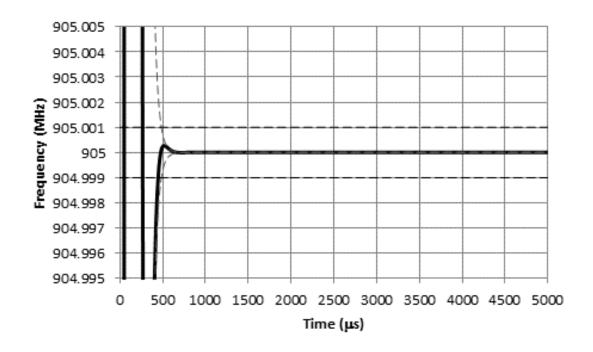

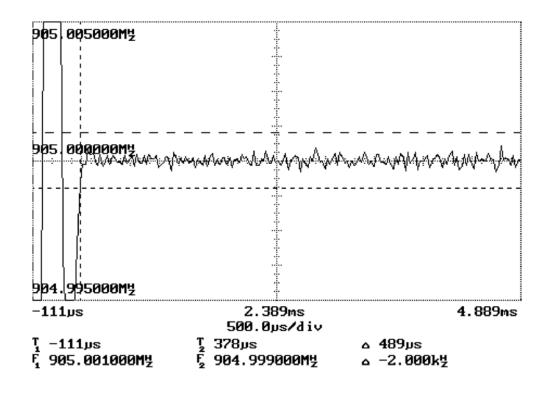

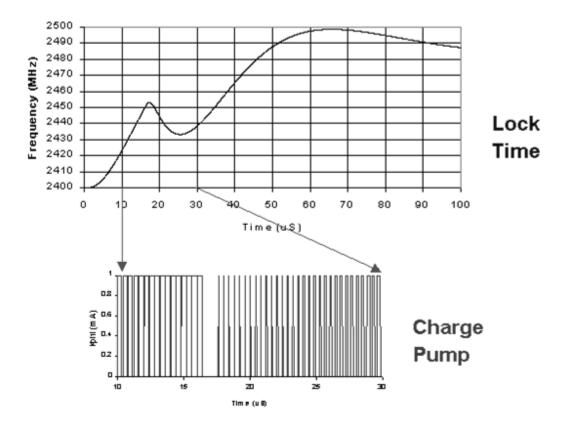

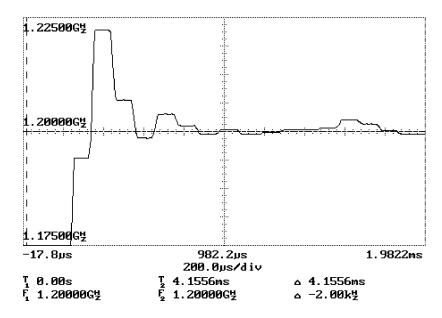

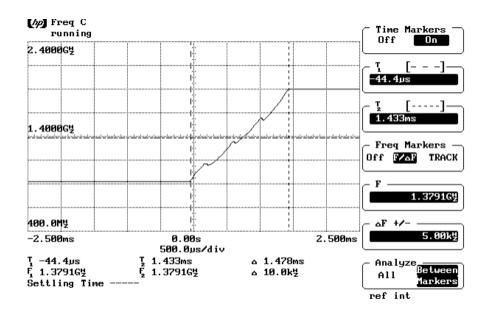

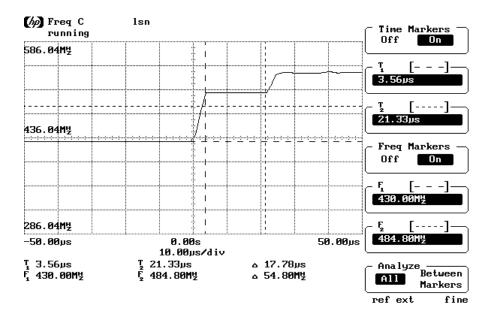

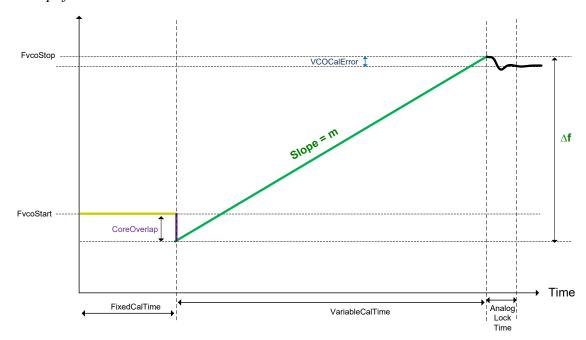

#### **Transient Response and Lock Time**

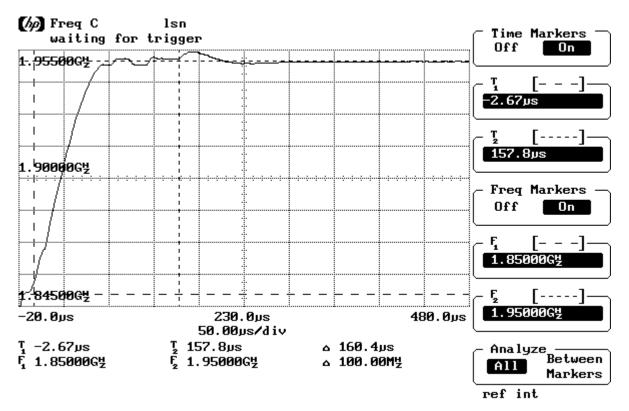

The *lock time* is typically thought of as the amount of time it takes the PLL to settle to a given *frequency tolerance* after the N divider value is changed. The lock time definition can be expanded to included cases where there is a phase disturbance or when the tolerance is expressed as a phase error instead of a frequency error.

Figure 2.5 PLL Transient Response

#### Conclusion

Phase noise, spurs, and lock time are key performance characteristics and are all impacted dramatically by the loop characteristics, especially the loop bandwidth. A lower loop bandwidth tends to improve spurs and far out phase noise, but degrades the lock time, and the opposite is true of a wide loop bandwidth, although it may improve close-in phase noise depending on the noise quality of the input reference. Different applications may have different requirements, so there is no single PLL design that is optimal for every application.

#### **Chapter 3** Impact of the PLL Performance on the System

#### Introduction

Phase noise, spurs, and lock time are critical performance characteristics of a PLL. This chapter discusses the impact of these on the performance of a typical system.

#### **Typical Wireless Receiver Application**

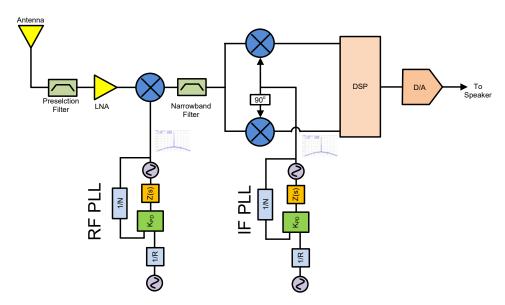

Figure 3.1 Typical PLL Receiver Application

#### **General Receiver Description**

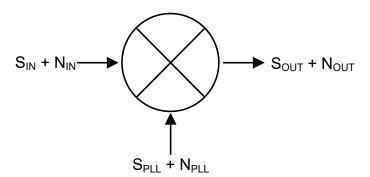

Figure 3.1 shows a typical receiver application using a PLL. Several different channels, each with a unique frequency, are received by the antenna and allowed to pass through the preselection filter. The signal is them amplified with a *low noise amplifier (LNA)* and downconverter with the *RF (Radio Frequency)* PLL to a fixed *IF (Intermediate Frequency)* signal. In other words, the frequency of the RF PLL is adjusted such that the difference of the desired channel frequency and the RF PLL frequency is always the same. This signal then goes through the narrow filter that is at this fixed value in order to remove the unwanted mixer image as well as mixing products formed by undesired channels that pass through the preselection filter. The IF PLL mixes this frequency down to baseband so that the information on the signal can be attained.

Other than the obvious parameters of a PLL such as cost, size, and current consumption, the phase noise, reference spurs, and lock time are important to the performance of the system and will be discussed in more detail.

#### Phase Noise, Spurs, and Lock Time as They Relate to This System

Phase noise at lower offsets from the carrier has a tendency to increase bit error rates and degrade the signal to noise ratio of the system. Many systems that care about integrated phase noise that can be impacted heavily by the lower offset phase noise. Phase noise at farther offsets can mix with other signals from other users in the system in order to create undesired noise products.

Spurs are noise concentrated at discrete offset frequencies from the carrier. These offset frequencies are typically multiples of the channel spacing. These offset frequencies are typically exactly at frequencies where an adjacent user of the system can be and can mix down to create undesired noise products that fall on the desired carrier frequency.

Lock time is the time that it takes for the PLL to change frequencies. This can be for applications that scan over a frequency band or do frequency hopping. When the PLL is switching frequencies, no data can be transmitted, so lock time of the PLL must lock fast enough as to not slow the data rate. Lock time can also be related to power consumption. In some systems, the PLL only needs to be powered up when data is transmitted or received. During other times, the PLL and many other RF components can be off. If the PLL lock time is less, then that allows systems like this to spend more time with the PLL powered down and therefore current consumption is reduced. For other systems, the PLL need to scan over a range of frequencies and these applications tend to need faster PLL lock times.

#### **Analysis of Receiver System**

For the receiver shown in Figure 3.1, the PLL that is closest to the antenna is typically the most challenging from a design perspective, due to the fact that it is tunable and higher frequency. Since this PLL is tunable, there is typically a more difficult lock time requirement, which in turn makes it more challenging to meet spur requirements as well. In addition to this, the requirements on this PLL are also typically stricter because the undesired channels are not yet filtered out from the antenna.

The IF PLL has less stringent requirements, because it is lower frequency and also it is often fixed frequency. This makes lock time requirements easier to meet. There is also a tradeoff between lower spur levels and faster lock times for any PLL. So if the lock time requirements are relaxed, then the spur requirements are also easier to meet. The signal path coming to the second PLL has already been filtered, so typically the lock time and spur requirements are often less difficult to meet.

#### Example of an Ideal System with an Ideal PLL

For this example, assume all the system components are ideal. All mixers, LNAs and filters have 0 dB gain and noise figure. All filters are assumed to have an idea "brick wall" response. The PLL is assumed to put out a pure signal and have zero lock time.

| Parameter          | Value           | Units |

|--------------------|-----------------|-------|

| Receive Frequency  | 869.03 - 893.96 | MHz   |

| RF PLL Frequency   | 783.03 - 807.96 | MHz   |

| IF PLL Frequency   | 86              | MHz   |

| Channel Spacing    | 30              | kHz   |

| Number of Channels | 831             | n/a   |

| IF PLL Frequency   | 240             | MHz   |

**Table 3.1** *RF System Parameters*

The received channel will be one of the 831 channels. The channels will be designated 0 to 830, where channel 0 is at 869.03 MHz and channel 830 is at 893.96 MHz. Now suppose one wants to receive channel 453 at 888.62 MHz. This frequency comes in through the antenna, filter, and LNA and is presented to the first mixer. The RF PLL frequency is then programmed to 802.62 MHz. The output of the mixer is therefore the sum and difference of these two frequencies, which would be 1691.24 MHz and 86 MHz. The filter afterwards filters out the high frequency signal so that only the 86 MHz signal passes through. This 86 MHz signal is then down converted to baseband with the IF PLL frequency, which is a fixed 86 MHz.

#### Ideal System with a Non-Ideal PLL

Consider the effects of a non-zero lock time. Suppose that the RF PLL takes 1 ms to change frequencies and the IF PLL takes 10 ms to change channels. For this application, the fact that the IF PLL takes 10 ms to change channels really does not have any impact on system performance. What this means is that once the receiver is turned on, it takes an extra 10 ms to power up. Because the IF PLL never changes frequency, this is the only time this lock time comes into play. Now the 1 ms lock time on the RF PLL has a greater impact. If a person was using their cell phone and it was necessary to change the channel, then this lock time would matter. This might happen if the user was leaving a cell and entering another cell and the channel they were on was in use. Also, sometimes there is a supervisory channel that the cell phone needs to periodically switch to in order to receive and transmit information to the network. This is the factor that drives the lock time requirement for the PLL in the IS-54 standard, after which this example was modeled. The time needed to switch back and forth to do this needs to be transparent to the user and no data can be transmitted or received when the PLL is switching frequencies.

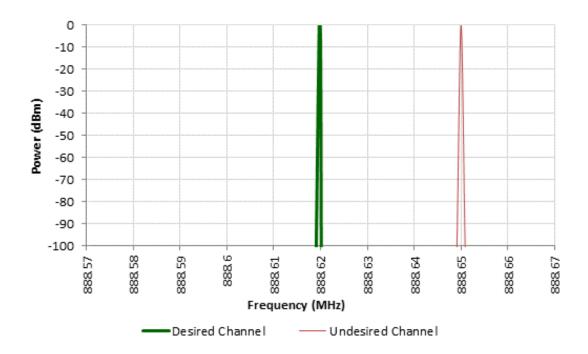

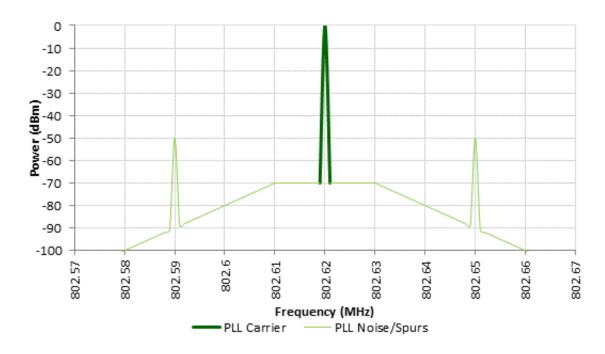

Now consider the impact of phase noise and spurs of the PLL. Suppose two signals, the desired channel to be received at 888.62 MHz, and an undesired channel at 888.65 MHz, as shown in Figure 3.2.

Figure 3.2 Output of the Preselection Filter

Assume that the RF PLL output has an output at 802.62 MHz with noise and spurs as shown in Figure 3.3.

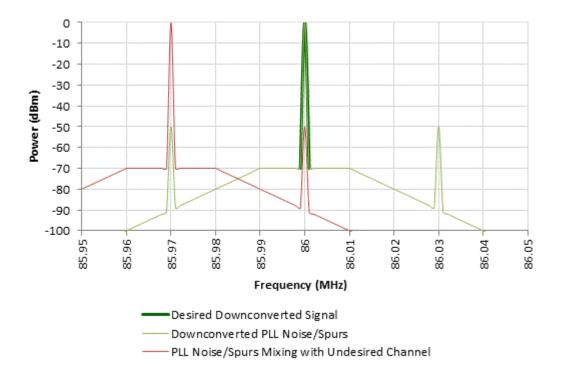

Figure 3.3 Signal with Noise from RF PLL

The desired output would be a pure 86 MHz tone, but the noise and spurs of the RF PLL mix with both the desired and undesired channels. One of the purposes of the narrowband filter is to remove noise and spurs, but the spur caused by the mixing of the 888.65 MHz undesired channel and the spur at 802.65 MHz lands exactly at 86 MHz and cannot be filtered as shown in Figure 3.4. Also, as no filter is perfect, some of the phase noise close to this 86 MHz signal will also pass through the narrowband filter.

Figure 3.4 Output Signal from Mixer

#### Conclusion

This chapter has investigated the impacts of phase noise, spurs, and lock time on system performance. These three performance parameters are greatly influenced by many factors including the VCO, loop filter, and *N* divider value. Of course it is desirable to minimize all three of these parameters simultaneously, but there are important trade-offs that need to be made. Applications where the PLL only has to tune to fixed frequency tend to be less demanding on the PLL because the lock time requirements tend to be very relaxed, allowing one to optimize more for spur levels. There is no one PLL design that is optimal for every application.

# PLL Building Blocks

**Chapter 4** Input Sources, Crystals, and Principles of Oscillation

#### Introduction

The PLL starts with the assumption that there is an input signal. This should be very accurate in frequency as any error is translated directly to the VCO. This signal can be a recovered clock, a frequency generated from another chip, or a signal generated by a crystal /crystal oscillator. Aside from the frequency of the input signal, characteristics such as phase noise, amplitude, and slew rate are also critical. This chapter discusses some important properties of recovered clocks, crystals, and crystal oscillators.

#### **Recovered Clocks**

When data is transmitted over a long distance, one technique is to serialize the data and embed the clock. By doing this, fewer wires are needed for transmission and issues with skew between the lines are eliminated. The descrializer then recovers the clock from the data and interprets the signal sent. Often times, recovered clocks do not have very good noise performance, but a PLL can be used to clean up the signal.

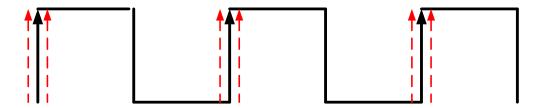

Figure 4.1 Recovered Clock Before and After Being Cleaned by a PLL

#### **Crystals and Crystal Oscillators**

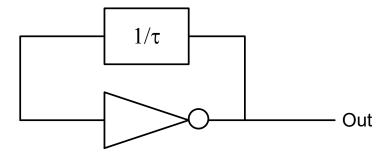

#### Principles of Oscillation

The general idea for an oscillator is to have an inverter with the output fed back to the input through a filter. Since it is not possible to filter without delay, this filter can also be thought of as a delay. In order for a circuit to oscillate, it must satisfy the following conditions known as the *Barkhausen criterion*.

- 1. The open loop gain at the oscillation frequency must be 1.

- 2. The phase of the open loop gain at the oscillation frequency, including the phase shift of the inverter must be a zero or some other multiple of 360 degrees.

The most basic oscillator is called the *ring oscillator*. This is basically a series of inverter with the output fed back to the input. A delay is added to set the frequency. If the gate delay of the inverter is significant, it adds to this delay. This delay can also be thought of as a filter. The only difference is that a filter produces a sine wave instead of a square wave. This circuit model works especially well for crystal oscillators and is very intuitive. The fundamental frequency of oscillation,  $f_{osc}$ , is easy to calculate once the delay,  $\tau$  is known.

$$f_{OSC} = \frac{1}{\tau} \tag{4.1}$$

Figure 4.2 A Typical Crystal Oscillator Diagram

Note that there is no input and the oscillator relies on noise to get it started. Once it does, the inverter sustains the oscillations. The startup time is governed by the gain of the inverter and the external components around it. One way to implement the delay is with a crystal.

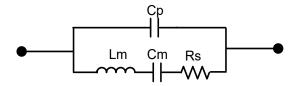

#### Crystal Element for Used in Oscillators

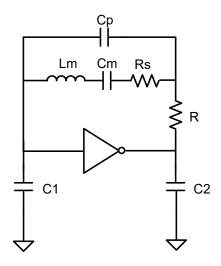

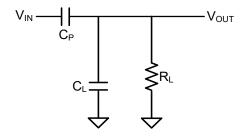

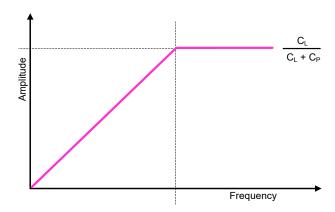

The crystal can be viewed as a filter with a very low bandwidth and high frequency accuracy with an equivalent circuit in Figure 4.3 with Lm (motional inductance), Cm (motional capacitance), Rs (series resistance), and Cp (parallel capacitance).

Figure 4.3 A Typical Crystal Oscillator Circuit

The impedance of the crystal is given by:

$$Z(s) = \frac{s^2 + s \cdot \left(\frac{Rs}{Lm}\right) + \left(\frac{1}{Lm \cdot Cm}\right)}{s \cdot Cp \cdot \left(s^2 + s \cdot \left(\frac{Rs}{Lm}\right) + \left(\frac{Cm + Cp}{Cm \cdot Lm \cdot Cp}\right)\right)}$$

(4.2)

The imaginary part of the numerator will never be zero **Rs**, but satisfying the following equation for series resonance will minimize the impedance.

$$s^2 + \left(\frac{1}{Lm \cdot Cm}\right) = 0 \tag{4.3}$$

$$\omega_{Series} = \sqrt{\frac{1}{Lm \cdot Cm}} \tag{4.4}$$

If we set the real part of the portion of the denominator in parenthesis equal to zero, we get the frequency for parallel resonance.

$$s^2 + \left(\frac{Cm + Cp}{Lm \cdot Cm \cdot Cp}\right) = 0 (4.5)$$

$$\omega_{Parallel} = \sqrt{\frac{Cm + Cp}{Lm \cdot Cm \cdot Cp}} = \frac{1}{\sqrt{Lm \cdot Cm}} \cdot \sqrt{1 + \frac{Cm}{Cp}} = \omega_{Series} \cdot \sqrt{1 + \frac{Cm}{Cp}}$$

(4.6)

The series and parallel resonant frequencies correspond to totally different values for the crystal impedance, but these frequencies are typically very close because Cm is typically very small compared to Cp. All crystals have a series and parallel resonant mode and the mode of oscillation depends how the crystal is hooked up in the circuit.

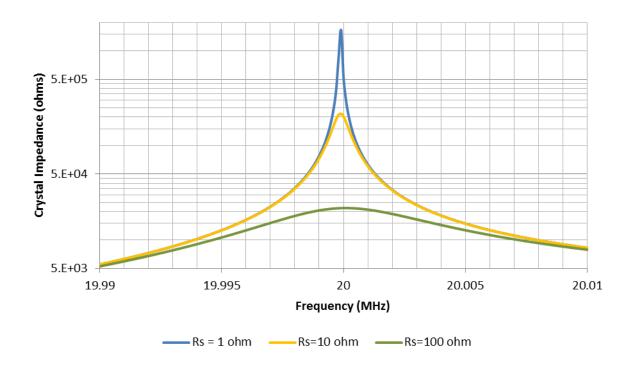

The value of Rs has only a very slight impact on the oscillation frequency. However, it does impact how sharp the cutoff is, which corresponds to the noise. Below is an example of a 20 MHz parallel resonance shown for Cp=5.4 pF, Cm=0.02545 pF, Lm=2.5 mH, and Rs at various values.

Figure 4.4 Crystal Resonance

#### Typical Parallel Crystal Circuit

For parallel resonant of the circuit, the crystal, the output of the inverter is what is used to drive the rest of the circuit. Load capacitors of C1 and C2 are the load capacitors, which are supplied externally to help stabilize the frequency and improve spurious emissions. These values effective are in parallel with Cp. The series resonant frequency is not shifted, but the parallel resonant frequency is shifted closer to the resonant frequency as follows:

$$\omega_{Parallel} = \omega_{Series} \cdot \sqrt{1 + \frac{Cm}{Cp + \left(\frac{C1 \cdot C2}{C1 + C2}\right)}}$$

(4.7)

The load capacitors can also be used to slightly "pull" the crystal. The capacitors can reduce harmonics and sometimes making C2 > C1 can help reduce them even further. If harmonics are still an issue, the resistor, R, can optionally be added.

Figure 4.5 Parallel Crystal Oscillator

#### Common Types of Crystal Oscillators

Frequency accuracies of ten parts in one million are not uncommon for crystal oscillators. The main cause of frequency error in these oscillators is drift over temperature. The *Temperature Compensated Crystal Oscillator* (TCXO) has a temperature sensor and compensation to correct the crystal frequency over temperature. This improves the frequency accuracy by about a factor of ten. The *Oven Controlled Crystal Oscillator* (OCXO) improves the performance by approximately another factor of ten by having an oven heat the crystal to a constant temperature.

| Acronym | Oscillator Type                            | Accuracy | Comments                                                                                             |

|---------|--------------------------------------------|----------|------------------------------------------------------------------------------------------------------|

| XO      | Crystal Oscillator                         | 10 ppm   | This is a crystal plus the inverter.                                                                 |

| TCXO    | Temperature compensated crystal oscillator | 1 ppm    | Uses circuitry to compensate frequency over temperature, but sometimes this circuitry can add noise. |

| VCXO    | Voltage compensated crystal oscillator     | 10 ppm   | Like a crystal oscillator, but a voltage can be used to tune the frequency                           |

| OCXO    | Oven controlled crystal oscillator         | 0.1 ppm  | Uses an oven to maintain constant temperature                                                        |

Table 4.1 Common Types of Crystal Oscillators

#### Conclusion

The input source to the PLL can come from many sources such as another device or a crystal oscillator. It typically needs to be clean and highly accurate in order to generate a good frequency at the output. Aside from the noise and accuracy of the signal, one does need to be also mindful of the output format and slew rate. In general, PLLs like to have a higher slew rate for the best phase noise and spur performance. Differential inputs typically can have better phase noise as well.

#### References

- [1] Gardner, F.M. *Phaselock Techniques*, 2<sup>nd</sup> ed., John Wiley & Sons, 1980

- [2] Massovich, Vadim Frequency Synthesis: Theory and Design, 3<sup>rd</sup> ed., John Wiley & Sons 1987

- [3] 1997 ARRL Handbook, 74<sup>th</sup> ed. The American Radio Relay League, 1996

- [4] Rohde, Ulrich L. Microwave and Wireless Synthesizers: Theory and Design, John Wiley & ,1997

#### **Chapter 5** The Input Path and R Divider

#### Introduction

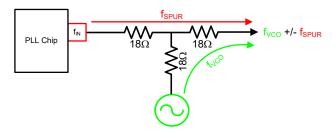

Although the input path and R divider might not seem be the most complicated blocks of the PLL, they are still worthy of some discussion because the output of this block gets multiplied by the N divider to the output of the VCO. If this block is noisy or if the input signal does not have a sufficient slew rate, then there can be degradations in the spurs and phase noise. When input frequency ( $f_{OSC}$ ) is a low frequency sine wave, this tends to lead to slower slew rates on the signal that can impact the performance of the PLL. The input path can also be more sophisticated and include doublers and multipliers.

#### Connecting to the Input (OSCin) Pin

#### General Properties of the Input Pin

The input pin to a PLL often has its own bias level and requires the signal to be AC coupled. The input pin to the PLL can be either differential or single-ended.

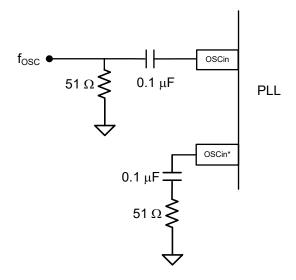

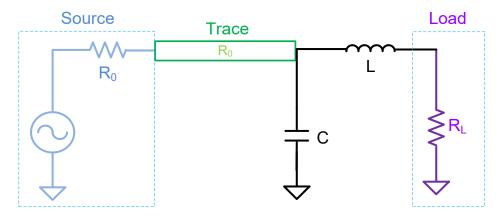

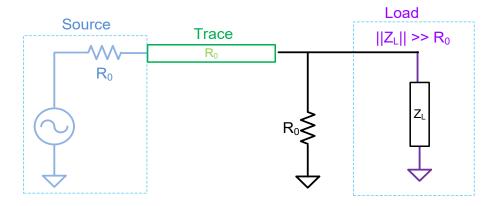

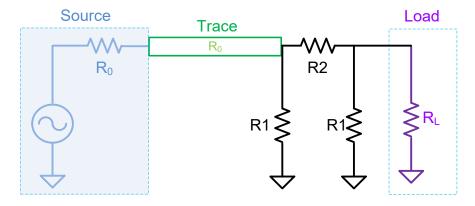

#### PLLs with Differential OSCin Input

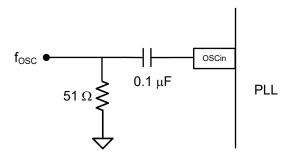

Many PLLs offer a differential OSCin input. If this is offered, the ideal way to drive this is differentially with a signal of high slew rate. In the case that the input source is single-ended, one can either use a balun or AC couple the unused input to ground. For optimal performance, some devices get better spurs if the impedance as seen looking from the OSCin pin is the same as looking outward from the OSCin\* pin as shown in Figure 5.1. The likely reason for this is that any spurious noise on the ground gets tracked out better by the pins.

Figure 5.1 Driving a differential input as single-ended

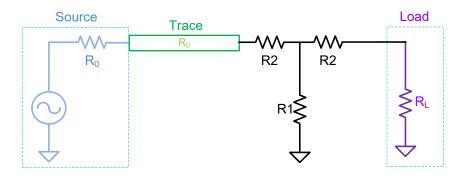

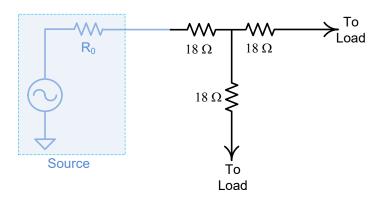

#### PLLs with Single Ended OSCin Pin

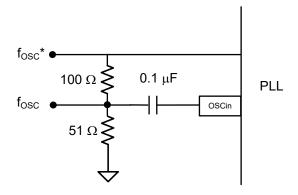

For the case of a single-ended OSCin input and a single-ended source, it is typical to just a shunt 50 ohm resistor to ground. This works if we assume that the driving source has 50 ohm output impedance, the amplitude is not too high, and the input impedance of the PLL is not too high. If this is not the case, one can either use a series resistor or a resistive pad to correct for this.

Figure 5.2 Driving a PLL Single-ended

Another situation that might come up is if the input signal is differential, but the input pin is only single-ended. One way to resolve this is to use a balun, but if this is undesired it is possible to just use one side of the differential output. If the impedance presented to the OSCin pin is important, it is allowable to ground just one side of the differential output if it is AC coupled to the driver as shown in Figure 5.3. However, do not ground both sides as this will interfere with the differential termination.

**Figure 5.3** *Driving a PLL Single-ended with a Differential Input*

#### **R** Divider Structure

The R divider is typically done in a lower frequency process and is often differentially done in CMOS or CML. It is typically done with a series of flip-flops.

#### **Doublers and Input Multipliers**

Some devices offer programmable input multipliers to allow improvement to PLL phase noise or spurs. However, one has to be aware that these blocks can add noise. Doublers are easier to implement, so they often do not add noticeable noise. Multipliers greater than two can add a significant amount of noise and the amount of added noise is device specific.

#### The Importance of Slew Rate

It is often the case that slew rate is important to the OSCin input pin. The reason for this is that this gives the input signal greater noise immunity. This noise can come in the form of phase noise or spurs. It is also the case that sometimes this noise and spurious might come from inside the PLL. In any case, the higher slew rate almost always is a benefit. For a sine wave, higher slew rates come with higher amplitude and frequency. At some point, the faster slew rate does not help, and a typical LVPECL, LVDS, or LVPECL signal has a sufficient slew rate.

#### Conclusion

The input path to the PLL is an important part to the PLL because if this is not connected correctly, it can lead to performance degradations in phase noise and spurs.

#### **Chapter 6** The Phase Detector and Charge Pump

#### Introduction

The phase detector is a device that converts the differences in the two phases from the N counter and the R counter into an output voltage. This output voltage can either be applied directly to the loop filter or converted to a current by the charge pump. The voltage phase detector is presented to support legacy literature, but the main focus of this book is charge pump PLLs.

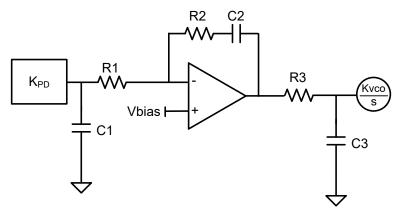

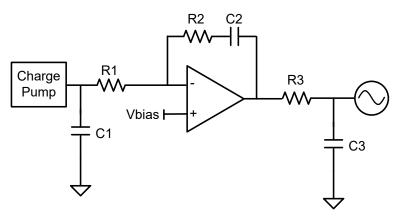

#### The Modern Charge Pump vs. the Voltage Phase Detector

The Voltage Phase Detector

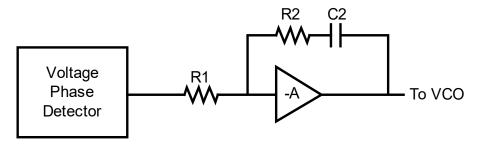

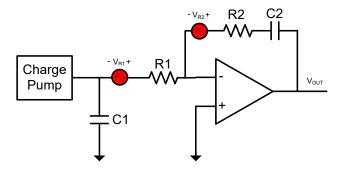

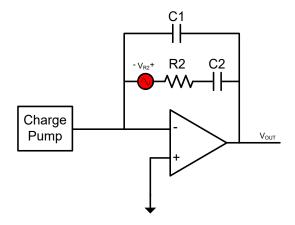

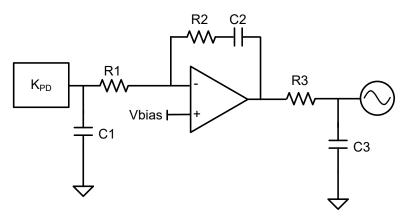

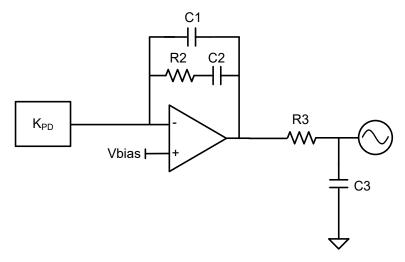

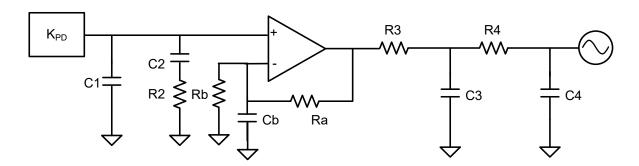

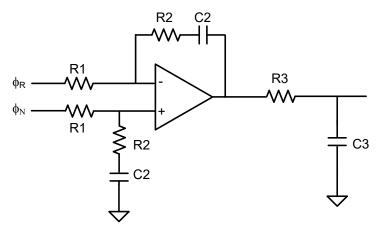

The voltage phase detector was the approach that was commonly used before the introduction of the charge pump and outputs a voltage proportional to the phase error between the outputs of the N and R dividers. It can be implemented with a mixer, XOR gate, or JK flip flop. Perhaps the reason why the voltage phase detector lost popularity compared to the charge pump was that it was unable to attain and hold lock if the VCO frequency/phase was too far off from the target value, unless acquisition aids or an active filter is used. Floyd Gardner's classical book, *Phaselock Techniques*, goes into great detail about all the details and pitfalls of this sort of phase detector and presents the following topology for active filters.

Figure 6.1 Classical Active Loop Filter Topology for a Voltage Phase Detector

Active filters require an op amp, which add cost, area, current, and noise, and tend to be less popular unless the op-amp is necessary for some other purposes, such as providing a larger tuning voltage range to the VCO. Although the voltage phase detector might have applications where it may be superior to the charge pump, it is far less common and therefore not discussed in much depth in this book.

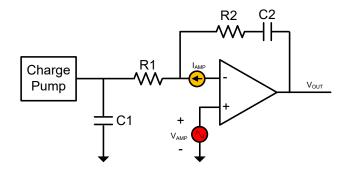

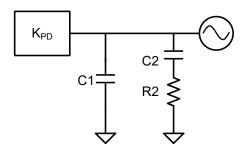

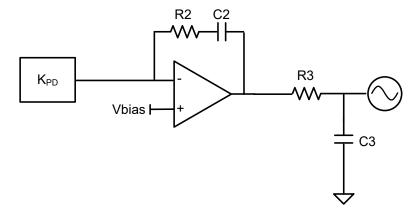

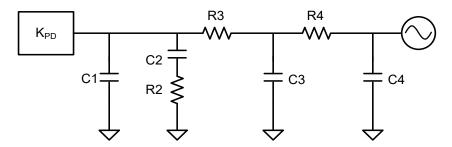

## The Introduction of the Phase/Frequency Detector (PFD) and Charge Pump

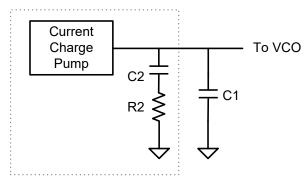

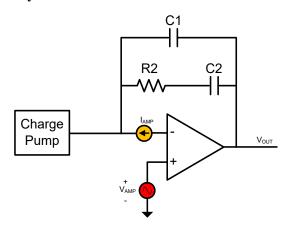

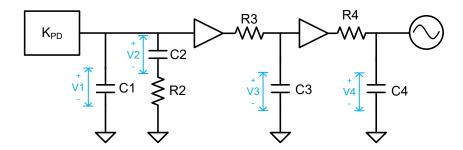

The phase/frequency detector (*PFD*) and charge pump combination has replaced the voltage detector in many designs because it has no issues with attaining and maintaining lock and requires no active components. Referring to Figure 6.2, the charge pump architecture may be different, but it mathematically achieves the same functionality as integrating an ideal op amp for the voltage phase detector. The current can be thought of as the output voltage in Figure 6.1 divided by R1. The charge pump PLL requires the additional component C1 in order to help filter the current pulses it outputs, but this component also provides additional filtering for spurs, which makes it a good idea to have anyways.

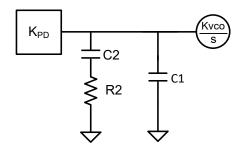

**Figure 6.2** Passive Loop Filter with PFD and Charge Pump

## **Phase Frequency Detector High Level Description**

The PFD compares the outputs of the N and R counters in order to generate a correction voltage, which is converted to a current by the charge pump. This book will treat the charge pump and PFD as one block because they are typically integrated together.

Figure 6.3 Phase/Frequency Detector with Charge Pump

Looking carefully at Figure 6.3, observe the VCO gain is divided by a factor of s in order to convert the VCO output from frequency to phase. The reason that this is done is that it makes more sense to model the PLL in terms of phases and not frequencies to help model the phase detector. If the frequency output is sought, then it is only necessary to multiply the transfer function by a factor of s, which corresponds to differentiation. So the phase-frequency detector not only causes the input phases to be equal, but also the input frequencies, since they are related.

## **Phase Frequency Detector Structure and Theoretical Operation**

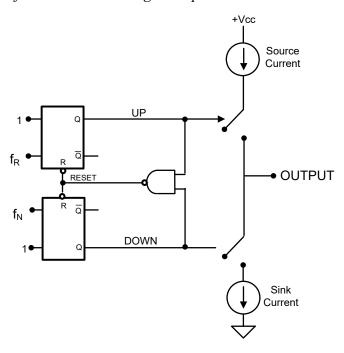

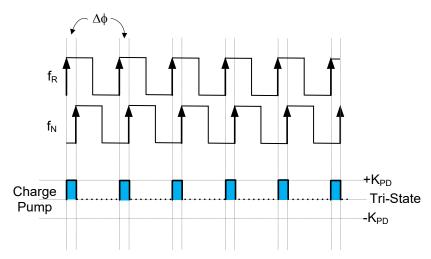

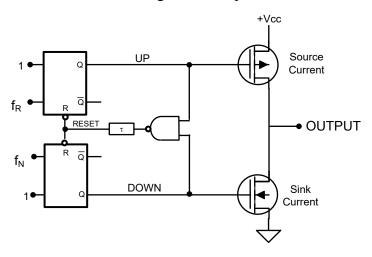

Simplified Structure of the PFD and Charge Pump

Figure 6.4 Phase/Frequency Detector and Charge Pump

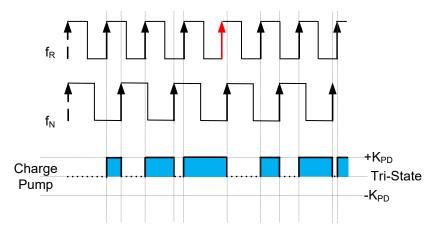

An implementation of the PFD and charge pump is shown in Figure 6.4 with  $f_N$  representing the signal from the N divider and  $f_R$  the signal of the R divider. The circuit has the three possible states of the source current enabled, the sink current enabled, or both currents disabled. However, the state of both currents enabled is not allowed because if both the UP and DOWN signals were high, it would reset the flip-flops and causing both switches to be open.

The circuit in Figure 6.4 is said to have positive *phase detector polarity* because a positive phase error leads to a positive correction current. On many PLLs, it is possible to invert the polarity of the phase detector so that the behavior between the sink and source currents is reversed. When this is done, the phase detector is said to have a negative phase detector polarity. This feature is often useful when using active filters.

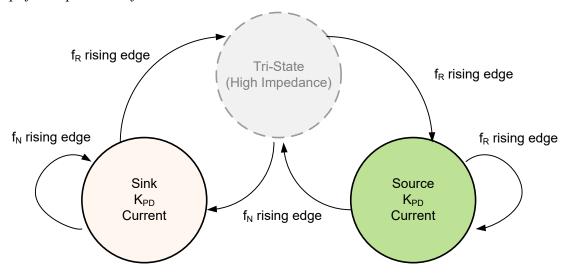

## Simplified Operation of the PFD

Figure 6.5 States Diagram of the Phase Frequency Detector

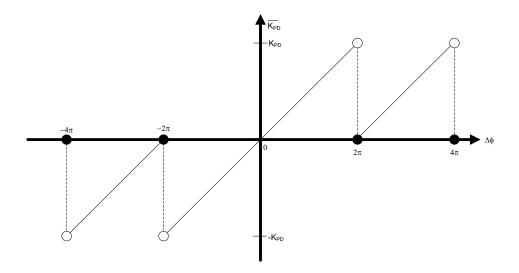

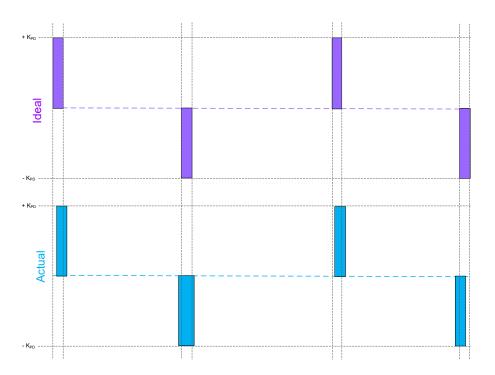

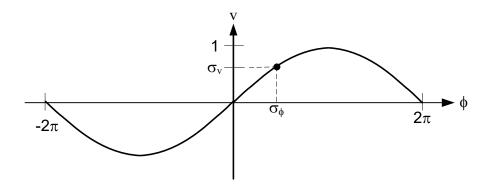

A simplified time-averaged output of the PFD with respect to phase error between the N and R divider outputs  $\Delta \phi$  is shown below.

Figure 6.6 Simplified Time-Averaged Output of the Phase Detector

The PFD can lock to any phase error, but there are some performance considerations if the phase error is very small or if the phase error exceeds  $2\pi$ . These cases are discussed now.

# Operation in the Linear Region $-2\pi < |\Delta \phi| < 2\pi$

**Figure 6.7** *PFD Output for an Error Less than*  $2\pi$

Figure 6.6 shows the time averaged output of the phase detector. The slope of this line,  $\overline{K_{PD}}$ , corresponds to the time-averaged charge pump gain and can be calculated as follows:

$$\overline{K_{PD}} = \frac{K_{PD} - (-K_{PD})}{2\pi - (-2\pi)} = \frac{K_{PD}}{2\pi}$$

(6.1)

For this equation, there is debate over the division by a factor of  $2\pi$ . Although it is technically correct to include this factor, it is typically left out because most calculations involve multiplying it by the VCO gain, which contains a factor of  $2\pi$  to convert it from MHz/volt to MRad/volt. Knowing that these will cancel, this book will use the practical definition of disregarding this factor rather than the academic version of this formula in order to simplify calculations and reduce the possibility for round off errors.

$$\overline{K_{PD}} = K_{PD} \cdot \Delta \phi \tag{6.2}$$

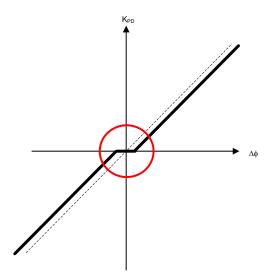

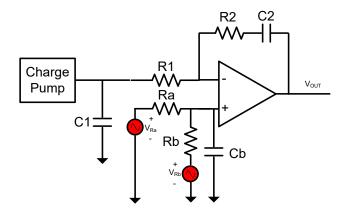

# Operation near the Dead Zone of the Linear Region

When operating near zero phase error, the structure of the phase detector becomes more relevant and there is more interest in real-world features such unequal sink and source currents as well as the unequal turn on times of the sink and source currents. To discuss this, Figure 6.8 shows a more detailed diagram of the phase detector.

**Figure 6.8** *Detailed Phase Detector Drawing*

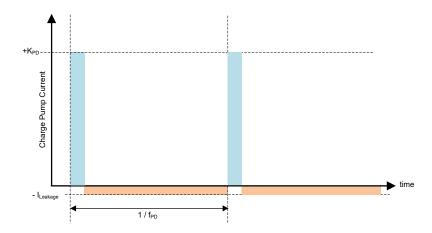

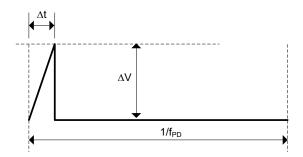

Figure 6.9 shows the impact of the non-zero turn on times of the sink and source currents as well as their mismatch.

Figure 6.9 Non-Ideal Charge Pump Operating Near Zero Phase Error

Near zero phase error the nonzero turn on times of sink and source MOS devices significantly reduces the gain from the ideal value. This area of operation of the phase is known as the *dead zone*. In this region, the charge pump gain tends to be very low which makes the loop unable to suppress the VCO noise. Furthermore, the phase detector can look nonlinear and lead to high phase noise and fractional spurs. The strategy in most PFD designs is to avoid this dead zone.

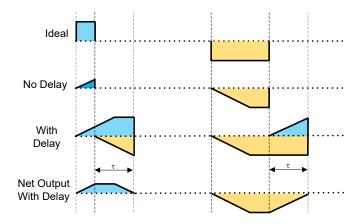

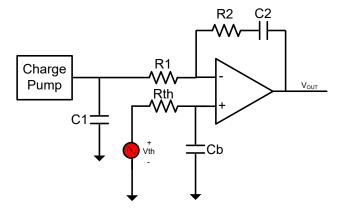

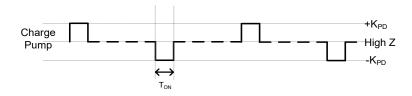

There are some common strategies to deal with the dead zone. One method is to introduce a bleed current that pulls the phase detector away from operating with zero phase error. Another is to introduce a minimum on time for the phase detector to ensure that it operates away from a phase error that is too small, and a third is to introduce a small delay  $\tau$ , to deemphasize nonzero turn on times for the sink and source devices in the charge pump as shown in Figure 6.10.

**Figure 6.10** *PFD with Delay to Reduce Dead Zone*

If the rise and fall times of the MOS devices are identical, then the total area under the curve will be identical to the ideal area provided the delay is longer than the turn on time of these MOS devices and that the phase error in question is greater than the rise time. For purposes of comparing the phase error, express in terms of absolute time, not a phase error.

$$\Delta t = K_{PD} \cdot \frac{\Delta \phi}{2\pi \cdot f_{PD}} \tag{6.3}$$

| Phase Error           | Ideal                   | No Delay                                                           | With Delay                                                                    |

|-----------------------|-------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------|

| $ \Delta t  < t_R$    | $K_{PD} \cdot \Delta t$ | $K_{PD} \cdot \frac{\Delta t^2}{2 \cdot t_R}$                      | $K_{\scriptscriptstyle PD} \cdot rac{arDelta t^2}{t_{\scriptscriptstyle R}}$ |

| $ \Delta t  \geq t_R$ |                         | $K_{PD} \cdot \Delta t - K_{PD} \cdot t_R / 2 \cdot sgn(\Delta t)$ | $K_{PD} \cdot \Delta t$                                                       |

**Table 6.1** Charge Injected for Phase Error of ∆t

## Operation Out of the Linear Region, $|\Delta t| \ge t_R$ :

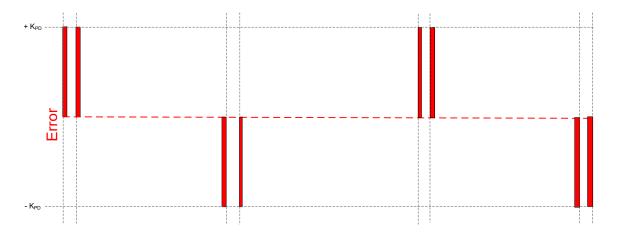

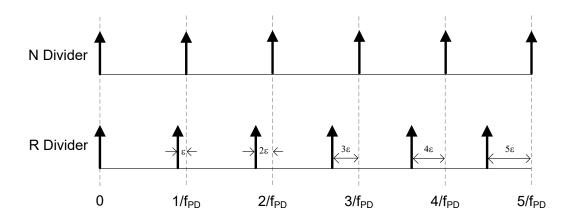

At first glance, it may seem absurd to talk about a phase greater than  $2\pi$ , but what this really means is that one counter is having more rising edges than another, which typically implies that the inputs to the phase detector are not the same frequency and the PLL is not in lock. In this case, the PFD does put current in the correct direction, but the magnitude does not track the phase error. Two phenomenon of interest in this situation are cycle slipping and the time-averaged duty cycle of the phase detector.

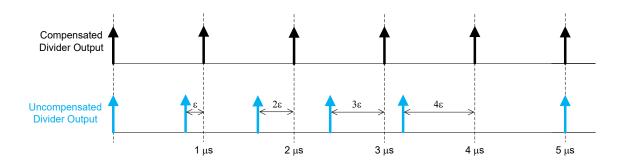

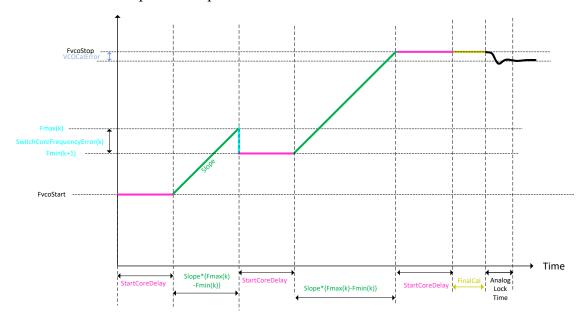

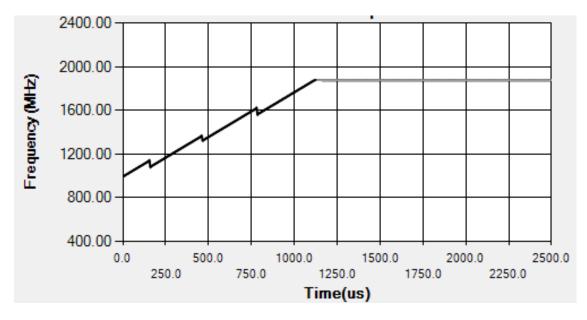

## Cycle Slipping

When one of the rising edges of one of the inputs to the phase detector does not get counted, this is known as a cycle slip. One situation where this comes up is if the N divider is changed abruptly to change the VCO frequency and the input frequencies to the phase detector are therefore different. This causes degradation in the lock time.

Figure 6.11 Cycle Slip Example Assuming 0 Hz Loop Bandwidth

Figure 6.11 shows situation when the N divider is abruptly changed to a higher value in order to direct the VCO to a higher frequency. As the duty cycle increases, eventually one cycle of the R divider is not counted, which causes the duty cycle of the charge pump to go back to a lower state. This is known as a *cycle slip*. The PFD does recover, but this increase the lock time. If the loop bandwidth is wide enough, the PLL can track this before the cycle slip happens, but this depends on the ratio of the phase detector frequency to the loop bandwidth.

In order to calculate the time to the first cycle slip, it is necessary to find the time when the faster counter will get one cycle ahead of the slower divider. For instance, if the N divider output was faster than the R divider output, the equation would be as follows.

$$(t+1)\cdot f_R = t\cdot f_N \tag{6.4}$$

If it was the case that the R divider output frequency was higher, then just switch the frequencies around. Solving these equations gives the following conditions for the first cycle slip.

$$t \ge \begin{cases} \infty & f_N = f_R \\ \frac{f_R}{f_N - f_R} & f_R < f_N \\ \frac{f_N}{f_R - f_N} & f_R > f_N \end{cases}$$

$$(6.5)$$

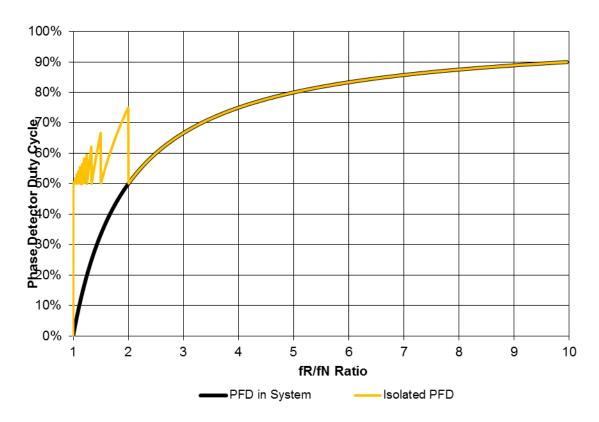

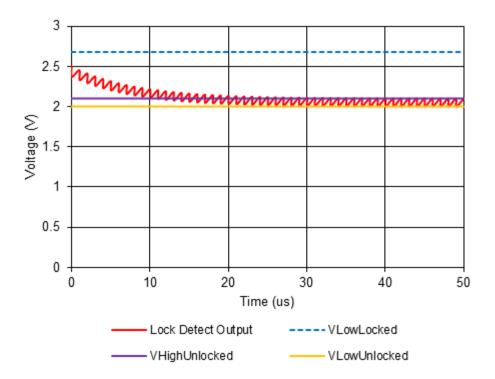

Calculation of Duty Cycle When Inputs Differ in Frequency

If two inputs to the phase detector differ in frequency, there are situations when the duty cycle of the phase detector would be of interest. One such situation would be if one was to construct a lock detect circuit. In order to calculate the duty cycle, make the simplifying assumption that loop bandwidth is wide enough to avoid cycle slipping. Also, without loss of generality, one can assume that the R divider output is greater than the N divider. If not, then swap the names and do the same analysis. Finally, assume that both the R and N dividers start off in phase. Under these assumptions, the phase at the output of the R divider after one cycle would be:

$$\phi_R = f_R \cdot \left(\frac{1}{f_R}\right) = 1 \tag{6.6}$$

The phase at the output of the N divider after this same period of time can also be calculated.

$$\phi_N = f_N \cdot (1/f_R) = f_N/f_R$$

(6.7)

Assuming the magnitude of the phase error does not exceed  $2\pi$ , the time-averaged phase error of the PFD, expressed in cycles (not radians), can be calculated as:

$$\overline{\Delta\phi} = \begin{cases}

1 - \frac{f_N}{f_R} & f_N \leq f_R \\

1 - \frac{f_R}{f_N} & f_N > f_R

\end{cases}$$

(6.8)

As the ratio becomes infinite, the duty cycle approaches 100%. If the ratio of the input frequencies is two, then the duty cycle is 50%. For ratios above 2, it makes no difference if we assume there is cycle slipping or not. However, for ratios below two, assuming a 0 Hz bandwidth as opposed to no cycle slipping does make a difference.

**Figure 6.12** *Duty Cycle of the PFD for Inputs of Unequal Frequency*

For purposes of measuring the charge pump current, it is important to be aware of this duty cycle. Even if the ratio of these frequencies is ten, still the duty cycle of the charge pump is only 90%. The best way to do this is to actually remove the input to the N counter completely and set the N counter value to the maximum value. Theoretically, the N counter value should not matter, but if there is no signal there, there could be some self-oscillation at this pin. To see the sink current, invert the polarity of the phase detector.

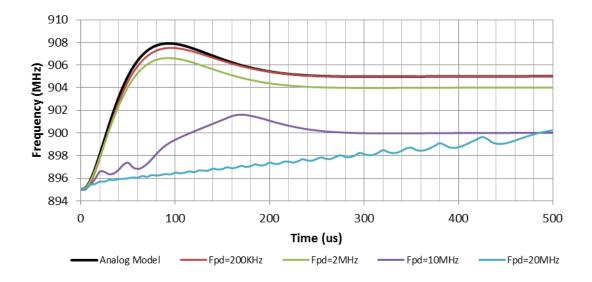

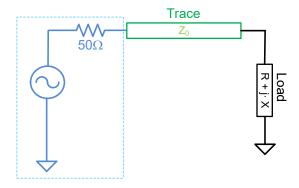

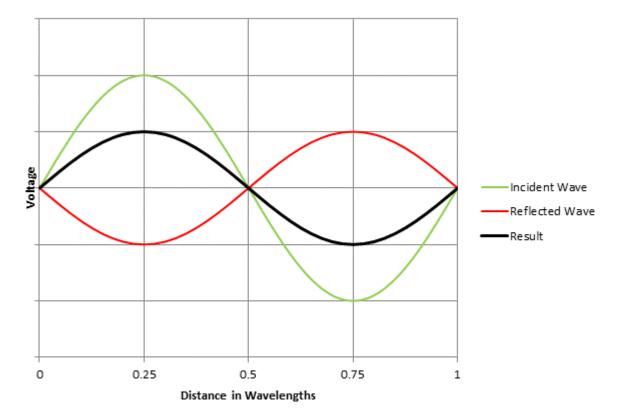

## The Continuous Time Approximation

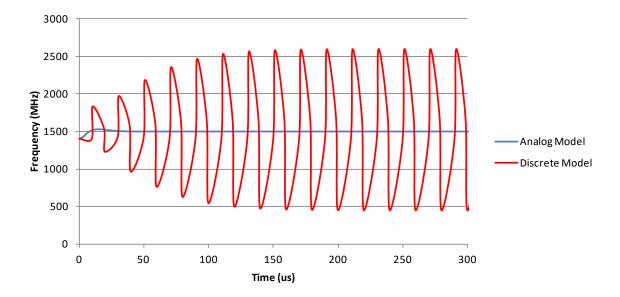

It greatly simplifies calculations to model the charge pump current as a continuous current with a magnitude equal to the time-averaged value of these currents from the charge pump. However, the phase/frequency detector technically puts out a pulse width modulated signal and not a continuous current. This approximation is referred to as the *continuous time approximation* and is a valid provided that the loop bandwidth is no more than about one-

tenth of the phase detector frequency. Reference [2] goes into the justification for this result. In practice, one will start to see the loop go unstable when the loop bandwidth reaches about one-third of the phase detector frequency and would probably never want to exceed one-fifth the phase detector frequency to avoid any issues. Between one-tenth and one-fifth, the PLL will probably still lock, but the performance may be degraded. Specifically, increasing the loop bandwidth beyond one-tenth of the phase detector frequency might not yield the expected improvement in lock time. Also, spurs might have a cusping effect due to this sampling. If the loop bandwidth is less than about 1/100<sup>th</sup> of the phase detector frequency, then the lock time could be degraded due to cycle slipping, which will be discussed in a later chapter. It will also be shown in a later chapter why the discrete sampling action of the phase detector causes the phase detector to get noisier at higher phase detector frequencies.

#### Conclusion

This chapter has discussed the PFD (Phase Frequency Detector) and has given some characterization on how it performs for different types of inputs. It is important to also remember that most of the time that this book refers to the PFD, it is meant to also include the charge pump. When charge pump is referred to, it is just the devices sinking or sourcing the current. Also, the gain of the PFD in this book will be defined as the charge pump gain. Other references may divide by a factor of  $2\pi$ , but it is commonly done so in industry as this factor gets cancelled out by another factor of  $2\pi$  in the VCO gain.

#### References

- [1] Best, Roland E., *Phase-Lock Loop Theory, Design, Applications*, 3<sup>rd</sup>. ed, McGraw-Hill 1995

- [2] Gardner, F.M., *Charge-Pump Phase-Lock Loops*, IEEE Trans. Commun. vol. COM-28, pp. 1849 1858, Nov 1980

- [3] Gardner, F.M. *Phaselock Techniques*, 2<sup>nd</sup> ed., John Wiley & Sons, 1980

# **Chapter 7** The Loop Filter

### Introduction

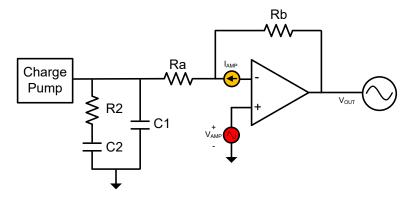

The loop filter is a low pass filter that translates the charge pump output current into a tuning voltage for the VCO. However, not just any old low pass filter will do. The loop filter transfer function is actually a part of the entire closed loop PLL which also includes the N divider value, charge pump gain, and VCO gain. This closed loop transfer function has a profound impact on PLL switching speed, spurs, phase noise, and stability. There are many chapters in this book devoted to just loop filter design, so this chapter gives just a brief overview of loop filters.

## **Loop Filter Structure**

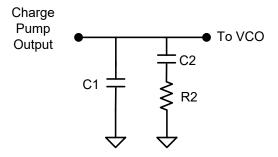

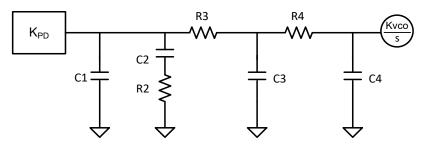

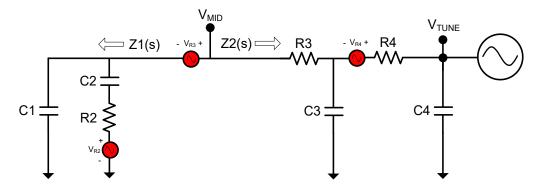

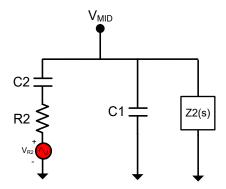

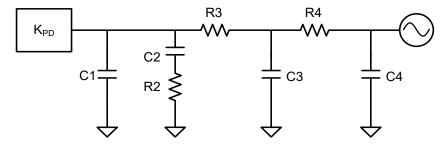

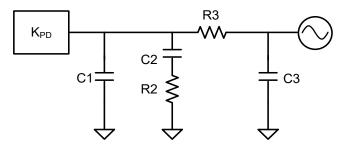

A loop filter can be implemented with resistors and capacitors and a simple one is shown in the following figure.

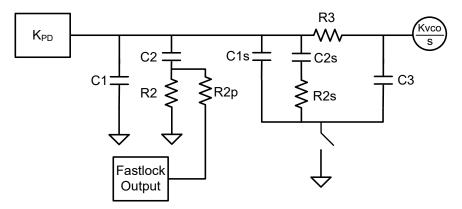

Figure 7.1 Typical Loop Filter

The transfer function for this loop filter in this case is simply the impedance of the loop filter which can be written as follows:

$$Z(s) = \frac{1 + s \cdot C2 \cdot R2}{(C1 + C2) \cdot s \cdot \left(1 + s \cdot \frac{C1 \cdot C2 \cdot R2}{C1 + C2}\right)} = \frac{1 + s \cdot T2}{A0 \cdot s \cdot (1 + s \cdot T1)} \tag{7.1}$$

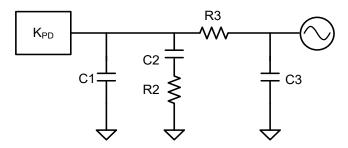

The zero, T2, is always necessary for stability of the system and there are also poles at zero and T1. In the case of a charge pump PLL, the pole T1 is necessary. Without this pole, the sharp corrections of the charge pump would be theoretically be directly converted to a voltage by the resistor R2 and cause huge voltage swings to the VCO input, which would lead to high phase noise and spurs. In reality, the VCO has an input capacitance that would act as capacitor C1 to lessen this effect, although it is not good practice to depend on it. Additional poles may be added to improve the ability to filter noise at farther offsets. The *loop filter order* is defined by the number of poles in the loop filter.

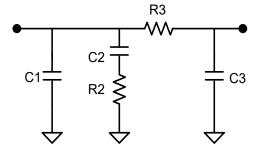

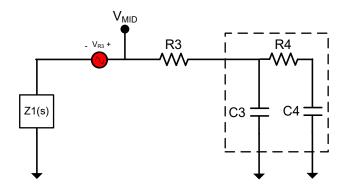

**Figure 7.2** A Third Order Loop Filter

### The Loop Filter Transfer Function

The generalized loop filter transfer function is defined as the output voltage at the VCO divided by current injected by the PLL charge pump and is shown by the following expression.

$$Z(s) = \frac{1 + s \cdot T2}{A0 \cdot s \cdot (1 + s \cdot T1) \cdot (1 + s \cdot T3) \cdot (1 + s \cdot T4)}$$

(7.2)

The pole, T2, and the zero, T1, are required. The poles T3 and T4 are optional and can be set to zero if they are not used. The order of the loop filter is defined by the number of poles it has, including the pole at zero. So the loop filter in Figure 7.2 is considered a third order loop filter, since it has a pole at zero, T1, and T3.

# **Passive and Active Loop Filters**

In general, it is ideal to implement the loop filter with just resistors and capacitors for the reasons of cost and noise. However, in some situations, there may be reasons to use an active device such as an op-amp. The most common reason for this is when the charge pump cannot put out a high enough voltage. In either case, the analysis for such filter is the same using the poles and zeros of the transfer function.

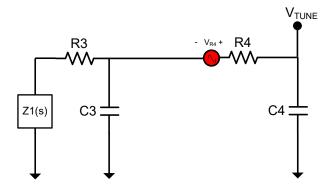

## **Degenerate Loop Filters**

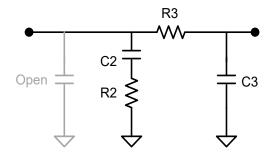

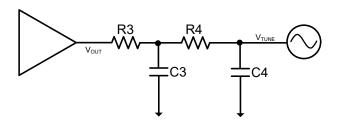

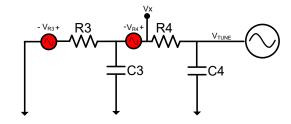

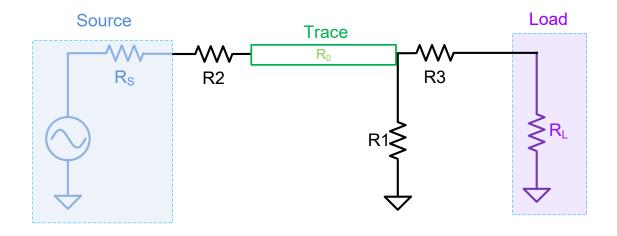

Degenerate loop filters are ones that have zero valued components. This can be unintentional or intentional. One common situation when they may unintentionally arise is with partially integrated loop filters. One occurrence of this is when the filter has fixed component values for the higher poles formed by C3, C4, R3, or R4 and one tries to design for a loop bandwidth that is wider than possible. In this case, it can sometimes lead to a case where the capacitor C1 is zero.

**Figure 7.3** *Degenerate 3<sup>nd</sup> Order Loop Filter*

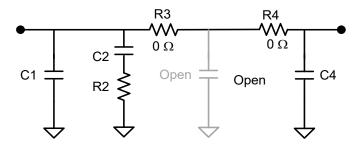

In other situations, degenerate filters are intentionally created. One good reason for this is when one wants the board layout to accommodate different possibilities by putting a fourth order filter layout and then using zero value components if the extra poles are not needed. In Figure 7.4, the capacitance for C1 has been distributed between its normal spot and also a spot closer to the VCO. In some situations, this could yield better performance if the footprint on the PCB for C4 is much closer to the VCO than the footprint for C1.

**Figure 7.4** Degenerate 4<sup>th</sup> Order Loop Filter

For the purposes of defining these filters, they will be named based on the number of poles that they have, including the one at zero. For instance, Figure 7.3 is considered a 2<sup>nd</sup> order filter because it has two poles, but will be called a degenerate 3<sup>rd</sup> order filter because this is what it would be if the components were not all non-zero. Figure 7.4 is considered a 2<sup>nd</sup> order filter, but a degenerate 4<sup>th</sup> order filter.

43

## Conclusion

The loop filter is key the performance of the PLL system and has a lot of degrees of flexibility for one to design. The loop filter can have different orders; this book assumes that it can be of order two, three, or four. There is no one loop filter that is right for every application as it involves performance trade-offs. Later chapters will cover the characteristics of the loop filter in much greater depth.

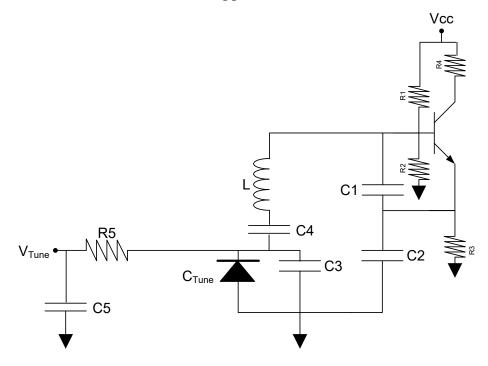

# **Chapter 8** Voltage Controlled Oscillators

### Introduction

The voltage controlled oscillator (VCO) generates a frequency based on the input voltage; it can be thought of as a voltage to frequency converter. Although the principles of oscillators have already been covered and apply to voltage controlled oscillators, there are more details specific to VCOs that are worthy of study. This chapter discusses the performance characteristics of the VCO and then follows it up with the structure and implementation.

#### VCO Performance Characteristics

## Frequency and Tuning Range

The range of frequencies that a VCO can produce is perhaps the most critical and relevant parameter for the VCO. A wider frequency range is always desirable, but this comes at the expense of phase noise. The minimum frequency is defined to be  $f_{VCOmin}$  and is produced by an input voltage of  $V_{TuneMin}$ . The maximum frequency is defined to be  $f_{VCOmax}$  and is produced by an input voltage of  $V_{TuneMax}$ . For some VCOs, going below the minimum tuning voltage can degrade the performance, or cause the VCO to not oscillate at all. The VCO frequency changes as a function of supply voltage, process, and temperature, so the guaranteed frequency range that is typically specified in a manufacturer's datasheet will typically be narrower than the actual range of the VCO.

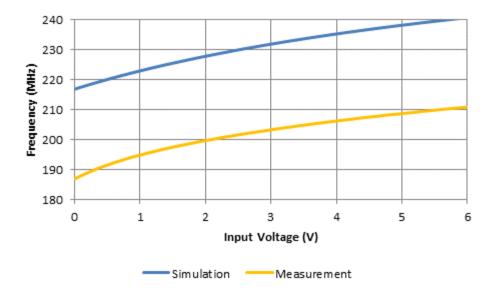

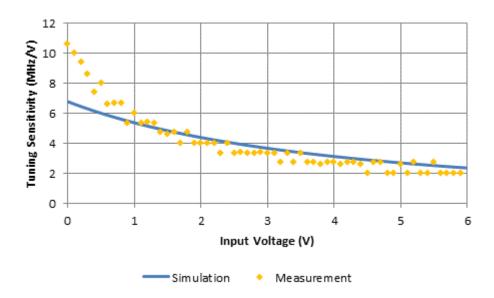

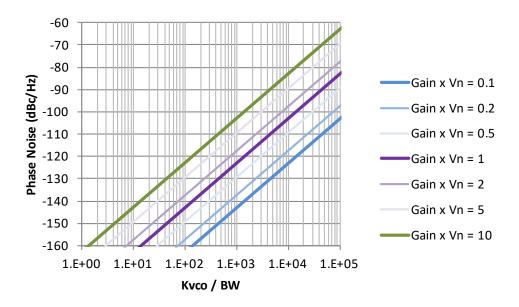

#### VCO Gain

The gain of the VCO,  $K_{VCO}$ , is expressed in MHz/V and is how much the output frequency changes for a change in the input voltage. It is desirable for this to be constant over the VCO tuning range and if this is assumed this can be calculated as follows:

$$K_{VCO} = \frac{df_{VCO}}{dV_{Tune}} \approx \frac{f_{VCOmax} - f_{VCOmin}}{V_{TuneMax} - V_{TuneMin}}$$

(8.1)

The VCO gain can be calculated from measured by taking the slope of the tuning curve. If it is constant, then it can be calculated for the whole range. If not, it can be calculated by calculating the slope of the tuning curve in a small range about each  $V_{Tune}$  voltage or by breaking up the VCO tuning range can be broken up into several regions. The VCO gain has a significant impact on the closed loop transfer. If this gain changes significantly, by say a factor of 1.5 or more, it can throw the loop dynamics off. It is often possible to compensate for this with the charge pump gain.

# Supply Voltage, Pushing, and Power Supply Noise Rejection

The supply can impact the performance of the VCO. *Pushing* refers to how much a change in voltage at the power supply pins of the VCO impact the output frequency and is typically measured in MHz/V. It is generally desirable to have this pushing to be lower. The first reason is that if there is an abrupt change in voltage, it could cause a glitch in the VCO frequency which would then need to settle out. The other reason is that any noise voltage on the power supply pins gets multiplied by the pushing goes to the output of the VCO. If the gain at this pin is high, then the noise at the output of the VCO will be worse.

### Pulling

Pulling refers to how much the VCO frequency will shift when a load is placed on the output. One example of where this can be an issue is in a circuit when the power amplifier is first turned on. This changes the load presented to the VCO and can cause a frequency disturbance that needs to settle out.

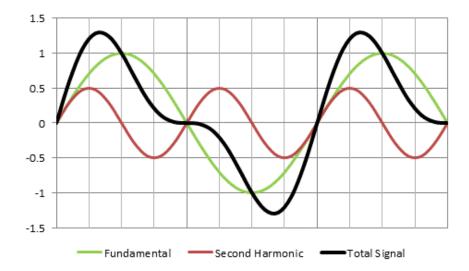

### Harmonics

VCOs generate harmonics, which occur at a multiple of the out frequency. In general, these are considered undesirable. The first exception to this is if the desired output is a square wave, which is very rich in odd harmonics. The other exception is when one wants to intentionally lock the PLL to one of these harmonics in order to get a higher frequency. In this case, a higher harmonic of the VCO is intentionally used as the intended signal. The drawback of this approach is that a lot of power is sacrificed.

### Other Issues with VCOs

- Output power can vary with frequency, voltage, and temperature.

- VCO gain can vary with frequency, voltage, and temperature.

- VCO tank circuit can interact with loop filter if there is insufficient isolation

- Some VCOs may have high leakage currents, especially if their minimum tuning voltage is violated.

- Some VCOs may not oscillate if the tuning voltage is 0 V.

- VCOs typically have an input capacitance, which adds in to the loop filter. Typically this is the varactor diode and whatever is in parallel with this.

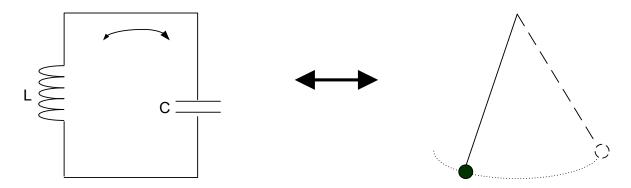

### Relating the VCO to a Pendulum

Although the concept of an amplifier with a filter in the feedback path does apply to a VCO, this is a hard way to visualize the VCO. This is because transistors and FETs do not deal strictly with voltage gains. In order to understand VCOs, it is easier to understand them as a tank circuit and amplification circuitry.

#### VCO Tank Circuits

The tank circuit consists of an inductor and a capacitor and has many analogies to the pendulum. In the pendulum, the energy changes from potential to kinetic. For the tank circuit, the energy changes from the magnetic field in the inductor to the magnetic field in the capacitor plates. This can be thought of as an electronic spring, or others compare it to a pendulum.

Figure 8.1 Comparison of a VCO Tank Circuit to a Pendulum

| Characteristic | Conservation of Energy                                                                                 | Frequency                   |

|----------------|--------------------------------------------------------------------------------------------------------|-----------------------------|

| Pendulum       | $m \cdot g \cdot l \cdot \sin\theta + \frac{1}{2} \cdot m \cdot \left(\frac{d\theta}{dt}\right)^2 = E$ | $\sqrt{\frac{g}{l}}$        |

| Tank Circuit   | $\frac{1}{2} \cdot C \cdot V^2 + \frac{1}{2} \cdot L \cdot C^2 \cdot \left(\frac{dV}{dT}\right)^2 = E$ | $\frac{1}{\sqrt{L\cdot C}}$ |

Figure 8.2 Tank Circuit and Pendulum Equations Assuming no Losses

When the voltage is maximized in the tank circuit, the energy stored in the capacitor is maximized and the energy stored in the inductor is zero. When the voltage is minimized, the capacitor has no energy and the inductor has a maximum amount of energy in its magnetic field. The reason that this is called a tank circuit is that the energy inside sloshes between the inductor and the capacitor. If there were no parasitic resistances, this circuit could continue forever. This is very similar to the pendulum, where the potential energy is maximized and the kinetic energy is zero when the pendulum is at its highest position.

Likewise, when the pendulum is at its lowest position, the potential energy is minimized and the kinetic energy is maximized; the pendulum is moving at maximum speed at this time. However, there are resistances, so amplification is needed to sustain the oscillation.

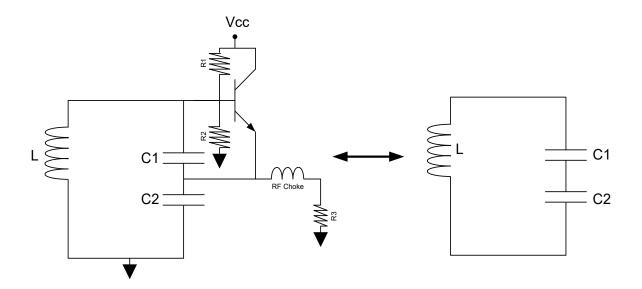

## Implementation of Amplifier

The traditional oscillator model of an amplifier and a delay in the feedback path is intuitive and easy to understand. However, a typical high frequency VCO does not typically use a voltage amplifier, but rather uses transistors devices with current gains. It is easier to visualize the principles of operation of this sort of oscillator as a tank circuit with some active circuit to sustain the oscillation. The basic idea is that the full voltage of the tank circuit drives the amplifier, but the output of the amplifier is lightly coupled to the tank circuit so as not to disturb the natural oscillations of the circuit. Aside from coupling in the amplified signal to the tank, the coupling network is also actually part of the tank as well. In Figure 8.3, capacitors C1 and C2 form the coupling network.

#### **VCO Structure**

### Oscillator Topologies

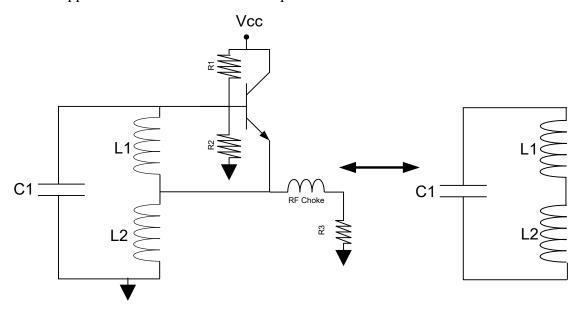

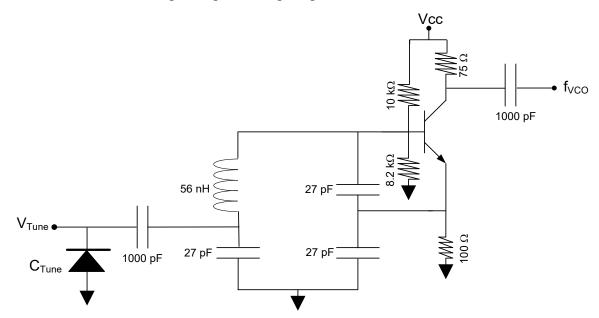

The common types of VCOs are Colpitts, Clapp, and Hartley. The thing that makes them different is how the output of the amplifying device is applied to the tank circuit.

In the Colpitts design, there is a capacitive divider that forms part of the resonant capacitance to which this is applied.

Figure 8.3 Colpitts Oscillator and Its Tank Circuit

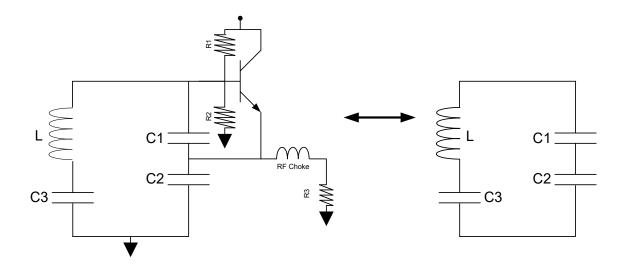

Figure 8.4 Clapp Oscillator and its Tank Circuit

The Clapp oscillator is very similar to the Colpitts oscillator, except for the fact that there is a series capacitor, C3 in this case, added in series with the inductor. It also goes by the name of Clapp-Gouriet and Series Tuned Colpitts Oscillator.

Figure 8.5 Hartley Oscillator and its Tank Circuit

In the Hartley oscillator, the feedback from the amplifier is applied to the inductor. To implement this, there are two inductors, and the voltage is applied between them. The sum of the two inductors forms the total inductance.

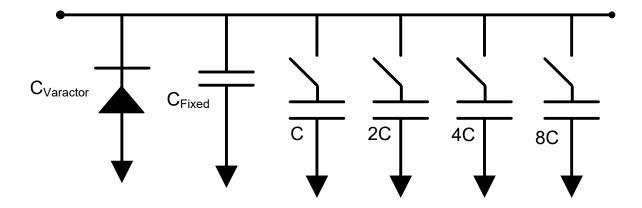

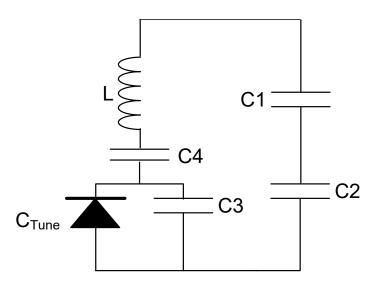

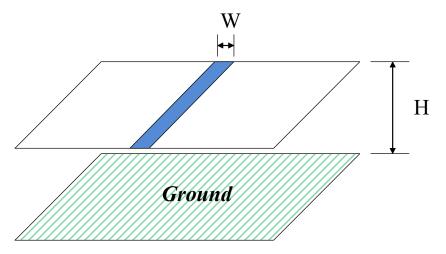

#### The Varactor Diode

The concept of the tank circuit has been discussed, but the circuits are only designed to operate at a single frequency; no mention has been made of what makes it possible to adjust the frequency. For the VCO, the varactor diode is the component that does this. It is a reverse biased diode that has a junction capacitance between the P and N junctions. Between these two junctions, there is a depletion layer. The width of this depletion layer widens as the reverse voltage across the diode is increases. Recall that for two parallel plates, the capacitance is inversely proportional to the distance between the plates. This situation applies to the varactor diode. As the voltage is increased, the capacitance becomes less in accordance with the following equation.

$$C_{Varactor}(V) = \frac{C_{Varactor}(0)}{(\alpha + V)^{\gamma}}$$

(8.2)

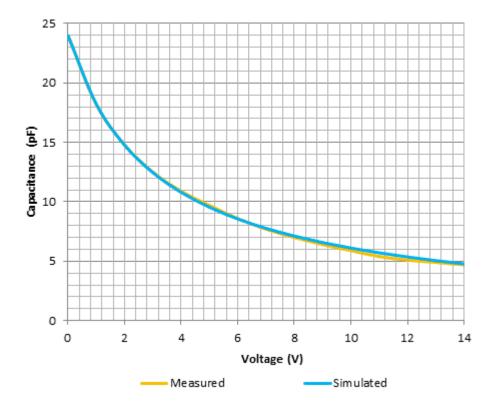

$C_{Varactor}(V)$  is the capacitance of the varactor diode,  $C_{Varactor}(0)$  is the diode capacitance specified at a zero volts.  $\alpha$  is the diode potential voltage, V is the voltage applied, and  $\gamma$  is an exponent that is typically on the order of 0.5. For instance, here is some data for the 1SV229 varactor diode as modeled from the datasheet with  $C_{Varactor}(0) = 24$  pF,  $\alpha = 2.8$ , and  $\gamma = 0.9$ .

Figure 8.6 Varactor Diode Capacitance for 1SV229 Diode

The varactor diode typically is placed in parallel with one of the capacitors in the tank circuit. Maximum tuning range is attained if the varactor diode completely replaces a capacitor, however the phase noise is typically better there is some capacitance in parallel with the varactor diode. This is because the quality factor of a fixed value capacitor is typically higher than that for the varactor. There are many techniques for reducing the noise due to the varactor diode, such as putting multiple ones in parallel, which divides their noise resistance.

## Oscillation Frequency Calculation

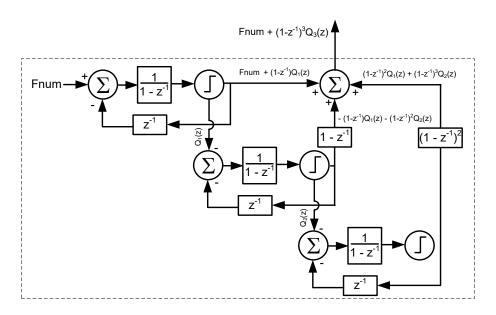

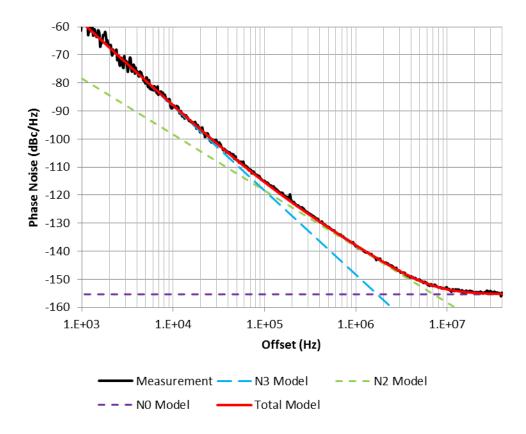

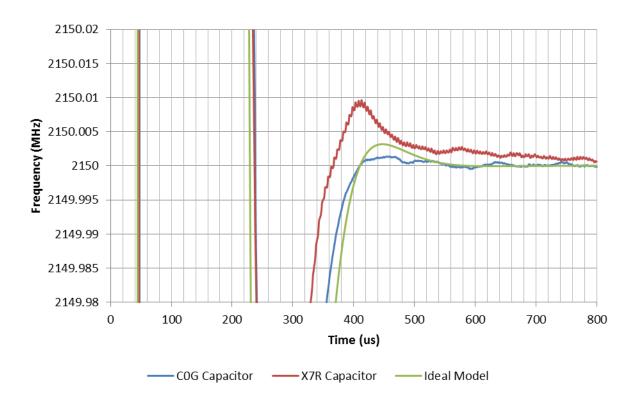

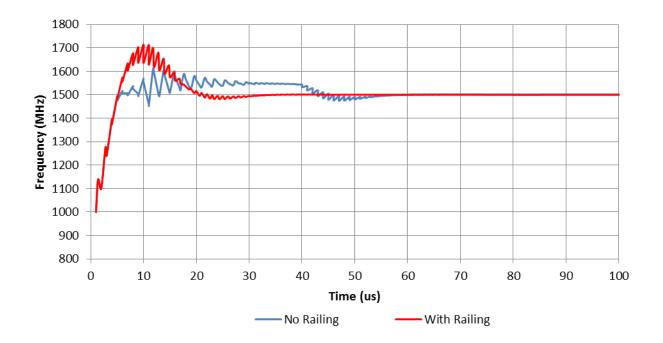

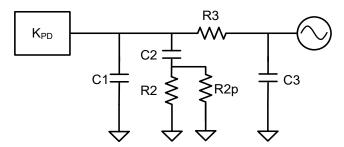

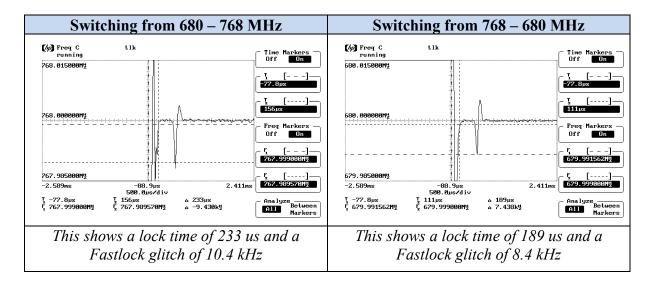

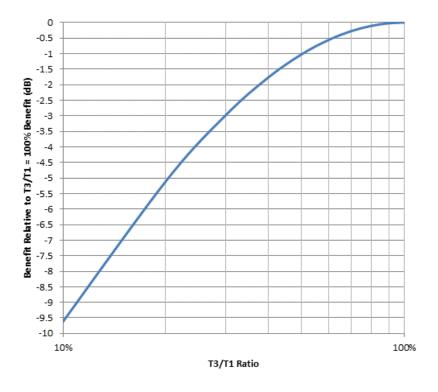

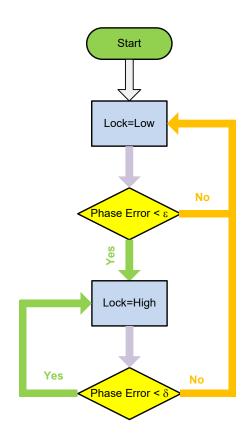

The theoretical oscillation frequency can be found once circuit inductance and capacitance are found. The value for the circuit inductance, L, is straightforward to calculate. The capacitance,  $C_{Equivalent}$ , is easier to find if one first simplifies the circuit by removing the amplifier and bias circuitry. The grounds can also be removed because the frequency is the same everywhere in the tank, so the placement of the ground can be ignored. This is done in Figure 8.3, Figure 8.4, and Figure 8.5.