# Using the TMS320DM643x Bootloader

Daniel Allred

#### **ABSTRACT**

This document describes the functionality of the DM643x ROM bootloader software. Please note that the ROM bootloader requires use of Application Image Script (AIS) as the primary data format for loading code/data. AIS is a Texas Instruments, Inc. proprietary data format that is explained in detail in Section 3 of this document.

Project collateral and source code discussed in this application report can be downloaded from the following URL: <a href="http://www.ti.com/lit/zip/SPRAAG0">http://www.ti.com/lit/zip/SPRAAG0</a>.

|        | Contents                                                       |    |  |  |  |  |  |

|--------|----------------------------------------------------------------|----|--|--|--|--|--|

| 1      | Introduction                                                   | 3  |  |  |  |  |  |

| 2      | Boot Mode Description                                          | 4  |  |  |  |  |  |

| 3      | Application Image Script2                                      |    |  |  |  |  |  |

| 4      | Booting Operating Systems ( Linux®/ DSP/BIOS™,etc.)            |    |  |  |  |  |  |

| 5      | ROM Bootloader RAM Memory Requirements and Code/Data Placement |    |  |  |  |  |  |

| 6      | ROM Bootloader Cache Considerations                            |    |  |  |  |  |  |

| 7<br>8 | AIS Generation Tool, genAISSample AIS Boot Images              |    |  |  |  |  |  |

| 9      | Debugging Boot Failures                                        |    |  |  |  |  |  |

| 10     | Determining On-Chip Bootloader Version                         |    |  |  |  |  |  |

| 11     | Calculating CRC                                                |    |  |  |  |  |  |

| 12     | References                                                     |    |  |  |  |  |  |

| App    | Appendix A Calculating the CRC                                 |    |  |  |  |  |  |

|        | List of Figures                                                |    |  |  |  |  |  |

| 1      | Signal Connections for I2C EEPROM Boot Mode                    | 12 |  |  |  |  |  |

| 2      | SPI Transfer With CLKSTP = 11 and CLKXP = 0                    | 15 |  |  |  |  |  |

| 3      | 24x8 Bit SPI EEPROM Read Timing                                | 20 |  |  |  |  |  |

| 4      | DM643x 24x8 Bit Address SPI Boot                               | 20 |  |  |  |  |  |

| 5      | Basic Structure of Application Image Script                    | 21 |  |  |  |  |  |

| 6      | Structure of SET Command                                       | 22 |  |  |  |  |  |

| 7      | Valid SET Command Data Types                                   | 23 |  |  |  |  |  |

| 8      | Structure of GET Command                                       | 24 |  |  |  |  |  |

| 9      | Structure of Section Load Command                              | 24 |  |  |  |  |  |

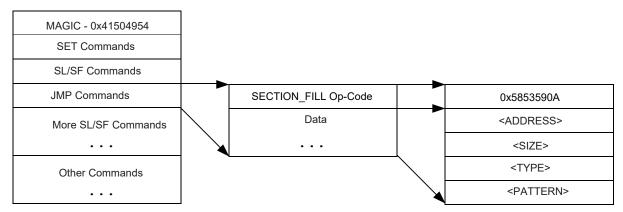

| 10     | Structure of Section Fill Command                              | 25 |  |  |  |  |  |

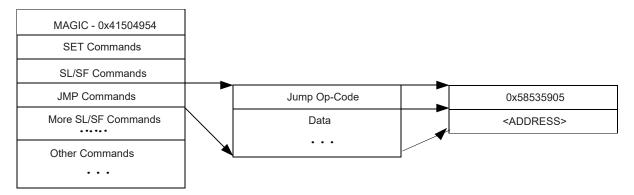

| 11     | Structure of Jump Command                                      | 25 |  |  |  |  |  |

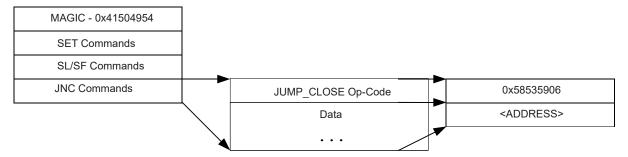

| 12     | Structure of Jump_Close Command                                | 26 |  |  |  |  |  |

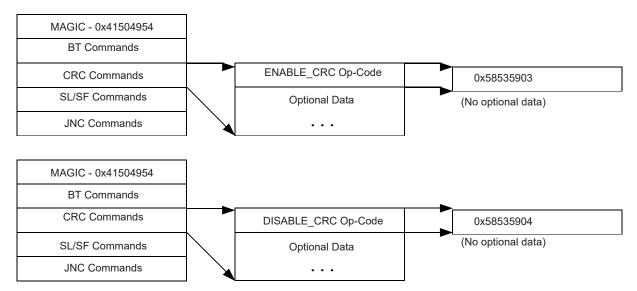

| 13     | Structure of Enable CRC/Disable CRC Commands                   |    |  |  |  |  |  |

| 14     | Structure of Request CRC Command                               | 28 |  |  |  |  |  |

| 15     | Structure of Function Execute Command                          | 29 |  |  |  |  |  |

| 16     | UART AIS Boot Image                                            | 40 |  |  |  |  |  |

| 1  | Terms and Abbreviations                                                                                                             | 3               |

|----|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2  | Non-Fastboot Modes (FASTBOOT = 0)                                                                                                   | <mark>5</mark>  |

| 3  | Fixed-Multiplier Fastboot Modes (FASTBOOT = 1, AEM[2:0] = 001b)                                                                     | 6               |

| 4  | User-Select Multiplier Fastboot Modes (FASTBOOT = 1, AEM[2:0] = 000b, 011b, 100b, or 101b)                                          | <mark>7</mark>  |

| 5  | PLL Multiplier Selection (PLLMS[2:0]) in User-Select Multiplier Fastboot Modes (FASTBOOT = 1; AEM[2:0] = 000b, 011b, 100b, or 101b) | 7               |

| 6  | PLL Multiplier Based on Value AEM and PLLMS[2:0] Pins                                                                               | 8               |

| 7  | PLL1 and PLL2 Multiplier Ranges                                                                                                     | 9               |

| 8  | PLLC1 Clock Frequency Ranges                                                                                                        | 9               |

| 9  | PLLC2 Clock Frequency Ranges                                                                                                        | 9               |

| 10 | CPU Frequency During FASTBOOT                                                                                                       | 9               |

| 11 | I2C EEPROM Layout for PCI Autoinitialization Data                                                                                   | 11              |

| 12 | I2C Timing Register Settings                                                                                                        | 13              |

| 13 | SPI Master Clock Frequencies for FASTBOOT = 1                                                                                       | 14              |

| 14 | SPI Master Boot Modes                                                                                                               | 15              |

| 15 | SPI 16x8 EEPROM-to-DSP McBSP0 Connection                                                                                            | 15              |

| 16 | Supported NAND Device Types                                                                                                         | 16              |

| 17 | UART Connection Attributes for Boot                                                                                                 | 17              |

| 18 | SPI EEPROM and DSP Pin Connections for 24 Bit SPI Mode                                                                              | 20              |

| 19 | AIS Version 2.0 Supported Opcodes                                                                                                   | 21              |

| 20 | Numeric Formats That Can Be Used in SET Command                                                                                     | <mark>22</mark> |

| 21 | Valid SET Command Data Types                                                                                                        | 23              |

| 22 | Valid SET Command Data Types Field Descriptions                                                                                     | 23              |

| 23 | Pre-Defined ROM Functions                                                                                                           |                 |

| 24 | Sample Function Execute Command                                                                                                     | 29              |

| 25 | DM643x Program Options                                                                                                              | 33              |

| 26 | EMIFA ROM Fast Boot AIS Boot Image Example                                                                                          |                 |

| 27 | I2C AIS Boot Image Example                                                                                                          | 36              |

| 28 | AIS Image in I2C EEPROM Memory                                                                                                      | 37              |

| 29 | SPI AIS Boot Image Example                                                                                                          | 37              |

| 30 | AIS Image in SPI EEPROM Memory                                                                                                      | 38              |

| 31 | NAND Boot AIS Boot Image Example                                                                                                    | 40              |

| 32 | Debugging Boot Failures                                                                                                             | 42              |

www.ti.com Introduction

#### 1 Introduction

The ROM bootloader resides in the ROM of the device beginning at ROM address 0x00100000. The ROM boot loader (RBL) implements methods for booting in the listed modes. It reads the contents of the BOOTCFG register to determine boot mode and performs appropriate commands to effect boot of device. If an improper boot mode is chosen or if for some reason an error is detected during boot from a slave device, the RBL communicates this through UART as default boot device.

When booting in master mode, the boot loader reads the boot information from the slave device as and when required. When booting in slave mode, the boot loader depends on the master device to feed the boot information as and when required. Please note that for all boot modes, the ROM bootloader disables the watchdog timer for a duration of boot. All applications MUST avoid configuring the watchdog timer during the boot process. (No AIS commands or code should change this during boot). Figure 16 shows a list of terms and abbreviations used in this application report

- Emulation boot

- HPI

- PCI (DSP as slave)

- EMIFA ROM direct boot

- · EMIFA ROM fast boot with AIS

- · EMIFA ROM fast boot without AIS

- NAND

- I2C (DSP as master)

- SPI 16×8 (DSP as master, 16 bits of address per SPI operation, supporting upto 64Kx8 devices)

- SPI 24×8 (DSP as master, 24 bits of address transmitted per SPI operation supporting upto 16Mx8 devices)

- · UART (DSP as slave), no flow control

- · UART (DSP as slave), with flow control

- VLYNQ (DSP as slave)

**Table 1. Terms and Abbreviations**

| Term       | Description                                                 |

|------------|-------------------------------------------------------------|

| Bootloader | SW/Code for ROM DM643x Bootloader                           |

| AIS        | Application Image Script                                    |

| BL         | Boot Loader (referring to the bootloader in this text)      |

| DSP        | Digital Signal Processor (referring to DM643x in this text) |

| EMIF       | External Memory Interface                                   |

| GPIO       | General-Purpose Input/Output                                |

| HPI        | Host Port Interface                                         |

| I2C        | Inter Integrated Circuit                                    |

| NAND       | Inverted AND Gate Not AND                                   |

| OFD        | Object File Display                                         |

| OS         | Op-Code Synchronization                                     |

| PCI        | Peripheral Component Interconnect                           |

| POS        | Ping Op-Code Synchronization                                |

| ROM        | Read Only Memory                                            |

| SPI        | Serial Peripheral Interface                                 |

| SRGR       | Sample Rate Generator Control Register                      |

| UART       | Universal Asynchronous Receiver/Transmitter                 |

DSP/BIOS is a trademark of Texas Instruments.

Linux is a registered trademark of Linux Torvalds in the U.S. and/or other countries.

Windows is a registered trademark of Microsoft Corporation in the United States and/or other countries.

All other trademarks are the property of their respective owners.

## 2 Boot Mode Description

The selection of the following boot modes depend upon the status of boot device pins. The status of these pins is captured on the rising edge of device POR reset into the BOOTCFG register. The bootloader reads the contents of the BOOTCFG register and branches to the appropriate code to implement the selected boot.

The boot modes are grouped into three categories — Non-Fastboot Modes, Fixed-Multiplier Fastboot Modes, and User-Select Multiplier Fastboot Modes.

- Non-Fastboot Modes (FASTBOOT = 0): The device operates in default phased-locked loop (PLL) bypass mode during boot. The Non-Fastboot bootmodes are shown in Table 2.

- Fixed-Multiplier Fastboot Modes (FASTBOOT = 1, AEM[2:0] = 001b): The bootloader code speeds

up the device during boot according to the fixed PLL multipliers. The Fixed-Multiplier Fastboot

bootmodes are shown in Table 3.

- **NOTE:** The PLLMS[2:0] configurations have *no* effect on the Fixed-Multiplier Fastboot Modes, as these pins function as AEAW[2:0] to select the EMIFA address width when AEM[2:0] = 001b.

- User-Select Multiplier Fastboot Modes (FASTBOOT = 1, AEM[2:0] = 000b,011b,100b,101b): The bootloader code speeds up the device during boot. The PLL multiplier is selected by the user via the PLLMS[2:0] pins. The User-Select Multiplier Fastboot bootmodes are shown in Table 4.

If an invalid boot mode is specified, the bootloader writes an error code to the ERR field of the BOOTCMPLT register and then defaults to UART boot for all non-host boot modes (for example, I2C, SPI).

Boot device pins must be configured to one of the valid modes. A description of each valid mode is given in subsequent sections.

All other modes *not* shown in these tables are reserved and invalid settings.

www.ti.com Boot Mode Description

# Table 2. Non-Fastboot Modes (FASTBOOT = 0)

| DEVICE BOOT AND CONFIGURATION PINS |        | воот                                                  | DM643x DMP     | PLLC1 CLOCK SETTING AT BOOT |                                     |                                  | DSPBOOTADDR   |

|------------------------------------|--------|-------------------------------------------------------|----------------|-----------------------------|-------------------------------------|----------------------------------|---------------|

| BOOTMODE[3:0]                      | PCIEN  | DESCRIPTION (1)                                       | (Master/Slave) | PLL<br>MODE (2)             | CLKDIV1 DOMAIN<br>(SYSCLK1 DIVIDER) | DEVICE<br>FREQUENCY<br>(SYSCLK1) | (DEFAULT) (1) |

| 0000                               | 0 or 1 | No Boot (Emulation Boot)                              | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 0001                               | 0 or 1 | Reserved                                              | -              | -                           | -                                   | _                                | _             |

| 0010                               | 0      | HPI Boot                                              | Slave          | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 0010                               | 1      | Reserved                                              | -              | -                           | -                                   | -                                | -             |

| 0011                               | 0 or 1 | Reserved                                              | -              | -                           | -                                   | -                                | -             |

| 0100                               | 0 or 1 | EMIFA ROM Direct<br>Boot<br>[PLL Bypass Mode]         | Master         | Bypass                      | /1                                  | CLKIN                            | 0x4200 000    |

| 0101                               | 0 or 1 | I2C Boot<br>[STANDARD<br>MODE] <sup>(3)</sup>         | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 0110                               | 0 or 1 | 16-bit SPI Boot<br>[McBSP0]                           | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 0111                               | 0 or 1 | NAND Flash Boot                                       | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 1000                               | 0 or 1 | UART Boot without<br>Hardware Flow<br>Control [UART0] | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 1001                               | 0 or 1 | Reserved                                              | -              | -                           | -                                   | _                                | -             |

| 1010                               | 0 or 1 | VLYNQ Boot                                            | Slave          | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 1011                               | 0 or 1 | Reserved                                              | -              | -                           | -                                   | -                                | -             |

| 1100                               | 0 or 1 | Reserved                                              | -              | -                           | -                                   | -                                | -             |

| 1101                               | 0 or 1 | Reserved                                              | -              | -                           | -                                   | -                                | _             |

| 1110                               | 0 or 1 | UART Boot with<br>Hardware Flow<br>Control [UART0]    | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

| 1111                               | 0 or 1 | 24-bit SPI Boot<br>(McBSP0 + GP[97])                  | Master         | Bypass                      | /1                                  | CLKIN                            | 0x0010 0000   |

<sup>(1)</sup> For all boot modes that default to DSPBOOTADDR = 0x0010 0000 (i.e., all boot modes except the EMIFA ROM Direct Boot, BOOTMODE[3:0] = 0100, FASTBOOT = 0), the bootloader code disables all C64x+ cache (L2, L1P, and L1D) so that upon exit from the bootloader code, all C64x+ memories are configured as all RAM. If cache use is required, the application code must explicitly enable the cache.

<sup>(2)</sup> The PLL MODE for Non-Fastboot Modes is fixed as shown in this table; therefore, the PLLMS[2:0] configuration pins have no effect on the PLL MODE.

<sup>(3)</sup> I2C Boot (BOOTMODE[3:0] = 0101b) is *only* available if the MXI/CLKIN frequency is between 21 MHz to 30 MHz. I2C Boot is *not* available for MXI/CLKIN frequencies less than 21 MHz.

## Table 3. Fixed-Multiplier Fastboot Modes (FASTBOOT = 1, AEM[2:0] = 001b)

| DEVICE BOOT AND CONFIGURATION PINS |        | BOOT DM643x DMP                                                 | PLLC1 CLOCK SETTING AT BOOT |                 |                                        | DODDOGTADDD                      |                              |

|------------------------------------|--------|-----------------------------------------------------------------|-----------------------------|-----------------|----------------------------------------|----------------------------------|------------------------------|

| BOOTMODE[3:0]                      | PCIEN  | DESCRIPTION (1)                                                 | (Master/Slave)              | PLL<br>MODE (2) | CLKDIV1 DOMAIN<br>(SYSCLK1<br>DIVIDER) | DEVICE<br>FREQUENCY<br>(SYSCLK1) | DSPBOOTADDR<br>(DEFAULT) (1) |

| 0000                               | 0 or 1 | No Boot (Emulation Boot)                                        | Master                      | Bypass          | /1                                     | CLKIN                            | 0x0010 0000                  |

| 0001                               | 0      | HPI Boot with PLL<br>Multiplier x27 at boot                     | Slave                       | x27             | /2                                     | CLKIN x27 / 2                    | 0x0010 0000                  |

|                                    | 1      | Reserved                                                        | -                           | -               | -                                      | _                                | -                            |

| 0010                               | 0      | HPI Boot with PLL<br>Multiplier x20 at boot                     | Slave                       | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

|                                    | 1      | Reserved                                                        | -                           | -               | _                                      | _                                | -                            |

| 0011                               | 0      | HPI Boot with PLL<br>Multiplier x15 at boot                     | Slave                       | x15             | /2                                     | CLKIN x15 / 2                    | 0x0010 0000                  |

|                                    | 1      | Reserved                                                        | -                           | -               | _                                      | -                                | -                            |

| 0100                               | 0 or 1 | EMIFA ROM<br>FASTBOOT<br>with Application<br>Image Script (AIS) | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 000                   |

| 0101                               | 0 or 1 | I2C Boot<br>[FAST MODE] <sup>(3)</sup>                          | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 0110                               | 0 or 1 | 16-bit SPI Boot<br>[McBSP0]                                     | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 0111                               | 0 or 1 | NAND Flash Boot                                                 | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 1000                               | 0 or 1 | UART Boot without<br>Hardware Flow<br>Control [UART0]           | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 1001                               | 0 or 1 | EMIFA ROM<br>FASTBOOT<br>without AIS                            | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 1010                               | 0 or 1 | VLYNQ Boot                                                      | Slave                       | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 1011                               | 0 or 1 | Reserved                                                        | -                           | -               | -                                      | -                                | -                            |

| 1100                               | 0 or 1 | Reserved                                                        | -                           | -               | -                                      | -                                | -                            |

| 1101                               | 0 or 1 | Reserved                                                        | -                           | -               | -                                      | -                                | -                            |

| 1110                               | 0 or 1 | UART Boot with<br>Hardware Flow<br>Control [UART0]              | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

| 1111                               | 0 or 1 | 24-bit SPI Boot<br>(McBSP0 + GP[97])                            | Master                      | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                  |

<sup>(1)</sup> For all boot modes that default to DSPBOOTADDR = 0x0010 0000, the bootloader code disables all C64x+ cache (L2, L1P, and L1D) so that upon exit from the bootloader code, all C64x+ memories are configured as all RAM. If cache use is required, the application code must explicitly enable the cache.

<sup>(2)</sup> The PLL MODE for Fixed-Multiplier Fastboot Modes is fixed as shown in this table; therefore, the PLLMS[2:0] configuration pins have no effect on the PLL MODE.

<sup>(3)</sup> I2C Boot (BOOTMODE[3:0] = 0101b) is *only* available if the MXI/CLKIN frequency is between 21 MHz to 30 MHz. I2C Boot is *not* available for MXI/CLKIN frequencies less than 21 MHz.

www.ti.com Boot Mode Description

Table 4. User-Select Multiplier Fastboot Modes (FASTBOOT = 1, AEM[2:0] = 000b, 011b, 100b, or 101b)

| DEVICE BOOT AND CONFIGURATION PINS |        | BOOT DM643x DMP                                       |                | PL              | DODDOOT4DDD                            |                                  |                                           |

|------------------------------------|--------|-------------------------------------------------------|----------------|-----------------|----------------------------------------|----------------------------------|-------------------------------------------|

| BOOTMODE[3:0]                      | PCIEN  | BOOT DESCRIPTION (1)                                  | (Master/Slave) | PLL<br>MODE (2) | CLKDIV1 DOMAIN<br>(SYSCLK1<br>DIVIDER) | DEVICE<br>FREQUENCY<br>(SYSCLK1) | - DSPBOOTADDR<br>(DEFAULT) <sup>(1)</sup> |

| 0000                               | 0 or 1 | No Boot (Emulation Boot)                              | Master         | Bypass          | /1                                     | CLKIN                            | 0x0010 0000                               |

|                                    | 0      | Reserved                                              | _              | -               | -                                      | _                                | -                                         |

| 0001                               | 1      | PCI Boot without<br>Auto Initialization               | Slave          | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

|                                    | 0      | HPI Boot                                              | Slave          | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 0010                               | 1      | PCI Boot with Auto<br>Initialization                  | Slave          | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 0011                               | 0 or 1 | Reserved                                              | _              | -               | -                                      | _                                | _                                         |

| 0100                               | 0 or 1 | EMIFA ROM<br>FASTBOOT<br>with AIS                     | Master         | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 0101                               | 0 or 1 | I2C Boot<br>[FAST MODE] <sup>(3)</sup>                | Master         | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 0110                               | 0 or 1 | 16-bit SPI Boot<br>[McBSP0]                           | Master         | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 0111                               | 0 or 1 | NAND Flash Boot                                       | Master         | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 1000                               | 0 or 1 | UART Boot without<br>Hardware Flow<br>Control [UART0] | Master         | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 1001                               | 0 or 1 | EMIFA ROM<br>FASTBOOT<br>without AIS                  | Master         | Table 5         | /2                                     | Table 5                          | -                                         |

| 1010                               | 0 or 1 | VLYNQ Boot                                            | Slave          | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                               |

| 1011                               | 0 or 1 | Reserved                                              | -              | -               | -                                      |                                  | _                                         |

| 1100                               | 0 or 1 | Reserved                                              | _              | -               | -                                      | _                                | _                                         |

| 1101                               | 0 or 1 | Reserved                                              | -              | -               | -                                      | -                                | _                                         |

| 1110                               | 0 or 1 | UART Boot with<br>Hardware Flow<br>Control [UART0]    | Master         | Table 5         | /2                                     | Table 5                          | 0x0010 0000                               |

| 1111                               | 0 or 1 | 24-bit SPI Boot<br>(McBSP0 + GP[97])                  | Master         | x20             | /2                                     | CLKIN x20 / 2                    | 0x0010 0000                               |

<sup>(1)</sup> For all boot modes that default to DSPBOOTADDR = 0x0010 0000, the bootloader code disables all C64x+ cache (L2, L1P, and L1D) so that upon exit from the bootloader code, all C64x+ memories are configured as all RAM. If cache use is required, the application code must explicitly enable the cache.

Table 5. PLL Multiplier Selection (PLLMS[2:0]) in User-Select Multiplier Fastboot Modes (FASTBOOT = 1; AEM[2:0] = 000b, 011b, 100b, or 101b)

| DEVICE BOOT AND CONFIGURATION PINS | PLLC1 CLOCK SETTING AT BOOT |                                     |                            |  |  |

|------------------------------------|-----------------------------|-------------------------------------|----------------------------|--|--|

| PLLMS[2:0]                         | PLL MODE                    | CLKDIV1 DOMAIN<br>(SYSCLK1 DIVIDER) | DEVICE FREQUENCY (SYSCLK1) |  |  |

| 000                                | x20                         | /2                                  | CLKIN x20 / 2              |  |  |

| 001                                | x15                         | /2                                  | CLKIN x15 / 2              |  |  |

| 010                                | x16                         | /2                                  | CLKIN x16 / 2              |  |  |

| 011                                | x18                         | /2                                  | CLKIN x18 / 2              |  |  |

| 100                                | x22                         | /2                                  | CLKIN x22 / 2              |  |  |

| 101                                | x25                         | /2                                  | CLKIN x25 / 2              |  |  |

| 110                                | x27                         | /2                                  | CLKIN x27 / 2              |  |  |

| 111                                | x30                         | /2                                  | CLKIN x30 / 2              |  |  |

<sup>(2)</sup> Any supported PLL MODE is available. [See Table 5 for supported DM643x PLL MODE options].

<sup>(3)</sup> I2C Boot (BOOTMODE[3:0] = 0101b) is *only* available if the MXI/CLKIN frequency is between 21 MHz to 30 MHz. I2C Boot is *not* available for MXI/CLKIN frequencies less than 21 MHz.

#### 2.1 Boot Requirements, Constraints, and Default Settings

Please make note of the following requirements:

- FASTBOOT is required for all PCI boot modes.

- Bootloader only supports 16-bit address width for I2C EEPROMs.

- For PCI boot with auto-initialization, an I2C EEPROM must be connected to I2C of the device.

- Please note that all boot timings are optimized for a 27 MHZ input clock frequency.

- I2C, SPI, UART, NAND, and EMIFA FASTBOOT (BOOTMODE[3:0]=0100b) requires data for boot to be stored in AIS Format. AIS is a Texas Instruments, Inc proprietary format for boot images. A detailed description of AIS is given in Section 3 of this document. Any formats used for HOST modes such as HPI and PCI is solely at the discretion of the user.

- When FASTBOOT is selected, the bootloader configures the PLL. The value of the PLL multiplier

depends on the status of the AEM and PLLMS[2:0] pins latched at reset into the BOOTCFG register.

This document bases all timing calculations assuming a 27 MHZ input clock to the device. For more

detailed information and presentation of a wider range of operating frequencies for FASTBOOT, see

the device-specific data sheet.

- The ROM bootloader does not support any NAND devices which specifically require the toggle of chip select signal for operation.

- · For NAND boot, the NAND device must be connected to EMIFA CS2.

- The bootloader disables CACHE during the boot process, regardless of boot mode chosen. The only boot mode exception is, direct EMIF boot, in which the boot loader is not invoked; therefore, CACHE is in power on the default state.

- The bootloader supports SPI EEPROMS with data arrangement x8 bits for all SPI-boot modes.

Becasue the bootloader only provides enough clocks to retrieve 8 bits of data, it cannot support devices with x16 bit data arrangement.

#### 2.2 FASTBOOT Mode

With the exception of emulation bootmode (BOOTMODE[3:0]==0000b), when FASTBOOT option is selected, the bootloader software programs the PLL. The PLL multiplier used depends on the value of the AEM and PLLMS[2:0] pins latched at reset. The bootloader reads the value of these pins as latched into the BOOTCFG register at device POR reset and selects PLL multiplier according to Table 6. For more detailed description of these settings and associated timings, see the device-specific data sheet.

Table 6. PLL Multiplier Based on Value AEM and PLLMS[2:0] Pins

| FASTBOOT | AEM    | PLLMS[2:0] | PLLM                                                                   |

|----------|--------|------------|------------------------------------------------------------------------|

| 1        | 001    | N/A        | If ((BOOTMODE[3:0] == 0001) && (PCIEN==0)) Then PLLM = 26 (CLKIN × 27) |

|          |        |            | If ((BOOTMODE[3:0]==0011) && (PCIEN==0)) Then PLLM=14 (CLKIN × 15)     |

|          |        |            | PLLM = 19 (CLKIN × 20) for all other values of BOOTMODE[3:0], PCIEN    |

| 1        | != 001 | 000        | PLLM = 19 (CLKIN × 20) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 001        | PLLM = 14 (CLKIN × 15) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 010        | PLLM = 15 (CLKIN × 16) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 011        | PLLM = 17 (CLKIN × 18) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 100        | PLLM = 21 (CLKIN × 22) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 101        | PLLM = 24 (CLKIN × 25) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 110        | PLLM = 26 (CLKIN × 27) for all values of BOOTMODE[3:0], PCIEN          |

|          |        | 111        | PLLM = 29 (CLKIN × 30) for all values of BOOTMODE[3:0], PCIEN          |

Note that the bootloader does not generate an error condition for invalid selections of the PLL multiplier. Therefore, care must be taken to ensure that the selected PLL multiplier does not exceed the timing constraints and operating frequency for boot peripheral or the PLL. Please see the following tables for constraints on PLL multipliers and clock frequencies. For more detailed information on these requirements, see the device-specific data sheet.

www.ti.com Boot Mode Description

## Table 7. PLL1 and PLL2 Multiplier Ranges

| PLL Multiplier (PLLM) | MIN | MAX |

|-----------------------|-----|-----|

| PLL1 Multiplier       | x14 | x30 |

| PLL2 Multiplier       | x14 | x32 |

## **Table 8. PLLC1 Clock Frequency Ranges**

| CI                           | MIN                        | MAX | UNIT              |     |

|------------------------------|----------------------------|-----|-------------------|-----|

| MXI/CLKIN                    |                            | 20  | 30 <sup>(1)</sup> | MHz |

| PLLOUT                       | At 1.2-V CV <sub>DD</sub>  | 400 | 600               | MHz |

|                              | At 1.05-V CV <sub>DD</sub> | 400 | 520               | MHz |

|                              | -600 devices               |     | 600               | MHz |

| SYSCLK1 (CLKDIV1 Domain)     | -500 devices               |     | 500               | MHz |

| STOCERT (GERDIV I Dollialli) | -400 devices               |     | 400               | MHz |

|                              | -300 devices               |     | 300               | MHz |

<sup>(1)</sup> MXI/CLKIN input clock is used for both PLL controllers (PLLC1 and PLLC2).

## Table 9. PLLC2 Clock Frequency Ranges

|                          | MIN                        | MAX | UNIT |     |

|--------------------------|----------------------------|-----|------|-----|

| MXI/CLKIN <sup>(1)</sup> |                            | 20  | 30   | MHz |

| PLLOUT                   | At 1.2-V CV <sub>DD</sub>  | 400 | 900  | MHz |

| PLLOUT                   | At 1.05-V CV <sub>DD</sub> | 400 | 666  | MHz |

| PLL2_SYSCLK1 (to DDR2 P  | HY)                        |     | 333  | MHz |

| PLL2_SYSCLK2 (to VPBE)   |                            |     | 54   | MHz |

<sup>(1)</sup> MXI/CLKIN input clock is used for both PLL controllers (PLLC1 and PLLC2).

## 2.2.1 CPU Frequency With FASTBOOT Options

The boot loader software uses a fixed PLL divider of 1 (divide by 2), for deriving CPU clock. Assuming an input oscillator frequency of 27 MHz, Table 10 lists the resulting CPU frequencies based on the PLLM values selected by FASTBOOT options.

**Table 10. CPU Frequency During FASTBOOT**

| PLLM | CPU Frequency (MHz) |

|------|---------------------|

| 19   | 270                 |

| 14   | 202.5               |

| 15   | 216                 |

| 17   | 243                 |

| 21   | 297                 |

| 24   | 337.5               |

| 26   | 364.5               |

| 29   | 405                 |

## 2.3 Emulation Boot (BOOTMODE[3:0] = 0000b, FASTBOOT = 0 or 1)

In this boot mode, the ROM boot loader software executes a software loop. The emulation software has responsibility for performing any code download and controlling the device. All FASTBOOT options are ignored for this boot mode. The PLL operates in bypass mode, yielding a CPU timing of 27 MHZ.

# 2.4 HPI Boot (BOOTMODE[3:0] = 0001b or 0010b, or 0011b, PCIEN = 0, FASTBOOT = 0 or 1)

In HPI-boot mode, the device bootloader hardware module branches to the start of the ROM bootloader software. Then, the ROM bootloader code performs the following sequence:

- 1. When FASTBOOT = 1, the bootloader programs the PLL based on PLL multiplier settings latched at reset, as discussed in Table 6.

- 2. Configures any HPI register that may be required.

- Clears the DSP Boot Address Register (DSPBOOTADDR). Clears boot error code field (BOOTCMPLT.ERR) and boot complete bit (BOOTCMPLT.BC) in the Boot Complete Register (BOOTCMPLT).

- 4. Posts HINT to the HOST device, signaling that the DSP is awake and ready for code download.

- 5. Enters a software loop waiting for non-zero value in the BOOTCMPLT.BC register.

- 6. When download of application is complete, the HOST writes the application start address into the DSPBOOTADDR register and then sets the boot complete bit in BOOTCMPLT register.

- 7. Once BOOTCMPLT.BC has been set by HOST, the ROM bootloader software branches to the address set by HOST in DSPBOOTADDR.

#### 2.5 PCI Boot

DM643x supports the PCI boot with DSP as PCI slave only. The bootloader implements the PCI boot with and without auto-initialization. When the PCI boot with auto-initialization is selected, the bootloader expects auto-init data to be stored in I2C EEPROM connected to I2C of the device. Please note that although the bootloader attempts boot when FASTBOOT mode is not enabled, this is NOT the recommended mode for the PCI boot. Please enable FASTBOOT with any PCI-boot mode to ensure PCI timing meets requirements.

#### 2.5.1 PCI Boot With No Auto-Initialization

In PCI-boot mode with no auto-initialization, the ROM bootloader performs the following steps:

- Bootloader configures PLL using the PLL multiplier selected based on the value of AEM and PLLMS[2;0] according to Table 6. (Please note that if FASTBOOT is not selected, the bootloader still attempts to complete boot. However, the PCI operating frequency may not meet minimal PCI requirements of 33 MHZ).

- 2. Clears the DSPBOOTADDR and BOOTCMPLT register fields.

- 3. When boot mode = 0001b, the ROM bootloader sets PCI CONFIG\_DONE bit in the PCI Configuration Done Register (PCICFGDONE) and the PCI Slave Control Register (PCISLVCNTL) to 1. When boot mode = 0010b, PCI auto-init mode is enabled and the ROM bootloader programs the PCI wrapper registers setting CONFIG\_DONE = 1 after this is complete.

- 4. The bootloader then enters a software loop polling for BOOTCMPLT.BC. Once boot complete is detected, the ROM bootloader software branches to the address set by the HOST in DSPBOOTADDR register.

When FASTOOT mode is selected along with the PCI boot, as the first step, the ROM bootloader software configures the PLL prior to clearing DSPBOOTADDR and BOOTCMPLT registers.

www.ti.com Boot Mode Description

#### 2.5.2 PCI With Auto-Initialization

When auto-initialization is used, the PCI configuration registers are programmed by the on-chip ROM Boot Loader (RBL) with the values stored in an I2C EEPROM connected to the I2C interface of the device.

PCI I2C EEPROM auto-initialization is enabled when BOOTMODE[3:0] = 0010b, PCIEN = 1, and FASTBOOT = 1. If auto-initialization is not enabled, the PCI configuration registers are left with their default values and the I2C EEPROM is not accessed for PCI configuration purposes. The function of the BOOTMODE[3:0], PCIEN, and FASTBOOT pins is fully described in the device data manual, refer to that document for more details.

When auto-initialization is enabled, the CONFIG\_DONE bit in the configuration done register (PCICFGDONE) takes a default value of 0. This prevents the PCI from responding to any requests. When auto-initialization is completed, the RBL sets the CONFIG\_DONE bit to 1 to allow the PCI to respond to requests.

#### 2.5.2.1 I2C EEPROM Memory Map

The on-chip ROM Bootloader requires big-endian format for the data stored in the I2C EEPROM. Byte addresses 400h through 41Bh of the I2C EEPROM are reserved for auto-initialization of PCI configuration registers. The remaining locations are not used for auto-initialization and can be used for storing other data. Table 11 summarizes the I2C EEPROM memory layout, as required for PCI auto-initialization.

The data as stored in I2C EEPROM must begin at I2C EEPROM address 0×400 and is formatted as shown in Table 11.

Table 11. I2C EEPROM Layout for PCI Autoinitialization Data

| Byte Address | Contents                   |

|--------------|----------------------------|

| 0x400        | Vendor ID [15:8]           |

| 0x401        | Vendor ID [7:0]            |

| 0x402        | Device ID [15:8]           |

| 0x403        | Device ID [7:0]            |

| 0x404        | Class code [7:0]           |

| 0x405        | Revision ID [7:0]          |

| 0x406        | Class code [23:16]         |

| 0x407        | Class code [15:8]          |

| 0x408        | Subsystem vendor ID [15:8] |

| 0x409        | Subsystem vendor ID [7:0]  |

| 0x40a        | Subsystem ID [15:8]        |

| 0x40b        | Subsystem ID [7:0]         |

| 0x40c        | Max_Latency                |

| 0x40d        | Min_Grant                  |

| 0x40e        | Reserved (use 0x00)        |

| 0x40f        | Reserved (use 0x00)        |

| 0x410        | Reserved (use 0x00)        |

| 0x411        | Reserved (use 0x00)        |

| 0x412        | Reserved (use 0x00)        |

| 0x413        | Reserved (use 0x00)        |

| 0x414        | Reserved (use 0x00)        |

| 0x415        | Reserved (use 0x00)        |

| 0x416        | Reserved (use 0x00)        |

| 0x417        | Reserved (use 0x00)        |

| 0x418        | Reserved (use 0x00)        |

| 0x419        | Reserved (use 0x00)        |

| 0x41a        | Byte Checksum              |

| 0x41b        | Reserved (must use 0xAA)   |

The PCI initialization data is expected to be stored in BIG-ENDIAN format.

#### 2.5.2.2 I2C EEPROM Checksum for Autoinitialization Data

The PCI configuration data contained in the I2C EEPROM is checked against a checksum. The configuration data is treated as an array of bytes, starting from the lowest I2C address (400h) to the highest (419h), for a total of 26 bytes.

Byte Checksum = AAh XOR Byte0(400h) XOR Byte1(401h)... XOR Byte25(419h)

If the I2C EEPROM is not accessed for PCI configuration purposes (that is, PCI\_EEAI = 0 at reset), then the checksum is not performed. If the checksum fails, the on-chip ROM bootloader defaults to the UART boot and it does not set the CONFIG\_DONE bit in the configuration done register (PCICFGDONE).

#### 2.5.2.3 DSP I2C EEPROM Interface

For PCI auto-initialization, the DSP supports I2C EEPROMs or devices operating as I2C slaves with the following features:

- The memory device complies with Philips I2C Bus Specification v 2.1

- The memory device uses two bytes for internal addressing; that is, the read/write bit followed by two bytes for addressing

- The memory device has the capability to autoincrement its internal address counter such that the contents of the memory device can be read sequentially

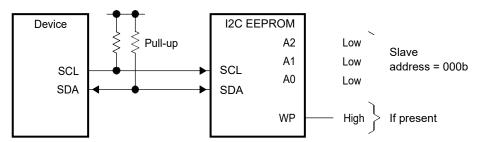

During PCI auto-initialization, the DSP acts as the master and the I2C EEPROM acts as the slave. Figure 1 shows the minimum connection required between the DSP and one I2C EEPROM. The required pull-ups must be placed on SDA and SCL to ensure that the I2C EEPROM interface works correctly. The slave address of the I2C EEPROM slave address must be set to 50h.

Figure 1. Signal Connections for I2C EEPROM Boot Mode

Some I2C EEPROMs have a write-protect (WP) feature that prevents unauthorized writes to memory. This feature is not needed for auto-initialization because the DSP will only read data from the I2C EEPROM. The write protect feature can be enabled or disabled.

For detailed information on the I2C, see the *TMS320DM643x DMP Inter-Integrated Circuit (I2C) Peripheral User's Guide* (SPRU991).

#### 2.6 EMIFA ROM Direct Boot (BOOTMODE[3:0] = 0100b, FASTBOOT = 0)

EMIFA direct boot does not require intervention from the ROM bootloader software. The DSP hardware boot module causes direct branch to start of EMIFA memory at address 0×42000000.

## 2.7 EMIFA ROM Fast Boot Without AIS (BOOTMODE[3:0] = = 1001b, FASTBOOT == 1)

In this boot mode, the ROM bootloader configures the PLL based on values of AEM and PLLMS[2:0] pins latched at reset. Then, it branches directly to address 0×42000000. This boot mode effectively operates the same as EMIFA direct boot (BOOTMODE[3:0]==0100b, FASTBOOT==0), with exception that the PLL is now configured. This enables faster EMIF clock to speed boot from an external device.

www.ti.com Boot Mode Description

# 2.8 EMIFA ROM Fast Boot With AIS (BOOTMODE[3:0] = 0100b, FASTBOOT = 1)

During EMIFA FAST ROM boot mode the DSP hardware boot module transfers control to the ROM bootloader software. This boot mode operates differently than the EMIFA direct boot. The ROM bootloader controls the boot process, first programming the PLL to operate at faster CPU speeds, then reading code/data starting at EMIFA address 0×42000000. The data stored in the FLASH/ROM must be in AIS format. A description of AIS is given in Section 3 of this document. The AIS boot image consists of AIS commands and data necessary to load the application code into the DSP memory. Using the AIS format, eliminates requirement for user defined secondary boot loader to load code. The ROM bootloader processes AIS commands from the EMIFA ROM until an AIS JUMP\_CLOSE instruction is encountered. The JUMP\_CLOSE instruction contains the application code start address. This command signals that the application has been fully loaded and all AIS commands have been processed for the boot. The ROM bootloader clears its internal state and then branches to the start of the application code. EMIF FASTBOOT sequence:

- 1. Programs the PLL using the PLL multiplier selected by the value of the AEM and PLLMS[2:0] pins as shown in Table 6.

- 2. Reads the value of the 8\_16 pin as latched into the BOOTCFG register and sets the EMIF data width accordingly.

- 3. Fetches the AIS data from the external memory and processes the AIS commands until the JUMP CLOSE command is encountered.

- 4. Branches to the application start address given in the JUMP CLOSE command.

# 2.9 I2C Master Mode Boot (BOOTMODE[3:0] = 0101b, FASTBOOT = 0 or 1)

The DM643x supports the I2C boot with DSP as I2C master only. The DSP hardware boot module transfers control to the ROM bootloader software at device reset. The ROM bootloader configures the I2C peripheral device, and begins read of data from the I2C EEPROM. The data stored in the I2C EEPROM is expected to be in AIS format. The first 32 bits are ignored by the bootloader; this location is currently reserved. The second 32 bit word must contain the AIS magic number. The remaining data in the I2C EEPROM must be in AIS format. Please refer to Section 3 for details of AIS. Boot sequence for I2C is as follows:

- 1. When FASTBOOT = 1, bootloader programs PLL using PLL miltiplier selected by values of AEM and PLLMS[2:0] as seen in Table 6.

- 2. Configures I2C for master mode with slave address register set to 0x50, and own address register set to 0x29.

- 3. Processes each AIS command until JUMP CLOSE command is encountered.

- 4. Branches to application start address

- 5. If an error occurs during the I2C boot process, the bootloader writes an error condition in the ERR field of the BOOTCMPLT register. Then, it attempts to perform boot through UART.

#### 2.9.1 I2C Master Boot Timing

The bootloader sets the following values for I2C clock pre-scale and clock low hold/clock high hold registers:

| FASTBOOT | Register | Value |

|----------|----------|-------|

| 0        | IPSC     | 0x2   |

|          | ICCLKH   | 0x2D  |

|          | ICLKL    | 0x2D  |

| 1        | IPSC     | 0x2   |

|          | ICCLKH   | 0x8   |

|          | ICCLKL   | 0x8   |

**Table 12. I2C Timing Register Settings**

The frequency of the I2C master clock is derived by:

I2C master clock frequency =

$$\frac{I2C \text{ peripheral clock frequency}}{(IPSC + 1)^* \lambda (ICCLKL + D) + (ICCLKH + D)}$$

For DM643x , the I2C input clock is directly derived from CLKIN. The value of the quantity represented by "D" is determined by the IPSC value (IPSC > 1, D = 5, IPSC = 1, D = 6, IPSC = 0, D = 7). For purposes of determining the I2C master clock used for boot, D = 5, since the boot loader software always programs a value of 2 for IPSC. Assuming an input oscillator frequency of 27 MHz, the settings for IPSC< ICLKH, ICCLKL, in Table 12 yields the following I2C master clock frequencies:

FASTBOOT == 1

I2C Master clock ~ 310 Khz

FASTBOOT == 0

I2C Master clock ~87 Khz

Please note that the input clock for the I2C module bypasses the PLL, therefore any FASTBOOT option settings using AEM and PLLMS[2:0] and subsequent PLLM selection has no effect on the frequency of the I2C master clock.

#### 2.10 SPI 16x8 Master Mode Boot (BOOTMODE[3:0] = 0110b, FASTBOOT = 0 or 1)

SPI 16x8 boot is implemented by configuring MCBSP0 of the device to operate in SPI mode. This mode supports SPI EEPROMS that require 16 bits of address and fetch/receive 8 bits of data. Sixteen bits of address allows boot from SPI devices with sizes upto 64Kx8. The bootloader only supports DSP as SPI master for this boot mode. The bootloader software configures MCBSP0 for SPI mode with 32 bit data transmit/receive. The SPI read command and 16 bit address are packed into the upper 3 bytes of the 32-bit word. The fourth empty byte provides the clock cycles needed to retrieve 8 bits of data out from the SPI EEPROM. The boot flow is as follows:

- 1. If FASTBOOT is enabled, the bootloader programs PLL using PLLM value selected according to Table 6.

- 2. The bootloader then reads AIS formatted boot image from EEPROM.

- 3. When last AIS command is encountered (JUMP CLOSE command) the bootloader branches to application entry address given in the command.

#### 2.10.1 SPI 16x8 Master Boot Timing

The SPI master clock frequency is derived from the internal clock provided to the MCBSP0. The peripheral clock is derived by a fixed divide of 1/6 the CPU clock. The master clock is then further divided by the value of the CLKGDV field of the MCBSP's SRGR. The bootloader software fixes the CLKGDV at a value of 0x2. This provides a divide down ratio of 1/3 of the MCBSP input clock. Table 13 shows the derived master clock frequency based on the possible PLLM values.

| PLLM | PLLOUT (MHz) | CPU (MHz) | MCBSP (MHz) | SPI Master (MHz) |  |

|------|--------------|-----------|-------------|------------------|--|

| 19   | 540          | 270       | 45          | 15               |  |

| 14   | 404          | 202       | 33.7        | 11               |  |

| 15   | 432          | 216       | 36          | 12               |  |

| 17   | 486          | 243       | 40.5        | 13.5             |  |

| 21   | 594          | 297       | 49.5        | 16.5             |  |

| 24   | 675          | 337       | 56          | 18.7             |  |

| 26   | 729          | 364       | 60.7        | 20.2             |  |

| 29   | 810          | 405       | 67.5        | 22.5             |  |

|      |              |           |             |                  |  |

Table 13. SPI Master Clock Frequencies for FASTBOOT = 1

www.ti.com Boot Mode Description

Please note that the timings given in the table are based on 27 Mhz input clock frequency. Please check the device-specific datasheet and the datasheet for the your SPI EEPROM to determine proper timiing and frequency range.

#### 2.10.2 SPI 16x8 Master Boot Signal Polarity

MCBSP0 is configured for SPI Master boot with the following modes selected:

Register

Value

PCR

Field Values Set

FSXM = 1, FSRP = 1, CLKXM = 0, FSXP = 1

SPCR

Field Values Set

CLKSTP = 3, (11b)

RCR

Field Values Set

RDATDLY = 1

XCR

Field Value Set

XDATDLY = 1

**Table 14. SPI Master Boot Modes**

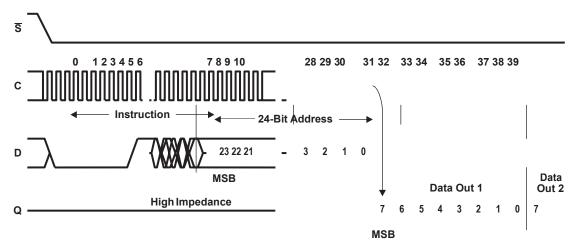

With these modes selected, the SPI master clock polarity is inactive high, and a MCBSP begins data transfer one-half clock cycle prior to first rising edge of clock amd samples input data on the rising edge of the clock. This operation supports SPI EEPROMS that sample data on rising edge of clock, and send data out on falling edge of clock.

Figure 2. SPI Transfer With CLKSTP = 11 and CLKXP = 0

For further details on how the MCBSP operates when in SPI mode, please refer to the *TMS320C6000 Multi-Channel Buffered Serial Port User's Guide* (SPRU580).

#### 2.10.3 Connecting SPI EEPROM for SPI 16x8 Boot

To enable boot from 16x8 SPI EPPROM, the EEPROM should be connected to McbSP0 pins in accordance with Table 15

| SPI EEPROM | McBSP0 |  |

|------------|--------|--|

| Sn         | FSX0   |  |

| С          | CLKX0  |  |

| D          | DX0    |  |

| Q          | DR0    |  |

Table 15. SPI 16x8 EEPROM-to-DSP McBSP0 Connection

## 2.11 NAND Flash Boot (BOOTMODE[3:0] = 0111b, FASTBOOT = 0 or 1)

NAND flash boot is fully supported on Rev 1.30 of the device. For Rev 1.0 and Rev 1.20, this boot mode was supported through secondary boot only. On Rev 1.30 of the device, the bootloader supports boot using AIS image script stored in NAND starting at Block 1 or above. The bootloader searchs for the AIS magic number in the first 32 bits of the of the page 0 of the block. If the magic number is not found, it continues searching through all of the NAND blocks until the last block is searched. If the magic number is not found it will abort the bootloader code skips bad blocks. A bad block is indicated when the bootloader detects the value 0xBADDBADD in starting in byte offset 0x4 in the NAND block spare memory area. When a bad block is detected, the bootloader skips this block and proceeds to the next block. The bootloader also performs 1 bit ECC correction when errors are detected in data read from the block. The bootloader uses the hardware ECC calculation provided by the DMP's EMIF module to detect and correct ECC errors.

On Rev 1.0 and Rev 1.20 of the device, there is a race condition in the polling for NAND ready in the ROM bootloader that prevents successful boot from NAND. Therefore, this boot mode is not fully supported in ROM. Workaround for this problem is to boot from any of the other supported boot methods, such as I2C or SPI, and allow a secondary bootloader to load code from NAND Flash. A sample secondary boot loader and the code needed to Flash the secondary code to I2C or SPI is given in the attachment to this document. A list of devices supported by the secondary NAND boot is given in Table 16. Please note that the secondary bootloader does not support any NAND devices that specifically require toggle of chip select signal for operation. The NAND device used for boot must be connected to EMIFA CS2.

Table 16. Supported NAND Device Types

| Device ID | Page Size | Total Memory Size |

|-----------|-----------|-------------------|

| 0×E3      | 512+16    | 4 MB              |

| 0×E5      | 512+16    | 4 MB              |

| 0×E6      | 512+16    | 8 MB              |

| 0×39      | 512+16    | 8 MB              |

| 0×6B      | 512+16    | 8 MB              |

| 0×73      | 512+16    | 16 MB             |

| 0×33      | 512+16    | 16 MB             |

| 0×75      | 512+16    | 32 MB             |

| 0×35      | 512+16    | 32 MB             |

| 0×43      | 512+16    | 16 MB             |

| 0×45      | 512+16    | 32 MB             |

| 0×53      | 512+16    | 16 MB             |

| 0×55      | 512+16    | 32 MB             |

| 0×76      | 512+16    | 64 MB             |

| 0×36      | 512+16    | 64 MB             |

| 0×79      | 512+16    | 128 MB            |

| 0×71      | 512+16    | 256 MB            |

| 0×46      | 512+16    | 64 MB             |

| 0×56      | 512+16    | 64 MB             |

| 0×74      | 512+16    | 128 MB            |

| 0×F1      | 2048+64   | 128 MB            |

| 0×A1      | 2048+64   | 128 MB            |

| 0xAA      | 2048+64   | 256 MB            |

| 0×DA      | 2048+64   | 256 MB            |

| 0×AC      | 2048+64   | 512 MB            |

| 0×DC      | 2048+64   | 512 MB            |

| 0×B1      | 2048+64   | 128 MB            |

| 0×C1      | 2048+64   | 128 MB            |

www.ti.com Boot Mode Description

The secondary bootloader expects the data in NAND to be in AIS format. Please note that AIS data is considered to be a serial stream, therefore, all AIS data must be contained in contiguous pages/blocks within the Flash. Currently, the secondary bootloader makes no attempt to bypass bad blocks. Once it has determined location for the start of AIS data, it assumes that the remaining data is in contiguous 'good' blocks of memory. The secondary bootloader does perform 1 bit error correction, when ECC 1 bit error is detected. The bootloader begins the search of AIS data from block 1 of the memory and searches all of the remaining blocks to find the AIS magic number. Block 0 is reserved for use of the application.

## 2.12 UART Boot (BOOTMODE[3:0] = 1000b, 1110b, FASTBOOT = 0 or 1)

UART boot differs from the other boot modes in that the bootloader software performs some communication with the HOST during the boot process. The bootloader performs the following sequence when UART boot is selected.

- 1. When FASTBOOT = 1, the bootloader programs the PLL using the PLL mulitplier selected according to Table 6.

- 2. Bootloader configures UART registers as required by chosen mode.

- 3. Bootloader sends message BOOTME through the serial interface to the HOST.

- 4. Bootloader waits response from the HOST in the form of the AIS magic number. The bootloader will continually loop, waiting for response.

- 5. When response is received from HOST< the bootloader processes AIS commands as read from the serial interface until a JUMP CLOSE command is encountered.

- 6. When JUMP CLOSE command is read, the bootlander sends message, DONE, to the HOST and then branches to the application start address.

Please note that the AIS commands are expected to be in ASCII representation, hence to send the AIS magic word, 0x41504954, the character sequence "41","50","49","54", is expected to be recieved by the bootloader. A sample AIS stream for UART boot is given in Section 3.

### 2.12.1 UART Boot Timing

Operationally, UART boot via BOOTMODES[3:0]==1000b and 1110b are essentially the same. The difference is in the management of data flow. When BOOTMODE[3:0] = 1000b, UART boot is executed without use of hardware flow control. UART BOOTMODE[3:0]=1110b is selected, then the UART is configured to use the hardware flow control module. In both modes the UART FIFO is enabled, and is set for the maximum FIFO size of 14.

The bootloader software does not use auto-baud detect. The UART clock divide registers are set for a total divide down value of 15. With a 27 MHZ input clock, this yields an approximate baud rate of 115 kbps (kilobits per second). The input clock supplied to the UART bypasses the PLL, therefore this baud rate is unaffected by PLL configuration and advantage can be taken of the FASTBOOT modes for faster CPU clock. The required connection settings for UART boot are given in Table 17

Attribute

Value

Baud Rate

115 kbps

Data Bits

8

Stop Bits

1

Parity

None

Flow Control

Hardware flow control (BOOTMODE[3:0] == 1110b), or none (BOOTMODE[3:0] == 1000b)

**Table 17. UART Connection Attributes for Boot**

#### 2.13 VLYNQ Boot (BOOTMODE[3:0]=1010b, FASTBOOT = 0 or 1)

The ROM bootloader supports boot via VLYNQ with DSP as VLYNQ slave. The bootloader ensures that VLYNQ is enabled and then polls for BOOTCMPLT.CMPLT flag in the BOOTCMPLT register to indicate that the download of application by VLYNQ Host is complete. The bootloader will then branch to the start address in DSPBOOTADDR as written by the VLYNQ Host. The boot process for VLYNQ then is as follows:

- 1. If FASTBOOT is enabled bootloader configures PLL according using appropriate PLL multiplier.

- 2. Bootloader makes sure VLYNQ is enabled.

- 3. Bootloader executes empty loop polling for BOOTCMPLT.CMPLT flag.

- 4. VLYNQ Host downloads application to DSP.

- 5. VLYNQ Host writes application start address to DSPBOOTADDR register.

- 6. VLYNQ Host writes 1 to BOOTMCPLT.CMPLT register flag.

- 7. Bootloader detects BOOTCMPLT.CMPLT and branches to start address in DSPBOOTADDR.

#### 2.13.1 VLYNQ Boot Timing

There are two independent clocks that should be considered when configuring the DSP for boot from VLYNQ. There are 1) the VLYNQ clock (data clock) and 2) the internal VLYNQ module clock. Because the DSP is acting as VLYNQ slave for purposes of boot, the VLYNQ clock (data clock) will be provided externally by a VLYNQ master. This is the clock that determines the VLYNQ data rate. The VLYNQ clock frequency should be determined by the system requirements and is independent of the internal VLYNQ module clock frequency.

The internal VLYNQ module clock is provided by the clock module within the DSP and is affected by CLKIN/PLLOUT depending on PLL mode. When PLL is in bypass mode, the internal VLYNQ module clock is derived from CLKIN and has value CLKIN/6. When any of the FASTBOOT options are chosen, then PLL is no longer in bypass mode, and internal VLYNQ module clock timing is derived from PLLOUT, and has value SYSCLK1/6 (SYSCLK1 is CPU clock). The internal VLYNQ module clock should not exceed 99 Mhz. So care should be taken when choosing PLL multipliers for FASTBOOT option that the value of SYSCLK1 does not exceed 594 Mhz, keeping internal VLYNQ module clock at or below the rated operating frequency of 99Mhz. Again, the 99Mhz limitation is on internal VLYNQ module clock ONLY and has no effect on the external VLYNQ clock (data clock) provided by the VLYNQ Master.

## 2.14 SPI 24×8 Master Mode Boot (BOOTMODE[3:0]=1111b, FASTBOOT = 0 or 1)

This bootmode supports SPI EEPROMs that require 24 bits of address and transfer 8 bits of data per read/write cycle. Twenty-four bits of address allows support of SPI EEPROMS with size upto 16Mx8. As in SPI 16-bit mode, data stored in the SPI EEPROM is expected to be formatted as a valid AIS image and follows the same boot flow:

- 1. If FASTBOOT is enabled, bootloader configures PLL

- 2. The bootloader then reads AIS formatted boot image from EEPROM.

- 3. When last AIS command is encountered (JUMP CLOSE command) the bootloader branches to application entry address given in the command.

To enable communication with SPI EEPROMs that require 24 bits of address, the McBSP is configured differently for 24 bit SPI Master mode boot, than in 16x8 Master mode. The McBSP has a native limitation of 32 bits for transmit/receive when operating in SPI mode. To effectively address SPI EEPROMs requiring 24 bits of address, 40 bits are actually needed; 8 bits of command + 24 bits of address + 8 bits to clock data in/out of the EEPROM. So in SPI 24x8 Master boot, a GPIO pin is used as chip select signal, instead of FSX0 which is normally connected for this purpose. When using this boot mode the FSX0 pin should not be connected and is unused. McBSP0 is then configured to transmit/receive 8 bit data. Please note that chip select is assumed inactive high for this boot mode. The 40 bits needed to communicate with the SPI device are transmitted in separate bytes. The transmit sequence from the DSP to EEPROM is:

1. Assert GPIO (drive GPIO high initially before McBSP0 is released to avoid premature chip select toggle).

www.ti.com Boot Mode Description

- 2. De-assert GPIO (driving chip select low).

- 3. Transfer 8 bits of SPI command.

- 4. Transfer SPI addres bits [23:16].

- 5. Transfer SPI address bits [5:8].

- 6. Transfer SPI addres bits [7:0].

- 7. Send 8 dummy bits to enable clock out of data from EEPROM.

- 8. Bootloader reads 8 bits from DR0.

- 9. Assert GPIO (drive chip select high).

#### 2.14.1 SPI 24x8 Master Boot Timings

Timings for SPI 24x8 Master Boot is determined by system PLL settings and McBSP0 divide down clock. These are described in detail in Section 2.10.1

## 2.14.2 SPI 24x8 Boot Signal Polarity

The McBSP SPI mode settings for 24x8 mode are the same as for 16x8 SPI Master mode, CLKSTP = 11b, CLKXP = 0. In this mode, data is transmitted from DSP one-half cycle prior to rising edge of clock and received on rising edge of clock. This operational mode is compatible with SPI EEPROMS which sample data in on rising edge of clock and clock data out on the falling edge.

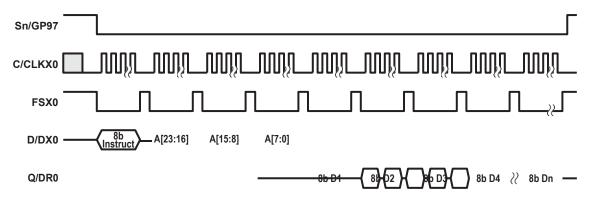

The read timings for the 24-bit SPI mode are given below. Figure 3 shows example 24x8 bit SPI EEPROM read timing.

Figure 3. 24x8 Bit SPI EEPROM Read Timing

Figure 4 shows how the DM643x 24x8 bit SPI boot works. Table 18 shows the pin connection between the DM643x and the 24x8 SPI EEPROM.

Figure 4. DM643x 24x8 Bit Address SPI Boot

## 2.14.3 Connecting SPI EEPROM for SPI 24x8 Boot

For 24×8 bit SPI mode, the McBSP0 pins must be connected to the SPI EEPROM according to Table 18

Table 18. SPI EEPROM and DSP Pin Connections for 24 Bit SPI Mode

| SPI EEPROM | DSP    | Comment                                             |  |

|------------|--------|-----------------------------------------------------|--|

| Sn         | GPIO97 | GPIO97 Connects GPIO97 to chip select of SPI EEPROM |  |

| С          | CLKX0  | Connects CLKX0 to clock of SPI EEPROM               |  |

| D          | DX0    | DX0 Connects DX0 to data in of SPI EEPROM           |  |

| Q          | DR0    | Connects DR0 to data out of SPI EEPROM              |  |

| -          | FSX0   | Leave uncconected, this signal is not used          |  |

## 3 Application Image Script

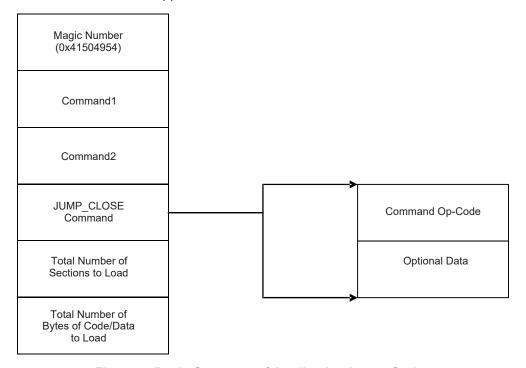

The bootloader accepts boot information in the form of a script, called application image script (AIS). Application image script is a Texas Instruments, Inc. proprietary application image transfer format. This script is a binary file consisting of a script header followed by various commands that can be interpreted and executed by the boot loader. Each command contains an op-code, followed by optional additional data required to execute the op-code. The bootloader currently supports AIS version 1.99; all commands and data are assumed to be 32 bits in width.

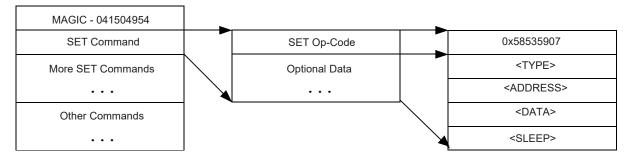

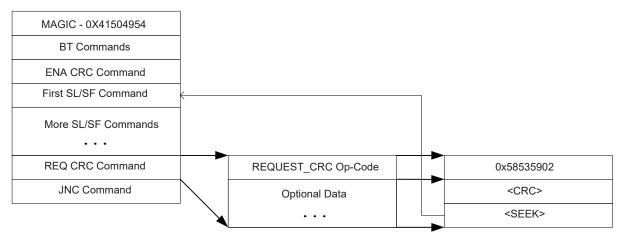

The AIS starts a header that consists of a magic word (0×41504954); the header is then followed by a series of commands as shown in Figure 5. Each command consists of an op-code followed by optional additional data. All AIS command streams are terminated with a JUMP\_CLOSE command which causes transfer of control to the loaded application code and terminates execution of the ROM bootloader.

Figure 5. Basic Structure of Application Image Script

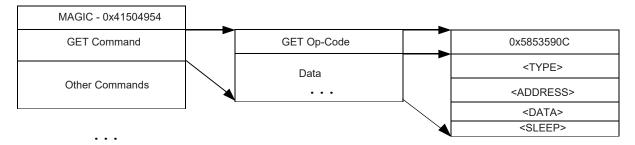

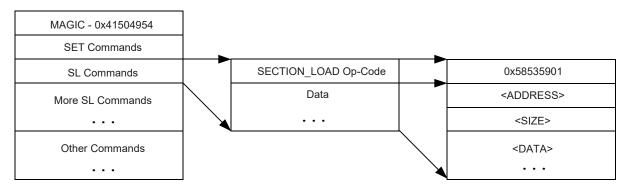

The bootloader only accepts data in AIS format for all modes except HPI ad PCI. The following sections define each command with appropriate op-code, structure and placement in AIS. Table 19 lists the various opcodes that are supported by AIS 1.0.

| Table | 19. AIS \ | ersion 2 | 2.0 Suppor | rted Opcode | <del>)</del> S |

|-------|-----------|----------|------------|-------------|----------------|

|       |           |          |            |             |                |

| Opcode       | Value      |  |

|--------------|------------|--|

| Section Load | 0×58535901 |  |

| Request CRC  | 0×58535902 |  |

| Enable CRC   | 0×58535903 |  |

| Disable CRC  | 0×58535904 |  |

| Jump         | 0×58535905 |  |

| Jump_Close   | 0×58535906 |  |

| Set          | 0×58535907 |  |

| Start Over   | 0×58535908 |  |

| Reserved     | 0×58535909 |  |

| Section Fill | 0×5853590A |  |

| Get          | 0×5853590C |  |

Application Image Script www.ti.com

Table 19. AIS Version 2.0 Supported Opcodes (continued)

| Opcode           | Value      |

|------------------|------------|

| Function Execute | 0x5853590D |

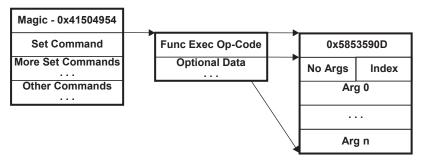

#### 3.1 SET Command

The SET command is a simple mechanism that enables you to write 8-bit, 16-bit or 32-bit data to any address in DSP address space. One of the arguments to this command implements a delay after the memory write happens. This can be used for memory mapped register write to take effect. Set commands may be used to configure various peripherals of the DSP. This includes PLL and EMIF at minimum and can configure more peripherals if required.

When DSP comes up from reset, the PLL is in bypass mode. As a result, the CPU is clocked at the same frequency as connected crystal/CLK IN, which is generally very low. This results in slow communication and high boot time. Selecting FASTBOOT mitigates this by programming the PLL with a slightly higher multiplier of 0×C, but this does not change default EMIF wait states, etc. In order to reduce boot time, the PLL and EMIF registers can be re-configured at the very beginning of the boot process using a series of SET commands. For this reason, all SET commands for configuring EMIF and setting PLL should be placed at the beginning of the AIS boot image as shown in Figure 6.

Figure 6. Structure of SET Command

Each set command consists of SET (0×58535907) op-code, followed by four words of additional data as shown. SET command entries in AIS can be explained using the following representation:

<Address> = <Data><Type>::<Sleep>

The above command instructs bootloader to write <code><Data></code> to address <code><Address></code> in DSP address space and then sleep for <code><Sleep>\*</code> CPU clocks. The data-type field <code><Type></code> decides whether <code><Data></code> should be written as 8 bit <code>(B)</code>, 16-bit <code>(S)</code> or 32-bit <code>(I)</code> All other fields can be in any numeric format as described in Table 20.

Table 20. Numeric Formats That Can Be Used in SET Command

| Name          | Format            | Example 1   | Example 2 | Example 3 |

|---------------|-------------------|-------------|-----------|-----------|

| Hexadecimal 1 | 0[xX][0-9a-fA-F]+ | 0×1234abCD  | 0×1000    | 0×5a      |

| Octal         | 0[0-7]+           | 02215125715 | 010000    | 0132      |

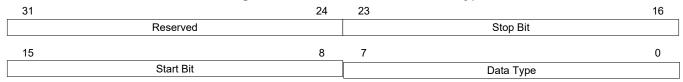

The data-type field <Type> determines the size of the data item such as 8-bit (B), 16-bit (S) or 32-bit (I). Data-type also can be a *field* or *bits*. This allows the setting of a particular range of bits within the data at the specified address. For *field* and *bits* data-types, the <Type> field also encodes the *start* and *stop* bit positions that define the field to be modified. Table 21 gives a full list of the data-types that can be used.

Table 21. Valid SET Command Data Types

| Data Type         | Value |  |

|-------------------|-------|--|

| 8 bit             | 1     |  |

| 16 bits           | 2     |  |

| 32 bits           | 3     |  |

| Field (1-32 bits) | 4     |  |

| Bits(1-32 bits)   | 5     |  |

The *field* and *bits* data-types are handled similarly by the bootloader. The difference between these types are that with a specifier of *field*, the bootloader performs a read/modify write operation at the given address. The *bits* data type results in a read of the address, followed by a write of the new value to the address. The <Type> specification is a 32-bit word that contains fields for data type (shown above), *start bit*, and *stop bit*. The *start bit* and *stop bit* fields are required only if a data-type of *field(3)* or (*bits(4)* is used. These fields delimit the number of bits that are affected by the instruction. Table 19 shows the encoding of the 32 bit <Type>.