# LMH5485-SP Radiation Hardened Assured, Negative Rail Input, Rail-to-Rail Output, Precision, 850MHz Fully Differential Amplifier

## 1 Features

- QMLV (QML class V) MIL-PRF-38535 qualified, SMD 5962R1920401VXC

- TID assured for every wafer lot up to 100krad (Si)

- Single event latch-up (SEL) immune to LET = 77MeV-cm<sup>2</sup>/mg

- Qualified over the military temperature range: -55°C to +125°C

- Gain bandwidth product (GBWP): 850MHz

- Slew rate: 1400V/μs

- HD2, HD3: -111dBc, -149dBc (100kHz, 2V<sub>PP</sub>)

- Input voltage noise: 2.4nV/√Hz

- Low offset drift: ±0.5μV/°C (typical)

- Negative rail input (NRI), rail-to-rail output (RRO)

- Power supply:

- Supply voltage range: 2.7V to 5.4V

- Quiescent current: 10.1mA

- Power-down capability: 2μA (typical)

## 2 Applications

- Low-power, high-performance ADC driver:

- SAR, ΔΣ, and pipeline

- Differential DAC output driver

- [Command and data handling](#)

- Launch vehicle systems

- Space imaging systems:

- Optical imaging payload

- Radar imaging payload

- Thermal imaging cameras

## 3 Description

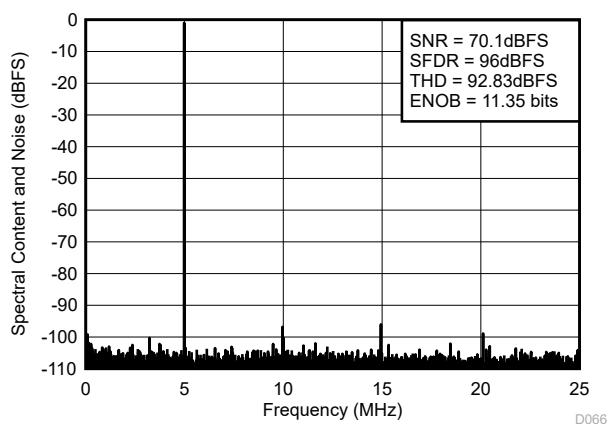

The LMH5485-SP is a radiation-hardened assured, low-power, voltage-feedback, fully differential amplifier (FDA). This device is able to achieve a high gain

bandwidth product (GBWP) of 850MHz to maintain excellent distortion performance over a wide range of frequencies. This wide bandwidth range is also achieved with a relatively low power consumption of 10.1mA and broadband voltage noise of 2.4nV/√Hz. These features make the LMH5485-SP an excellent choice for power-sensitive data acquisition systems with frequencies > 10MHz that require both the best signal-to-noise ratio (SNR) and spurious-free dynamic range (SFDR).

The LMH5485-SP features the negative-rail input required when interfacing with a dc-coupled, ground-centered source signal. This negative-rail input with a rail-to-rail output allows for easy interface between single-ended, ground-referenced, bipolar signal sources and a wide variety of successive approximation register (SAR), delta-sigma (ΔΣ), or pipeline ADCs using only a single 2.7V to 5.4V power supply. The LMH5485-SP also features a low offset voltage drift of ±0.5μV/°C to maintain excellent dc performance over a wide temperature range of -55°C to +125°C.

## Device Information

| PART NUMBER <sup>(1)</sup> | GRADE <sup>(2)</sup>               | PACKAGE                  |

|----------------------------|------------------------------------|--------------------------|

| 5962R1920401VXC            | Radiation hardened assured (RHA)   | Ceramic CFP              |

| 5962-1920401VXC            | QMLV                               | HKX (8)<br>6.5mm × 6.5mm |

| LMH5485HKX/EM              | Engineering samples <sup>(3)</sup> |                          |

(1) See [Section 4](#).

(2) For more information, see [Section 12](#).

(3) These units are intended for engineering evaluation only. These units are processed to a non-compliant flow. These units are not suitable for qualification, production, radiation testing or flight use. Parts are not warranted for performance over the full MIL specified temperature range of -55°C to +125°C or operating life.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                          |           |                                                                            |           |

|----------------------------------------------------------|-----------|----------------------------------------------------------------------------|-----------|

| <b>1 Features</b> .....                                  | <b>1</b>  | 8.1 Overview.....                                                          | <b>15</b> |

| <b>2 Applications</b> .....                              | <b>1</b>  | 8.2 Functional Block Diagram.....                                          | <b>15</b> |

| <b>3 Description</b> .....                               | <b>1</b>  | 8.3 Feature Description.....                                               | <b>16</b> |

| <b>4 Related Products</b> .....                          | <b>2</b>  | 8.4 Device Functional Modes.....                                           | <b>17</b> |

| <b>5 Pin Configuration and Functions</b> .....           | <b>2</b>  | <b>9 Application and Implementation</b> .....                              | <b>20</b> |

| <b>6 Specifications</b> .....                            | <b>3</b>  | 9.1 Application Information.....                                           | <b>20</b> |

| 6.1 Absolute Maximum Ratings.....                        | 3         | 9.2 Typical Applications.....                                              | <b>20</b> |

| 6.2 ESD Ratings.....                                     | 3         | 9.3 Power Supply Recommendations.....                                      | <b>21</b> |

| 6.3 Recommended Operating Conditions.....                | 3         | 9.4 Layout.....                                                            | <b>22</b> |

| 6.4 Thermal Information.....                             | 3         | <b>10 Device and Documentation Support</b> .....                           | <b>23</b> |

| 6.5 Electrical Characteristics for $V_S = 5V$ .....      | 4         | 10.1 Documentation Support.....                                            | <b>23</b> |

| 6.6 Electrical Characteristics for $V_S = 3V$ .....      | 6         | 10.2 Receiving Notification of Documentation Updates.....                  | <b>23</b> |

| 6.7 Quality Conformance Inspection.....                  | 8         | 10.3 Support Resources.....                                                | <b>23</b> |

| 6.8 Typical Characteristics: 5V Single Supply.....       | 9         | 10.4 Trademarks.....                                                       | <b>23</b> |

| 6.9 Typical Characteristics: 3V Single Supply.....       | 10        | 10.5 Electrostatic Discharge Caution.....                                  | <b>23</b> |

| 6.10 Typical Characteristics: 3V to 5V Supply Range..... | 11        | 10.6 Glossary.....                                                         | <b>23</b> |

| <b>7 Parameter Measurement Information</b> .....         | <b>14</b> | <b>11 Revision History</b> .....                                           | <b>23</b> |

| 7.1 Example Characterization Circuits.....               | 14        | <b>12 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>23</b> |

| <b>8 Detailed Description</b> .....                      | <b>15</b> |                                                                            |           |

## 4 Related Products

| DEVICE      | RAD TOLERANCE | GBWP (MHz) | $I_Q$ (mA) | HD2 / HD3 (dBc) 2V <sub>PP</sub> AT 10MHz | INPUT NOISE (nV/√Hz) | RAIL-TO-RAIL               |

|-------------|---------------|------------|------------|-------------------------------------------|----------------------|----------------------------|

| LMH5485-SP  | 100kRad TID   | 850        | 10.1       | -79 / -97                                 | 2.4                  | Negative rail input/Output |

| LMH5485-SEP | 30kRad TID    | 850        | 10.1       | -90 / -102                                | 2.4                  | Negative rail input/Output |

| THS4513-SP  | 150kRad TID   | 3000       | 37.7       | -106 / -108                               | 2.2                  | No                         |

| LMH5401-SP  | 100kRad TID   | 6500       | 60         | -99 / -100                                | 1.25                 | No                         |

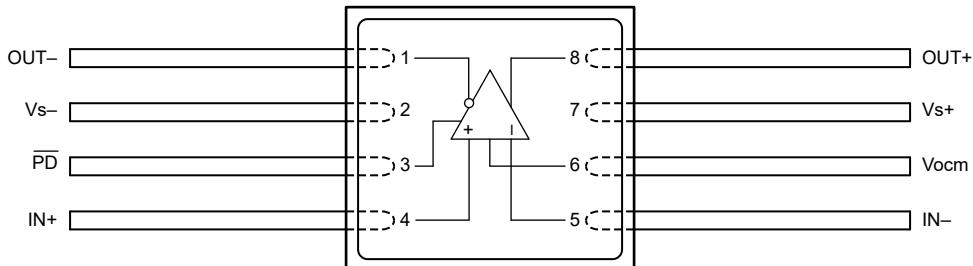

## 5 Pin Configuration and Functions

Figure 5-1. HKX Package, 8-Pin CFP (Top View)

Table 5-1. Pin Functions

| PIN  |     | TYPE   | DESCRIPTION                                                                       |

|------|-----|--------|-----------------------------------------------------------------------------------|

| NAME | NO. |        |                                                                                   |

| IN+  | 4   | Input  | Noninverting (positive) amplifier input                                           |

| IN-  | 5   | Input  | Inverting (negative) amplifier input                                              |

| OUT+ | 8   | Output | Noninverting (positive) amplifier output                                          |

| OUT- | 1   | Output | Inverted (negative) amplifier output                                              |

| PD   | 3   | Input  | Power down. PD = logic low = power-down mode; PD = logic high = normal operation. |

| Vocm | 6   | Input  | Common-mode voltage input                                                         |

| Vs+  | 7   | Power  | Positive power-supply input                                                       |

| Vs-  | 2   | Power  | Negative power-supply input                                                       |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                        |                                                                     | MIN                      | MAX                      | UNIT |

|------------------|--------------------------------------------------------|---------------------------------------------------------------------|--------------------------|--------------------------|------|

| V <sub>S</sub>   | Supply voltage (V <sub>S+</sub> ) – (V <sub>S-</sub> ) | PD = logic high                                                     |                          | 5.5                      | V    |

|                  |                                                        | PD = logic low                                                      |                          | 5.25                     |      |

| V <sub>IN</sub>  | Input voltage                                          |                                                                     | (V <sub>S-</sub> ) – 0.5 | (V <sub>S+</sub> ) + 0.5 | V    |

| V <sub>OUT</sub> | Output voltage                                         |                                                                     | (V <sub>S-</sub> ) – 0.5 | (V <sub>S+</sub> ) + 0.5 | V    |

| V <sub>ID</sub>  | Differential input voltage                             |                                                                     |                          | ±1                       | V    |

| I <sub>I</sub>   | Continuous input current                               |                                                                     |                          | ±20                      | mA   |

| I <sub>O</sub>   | Continuous output current                              |                                                                     |                          | ±80                      | mA   |

|                  | Continuous power dissipation                           | See <i>Thermal Information</i> and <i>Thermal Analysis</i> sections |                          |                          |      |

| T <sub>J</sub>   | Junction temperature                                   |                                                                     |                          | 150                      | °C   |

| T <sub>A</sub>   | Ambient temperature                                    |                                                                     | –55                      | 125                      | °C   |

| T <sub>stg</sub> | Storage temperature                                    |                                                                     | –65                      | 150                      | °C   |

(1) Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

|                    |                         | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±750  |      |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                       |                 | MIN | NOM | MAX | UNIT |

|-----------------|-----------------------|-----------------|-----|-----|-----|------|

| V <sub>S+</sub> | Single-supply voltage | PD = logic high | 2.7 | 5   | 5.4 | V    |

|                 |                       | PD = logic low  | 2.7 | 5   | 5.1 | V    |

| T <sub>A</sub>  |                       |                 | –55 | 25  | 125 | °C   |

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | LMH5485-SP | UNIT |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | HKX (CFP)  |      |

|                               |                                              | 8 PINS     |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 145.7      | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 67.6       | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 128.1      | °C/W |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 61.1       | °C/W |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 122.1      | °C/W |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 55.8       | °C/W |

(1) For information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 6.5 Electrical Characteristics for $V_S = 5V$

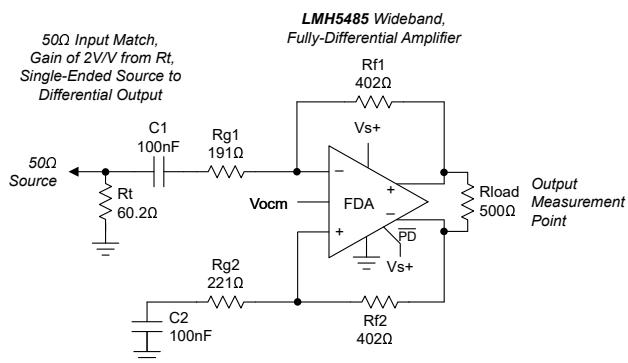

The following specifications correspond to the respectively identified subgroup temperature (see [Section 6.7](#)), unless otherwise noted.  $V_{OCM} = \text{open}$  (defaults midsupply),  $V_{OUT} = 2V_{PP}$ ,  $R_f = 402\Omega$ ,  $R_{LOAD} = 499\Omega$ ,  $50\Omega$  input match,  $G = 2V/V$ , single-ended input, differential output, and  $PD = V_{S+}$ , unless otherwise noted. See [Section 7.1](#) for a test circuit with an ac-coupled gain of  $2V/V$ , and [Section 7.1](#) for a dc-coupled gain of a  $2V/V$ .

| PARAMETER                            | TEST CONDITIONS                                                                         | SUB-GROUP <sup>(1)</sup>                 | MIN       | TYP              | MAX                  | UNIT                   |

|--------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------|-----------|------------------|----------------------|------------------------|

| <b>AC PERFORMANCE</b>                |                                                                                         |                                          |           |                  |                      |                        |

| Small-signal bandwidth               | $V_{OUT} = 100mV_{PP}$                                                                  | $G = 1$                                  |           |                  | 530                  | MHz                    |

|                                      |                                                                                         | $G = 2$                                  |           |                  | 490                  |                        |

|                                      |                                                                                         | $G = 5$                                  |           |                  | 240                  |                        |

|                                      |                                                                                         | $G = 10$                                 |           |                  | 125                  |                        |

| GBWP                                 | $V_{OUT} = 100mV_{PP}$ , $G = 20$                                                       |                                          |           |                  | 1200                 | MHz                    |

|                                      | $V_{OUT} = 2V_{PP}$                                                                     |                                          |           |                  | 315                  | MHz                    |

|                                      | $V_{OUT} = 2V_{PP}$                                                                     |                                          |           |                  | 50                   | MHz                    |

| Slew rate <sup>(2)</sup>             | $V_{OUT} = 2V_{PP}$ , $FPBW$                                                            |                                          |           |                  | 1400                 | $V/\mu s$              |

| Rise and fall time                   | $V_{OUT} = 2V$ step, input $\leq 0.5ns$ $t_r$                                           |                                          |           |                  | 1.4                  | ns                     |

| Settling time                        | $V_{OUT} = 2V$ step, $t_r = 2ns$                                                        | To 1%                                    |           |                  | 5.4                  | ns                     |

|                                      |                                                                                         | To 0.1%                                  |           |                  | 10                   |                        |

| Overshoot and undershoot             | $V_{OUT} = 2V$ step, input $\leq 0.3ns$ $t_r$                                           |                                          |           |                  | 24%                  |                        |

| Harmonic distortion                  | 100kHz, $V_{OUT} = 2V_{PP}$                                                             | HD2                                      |           |                  | -111                 | dBc                    |

|                                      |                                                                                         | HD3                                      |           |                  | -149                 |                        |

|                                      | 10MHz, $V_{OUT} = 2V_{PP}$                                                              | HD2                                      |           |                  | -79                  |                        |

|                                      |                                                                                         | HD3                                      |           |                  | -97                  |                        |

| 2nd-order intermodulation distortion | $f = 10MHz$ , 100kHz tone spacing, $V_{OUT}$ envelope = $2V_{PP}$ (1V $_{PP}$ per tone) |                                          |           |                  | -90                  | dBc                    |

| 3rd-order intermodulation distortion |                                                                                         |                                          |           |                  | -85                  |                        |

| Input voltage noise                  | $f > 100kHz$                                                                            |                                          |           |                  | 2.4                  | $nV/\sqrt{Hz}$         |

| Input current noise                  | $f > 1MHz$                                                                              |                                          |           |                  | 1.9                  | $pA/\sqrt{Hz}$         |

| Overdrive recovery time              | 2 $\times$ output overdrive, either polarity                                            |                                          |           |                  | 20                   | ns                     |

| Closed-loop output impedance         | $f = 10MHz$ (differential)                                                              |                                          |           |                  | 0.1                  | $\Omega$               |

| <b>DC PERFORMANCE</b>                |                                                                                         |                                          |           |                  |                      |                        |

| $A_{OL}$                             | Open-loop voltage gain                                                                  |                                          | [1, 2, 3] | 97               | 119                  | dB                     |

|                                      | Input-referred offset voltage                                                           |                                          | [1, 2, 3] | -900             | $\pm 100$            | $\mu V$                |

|                                      | Input offset voltage drift <sup>(3)</sup>                                               |                                          |           | -4               | $\pm 0.5$            | $\mu V/\text{°C}$      |

|                                      | Input bias current                                                                      | Positive out of node                     | [1, 2, 3] | 0.4              | 10                   | $\mu A$                |

|                                      | Input bias current drift <sup>(3)</sup>                                                 |                                          |           |                  | 6                    | $nA/\text{°C}$         |

|                                      | Input offset current                                                                    |                                          | [1, 2, 3] | -1200            | $\pm 150$            | nA                     |

|                                      | Input offset current drift <sup>(3)</sup>                                               |                                          |           | -1.5             | $\pm 0.3$            | $nA/\text{°C}$         |

| <b>INPUT</b>                         |                                                                                         |                                          |           |                  |                      |                        |

|                                      | Common-mode input low                                                                   | < 3dB degradation in CMRR from midsupply | [1, 2, 3] | $(V_{S-}) - 0.2$ | $V_{S-}$             | V                      |

|                                      | Common-mode input high                                                                  | < 3dB degradation in CMRR from midsupply | [1, 2, 3] | $(V_{S+}) - 1.3$ | $(V_{S+}) - 1.2$     | V                      |

|                                      | Common-mode rejection ratio                                                             | Input pins at midsupply                  | [1, 2, 3] | 82               | 100                  | dB                     |

|                                      | Input impedance differential mode                                                       | Input pins at midsupply                  |           |                  | $110 \parallel 1.25$ | $k\Omega \parallel pF$ |

## 6.5 Electrical Characteristics for $V_S = 5V$ (continued)

The following specifications correspond to the respectively identified subgroup temperature (see [Section 6.7](#)), unless otherwise noted.  $V_{OCM} = \text{open}$  (defaults midsupply),  $V_{OUT} = 2V_{PP}$ ,  $R_f = 402\Omega$ ,  $R_{LOAD} = 499\Omega$ ,  $50\Omega$  input match,  $G = 2V/V$ , single-ended input, differential output, and  $\bar{PD} = V_{S+}$ , unless otherwise noted. See [Section 7.1](#) for a test circuit with an ac-coupled gain of  $2V/V$ , and [Section 7.1](#) for a dc-coupled gain of a  $2V/V$ .

| PARAMETER                                               | TEST CONDITIONS                                        | SUB-GROUP <sup>(1)</sup>                                                | MIN                                                            | TYP               | MAX               | UNIT     |

|---------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|-------------------|----------|

| <b>OUTPUT</b>                                           |                                                        |                                                                         |                                                                |                   |                   |          |

|                                                         | Output voltage low                                     | [1, 2, 3]                                                               | $(V_{S-}) + 0.2$                                               | $(V_{S-}) + 0.25$ | $(V_{S-}) + 0.25$ | V        |

|                                                         | Output voltage high                                    | [1, 2, 3]                                                               | $(V_{S+}) - 0.25$                                              | $(V_{S+}) - 0.2$  | $(V_{S+}) - 0.2$  | V        |

|                                                         | Output current drive                                   | [1, 2, 3]                                                               | $\pm 70$                                                       | $\pm 100$         | $\pm 100$         | mA       |

| <b>POWER SUPPLY</b>                                     |                                                        |                                                                         |                                                                |                   |                   |          |

|                                                         | Quiescent operating current                            | [1, 2, 3]                                                               | 9.2                                                            | 10.1              | 11                | mA       |

| PSRR                                                    | Power-supply rejection ratio<br>$V_{OUT}$              | Either supply pin to differential                                       | [1, 2, 3]                                                      | 82                | 100               | dB       |

| <b>POWER DOWN</b>                                       |                                                        |                                                                         |                                                                |                   |                   |          |

|                                                         | Enable voltage threshold                               | [1, 2, 3]                                                               | $(V_{S-}) + 1.7$                                               | $(V_{S-}) + 1.7$  | $(V_{S-}) + 1.7$  | V        |

|                                                         | Disable voltage threshold                              | [1, 2, 3]                                                               | $(V_{S-}) + 0.7$                                               | $(V_{S-}) + 0.7$  | $(V_{S-}) + 0.7$  | V        |

|                                                         | Disable pin bias current                               | $\bar{PD} = V_{S-} \rightarrow V_{S+}$                                  | [1, 2, 3]                                                      | 20                | 50                | nA       |

|                                                         | Power-down quiescent current                           | $\bar{PD} = (V_{S-}) + 0.7V$                                            | $T_A = 25^\circ C$<br>$T_A = -40^\circ C$<br>to $+125^\circ C$ | [1, 2, 3]         | 6<br>100          | 30       |

|                                                         |                                                        | $\bar{PD} = V_{S-}$                                                     | $T_A = 25^\circ C$<br>$T_A = -40^\circ C$<br>to $+125^\circ C$ | [1, 2, 3]         | 2<br>30           | 8        |

|                                                         | Turn-on delay                                          | Time from $\bar{PD} = \text{low}$ to<br>$V_{OUT} = 90\%$ of final value |                                                                |                   | 100               | ns       |

|                                                         | Turn-off delay                                         | Time from $\bar{PD} = \text{low}$ to<br>$V_{OUT} = 10\%$ of final value |                                                                |                   | 60                | ns       |

| <b>OUTPUT COMMON-MODE VOLTAGE CONTROL<sup>(4)</sup></b> |                                                        |                                                                         |                                                                |                   |                   |          |

|                                                         | Small-signal bandwidth                                 | $V_{OCM} = 100mV_{PP}$                                                  |                                                                |                   | 150               | MHz      |

|                                                         | Slew rate <sup>(2)</sup>                               | $V_{OCM} = 2V$ step                                                     |                                                                |                   | 400               | V/μs     |

|                                                         | Gain                                                   | [1, 2, 3]                                                               | 0.975                                                          | 0.982             | 0.995             | V/V      |

|                                                         | Input bias current                                     | Considered positive out of node                                         | [1, 2, 3]                                                      | -0.9              | 0.1               | 0.9      |

|                                                         | Input impedance                                        | $V_{OCM}$ pin driven to midsupply                                       |                                                                |                   | 47    1.2         | kΩ    pF |

|                                                         | Default voltage offset from<br>midsupply               | $V_{OCM}$ pin open                                                      | [1, 2, 3]                                                      | -50               | ±8                | 50       |

| CM $V_{OS}$                                             | Common-mode offset voltage                             | $V_{OCM}$ pin driven to midsupply                                       | [1, 2, 3]                                                      | -8                | ±2                | 8        |

|                                                         | CM $V_{OS}$ drift <sup>(3)</sup>                       | $V_{OCM}$ pin driven to midsupply                                       |                                                                | -20               | ±4                | +20      |

|                                                         | Common-mode loop supply<br>headroom to negative supply | < ±15mV shift from midsupply CM<br>$V_{OS}$                             | [1, 2, 3]                                                      | 0.94              |                   | V        |

|                                                         | Common-mode loop supply<br>headroom to positive supply | < ±15mV shift from midsupply CM<br>$V_{OS}$                             | [1, 2, 3]                                                      | 1.2               |                   | V        |

(1) For subgroup definitions, see [Section 6.7](#)

(2) This slew rate is the average of the rising and falling time estimated from the large-signal bandwidth as:  $(V_P / \sqrt{2}) \times 2\pi \times f_{-3dB}$ .

(3) Input offset voltage drift, input bias current drift, input offset current drift, and  $V_{OCM}$  drift are average values calculated by taking data at the maximum-range ambient-temperature end-points, computing the difference, and dividing by the temperature range.

(4) Specifications are from the input  $V_{OCM}$  pin to the differential output average voltage.

## 6.6 Electrical Characteristics for $V_S = 3V$

The following specifications correspond to the respectively identified subgroup temperature (see [Section 6.7](#)), unless otherwise noted.  $V_{OCM} = \text{open}$  (defaults midsupply),  $V_{OUT} = 2V_{PP}$ ,  $R_f = 402\Omega$ ,  $R_{LOAD} = 499\Omega$ ,  $50\Omega$  input match,  $G = 2V/V$ , single-ended input, differential output, and  $PD = V_S+$ , unless otherwise noted. See [Section 7.1](#) for a test circuit with an ac-coupled gain of  $2V/V$ , and [Section 7.1](#) for a dc-coupled gain of  $2V/V$ .

| PARAMETER                            | TEST CONDITIONS                                                                         | SUB-GROUP <sup>(1)</sup>                      | MIN       | TYP            | MAX                  | UNIT                   |

|--------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------|-----------|----------------|----------------------|------------------------|

| <b>AC PERFORMANCE</b>                |                                                                                         |                                               |           |                |                      |                        |

| Small-signal bandwidth               | $V_{OUT} = 100mV_{PP}$                                                                  | G = 1                                         |           |                | 510                  | MHz                    |

|                                      |                                                                                         | G = 2                                         |           |                | 475                  |                        |

|                                      |                                                                                         | G = 5                                         |           |                | 240                  |                        |

| GBWP                                 | $V_{OUT} = 100mV_{PP}$ , $G = 20$                                                       |                                               |           |                | 850                  | MHz                    |

|                                      | Large-signal bandwidth                                                                  | $V_{OUT} = 2V_{PP}$                           |           |                | 300                  | MHz                    |

|                                      | Bandwidth for 0.1dB flatness                                                            | $V_{OUT} = 2V_{PP}$                           |           |                | 50                   | MHz                    |

|                                      | Slew rate <sup>(2)</sup>                                                                | $V_{OUT} = 2V$ step, $FPBW$                   |           |                | 1200                 | V/ $\mu$ s             |

|                                      | Rise and fall time                                                                      | $V_{OUT} = 2V$ step, input $\leq 0.5ns$ $t_r$ |           |                | 1.6                  | ns                     |

| Settling time                        | $V_{OUT} = 2V$ step, $t_r = 2ns$                                                        | To 1%                                         |           |                | 5                    | ns                     |

|                                      |                                                                                         | To 0.1%                                       |           |                | 9                    |                        |

|                                      | Overshoot and undershoot                                                                | $V_{OUT} = 2V$ step, input $\leq 0.3ns$ $t_r$ |           |                | 25%                  |                        |

| Harmonic distortion                  | 100kHz, $V_{OUT} = 2V_{PP}$                                                             | HD2                                           |           |                | -111                 | dBc                    |

|                                      |                                                                                         | HD3                                           |           |                | -150                 |                        |

|                                      | 10MHz, $V_{OUT} = 2V_{PP}$                                                              | HD2                                           |           |                | -80                  |                        |

|                                      |                                                                                         | HD3                                           |           |                | -96                  |                        |

| 2nd-order intermodulation distortion | $f = 10MHz$ , 100kHz tone spacing, $V_{OUT}$ envelope = $2V_{PP}$ (1V $_{PP}$ per tone) |                                               |           |                | -89                  | dBc                    |

| 3rd-order intermodulation distortion |                                                                                         |                                               |           |                | -87                  |                        |

| Input voltage noise                  | $f > 100kHz$                                                                            |                                               |           |                | 2.4                  | nV/ $\sqrt{Hz}$        |

| Input current noise                  | $f > 1MHz$                                                                              |                                               |           |                | 1.9                  | pA/ $\sqrt{Hz}$        |

| Overdrive recovery time              | 2 $\times$ output overdrive, either polarity                                            |                                               |           |                | 20                   | ns                     |

| Closed-loop output impedance         | $f = 10MHz$ (differential)                                                              |                                               |           |                | 0.1                  | $\Omega$               |

| <b>DC PERFORMANCE</b>                |                                                                                         |                                               |           |                |                      |                        |

| $A_{OL}$                             | Open-loop voltage gain                                                                  | [1, 2, 3]                                     | 97        | 119            |                      | dB                     |

|                                      | Input-referred offset voltage                                                           | [1, 2, 3]                                     | -900      | $\pm 100$      | 900                  | $\mu V$                |

|                                      | Input offset voltage drift <sup>(3)</sup>                                               |                                               | -4        | $\pm 0.5$      | 4                    | $\mu V/^\circ C$       |

|                                      | Input bias current                                                                      | Positive out of node                          | [1, 2, 3] | 0.4            | 9                    | 15                     |

|                                      | Input bias current drift <sup>(3)</sup>                                                 |                                               |           |                | 5                    | 15                     |

|                                      | Input offset current                                                                    | [1, 2, 3]                                     | -1200     | $\pm 150$      | 1200                 | nA                     |

|                                      | Input offset current drift <sup>(3)</sup>                                               |                                               | -4        | $\pm 0.3$      | 4                    | nA/ $^\circ C$         |

| <b>INPUT</b>                         |                                                                                         |                                               |           |                |                      |                        |

|                                      | Common-mode input low                                                                   | < 3dB degradation in CMRR from midsupply      | [1, 2, 3] | $(V_S-) - 0.2$ | $V_{S-}$             | V                      |

|                                      | Common-mode input high                                                                  | < 3dB degradation in CMRR from midsupply      | [1, 2, 3] | $(V_S+) - 1.3$ | $(V_S+) - 1.2$       | V                      |

|                                      | Common-mode rejection ratio                                                             | Input pins at midsupply                       | [1, 2, 3] | 82             | 100                  | dB                     |

|                                      | Input impedance differential mode                                                       | Input pins at midsupply                       |           |                | 110 $\parallel$ 1.25 | $k\Omega \parallel pF$ |

## 6.6 Electrical Characteristics for $V_S = 3V$ (continued)

The following specifications correspond to the respectively identified subgroup temperature (see [Section 6.7](#)), unless otherwise noted.  $V_{OCM} = \text{open}$  (defaults midsupply),  $V_{OUT} = 2V_{PP}$ ,  $R_f = 402\Omega$ ,  $R_{LOAD} = 499\Omega$ ,  $50\Omega$  input match,  $G = 2V/V$ , single-ended input, differential output, and  $\bar{PD} = V_{S+}$ , unless otherwise noted. See [Section 7.1](#) for a test circuit with an ac-coupled gain of  $2V/V$ , and [Section 7.1](#) for a dc-coupled gain of  $2V/V$ .

| PARAMETER                                               | TEST CONDITIONS                                                                                            | SUB-GROUP <sup>(1)</sup>             | MIN       | TYP                | MAX               | UNIT                   |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------|--------------------|-------------------|------------------------|

| <b>OUTPUT</b>                                           |                                                                                                            |                                      |           |                    |                   |                        |

|                                                         | Output voltage low                                                                                         | [1, 2, 3]                            |           | $(V_{S-}) + 0.2$   | $(V_{S-}) + 0.25$ | V                      |

|                                                         | Output voltage high                                                                                        | [1, 2, 3]                            |           | $(V_{S+}) - 0.25$  | $(V_{S+}) - 0.2$  | V                      |

|                                                         | Output current drive                                                                                       | [1, 2, 3]                            | $\pm 49$  | $\pm 60$           |                   | mA                     |

| <b>POWER SUPPLY</b>                                     |                                                                                                            |                                      |           |                    |                   |                        |

|                                                         | Quiescent operating current                                                                                | [1, 2, 3]                            | 8.9       | 9.7                | 10.6              | mA                     |

| PSRR                                                    | Power-supply rejection ratio<br>$V_{OUT}$                                                                  | Either supply pin to differential    | [1, 2, 3] | 82                 | 100               | dB                     |

| <b>POWER DOWN</b>                                       |                                                                                                            |                                      |           |                    |                   |                        |

|                                                         | Enable voltage threshold                                                                                   | [1, 2, 3]                            |           | $(V_{S-}) + 1.7$   |                   | V                      |

|                                                         | Disable voltage threshold                                                                                  | [1, 2, 3]                            |           |                    | $(V_{S-}) + 0.7$  | V                      |

|                                                         | Disable pin bias current<br>$\bar{PD} = V_{S-} \rightarrow V_{S+}$                                         | [1, 2, 3]                            |           | 20                 | 50                | nA                     |

|                                                         | Power-down quiescent current<br>$\bar{PD} = (V_{S-}) + 0.7V$                                               | [1, 2, 3]                            |           | 2                  | 33                | $\mu A$                |

|                                                         |                                                                                                            | $\bar{PD} = V_{S-}$                  | [1, 2, 3] |                    | 1                 | $\mu A$                |

|                                                         | Turn-on delay<br>$V_{OUT} = 90\%$ of final value                                                           | Time from $\bar{PD} = \text{low}$ to |           |                    | 100               | ns                     |

|                                                         | Turn-off delay<br>$V_{OUT} = 10\%$ of final value                                                          | Time from $\bar{PD} = \text{low}$ to |           |                    | 60                | ns                     |

| <b>OUTPUT COMMON-MODE VOLTAGE CONTROL<sup>(4)</sup></b> |                                                                                                            |                                      |           |                    |                   |                        |

|                                                         | Small-signal bandwidth<br>$V_{OCM} = 100mV_{PP}$                                                           |                                      |           | 140                |                   | MHz                    |

|                                                         | Slew rate <sup>(2)</sup><br>$V_{OCM} = 1V$ step                                                            |                                      |           | 350                |                   | $V/\mu s$              |

|                                                         | Gain                                                                                                       | [1, 2, 3]                            | 0.975     | 0.987              | 0.991             | $V/V$                  |

|                                                         | Input bias current<br>Considered positive out of node                                                      | [1, 2, 3]                            | -0.8      | 0.1                | 0.8               | $\mu A$                |

|                                                         | Input impedance<br>$V_{OCM}$ pin driven to midsupply                                                       |                                      |           | 47 $\parallel$ 1.2 |                   | $k\Omega \parallel pF$ |

|                                                         | Default voltage offset from<br>midsupply<br>$V_{OCM}$ pin open                                             | [1, 2, 3]                            | -50       | $\pm 10$           | 50                | mV                     |

| CM $V_{OS}$                                             | Common-mode offset voltage<br>$V_{OCM}$ pin driven to midsupply                                            | [1, 2, 3]                            | -8        | $\pm 2$            | 8                 | mV                     |

|                                                         | CM $V_{OS}$ drift <sup>(3)</sup><br>$V_{OCM}$ pin driven to midsupply                                      |                                      | -22       | $\pm 4$            | 22                | $\mu V/^\circ C$       |

|                                                         | Common-mode loop supply<br>headroom to negative supply<br>$< \pm 15mV$ shift from midsupply CM<br>$V_{OS}$ | [1, 2, 3]                            | 0.94      |                    |                   | V                      |

|                                                         | Common-mode loop supply<br>headroom to positive supply<br>$< \pm 15mV$ shift from midsupply CM<br>$V_{OS}$ | [1, 2, 3]                            | 1.2       |                    |                   | V                      |

(1) For subgroup definitions, see [Section 6.7](#)

(2) This slew rate is the average of the rising and falling time estimated from the large-signal bandwidth as:  $(V_P / \sqrt{2}) \times 2\pi \times f_{-3dB}$ .

(3) Input offset voltage drift, input bias current drift, input offset current drift, and  $V_{OCM}$  drift are average values calculated by taking data at the maximum-range ambient-temperature end-points, computing the difference, and dividing by the temperature range. Maximum drift set by distribution of a large sampling of devices. Drift is not specified by test or QA sample test.

(4) Specifications are from input  $V_{OCM}$  pin to differential output average voltage.

## 6.7 Quality Conformance Inspection

MIL-STD-883, Method 5005 - Group A

| SUBGROUP | DESCRIPTION         | TEMPERATURE (°C) |

|----------|---------------------|------------------|

| 1        | Static tests at     | 25               |

| 2        | Static tests at     | 125              |

| 3        | Static tests at     | -55              |

| 4        | Dynamic tests at    | 25               |

| 5        | Dynamic tests at    | 125              |

| 6        | Dynamic tests at    | -55              |

| 7        | Functional tests at | 25               |

| 8A       | Functional tests at | 125              |

| 8B       | Functional tests at | -55              |

## 6.8 Typical Characteristics: 5V Single Supply

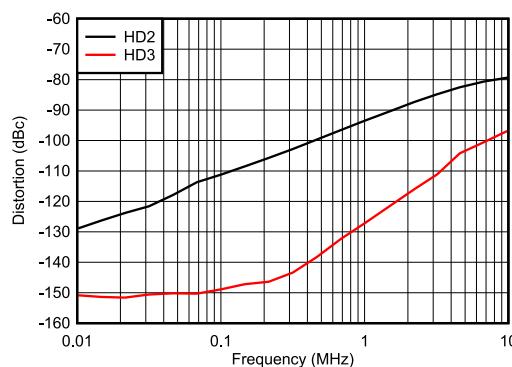

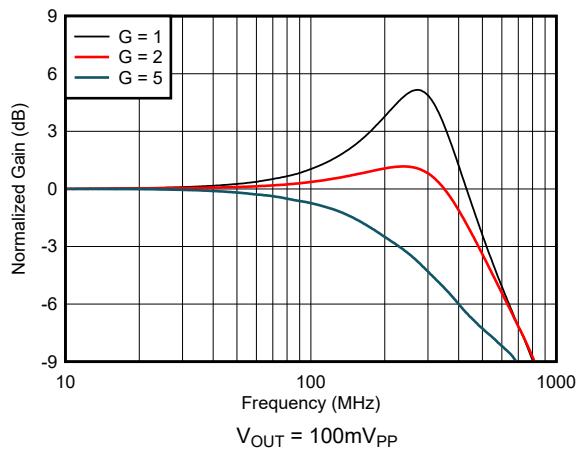

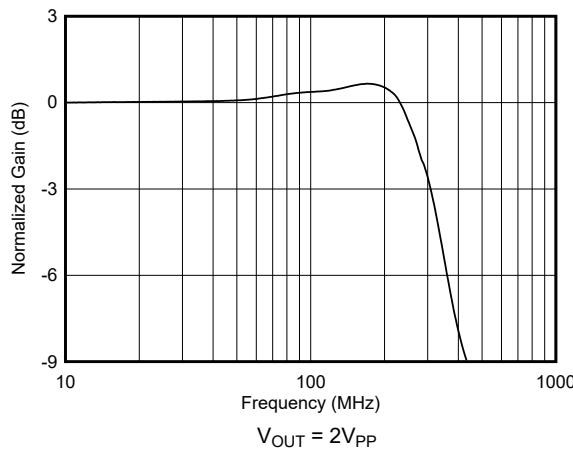

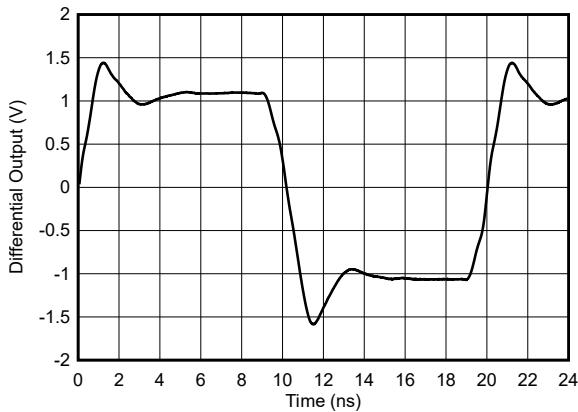

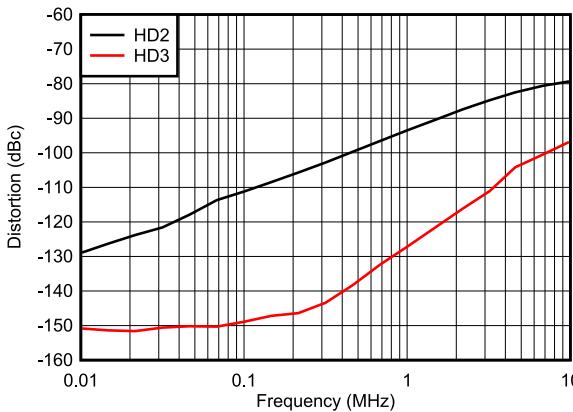

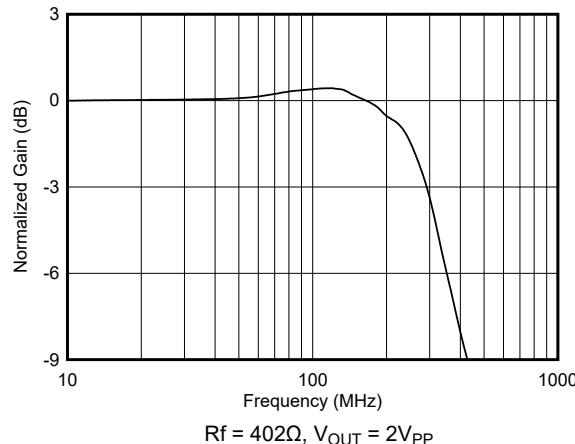

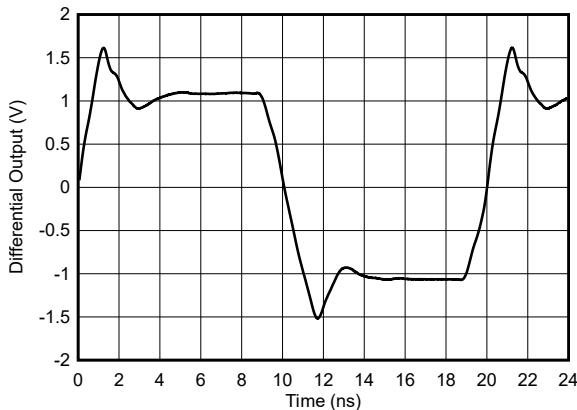

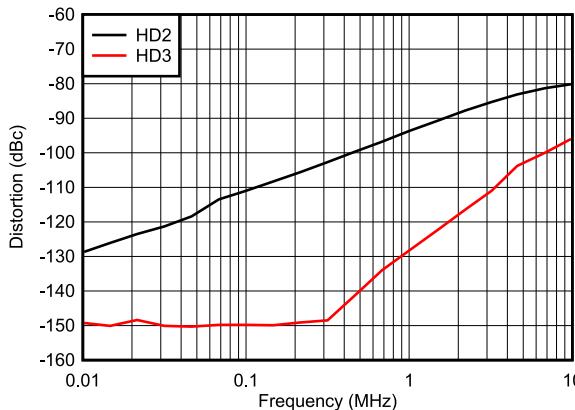

at  $V_{S+} = 5V$ ,  $V_{S-} = GND$ ,  $R_F = 402\Omega$ ,  $V_{OCM}$  is open,  $50\Omega$  single-ended input to differential output, gain = 2V/V,  $R_{LOAD} = 500\Omega$ , and  $T_A \approx 25^\circ C$  (unless otherwise noted)

Figure 6-1. Small-Signal Frequency Response vs Gain

Figure 6-2. Large-Signal Frequency Response

Figure 6-3. Large-Signal Step Response

Figure 6-4. Harmonic Distortion Over Frequency

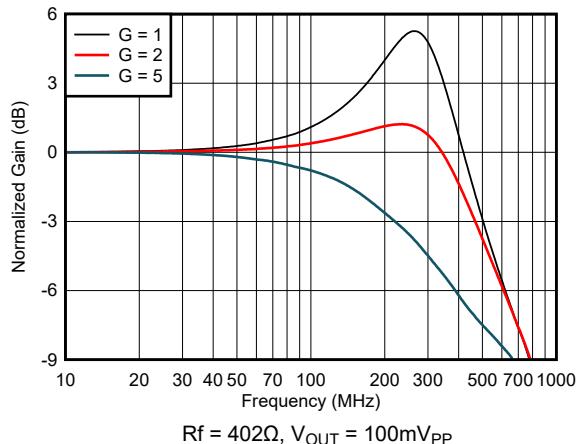

## 6.9 Typical Characteristics: 3V Single Supply

at  $V_{S+} = 3V$ ,  $V_{S-} = GND$ ,  $V_{OCM}$  is open,  $50\Omega$  single-ended input to differential output, gain = 2V/V,  $R_{LOAD} = 500\Omega$ , and  $T_A \approx 25^\circ C$  (unless otherwise noted)

Figure 6-5. Small-Signal Frequency Response vs Gain

Figure 6-6. Large-Signal Frequency Response

Figure 6-7. Large-Signal Step Response

Figure 6-8. Harmonic Distortion Over Frequency

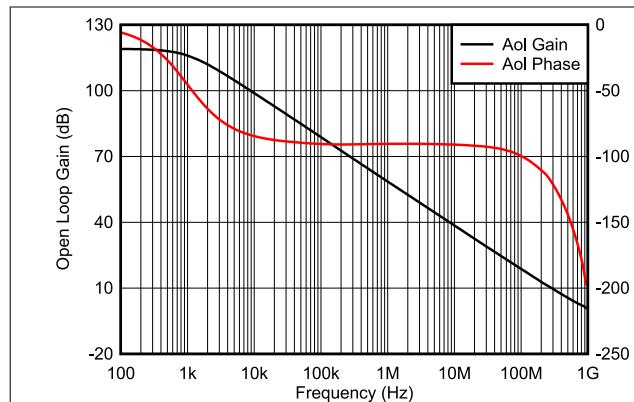

## 6.10 Typical Characteristics: 3V to 5V Supply Range

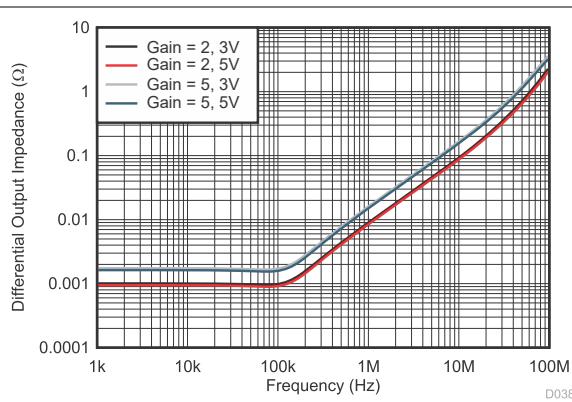

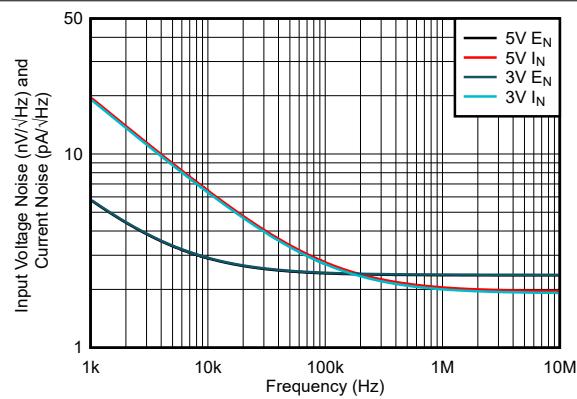

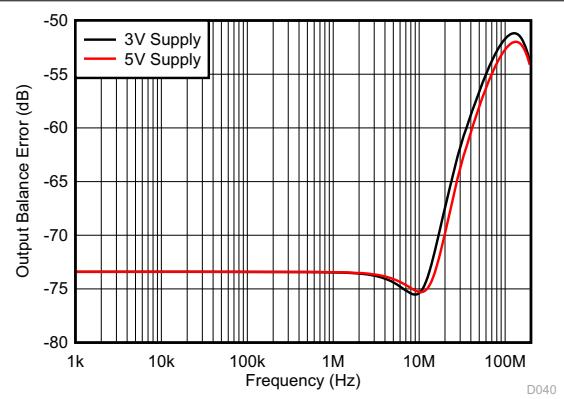

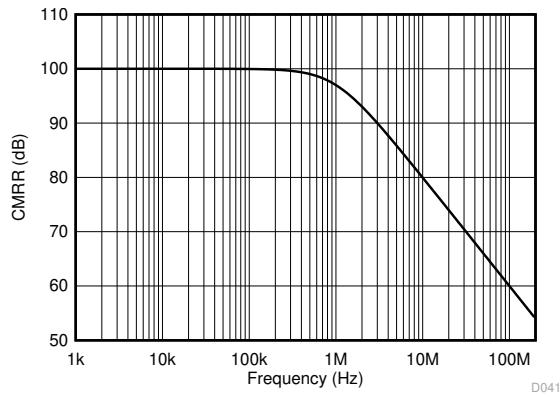

at  $V_{S+} = 3V$  and  $5V$ ,  $V_{S-} = GND$ ,  $V_{OCM}$  is open,  $50\Omega$  single-ended input to differential output, gain =  $2V/V$ ,  $R_{LOAD} = 500\Omega$ , and  $T_A \geq 25^\circ C$  (unless otherwise noted)

**Figure 6-9. Main Amplifier Differential Open-Loop Gain and Phase vs Frequency**

Single-ended input to differential output, simulated differential output impedance, see [Figure 7-1](#)

**Figure 6-10. Closed-Loop Output Impedance**

**Figure 6-11. Input Spot Noise Over Frequency**

Single-ended input to differential output, gain of 2 (see [Figure 7-1](#)), simulated with 1% resistor, worst-case mismatch

**Figure 6-12. Output Balance Error Over Frequency**

Common-mode in to differential out, gain of 2 simulation

**Figure 6-13. CMRR Over Frequency**

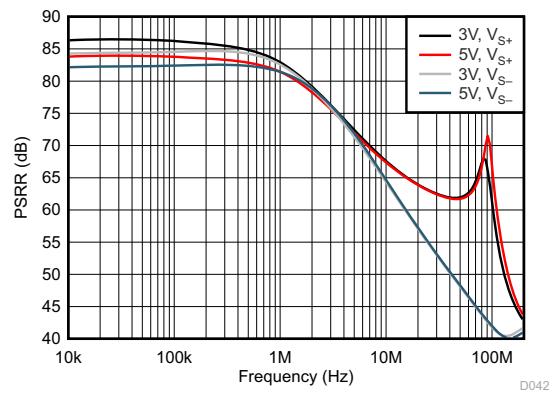

Single-ended to differential, gain of 2 (see [Figure 7-1](#)) PSRR simulated to differential output

**Figure 6-14. PSRR Over Frequency**

## 6.10 Typical Characteristics: 3V to 5V Supply Range (continued)

at  $V_{S+} = 3V$  and  $5V$ ,  $V_{S-} = GND$ ,  $V_{OCM}$  is open,  $50\Omega$  single-ended input to differential output, gain =  $2V/V$ ,  $R_{LOAD} = 500\Omega$ , and  $T_A \geq 25^\circ C$  (unless otherwise noted)

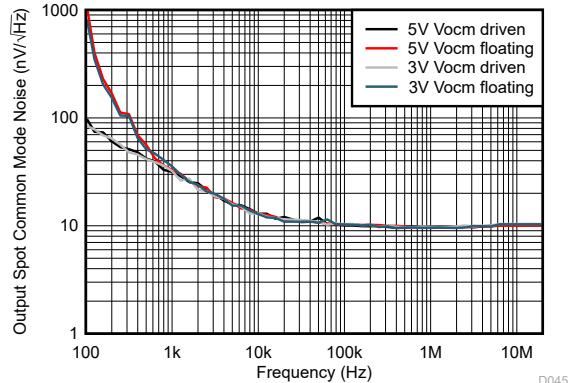

Vocom input either driven to midsupply by low impedance source, or allowed to float and default to midsupply

**Figure 6-15. Output Common-Mode Noise**

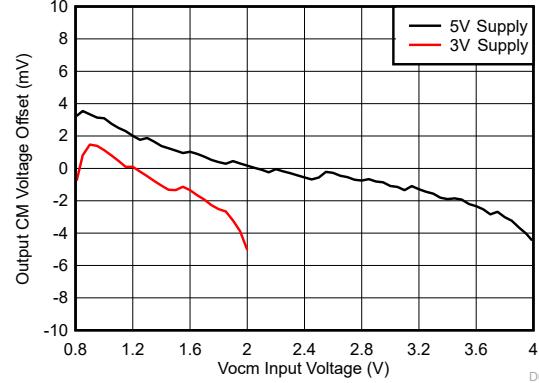

Average Vocom output offset of 37 units, standard deviation < 2.5mV, see [Figure 7-2](#)

**Figure 6-16. Vocom Offset vs Vocom Setting**

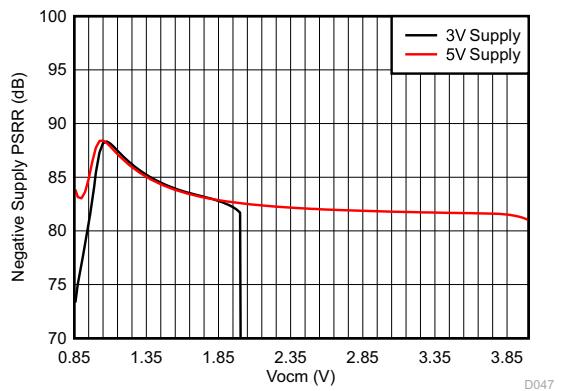

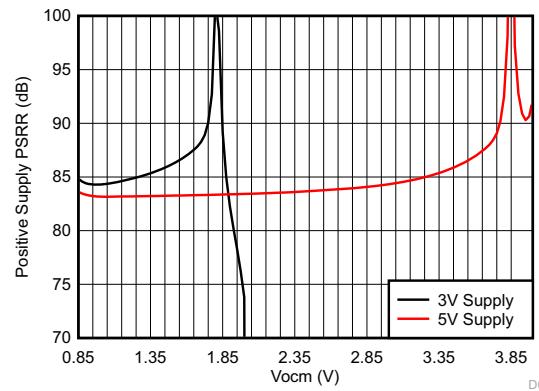

Single-ended to differential gain of 2 (see [Figure 7-1](#)), PSRR for negative supply to differential output (1kHz simulation)

**Figure 6-17. -PSRR vs Vocom Approaching Vs-**

Single-ended to differential gain of 2 (see [Figure 7-1](#)), PSRR for positive supply to differential output (1kHz simulation)

**Figure 6-18. +PSRR vs Vocom Approaching Vs+**

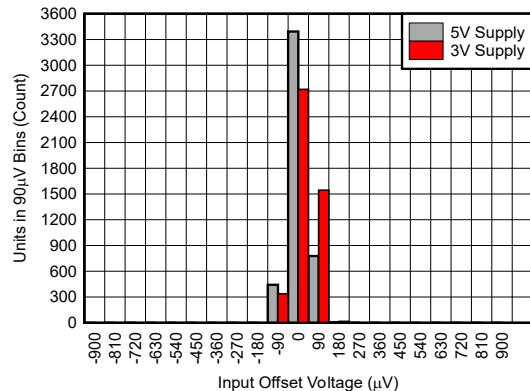

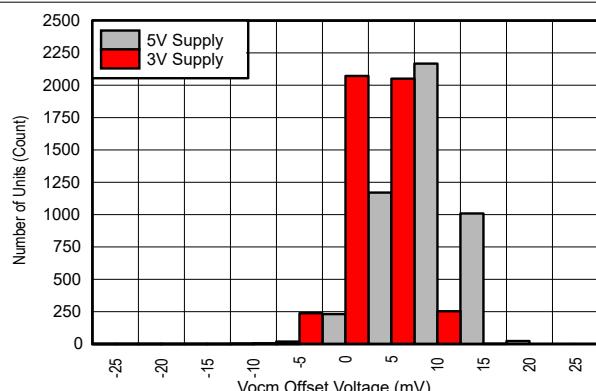

Total of 4618 units for each supply.

For  $V_S = 5V$ :  $\mu = -35.1\mu V$ ,  $\sigma = 38.9\mu V$

**Figure 6-19. Input Offset Voltage**

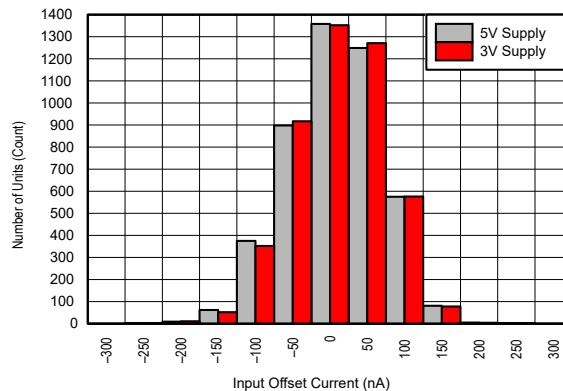

Total of 4618 units for each supply.

For  $V_S = 5V$ :  $\mu = 16.7nA$ ,  $\sigma = 62.3nA$

**Figure 6-20. Input Offset Current**

## 6.10 Typical Characteristics: 3V to 5V Supply Range (continued)

at  $V_{S+} = 3V$  and  $5V$ ,  $V_{S-} = GND$ ,  $V_{OCM}$  is open,  $50\Omega$  single-ended input to differential output, gain =  $2V/V$ ,  $R_{LOAD} = 500\Omega$ , and  $T_A \geq 25^\circ C$  (unless otherwise noted)

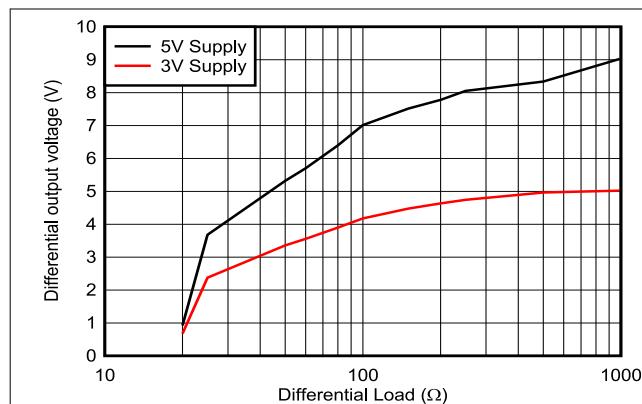

Maximum differential output swing,  $V_{OCM}$  at midsupply

**Figure 6-21. Differential Output Voltage vs Rload**

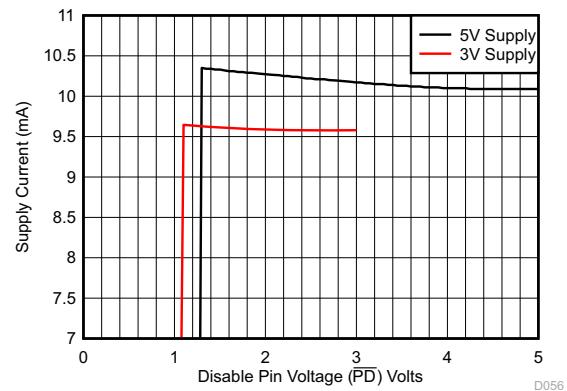

**Figure 6-22. Supply Current vs PD Voltage**

$V_{OCM}$  input floating. Total of 4618 units for each supply,

For  $V_S = 5V$ :  $\mu = 6.8mV$ ,  $\sigma = 3.9mV$

**Figure 6-23. Common-Mode Output Offset from Vs+ / 2 Default Value**

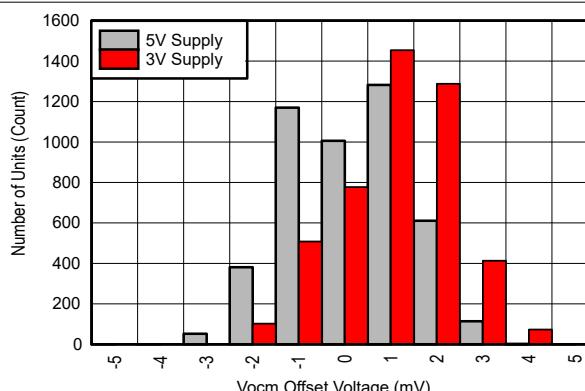

Total of 4618 units for each supply,

For  $V_S = 5V$ :  $\mu = 0.3mV$ ,  $\sigma = 1.3mV$

**Figure 6-24. Common-Mode Output Offset from Driven Vocom**

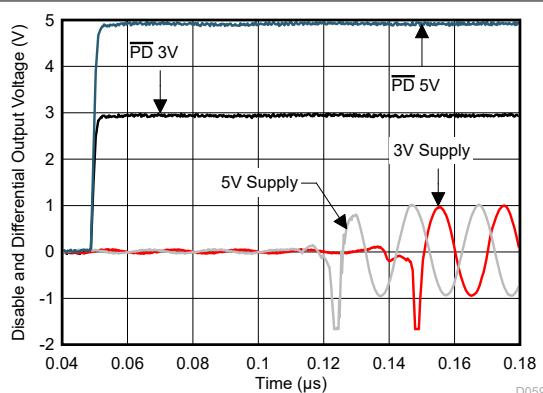

10MHz,  $1V_{PP}$  input single to differential gain of 2,

see [Figure 7-2](#)

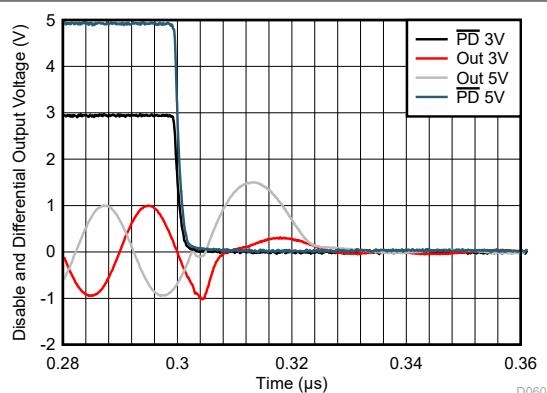

**Figure 6-25. PD Turn-On Waveform**

10MHz,  $1V_{PP}$  input single to differential gain of 2,

see [Figure 7-2](#)

**Figure 6-26. PD Turn-Off Waveform**

## 7 Parameter Measurement Information

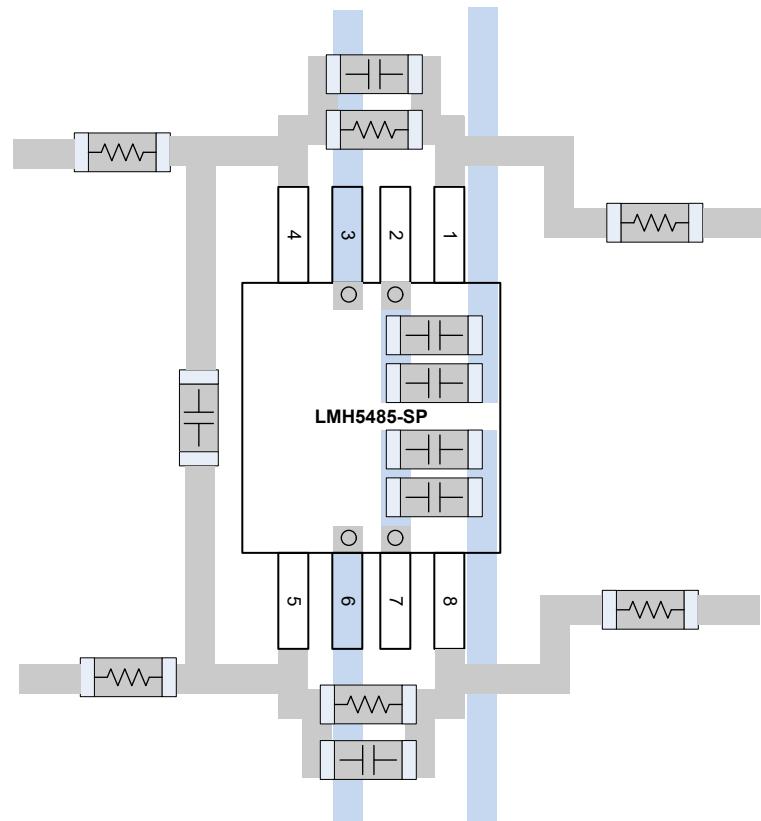

### 7.1 Example Characterization Circuits

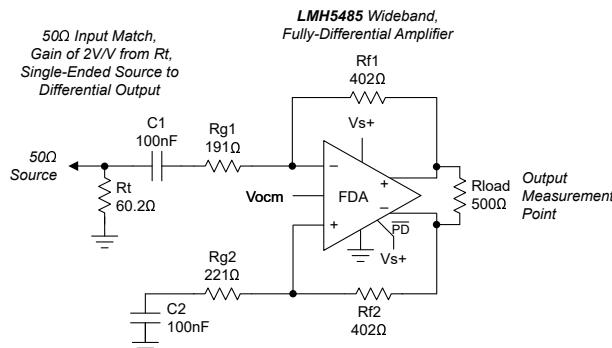

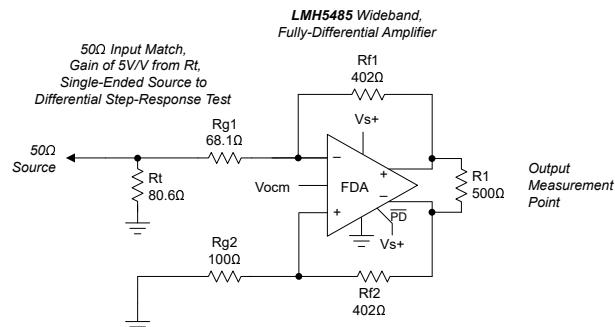

The LMH5485-SP offers the advantages of a fully differential amplifier (FDA) design, with the trimmed input offset voltage of a precision op amp. The FDA is an extremely flexible device that provides a purely differential output signal centered on a settable output common-mode level. The primary options revolve around the choices of single-ended or differential inputs, ac-coupled or dc-coupled signal paths, gain targets, and resistor value selections. Differential sources can certainly be supported and are often simpler to both implement and analyze. Figure 7-1 and Figure 7-2 show examples of both ac and dc coupled single-ended to differential circuits.

**Figure 7-1. AC-Coupled, Single-Ended Source to a Differential Gain of a 2V/V Test Circuit**

**Figure 7-2. DC-Coupled, Single-Ended-to-Differential, Basic Test Circuit Set for a Gain of 5V/V**

Most lab equipment is single-ended; therefore, the characterization circuits typically operate with a single-ended, matched, 50Ω input termination to a differential output at the FDA output pins. That output is then translated back to single-ended through a variety of baluns (or transformers) depending on the test and frequency range. DC-coupled, step-response testing uses two 50Ω scope inputs with trace math.

Figure 7-1 shows how most characterization plots fix the  $R_f$  value at 402Ω. This value is completely flexible in application, but the 402Ω provides a good compromise for the issues linked to this value, specifically:

- Added output loading. The FDA appears like an inverting op amp design with both feedback resistors as an added load across the outputs (approximate total differential load in Figure 7-1 is  $500\Omega \parallel 804\Omega = 308\Omega$ ).

- Noise contributions because of the resistor values. The resistors contribute both a  $4kTR$  term and provide gain for the input current noise.

- Parasitic feedback pole at the input summing nodes. This pole created by the feedback  $R$  value and the 1.25pF differential input capacitance (as well as any board layout parasitic) introduces a zero in the noise gain, decreasing the phase margin in most situations. This effect must be managed for best frequency response flatness or step response overshoot. The 402Ω value selected does degrade the phase margin slightly over a lower value, but does not decrease the loading significantly from the nominal 500Ω value across the output pins.

## 8 Detailed Description

### 8.1 Overview

The LMH5485-SP is a voltage-feedback-based, fully-differential amplifier (FDA) with a trimmed supply current and input offset voltage. The core differential amplifier is a slightly decompensated voltage-feedback design with a high slew-rate, precision input stage. This design gives a 490MHz, gain of 2V/V, small-signal bandwidth shown in the characterization curves, with a 1400V/ $\mu$ s slew rate, yielding approximately a 315MHz, 2V<sub>PP</sub>, large-signal bandwidth in the same circuit configuration.

The outputs offer near rail-to-rail output swing (0.2V headroom to either supply), while the device inputs are negative rail inputs with approximately 1.2V of headroom required to the positive supply. Figure 7-2 shows how this negative rail input directly supports a bipolar input around ground in a dc-coupled, single-supply design. Similar to all FDA devices, the output average voltage (common-mode) is controlled by a separate common-mode loop. The target for this output average is set by the  $V_{OCM}$  input pin that can be either floated to default near midsupply or driven to a desired output common-mode voltage. The  $V_{OCM}$  range extends from a very low 0.91V above the negative supply to 1.1V below the positive supply, supporting a wide range of modern analog-to-digital converter (ADC) input common-mode requirements using a single 2.7V to 5.4V supply range for the LMH5485-SP.

A power-down pin ( $\overline{PD}$ ) is included. Pull the  $\overline{PD}$  pin voltage to the negative supply to turn the device off, putting the LMH5485-SP into a very-low quiescent current state. To use the full supply range of the device, keep the device in normal operation by keeping the  $\overline{PD}$  pin asserted high. When the device is disabled, remember that the signal path is still present through the passive external resistors. Input signals applied to a disabled LMH5485-SP, as with any disabled FDA device, still appear at the outputs at some level through this passive resistor path.

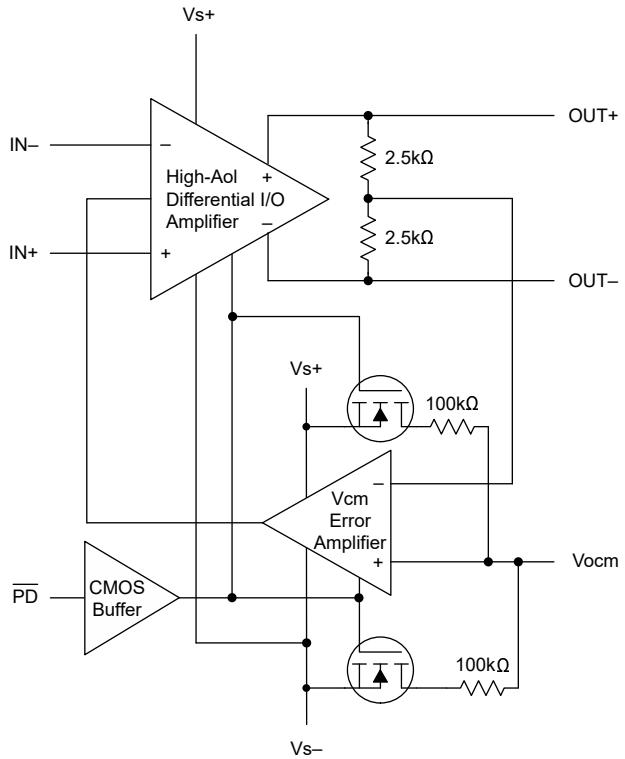

### 8.2 Functional Block Diagram

## 8.3 Feature Description

### 8.3.1 Differential I/O

The LMH5485-SP combines a core differential I/O, high-gain block with an output common-mode sense that is compared to a reference voltage and then fed back into the main amplifier block to control the average output to that reference. The differential I/O block is a classic, high open-loop gain stage with a dominant pole at approximately 900Hz. This voltage feedback structure projects a single-pole, unity-gain  $A_{OL}$  at 850MHz (gain bandwidth product). The high-speed differential outputs include an internal averaging resistor network to sense the output common-mode voltage. This voltage is compared by a separate  $V_{cm}$  error amplifier to the voltage on the  $V_{ocm}$  pin. If floated, this reference is at half the total supply voltage across the device using two 100k $\Omega$  resistors. This  $V_{cm}$  error amplifier transmits a correction signal into the main amplifier to force the output average voltage to meet the target voltage on the  $V_{ocm}$  pin. The bandwidth of this error amplifier is approximately the same bandwidth as the main differential I/O amplifier.

The differential outputs are collector outputs to obtain the rail-to-rail output swing. These outputs are relatively high-impedance, open-loop sources; however, closing the loop provides a very low output impedance for load driving. No output current limit or thermal shutdown features are provided in this lower-power device. The differential inputs are PNP inputs to provide a negative-rail input range.

To operate the LMH5485-SP connect the OUT– pin to the IN+ pin through an  $R_f$ , and the OUT+ pin to the IN– pin through the same value of  $R_f$ . Bring in the inputs through additional resistors to the IN+ and IN– pins. The differential I/O op amp operates similarly to an inverting op amp structure where the source must drive the input resistor and the gain is the ratio of the feedback to the input resistor.

### 8.3.2 Power-Down Control Pin ( $\overline{PD}$ )

The LMH5485-SP includes a power-down control pin,  $\overline{PD}$ . This pin must be asserted high for correct amplifier operation. The  $\overline{PD}$  pin cannot be floated because there is no internal pullup or pull-down resistor on this pin to reduce disabled power consumption. Asserting this pin low (within 0.7V of the negative supply) puts the LMH5485-SP into a very low quiescent state (approximately 2 $\mu$ A). Switches in the default  $V_{ocm}$  resistor string open to eliminate the fixed bias current (25 $\mu$ A) across the supply in this 200k $\Omega$  voltage divider to mid-supply.

#### 8.3.2.1 Operating the Power Shutdown Feature

When the  $\overline{PD}$  pin is asserted high, close to the positive supply, the device is in normal active mode of operation. To disable the device for reduced power consumption, assert the  $\overline{PD}$  low, close to the negative supply. [Figure 6-22](#) shows the PD pin voltage and the corresponding quiescent current drawn. For applications that require the device to only be powered on when the supplies are present, tie the  $\overline{PD}$  pin to the positive supply voltage.

The disable operation is referenced from the negative supply (normally, ground). For split-supply operation, with the negative supply below ground, a disable control voltage below ground is required to turn the LMH5485-SP off when the negative supply exceeds –0.7V.

For single-supply operation, a minimum of 1.7V greater than the negative supply (ground, in this case) is required for proper operation. This minimum logic-high level allows for direct operation from 1.8V supply logic.

### 8.3.3 Input Overdrive Operation

The LMH5485-SP input stage architecture is intrinsically robust to input overdrives with the series input resistor required by all applications. High input overdrives cause the outputs to limit the maximum swings with the remaining input current through the  $R_g$  resistors absorbed by internal, back-to-back protection diodes across the two inputs. These diodes are normally off in application, and only turn on to absorb the currents that a large input overdrive can produce through the source impedance and or the series  $R_g$  elements required by all designs.

The internal input diodes can safely absorb up to  $\pm 15$ mA in an overdrive condition. For designs that require more current to be absorbed, consider adding an external protection diode.

## 8.4 Device Functional Modes

This wideband FDA requires external resistors for correct signal-path operation. When configured for the desired input impedance and gain setting with these external resistors, the amplifier can be either *on* with the  $\overline{PD}$  pin asserted to a voltage greater than  $(V_{S-}) + 1.7V$  or turned *off* by asserting  $\overline{PD}$  low. Disabling the amplifier shuts off the quiescent current and stops the correct amplifier operation. The signal path is still present for the source signal through the external resistors.

The  $V_{OCM}$  control pin sets the output average voltage. Left open,  $V_{OCM}$  defaults to an internal midsupply value. Driving this high-impedance input with a voltage reference within the valid range sets a target for the internal  $V_{CM}$  error amplifier.

### 8.4.1 Operation from Single-Ended Sources to Differential Outputs

One of the most useful features supported by the FDA device is an easy conversion from a single-ended input to a differential output centered on a user-controlled, common-mode level. While the output side is relatively straightforward, the device input pins move in a common-mode sense with the input signal. This common-mode voltage at the input pins moving with the input signal acts to increase the apparent input impedance to be greater than the  $R_g$  value. This input active impedance issue applies to both ac- and dc-coupled designs, and requires somewhat more complex solutions for the resistors to account for this active impedance, and is shown in the following subsections.

#### 8.4.1.1 AC-Coupled Signal Path Considerations for Single-Ended Input to Differential Output Conversion

When the signal path can be ac-coupled, the dc biasing for the LMH5485-SP becomes a relatively simple task. In all designs, start by defining the output common-mode voltage. The ac-coupling issue can be separated for the input and output sides of an FDA design. In any case, the design starts by setting the desired  $V_{OCM}$ . When an ac-coupled path follows the output pins, the best linearity is achieved by operating  $V_{OCM}$  at mid-supply. The  $V_{OCM}$  voltage must be within the linear range for the common-mode loop, as specified in the headroom specifications (approximately 0.91V greater than the negative supply and 1.1V less than the positive supply). If the output path is also ac coupled, simply letting the  $V_{OCM}$  control pin float is typically preferred to get a midsupply default  $V_{OCM}$  bias with minimal elements. To limit noise, place a  $0.1\mu F$  decoupling capacitor on the  $V_{OCM}$  pin to ground.

After  $V_{OCM}$  is defined, check the target output voltage swing and ensure that the  $V_{OCM}$  plus the positive or negative output swing on each side does not clip into the supplies. Check that  $V_{OCM} \pm V_p$  does not exceed the absolute supply rails for this rail-to-rail output (RRO) device.

Going to the device input pins side, because both the source and balancing resistor on the nonsignal input side are dc blocked (see [Figure 7-1](#)), no common-mode current flows from the output common-mode voltage, thus setting the input common-mode equal to the output common-mode voltage.

This input headroom also sets a limit for higher  $V_{OCM}$  voltages. Because the input  $V_{ICM}$  is the output  $V_{OCM}$  for ac-coupled sources, the 1.2V minimum headroom for the input pins to the positive supply overrides the 1.1V headroom limit for the output  $V_{OCM}$ . The input signal also moves this input  $V_{ICM}$  around the dc bias point.

#### 8.4.1.2 DC-Coupled Input Signal Path Considerations for Single-Ended to Differential Conversion

The output considerations remain the same as for the ac-coupled design. Again, the input can be dc-coupled while the output is ac-coupled. A dc-coupled input with an ac-coupled output can have some advantages to move the input  $V_{ICM}$  down if the source is ground referenced. [Figure 7-2](#) shows how when the source is dc-coupled into the LMH5485-SP, both sides of the input circuit must be dc coupled to retain differential balance. Normally, the nonsignal input side has an  $R_g$  element biased to whatever the source midrange is expected to be. Providing this midscale reference gives a balanced differential swing around  $V_{OCM}$  at the outputs.

One significant consideration for a dc-coupled input is that  $V_{OCM}$  sets up a common-mode bias current from the output back through  $R_f$  and  $R_g$  to the source on both sides of the feedback. Without input balancing networks, the source must sink or source this dc current. After the input signal range and biasing on the other  $R_g$  element is set, check that the voltage divider from  $V_{OCM}$  to  $V_{IN}$  through  $R_f$  and  $R_g$  (and possibly  $R_s$ ) establishes an input  $V_{ICM}$  at the device input pins that is in range. If the average source is at ground, the negative rail input stage for

the LMH5485-SP is in range for applications using a single positive supply and a positive output  $V_{OCM}$  setting because this dc current lifts the average FDA input summing junctions up off of ground to a positive voltage (the average of the  $V_+$  and  $V_-$  input pin voltages on the FDA).

#### 8.4.2 Differential-Input to Differential-Output Operation

In many ways, this method is a much simpler way to operate the FDA from a design equations perspective. Assuming the two sides of the circuit are balanced with equal  $R_f$  and  $R_g$  elements, the differential input impedance is the sum of the two  $R_g$  elements to a differential inverting summing junction. In these designs, the input common-mode voltage at the summing junctions does not move with the signal, but must be DC biased in the allowable range for the input pins with consideration given to the voltage headroom required from each supply. Slightly different considerations apply to AC- or DC-coupled, differential-in to differential-out designs, as described in the following sections.

##### 8.4.2.1 AC-Coupled, Differential-Input to Differential-Output Design Issues

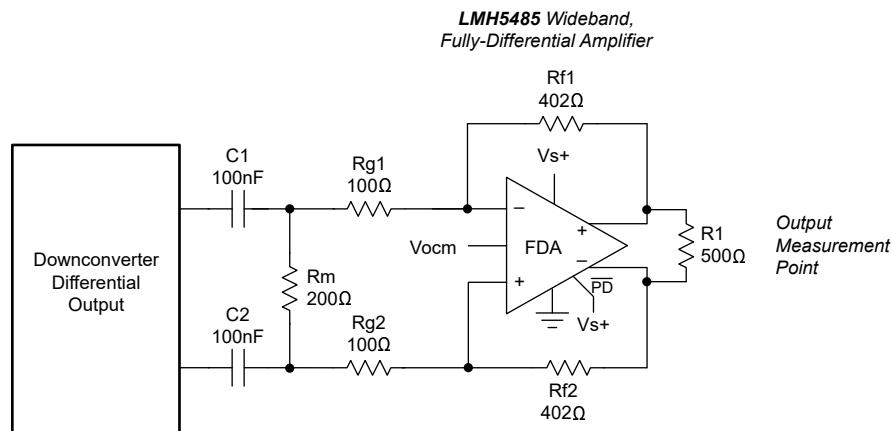

There are two typical ways to use the LMH5485-SP with an ac-coupled differential source. In the first method, the source is differential and can be coupled in through two blocking capacitors. The second method uses either a single-ended or a differential source and couples in through a transformer (or balun). [Figure 8-1](#) shows a typical blocking capacitor approach to a differential input. An optional input differential termination resistor ( $R_m$ ) is included in this design. This  $R_m$  element allows the input  $R_g$  resistors to be scaled up while still delivering lower differential input impedance to the source. In this example, the  $R_g$  elements sum to show a  $200\Omega$  differential impedance, while the  $R_m$  element combines in parallel to give a net  $100\Omega$ , ac-coupled, differential impedance to the source. Again, the design proceeds by selecting the  $R_f$  element values, then the  $R_g$  to set the differential gain, then an  $R_m$  element (if needed) to achieve a target input impedance. Alternatively, the  $R_m$  element can be eliminated, the  $R_g$  elements set to the desired input impedance, and  $R_f$  set to the get the differential gain ( $= R_f / R_g$ ).

**Figure 8-1. Down-Converting Mixer Delivering an AC-Coupled Differential Signal to the LMH5485-SP**

The dc biasing here is very simple. The output  $V_{OCM}$  is set by the input control voltage. Because there is no dc current path for the output common-mode voltage, that dc bias also sets the input pins common-mode operating points.

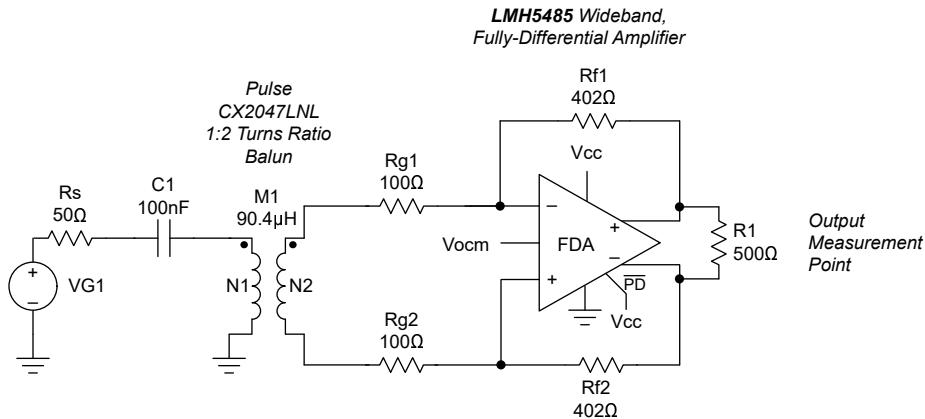

Transformer input coupling allows either a single-ended or differential source to be coupled into the LMH5485-SP, which also improves the input-referred noise figure. These designs assume a source impedance that must be matched in the balun interface. [Figure 8-2](#) shows the simplest approach where an example 1:2 turns ratio step-up transformer is used from a  $50\Omega$  source.

**Figure 8-2. Input Balun Interface Delivers a Differential Input to the LMH5485-SP**

In this example, this 1:2 turns ratio step-up transformer provides a source and load match from the  $50\Omega$  source if the secondary is terminated in  $200\Omega$  (turns-ratio squared is the impedance ratio across a balun). The two  $R_g$  elements provide that termination as these resistors sum to the differential virtual ground at the FDA summing junctions. The input blocking cap ( $C_1$ ) is optional and included only to eliminate dc shorts to ground from the source. This implementation often improves the total noise figure compared to using just the FDA, as this configuration allows for reduction of the amplifier noise gain.

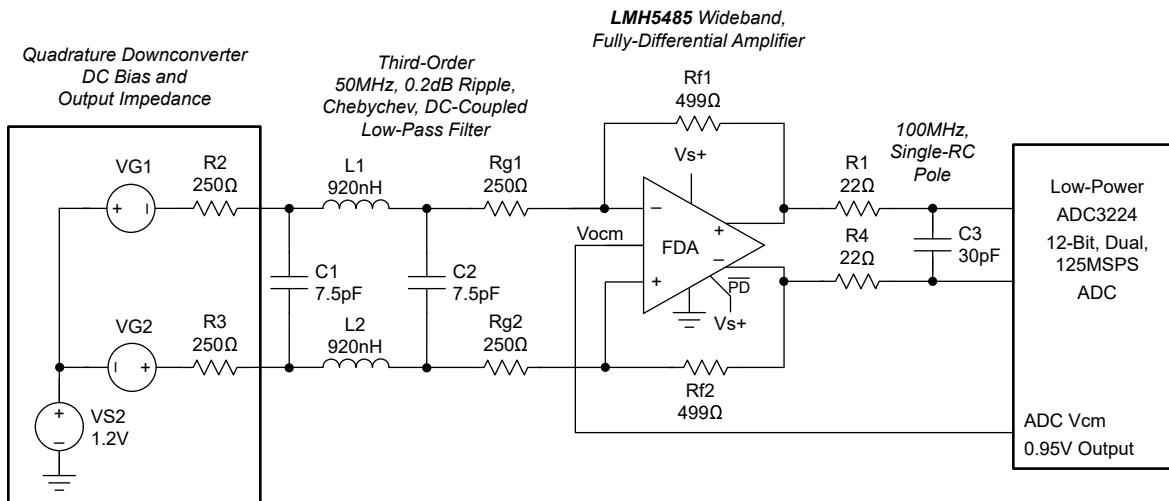

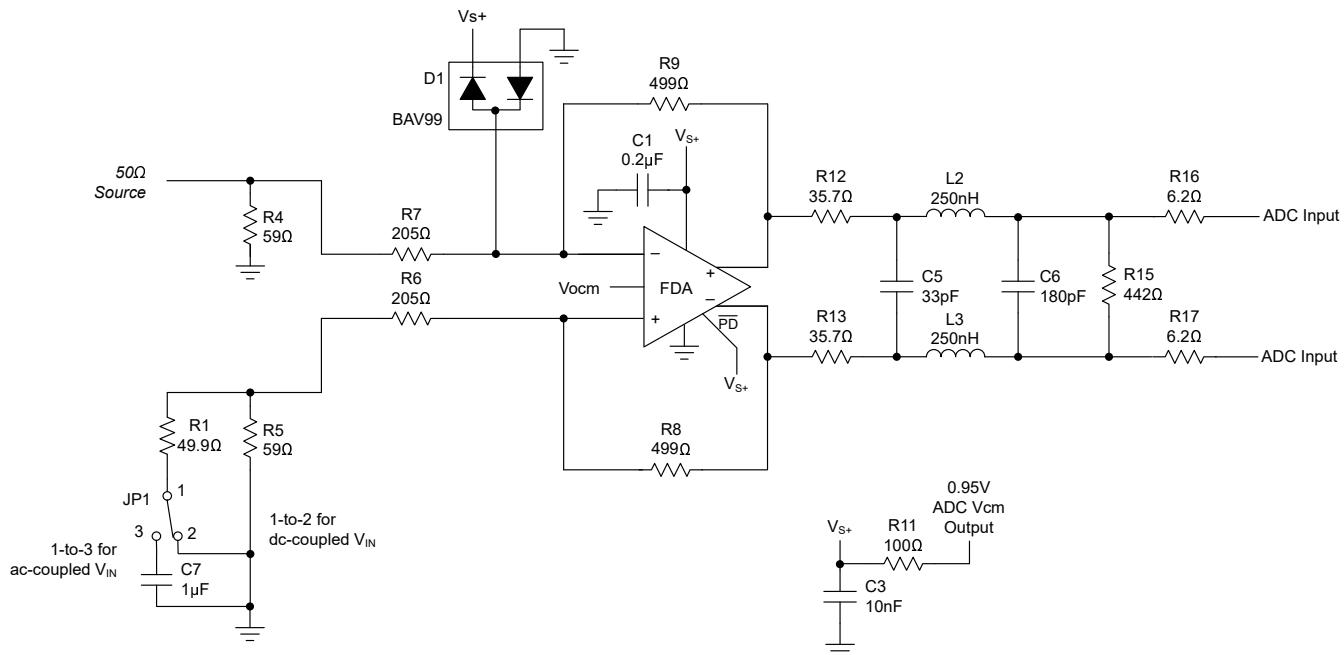

#### 8.4.2.2 DC-Coupled, Differential-Input to Differential-Output Design Issues