**bq25120A**SLUSD08A –MAY 2017–REVISED JANUARY 2018

# bq25120A Low I<sub>Q</sub> Highly Integrated Battery Charge Management Solution for Wearables and IoT

#### 1 Features

- Increases System Operation Time Between Charges

- Configurable 300-mA Buck Regulator (1.8-V Default)

- 700 nA (typical) Iq with Buck Converter Enabled (No Load)

- Configurable Load Switch or 100mA LDO Output (Load Switch by Default)

- Up to 300-mA Charge Current for Fast Charging

- 0.5% Accurate Battery Voltage Regulation (Configurable from 3.6 V to 4.65 V in 10-mV Steps)

- Configurable Termination Current Down to 500 μA

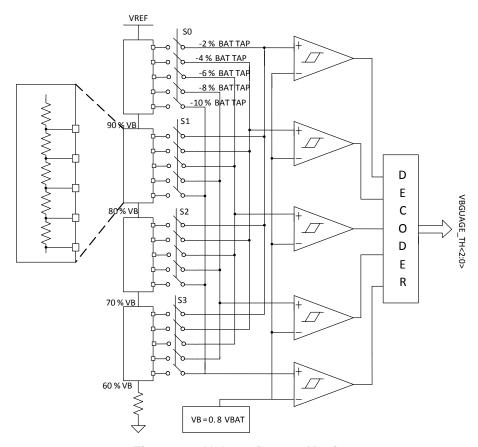

- Simple Voltage Based Battery Monitor

- Highly Integrated Solution with Small Footprint

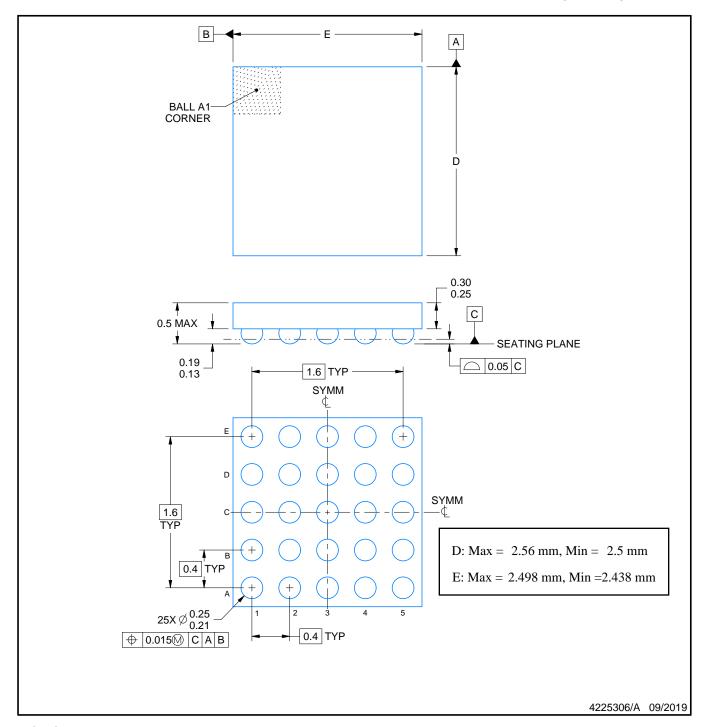

- 2.5 mm x 2.5 mm WCSP Package and 6 External Components for Minimal Solution

- Push-Button Wake-Up and Reset with Adjustable Timers

- Power Path Management for Powering the System and Charging the Battery

- Power Path Management enables <50 nA Ship Mode Battery Quiescent Current for Longest Shelf Life

- Battery Charger Operates from 3.4 V 5.5 V<sub>IN</sub> (5.5-V OVP / 20-V Tolerant)

- Dedicated Pins for Input Current Limit, Charge Current, Termination Current, and Status Output

- I<sup>2</sup>C Communication Control

- Charge Voltage and Current

- Termination Threshold

- Input Current Limit

- VINDPM Threshold

- Timer Options

- Load Switch Control

- Controls for Interrupts for Faults and Status

- System Output Voltage Adjustment

- LDO Output Voltage Adjustment

## 2 Applications

- Smart Watches and other Wearable Devices

- Fitness Accessories

- · Health Monitoring Medical Accessories

- Rechargeable Toys

## 3 Description

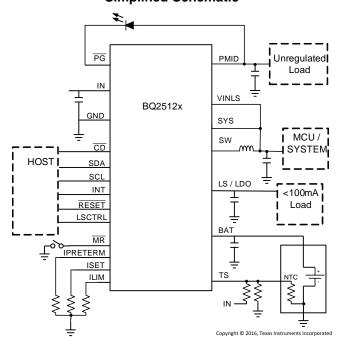

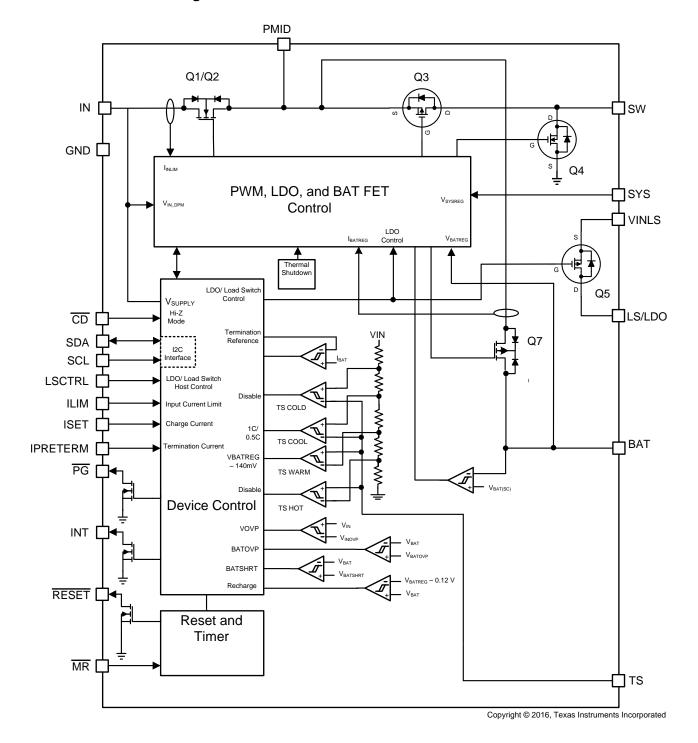

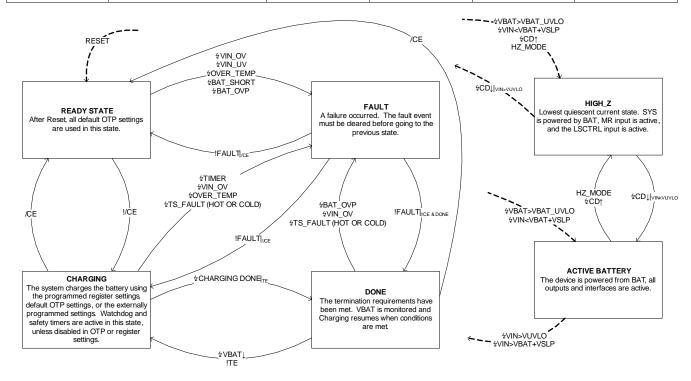

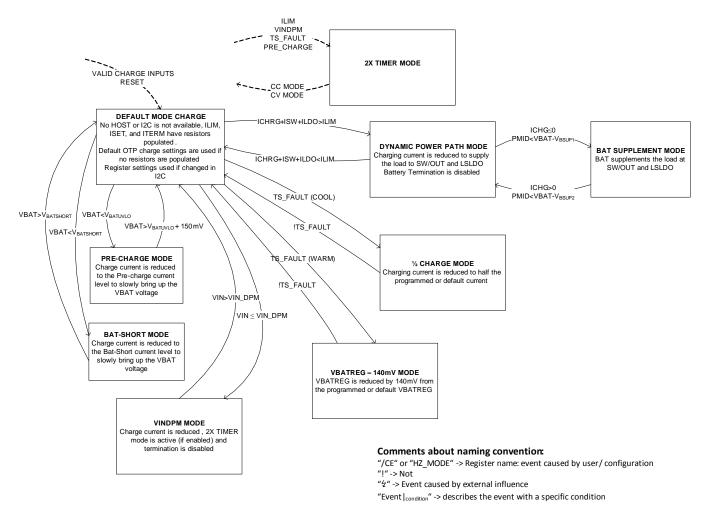

The bq25120A is a highly integrated battery charge management IC that integrates the most common functions for wearable devices: Linear charger, regulated output, load switch, manual reset with timer, and battery voltage monitor. The integrated buck converter is a high efficiency, low  $I_{\rm Q}$  switcher using DCS control that extends light load efficiency down to 10- $\mu$ A load currents. The low quiescent current during operation and shutdown enables maximum battery life. The device supports charge currents from 5 mA to 300 mA. The input current limit, charge current, buck converter output voltage, LDO output voltage, and other parameters are programmable through the  $I^2$ C interface.

#### **Device Information**(1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| BQ25120A    | DSBGA (25) | 2.50 mm x 2.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

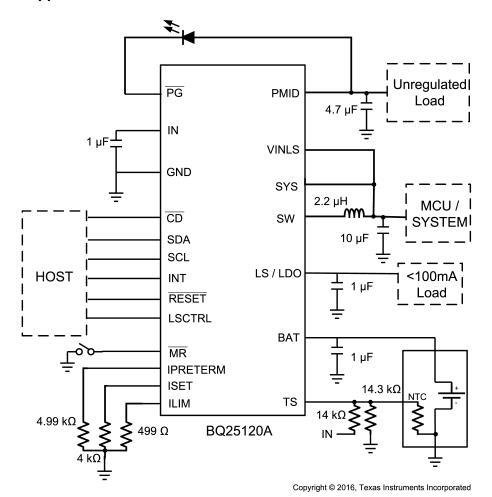

#### Simplified Schematic

## **Table of Contents**

| 1 | Features 1                                                        |    | 9.3 Feature Description              | 18              |

|---|-------------------------------------------------------------------|----|--------------------------------------|-----------------|

| 2 | Applications 1                                                    |    | 9.4 Device Functional Modes          | 31              |

| 3 | Description 1                                                     |    | 9.5 Programming                      | <mark>33</mark> |

| 4 | Revision History2                                                 |    | 9.6 Register Maps                    | 36              |

| 5 | Description (continued)3                                          | 10 | Application and Implementation       | 47              |

| 6 | Device Comparison Table3                                          |    | 10.1 Application Information         |                 |

| 7 | Pin Configuration and Functions4                                  |    | 10.2 Typical Application             | 47              |

| - | <del>-</del>                                                      | 11 | Power Supply Recommendations         | 62              |

| 8 | Specifications                                                    | 12 | Layout                               | 63              |

|   | 8.1 Absolute Maximum Ratings                                      |    | 12.1 Layout Guidelines               |                 |

|   | 8.2 ESD Ratings                                                   |    | 12.2 Layout Example                  |                 |

|   | 8.3 Recommended Operating Conditions                              | 13 | Device and Documentation Support     | 64              |

|   |                                                                   |    | 13.1 Device Support                  |                 |

|   | 8.5 Electrical Characteristics                                    |    | 13.2 Trademarks                      |                 |

|   | 8.6 Timing Requirements                                           |    | 13.3 Electrostatic Discharge Caution |                 |

| _ | 8.7 Typical Characteristics                                       |    | 13.4 Glossary                        |                 |

| 9 | Detailed Description         17           9.1 Overview         17 | 14 | Mechanical, Packaging, and Orderable |                 |

|   | 9.2 Functional Block Diagram                                      |    | Information                          | 64              |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Original (May 2017) to Revision A                           |    |  |

|---|--------------------------------------------------------------------------|----|--|

| • | Changed expression terms in Equation 3 and Equation 4 for clarification. | 26 |  |

## 5 Description (continued)

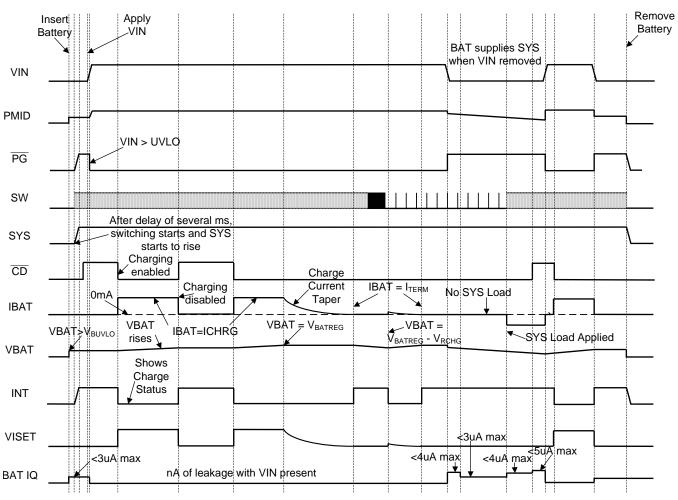

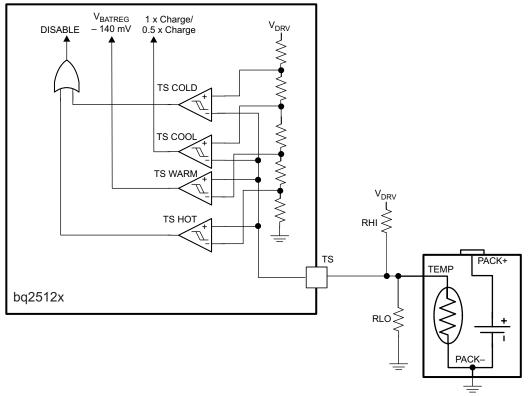

The battery is charged using a standard Li-lon charge profile with three phases: precharge, constant current and constant voltage. A voltage-based JEITA compatible battery pack thermistor monitoring input (TS) is included that monitors battery temperature and automatically changes charge parameters to prevent the battery from charging outside of its safe temperature range. The charger is optimized for 5-V USB input, with 20-V tolerance to withstand line transients. The buck converter is run from the input or battery. When in battery only mode, the device can run from a battery up to 4.65 V.

A configurable load switch allows system optimization by disconnecting infrequently used devices. The manual reset with timer allows mutliple different configuration options for wake are reset optimization.

## 6 Device Comparison Table

| PART NUMBER | VINDPM  | DEFAULT SYS<br>OUTPUT | DEFAULT LDO<br>OUTPUT | DEFAULT<br>VBERG | DEFAULT<br>CHARGE<br>CURRENT | DEFAULT<br>TERMINATION<br>CURRENT | DEFAULT SHIP<br>MODE |

|-------------|---------|-----------------------|-----------------------|------------------|------------------------------|-----------------------------------|----------------------|

| BQ25120A    | Enabled | 1.8 V                 | Load Switch           | 4.2 V            | 10 mA                        | 2 mA                              | Off                  |

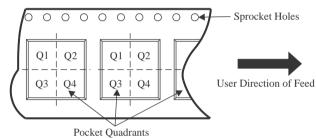

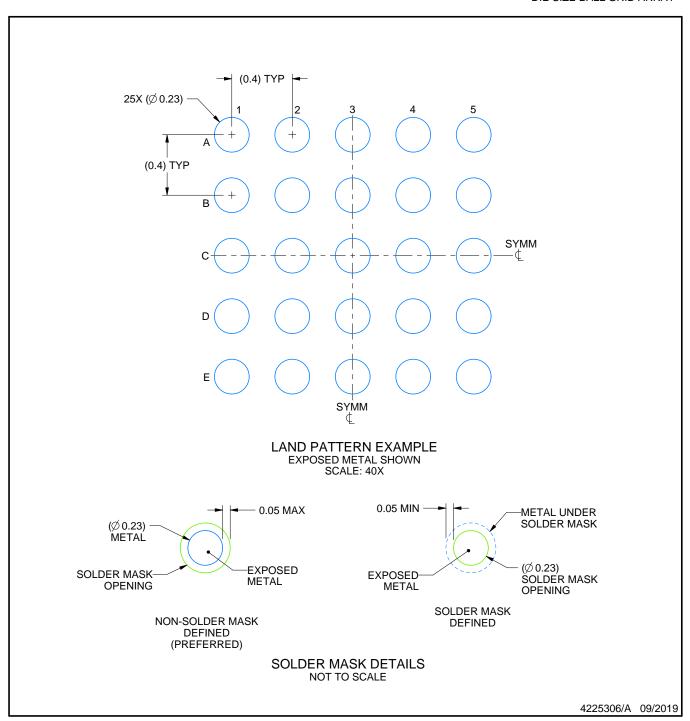

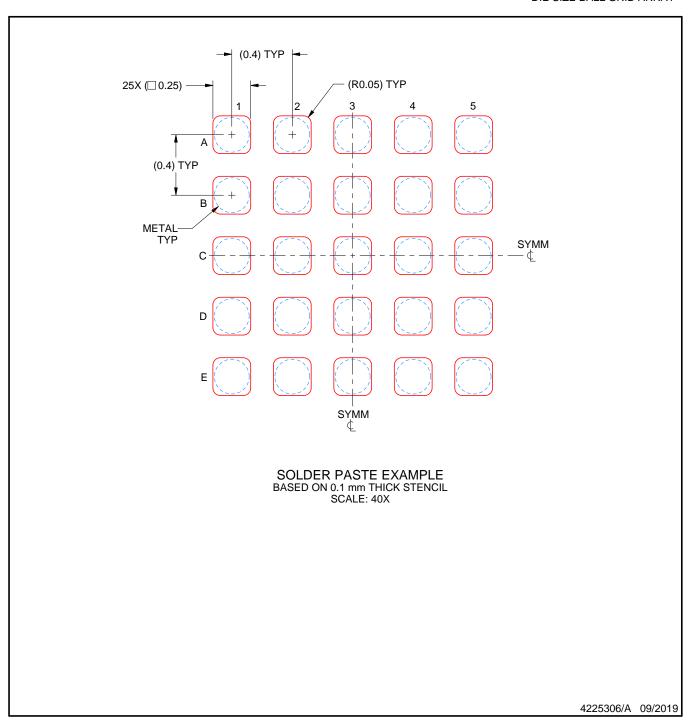

## 7 Pin Configuration and Functions

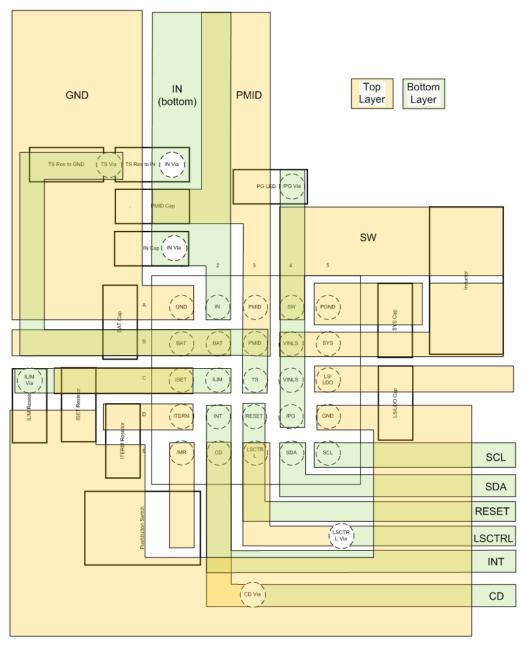

A GND (IN PMID) (SW PGND)

B BAT (BAT) (PMID) (VINLS) (SYS)

C (ISET) (ILIM) (TS) (VINLS) (LS/LDO)

D (IPRETE RM) (INT) (RESET) (/PG) (GND)

E (/MR) (/CD) (LSCTRL) (SDA) (SCL)

#### **Pin Functions**

| P      | IN     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO.    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| IN     | A2     | 1   | DC Input Power Supply. IN is connected to the external DC supply. Bypass IN to GND with at least 1 $\mu$ F of capacitance using a ceramic capacitor.                                                                                                                                                                                                                                                                                                 |  |

| PMID   | A3, B3 | I/O | High Side Bypass Connection. Connect at least $3\mu F$ of ceramic capacitance with DC bias derating from PMID to GND as close to the PMID and GND pins as possible. When entering Ship Mode, PMID is discharged by a 20-k $\Omega$ internal discharge resistor.                                                                                                                                                                                      |  |

| GND    | A1, D5 |     | Ground connection. Connect to the ground plane of the circuit.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| PGND   | A5     |     | Power ground connection. Connect to the ground plane of the circuit. Connect the output filter cap from the buck converter to this ground as shown in the layout example.                                                                                                                                                                                                                                                                            |  |

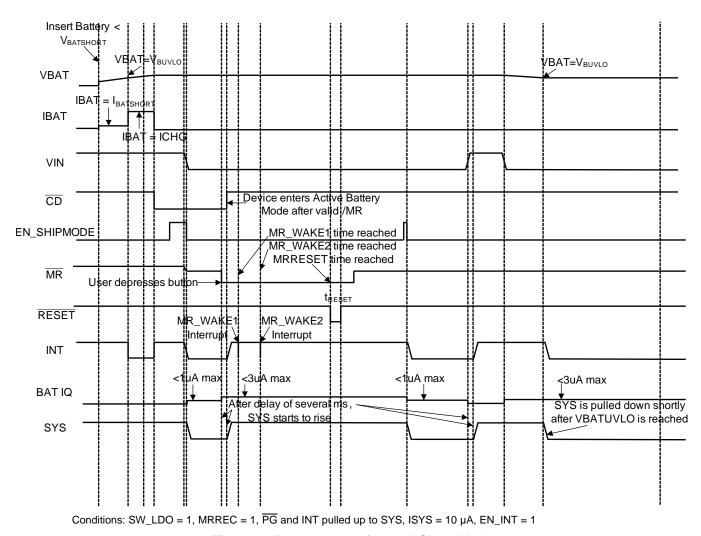

| CD     | E2     | I   | Chip Disable. Drive $\overline{\text{CD}}$ low to place the <u>part</u> in High-Z mode with battery only present, enable charging when $V_{\text{IN}}$ is valid. Drive $\overline{\text{CD}}$ high for Active Battery mode when battery is present, and disable charge when $V_{\text{IN}}$ is present. $\overline{\text{CD}}$ is pulled low internally with 900 modes.                                                                              |  |

| SDA    | E4     | I/O | $I^2$ C Interface Data. Connect SDA to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                      |  |

| SCL    | E5     | I   | I <sup>2</sup> C Interface Clock. Connect SCL to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                                                            |  |

| ILIM   | C2     | I   | Adjustable Input Current Limit Programming. Connect a resistor from ILIM to GND to program the input current limit. The input current includes the system load and the battery charge current. Connect ILIM to GND to set the input current limit to the internal default threshold. ILIM can also be updated through I <sup>2</sup> C.                                                                                                              |  |

| LSCTRL | E3     | 1   | Load Switch and LDO Control Input. Pull high to enable the LS/LDO output, pull low to disable the LS/LDO output.                                                                                                                                                                                                                                                                                                                                     |  |

| ISET   | C1     | I   | Fast-Charge Current Programming Input. Connect a resistor from ISET to GND to program the fast-charge current level. Connect a resistor from ISET to GND to set the charge current to the internal default. ISET can also be updated through I <sup>2</sup> C. While charging, the voltage at ISET reflects the actual charging current and can be used to monitor charge current if an ISET resistor is present and the device is not in host mode. |  |

## Pin Functions (continued)

| Pl       | IN     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IPRETERM | D1     | I   | Termination current programming input. Connect a $0-\Omega$ to $10-k\Omega$ resistor from IPRETERM to GND to program the termination current between 5% and 20% of the charge current. The pre-charge current is the same as the termination current setting. Connect IPRETERM to GND to set the termination current to the internal default threshold. IPRETERM can also be updated through $I^2C$ .                                                                                                                                                                                                                                                                                       |

| INT      | D2     | 0   | Status Output. INT is an open-drain output that signals charging status and fault interrupts. INT pulls low during charging. INT is high impedance when charging is complete, disabled, or the charger is in high impedance mode. When a fault occurs, a 128µs pulse is sent out as an interrupt for the host. INT charge indicator function is enabled/disabled using the EN_INT bit in the control register. Connect INT to a logic rail using an LED for visual indication of charge status or through a $100 \mathrm{k}\Omega$ resistor to communicate with the host processor.                                                                                                         |

| PG       | D4     | 0   | Open-drain Power Good status indication output. $\overline{PG}$ pulls to GND when $V_{IN}$ is above $V_{(BAT)}+V_{SLP}$ and less that $V_{OVP}$ . $\overline{PG}$ is high-impedance when the input power is not within specified limits. Connect $\overline{PG}$ to the desired logic voltage rail using a $1k\Omega$ to $100k\Omega$ resistor, or use with an LED for visual indication. $\overline{PG}$ can also be configured as a push-button voltage shifted output (MRS) in the registers, where the output of the $\overline{PG}$ pin reflects the status of the $\overline{MR}$ input, but pulled up to the desired logic voltage rail using a $1k\Omega$ to $100k\Omega$ resistor. |

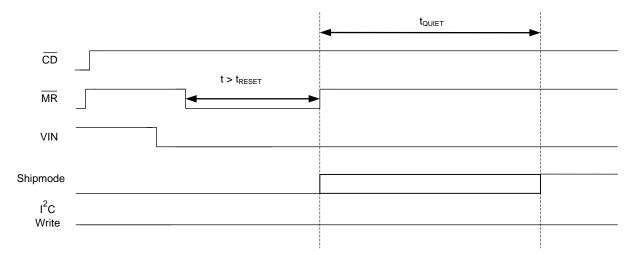

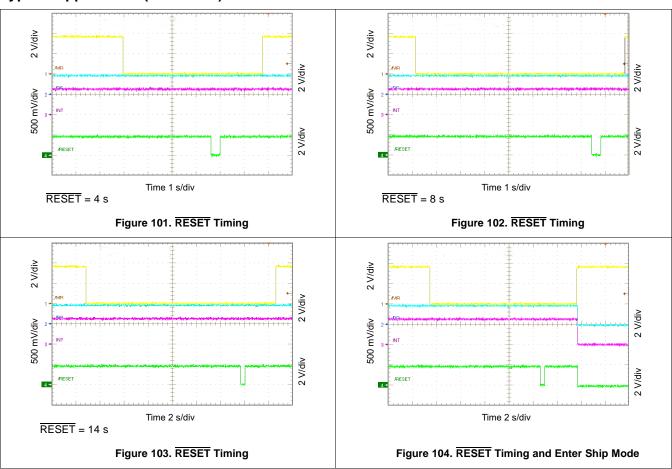

| RESET    | D3     | 0   | Reset Output. $\overline{\text{RESET}}$ is an open drain active low output that goes low when $\overline{\text{MR}}$ is held low for longer than $t_{\text{RESET}}$ , which is configurable by the MRRESET registers. $\overline{\text{RESET}}$ is deasserted after the $t_{\text{RESET\_D}}$ , typically 400ms.                                                                                                                                                                                                                                                                                                                                                                            |

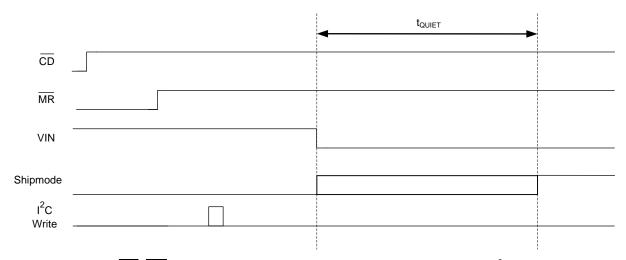

| MR       | E1     | I   | Manual Reset Input. $\overline{\text{MR}}$ is a <u>pu</u> sh-button input that must be held low for greater than $t_{\text{RESET}}$ to assert the reset output. If $\overline{\text{MR}}$ is pressed for a shorter period, there are <u>two</u> programmable timer events, $t_{\text{WAKE1}}$ and $t_{\text{WAKE2}}$ , that trigger an interrupt to the host. The $\overline{\text{MR}}$ input can also be used to bring the device out of Ship mode.                                                                                                                                                                                                                                       |

| SW       | A4     | 0   | Inductor Connection. Connect to the switched side of the external inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SYS      | B5     | 1   | System Voltage Sense Connection. Connect SYS to the system output at the output bulk capacitors. Bypass SYS locally with at least 4.7 $\mu$ F of effective ceramic capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LS/LDO   | C5     | 0   | Load Switch or LDO output. Connect 1 $\mu$ F of effective ceramic capacitance to this pin to assure stability. Be sure to account for capacitance bias voltage derating when selecting the capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VINLS    | B4, C4 | I   | Input to the Load Switch / LDO output. Connect 1 $\mu F$ of effective ceramic capacitance from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BAT      | B1, B2 | I/O | Battery Connection. Connect to the positive terminal of the battery. Bypass BAT to GND with at least 1 $\mu$ F of ceramic capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TS       | C3     | I   | Battery Pack NTC Monitor. Connect TS to the center tap of a resistor divider from VIN to GND. The NTC is connected from TS to GND. The TS function provides four thresholds for JEITA compatibility. TS faults are reported by the I <sup>2</sup> C interface during charge mode.                                                                                                                                                                                                                                                                                                                                                                                                           |

## 8 Specifications

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                                            |         | MIN  | MAX | UNIT |

|---------------------------------------|------------------------------------------------------------|---------|------|-----|------|

|                                       | IN                                                         | wrt GND | -0.3 | 20  | V    |

| Input voltage                         | PMID, VINLS                                                | wrt GND | -0.3 | 7.7 | V    |

| input voltage                         | CD, SDA, SCL, ILIM, ISET, IPRETERM, LSCTRL, INT, RESET, TS | wrt GND | -0.3 | 5.5 | V    |

| Output voltage                        | SYS                                                        |         |      | 3.6 | V    |

| Input current                         | IN                                                         |         |      | 400 | mA   |

| Sink current                          | INT                                                        |         |      | 10  | mA   |

| Sink/Source Current                   | RESET                                                      |         |      | 10  | mA   |

| Output Voltage Continuos              | SW                                                         |         | -0.7 | 7.7 | V    |

| Outrout Commant Continuous            | SW                                                         |         |      | 400 | mA   |

| Output Current Continuous             | SYS, BAT                                                   |         |      | 300 | mA   |

| Current                               | LS/LDO                                                     |         |      | 150 | mA   |

| BAT Operating Voltage                 | VBAT, MR,                                                  |         |      | 6.6 | V    |

| Junction Temperature                  |                                                            |         | -40  | 125 | °C   |

| Storage Temperature, T <sub>stg</sub> |                                                            |         |      | 300 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                         |                                                     | MIN | NOM | MAX                | UNIT |

|-----------------------------------------|-----------------------------------------------------|-----|-----|--------------------|------|

| \ /                                     | IN voltage range                                    | 3.4 | 5   | 20                 | M    |

| $V_{IN}$                                | IN operating voltage range, recommended             | 3.4 | 5   | 5.5                | V    |

| V <sub>(BAT)</sub>                      | V <sub>(BAT)</sub> operating voltage range          |     |     | 5.5 <sup>(1)</sup> | V    |

| V <sub>(VINLS)</sub>                    | VINLS voltage range for Load Switch                 | 0.8 |     | 5.5 <sup>(2)</sup> | V    |

| V <sub>(VINLS)</sub>                    | VINLS voltage range for LDO                         | 2.2 |     | 5.5                | V    |

| I <sub>IN</sub>                         | Input Current, IN input                             |     |     | 400                | mA   |

| I <sub>(SW)</sub>                       | Output Current from SW, DC                          |     |     | 300                | mA   |

| I <sub>(PMID)</sub>                     | Output Current from PMID, DC                        |     |     | 300                | mA   |

| ILS/LDO                                 | Output Current from LS/LDO                          |     |     | 100                | mA   |

| I <sub>(BAT)</sub> , I <sub>(SYS)</sub> | Charging and discharging using internal battery FET |     |     | 300                | mA   |

| TJ                                      | Operating junction temperature range                | -40 |     | 125                | °C   |

<sup>(1)</sup> Any voltage greater than shown should be a transient event.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> These inputs will support 6.6 V for less than 10% of the lifetime at V<sub>(BAT)</sub> or VIN, with a reduced current and/or performance.

#### 8.4 Thermal Information

|                        |                                              | bq25120A                                                                                                                                                                                                                       |      |

|------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | bq25120A           YFP (DSBGA)         UNIT           25 PINS         60         °C/W           0.3         °C/W           12.0         °C/W           1.2         °C/W           12.0         °C/W           N/A         °C/W | UNIT |

|                        |                                              | 25 PINS                                                                                                                                                                                                                        |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 60                                                                                                                                                                                                                             | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 0.3                                                                                                                                                                                                                            | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 12.0                                                                                                                                                                                                                           | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1.2                                                                                                                                                                                                                            | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 12.0                                                                                                                                                                                                                           | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A                                                                                                                                                                                                                            | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

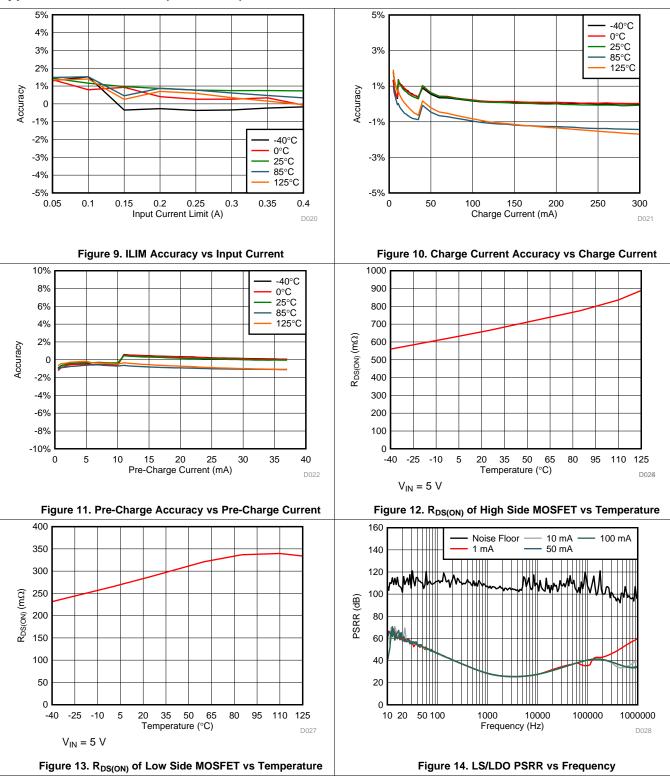

## 8.5 Electrical Characteristics

Circuit of Figure 1,  $V_{(UVLO)} < V_{IN} < V_{(OVP)}$  and  $V_{IN} > V_{(BAT)} + V_{(SLP)}$ ,  $T_J = -40^{\circ}\text{C}$  to 85°C and  $T_J = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

| Р                         | ARAMETERS                                             | TEST CONDITIONS                                                                                                                                                                                                                                    | MIN   | TYP                                          | MAX  | UNIT |

|---------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------|------|------|

| INPUT CURRE               |                                                       | 123.35.15.11                                                                                                                                                                                                                                       |       |                                              |      |      |

| IIII OT OOKKE             |                                                       | $V_{(UVLO)} < V_{IN} < V_{(OVP)}$ and $V_{IN} > V_{(BAT)} + V_{(SLP)}$ PWM                                                                                                                                                                         |       | 1                                            |      | mΛ   |

| lisi                      | Supply Current for                                    | Switching, $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}$ $V_{(\text{UVLO})} < V_{\text{IN}} < V_{(\text{OVP})} \text{ and } V_{\text{IN}} > V_{(\text{BAT})} + V_{(\text{SLP})} \text{ PWM NOT}$                                |       |                                              |      | mA   |

| Control                   |                                                       | Switching                                                                                                                                                                                                                                          |       |                                              | 3    | mA   |

|                           |                                                       | 0°C < T <sub>J</sub> < 85°C, V <sub>IN</sub> = 5 V, Charge Disabled                                                                                                                                                                                |       |                                              | 1.5  | mA   |

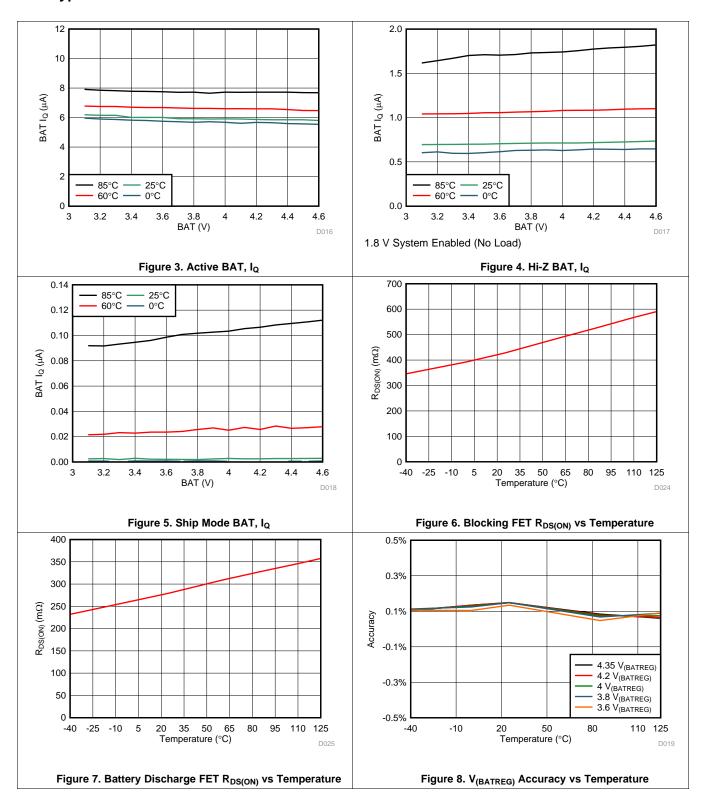

|                           |                                                       | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 60^{\circ}\text{C}, \text{ V}_{\text{IN}} = 0 \text{ V}, \text{ High-Z Mode, PWM Not Switching, V}_{\text{(BUVLO)}} < \text{V}_{\text{(BAT)}} < 4.65 \text{ V}$                                         |       | 0.7                                          | 1.2  | μΑ   |

|                           | Battery discharge current                             | $0^{\circ}C < T_{J} < 60^{\circ}C, \ V_{IN} = 0 \ V, \ High-Z \ Mode, \ PWM \ Not Switching, \ V_{(BUVLO)} < V_{(BAT)} < 6.6 \ V$                                                                                                                  |       | 0.9                                          | 1.5  | μΑ   |

| I(BAT_HIZ)                | in High Impedance Mode                                | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 60^{\circ}\text{C}, \text{V}_{\text{IN}} = 0 \text{ V or floating, High-Z Mode, PWM}$ Switching, No Load                                                                                                |       | 0.75                                         | 3.5  | μΑ   |

|                           |                                                       | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C},  \text{V}_{\text{IN}} = 0  \text{V},  \text{High-Z Mode, PWM Switching,}  \text{LSLDO enabled}$                                                                                     |       | 1.35                                         | 4.25 | μΑ   |

| 1                         | Battery discharge current                             | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C},  \text{V}_{\text{IN}} = 0 \text{V},  \text{Active Battery Mode, PWM}$ Switching, LSLDO enabled, I2C Enabled, $ \text{V}_{(\text{BUVLO})} < \text{V}_{(\text{BAT})} < 4.65 \text{V}$ |       | 6.8                                          | 12   | μA   |

| I(BAT_ACTIVE)             | in Active Battery Mode                                | $\begin{array}{l} 0^{\circ}C < T_{J} < 85^{\circ}C, \ 0 < V_{IN} < V_{IN(UVLO)}, \ Active \ Battery \ Mode, \\ PWM \ Switching, \ LSLDO \ disabled, \ I2C \ Enabled, \ \overline{CD} = Low, \\ V_{(BUVLO)} < V_{(BAT)} < 4.65 \ V \end{array}$     |       | 6.2                                          | 11   | μΑ   |

| I <sub>(BAT_SHIP)</sub>   | Battery discharge current in Ship Mode                | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}, \text{ V}_{\text{IN}} = 0 \text{ V}, \text{ Ship Mode}$                                                                                                                             |       | 2                                            | 150  | nA   |

| POWER-PATH                | MANAGEMENT and INPUT                                  | CURRENT LIMIT                                                                                                                                                                                                                                      |       |                                              | *    |      |

| V <sub>DO(IN-PMID)</sub>  | $V_{IN} - V_{(PMID)}$                                 | V <sub>IN</sub> = 5 V, I <sub>IN</sub> = 300 mA                                                                                                                                                                                                    |       | 125                                          | 170  | mV   |

| V <sub>DO(BAT-PMID)</sub> | $V_{(BAT)} - V_{(PMID)}$                              | V <sub>IN</sub> = 0 V, V <sub>(BAT)</sub> > 3 V, I <sub>ff</sub> = 400 mA                                                                                                                                                                          |       | 120                                          | 160  | mV   |

| V <sub>(BSUP1)</sub>      | Enter supplement mode threshold                       | $V_{(BAT)} > V_{(BUVLO)}$                                                                                                                                                                                                                          |       | $V_{(PMID)} < V_{(BAT)} - 25 $ mV            |      | ٧    |

| V <sub>(BSUP2)</sub>      | Exit supplement mode threshold                        | $V_{(BAT)} > V_{(BUVLO)}$                                                                                                                                                                                                                          |       | $V_{(PMID)} < V_{(BAT)} - 5mV$               |      | V    |

| I <sub>(BAT_OCP)</sub>    | Current Limit, Discharge<br>Mode                      | $V_{(BAT)} > V_{(BUVLO)}$                                                                                                                                                                                                                          | 0.85  | 1.15                                         | 1.35 | Α    |

|                           | Input Current Limit                                   | Programmable Range, 50-mA steps                                                                                                                                                                                                                    | 50    |                                              | 400  | mA   |

| I <sub>(ILIM)</sub>       | Maximum Input Current using ILIM                      |                                                                                                                                                                                                                                                    |       | K <sub>(ILIM)</sub> /<br>R <sub>(ILIM)</sub> |      |      |

| -(ILIM)                   | I <sub>ILIM</sub> accuracy I <sub>ILIM</sub>          | 50 mA to 100 mA                                                                                                                                                                                                                                    | -12%  | , ,                                          | 12%  |      |

|                           | accuracy                                              | 100 mA to 400 mA                                                                                                                                                                                                                                   | -5%   |                                              | 5%   |      |

|                           | Maximum input current                                 | I <sub>(ILIM)</sub> = 50 mA to 100 mA                                                                                                                                                                                                              | 175   | 200                                          | 225  | ΑΩ   |

| K <sub>(ILIM)</sub>       | factor                                                | I <sub>(ILIM)</sub> = 100 mA to 400 mA                                                                                                                                                                                                             | 190   | 200                                          | 210  | ΑΩ   |

| V <sub>IN(DPM)</sub>      | Input voltage threshold when input current is reduced | Programmable Range using $V_{\text{IN(DPM)}}$ Registers. Can be disabled using $V_{\text{IN(DPM\_ON)}}$                                                                                                                                            | 4.2   |                                              | 4.9  | V    |

| - IN(DFW)                 | V <sub>IN_DPM</sub> threshold accuracy                |                                                                                                                                                                                                                                                    | -3%   |                                              | 3%   |      |

| BATTERY CHA               | ARGER                                                 | <u> </u>                                                                                                                                                                                                                                           |       |                                              |      |      |

| V <sub>D(PPM)</sub>       | PMID voltage threshold when charge current is reduced | Above V <sub>(BATREG)</sub>                                                                                                                                                                                                                        |       | 0.2                                          |      | V    |

| R <sub>ON(BAT-PMID)</sub> | Internal Battery Charger<br>MOSFET on-resistance      | Measured from BAT to PMID, V <sub>(BAT)</sub> = 4.35 V, High-Z mode                                                                                                                                                                                |       | 300                                          | 400  | mΩ   |

|                           | Charge Voltage                                        | Operating in voltage regulation, Programmable Range, 10-mV steps                                                                                                                                                                                   | 3.6   |                                              | 4.65 | V    |

| $V_{(BATREG)}$            | Voltage Regulation                                    | T <sub>J</sub> = 25°C                                                                                                                                                                                                                              | -0.5% |                                              | 0.5% |      |

|                           | Accuracy                                              | T <sub>J</sub> = 0°C to 85°C                                                                                                                                                                                                                       | -0.5% |                                              | 0.5% |      |

## **Electrical Characteristics (continued)**

Circuit of Figure 1,  $V_{(UVLO)} < V_{IN} < V_{(OVP)}$  and  $V_{IN} > V_{(BAT)} + V_{(SLP)}$ ,  $T_J = -40^{\circ}\text{C}$  to 85°C and  $T_J = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

| P                                  | PARAMETERS                                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN                                                                       | TYP                         | MAX  | UNIT                 |

|------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------|------|----------------------|

|                                    | Fast Charge Current<br>Range                     | V <sub>(BATUVLO)</sub> < V <sub>(BAT)</sub> < V <sub>(BATREG)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                         |                             | 300  | mA                   |

| I <sub>(CHARGE)</sub>              | Fast Charge Current using ISET                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           | $K_{(ISET)}$ / $R_{(ISET)}$ |      | А                    |

|                                    | Fast Charge Current<br>Accuracy                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -5%                                                                       |                             | 5%   |                      |

| K <sub>(ISET)</sub>                | Fast Charge Current Factor                       | 5 mA > I <sub>(CHARGE)</sub> > 300 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 190                                                                       | 200                         | 210  | ΑΩ                   |

|                                    | Termination charge current                       | Termination current programmable range over I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.5                                                                       |                             | 37   | mA                   |

|                                    |                                                  | $I_{(CHARGE)}$ < 300 mA, $R_{(ITERM)}$ = 15 k $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           | 5                           |      | % of I <sub>SE</sub> |

| I <sub>(TERM)</sub>                | Termination Current using                        | $I_{(CHARGE)}$ < 300 mA, $R_{(ITERM)}$ = 4.99 k $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           | 10                          |      | % of I <sub>SE</sub> |

| (ILIXIVI)                          | IPRETERM                                         | $I_{(CHARGE)}$ < 300 mA, $R_{(ITERM)}$ = 1.65 k $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           | 15                          |      | % of I <sub>SI</sub> |

|                                    |                                                  | $I_{(CHARGE)}$ < 300 mA, $R_{(ITERM)}$ = 549 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           | 20                          |      | % of I <sub>SI</sub> |

|                                    | Accuracy                                         | I <sub>(TERM)</sub> > 4 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  K <sub>(ISET)</sub> / R <sub>(ISET)</sub> -5%  190 200  0.5  5  10  15 | 10%                         |      |                      |

| t <sub>DGL(TERM)</sub>             | TERM deglitch time                               | Both rising and falling, 2-mV over-drive, t <sub>RISE</sub> , t <sub>FALL</sub> = 100 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           | 64                          |      | ms                   |

| 502(121111)                        | Pre-charge current                               | Pre-charge current programmable range over I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.5                                                                       |                             | 37   | mA                   |

| I <sub>(PRE_CHARGE)</sub>          | Pre-charge Current using I <sub>PRETERM</sub>    | The strange service programmer and great serv |                                                                           | I <sub>(TERM)</sub>         |      | А                    |