# Application Brief How to Approach a Power-Supply Design – Part 4

Markus Zehendner

This application brief introduces the single-ended primary inductance converter (SEPIC) and Zeta converter. Both topologies can be a cost-effective alternative to a buck-boost converter in the power range up to 25 W.

## SEPICs

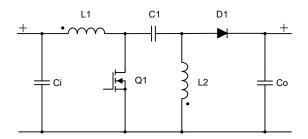

The SEPIC topology can step up and step down the input voltage. The energy transfers from the input to the output when switch Q1 is not conducting. Figure 1 shows the schematic of a nonsynchronous SEPIC.

## Figure 1. Nonsynchronous SEPIC Schematic

Equation 1 calculates the duty cycle in continuous conduction mode (CCM) as:

$$D = \frac{V_{OUT} + V_f}{V_{OUT} + V_f + V_{IN}}$$

(1)

Equation 2 calculates the maximum metal-oxide semiconductor field-effect transistor (MOSFET) stress as:

$$V_{Q1} = V_{IN} + V_{OUT} + V_f + \frac{V_{C1, ripple}}{2}$$

(2)

Equation 3 gives the maximum diode stress as:

$$V_{D1} = V_{IN} + V_{OUT} + \frac{V_{C1, ripple}}{2}$$

(3)

where

- V<sub>IN</sub> is the input voltage

- V<sub>OUT</sub> is the output voltage

- V<sub>f</sub> is the diode forward voltage

- V<sub>C1,ripple</sub> is the voltage ripple across the coupling capacitor

The inductor-capacitor (LC) filter L1 and Ci is pointing to the input of the SEPIC. This leads to a smaller ripple at the input due to the continuous current flow. At the output, the ripple is bigger because there is a pulsed output current.

A nonsynchronous SEPIC costs less than a buck-boost topology because only one gate driver (compared to two for a two-switch buck-boost converter) and only two semiconductor components (instead of four) is needed. Another advantage of a SEPIC over a buck-boost topology is the better electromagnetic interference (EMI)

1

behavior when both converters are operating in buck mode as a result of the continuous input current of the SEPIC.

A SEPIC is easily built by using a boost controller because MOSFET Q1 needs to be driven on the low side.

The right half-plane zero (RHPZ) is the limiting factor for the achievable regulation bandwidth of a SEPIC. The maximum bandwidth is roughly one-fifth the RHPZ frequency. Equation 4 calculates an estimation of the single RHPZ frequency of the transfer function of the SEPIC:

$$f_{\rm RHPZ} = \frac{V_{\rm OUT} \times (1-D)^2}{2 \times \pi \times D^2 \times L_2 \times I_{\rm OUT}}$$

(4)

Solving Equation 5 for s has either one or two more RHPZs as a result:

$$1 - s \times \frac{C_1 \times (L_1 + L_2) \times \frac{V_{\text{OUT}}}{I_{\text{OUT}}}}{L_1} \times \frac{(1 - D)^2}{D^2} + s^2 \times \frac{L_2 \times C_1}{D} = 0$$

(5)

where

- V<sub>OUT</sub> is the output voltage

- D is the duty cycle

- I<sub>OUT</sub> is the output current

- L<sub>1</sub> is the inductance of inductor L1

- L<sub>2</sub> is the inductance of inductor L2

- C<sub>1</sub> is the capacitance of coupling capacitor C1 and s is the complex frequency variable

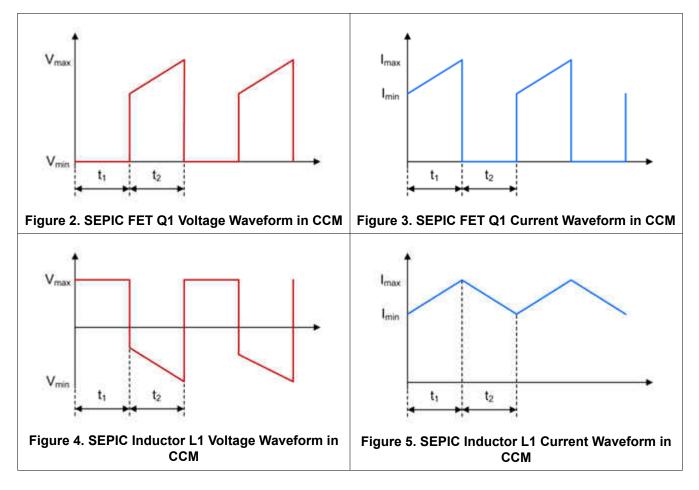

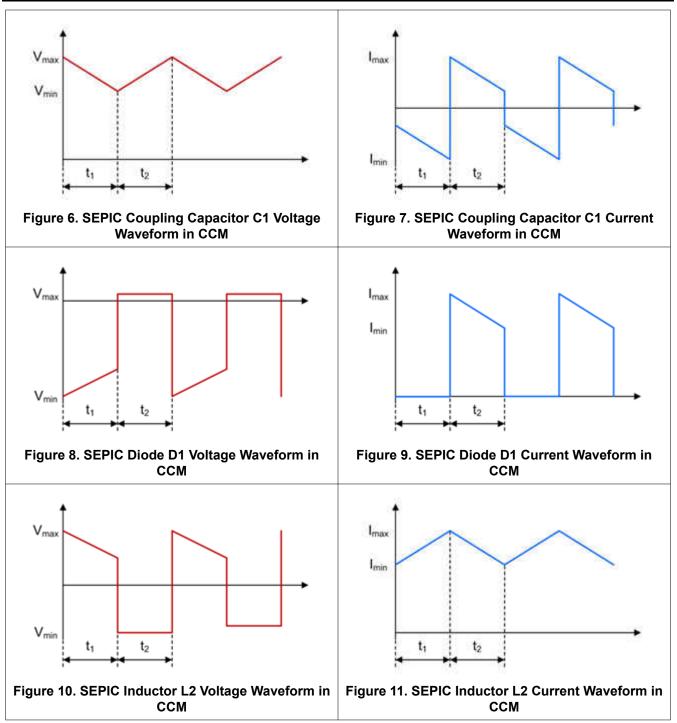

Figure 2 through Figure 11 show voltage and current waveforms in CCM for FET Q1, inductor L1, coupling capacitor C1, diode D1, and inductor L2 in a nonsynchronous SEPIC.

# Zeta Converters

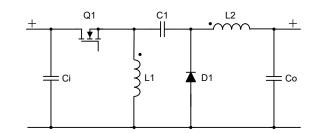

The Zeta topology can step up and step down the input voltage. The energy transfers from the input to the output when switch Q1 is conducting. Figure 12 shows the schematic of a nonsynchronous Zeta converter.

#### Figure 12. Nonsynchronous Zeta Converter Schematic

Equation 6 calculates the duty cycle in CCM as:

$$D = \frac{V_{OUT} + V_f}{V_{OUT} + V_f + V_{IN}}$$

(6)

Equation 7 calculates the maximum MOSFET stress as:

$$V_{Q1} = V_{IN} + V_{OUT} + V_f + \frac{V_{C1, ripple}}{2}$$

(7)

Equation 8 gives the maximum diode stress as:

$$V_{D1} = V_{IN} + V_{OUT} + \frac{V_{C1, ripple}}{2}$$

(8)

where

- V<sub>IN</sub> is the input voltage

- V<sub>OUT</sub> is the output voltage

- V<sub>f</sub> is the diode forward voltage

- V<sub>C1,ripple</sub> is the voltage ripple across the coupling capacitor

The LC filter L2 and Co in a Zeta converter is pointing to the output. As a result, the output ripple is smaller compared to the input ripple, because the output current is continuous and the input current is pulsed. Using the Zeta topology for very sensitive loads is recommended, where a SEPIC or buck-boost converter does not fit due to their higher output ripple. The Zeta topology has the same advantage regarding cost and component count over the buck-boost converter as the SEPIC.

A Zeta converter can be built by using a buck controller or converter; a P-channel MOSFET or high-side MOSFET driver is needed.

The Zeta converter does not have a RHPZ, because the controller can immediately react to changes at the output. Therefore, higher bandwidths with a Zeta converter can be achieved than with a SEPIC or buck-boost converter while using less output capacitance.

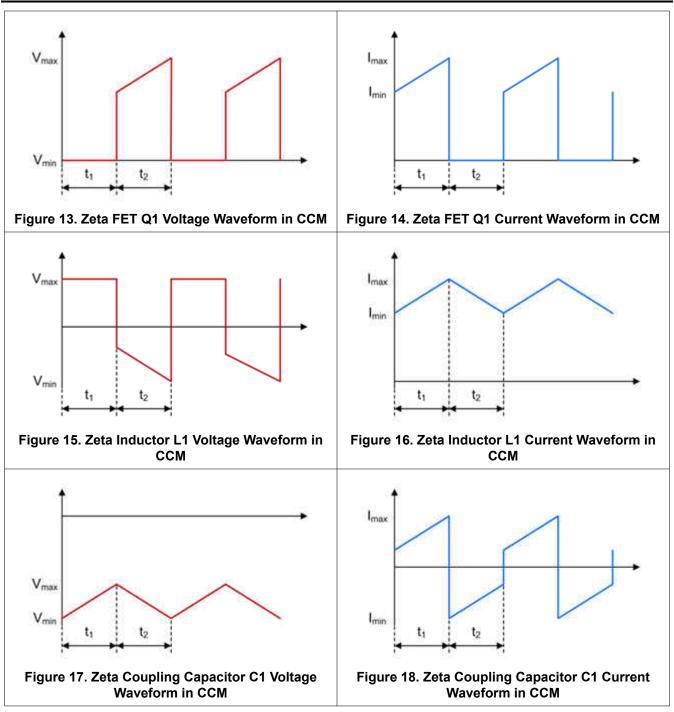

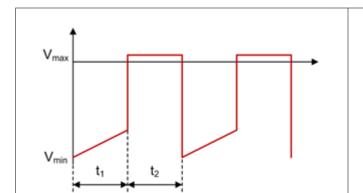

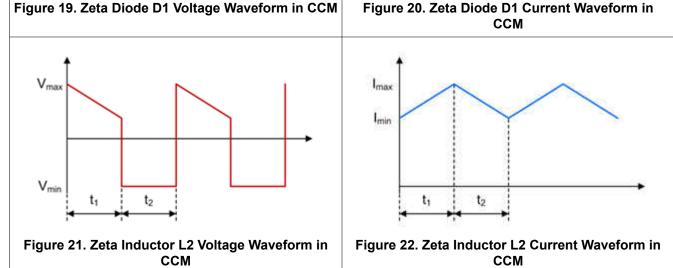

Figure 13 through Figure 22 show voltage and current waveforms in CCM for FET Q1, inductor L1, coupling capacitor C1, diode D1, and inductor L2 in a nonsynchronous Zeta converter.

Imax

Imin

t1

t<sub>2</sub>

For both topologies, using coupled inductors instead of two separate inductors has two advantages. The first advantage is that only half the inductance is required for a similar current ripple (compared to a two-inductor design) because of ripple cancellation by coupling the windings. The second advantage is that the resonance in the transfer function caused by the two inductors and the coupling capacitor can be removed. Dampen this resonance with a resistor-capacitor (RC) network in parallel with coupling capacitor C1, if needed.

One drawback to using coupled inductors is that the same inductance value for both inductors must be used. Another limitation is typically their current rating. Single inductors can sometimes be needed for applications with high output currents.

It is possible to configure both topologies as a converter with synchronous rectification. But if this method is used, you must AC-couple the high-side gate-drive signal, because many controllers require that you connect them to the switch node. Both topologies have two switch nodes each, so take care to avoid negative voltagerating violations on the switch pin. Two examples with a synchronous SEPIC and a synchronous Zeta converter are the 12V@5A Synchronous SEPIC Converter Reference Design and the 40W Synchronous Zeta Converter with Two Inductors Reference Design, respectively.

## **Additional Resources**

- Watch these TI training videos:

- Topology Tutorial: What is a SEPIC?

- Topology Tutorial: What is a Zeta Converter?

- Read these Analog Applications Journal articles:

- Benefits of a coupled-inductor SEPIC converter

- Designing DC/DC converters based on Zeta topology

- Design your power stage with Power Stage Designer.

- Download the Power Topologies Handbook and Power Topologies Quick Reference Guide.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated