## Technical White Paper Enabling Low Power Embedded Systems With AM62x Processors

# **TEXAS INSTRUMENTS**

Kazunobu Shin, Systems & Architecture, Member Group of Technical Staff Venkateswar Kowkutla, Systems & Architecture, Senior Member of Technical Staff

## **Table of Contents**

| 1 Introduction                                    | 2 |

|---------------------------------------------------|---|

| 2 AM62x Power Management Features                 |   |

| 2.1 Low Power Modes                               | 3 |

| 2.2 Active Power Management                       |   |

| 2.3 Power Supply Simplification                   | 4 |

| 2.4 Power Solutions                               |   |

| 3 Low Power Processor Architecture Considerations | 6 |

| 4 AM62x Power Consumption                         |   |

| 5 Power Estimation Tool                           |   |

| 6 Conclusion                                      |   |

|                                                   |   |

## Trademarks

All trademarks are the property of their respective owners.

1

## **1** Introduction

The increasing popularity of embedded systems in a wide range of applications pushes for a higher level of integration onto a single SoC. This high level of integration leads to higher power dissipation, increased thermal system cost, degraded performance, and reduced battery life. To overcome these challenges, SoCs should be defined, architected, and designed in the context of their usage in the targeted embedded systems. Since every application is different, picking the correct operating settings for the SoC will achieve optimal performance and power. This paper presents novel features and techniques developed on the AM62x processors - a next-generation Sitara MPU device from Texas Instruments.

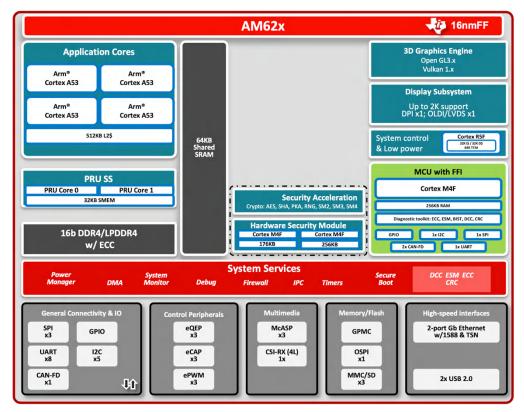

AM62x processors feature a high-performance Quad-core Cortex A53 with 64-bit architecture, a powerful 3D Graphics Engine, an integrated M4F MCU Channel for general purpose usage or safety with full freedomfrom interface (FFI) from the application domain, a Dual-core M4F for Foundational and Automotive/Industrial Security, a dedicated R5F core for device resources and low power management. The modular architecture of this device delivers performance with support for several low power modes without sacrificing critical system resources, such as connectivity, power, security, safety, and cost. Figure 1 shows a high-level AM62x processor block diagram.

Figure 1-1. Block Diagram of the Sitara<sup>™</sup> AM62x Processors

## 2 AM62x Power Management Features

The AM62 processor uses several essential techniques to reduce active and static power consumption. Table 2-1 shows the AM62x power management features and the benefits.

| Key Features                | AM62x Power Management                                                                  | Benefits                                                                                                                    |

|-----------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Low Power Modes             | DeepSleep, MCU Only, Standby, Partial I/O                                               | Longer battery operation lifetime                                                                                           |

| Active Power Management     | Low bus clock frequency operation at 125 MHz (OPP low)                                  | Low active power consumption for low activity use cases                                                                     |

|                             | Dynamic frequency scaling (DFS)                                                         | Thermal management                                                                                                          |

| Power Supply Simplification | Up to 1.25 GHz A53 at 0.75 V<br>Up to 1.4 GHz A53 at 0.85 V                             | Differentiated low power capability with 0.75-V<br>core power supply<br>Higher performance with 0.75-V core power<br>supply |

|                             | Single core power supply<br>Simpler power domains                                       | Lower cost power solution and less complicated software control for power management                                        |

|                             | Simple power sequencing with integrated LDO enabling a low-cost discrete power solution | Easier to optimize a power solution for the<br>overall system<br>Low-cost power solution                                    |

| Companion PMIC              | New low cost PMIC                                                                       | Low cost PMIC optimized for AM62x                                                                                           |

| Table 2-1. AM62 | k Power Managemen | t Features |

|-----------------|-------------------|------------|

|-----------------|-------------------|------------|

#### 2.1 Low Power Modes

The AM62x processor supports optimized low power modes with varying levels of power dissipation: Partial I/O mode to Deepsleep mode to Standby mode (sub mW to a few mW). Table 2-2 shows a high-level description of various low-power modes supported on AM62x processors.

| Low Power Modes | Wakeup Sources                                                                       | Application State and Use Case                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Partial I/O     | CANUART I/O Bank pins                                                                | The entire SoC is OFF except I/O pins in CANUART I/O bank to maintain I/O wakeup capability from CANUART I/O Bank I/O pins.                                                                                                                                                                                                                                                                             |

| DeepSleep       | GP Timers, RTC Timer, UART, I2C,<br>MCU GPI00, I/O Daisy Chain, USB<br>wakeup events | Core domain register information will be lost. On-chip peripheral register (context) information of core domain needs to be saved by application to DDR before entering this mode. DDR is in self-refresh. Boot ROM executes and branches to peripheral context restore for wakeup, followed by system resume. This mode is primarily used for Suspend to RAM for battery lifetime or backup operation. |

| MCU Only        | DeepSleep wakeup events, Interrupt<br>evens supported in MCU channel                 | The MCU subsystem runs at the MCU PLL clock. The rest of the SoC status is the same as DeepSleep. DDR is in self-refresh. MCU can run applications with MCU domain peripherals while in this low power mode.                                                                                                                                                                                            |

| Standby         | Any SoC interrupt event                                                              | On-chip contents are fully preserved. Any SoC interrupt event<br>can cause a wakeup event from this low power mode. A53<br>and MCU M4F are in WFI or power down. DDR memory is in<br>self-refresh. The device can run low-level processing with non-<br>Wakeup/MCU domain peripherals and support wakeup from thos<br>peripherals.                                                                      |

#### Table 2-2. AM62x Low Power Modes

**Partial I/O**: I/O pins and small logic in the CANUART I/O Bank are active, and the rest of the SoC is turned off. The user can use the I/O pins to aggregate multiple I/O wakeup events and toggle the PMIC\_LPM\_EN pin to enable PMIC or discrete power solution when an I/O wakeup event is triggered. The information on the I/O wakeup event is logged in the MMR in the CANUART I/O bank and helps the software to distinguish between cold boot and wakeup to respond to the wakeup event faster. This mode can be used to support CAN wakeup or Ethernet Wakeup.

**DeepSleep**: DeepSleep mode enables lower power consumption than Standby or MCU-Only. DeepSleep mode is typically used during inactivity when the user requires very low power while waiting for an event that requires processing or higher performance. DeepSleep is the lowest power mode which still includes DDR in self-refresh, so wakeup events do not require a full cold boot, significantly reducing wakeup latencies. The lowest power in this mode can be achieved by disabling both oscillators when the RTC or other timer function is not required.

**MCU Only**: MCU-Only can be used for low power use cases that require low-level processing during a low power mode. The status of the SoC is the same as DeepSleep, except the MCU channel is fully active to run applications with MCU channel resources and peripherals. Any interrupt event in the MCU channel can initiate a wakeup from MCU-Only, and the wakeup events supported in DeepSleep can also trigger wakeup from MCU-Only.

**Standby:**The device can be placed in Standby mode to reduce power consumption during low activity levels. This first level of power management allows you to maintain the device context for fast resume times. Standby state results in lower power consumption than Active mode but require the user to save the switched-off power domain context to On-Chip Memory or DDR and restore the contexts to resume properly upon wakeup.

#### 2.2 Active Power Management

Dynamic Frequency Scaling (DFS) is a power management technique that dynamically scales the operating frequency across device Operating Performance Points (OPP). An OPP is a voltage/frequency pair that defines a specific power state. The software controls the clock frequency for each OPP to adjust the performance and power to the optimum point. The device supports DFS for Cortex-A53 only.

The AM62x processor supports lower bus frequency operation as OPP Low. The OPP Low must be configured at boot time. In OPP Low, the main CBASS clock frequency is reduced in half to lower active power consumption with reduced performance. The performance of some peripheral modules is limited or not available in this operating condition.

#### 2.3 Power Supply Simplification

When it comes to power optimization, it is imperative to consider how the SoC will be used in a given system alongside total system power optimization and not just the SoC power - a key part of the holistic approach. Minimizing the number of dedicated power rails needed by SoC not only simplifies the power-supply solution. AM62x device is architected with a shared core vdd along with flexibility to scale voltage level to meet the demands of wide range of applications.

Selecting the right core voltage for a given application results in an optimized system power. The AM62x device is able to demonstrate that by scaling core power supply from 0.8 V, the standard core voltage for the process node, to 0.75 V, there was a total of 15% reduction in active power. On the other hand, where performance is a key care about, scaling the core power supply from 0.8 V to 0.85 V resulted in 15% increase in device performance.

The AM62x processor supports simple core power supply without DVFS/AVS and enables 100K POH with the fixed core voltage for entire SoC with full performance entitlement.

#### 2.4 Power Solutions

By leveraging the simplified power requirements mentioned above, TI developed two types of low-cost power solutions for AM62x processors. The TPS65219 is the PMIC specifically designed for AM62x processors and fully leverages the simplified power requirements to provide the lowest cost PMIC for AM62x processors. A discrete power solution can provide the scalability and flexibility to adjust the power solution to be optimized for overall system requirements or meet different current capacities or the number of power supplies required by customers. Table 2-3 compares the two low-cost power solutions designed for AM62x processors.

|              | Discrete Power                                     | Single PMIC Solution |

|--------------|----------------------------------------------------|----------------------|

| Availability | Now: (TPS6282x, TPS745xx,<br>TLV7103318, TLV75518) | TPS65219             |

#### Table 2-3. AM62x Power Solutions

|                              | Discrete Power                                                                          | Single PMIC Solution                                                                     |

|------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Power Features               | Leverages AM62x analog integration<br>for power supply simplification                   | 2.7 to 5.5-V input supply                                                                |

|                              | Supports multiple input supplies: 3.3 V, 5 V                                            | Single PMIC solution developed specifically for AM62x/AM64x processors                   |

|                              | Scalability to meet different custom requirements for current capacity, and lowest cost | Automotive support                                                                       |

| Power Management Features    | N/A                                                                                     | Programmable power sequencing and default voltages                                       |

| Functional Safety            | Customer driven implementation<br>leveraging AM62x features                             | N/A                                                                                      |

| Power Solution Size Estimate | Scalable based on system requirements                                                   | 81.54 mm2 with 4 x 4 mm2 QFN, 0.4-mm pitch<br>69.66 mm2 with 5 x 5 mm2 QFN, 0.5-mm pitch |

| AM62x EVM                    | AM62x SK                                                                                | AM62Q SK                                                                                 |

Table 2-3. AM62x Power Solutions (continued)

## **3 Low Power Processor Architecture Considerations**

Hardware and software co-design is extremely critical to power and latency optimization. Figuring out the right hardware-software boundary, identifying which function is in hardware and which function is in software earlier on during the definition is key. Simplifying software sequences for low power mode entry and exit modes by eliminating save and restore of configuration settings supported by innovative new features such as USB and DDR Reset Isolation and Retention schemes. Optimizing IO states (pull-ups and pull-downs) based on low power use-case and ability to put IOs in retention enhances the system robustness and reliability.

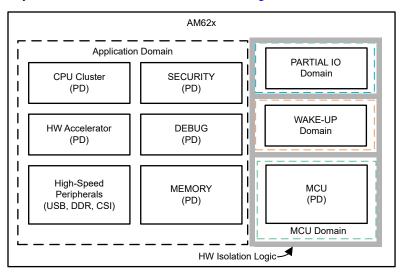

Early in the development phase, several different HW/SW partitions were evaluated, to determine best implementation to meet overall system use-cases and goals (cost, performance, power, and latency). The AM62x processor is mainly divided into 4 domains, as shown in Figure 3-1.

Figure 3-1. SoC Partition

**Application domain** comprising of high-performance CPUs, HW accelerators, and high-speed peripherals. This domain is further divided into various sub-systems with internal power switches. Depending on the system use-cases, these sub-systems can be completely powered-down using the internal power-domain switches. For example: un-used CPU cores in a cluster, HW accelerators (graphics, display), and so forth. In addition, during DeepSleep and MCU only low power modes, application domain is put to lowest power mode through internal subsystem power gating.

**MCU domain** comprising of real-time CPUs and peripherals. This domain can be configured to operate completely independent from the application domain: a key differentiating feature in several automotive, industrial, and battery-operated applications. During DeepSleep mode, the MCU domain can be powered-down through internal power switches.

**Wake-up domain** comprising of Power Management CPU and system components such as clocks, resets, power, and wake-up. This domain is responsible for device boot-up, resource configuration and management, and low power management. Hardware isolation is built around this domain to ensure that clear separation between application and MCU domains. By carefully partitioning the responsibilities between hardware and software functions, Sitara MPU devices achieve simpler and robust low power mode entry and exit sequences. In addition, to improve low power mode entry/exit latencies, Sitara MPU devices developed innovative new features such as USB and DDR reset isolation and retention schemes to avoid complex software sequences that require peripheral configuration save and restore.

## 4 AM62x Power Consumption

Table 4-1 shows power consumption at various SoC states and the scalability of power and performance. By leveraging low power mode implementation and techniques, AM62 processors achieve less than 500-mW power consumption for a single A53 core running at 1 GHz. The power consumption is almost half of the power consumption achieved by similar low power and low-cost processors in previous generations. AM62x processor power can still be less than 1 W when Quad A53 cores run a stressful application on all four cores at 1.4 GHz.

|                                   |                       |                            |                            | Cortex A53 at 1.4 GHz<br>0.85-V VDD_CORE |                            |                            |

|-----------------------------------|-----------------------|----------------------------|----------------------------|------------------------------------------|----------------------------|----------------------------|

|                                   | ldle<br>1xA53<br>(mW) | Dhrystone<br>1xA53<br>(mW) | Dhrystone<br>4xA53<br>(mW) | 1xA53                                    | Dhrystone<br>1xA53<br>(mW) | Dhrystone<br>4xA53<br>(mW) |

| VDD_CORE                          | 343                   | 395                        | 570                        | 466                                      | 565                        | 880                        |

| VDDR_CORE                         | 3                     | 4                          | 7                          | 2                                        | 4                          | 8                          |

| VDDS_DDR                          | 45                    | 45                         | 45                         | 45                                       | 45                         | 45                         |

| Total (without I/O<br>and Analog) | 391                   | 444                        | 622                        | 513                                      | 614                        | 933                        |

#### Table 4-1. AM62x Power Consumption

7

## **5** Power Estimation Tool

TI provides the Power Estimation Tool (PET) based on the processor power model created from measured and simulated data. Developers gain insight into the power consumption of AM62x processors for various application scenarios, electrical parameters, silicon process variations, and environmental conditions before they start designing hardware and software. The power estimations from the tool can be used for deciding the operating performance points of the AM62x processor, evaluating thermal design, or estimating the battery lifetime of the end products. The tool allows the developer to choose different operating conditions and processor configurations to make a trade-off between operating performance and power consumption with various power-saving techniques. This tool estimates power consumption during realistic operating modes and is not intended for power supply sizing.

|                         | Modi Flable fields<br>Static Flekts<br>Calculated Power Outputs |                                        |                |                      |                           |                 |

|-------------------------|-----------------------------------------------------------------|----------------------------------------|----------------|----------------------|---------------------------|-----------------|

| Operating Performance P | Salat (DPP)                                                     |                                        | Processor Core | Utilization (%)      |                           | 1               |

|                         | MPU A530/L/2/3 Frequency (MHz)                                  | 1250                                   |                | MPU-A530             | 100%                      |                 |

|                         | GPU Frequency (MHb)                                             | 500                                    |                | MPU-AS31             | 100%                      |                 |

|                         | MCU M4F Frequency (MHz)                                         | 500<br>400<br>333<br>313<br>313<br>400 |                | MPU-A532             | 100%                      |                 |

|                         | PRU-55 Frequency (MHz)                                          | 333                                    |                | MPU-A533             | 100%                      |                 |

|                         | HSM Frequency (MHz)                                             | 313                                    | 1              | GPU                  | 100%                      |                 |

|                         | RSF Frequency (MHz)                                             | 400                                    |                | <b>R</b> SF          | 100%                      |                 |

|                         | a final data data data data data data data da                   |                                        |                | MCU-M4F              | 100%                      |                 |

|                         |                                                                 |                                        |                | FRU-55               | 18                        |                 |

|                         |                                                                 |                                        |                | HSM                  | 100%                      |                 |

|                         |                                                                 |                                        |                | Security Accelerator | 100%                      |                 |

| VEMOSIO                 | Made                                                            | KO Utilization (%)                     |                | Peripherals          | Mode                      | Utilization (%) |

| ACU UART                | 1m 3p3+                                                         | 15                                     |                | DOR Type/Rate        | ddr# 533 16               |                 |

| VALUP LUART             | 112k_1p8+                                                       | 19                                     |                | DOR WR %             | 50%                       | -               |

| TRAIN LAURT             | Jplin 1phy                                                      | 15                                     |                | US82 Port 0          | device is                 | 39              |

| WCU SPL 0               | Stave 6.25 Mbaud 198v                                           | 99%                                    |                | US82 Port 1          | host is                   | 1               |

| ACU SPI 1               | Stave 2.083 Mbaud Ja8v                                          | 15                                     |                | WMC/500 (8b)         | ditr 200mbs               |                 |

| ACU SPL 2               | Stave 6.25 Mboud 1pdv                                           | 18                                     |                | MMC/501 (4b)         | dor_200mbs                | 9               |

| 0941                    | tessi_ddr_master_160_3p3v                                       | 99%                                    |                | MMC/502 (4b)         | str 50mbs                 | 99              |

| SPINC                   | 365 SD MH: 3p3V                                                 | 97%                                    |                | CLDI                 | ditabled                  | 100             |

| TUO                     | 2%   2048+1080+60 fps 24b   1p8V                                | 99%                                    |                | CSI                  | power_down_reset          | 6               |

| Ethernet (CPSW) Port 0  | 07                                                              | 09                                     |                |                      |                           |                 |

| thernet (CPSW) Port 1   | ignii 1000 JpJx                                                 | 993                                    |                |                      |                           |                 |

| WCASPO                  | 2Ch TX 48 ksps 24b JaBy                                         | 28                                     | 8              |                      |                           |                 |

| MoASP1                  | unused                                                          | 100%                                   |                |                      |                           |                 |

| PRUI-SS                 | 0 <sup>m</sup>                                                  | - 18                                   |                |                      |                           |                 |

| stimated Power          |                                                                 |                                        | -              | General              |                           |                 |

| stimated Power          | Burney Kurnels                                                  | Voltage (V)                            | Power (W)      | beneral              | Junction Temperature (PC) | -               |

|                         | Power Supply<br>VOD CORE                                        | 0.75                                   |                | 1                    | Power Estimation Mode     | 2               |

|                         | VODAA CORE                                                      | 0.85                                   |                |                      | Lowe countrol work        | M               |

|                         | V00A 1V8                                                        | 18                                     |                |                      |                           |                 |

|                         | V005 008                                                        | 11                                     | 0.             | 1                    |                           |                 |

|                         | SOC DVDD1V8                                                     | 1.1                                    |                | 2                    |                           |                 |

|                         | SOC DV003V3                                                     | 33                                     |                |                      |                           |                 |

|                         | SOC_DVD03V3                                                     | 3.5                                    | 127            |                      |                           |                 |

|                         | 106.8                                                           |                                        | 120            | 0                    |                           |                 |

species precision revent consingtion regences or event an parameters since process wheneves, environmental considering and solvent on the processor norms are Adual power consumption should be verified in the real system. The power estimates are meant for estimating power consumption during realistic operating modes; it is not interview power supply sking. The power estimates are preliminary and subject to change.

Figure 5-1. AM62x Power Estimation Tool

## 6 Conclusion

AM62 processors enable low-power embedded systems for edge devices with analytics or human-machine interface capability. Low power modes and low active power consumption allow a wide range of battery-operated applications and small form factor product design without heatsink or fans. Unique 0.75-V core voltage operation and power management features support adjusting performance and power for optimal for each customer application and help enable a simple and low-cost power solution by leveraging advanced analog integration.

9

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated