# System Power Savings Using Dynamic Voltage Scaling

Scot Lester

Texas Instruments

# What Is Dynamic Voltage Scaling?

- Dynamic voltage scaling, or DVS, is a method of reducing the average power consumption in embedded systems.

- This is accomplished by reducing the switching losses of the system by selectively reducing the frequency and voltage of the system.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Where Is DVS Used?

- DVS is typically used in battery-operated devices where power savings and battery run times are paramount.

- DVS is also used in large systems with multiple processors/DSPs where power savings is required for thermal reasons.

- DVS is implemented extensively in:

- Cell phones

- PDAs

- MP3 players

- Microcontroller-based battery-operated devices

**Minds in Motion**

# Underlying Concepts for Microprocessor/Controller/DSP Systems

- Today's embedded systems use high clock frequencies to boost processing power and system performance.

- The power dissipated by an embedded system is (typically) dominated by switching losses.

- The losses from switching are due to the capacitance of what is being switched. Examples of the capacitance being switched include trace impedance, load capacitance and the gates of MOSFETs used to implement logic in the processor.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Power Dissipation in a Capacitor

$$Power = \frac{1}{2}CV^2F$$

- V is the voltage the capacitor is charged to, F is the frequency that the voltage is switched across the capacitor.

- Power goes up by the square of the voltage.

- Power goes up linearly with switching frequency.

**Minds in Motion**

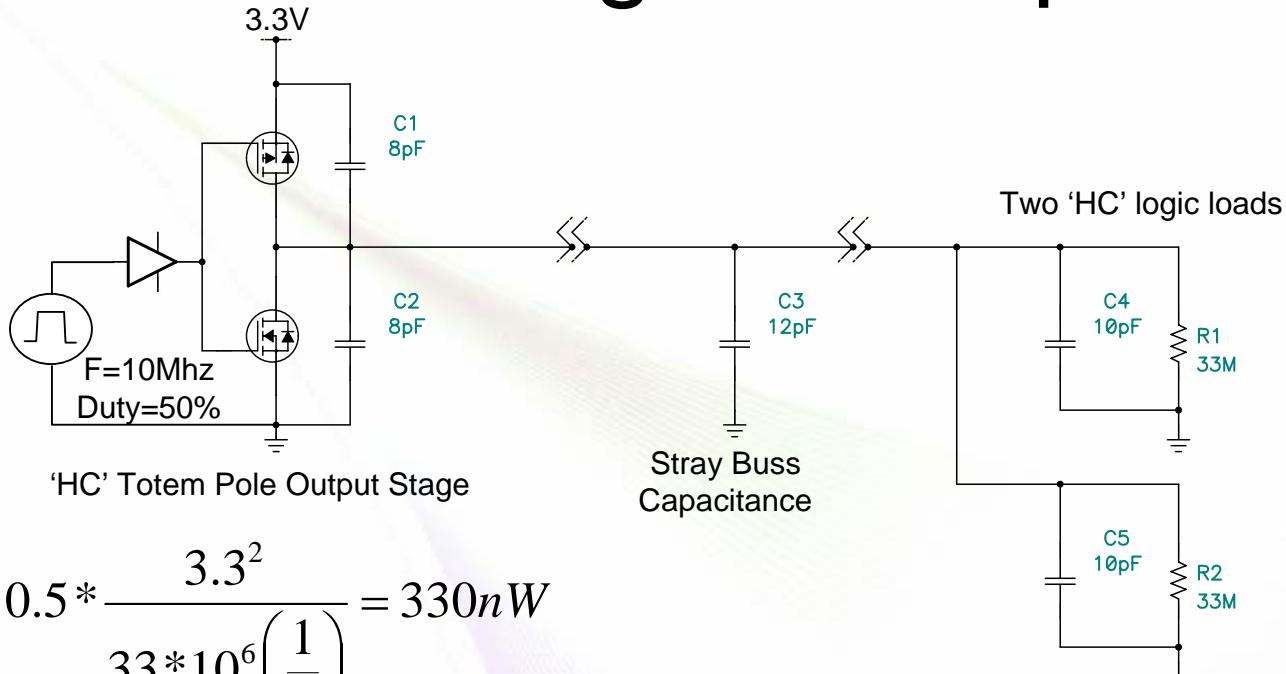

# Discreet Logic Example

$$P_r = D * \frac{V^2}{R} = 0.5 * \frac{3.3^2}{33 * 10^6 \left(\frac{1}{2}\right)} = 330\text{nW}$$

$$P_{sw} = \frac{1}{2} C V^2 F = \frac{1}{2} * (8\text{pF} + 8\text{pF} + 12\text{pF} + 10\text{pF} + 10\text{pF}) * 3.3^2 * 10^7 = 2.613\text{mW}$$

**Power loss due to switching capacitors is 7,900 times higher than powering the load resistance!**

**Minds in Motion**

# Reducing Voltage and Frequency Adds Up to Power Savings

- Can reduce the switching power by a factor of **2** by reducing the switching frequency to one-half.

- Can reduce the switching power by a factor of **4** by reducing the voltage by one-half.

- Can reduce the switching power by a factor of **8** by reducing the voltage by a factor of two and the frequency by one-half.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

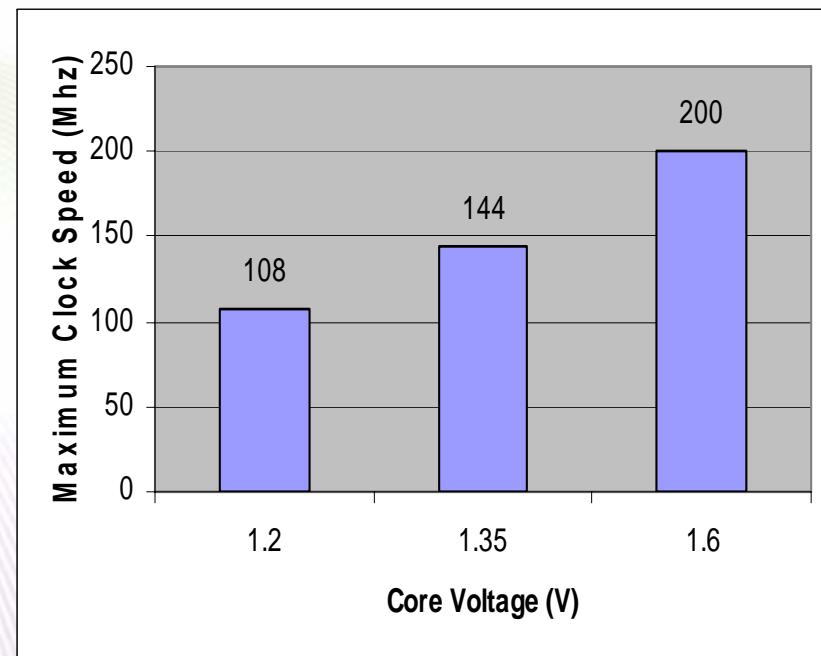

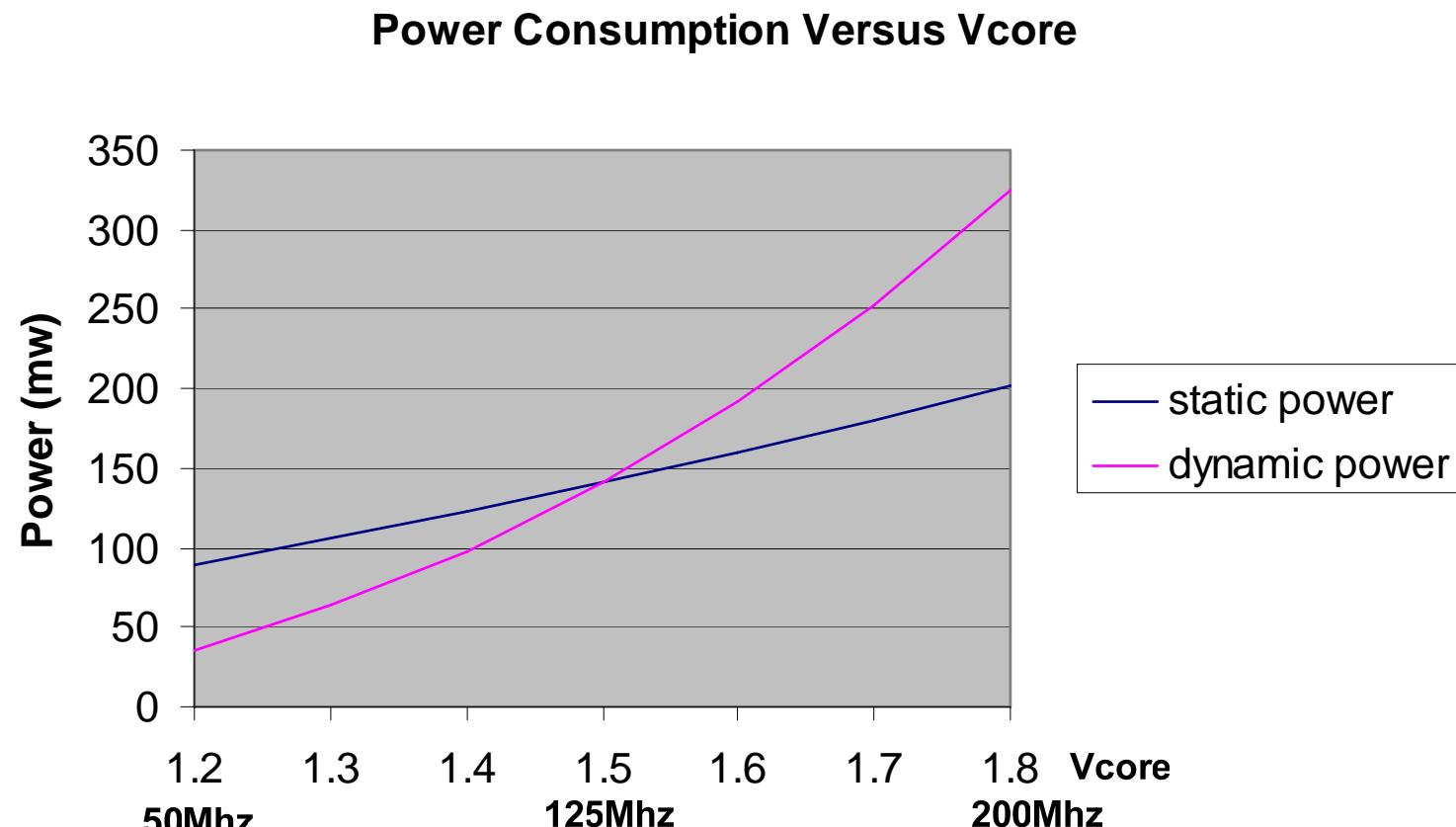

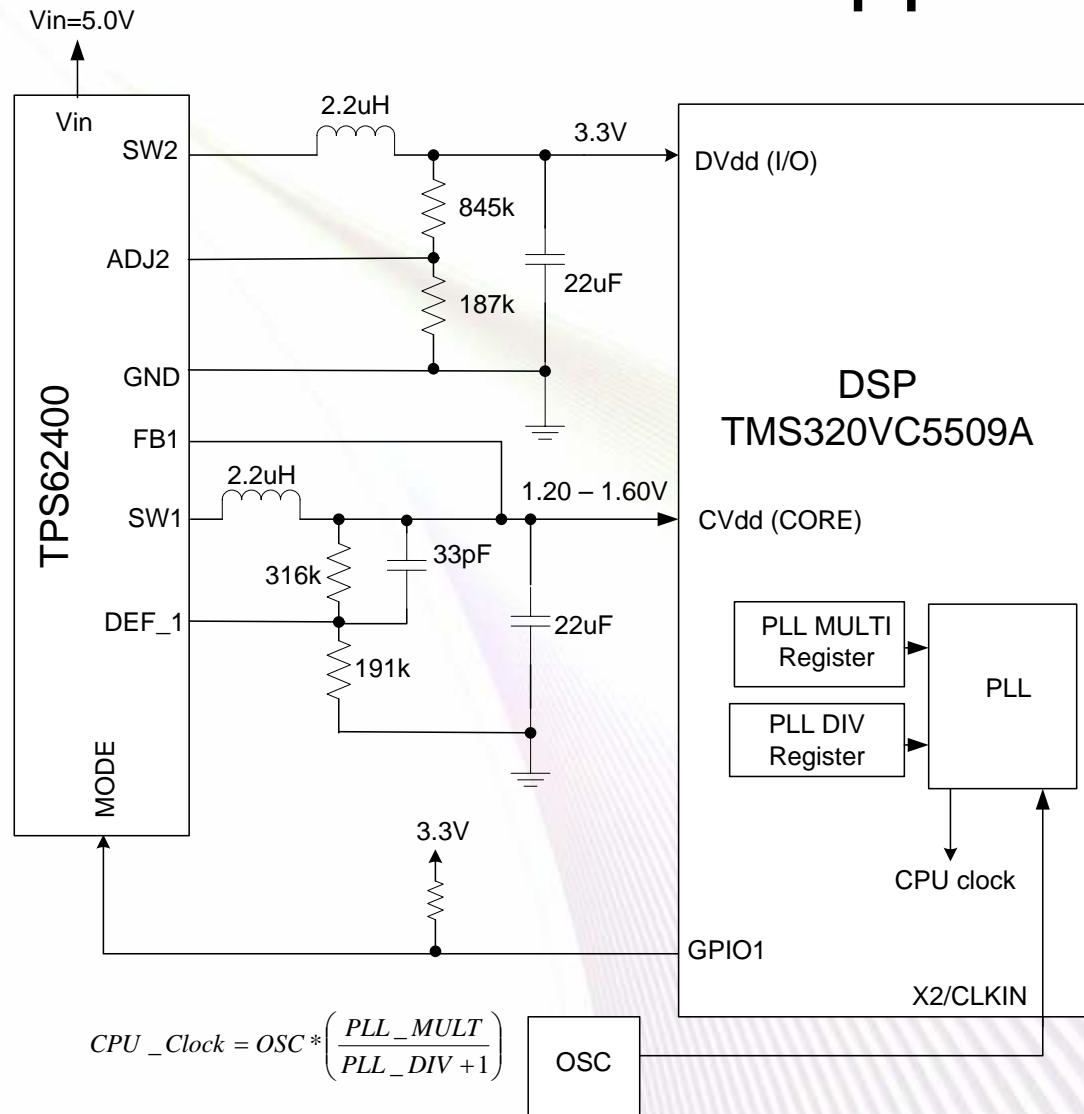

# A DSP Example Using DVS

- Look at the TMS320VC5509A, a more complex example. This is a dual voltage rail DSP IC.

- The I/O voltage is 3.3V.

- The core voltage is between 1.2V and 1.6V.

- The maximum processor clock that can be supported is related to the core voltage.

- As in previous slides, the current consumption will go up as the core voltage goes up due to switching losses.

**Minds in Motion**

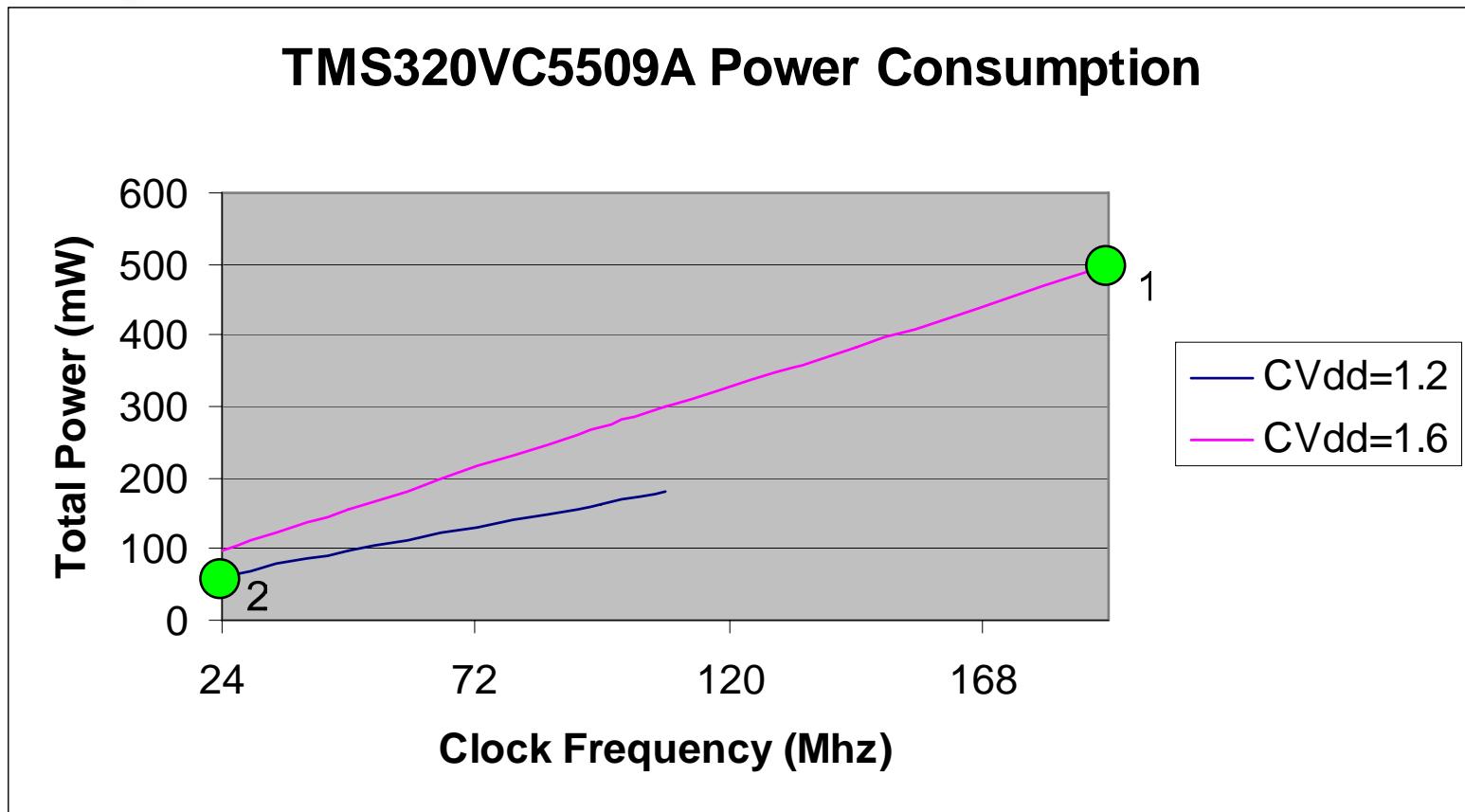

# Digital Signal Processor Example

Point 1,  $V_{core}=1.6$ ,  $F=192\text{Mhz}$ , Power=500mW

Point 2,  $V_{core}=1.2$ ,  $F=24\text{Mhz}$ , Power=50mW

**Minds in Motion**

# Static Losses: Sidebar

- The TMS320VC5509A has very low static losses. What effect would higher static losses have?

- Static losses do not change with the frequency of operation.

- Excluding any loads, static losses are mostly due to leakage currents in transistors, which are dependent on the geometry of the silicon used to fabricate the transistors.

- The amount of leakage current is mostly linear with the voltage applied (Vcc). Looks like a resistor.

Minds in Motion

Technology for Innovators™

TEXAS INSTRUMENTS

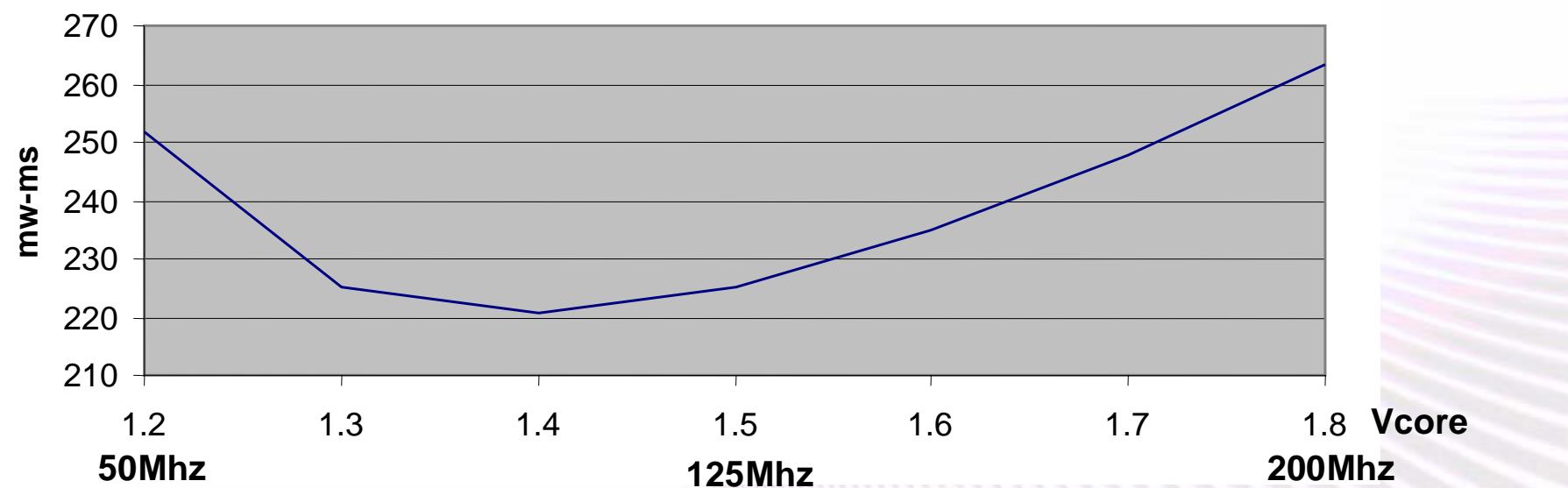

# Lower Voltage Is Not Always the Lowest Power Operating Point

- Need to take into account static losses to find lowest operating power point.

- Need to look at how long the required software process will take to execute (number of clock cycles).

- At lower clock frequencies there will be lower dynamic losses but the amount of time to perform the operation is longer and static losses are incurred the entire time.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Static and Dynamic Power Loss

Minds in Motion

Technology for Innovators™

TEXAS INSTRUMENTS

# Power to Perform a Fixed-Length Process

**Power Time Product to Perform 1 Million Clock Cycle Process**

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

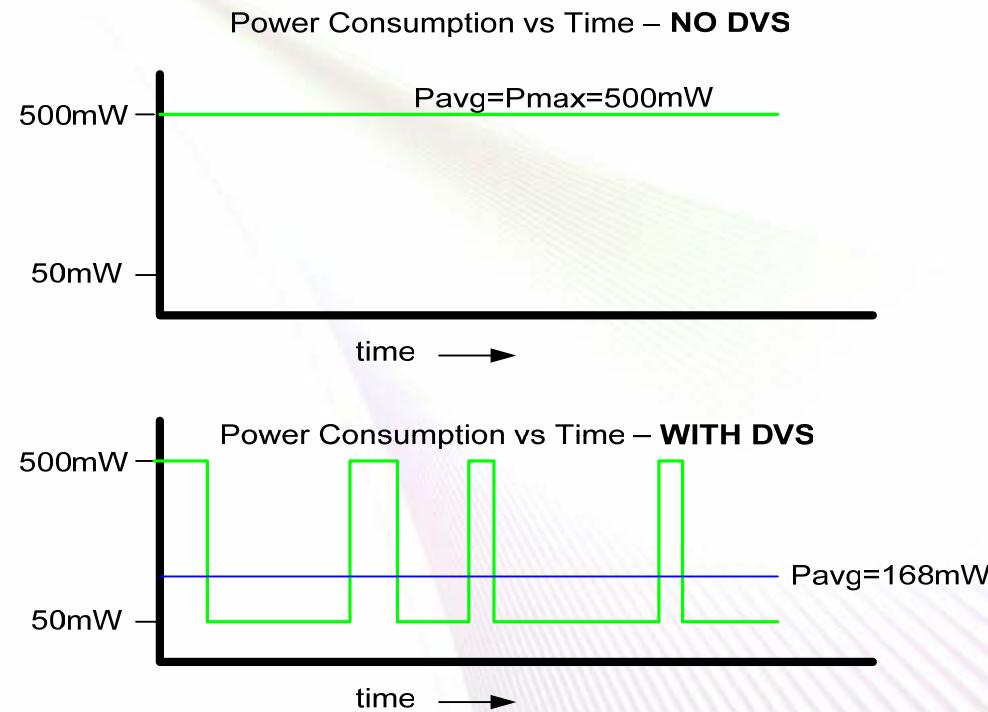

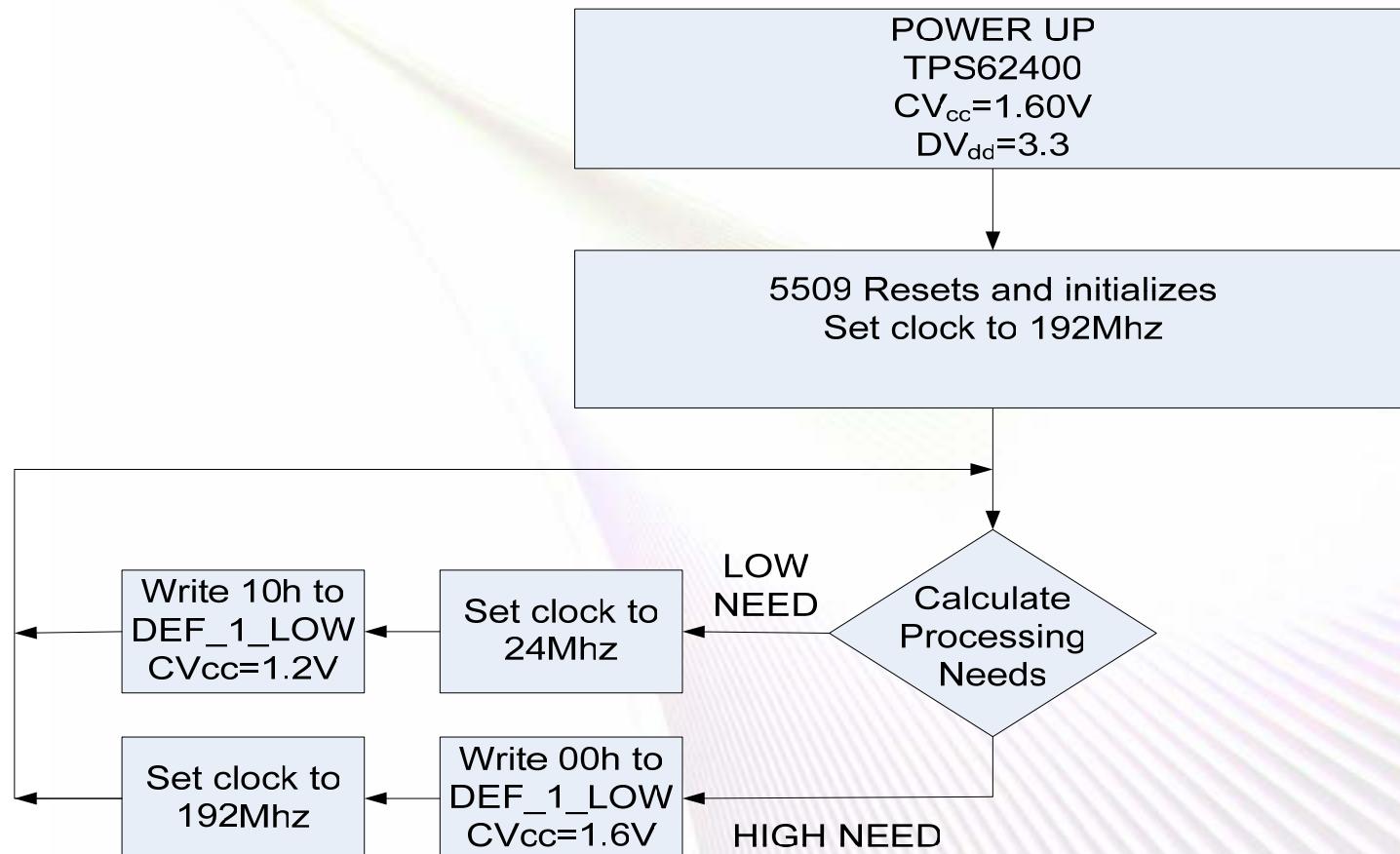

# Back to DVS: Process

- The DSP operating system predicts the immediate processing needs.

- DSP adjusts its clock frequency to match the needed processing power. This will **linearly** reduce the switching power.

- If the power supply powering the DSP supports DVS, then the DSP can adjust the voltage to what is needed to maintain the clock frequency. This will **exponentially** reduce the switching power.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Impact of DVS

Minds in Motion

Technology for Innovators™

TEXAS INSTRUMENTS

# DVS Power Supply Requirements

- Most DVS systems have dual voltage rails (core voltage and I/O voltage). A dual-channel power supply reduces parts count and cost, and it simplifies the design.

- One or both voltage outputs needs to be adjustable “on the fly” so that the supply voltage can dynamically track the needs of the processor.

- The output voltage of the power supply needs to change based on a digital input or some other communications channel.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

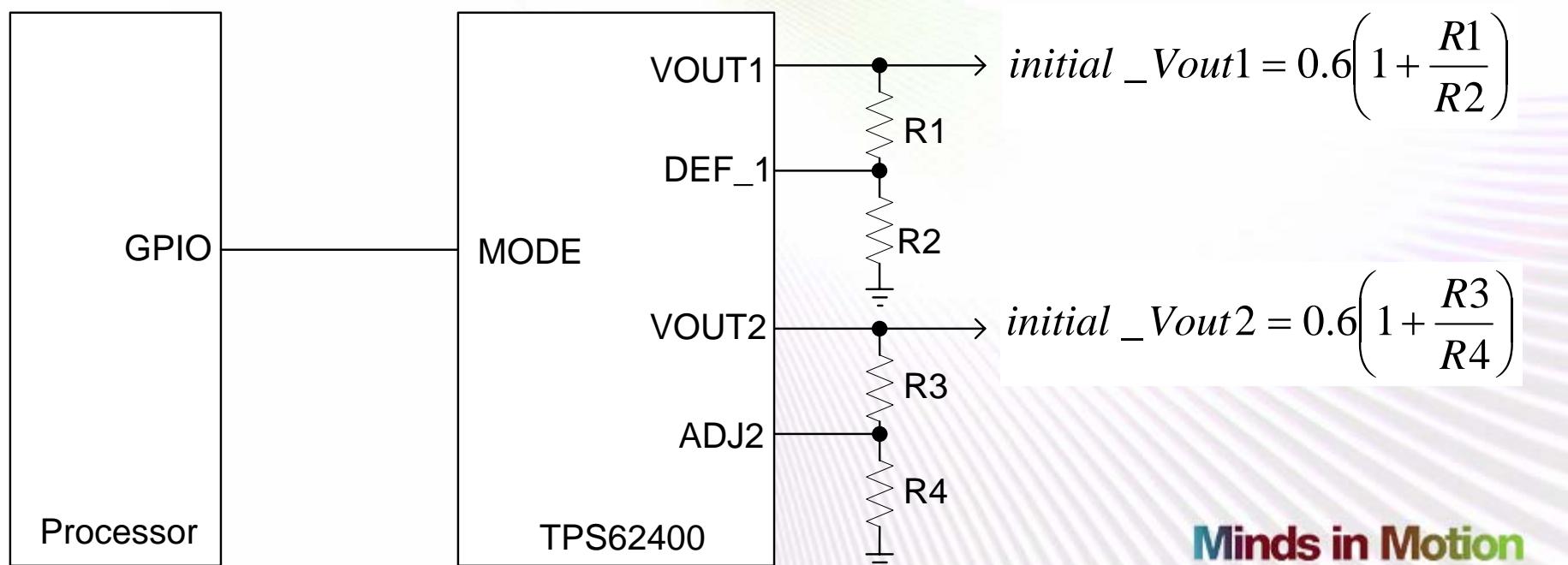

# TPS624xx

- Some ICs that are designed to support DVS of dual-core processors, FPGAs, and digital signal processors are the TPS62400, TPS62401 and TPS62420 from TI.

- They are dual output step-down DC/DC converters.

- Output currents are 400mA/600mA or 600mA/1000mA.

- Input voltage range is 2.5 - 6.0 VDC.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Features

- Software or pin-programmable output voltage selection to support dynamic voltage scaling applications. The output voltage can be changed “on-the-fly.”

- All versions support a one-wire serial communications channel (Easyscale) to change the output voltages of either output.

- TPS62401 has digital input to select between two different output voltages for VOUT1.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

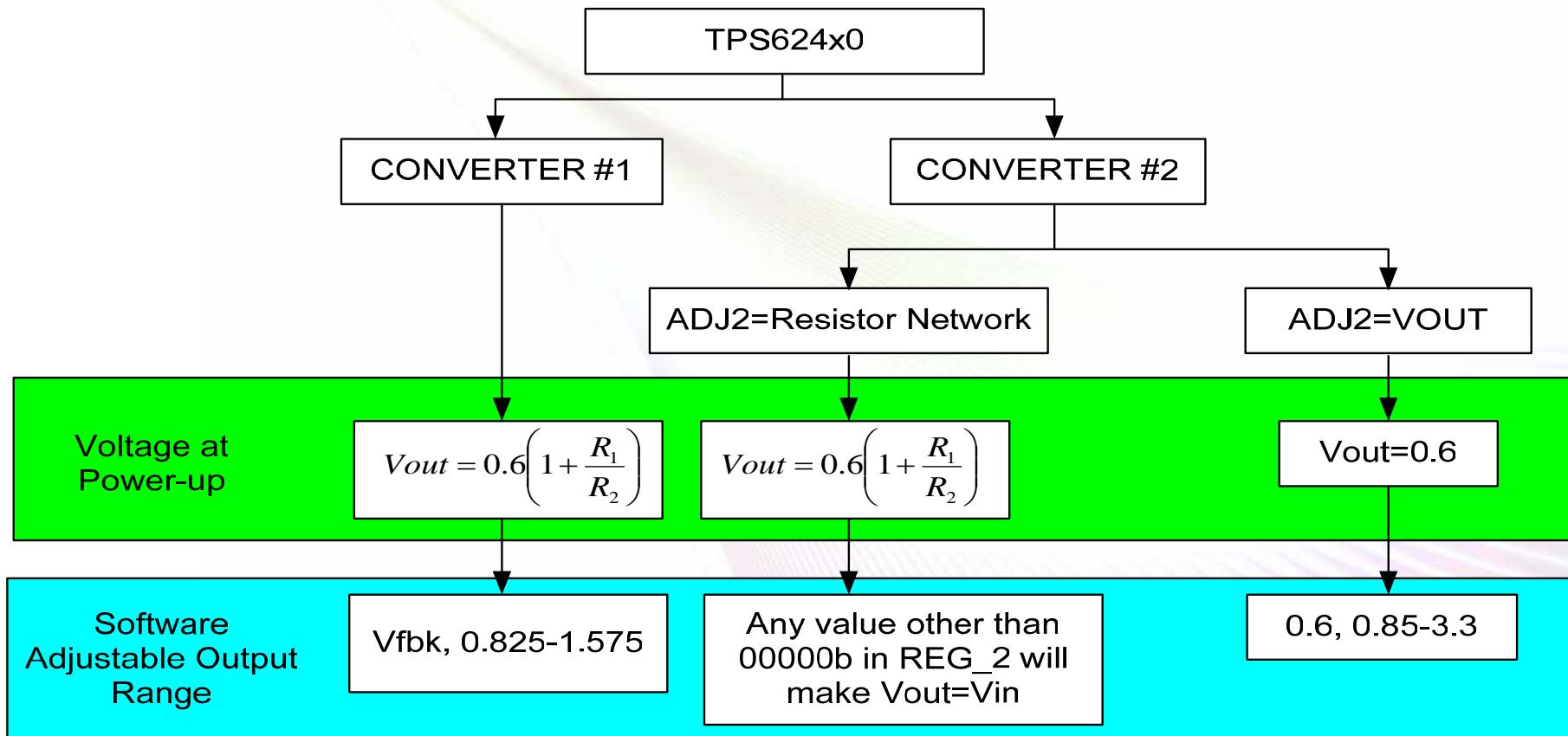

# TPS62400 'Adjustable' Output

Output voltage at power-up is determined by a feedback resistor network. Output can then be changed using Easyscale interface.

Minds in Motion

# TPS624x0 Output Voltage Selection

Minds in Motion

Technology for Innovators™

TEXAS INSTRUMENTS

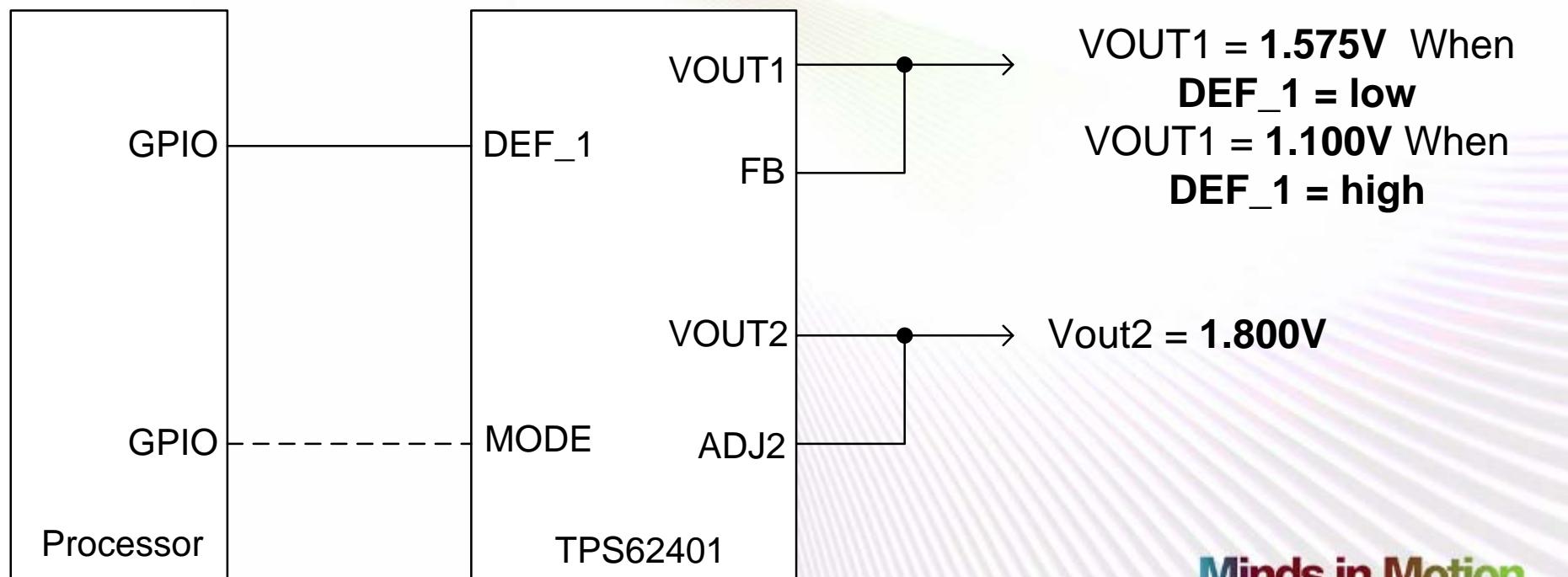

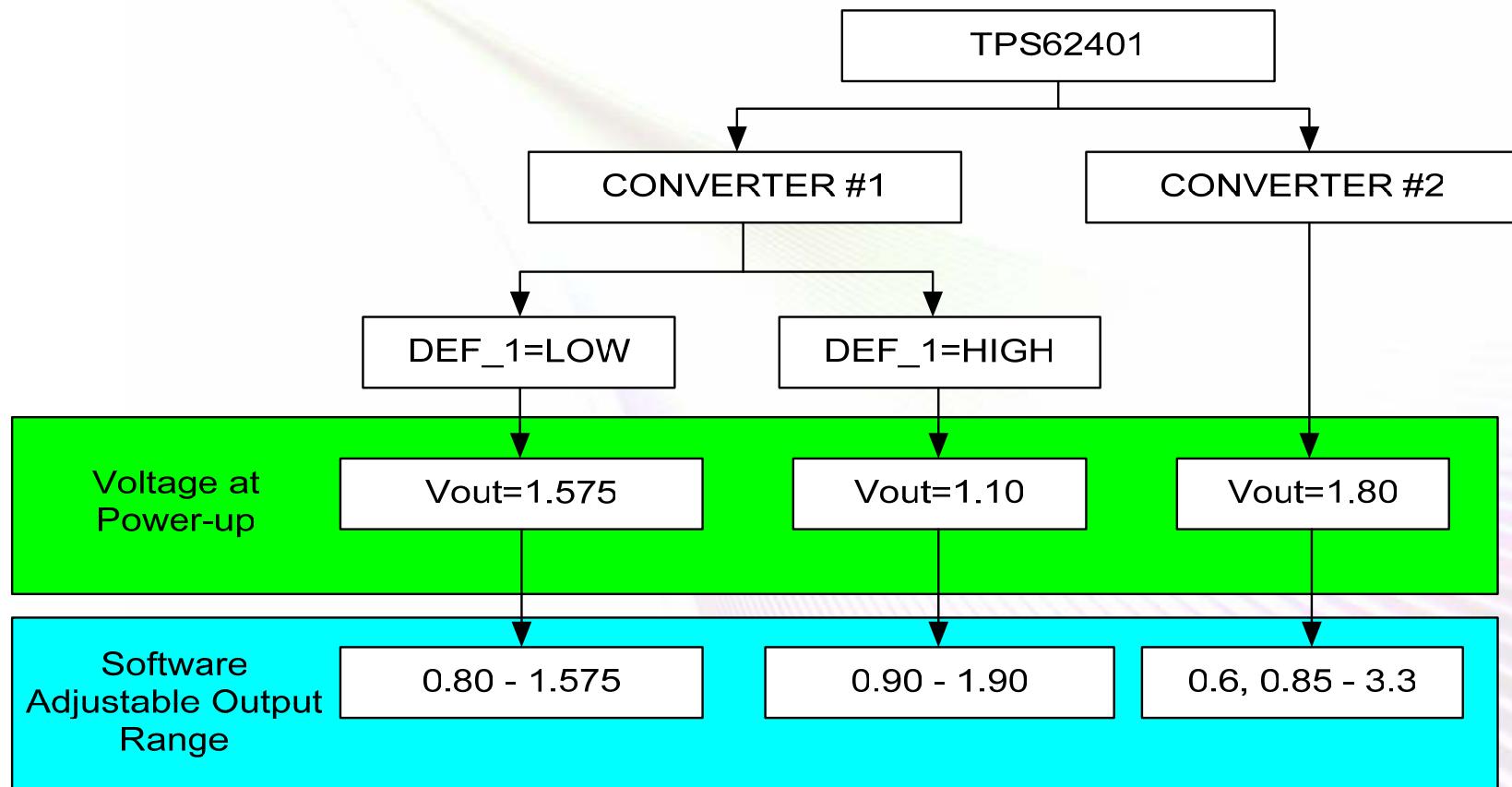

# TPS62401 'Fixed' Output

DEF\_1 pin acts as digital input to switch between two factory-preset output voltages. After power-up, the voltages can be altered using Easyscale.

Minds in Motion

# TPS62401 ‘Fixed-Output’ Output Voltage Selection

Minds in Motion

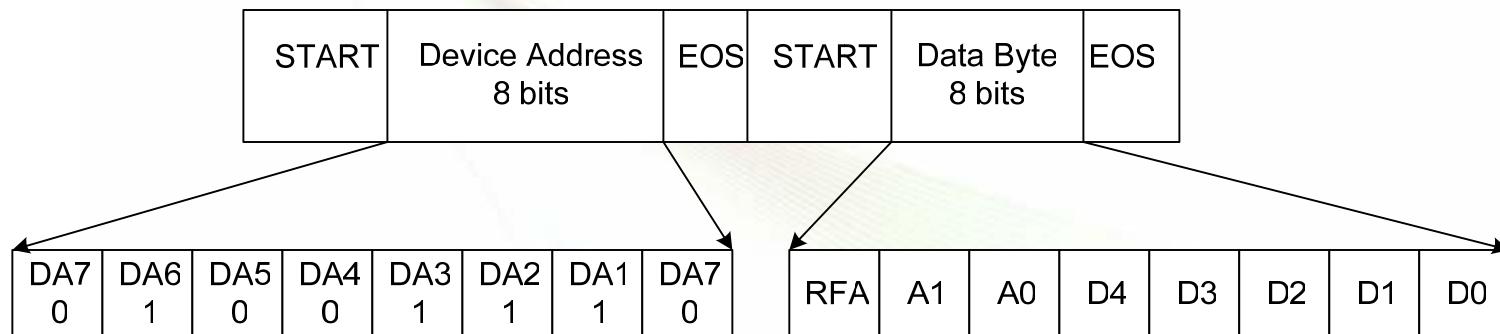

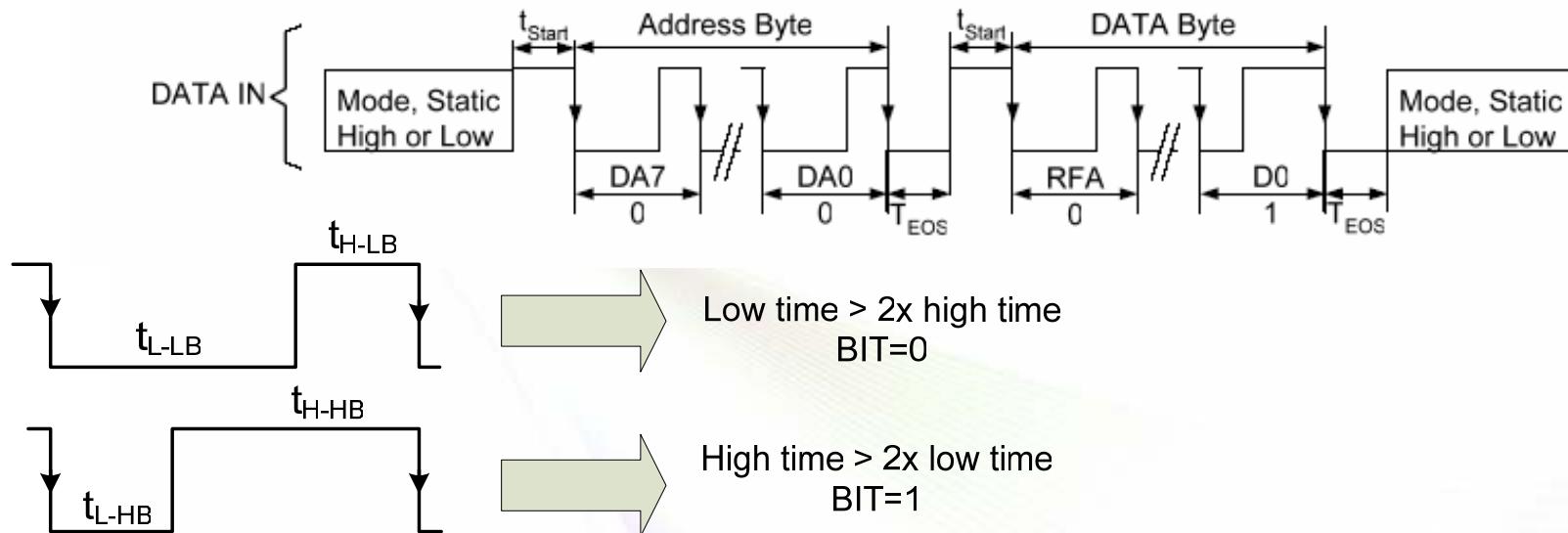

# Easyscale Protocol

Fixed to 4E hex

RFA: Request for Acknowledge

0=no ack

A0 & A1: Register Address

00 – DEF\_1\_LOW reg.

01 – DEF\_1\_High reg.

10 – DEF\_2 reg

11 – not valid

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Easyscale Waveforms & Bit Coding

|             |                                       |                                           |                     |     |    |

|-------------|---------------------------------------|-------------------------------------------|---------------------|-----|----|

| $t_{H\_LB}$ | High Time Low Bit, logic 0 detection  | signal level on MODE/DATA pin is $> 1.2V$ | 2                   | 200 | us |

| $t_{L\_LB}$ | Low Time Low Bit, logic 0 detection   | signal level on MODE/DATA pin $< 0.4V$    | $2x$<br>$t_{H\_LB}$ | 400 | us |

| $t_{L\_HB}$ | LowTime High Bit, logic 1 detection   | signal level on MODE/DATA pin $< 0.4V$    | 2                   | 200 | us |

| $t_{H\_HB}$ | High Time High Bit, logic 1 detection | signal level on MODE/DATA pin is $> 1.2V$ | $2x$<br>$t_{L\_HB}$ | 400 | us |

**Minds in Motion**

# TPS62400 DSP Application

Minds in Motion

# DSP Firmware Process

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

# Conclusion

- DVS can achieve significant power savings.

- DVS implementation requires a special-purpose power supply.

- The power supply must be able to adjust the output voltage and remain stable.

- There must be an interface between the power supply and the DSP or processor.

- TI has several power supply ICs to support dynamic voltage scaling designs.

**Minds in Motion**

Technology for Innovators™

**TEXAS INSTRUMENTS**

## System Power Savings Using Dynamic Voltage Scaling

Scot Lester

Texas Instruments

12500 TI Blvd.

Dallas, TX 75252

ScotLester@TI.com

### Minds in Motion

Technology for Innovators™

TEXAS INSTRUMENTS