# TI Designs: TIDA-01447 3.3-V, 1-A, Cost-Effective, Single-Layer TO-247 LDO Replacement Reference Design With 91% Efficiency

# Texas Instruments

# Description

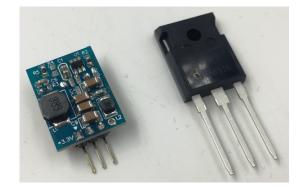

This reference design demonstrates a small solution size, high-efficiency, and low-EMI DC/DC module to replace LDOs in major home appliances. Replacing LDOs with DC/DC modules drastically improves system efficiency, saving on solution size and BOM cost while also eliminating the need for heat sinks. The module takes up the same amount of space as a TO-247 package and is pin-to-pin compatible with the TO-220 LDO, enabling quick evaluation and reduced time to market. The TPS561201 power converter enables a higher output current and lower power consumption at full-load, low-load, and standby operation.

This module is the same size with a TO-247 package and is pin compatible with the TO-220 LDO, enabling a quick evaluation and time to market.

### Resources

TIDA-01447 TPS561201

A

Design Folder Product Folder

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

### Features

- 3.3 V Regulated, up to 1-A Output Load

- 91% Efficiency

- 1.1-μA Standby Current and 423-μA No Load Current

- Small Form Factor: Pin-Compatible With TO-220 and Size-Compatible With TO-247 (15 mm × 20 mm)

- Less Than 35°C Increase at Full Load, Which Eliminates the Need of Heat Sink

- Reduces Onboard DC/DC Design Complexity, Saves R&D Time and Efforts for Switching Power Supply EMC Design (Quicker to Market)

### Applications

- Washing Machine and Dryer

- Refrigerator and Freezer

- Dishwasher

- Air Conditioner Indoor Units

### 1 System Description

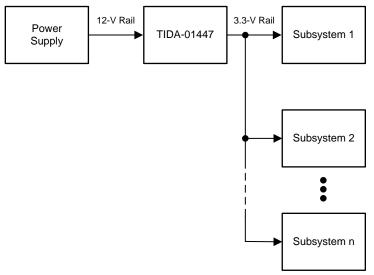

Traditionally, low dropout regulators (LDO) are used in home appliances to generate 5 V or 3.3 V from the 12-V rail. These LDOs are chosen mainly for their cost and size.

Copyright © 2017, Texas Instruments Incorporated

### Figure 1. System Diagram

With the tightening requirements on active and standby power consumption and the increasing current needs due to the addition of new features (for example, the Wi-Fi® module), the LDOs become an obstacle to achieving stringent energy ratings.

The TIDA-01447 is developed to answer this need of higher efficiency and current capability with the additional benefit of saving space by eliminating the heat sink, which is normally used to allow the LDOs to dissipate the losses.

### 1.1 Key System Specifications

2

The specifications of the TIDA-01447 design are listed in Table 1:

| PARAMETER                                          | SPECIFICATIONS                                                                                                      | DETAILS          |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|

| Input voltage range                                | 6.5 to 17 V                                                                                                         | _                |

| Output voltage and max current                     | 3.3 V at 1 A                                                                                                        | —                |

| Efficiency (full load, rated load, and light load) | 90%: 12 V $\rightarrow$ 3.3 V at 1 A; 91%: 12V $\rightarrow$ 3.3V at 0.500mA 80%: 12 V $\rightarrow$ 3.3 V at 10 mA | Section 3.2.2.1  |

| EMI performance                                    | EN55022 class A, >7-dB margin                                                                                       | Section 3.2.2.10 |

| Regulation (line and load)                         | ±3% across the input range and load current range                                                                   | Section 3.2.2.3  |

| Transient response                                 | ±3% from 0.1 to 1.0 A                                                                                               | Section 3.2.2.5  |

| Protections                                        | Short-circuit, hiccup mode OCP for both FETs, OTP, OVP                                                              | Section 3.2.2.7  |

| Operating ambient temperature                      | –30°C to 85°C                                                                                                       | Section 3.2.2.2  |

### **Table 1. Key System Specifications**

### 2 System Overview

# 2.1 Block Diagram

Figure 2. Block Diagram

# 2.2 Highlighted Products

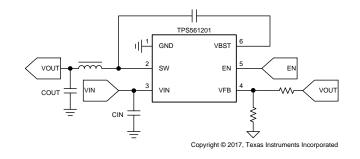

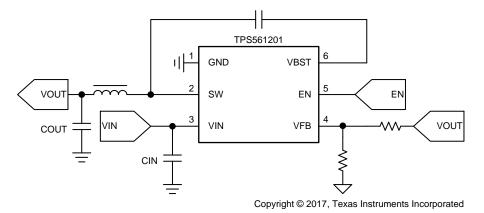

# 2.2.1 TPS561201

The TPS561201 is a simple, easy-to-use, 1-A synchronous step-down converters in a SOT-23 package. The devices are optimized to operate with minimum external component counts and also optimized to achieve low standby current.

These switch mode power supply (SMPS) devices employ D-CAP2<sup>™</sup> mode control providing a fast transient response and supporting both low equivalent series resistance (ESR) output capacitors such as specialty polymer and ultra-low ESR ceramic capacitors with no external compensation components.

The TPS561201 operates in pulse skip mode, which maintains high efficiency during light load operation. The TPS561201 is available in a 6-pin 1.6x2.9-mm SOT (DDC) package and specified from –40°C to 125°C of junction temperature.

Features:

- 1-A converter integrated 140-m  $\Omega$  and 84-m  $\Omega$  FETs

- D-CAP2 mode control with fast transient response

- Input voltage range: 4.5 to 17 V

- Output voltage range: 0.76 to 7 V

- Pulse-skip mode

- 580-kHz switching frequency

- Low shutdown current less than 10 µA

- 2% feedback voltage accuracy (25°C)

- Startup from pre-biased output voltage

- Cycle-by-cycle overcurrent limit

- Hiccup-mode overcurrent protection

- Non-latch UVP and TSD protections

- Fixed soft-start: 1.0 ms

4

### 2.3 System Design Theory

LDOs are devices that regulate the output voltage, while the output current is the same as the input current. This implies losses are proportional to the dropout between input and output voltage and the output current, as shown in Equation 1. These losses are the root cause of poor efficiency in LDOs. This translates to a limitation of the ratio between input and output voltage and maximum output current as well as the need of a heat sink. That heat sink adds cost and size to the overall solution.

A DC/DC switch mode power supply, including a Buck topology as in this project, present the advantage of having a higher efficiency, allowing them to be used in a wider variety of applications as well as being competitive with an LDO-based design with respect to cost and size (including all components and heat sink). Find more details on how a Buck topology works in the application report *Understanding Buck Power Stages In Switchmode Power Supplies* (SLVA057).

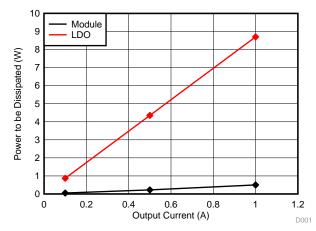

Compare the efficiency of the TIDA-01447 and an LDO-based design. The efficiency data for the TIDA-01447 design can be found in Section 3.2.2.1. In an LDO, the power to be dissipated can be estimated by Equation 1.

$$P_{\text{DISSIPATED}} = (V_{\text{IN}} - V_{\text{OUT}}) \times I_{\text{OUT}}$$

(1)

Now calculate the power dissipated by a 12-V input, 3.3-V output design at 1 A, 500 mA, and 100 mA to see what the performances are for the TIDA-01447 and for the LDO-based design.

For 1 A, the efficiency of the TIDA-01447 is 90% (10% loss). With 5 W at the output, 0.5 W are dissipated. For the LDO-based design, Equation 1 gives 8.7 W to be dissipated by the LDO.

For 500 mA, the efficiency of the TIDA-01447 is 91% (9% loss). With 2.5 W at the output, 0.225 W are dissipated. This is to be compared with 4.35 W for the LDO.

Finally for 100 mA, 0.0528 W needs to be dissipated for the TIDA-01447 (84% efficiency) versus 0.87 W for the LDO-based design.

Figure 3. Comparison of Power Dissipated

As shown in Figure 3, the LDO-based design needs to dissipate much more power than the TIDA-01447 design, which impacts both power consumption and cost and size due to the necessity of a heat sink.

# 2.4 Design Considerations

### System Overview

(2)

# 2.4.1 Part and Topology Selection

The first step of the design is to select the circuit topology. As cost and space are key in home appliance design and no isolation is needed for the 12-V to 3.3-V conversion, a Buck topology is chosen. Still, with the aim to reduce bill of material cost and size, a synchronous converter with integrated FET is preferred.

With this in mind, as well as the specification in Section 1.1, the TPS561201 is chosen. The converter includes two integrated switching FETs, internal loop compensation, and a 1-ms internal soft start to reduce component count. It integrates a 140-m $\Omega$  and a 84-m $\Omega$  MOSFET for up to 1-A continuous output current.

# 2.4.2 Design Steps and Passive Components Selection

The first step is to set the output voltage, which is adjusted by the resistor divider (R3 and R5). Set the range of the resistors; higher values decrease the losses in the resistor divider but make the feedback signal more sensitive to noise, while lower values will make the feedback signal more robust against noise but increase losses. On this project, a good trade-off is setting R5 at 10 k $\Omega$  and use Equation 2 to calculate R3.

$$\mathbf{R}_3 = \left(\frac{\mathbf{V}_{\mathsf{OUT}}}{0.768} - 1\right) \times \mathbf{R}_5$$

where:

- R5 = 10 kΩ

- V<sub>OUT</sub> = 3.3 V

Equation 2 gives R3 = 55.1 k $\Omega$ . A resistor value of 56.2 k $\Omega$  is then used for R3. By reversing Equation 2, an effective output voltage of V<sub>OUT</sub> = 5.084 V is given.

Then comes the choice of the output filter, including the output inductor (L1) and output capacitors (C3 and C4).

The LC filter used as the output filter has double pole at:

$$F_{\rm P} = \frac{1}{2\pi \sqrt{L_{\rm OUT} \times C_{\rm OUT}}}$$

(3)

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal gain of the device. The low frequency phase is 180 degrees. At the output filter pole frequency, the gain rolls off at a -40 dB per decade rate and the phase drops rapidly. D-CAP2 introduces a high frequency zero that reduces the gain roll off to -20 dB per decade and increases the phase to 90 degrees one decade above the zero frequency. The inductor and capacitor for the output filter must be selected so that the double pole of Equation 3 is located below the high frequency zero but close enough that the phase boost provided be the high-frequency zero provides adequate phase margin for a stable circuit.

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 4, Equation 5, and Equation 6. The inductor saturation current rating must be greater than the calculated peak current, and the RMS or heating current rating must be greater than the calculated RMS current. Use 580 kHz for  $f_{sw}$ . Make sure the chosen inductor is rated for the peak current of Equation 5 and the RMS current of Equation 6.

$$II_{p-p} = \frac{V_{OUT}}{V_{IN(MAX)}} \times \frac{V_{IN(MAX)} - V_{OUT}}{L_{O} \times f_{SW}}$$

(4)

$$II_{peak} = I_{O} + \frac{II_{p-p}}{2}$$

(5)

$$I_{LO(RMS)} = \sqrt{I_{O}^{2} + \frac{1}{12}II_{p-p}^{2}}$$

(6)

For this TIDesign, the inductor used is a Coilank ABG06A28M6R8 (6.8  $\mu$ H) with a peak current rating of 2.94 A and an RMS current rating of 2.47 A.

System Overview

An inductor between 3.3 and 4.7  $\mu$ H is recommended, but during testing, a 6.8  $\mu$ H inductor shows improved performance increasing the stability of the whole system. At the same time, C6 (100 pF) is also added to increase the transient response.

The capacitor value and ESR determines the amount of output voltage ripple. The TPS561201 is intended for use with ceramic or other low-ESR capacitors. Recommended values range from 20 to 68  $\mu$ F. Use Equation 7 to determine the required RMS current rating for the output capacitor.

$$I_{CO(RMS)} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{\sqrt{12} \times V_{IN} \times L_o \times f_{SW}}$$

(7)

For this design, two MURATA 22- $\mu$ F output capacitors are used.

The next step is to set the input capacitor. The TPS561201 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. TI recommends a ceramic capacitor over 10  $\mu$ F for the decoupling capacitor. An additional 0.1- $\mu$ F capacitor (C3) from pin 3 to ground is optional to provide additional high-frequency filtering. The capacitor voltage rating needs to be greater than the maximum input voltage.

For bootstrap capacitor selection, a  $0.1-\mu F$  ceramic capacitor must be connected between the VBST to SW pin for proper operation. TI recommends to use a ceramic capacitor.

The last step is to select the input filter. Considering the rated input RMS current, this TIDesign uses the ABG03A15M6R8 (6.8  $\mu$ H) with a peak current rating of 0.88 A and an RMS current rating of 0.88 A as the input inductor and the C3216X5R1E226M160AB (22  $\mu$ F) as the input capacitor.

# 3 Hardware, Testing Requirements, and Test Results

# 3.1 Required Hardware

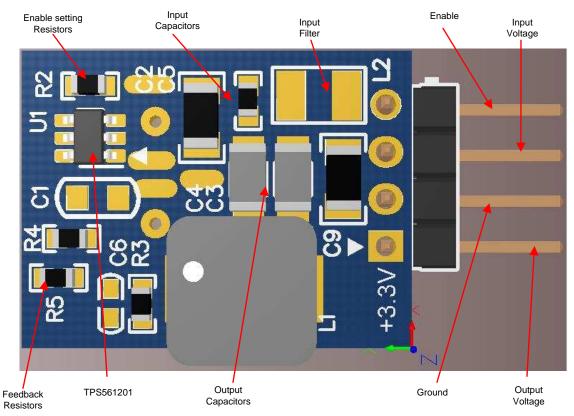

# 3.1.1 PCB Overview

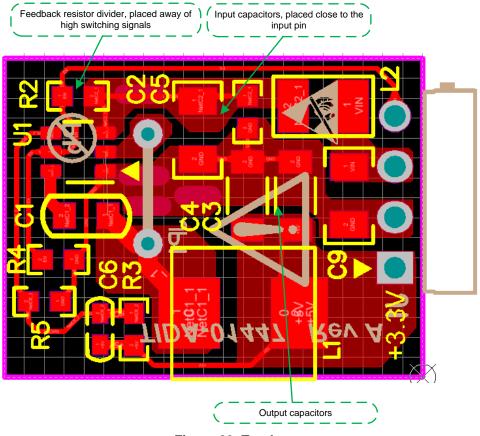

A picture of the PCB with the functional blocks is shown in Figure 4.

Figure 4. TIDA-01447 PCB With Functional Blocks

# 3.1.2 Connectors Settings

# **Table 2. Connector Settings**

| CONNECTOR | FUNCTION         |

|-----------|------------------|

| J1-1      | EN               |

| J1-2      | V <sub>IN</sub>  |

| J1-3      | GND              |

| J1-4      | V <sub>OUT</sub> |

# 3.2 Testing and Results

# 3.2.1 Setup

Figure 5 shows the setup and the test equipment used.

Figure 5. Picture of Test Setup for TIDA-01447

Table 3 lists the test equipment used to test the TIDA-01447.

| Table  | 3. | Test | Eaui | pment    |

|--------|----|------|------|----------|

| I UNIC | υ. | 1000 | Lyan | princine |

| TEST EQUIPMENT  | PART NUMBER            |

|-----------------|------------------------|

| Oscilloscope    | Tektronix DPO 3054     |

| Voltage probe   | Tektronix P6139A       |

| Current probe   | Tektronix TCP202       |

| Multimeter      | Fluke 287C             |

| Power supply    | Agilent E3631A         |

| Electronic load | Chroma 63103 and 63102 |

| Thermal camera  | Fluke TI110            |

# 3.2.2 Test Results

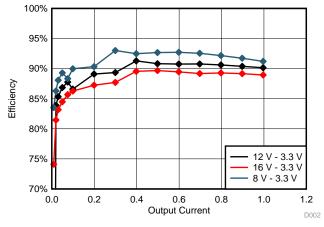

### 3.2.2.1 Efficiency

To test the efficiency, four multimeters are used: two are set up as voltmeters to measure the input and output voltages, and two are set up as ammeters to measure the input and output currents.

The measurements are done at a temperature of 28.3°C and with the enable setting resistors (R2 and R4) not populate, with a 6-V apply to the Enable pin.

Figure 6. TIDA-01447 Efficiency

Table 4, Table 5, and Table 6 list the details of the efficiency curves shown in Figure 6.

| V <sub>IN</sub> (V) | I <sub>IN</sub> (mA) | V <sub>out</sub> (V) | Ι <sub>ουτ</sub> (mA) | η           |

|---------------------|----------------------|----------------------|-----------------------|-------------|

| 7.950               | 0.4743               | 3.452                | 0.9962                | 0.912004689 |

| 7.950               | 0.4255               | 3.457                | 0.8975                | 0.917206542 |

| 7.950               | 0.3766               | 3.461                | 0.7973                | 0.921670992 |

| 7.950               | 0.3283               | 3.465                | 0.6971                | 0.925465664 |

| 7.960               | 0.2813               | 3.469                | 0.5984                | 0.927071190 |

| 7.970               | 0.2342               | 3.472                | 0.4982                | 0.926698004 |

| 7.970               | 0.1877               | 3.476                | 0.3980                | 0.924783869 |

| 7.980               | 0.1405               | 3.485                | 0.2992                | 0.930004727 |

| 7.980               | 0.0950               | 3.441                | 0.1990                | 0.903256826 |

| 7.990               | 0.0469               | 3.416                | 0.0987                | 0.899736611 |

| 7.990               | 0.0361               | 3.411                | 0.0747                | 0.883381582 |

| 7.990               | 0.0236               | 3.415                | 0.0493                | 0.892850703 |

| 7.995               | 0.0145               | 3.415                | 0.0299                | 0.880796187 |

| 7.995               | 0.0096               | 3.414                | 0.0194                | 0.862929956 |

| 7.995               | 0.0046               | 3.413                | 0.0090                | 0.835223101 |

| · ·                 |                      |                      |                       |             |  |  |

|---------------------|----------------------|----------------------|-----------------------|-------------|--|--|

| V <sub>IN</sub> (V) | I <sub>IN</sub> (mA) | V <sub>OUT</sub> (V) | I <sub>оυт</sub> (mA) | η           |  |  |

| 11.96               | 0.3204               | 3.4670               | 0.9963                | 0.901405669 |  |  |

| 11.97               | 0.2881               | 3.4725               | 0.8975                | 0.903731256 |  |  |

| 11.97               | 0.2556               | 3.4770               | 0.7973                | 0.906090245 |  |  |

| 11.97               | 0.2234               | 3.4820               | 0.6971                | 0.907708768 |  |  |

| 11.98               | 0.1922               | 3.4920               | 0.5984                | 0.907518775 |  |  |

| 11.98               | 0.1599               | 3.4920               | 0.4982                | 0.908181553 |  |  |

| 11.98               | 0.1264               | 3.4730               | 0.3980                | 0.912817512 |  |  |

| 11.98               | 0.0965               | 3.4520               | 0.2992                | 0.893404725 |  |  |

| 11.99               | 0.0641               | 3.4410               | 0.1990                | 0.890964780 |  |  |

| 11.99               | 0.0325               | 3.4190               | 0.0987                | 0.865991660 |  |  |

| 11.99               | 0.0243               | 3.4230               | 0.0747                | 0.877610972 |  |  |

| 11.99               | 0.0162               | 3.4220               | 0.0493                | 0.868545805 |  |  |

| 11.99               | 0.0100               | 3.4220               | 0.0299                | 0.853359466 |  |  |

| 11.99               | 0.0066               | 3.4220               | 0.0194                | 0.838916269 |  |  |

| 11.99               | 0.0320               | 3.4210               | 0.0089                | 0.079354931 |  |  |

# Table 5. Efficiency With 12-V Input

# Table 6. Efficiency With 16-V Input

| V <sub>IN</sub> (V) | I <sub>IN</sub> (mA) | V <sub>оυт</sub> (V) | I <sub>out</sub> (mA) | η           |

|---------------------|----------------------|----------------------|-----------------------|-------------|

| 15.97               | 0.2437               | 3.474                | 0.9964                | 0.889412211 |

| 15.97               | 0.2194               | 3.480                | 0.8977                | 0.891597680 |

| 15.97               | 0.1949               | 3.485                | 0.7974                | 0.892816604 |

| 15.98               | 0.1706               | 3.487                | 0.6972                | 0.891771367 |

| 15.98               | 0.1466               | 3.502                | 0.5984                | 0.894534266 |

| 15.98               | 0.1211               | 3.483                | 0.4982                | 0.896677515 |

| 15.98               | 0.0969               | 3.484                | 0.3980                | 0.895489847 |

| 15.98               | 0.0738               | 3.457                | 0.2992                | 0.877057026 |

| 15.99               | 0.0491               | 3.442                | 0.1990                | 0.872436821 |

| 15.99               | 0.0245               | 3.424                | 0.0987                | 0.862653444 |

| 15.99               | 0.0187               | 3.425                | 0.0748                | 0.856785491 |

| 15.99               | 0.0125               | 3.425                | 0.0493                | 0.844790494 |

| 15.99               | 0.0077               | 3.425                | 0.0299                | 0.831749551 |

| 15.99               | 0.0051               | 3.424                | 0.0194                | 0.814548308 |

| 15.99               | 0.0026               | 3.423                | 0.0090                | 0.741016020 |

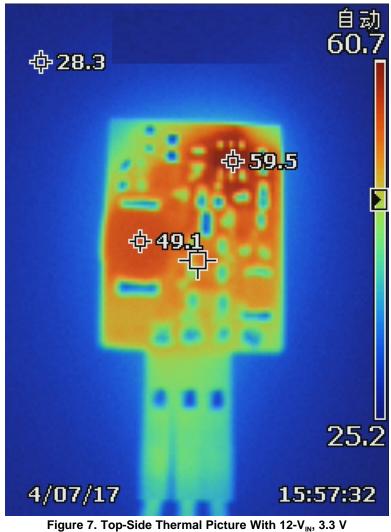

### 3.2.2.2 Thermal

The thermal picture in Figure 7 was taken at a room temperature of 28.3°C, with a 12-V input, 3.3 V at 1-A output without airflow.

Hardware, Testing Requirements, and Test Results

The hottest point of the design is the TPS561201 at 59.5°C. This is an increase of 31.2°C. Because the acceptable ambient temperature range is -30°C to 85°C, no heat sink is required for the TIDA-01447 to function properly.

gure 7. Top-Side Thermal Picture With 12-V<sub>IN</sub>, 3.3 at 1-A Output

#### 3.2.2.3 Line and Load Regulation

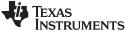

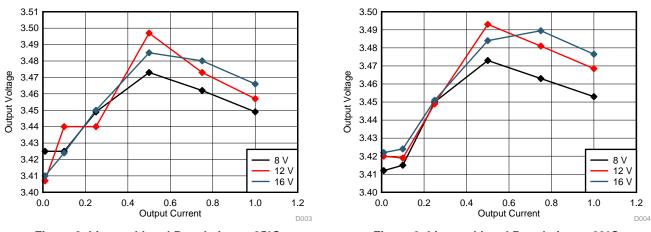

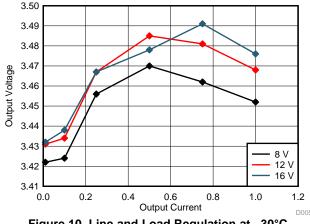

Figure 8, Figure 9, and Figure 10 show the output voltage variation, depending on load current, input voltage, and temperature. Across all input voltages and output currents, the output voltage varies between 3.49 and 3.41 V, well below the  $\pm 3\%$  that was the initial target.

Figure 8. Line and Load Regulation at 85°C

Figure 9. Line and Load Regulation at 23°C

Figure 10. Line and Load Regulation at -30°C

Table 7, Table 8, and Table 9 list the details of the regulation curves shown in Figure 8 and Figure 10.

| V <sub>IN</sub> | V <sub>OUT</sub> | I <sub>OUT</sub> |

|-----------------|------------------|------------------|

| 16              | 3.4660           | 1.00             |

| 16              | 3.4801           | 0.75             |

| 16              | 3.4850           | 0.50             |

| 16              | 3.4500           | 0.25             |

| 16              | 3.4240           | 0.10             |

| 16              | 3.4100           | 0.01             |

| 12              | 3.4570           | 1.00             |

| 12              | 3.4730           | 0.75             |

| 12              | 3.4970           | 0.50             |

| 12              | 3.4400           | 0.25             |

| 12              | 3.4400           | 0.10             |

| 12              | 3.4070           | 0.01             |

| 8               | 3.4490           | 1.00             |

| 8               | 3.4620           | 0.75             |

| 8               | 3.4730           | 0.50             |

| 8               | 3.4490           | 0.25             |

| 8               | 3.4250           | 0.10             |

| 8               | 3.4250           | 0.01             |

# Table 7. Line and Load Regulation at 85°C

|                 | <b>..</b>        |                  |

|-----------------|------------------|------------------|

| V <sub>IN</sub> | V <sub>out</sub> | Ι <sub>ουτ</sub> |

| 16              | 3.4765           | 1.00             |

| 16              | 3.4895           | 0.75             |

| 16              | 3.4840           | 0.50             |

| 16              | 3.4510           | 0.25             |

| 16              | 3.4240           | 0.10             |

| 16              | 3.4220           | 0.01             |

| 12              | 3.4685           | 1.00             |

| 12              | 3.4810           | 0.75             |

| 12              | 3.4930           | 0.50             |

| 12              | 3.4490           | 0.25             |

| 12              | 3.4190           | 0.10             |

| 12              | 3.4200           | 0.01             |

| 8               | 3.4530           | 1.00             |

| 8               | 3.4630           | 0.75             |

| 8               | 3.4730           | 0.50             |

| 8               | 3.4500           | 0.25             |

| 8               | 3.4150           | 0.10             |

| 8               | 3.4120           | 0.01             |

# Table 8. Line and Load Regulation at 23°C

# Table 9. Line and Load Regulation at -30°C

| V <sub>IN</sub> | V <sub>out</sub> | I <sub>OUT</sub> |

|-----------------|------------------|------------------|

| 16              | 3.476            | 1.00             |

| 16              | 3.491            | 0.75             |

| 16              | 3.478            | 0.50             |

| 16              | 3.467            | 0.25             |

| 16              | 3.438            | 0.10             |

| 16              | 3.432            | 0.01             |

| 12              | 3.468            | 1.00             |

| 12              | 3.481            | 0.75             |

| 12              | 3.485            | 0.50             |

| 12              | 3.467            | 0.25             |

| 12              | 3.434            | 0.10             |

| 12              | 3.431            | 0.01             |

| 8               | 3.452            | 1.00             |

| 8               | 3.462            | 0.75             |

| 8               | 3.470            | 0.50             |

| 8               | 3.456            | 0.25             |

| 8               | 3.424            | 0.10             |

| 8               | 3.422            | 0.01             |

Hardware, Testing Requirements, and Test Results

### www.ti.com

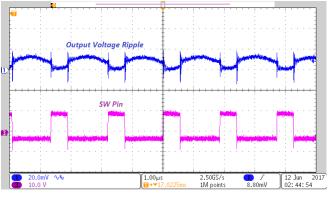

# 3.2.2.4 Output Voltage Ripple

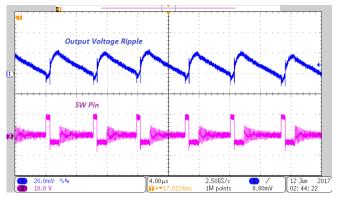

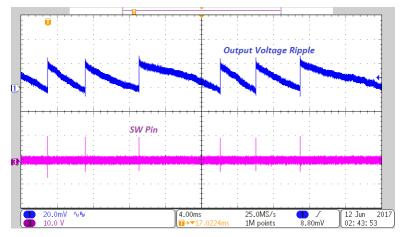

The output voltage ripple remains below 30 mVpp under full load (1 A), low load (10 mA), or no load. This ripple is well below the initial requirements of  $\pm 1\%$ .

Measurements are done at 28.3°C room temperature with a 12-V input voltage. The upper curve (1) is the output voltage with an oscilloscope in AC-coupling mode with 20 mV/div. The lower curve (2) is the switch node (pin 2 of the TPS561201) with 5 V/div.

Figure 11. Output Voltage Ripple at 1-A Output Load

Figure 12. Output Voltage Ripple at 10-mA Output Load

Figure 13. Output Voltage Ripple at No Load Output

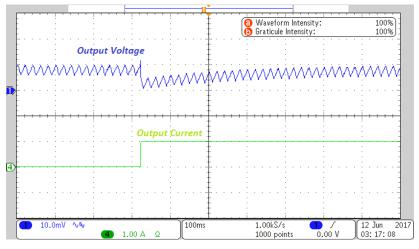

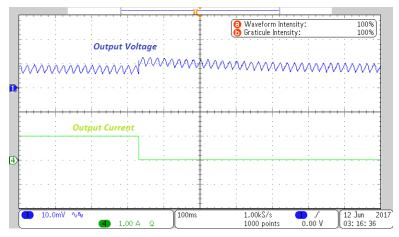

### 3.2.2.5 Transient Response

The transient response is below  $\pm 10$  mV for load steps between 10 mA and 1 A, which are the design requirements ( $\pm 3\%$ ).

Measurements are done at 28.3°C room temperature with a 12-V input voltage. The upper curve (1) is the output voltage with an oscilloscope in AC-coupling mode with 10 mV/div. The lower curve (4) is the output current with 1 A/div. The load step is applied with a 1-A/ms slew rate.

Figure 14. Transient Response From 10-mA to 1-A Output Load

Figure 15. Transient Response From 1-A to 10-mA Output Load

Hardware, Testing Requirements, and Test Results

### www.ti.com

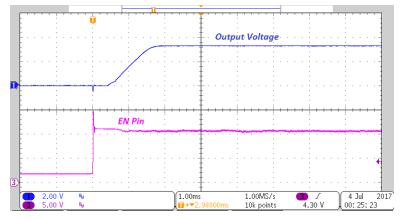

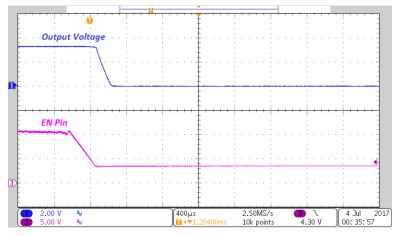

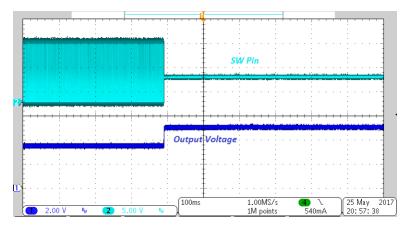

### 3.2.2.6 Start-up and Shutdown

For the start-up and the shutdown behavior, 12 V is applied at the input with a 1-A load at the output.

Measurements are done at 28.3°C room temperature. The upper curve (3) is the EN pin with an oscilloscope in DC-coupling mode with 2 V/div. The lower curve (2) is the switch node pin signal with an oscilloscope in DC-coupling mode with 10 V/div. The upper curve (1) is the output voltage with an oscilloscope in DC-coupling mode with 5 V/div. The lower curve (4) is the output current with 1 A/div.

The TIDA-01447 design takes 1.7 ms to provide 3.3 V. The output voltage is reached without overshoot.

Figure 16. Start-up at 12-V Input and 1-A Output Load

Figure 17. Shutdown at 12-V Input and 1-A Output Load

Hardware, Testing Requirements, and Test Results

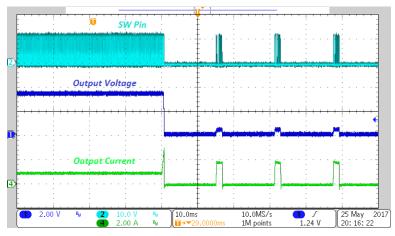

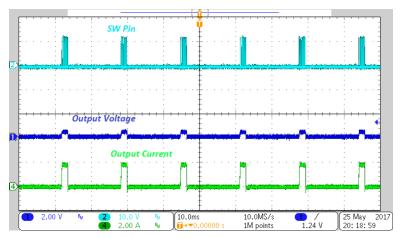

### 3.2.2.7 Overcurrent and Short-Circuit Test

The overcurrent protection is tested by having a transient load from a 1- to 3-A output current while the board is supplied with 12 V. The short-circuit protection is tested by shorting the output pin to ground.

The upper curve (1) is the output voltage with an oscilloscope in DC-coupling mode with 2 V/div (Figure 18) and 1 V/div (Figure 19). The lower curve (4) is the output current with 2 A/div.

As shown in Figure 18 and Figure 19, when the current is rising to the current limit level, the device enters overcurrent protection as described in the TPS561201 datasheet (SLVSC95). After waiting the preprogrammed time, the device tries to restart. Once the fault condition is removed, the device starts normally.

**Figure 18. Overcurrent Protection**

Figure 19. Short-Circuit Protection

Hardware, Testing Requirements, and Test Results

### www.ti.com

## 3.2.2.8 Overvoltage Test

The overvoltage protection is tested by applying 6 V at the output of the TIDA-01447 board while the board is supplied with 12 V and with a 1-A output load.

The upper curve (1) is the output voltage with an oscilloscope in DC-coupling mode with 2 V/div. The lower curve (2) is voltage at the switch node with 5 V/div.

Figure 20. Overvoltage Protection From 5 to 6 V

### 3.2.2.9 Standby and No-Load Currents

The standby current is measured with an ammeter at 26°C room temperature with a 12-V input voltage. The enable pin was set low through the connector, and the enable setting resistors (R2 and R4) not populated. The standby current was measured at 1.3  $\mu$ A.

The no-load current was measured with an ammeter at 26°C room temperature with a 12-V input voltage, with the enable setting resistors (R2 and R4) populated and no load attached at the output. The no-load current was measured at 472  $\mu$ A.

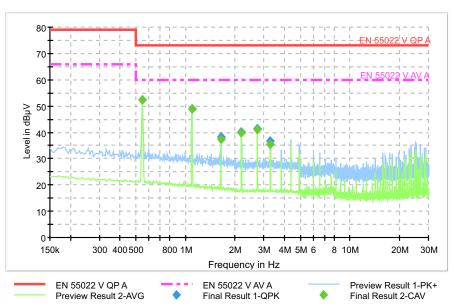

# 3.2.2.10 EMC Tests

The TIDA-01447 TI Design has been tested for EMI according to EN55022 Class A conducted emissions. The EMC tests were performed by the Shanghai Institute of Measurement and Testing Technology Fundamental Performance Test Centre (China).

Figure 21. Conducted Emission Test Setup

The board pass the conducted emission test with more than 7 dB of margin.

Figure 22. Conducted Emission Test Result

# Table 10. Final Result 1

| FREQ<br>(MHz) | QUASIPEAK<br>(dBµV) | MEAS TIME<br>(ms) | BANDWIDTH<br>(kHz) | PE  | LINE | CORR (dB) | MARGIN<br>(dB) | LIMIT (dBµV) |

|---------------|---------------------|-------------------|--------------------|-----|------|-----------|----------------|--------------|

| 0.5495        | 52.4                | 1000              | 9                  | FLO | L1   | 20.3      | 20.6           | 73           |

| 1.0940        | 48.8                | 1000              | 9                  | FLO | L1   | 20.4      | 24.2           | 73           |

| 1.6430        | 38.1                | 1000              | 9                  | FLO | L1   | 20.5      | 34.9           | 73           |

| 2.1920        | 40.2                | 1000              | 9                  | FLO | L1   | 20.6      | 32.8           | 73           |

| 2.7410        | 41.4                | 1000              | 9                  | FLO | L1   | 20.6      | 31.6           | 73           |

| 3.2855        | 36.7                | 1000              | 9                  | FLO | L1   | 20.7      | 36.3           | 73           |

# Table 11. Final Result 2

| FREQ<br>(MHz) | AVERAGE<br>(dBµV) | MEAS TIME<br>(ms) | BANDWIDTH<br>(kHz) | PE  | LINE | CORR (dB) | MARGIN<br>(dB) | LIMIT<br>(dBµV) |

|---------------|-------------------|-------------------|--------------------|-----|------|-----------|----------------|-----------------|

| 0.5495        | 52.5              | 1000              | 9                  | FLO | L1   | 20.3      | 7.5            | 60              |

| 1.0940        | 48.8              | 1000              | 9                  | FLO | L1   | 20.4      | 11.2           | 60              |

| 1.6430        | 37.3              | 1000              | 9                  | FLO | L1   | 20.5      | 22.7           | 60              |

| 2.1920        | 39.8              | 1000              | 9                  | FLO | L1   | 20.6      | 20.2           | 60              |

| 2.7410        | 41.2              | 1000              | 9                  | FLO | L1   | 20.6      | 18.8           | 60              |

| 3.2855        | 35.6              | 1000              | 9                  | FLO | L1   | 20.7      | 24.4           | 60              |

TEXAS INSTRUMENTS

www.ti.com

Design Files

# 4 Design Files

# 4.1 Schematics

To download the schematics, see the design files at TIDA-01447.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01447.

# 4.3 PCB Layout Recommendations

In switch mode DC/DC, take care to avoid coupling between the different loops to improve performances. In a Buck topology, the input loop is particularly critical; for this reason, place the input capacitors as close as possible to the TPS561201.

This is done by separating the noise sensitive loop (feedback and enable) from the high di/dt loops (input, switch node, bootstrap). Separate these loops by placing the components and traces of the feedback and enable loop as far as possible from components and traces with high di/dt.

Also give special attention was also given to the ground plane; try to make it as large and as solid as possible to both reduce noise sensitivity and help thermal dissipation.

With regards to thermal dissipation, the input and output voltage planes must also made as large and solid as possible to help keep the board as cool as possible.

Lastly, the soldering pad for the inductor was slightly enlarged to allow the tests of several inductors.

Figure 23. Top Layer

# 4.3.1 Layout Prints

Design Files

To download the layer plots, see the design files at TIDA-01447.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01447.

# 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01447.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01447.

# 5 Related Documentation

- 1. Texas Instruments, *Understanding Buck Power Stages In Switchmode Power Supplies*, Application Report (SLVA057)

- Texas Instruments, Layout Tips for EMI Reduction in DC / DC Converters, AN-2155 Application Report (SNVA638)

- 3. Texas Instruments, *Simple Success With Conducted EMI From DCDC Converters*, AN-2162 Application Report (SNVA489)

# 5.1 Trademarks

D-CAP2 is a trademark of Texas Instruments. Wi-Fi is a registered trademark of Wi-Fi Alliance. All other trademarks are the property of their respective owners.

# 6 About the Authors

**YUAN (JASON) TAO** is a systems engineer at Texas Instruments, where he is responsible for developing reference design solutions for the industrial segment. Yuan brings to this role his extensive experience in power electronics, high-frequency DC-DC, AC-DC converters, and analog circuit design. Yuan earned his master of IC design and manufacture from Shanghai Jiao Tong University in 2007.

**KEVIN STAUDER** is a system engineer in the Industrial Systems team at Texas Instruments, responsible for developing TI Designs for industrial applications.

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated