## TI Designs: TIDA-01416 Small, Efficient, Flexible Power Supply Reference Design for NXP™ i.MX7 Series Application Processors

# Texas Instruments

#### Description

This small, efficient and flexible power supply reference design demonstrates a complete power solution for NXP<sup>™</sup> i.MX7 processors. This simple solution uses just five DC/DC converters and one sequencer integrated circuit (IC) to power the i.MX7 in a very cost-effective design. This reference design supports numerous industrial applications and any application that requires a small, high-efficiency, flexible power supply solution.

#### Resources

| TIDA-01416          | 0 |

|---------------------|---|

| TLV62080, TLV62084A | F |

| TLV62085            | F |

| LM3880              | F |

Design Folder Product Folder Product Folder Product Folder

# ASK Our E2E Experts Community

#### Features

- 3.3-V to 5.5-V Input Voltage Range

- DCS-Control<sup>™</sup> Topology for Fast Transient Response

- High Efficiency and Low Quiescent Current

- Automatic Power Save Mode for Light Load Efficiency

- TLV6208x Family Approach for Low-Cost Solutions

#### Applications

- Appliances

- Test and Measurement

- Electronic Point of Sale

- Internet of Things

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 System Description

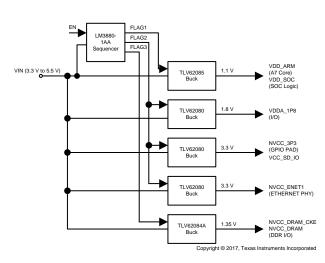

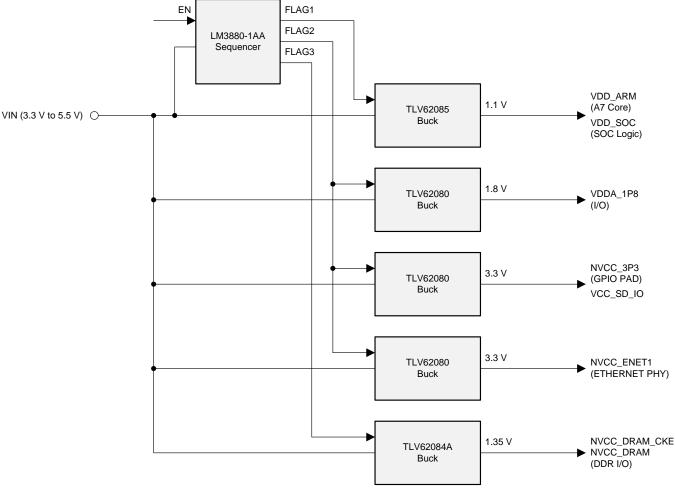

The i.MX7 series application processor from NXP is a highly-integrated, multi-market applications processor designed to enable various applications. This TIDA-01416 reference design provides a scalable power solution for several i.MX7 processor versions supporting space-constrained and cost-sensitive systems. The power architecture follows the source material in *i.MX 7Dual Family of Applications Processors Datasheet*. A 1.1-V rail is required for the core and system on chip (SoC), a 1.8-V rail for the input/output (I/O) pads, a 3.3-V rail for I/O and SD card pads, a 3.3-V rail for Ethernet controller, and a 1.35-V rail for DDR3 I/O pad supply.

This reference design achieves high efficiency by using efficient, integrated DC/DC converters and no low dropout (LDO) linear regulators. High efficiency results in a low self-temperature rise and higher reliability.

#### 1.1 Key System Specifications

| PAF                                                   | RAMETER            | SPECIFICATIONS                                                                                                               | DETAILS                                                             |

|-------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Input voltage range                                   |                    | 3.3 V to 5.5 V                                                                                                               | <u> </u>                                                            |

| OUTPUTS PROVIDED                                      |                    | · · · · · · · · · · · · · · · · · · ·                                                                                        |                                                                     |

| VDD_ARM, VDD_SOC                                      | Voltage setpoint   | 1.1 V                                                                                                                        | Section 3.1.1                                                       |

|                                                       | Ripple             | < 20 mV                                                                                                                      |                                                                     |

|                                                       | Transient response | < 5%                                                                                                                         |                                                                     |

|                                                       | Load regulation    | < 0.4 %                                                                                                                      |                                                                     |

|                                                       | Line regulation    | < 0.4%                                                                                                                       |                                                                     |

|                                                       | Voltage setpoint   | 1.8 V                                                                                                                        |                                                                     |

|                                                       | Ripple             | < 25 mV                                                                                                                      |                                                                     |

| VDDA_1P8                                              | Transient response | < 5%                                                                                                                         | Section 3.1.2                                                       |

|                                                       | Load regulation    | < 0.4 %                                                                                                                      |                                                                     |

|                                                       | Line regulation    | < 0.4 %                                                                                                                      |                                                                     |

|                                                       | Voltage setpoint   | 3.3 V                                                                                                                        |                                                                     |

|                                                       | Ripple             | < 20 mV                                                                                                                      |                                                                     |

| NVCC_3P3,<br>NVCC_ENET1                               | Transient response | < 5 %                                                                                                                        | Section 3.1.3                                                       |

| NVCC_ENETT                                            | Load regulation    | < 0.4 %                                                                                                                      |                                                                     |

|                                                       | Line regulation    | < 0.4 %, V <sub>IN</sub> > 3.3 V                                                                                             |                                                                     |

| NVCC_DRAM                                             | Voltage setpoint   | 1.35 V                                                                                                                       | Section 3.1.4                                                       |

|                                                       | Ripple             | < 20 mV                                                                                                                      |                                                                     |

|                                                       | Transient response | < 5%                                                                                                                         |                                                                     |

|                                                       | Load regulation    | < 0.4 %                                                                                                                      |                                                                     |

|                                                       | Line regulation    | < 0.4%, V <sub>IN</sub> > 3.3 V                                                                                              |                                                                     |

| Efficiency (each regulator at half of its rated load) |                    |                                                                                                                              | Section 3.1.1,<br>Section 3.1.2,<br>Section 3.1.3,<br>Section 3.1.4 |

| Efficiency (each regulator at its full rated load)    |                    | _                                                                                                                            | Section 3.1.1,<br>Section 3.1.2,<br>Section 3.1.3,<br>Section 3.1.4 |

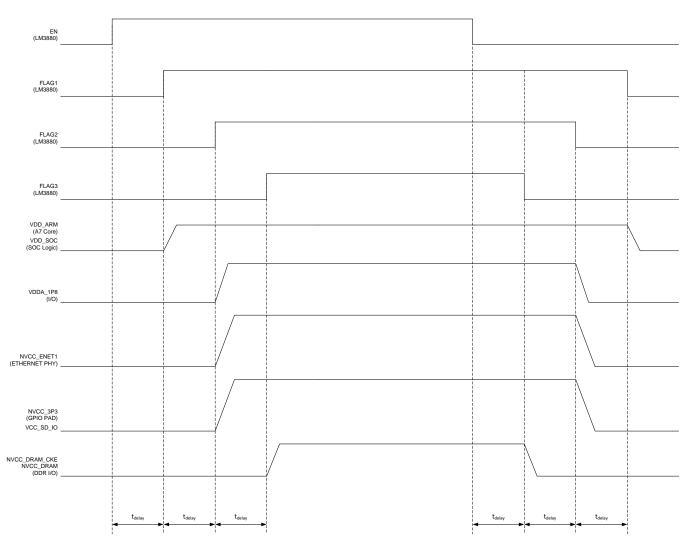

| Sequencing order (power up)                           |                    | <ol> <li>VDD_ARM and VDD_SOC;</li> <li>VDDA_1P8, NVCC_3P3, NVCC_SD_IO, and<br/>NVCC_ENET1;</li> <li>NVCC_DRAM_CKE</li> </ol> | Section 3.1.5                                                       |

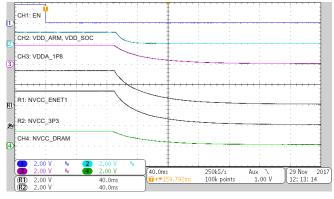

| Sequencing order (power down)                         |                    | <ol> <li>NVCC_DRAM_CKE;</li> <li>VDDA_1P8, NVCC_3P3, and NVCC_SD_IO;</li> <li>VDD_ARM and VDD_SOC</li> </ol>                 |                                                                     |

#### Table 1. Key System Specifications

www.ti.com

#### 2 System Overview

#### 2.1 Block Diagram

Figure 1. Block Diagram

### 2.2 Highlighted Products

#### 2.2.1 TLV62085

The TLV62085 is a 3-A, high-frequency, synchronous step-down converter optimized for small solution size and high efficiency. At medium to heavy loads, the converter operates in pulse-width modulation (PWM) mode and automatically enters power save mode operation at light load to maintain high efficiency over the entire load current range. Its DCS-Control<sup>™</sup> topology (**D**irect **C**ontrol with **S**eamless transition into power save mode) enables a very-fast transient response to regulate the output voltage during heavy load changes, while its high switching frequency enables the use of a small inductor and output capacitor.

#### 2.2.2 TLV62080, TLV62084A

The TLV6208x family of devices are small buck converters with few external components that enable costeffective solutions. The 1.2-A (TLV62080) and 2-A (TLV62084A) synchronous step-down converters provide high-efficiency over a wide output current range. At medium to heavy loads, the TLV6208x converters operate in PWM mode and automatically enter power save mode operation at light-load currents to maintain high efficiency over the entire load current range. With DCS-Control architecture, excellent load transient performance and output voltage regulation accuracy are achieved.

System Overview

#### www.ti.com

#### 2.2.3 LM3880

4

The LM3880 Simple Power Supply Sequencer offers the easiest method to control power-up sequencing and power-down sequencing of multiple independent voltage rails. The LM3880 contains a precision enable pin and three open-drain output flags. When the LM3880 is enabled, the three output flags sequentially release, after individual time delays, thus permitting the connected power supplies to start up. The output flags follow a reverse sequence during power down when the enable pin is pulled down.

#### 2.3 System Design Theory

The application processor power requirements are a function of the specific functionality used in a given application. In most cases, the current drawn by each rail is not known precisely during the design phase. Only gross estimates are available when the power supply is designed. For this reason, this reference design uses DC/DC converters that are high enough power to support the majority of i.MX7 applications, while still supplying a small solution size and high efficiency. Use 2-A converters to provide the 1.8-V and 3.3-V I/O rails and a 3-A converter for the common 1.1-V core and SoC rail. The output voltages of the converter are adjustable with external resistor feedback dividers.

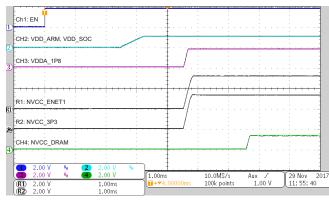

The i.MX7 application processor only requires a simple sequencing of the power rails. VDD SOC must be stable before NVDCC DRAM and NVDCC DRAM CKE start to ramp. For down sequencing, first NVCC\_DRAM and NVDCC\_DRAM\_CKE must be powered down before VDD\_SOC is disabled. Though no specific sequencing is required for the other rails, this reference design also applies a controlled sequencing of the other rails to reduce the inrush current drawn from the input source, as well as to provide a controlled system start-up. The LM3880-1AA Simple Sequencer starts VDD\_SOC and VDD\_ARM first; then VDD\_1P8, NVCC\_3P3 VCCA, and NVCC\_ENET1 second; and then finally, the 1.35-V converter (NVCC\_DRAM\_CKE and NVCC\_DRAM rail). This reference design uses the 1AA version of LM3880, which provides a sequencing power-up order of FLAG1, FLAG2, and FLAG3 with a delay time (t<sub>DELAY</sub>) of 10 ms. Power-up sequencing starts when the enable pin of the LM3880 device is pulled high and power-down sequencing starts when the enable pin is pulled low (see Figure 2). An external enable signal must be applied at jumper J12, such as from a microcontroller (MCU) or signal generator.

System Overview

#### 3 Hardware, Software, Testing Requirements and Test Results

To test this reference design, apply an input voltage (typically 3.6 V) to the J1 input connector. Apply an enable signal to jumper J12 with a signal generator to initiate the power-up sequencing of the output rails. For the high level, apply at least 1.4 V (maximum level is  $V_{IN}$ ); for the low level, apply less than 1.0 V.

#### 3.1 Testing and Results

This section includes the relevant test results to power the i.MX7 application processor. Unless otherwise noted, all testing was conducted with 3.6  $V_{IN}$  and at room temperature.

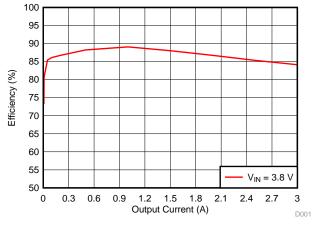

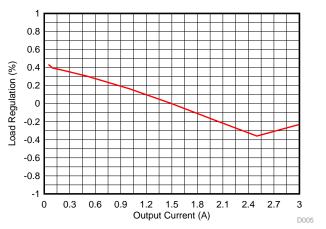

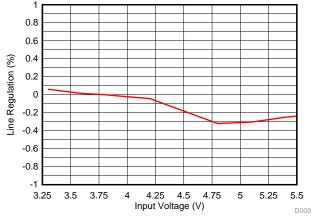

#### 3.1.1 VDD\_ARM, VDD\_SOC

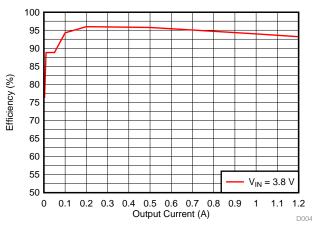

Figure 3. VDD\_ARM, VDD\_SOC Efficiency (3.8 V<sub>IN</sub>)

Figure 4. VDD\_ARM, VDD\_SOC Load Regulation (3.8 V<sub>IN</sub>)

Figure 5. VDD\_ARM, VDD\_SOC Line Regulation (3-A Load)

Small, Efficient, Flexible Power Supply Reference Design for NXP™ i.MX7

Series Application Processors

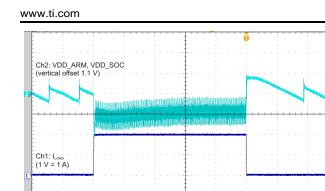

Figure 6. VDD\_ARM, VDD\_SOC Transient Response  $(V_{IN} = 3.8 \text{ V}, 10 \text{-mA to } 2 \text{-A Load Step})$

40.0µs

250MS/s 100k point:

130m\

29 Nov 2013 15: 25: 24

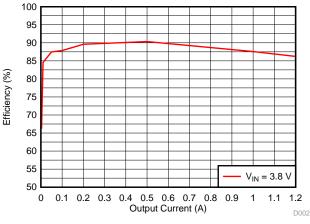

#### 3.1.2 VDDA\_1P8

Hardware, Software, Testing Requirements and Test Results

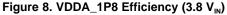

Figure 7. VDD\_ARM, VDD\_SOC Ripple (V<sub>IN</sub> = 3.8 V, 3-A Load)

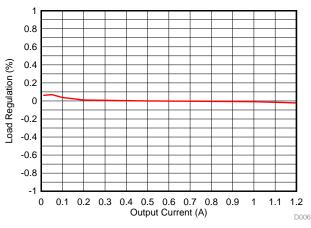

Figure 9. VDDA\_1P8 Load Regulation (3.8 V<sub>IN</sub>)

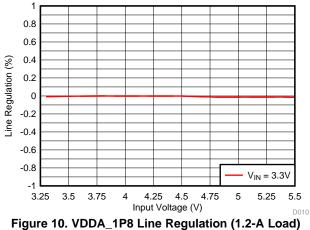

Hardware, Software, Testing Requirements and Test Results

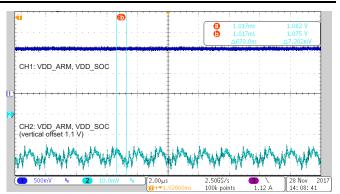

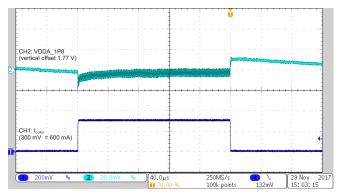

Figure 11. VDDA\_1P8 Transient Response (V<sub>IN</sub> = 3.8 V, 1-mA to 600-mA Load Step)

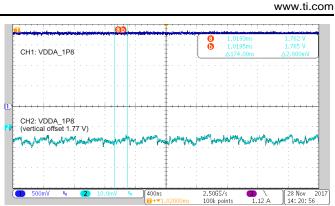

Figure 12. VDDA\_1P8 Ripple (V<sub>IN</sub> = 3.8 V, 1.2-A Load)

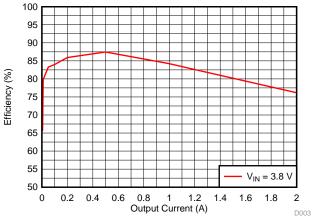

Figure 13. NVCC\_3P3 Efficiency (V<sub>IN</sub> = 3.8 V)

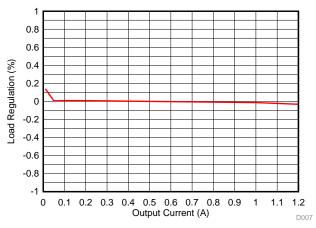

Figure 14. NVCC\_3P3 Load Regulation (V<sub>IN</sub> = 3.8 V)

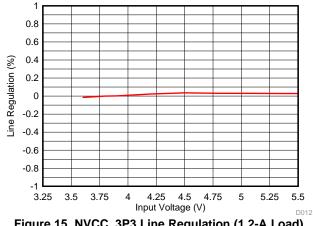

Figure 15. NVCC\_3P3 Line Regulation (1.2-A Load)

3.1.3

NVCC\_3P3

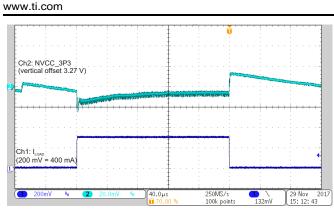

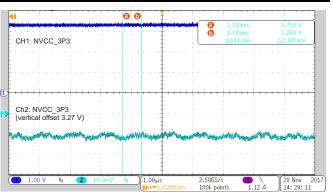

Figure 16. NVCC\_3P3 Transient Response ( $V_{IN} = 3.8 V$ , 1-mA to 600-mA Load Step)

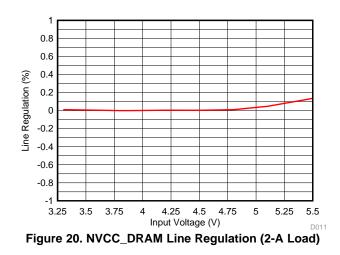

### 3.1.4 NVCC\_DRAM

Figure 18. NVCC\_DRAM Efficiency (V<sub>IN</sub> = 3.8 V)

#### Hardware, Software, Testing Requirements and Test Results

Figure 17. NVCC\_3P3 Ripple ( $V_{IN}$  = 3.8 V, 1.2-A Load)

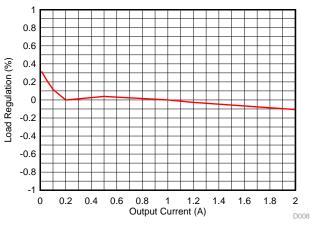

Figure 19. NVCC\_DRAM Load Regulation ( $V_{IN} = 3.8 V$ )

Hardware, Software, Testing Requirements and Test Results

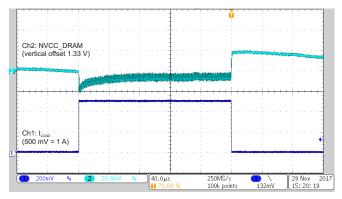

Figure 21. NVCC\_DRAM Transient Response ( $V_{IN}$  = 3.8 V, 1-mA to 1-A Load Step)

System Power Up and Power Down

3.1.5

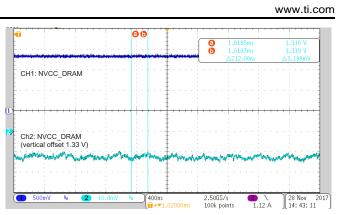

Figure 22. NVCC\_DRAM Ripple (V<sub>IN</sub> = 3.8 V, 2-A Load)

Figure 23. Power Up ( $V_{IN}$  = 3.8 V, No Load)

www.ti.com

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01416.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01416.

#### 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01416.

#### 4.4 Gerber Files

To download the Gerber files, see the design files at TIDA-01416.

#### 4.5 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01416.

#### 5 Related Documentation

- 1. NXP, i.MX 7Dual Family of Applications Processors Datasheet

- 2. Texas Instruments, *High Efficiency 3-A Step-Down Converterin 2-mm×2-mm VSON Package*

- 3. Texas Instruments, 1.2-A and 2-A High-Efficiency Step-Down Converter in 2-mm×2-mm WSON Package

- 4. Texas Instruments, Simple Power Sequencer

- 5. Texas Instruments, *High-efficiency, low-ripple DCS-Control™ offers seamless PWM/power-save transitions*

#### 5.1 Trademarks

DCS-Control is a trademark of Texas Instruments. NXP is a trademark of NXP Semiconductors.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated