## USING THE CONTINUOUS PARALLEL MODE WITH THE ADS7824 AND ADS7825

By Bonnie C. Baker

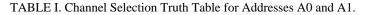

The ADS7824 and ADS7825 are 12-bit and 16-bit converters that have a four channel multiplexed front end. The channel selection on the analog input of these converters is programmable by way of the pins on the devices, A0 and A1 (see Table I). This feature provides the most flexibility by allowing the user to change to the preferred input channel on the fly. Additionally, the input channels can be cycled by utilizing the continuous mode of the converter. This mode is easily enabled by tying the CONTC pin high. In this mode, acquisition and conversions will take place continually, cycling through all four input channels without user intervention.

In the serial mode (PAR/ $\overline{SER}$  = LOW), the continuous mode (enabled with CONTC = HIGH) will cause the device to acquire and converter the input signal and cycle through all

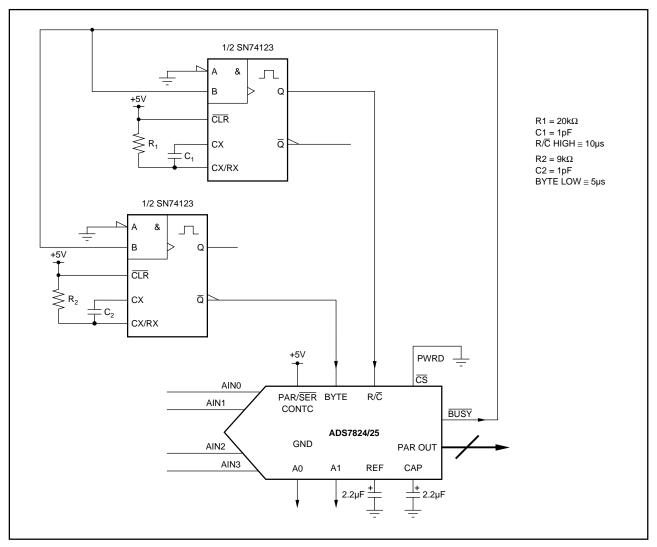

four channels continually as long as  $\overline{CS}$ ,  $R/\overline{C}$  and PWRD are LOW (see Table II). Selection as to which input channel will be accessed first is done with either the PWRD function or the CONTC pin. If PWRD is cycled, the first channel that will be acquired will be channel 0, AIN<sub>0</sub>. If CONTC is cycled, the register does not change and the current channel becomes the first in the sequence. When CONTC is HIGH, A0 and A1 address inputs become outputs. When BUSY rises at the end of a conversion, A0 and A1 will output the address of the channel that will be converted next. Additionally, data will be valid for the previous channel after BUSY rises. See Table II and Figure 1 for channel selection timing in the continuous, serial conversion mode.

| A0 | A1 | CONTC | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----|----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0  | 0  | 0     | Enables AIN <sub>0</sub> . A0 and A1 are configured as input pins and the user provides instructions to the device to determine which input will be accessed. This channel address is updated just before BUSY rises.                                                                                                                              |  |  |  |

| 0  | 1  | 0     | Enables AIN <sub>1</sub> . A0 and A1 are configured as input pins and the user provides instructions to the device to determine which input will be accessed. This channel address is updated just before BUSY rises.                                                                                                                              |  |  |  |

| 1  | 0  | 0     | Enables AIN <sub>2</sub> . A0 and A1 are configured as input pins and the user provides instructions to the device to determine which input will be accessed. This channel address is updated just before BUSY rises.                                                                                                                              |  |  |  |

| 1  | 1  | 0     | Enables AIN <sub>3</sub> . A0 and A1 are configured as input pins and the user provides instructions to the device to determine which input will be accessed. This channel address is updated just before BUSY rises.                                                                                                                              |  |  |  |

| 0  | 0  | 1     | Enables AIN <sub>0</sub> . A0 and A1 are configured as output pins. A0 and A1 cycle sequentially from one channel to the next as long as CONTC is HIGH. The channel that is being acquired or converted is output on these address lines. Data is valid for the pervious channel. These channels are updated when $\overline{\text{BUSY}}$ rises.  |  |  |  |

| 0  | 1  | 1     | Enables AIN <sub>1</sub> . A0 and A1 are configured as output pins. A0 and A1 cycle sequentially from one channel to the next as long as CONTC is HIGH. Then channel that is being acquired or converted is output on these address lines. Data is valid for the previous channel. These channels are updated when $\overline{\text{BUSY}}$ rises. |  |  |  |

| 1  | 0  | 1     | Enables AIN <sub>2</sub> . A0 and A1 are configured as output pins. A0 and A1 cycle sequentially from one channel to the next as long as CONTC is HIGH. The channel that is being acquired or converted is output on these address lines. Data is valid for the previous channel. These channels are updated when $\overline{\text{BUSY}}$ rises.  |  |  |  |

| 1  | 1  | 1     | Enables AIN <sub>3</sub> . A0 and A1 are configured as output pins. A0 and A1 cycle sequentially from one channel to the next as long as CONTC is HIGH. The channel that is being acquired or converted is output on these address lines. Data is valid for the previous channel. These channels are updated when BUSY rises.                      |  |  |  |

©1997 Burr-Brown Corporation

| CS           | R/C          | BUSY | PWRD | OPERATION                                                                                                                                                                    |  |

|--------------|--------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Х            | X            | Ŷ    | 0    | The end of conversion 'n' (when $\overline{\text{BUSY}}$ rises) increments the internal channel latches and outputs the channel address for conversion 'n + 1' on A0 and A1. |  |

| х            | х            | 0    | 0    | Conversion in process.                                                                                                                                                       |  |

| 0            | $\downarrow$ | 1    | 0    | Restarts continuous conversion process on next input channel.                                                                                                                |  |

| $\downarrow$ | 0            | 1    | 0    | Restarts continuous conversion process on next input channel.                                                                                                                |  |

| x            | X            | х    | 1    | All analog functions powered down. Conversion in process or initiated will yield meaningless data. Resets selected input channel for next conversion to AlN <sub>0</sub> .   |  |

| 0            | 0            | х    | 0    | Places the converter in the serial out, continuous mode (PAR/SER = low)                                                                                                      |  |

TABLE II. Truth Table for the Continuous Mode when the A/D Converter is in the Serial Output Mode (PAR/ $\overline{SER}$  = LOW). A0 and A1 become outputs in this mode. To remain in the continuous mode without interruption, CONTC = HIGH,  $\overline{CS}$  and  $R/\overline{C}$  = LOW.

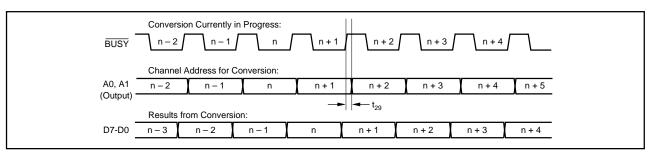

FIGURE 2. This Circuit can be Used to Place the ADS7824 or ADS7825 in the Continuous Mode if the Application Requires that these Devices be Configured for a Parallel Output.

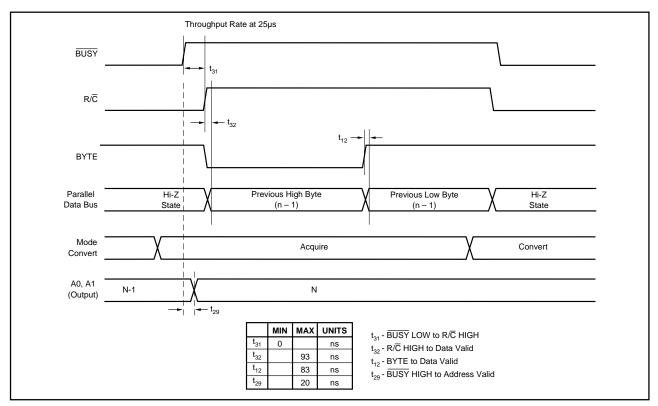

In the parallel mode (PAR/ $\overline{SER}$  = HIGH), the continuous mode (enabled with CONTC = HIGH) will cause the device to acquire and converter the input signal and cycle through all four channels continually as long as  $\overline{CS}$  and PWRD are LOW (see Table III). In contrast to the serial mode, the parallel output pins are in a high impedance setting unless  $R/\overline{C}$  is brought HIGH. Note that if  $R/\overline{C}$  is kept HIGH, the converter will not be in the continuous mode. Additionally, the BYTE pin controls the output byte. The BYTE pin must be toggled while  $\overline{\text{BUSY}}$  is HIGH if the total of 12 bits in the case of the ADS7824 and 16 bits in the case of the ADS7825 is required. Consequently, the continuous, parallel mode for these devices require some additional logic to toggle the  $R/\overline{C}$  and BYTE pin.

Figure 2 shows a circuit that can implement the continuous mode while these devices are in the parallel mode without

processor intervention. In this circuit, the ADS7824 (or ADS7825) is configured to operate in the continuous mode with CONTC HIGH, PAR/SER HIGH, and  $\overline{CS}$  LOW. On the rising edge of  $\overline{BUSY}$ ,  $R/\overline{C}$  is triggered high through a one shot, SN74123. This one shot stays high as dictated by the values of the resistor and capacitor, R1 and C1 and then falls. In this manner, the parallel outputs of the ADS7824/25 are taken out of their high impedance mode and the data from the previous conversion is available on the output pins. In order to access both the HIGH Byte and LOW Byte of the converted data, the other half of the dual, SN74123 is used to toggle the BYTE pin of the converter. Refer to Figure 3 for the timing details of this circuit.

As is with the serial continuous mode, the input channel selection is done with either the PWRD function or the CONTC pin. If PWRD is cycled, the first channel that will be acquired will be channel 0,  $AIN_0$ . If CONTC is cycled, the register does not change and the current channel becomes the first in the sequence. When CONTC is high, A0 and A1 address inputs become outputs. When  $\overline{BUSY}$  rises at the end of a conversion, A0 and A1 will output the address of the channel that will be converted next. Data will be valid for the previous channel after  $\overline{BUSY}$  rises. The address lines are updated when  $\overline{BUSY}$  rises. See Table III and Figure 3 for channel selection timing in the continuous, parallel conversion mode.

| CS | R/C          | BUSY | BYTE | PWRD | OPERATION                                                                                                                                                         |

|----|--------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0            | Ŷ    | Х    | 0    | The end of conversion 'n' (when BUSY rises) increments the internal channel latches and outputs the channel address for conversion 'n + 1' on A0 and A1.          |

| 0  | 0            | 0    | х    | 0    | Conversion in process.                                                                                                                                            |

| 0  | $\downarrow$ | 1    | Х    | 0    | Restarts continuous conversion process on next input channel.                                                                                                     |

| 0  | 1            | 1    | 1    | 0    | Disables Hi-Z mode at the parallel outputs and puts the MSB byte on the output pins.                                                                              |

| 0  | 1            | 1    | 0    | 0    | Disables Hi-Z mode at the parallel outputs and puts the LSB byte on the output pins.                                                                              |

| х  | x            | Х    | х    | 1    | All analog functions powered down. Conversion in process or initiated will yield meaningless data. Resets selected input channel for next conversion to $AIN_0$ . |

TABLE III. Truth Table for the Continuous Mode when the A/D Converter is in the Parallel Output Mode (PAR/ $\overline{SER}$  = HIGH, CONT = HIGH,  $\overline{CS}$  = LOW). A0 and A1 become outputs in this mode.

## FIGURE 3. Timing Diagram for Circuit Shown in Figure 2. In this diagram the byte control is arbitrary and the low byte can be acquired before the high byte without any consequences on operation.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated