Application Report SBAA159-December 2008

# Using the ADS1672 in Digital Filter Bypass Mode

Lijoy Philipose, Wern Koe, Tiak-Chean Tan

Data Acquisition Products

#### ABSTRACT

Data acquisition systems that must be very flexible and provide a high level of precision are often not economical to produce. Frequently, the only solution to designing such a system is to take the modulator output of a high-precision, delta-sigma ( $\Delta\Sigma$ ) data converter and marry it with programmable logic, such as a focal-plane grid array (FPGA). This paper discusses how to use the high-speed, multi-bit <u>ADS1672</u> from Texas Instruments in digital filter bypass mode.

#### Contents

| 1 | Introduction                   | 1 |

|---|--------------------------------|---|

| 2 | ADS1672 Bypass Mode Pinout     | 2 |

|   | Digital Interface Timing       |   |

|   | Error Cancellation Logic (ECL) |   |

|   | Application Test Results       |   |

|   | Conclusion                     |   |

#### List of Figures

| 1  | Flexible Data Acquisition System Block Diagram                                                    | 2 |

|----|---------------------------------------------------------------------------------------------------|---|

| 2  | Bypass Mode Pinout                                                                                | 2 |

| 3  | Modulator Data Retrieval Timing                                                                   | 4 |

| 4  | Hardware Connections                                                                              | 5 |

| 5  | Full System Block Diagram                                                                         | 5 |

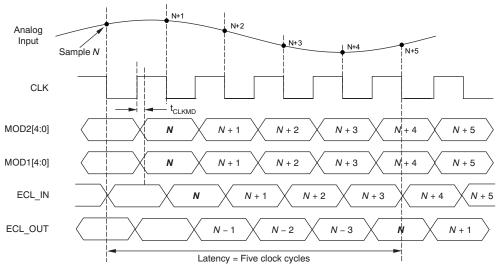

| 6  | Cycle Latency                                                                                     | 5 |

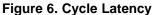

| 7  | Spectral Response of Modulator Output at f <sub>IN</sub> = 1 kHz, -0.5 dbFS                       | 6 |

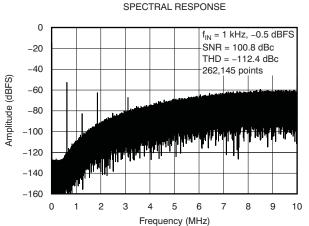

| 8  | Spectral Response of Modulator Output at f <sub>IN</sub> = 1 kHz, -6 dbFS                         | 6 |

| 9  | FFT After 312.5 kHz <i>Brick Wall</i> Filter at f <sub>IN</sub> = 1 kHz, –0.5 dbFS                | 6 |

| 10 | Enlarged View (8x) of FFT After 312.5 kHz Brick Wall Filter at f <sub>IN</sub> = 1 kHz, -0.5 dbFS | 6 |

| 11 | FFT After 312.5 kHz <i>Brick Wall</i> Filter at f <sub>IN</sub> = 1 kHz, –6 dbFS                  | 7 |

| 12 | Enlarged View (8x) of FFT After 312.5 kHz Brick Wall Filter at $f_{IN} = 1$ kHz, -6 dbFS          | 7 |

|    |                                                                                                   |   |

### 1 Introduction

The ADS1672 is a high-speed, high-precision analog-to-digital converter (ADC). This converter was built using advanced multi-bit delta-sigma architecture. The chopper-stabilized front end gives the converter low drift and low offset characteristics. The converter features two digital filters. The first filter (wide bandwidth) was designed to for ac, wide-bandwidth applications. The filter response provides very little passband ripple up to 305 kHz. The second filter (low latency) was designed for applications where low latency is required, but a flat passband transfer curve is not essential. Low-latency applications typically involve step signals and/or multiplexed analog channels.

Measurement and automated test systems must be able to measure a plethora of input signals. These signals can vary in signal amplitude as well as frequency content. Additionally, the time required to digitize these signals can vary. In the case of feedback systems, for instance, it is important that the cycle latency be as short as possible. Cycle latency is the period from when the converter starts to acquire the signal and the time it takes for an accurate representation of that signal to arrive at the output.

All trademarks are the property of their respective owners.

1

Data acquisition systems that require a great deal of flexibility are often configured to change the transfer curve of the data converter by varying the back-end digital filter. This back-end digital filter determines the group delay, conversion accuracy, and cycle latency of the converter.

The ADS1672 can be operated in digital filter bypass mode. In bypass mode, the onboard digital filters are shut down and the modulators outputs are directly connected to the pins of the converter. These output streams can be combined using error cancellation logic, and then fed into a custom filter configuration to achieve the desired filter response and system characteristics.

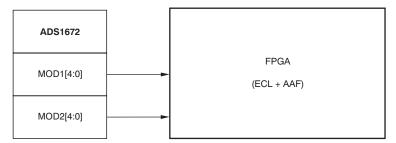

Figure 1 illustratees the concept of a flexible data acquisition system with the ADS1672 and an FPGA.

Figure 1. Flexible Data Acquisition System Block Diagram

# 2 ADS1672 Bypass Mode Pinout

In Figure 2, the ADS1672 operates in bypass mode at power-up with the pinout shown. The state of pins 14 through 17 sets the mode to either bypass mode or normal mode. If the pins are grounded, the part operates in normal mode. If all the pins are set to DVDD, the part runs in normal mode at power-up.

Using the ADS1672 in bypass mode re-assigns a total of 14 pins. The new pinout is shown in Figure 2. Shaded pins indicate a change to the pin configuration from the standard device pinout.

Figure 2. Bypass Mode Pinout

2

Table 1 provides a detailed description of the pin configuration for the ADS1672 in bypass mode.

| Pin      |                                                  |              |                                                                                                                      |  |  |

|----------|--------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| Name     | No.                                              | Input/Output | Description                                                                                                          |  |  |

| AVDD     | 1, 7, 11, 12,<br>53, 58                          | —            | Analog supply pins                                                                                                   |  |  |

| AGND     | 2, 3, 6, 9, 10,<br>54, 56, 57                    | _            | Analog ground                                                                                                        |  |  |

| AINN     | 4                                                | Input        | Negative analog input                                                                                                |  |  |

| AINP     | 5                                                | Input        | Positive analog input                                                                                                |  |  |

| RBIAS    | 8                                                | —            | Analog bias setting resistor                                                                                         |  |  |

| VCM      | 13                                               | _            | Terminal for external bypass capacitor connection to internal common-mode voltage. Connect 1-µF capacitor to ground. |  |  |

| DVDD     | 14, 15, 16, 17,<br>23, 24, 27, 34,<br>48, 49, 52 | _            | Digital supply pins                                                                                                  |  |  |

| DGND     | 18, 19, 20, 25,<br>26, 31, 47, 50,<br>51         | _            | Digital ground                                                                                                       |  |  |

| RSV2     | 21                                               | _            | Reserved pin. Short to DGND.                                                                                         |  |  |

| RSV1     | 22                                               | _            | Reserved pin. Short to DGND.                                                                                         |  |  |

| PDWN     | 28                                               | Input        | Power-down control; active low.                                                                                      |  |  |

| SCLK_SEL | 29                                               | Input        | Set to DGND.                                                                                                         |  |  |

| LVDS     | 30                                               | Input        | Set to DGND.                                                                                                         |  |  |

| MOD1[0]  | 32                                               | Output       | Modulator 1, bit 0; LSB.                                                                                             |  |  |

| MOD1[1]  | 33                                               | Output       | Modulator 1, bit 1                                                                                                   |  |  |

| MOD1[2]  | 35                                               | Output       | Modulator 1, bit 2                                                                                                   |  |  |

| MOD1[3]  | 36                                               | Output       | Modulator 1, bit 3                                                                                                   |  |  |

| MOD1[4]  | 37                                               | Output       | Modulator 1, bit 4; MSB.                                                                                             |  |  |

| CS       | 38                                               | -            | Leave floating.                                                                                                      |  |  |

| MOD2[0]  | 39                                               | Output       | Modulator 2, bit 0; LSB.                                                                                             |  |  |

| RSV3     | 40                                               |              | Reserved; this pin must be left floating. Do not connect or short to ground.                                         |  |  |

| SCLK     | 41                                               | _            | This pin must be left floating. Do not connect or short to ground.                                                   |  |  |

| SCLK     | 42                                               |              | This pin must be left floating. Do not connect or short to ground.                                                   |  |  |

| MOD2[1]  | 43                                               | Output       | Modulator 2, bit 1                                                                                                   |  |  |

| MOD2[2]  | 44                                               | Output       | Modulator 2, bit 2                                                                                                   |  |  |

| MOD2[3]  | 45                                               | Output       | Modulator 2, bit 3                                                                                                   |  |  |

| MOD2[4]  | 46                                               | Output       | Modulator 2, bit 4                                                                                                   |  |  |

| CLK      | 55                                               | Input        | Master clock input                                                                                                   |  |  |

| CAP1     | 59                                               | _            | Terminal for 1-µF external bypass capacitor                                                                          |  |  |

| VREFN    | 60, 61                                           | Input        | Negative reference voltage. Short to analog ground.                                                                  |  |  |

| CAP2     | 62                                               | —            | Terminal for 1-µF external bypass capacitor                                                                          |  |  |

| VREFP    | 63, 64                                           | Input        | Positive reference voltage                                                                                           |  |  |

# Table 1. ADS1672 Bypass Mode Pin Configurations

#### Digital Interface Timing

# 3 Digital Interface Timing

The advanced architecture of the ADS1672 consists of two modulators. Data from these two 5-bit modulators must be latched on the falling edge of every modulator (CLK) clock cycle. The raw data streams from both modulators must then be processed through error cancellation logic before being processed by the digital filter. This error cancellation logic generates a 7-bit representation of the input signal.

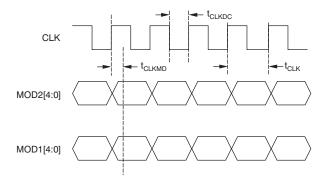

Figure 3 shows the modulator data retrieval timing sequence. Table 2 summarizes the timing requirements for this sequence.

Note: Chip select is tied low.

### Figure 3. Modulator Data Retrieval Timing

Proposed timing requirement conditions: At  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , AVDD = 5 V, DVDD = 3 V.

#### Table 2. Timing Requirements for Figure 3

| SYMBOL             | DESCRIPTION                                                | MIN  | TYP | MAX  | UNIT             |

|--------------------|------------------------------------------------------------|------|-----|------|------------------|

| t <sub>CLK</sub>   | CLK period (1/f <sub>CLK</sub> )                           | 50   |     |      | ns               |

| t <sub>CLKMD</sub> | CLK rising edge to Modulator 1 and Modulator 2 data valid. |      | 14  |      | ns               |

| t <sub>CLKDC</sub> | CLK pulse low width                                        | 0.45 |     | 0.56 | t <sub>CLK</sub> |

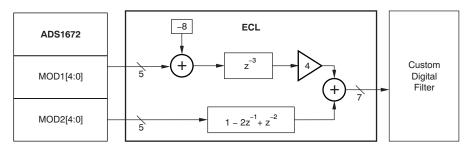

# 4 Error Cancellation Logic (ECL)

As noted earlier, the data output from the two 5-bit modulators must be processed through error cancellation logic. This error cancellation logic generates a 7-bit signed representation of the input signal. Modulator outputs are unsigned values.

Modulator 1 (MOD1) and Modulator 2 (MOD2) outputs must be combined to form a 10-bit digital word using Equation 1.

Digital Word =  $(MOD1 - 8) \times 4z^{-3} + MOD2 \times (1 - 2z^{-1} + z^{-2})$

(1)

Where:

- MOD1: 5-bit output from Modulator 1.

- MOD2: 5-bit output from Modulator 2.

# 5 Application Test Results

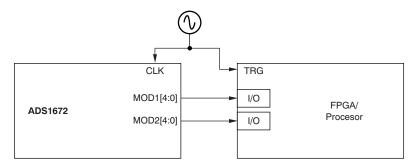

The hardware for this application can be configured as shown in Figure 4. The modulator (CLK) should be a clean square wave in order to achieve specified datasheet linearity. The output data from the modulator are available on every falling clock edge.

Figure 4. Hardware Connections

The processor (or FPGA) that captures the data must process the data through the error cancellation circuit. The output can then be post-processed, as Figure 5 shows.

Figure 5. Full System Block Diagram

The latency of this system is five clock cycles, as Figure 6 shows. The data are sampled on the falling clock edge and available at the modulator output one-half clock cycle later. This output sample *N* can be latched into the error correction logic on the falling edge. After the three clock delays through ECL, the digital representation of sample *N* is available.

#### Application Test Results

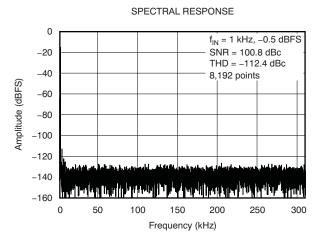

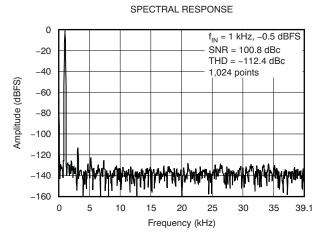

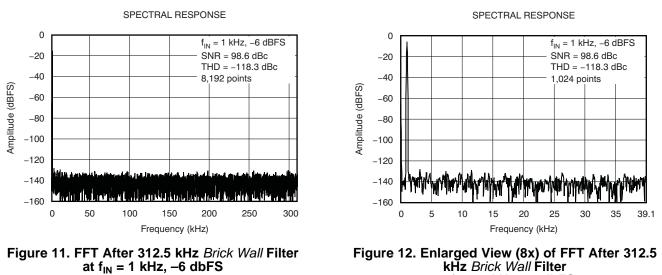

The data for the graphs shown in Figure 7 through Figure 12 were collected with the ADS1672 in bypass mode. The back-end implementation of the error cancellation logic and a brick wall filter (SNR BW of 312.5 kHz) was implemented on a PC. The tones shown in Figure 7 are tones from the chopper front end. These tones are sufficiently attenuated by the on-chip digital filters and thus do not alias back into the baseband.

Figure 7. Spectral Response of Modulator Output at  $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dbFS}$

SPECTRAL RESPONSE

Figure 8. Spectral Response of Modulator Output at  $f_{IN} = 1$  kHz, -6 dbFS

Figure 9. FFT After 312.5 kHz Brick Wall Filter at  $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dbFS}$

Figure 10. Enlarged View (8x) of FFT After 312.5 kHz Brick Wall Filter at  $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dbFS}$

# at f<sub>IN</sub> = 1 kHz, –6 dbFS

# 6 Conclusion

Although not shown or discussed here, dc performance of the ADS1672 ADC is also entirely a result of the analog portion of the chip (that is, the modulators). The digital filters of the ADC help to reduce the overall noise and attenuate out-of-band noise. It does not improve or degrade the linearity, offset error, gain error, and other critical specifications of the chip. Achieving specified datasheet performance is possible with careful analog circuit layout and proper digital filter design.

Using the ADS1672 in bypass mode is a very attractive solution for measurement and automated test systems that must measure an abundance of input signals and respond appropriately.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated