# AFE77xx Latte GUI

### 1 Trademarks

### 2 Introduction

The AFE77xx devices are a family of high-performance, multichannel transceivers that integrate four direct up-conversion transmitter chains, four direct down-conversion receiver chains, and two wideband RF sampling digitizing auxiliary chains (feedback paths).

Latte is a Python-based tool that can be used to generate the register commands to configure AFE77xx in a desired (and supported) mode. These register commands, saved in text format and referred to as configuration (or config) files in the rest of the document, can then be used by the host (FPGA or ASIC) in the application board to bring up the AFE77xx.

Latte can also be used to configure the AFE77xx evaluation module (EVM) when such an EVM is connected to the PC. Latte runs in simulation mode when no EVM is connected.

### 2.1 Hardware and Software Requirements

A PC with a minimum of 8GB RAM and a processor such as Intel i5 is required. The recommended RAM is 16GB or higher, as the execution time greatly depends on it. Latte is compatible with Windows 7 and 10.

### 2.2 Installation

Users can download the latest version of Latte from TI's mySecure website, or their Box account. The installer also includes the .INI files for the TSW14J5x board typically used to interface with TI EVMs.

### 2.3 Outline of This Document

- Section 3 gives an overview of Latte, including a quick start guide to run it in a pre-defined mode.

- Section 4 lists the various parameters used in Latte to define the AFE77xx configuration mode.

- Section 5 describes the GPIO configurablity in AFE77xx.

- Section 6 shows the recommended flow to modify a script and run it in Latte to generate a config file.

- Section 7 describes the various built-in functions in Latte.

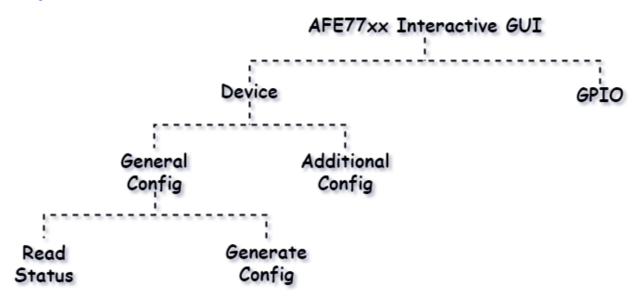

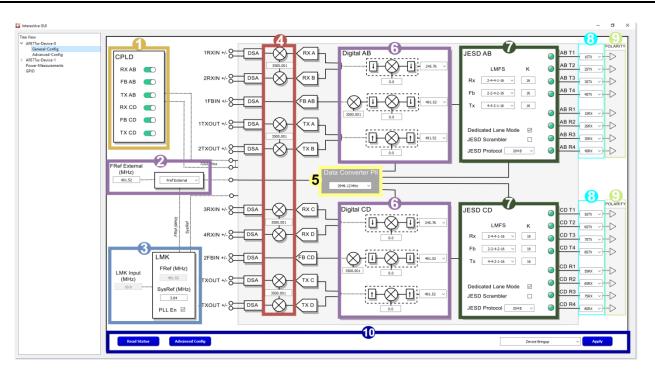

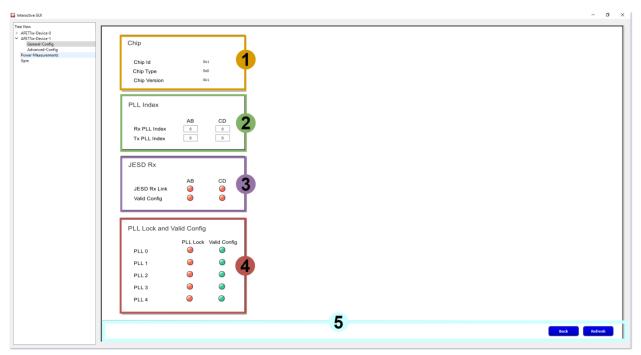

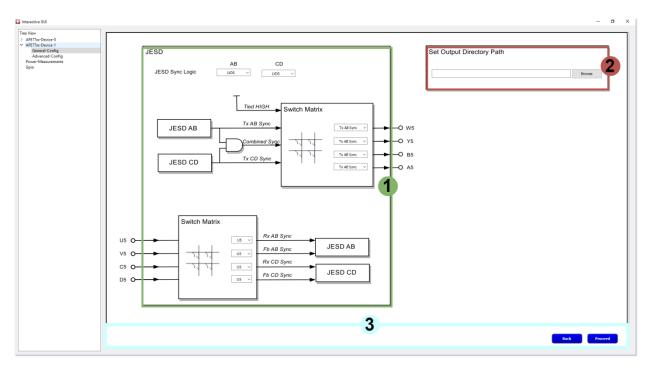

- Section 8 shows the configurablity through iGUI.

### 3 Latte Overview

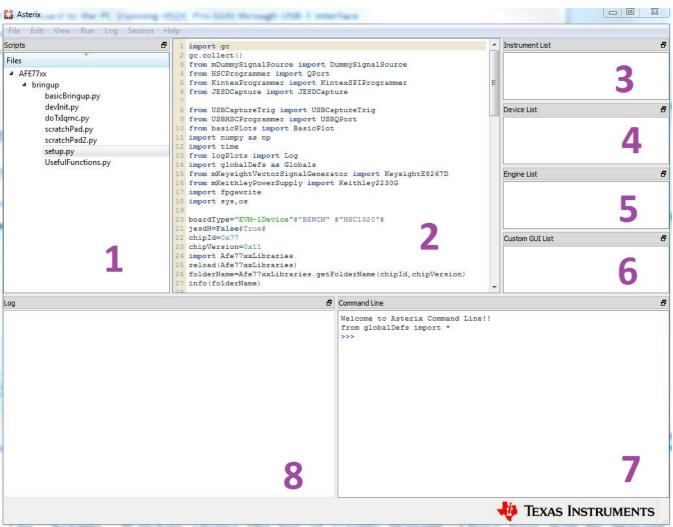

Launch Latte GUI from the desktop shortcut or from All Programs->Texas Instruments. It will display as shown in Figure 1.

1

Latte Overview

Figure 1. Latte User Interface

The Latte GUI is split into eight windows (labeled 1 through 8) that have the following functionalities:

- Window 1: This window (also called *Scripts*) shows the list of Python scripts that can be executed. Users can find the pre-defined scripts to configure AFE77xx in this window.

- Window 2: This window (also called *Editor*) shows the code in the script currently selected, and can be used to edit and save the code.

- Window 3 to 6: These windows get updated as the scripts are run, and are for informational purposes.

- Window 7: This window (also called *Command Line*) is used to enter and run individual commands or functions, usually after the initial configuration of the device. Examples of such functionalities include changing LO frequency, DSA settings, and so forth.

- Window 8: This window (also called *Log*) displays messages during script execution to display the current status, errors, and so forth. It is useful for monitoring execution status.

### 3.1 Useful Latte Short-Cuts:

Users may find these short-cuts helpful in carrying out routine operations in Latte.

- 1. **Run Script file**: A script can be executed by selecting the file in the Scripts window (1) and then pressing F5 (or by selecting *Run* and *Buffer* in the menu bar).

- 2. **Run portion of a script**: Part of a script can be run by selecting the lines in the Editor window (2) and then pressing F7 (or by selecting *Run* and *Run Selection* in the menu bar).

2

- 3. **Stop Execution**: Current execution of a script can be stopped by pressing F10 (or by selecting *Run* and *Stop* in the menu bar).

- 4. **Clear Session**: A working session in can be cleared by pressing Ctrl+T (or by selecting *Session* and *Clear Session* in the menu bar). This is equivalent to a restart of the Latte GUI and is required after events such as disconnecting or power-cycling the EVM, which require re-establishing the USB connection.

### 3.2 Latte File Structure and Names

The installation files are stored in a folder named Latte in the \Documents\Texas Instruments\ directory of each user. The files are organized in two folders named "lib" and "projects".

The "lib" folder includes the python scripts that are compiled and run to configure the device. Files and scripts are organized with relevant names. AFE77xx specific files can be found in "...\Afe77xxLibraries\AFE77xxLibraryPG1P1". For example, a file named "mAfeParameters.py" contains the configurable parameters and their typical values.

The "projects" folder contains executable Python scripts that are displayed in the GUI (Window 1 in Figure 1). A few relevant scripts and their purposes are listed below:

- "setup.py": This script checks for connected hardware (such as the AFE77xx EVM) and establishes the USB connection if possible. When no hardware is connected, it enters simulation mode.

- "devInit.py": This script loads the device register map, libraries, and iGUI. iGUI is alternative way to set the device configuration mode through a graphical interface instead of the text-based scripts.

- "basicBringup\_y.py": This script includes the parameters and the necessary function calls to configure the device. The "y" in the suffix indicates the configuration mode.

- "Useful\_functions.py": This script includes a collection of Python functions useful for dynamic configuration, such as changing the TX DSA.

### 3.3 Running Latte

This section shows the steps to use Latte to get a desired output.

### 3.3.1 Establish Connection (setup.py)

In the Scripts window, select *setup.py* and press F5 to run the program. Review the Log window for any errors or messages. When no hardware is connected, a message about Latte being run in Simulation Mode is displayed.

When an EVM is powered and connected to the PC, this step should result in no errors or warnings.

### 3.3.2 Compile Libraries (devlnit.py)

In the Scripts window, select *devInit.py* and press F5 to run the program. Check the Log window for status. No errors or warnings are expected. Close or minimize the iGUI window.

### 3.3.3 Device Configuration

This step actually configures the device or can be used to generate and save the register commands in text format. In the Scripts window, select *basicBringup\_y.py* and press F5 to run the program. For example, running "basicBringup\_Case-1.py" configures the device in the mode shown in Table 1.

| Case | RX                                                                                                              | тх                                                                                                              | FB                                                                                                 | CLK                                                    |

|------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 1    | <ul> <li>245.76 Msps</li> <li>24410</li> <li>SerDes=9830.4<br/>Mbps</li> <li>PLL0</li> <li>LO=3500 M</li> </ul> | <ul> <li>491.52 Msps</li> <li>44210</li> <li>SerDes=9830.4<br/>Mbps</li> <li>PLL0</li> <li>LO=3500 M</li> </ul> | <ul> <li>491.52 Msps</li> <li>22210</li> <li>SerDes=9830.4<br/>Mbps</li> <li>NCO=3500 M</li> </ul> | <ul> <li>FS=2949.12 M</li> <li>REF=491.52 M</li> </ul> |

| Table 1 | 1. Example | Use Case-1 |

|---------|------------|------------|

|---------|------------|------------|

This completes the steps required to generate the config file and EVM configuration (when connected).

### 4 Latte Parameters

The basicBringup script executed to configure the device consists of various parameters to set the device configuration mode. These parameters, categorized according to the functionalities they address are described in this section.

### 4.1 System Parameters

System parameters that apply to the general operating conditions of the device are shown in Table 2

- Format: sysParams.<parameter> = "value"

- Example: sysParams.FRef = 491.52

| Parameter              | Description, Type, and Typical Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Analog Signal Chain Pa | irameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| FRef                   | Reference frequency to the AFE PLLs. <ul> <li>Type, Unit: Floating number, MHz</li> <li>Typical value: 491.52</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Fs                     | Sampling rate of data converters in RX, TX,and FB. <ul> <li>Type, Unit: Floating number, MHz</li> <li>Typical value: 2949.12</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| halfRateModeRx         | Sets RX ADC sampling Rate to half of Fs. <ul> <li>Type: True/False</li> <li>Typical value: False</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| halfRateModeFb         | Sets FB ADC sampling Rate to half of Fs. <ul> <li>Type: True/False</li> <li>Typical value: False</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| halfRateModeTx         | Sets TX DAC sampling Rate to half of Fs. <ul> <li>Type: True/False</li> <li>Typical value: False</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| enableFbCd             | Enables FB2 when set to True <ul> <li>Typical value: True</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| mode2t2r               | <ul> <li>Configures mode for TDD enable pins.</li> <li>0: Common pin is used for TDD control. That is, one pin for 4TX, one pin for 4RX,and one pin for 2FB.</li> <li>1: AB and CD TDDs are enabled through different pins.</li> <li>2: AB: TDD, CD: FDD</li> <li>3: AB: FDD, CD: TDD</li> <li>Note that if this is non-zero when the pllMuxMode is in the following, some power saving mechanisms are not enabled, resulting in few 100 mW extra of power consumption.</li> <li>0: 4T4R Mode with PLL0 as Master</li> <li>1: 4T4R Mode with PLL2 as Master</li> <li>2: 4T4R FDD Mode</li> <li>Typical value: 0</li> </ul> |  |

| pllMuxModes            | <ul> <li>Sets PLL and LO Distribution mode.</li> <li>0: 4T4R Mode with PLL0 as Master</li> <li>1: 4T4R Mode with PLL2 as Master</li> <li>2: 4T4R FDD Mode (PLL0 for TX and PLL2 for RX)</li> <li>3: 2*2T2R FDD Mode: PLL0 TX 1 and 2, PLL2 TX 3 and 4, PLL3 RX 1 and 2, PLL4 RX 3 and 4</li> <li>4: 2T2R FDD - TDD Mode: PLL0 TX 1 and 2, PLL3 RX 1 and 2, PLL2 RX/TX 3 and 4</li> <li>Typical value: 0</li> </ul>                                                                                                                                                                                                         |  |

#### **Table 2. System Parameters**

| Parameter                    | Description, Type, and Typical Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Signal Chain Paramete |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| pllLo                        | Sets carrier (LO) frequencies for relevant PLLs in the following order: [PLL0, PLL1, PLL2, PLL3,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •                            | PLL4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | <ul> <li>PLL1 must be set to the same value as Fs, as the data converter clock is sourced from<br/>PLL1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | Type, Unit: Floating number, MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | • Typical value: [3500, 2949.12, 4500.5, 2600.0, 2100.0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| usePIIExternalLoClock        | Sets External Clock feed mode for AFE77xx pins [1EXTLOIN, 2EXTLOIN].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              | <ul> <li>The external clock fed into 1EXTLOIN is routed to PLL2, and is referred to as TDD Clock.<br/>The external clock fed into 2EXTLOIN is routed to PLL0, and is referred to as FDD Clock.<br/>Note that two times the carrier (LO) frequency must be input to the pins.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                              | True: Enables external clock feed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | <ul> <li>False: Disables external clock feed. Internal PLL(s) used.</li> <li>Typical value: [False False]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IECD204B/C and CarDoo Dar    | Typical value: [False,False]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                              | ancers<br>E77xx are partioned into two cores where each core services a 2TX_2RX_1FB transceiver chain.<br>TX1 and 2,and FB1 is referred to as Core-0.The core servicing RX3 and 4, TX3 and 4,and FB2 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LMFSHdRx                     | JESD mode for RX in the following order: [RX1 and 2, RX3 and 4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                              | Type, Unit: String     Typical and a file 444 off the 444 off |

|                              | • Typical value: ["24410", "24410"]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LMFSHdFb                     | <ul> <li>JESD mode for RX in the following order: [FB1, FB2]</li> <li>Type, Unit: String</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | <ul> <li>Typical value: ["22210", "22210"]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LMFSHdTx                     | JESD mode for TX in the following order: [TX1 and 2, TX3 and 4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                              | Type, Unit: String                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | • Typical value: ["44210","44210"]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| systemMode                   | In TDD mode operation, it can be assumed that RX and FB channels are not enabled concurrently. Therefore, the SerDes lanes carrying the respective digital outputs can be shared between the two. This parameter allows configurablity of lane sharing for [FB1,FB2]. In FDD mode, it is assumed that the RX ADC output and FB ADC output are on dedicated (non-shared) SerDes lanes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | 1: FDD (non-shared or dedicated)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                              | <ul> <li>2: TDD (shared)</li> <li>Typical value: [1,1]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                              | For dedicated lanes in TDD mode, set this parameter to FDD (1), followed by True for the parameter "dedicatedLaneMode".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| dedicatedLaneMode            | This parameter along with "systemMode" configures SerDes lane sharing mode for [FB1,FB2] in TDD mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | True: Dedicated lanes for RX and FB if "systemMode" is set to FDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                              | <ul> <li>False: Shared lanes for RX and FB if "systemMode" is set to TDD.</li> <li>Typical value: [True,True]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| iesdProtocol                 | Sets JESD204 protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | • 0: JESD204B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |