# Application Brief How to Tune the S-Parameters of Your Analog Front-End Signal Chain

# TEXAS INSTRUMENTS

#### Leaphar Castro, Shreenidhi Patil

Wide-bandwidth data-acquisition systems (for example, oscilloscopes and active probes) use an analog frontend (AFE) signal chain to capture high-frequency signals and fast-transient pulses. The key characteristics of a wide-band DAQ AFE include:

- Wide -3 dB bandwidth to measure a wide-frequency range of signals

- High-input impedance mode to prevent loading of the measured signals

- Low-noise to detect low-magnitude signals

- · Superior distortion performance to maintain signal fidelity

When looking across the industry today one can find a wide variety of amplifiers and buffers which support bandwidths greater than 1 GHz, however, these bandwidths refer to the small-signal bandwidth ( < 100 mV<sub>PP</sub>) and are not suitable to be used in an AFE, designed for large signals (> 1 V<sub>PP</sub>) in magnitude.

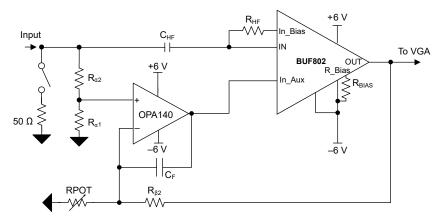

The BUF802 device is an open-loop, unity-gain buffer with a JFET-input stage that offers low-noise, highimpedance buffering for data acquisition system (DAQ) front-ends. The BUF802 supports DC to 3.1 GHz of bandwidth for a 1  $V_{PP}$  signal while offering excellent distortion and noise performance across the frequency range. The BUF802 can be used in a composite loop circuit with a precision amplifier as shown in Figure 1 for applications where wide-bandwidth and high-precision is desired.

Figure 1. Generic Composite Loop Front-End Stage with OPA140 and BUF802

This article explains tuning of the S-parameters, to achieve a flat frequency response and impedance matching for your front-end design.

## **Composite Loop Circuits**

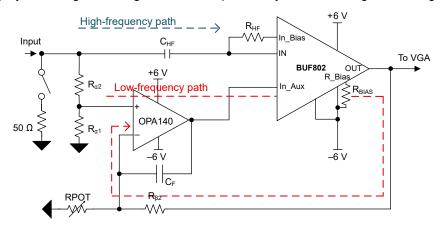

A composite loop circuit interleaves two different and often complementary sub-circuits to create a single seamless circuit block whose resulting performance is a combination of each sub-circuits benefits. The composite loop in Figure 2 splits the input signal into low frequency and high frequency components, taking each signal component to the output through two different circuits (transfer functions) and recombines them to reproduce a net output signal. The Low-frequency path gives the net transfer function good DC precision and the BUF802 (High-frequency path) allows the net transfer function to achieve a wide-bandwidth. One of the challenges of the circuit in Figure 2 is to smoothly interleave the two paths to achieve wide-bandwidth as well as good DC precision. Any mismatch in the transfer functions of the two paths will lead to a discontinuity in the

net transfer function frequency response resulting in a loss of signal fidelity. The BUF802 uses an innovative architecture to simplify the design challenges discussed previously of interleaving the two signal paths.

Figure 2. Composite Loop Low- and High-frequency Paths

#### **S-Parameters Fundamentals**

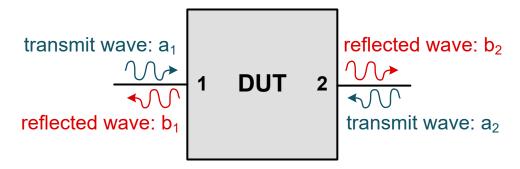

Scattering parameters or S-parameters provide a framework for describing networks based on the ratio of input transmission signals and reflected signals as shown in Figure 3.  $S_{11}$  represents ratio of the power reflected from port 1 ( $b_1/a_1$ , while  $a_2=0$ ).  $S_{21}$  represents ratio of the power transferred from port 1 to port 2 ( $b_2/a_1$ , while  $a_2=0$ ). For a unidirectional device such as a buffer (with port 1 as the input and port 2 as the output),  $S_{11}$  is the input port voltage reflection coefficient describing the level of input-impedance matching while  $S_{21}$  is the forward voltage gain and describes the frequency response.

Figure 3. Two-Port Network Wave Quantities

S-parameters are usually represented as a function of frequency. For a detailed analysis of S-parameters check out the blog *So, What are S-Parameters Anyway*?

## Tuning Circuit for the S21

To achieve the desired  $S_{21}$  across the frequency range the following conditions need to be met:

- Reduction of Peaking and Achieving Wide-Bandwidth

- Achieving Smooth Transition Between Low- to High-frequency

#### Reduction of Peaking and Achieving Wide-Bandwidth

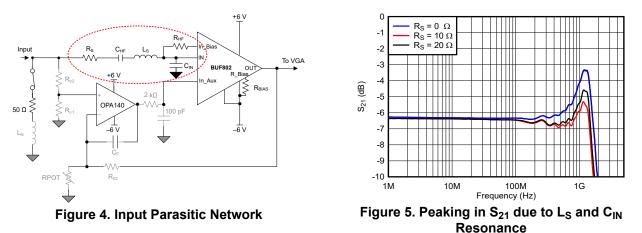

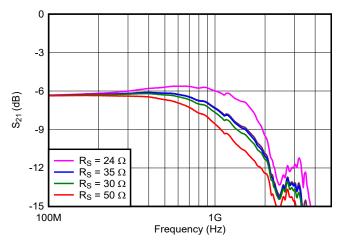

Figure 4 shows a composite loop circuit with input parasitics caused by the PCB and the DUT (BUF802). The parasitic inductance of the PCB trace ( $L_S$ ) can interact with the input capacitance of the BUF802 ( $C_{IN}$ ) to create a resonant LC circuit resulting in a peaked frequency response as shown in Figure 5. To reduce  $L_S$ , minimize the trace length from the input port to the BUF802s input. Figure 5 demonstrates the effect of a long trace on S<sub>21</sub>.

The peaking due to the resonance between  $L_S$  and  $C_{IN}$  can be dampened by the insertion of a series dampening resistor  $R_S$  as shown in Figure 4. Besides helping in dampening  $S_{21}$  peaking,  $R_S$  also helps with improvement of  $S_{11}$ . The exact math behind improvement of  $S_{11}$  is discussed in *Tuning of the*  $S_{11}$  *Parameter*.

The series input capacitor  $C_{HF}$  forms a voltage divider with  $C_{IN}$  reducing the gain of High-frequency path. It is therefore important to make  $C_{HF} >> C_{IN}$  to ensure the voltage divider does not attenuate the incoming AC signals.

The BUF802 can achieve a -3 dB bandwidth of 3.1-GHz for 1 V<sub>PP</sub> signals. The addition of R<sub>S</sub> to reduce S<sub>21</sub> peaking also reduces the bandwidth due to the addition of the RC pole caused by R<sub>S</sub> and C<sub>IN</sub>. This effect is seen in Figure 6.

Figure 6. S<sub>21</sub> Input Response with Varying R<sub>S</sub>

Table 1 summarizes the previous points.

| Increasing R <sub>S</sub>                      | Decreasing R <sub>S</sub>                   |

|------------------------------------------------|---------------------------------------------|

| Protects BUF802 against transients             | Increases bandwidth                         |

| Reduces peaking of S <sub>21</sub>             | Improves S <sub>11</sub> at lower frequency |

| Improves S <sub>11</sub> at higher frequencies | Reduces output noise                        |

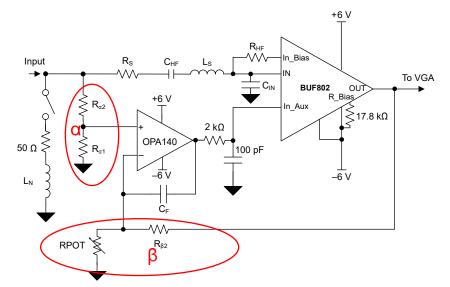

#### Achieving a Smooth Transition Between the Low- and High-Frequency Regions

The BUF802 can be used as a standalone buffer, Buffer Mode (BF Mode), or in a composite loop with a precision amplifier. Composite Loop Mode (CL Mode), helps to achieve both DC precision and wide, large-signal bandwidth. Operating the BUF802 in CL Mode with a precision amplifier requires the S21 responses (Gain) of the two different sub-circuits to be matched to maintain a smooth transition between the low-frequency and high-frequency response. A smooth transition can be achieved by adhering to the following two conditions:

- 1.  $\alpha/\beta = G$  (where  $\alpha = R_{\alpha 2} / (R_{\alpha 2} + R_{\alpha 1})$ , 1 / $\beta = 1 + (R_{\beta 2} / RPOT)$  as shown in Figure 7 and G = DC Gain of BUF802)

- 2. High-frequency response pole  $(f_{HF}) \le low-frequency pole (f_{LF})$

Figure 7.  $\alpha$  and  $\beta$  Resistor Network

For the first condition the low-frequency region is determined solely by the precision circuit. The incoming signal is divided down in amplitude by the ratio  $\alpha$  and is further gained up by 1/ $\beta$ , by the precision amplifier. Therefore, in the low-frequency region:

$$S_{21}$$

(at low-frequency) =  $\alpha * 1/\beta$  (1)

The Gain (G) can be found in the BUF802 data sheet and is typically 0.96 V/V.

(2)

To maintain a constant S<sub>21</sub> across frequency make **G** =  $\alpha/\beta$  by adjusting the value of RPOT.

The high-frequency pole of the BUF802 ( $f_{HF}$ ) path is created by  $C_{HF}$  and  $R_{HF}$  as is shown in Equation 3. The low-frequency pole ( $f_{LF}$ ) of the precision amplifier path is a function of the Gain Bandwidth Product (GBW) of the precision amplifier, the auxiliary path gain ( $G_{AUX}$ ) and the parasitic input capacitance of the BUF802 and is shown in Equation 4.

$$f_{HF} = 1/(2 \times \pi \times R_{HF} \times C_{HF})$$

(3)

$$f_{LF} = GBW \text{ (precision amplifier)} \times G_{AUX} \times \beta$$

(4)

The composite loop transition region should be designed so that the high-frequency pole ( $f_{HF}$ ) falls at a much lower frequency than the low-frequency pole ( $f_{LF}$ ). This ensures a sufficient overlap in the crossover frequency region and simplifies the complex transfer function into simple poles and zeros.

$C_F = C_{INPA} * (g R_{\alpha 1}/R_{\beta 2}-1)$

(5)

Application Brief

where  $C_{INPA}$  is the common mode input capacitance of the precision amplifier.

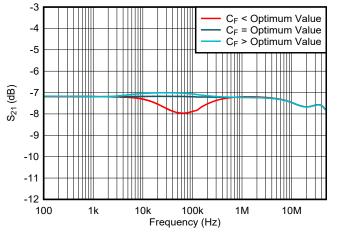

Figure 8 shows the effect of  $C_F$  tuning for its three different values.

Figure 8. Tuning Output Response with Different C<sub>F</sub> Value

Refer to section 9.2.1.2 in the BUF802 data sheet for the design procedure of a 1-GHz AFE using the previous equations.

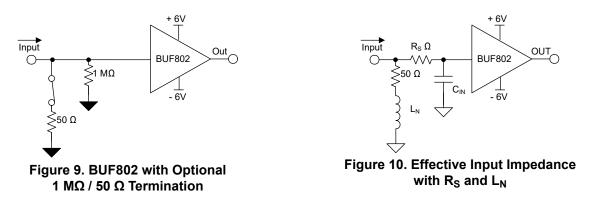

# Tuning Circuit for the Desired S<sub>11</sub>

Impedance matching is important to reduce reflections and preserve signal integrity. An S<sub>11</sub> better than -15 dB across the frequency of interest is considered an acceptable target spec. While a 50- $\Omega$  termination helps achieve the desired S<sub>11</sub>, it is important to have a high input impedance option to measure a signal without loading the previous driving stage. Hence, data acquisition systems can have a selectable 50- $\Omega$  input and 1-M $\Omega$  input termination option. The JFET-input stage of the BUF802 offers G- $\Omega$ 's of input impedance and can therefore be terminated with an external 1 M $\Omega$  resistor without affecting performance. If a 50  $\Omega$  termination is required it can be switched in via a relay as shown in Figure 9. The BUF802 therefore has the flexibility to be used in both 1-M $\Omega$  and 50- $\Omega$  terminated systems.

While it is possible to mount an exact 50- $\Omega$  termination to achieve the resistance at the input of the front-end composite loop circuit, the parasitic capacitance of the BUF802 (C<sub>IN</sub>) appears in parallel with the 50- $\Omega$  resistance resulting in a non-ideal termination across frequency.

The parasitic input capacitance of the BUF802 ( $C_{IN}$ ) is 2.4 pF. The input impedance of the BUF802 at a particular frequency ( $X_{CF}$ ) can be calculated using the formula:

$$X_{CF} = 1/(2\pi * f * 2.4 \text{ pF})$$

(6)

Therefore, the net input impedance seen by the signal will be:

X<sub>CF</sub> || 50 Ω

For example, at f = 1 GHz,  $X_{CF}$  is equal to 66.3  $\Omega$ . Therefore, the net input impedance seen by the signal is 66.3  $\Omega \parallel 50 \Omega = 28.5 \Omega$ .

The addition of  $R_S$  (to reduce  $S_{21}$  peaking), and, the addition of a series termination inductor ( $L_N$ ) (see Figure 10) results in a net input impedance as shown in Equation 8.

Net input impedance =

$$(50 \ \Omega + X_L) \parallel (R_S + X_{CF})$$

(8)

Where  $X_L = 2\pi * f * L_N$

With f = 1 GHz,  $R_s$  = 30  $\Omega$ ,  $L_N$  = 6.8 nH,  $C_{IN}$  = 2.4 pF and using Equation 8.

Input impedance =  $(50 \Omega + 42.7 \Omega) || (30 \Omega + 66.3 \Omega) \approx 48 \Omega$ .

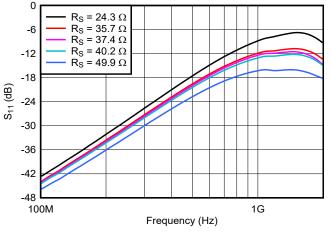

While  $R_S$  can be increased to bring the input impedance to an exact 50  $\Omega$ , we are limited by the maximum  $R_S$  value as discussed in Table 1. Figure 11, shows  $S_{11}$  vs frequency for different values of  $R_S$ .

Figure 11. S<sub>11</sub> with Varying R<sub>S</sub>

#### **Additional Information**

- For more details on discrete implementation design challenges and how the BUF802 alleviates these problems, read the *Simplify Analog Front-End Designs with Hi-Z Buffers* blog post.

- BUF802 TINA-TI / SPICE model.

- The Flexible 3.2-GSPS Multi-Channel AFE Reference Design for DSOs, Radar and 5G Wireless Test Systems illustrates the performance of the BUF802 in a composite loop AFE design with measurement analysis.

- For more information on how to set up the EVM, check out the BUF802EVM Video.

EXAS

TRUMENTS

(7)

(9)

www.ti.com

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated