# **PGA308**

# **User's Guide**

Literature Number: SBOU069B June 2009–Revised January 2012

# Contents

| 1 | PGA  | 308                                                                           | . 9 |

|---|------|-------------------------------------------------------------------------------|-----|

|   | 1.1  | Overview                                                                      | 10  |

|   |      | 1.1.1 Sensor Error Adjustment Range                                           | 11  |

|   | 1.2  | Related Documentation from Texas Instruments                                  | 12  |

|   | 1.3  | If You Need Assistance                                                        | 12  |

|   | 1.4  | Information About Cautions and Warnings                                       | 12  |

|   | 1.5  | FCC Warning                                                                   | 12  |

| 2 | Func | tional Description                                                            | 13  |

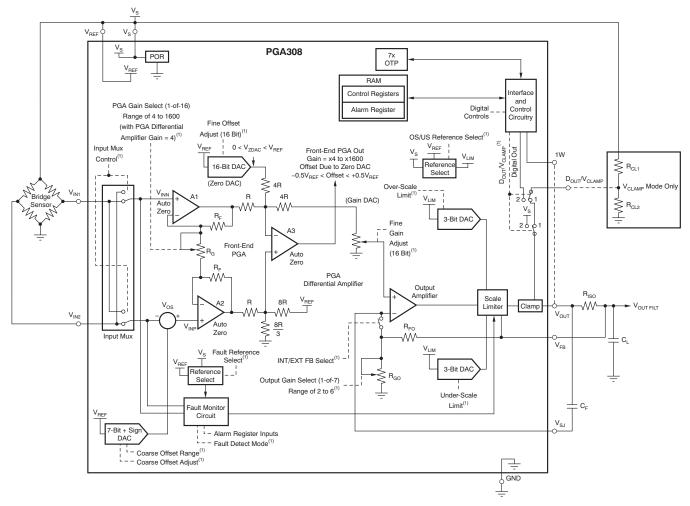

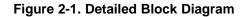

|   | 2.1  | Block Diagram                                                                 | 14  |

|   | 2.2  | Amplification Signal Path                                                     | 15  |

|   | 2.3  | Coarse and Fine Offset Adjustment                                             | 15  |

|   | 2.4  | Voltage Reference                                                             | 15  |

|   | 2.5  | Fault Monitor Circuit: Sensor Fault Detection (also see and )                 | 15  |

|   | 2.6  | Over-Scale and Under-Scale Limits                                             | 16  |

|   | 2.7  | V <sub>CLAMP</sub> Pin                                                        | 16  |

|   | 2.8  | Digital Interface: One-Wire Program Protocol                                  | 16  |

|   | 2.9  | Timeout on the One-Wire Interface                                             | 16  |

|   | 2.10 | Power-On Sequence of the PGA308                                               | 17  |

|   | 2.11 | One-Wire Operation with 1W Connected to $V_{\mbox{\scriptsize OUT}}$          | 17  |

|   | 2.12 | OTP Memory Banks                                                              | 18  |

| 3 | Anal | og Architecture                                                               | 19  |

|   | 3.1  | Gain Scaling                                                                  |     |

|   |      | 3.1.1 PGA308 Transfer Function                                                |     |

|   | 3.2  | Offset Scaling                                                                |     |

|   | 3.3  | Zero DAC Circuit Range                                                        |     |

|   |      | 3.3.1 Complete Scaling Example                                                |     |

|   | 3.4  | Output Amplifier                                                              |     |

|   | 3.5  | Over-Scale and Under-Scale Limits                                             |     |

|   | 3.6  | Fault Monitor Circuitry                                                       |     |

|   | 3.7  | D <sub>out</sub> /V <sub>clamp</sub> Pin                                      |     |

|   | 3.8  | System Budget for Over-Scale, Under-Scale, Linear Output, and Fault Detection |     |

|   | 3.9  | V <sub>REF</sub> Pin                                                          |     |

|   | 3.10 | General AC Considerations                                                     |     |

| 4 |      | led Digital Description                                                       |     |

|   | 4.1  | Memory Structure                                                              | 52  |

|   | 4.2  | OTP Memory Section                                                            | 53  |

|   | 4.3  |                                                                               |     |

|   | 4.4  | Digital Interface                                                             |     |

|   | 4.5  | One-Wire Interface Timeout                                                    | 56  |

|   | 4.6  | <u> </u>                                                                      | 56  |

| 5 |      | ating Modes                                                                   |     |

|   | 5.1  | Overview                                                                      |     |

|   | 5.2  | Common Applications                                                           |     |

|   |      | 5.2.1 Four-Terminal Module: Detailed Discussion                               | 60  |

3

| www.ti | i.com |

|--------|-------|

|--------|-------|

|       | 5.3    | One-Wire Write Mode, One-Wire Read Mode                                   | 64  |

|-------|--------|---------------------------------------------------------------------------|-----|

|       | 5.4    | OTP Program Mode                                                          | 66  |

|       | 5.5    | Standalone Mode                                                           | 67  |

|       | 5.6    | 1W Connected to V <sub>OUT</sub> Program Mode, Virtual Software Lock Mode | 70  |

|       | 5.7    | Virtual Software Lock Mode                                                | 71  |

|       | 5.8    | Software Lock Mode                                                        | 72  |

|       | 5.9    | Shutdown Mode                                                             | 74  |

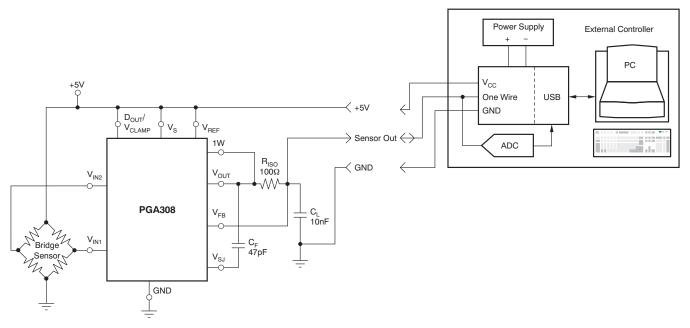

| 6     | Appli  | cations                                                                   | 75  |

|       | 6.1    | Typical Application Circuits                                              | 76  |

| 7     | Detail | ed Register Descriptions                                                  | 79  |

|       | 7.1    | Memory Structure and Register Locations                                   | 80  |

|       | 7.2    | Final Test Bank [OTP] Register                                            | 82  |

|       |        | 7.2.1 Final Test Bank [OTP] Register Overview                             | 82  |

|       |        | 7.2.2 Final Test Bank [OTP] Register Details                              | 82  |

|       | 7.3    | User Bank X [OTP] Register                                                | 86  |

|       |        | 7.3.1 User Bank X [OTP] Register Overview                                 | 86  |

|       |        | 7.3.2 User Bank X [OTP] Register Details                                  | 87  |

|       | 7.4    | [OTP AND RAM] Registers                                                   | 88  |

|       |        | 7.4.1 [OTP and RAM] Register Overview                                     | 88  |

|       |        | 7.4.2 [OTP and RAM] Register Details                                      | 88  |

|       | 7.5    | [RAM] Register                                                            | 97  |

|       |        | 7.5.1 [RAM] Register Overview                                             | 97  |

|       |        | 7.5.2 [RAM] Register Details                                              | 98  |

| Revis | ion Hi | story                                                                     | 103 |

## List of Figures

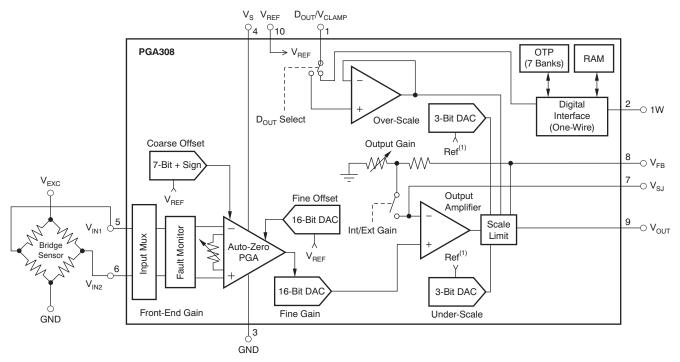

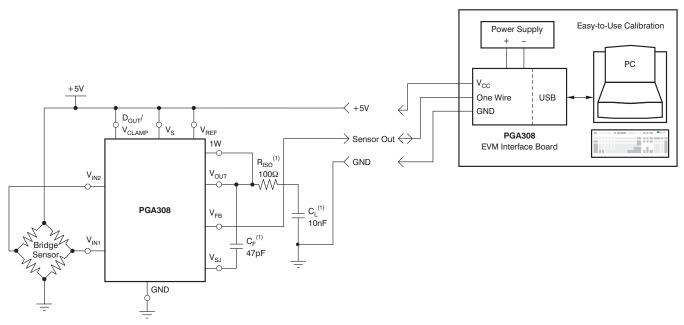

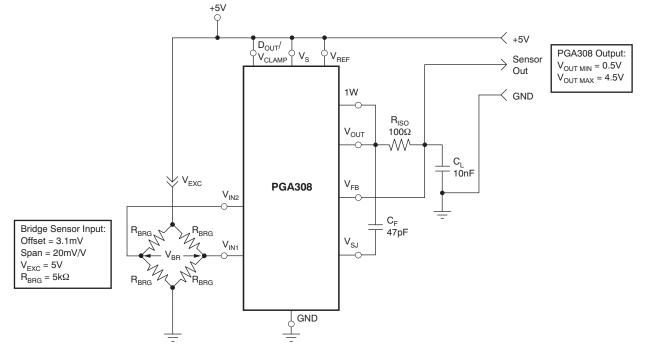

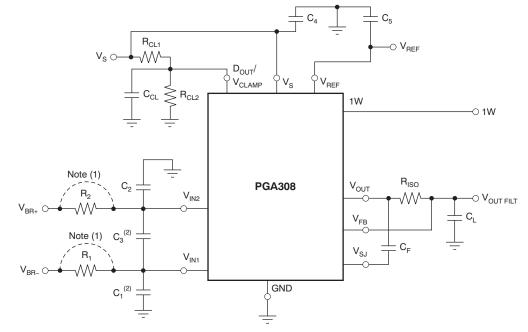

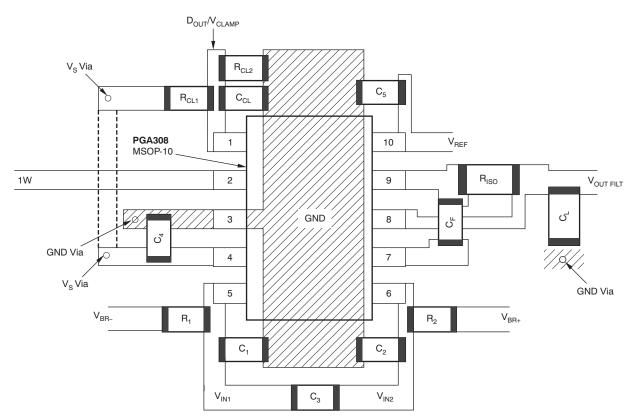

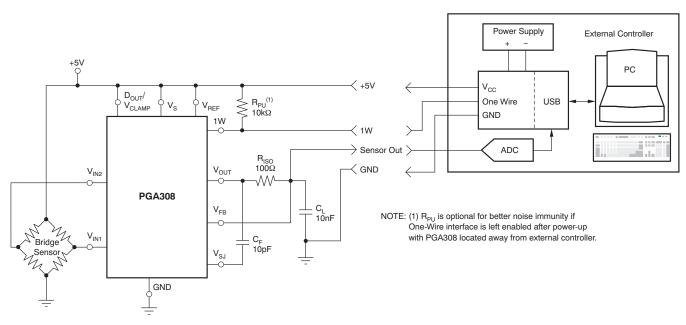

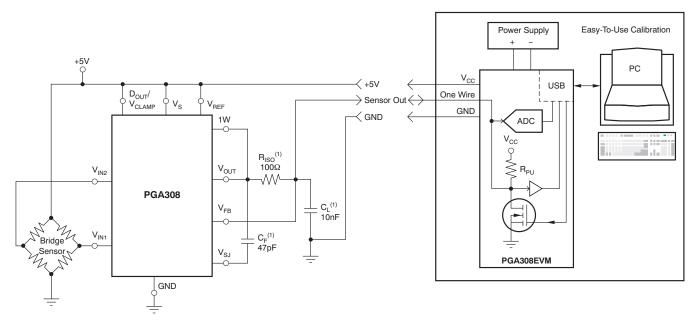

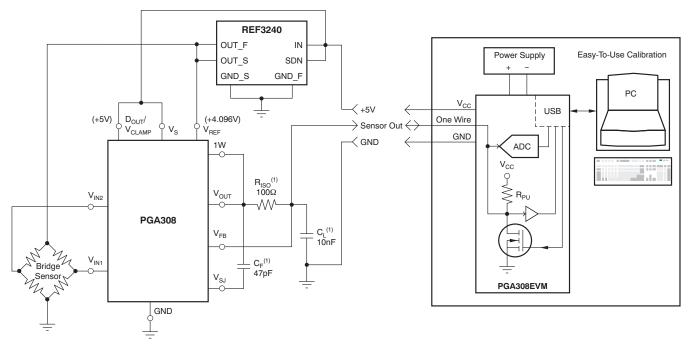

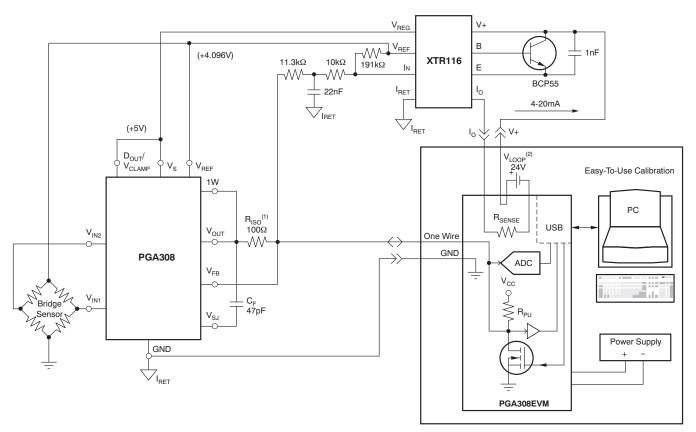

| 1-2.       PGA308, Evaluation Module, and Bridge Sensor Connections       11         2-1.       Detailed Block Diagram.       14         14.       PGA308 Gain Blocks       20         2-2.       Front-End PGA Cain: Internal Node Calculations.       21         2-3.       Fine Gain Adjust and Output Gain Select.       22         2-4.       Coarse offset Adjust Polarity       24         2-5.       Zero DAC Circuit Range.       26         3-7.       Complete Scaling Example Application Circuit       27         3-8.       Output Amplifier Viagre Extemal Feedback Resistors Rol Ext and Reso Ext       36         3-10.       Output Amplifier Viagre Extemal Feedback Resistors Rol Ext and Reso Ext       36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         2-7.       Fault Monitor Comparators.       39         3-13.       Bridge Sensor Configuration without Temperature Sense.       41         3-14.       Bridge Tault Example Bottom Bridge Temperature Sense.       41         3-17.       DarwV <sub>exam</sub> Function       43         3-18.       Bridge Sensor Configuration without Temperature Sense.       41         3-17.       DarwV <sub>exam</sub> Function       43         3-17.       DarwV <sub>exam</sub> Function       44                                                                                                                                                      | 1-1.  | PGA308 in a Typical Bridge Sensor Application                                                                          | 10              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------|-----------------|

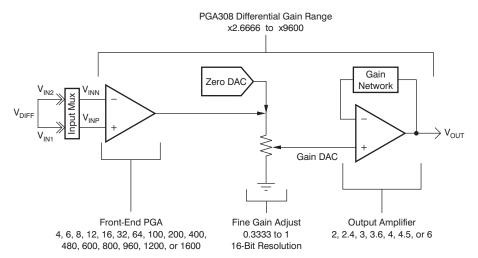

| 3-1.       PGA308 Gain Blocks       20         3-2.       Front-End PGA Gain: Internal Node Calculations       21         3-3.       Fine Gain Adjust and Output Gain Select       22         3-4.       Coarse Offset Adjust Polarity       24         2-5.       Carso DAC Circuit Range       26         3-7.       Complete Scaling Example Application Circuit       27         3-8.       Output Amplifier In a Common Three-Terminal Sensor Application       34         9.       Output Amplifier Ing External Feedback Resistors R <sub>0.6.EXT</sub> and R <sub>0.0.EXT</sub> 36         3-10.       Output Amplifier Ing External Feedback Resistors R <sub>0.6.EXT</sub> 36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         12.       Fault Monitor Comparators       39         3-13.       Bridge Sensor Configuration without Temperature Sense.       40         3-14.       Bridge Sensor Configuration with Temperature Sense.       41         3-15.       Bridge Sensor Configuration with Temperature Sense.       41         3-16.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       D <sub>0m</sub> /V <sub>C.Axe</sub> Function       43         3-18.       Bridge Sensor Configuration Schematic: AC Considerations       49         3-20.       PGA308 A                                                                                                                | 1-2.  | PGA308, Evaluation Module, and Bridge Sensor Connections                                                               | 11              |

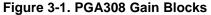

| 3-2.       Front-End PGA Gain: Internal Node Calculations.       21         3-3.       Fine Gain Adjust and Output Gain Select.       22         3-4.       Coarse offset Adjust And Output Gain Select.       24         3-5.       Coarse and Fine Offset Adjust.       24         3-6.       Zero DAC Circuit Range.       26         3-7.       Complete Scaling Example Application Circuit.       27         3-7.       Output Amplifier In a Common Three-Terminal Sensor Application       34         3-9.       Output Amplifier Using External Feedback Resistors R <sub>10 Ext</sub> and R <sub>50 Ext</sub> .       36         3-10.       Output Amplifier Minimum Gain at Low Supply       36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators.       39         3-13.       Bridge Sensor Configuration with Temperature Sense.       41         3-15.       Bridge Sensor Configuration with Temperature Sense.       41         3-16.       Pault Example: Bottom Bridge Temperature Sense.       41         3-17.       D <sub>ev</sub> /V <sub>cow</sub> F function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       49                                                                                                      | 2-1.  | Detailed Block Diagram                                                                                                 | 14              |

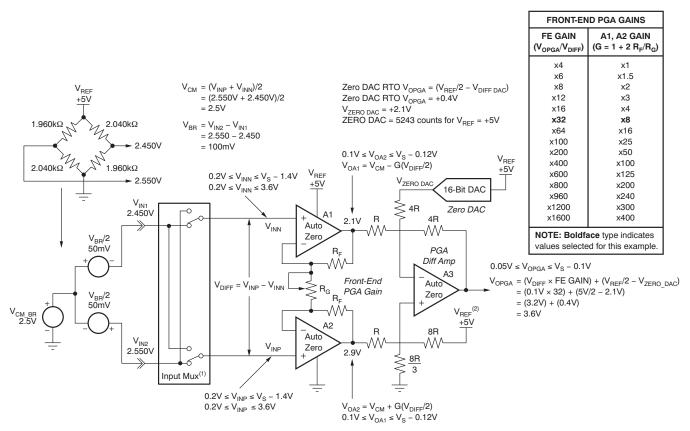

| 3-3.       Fine Gain Adjust and Output Gain Select.       22         3-4.       Coarse Offset Adjust.       24         3-5.       Coarse and Fine Offset Adjust.       25         3-6.       Zero DAC Circuit Range.       26         3-7.       Complete Scaling Example Application Circuit.       27         3-9.       Output Amplifier In Common Three-Terminal Sensor Application       34         3-9.       Output Amplifier Minimum Gain at Low Supply       36         3-10.       Output Amplifier Minimum Gain at Low Supply       36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators       39         3-13.       Bridge Sensor Configuration with Temperature Sense       40         3-14.       Bridge Sensor Configuration with Temperature Sense       41         3-15.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       D <sub>Qur</sub> /V <sub>cutup</sub> Function.       44         3-18.       Bridge Sansor Configuration with temperature Sense.       41         3-17.       D <sub>Qur</sub> /V <sub>cutup</sub> Function.       42         3-18.       Fault Example Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations <td>3-1.</td> <td>PGA308 Gain Blocks</td> <td>20</td>                                                           | 3-1.  | PGA308 Gain Blocks                                                                                                     | 20              |

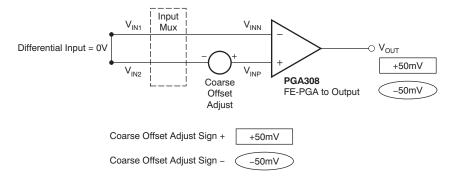

| 3-4.         Coarse Offset Adjust Polarity         24           3-5.         Carse and Fine Offset Adjust.         25           3-6.         Zero DAC Circuit Range.         26           3-7.         Complete Scaling Example Application Circuit         27           3-8.         Output Amplifier Using External Feedback Resistors R <sub>ro Exr</sub> and R <sub>ao Exr</sub> .         36           3-10.         Output Amplifier Minimum Gain at Low Supply         36           3-11.         Over-Scale and Under-Scale Limit Circuit         37           3-12.         Fault Monitor Comparators         39           3-13.         Bridge Sensor Configuration without Temperature Sense.         40           3-14.         Bridge Sensor Configuration with Temperature Sense.         41           3-15.         Bridge Fault Example: Bottom Bridge Temperature Sense.         41           3-16.         Fault Monitor Logic and Fault Level Selection.         43           3-17.         Dour/Vecume Function         43           3-18.         System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.         47           3-19.         PGA308 Application Schematic: AC Considerations         48           3-20.         PGA308 Application PCB Layout: AC Considerations         48           3-19.         PGA308 Monoute <td>3-2.</td> <td>Front-End PGA Gain: Internal Node Calculations</td> <td>21</td> | 3-2.  | Front-End PGA Gain: Internal Node Calculations                                                                         | 21              |

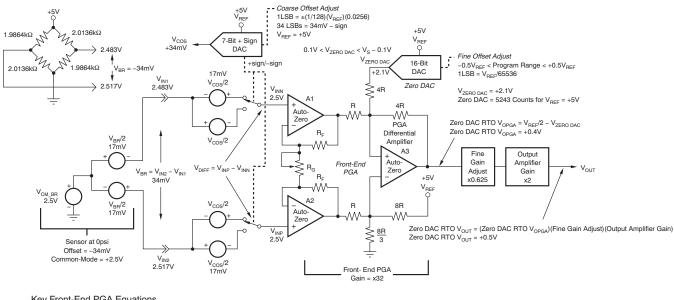

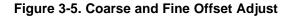

| 3-5.       Coarse and Fine Offset Adjust.       25         3-6.       Zero DAC Circuit Range.       26         3-7.       Complete Scaling Example Application Circuit.       27         3-8.       Output Amplifier in a Common Three-Terminal Sensor Application.       34         3-9.       Output Amplifier in a Common Three-Terminal Sensor Application.       36         3-10.       Output Amplifier Minimum Gain at Low Supply.       36         3-11.       Over Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators.       39         3-13.       Bridge Sensor Configuration without Temperature Sense.       40         3-14.       Bridge Sensor Configuration without Temperature Sense.       41         3-15.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       Dour/VcitAmp Fluction       44         418.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations.       48         3-20.       PGA308 Application Schematic: AC Considerations       49         4-1.       PGA308 Momory Structure.       52         4-2.       One-Wire Protocol Timing Diagram.       55         5-3.       PGA308                                                                                                                                                       | 3-3.  | Fine Gain Adjust and Output Gain Select                                                                                | 22              |

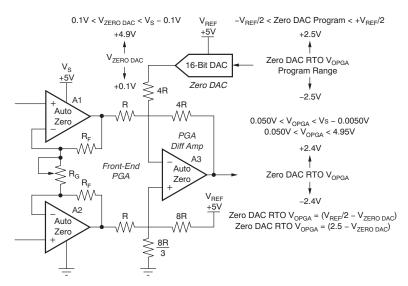

| 3-6.         Zero DAC Circuit Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-4.  | Coarse Offset Adjust Polarity                                                                                          | 24              |

| 3-7.       Complete Scaling Example Application Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-5.  | Coarse and Fine Offset Adjust                                                                                          | 25              |

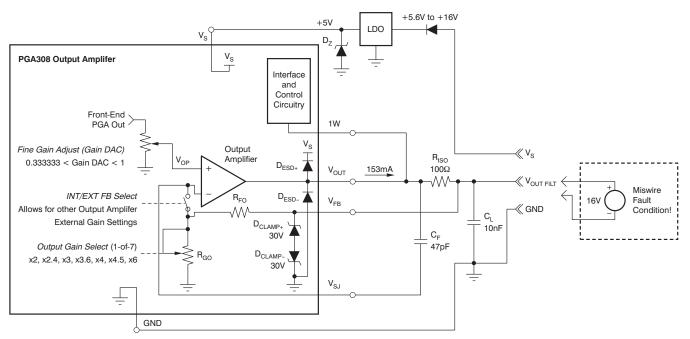

| 3-8.       Output Amplifier I a Common Three-Terminal Sensor Application       34         3-9.       Output Amplifier Using External Feedback Resistors R <sub>FG Ext</sub> and R <sub>GO Ext</sub> .       36         3-10.       Output Amplifier Minimum Gain at Low Supply       36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators       39         3-13.       Bridge Sensor Configuration without Temperature Sense.       40         3-14.       Bridge Sensor Configuration without Temperature Sense.       41         3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense.       42         3-16.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       Dour/Vecume Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application PCB Layout: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Command Byte       55         4-2.       One-Wire Trotocol Timing Diagram       56         5-3.       PGA308 Module       58         5-4.       Typical PGA308 Module       58         5-5.       One-Wire Ti                                                                                                                                   | 3-6.  | Zero DAC Circuit Range                                                                                                 | 26              |

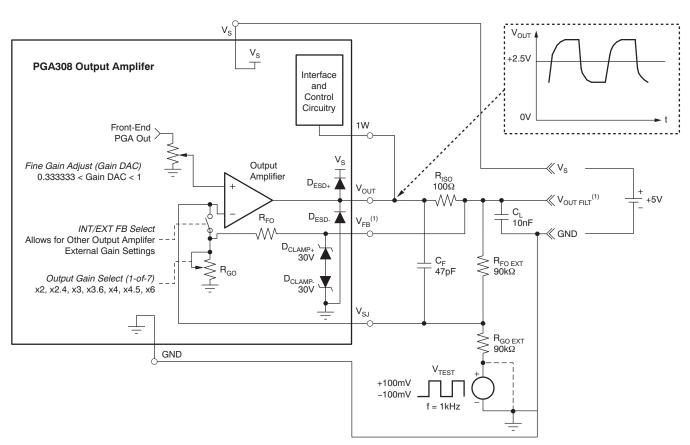

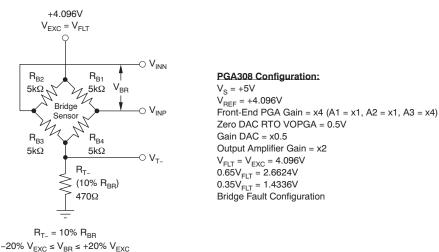

| 3-9.       Output Amplifier Using External Feedback Resistors R <sub>TO EXT</sub> and R <sub>GO EXT</sub> .       36         3-10.       Output Amplifier Minimum Gain at Low Supply       36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators       39         3-13.       Bridge Sensor Configuration with Temperature Sense       40         3-14.       Bridge Sensor Configuration with Temperature Sense       41         3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense       42         3-17.       D <sub>OUT</sub> /V <sub>CLMB</sub> Function       43         3-17.       D <sub>OUT</sub> /V <sub>CLMB</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       49         4-1       PGA308 Application Schematic: AC Considerations       49         4-1       PGA308 Application PCB Layout: AC Considerations       55         4-2.       One-Wire Protocol Timing Diagram       56         5-3.       PGA308 Application Boddet       55         5-4.       Typical PGA308 Module       59         5-5.       One-Wire Timing Diagram       56         5-6.       Pin 1W Circuit Protection Logic Levels <td>3-7.</td> <td>Complete Scaling Example Application Circuit</td> <td>27</td>             | 3-7.  | Complete Scaling Example Application Circuit                                                                           | 27              |

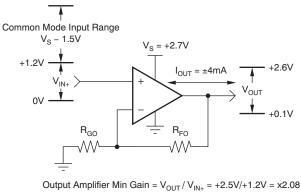

| 3-10.       Output Amplifier Minimum Gain at Low Supply       36         3-11.       Over-Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators       39         3-13.       Bridge Sensor Configuration with Temperature Sense       40         3-14.       Bridge Sensor Configuration with Temperature Sense       41         3-15.       Bridge Sensor Configuration with Temperature Sense       42         3-16.       Fault Monitor Logic and Fault Level Selection       43         3-17.       D <sub>out</sub> /V <sub>CLUBE</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application PCB Layout: AC Considerations       48         3-20.       PGA308 Memory Structure       52         4-11.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 Module       58         5-5.       One-Wire Timing Diagram       56         5-6.       Four-Terminal PGA308 Module       58         5-7.       Four-Terminal PGA308 Module       58         5-8.       SCR ESD Cell                                                                                                                                                                                       | 3-8.  | Output Amplifier in a Common Three-Terminal Sensor Application                                                         | 34              |

| 3-11.       Over-Scale and Under-Scale Limit Circuit       37         3-12.       Fault Monitor Comparators.       39         3-13.       Bridge Sensor Configuration without Temperature Sense.       40         3-14.       Bridge Sensor Configuration with Temperature Sense.       41         3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense.       42         3-16.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       D <sub>out</sub> /V <sub>ctuate</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Module       55         4-4.       Typical PGA308 Module       58         5-5.       One-Wire Timing Diagram.       56         5-6.       Four-Terminal PGA308 Module       58         5-7.       One-Wire Mode.       60         5-8.       SCR ESD Cell       60         5-9.       OTH Program Mode.       62                                                                                                                                                                                        | 3-9.  | Output Amplifier Using External Feedback Resistors $R_{\mbox{\scriptsize FO EXT}}$ and $R_{\mbox{\scriptsize GO EXT}}$ | 36              |

| 3-12.       Fault Monitor Comparators       39         3-13.       Bridge Sensor Configuration without Temperature Sense.       40         3-14.       Bridge Sensor Configuration with Temperature Sense.       41         3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense.       42         3-16.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       D <sub>OUT</sub> /V <sub>CLMM</sub> Function       43         3-17.       P <sub>OUT</sub> /V <sub>CLMM</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram.       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 Module       58         5-5.       Four-Terminal PGA308 Module       58         5-6.       Four-Terminal PGA308 Module       59         5-7.       Nortwire Konde       61         5-7.       Pin 1W Circuit EM//RFI Disturbance.       61         5-7.       Pin 1W Circuit EM//RFI Filtering       63         5-7.       One-Wire Read Mode       65 </td <td>3-10.</td> <td>Output Amplifier Minimum Gain at Low Supply</td> <td>36</td>                                                                                | 3-10. | Output Amplifier Minimum Gain at Low Supply                                                                            | 36              |

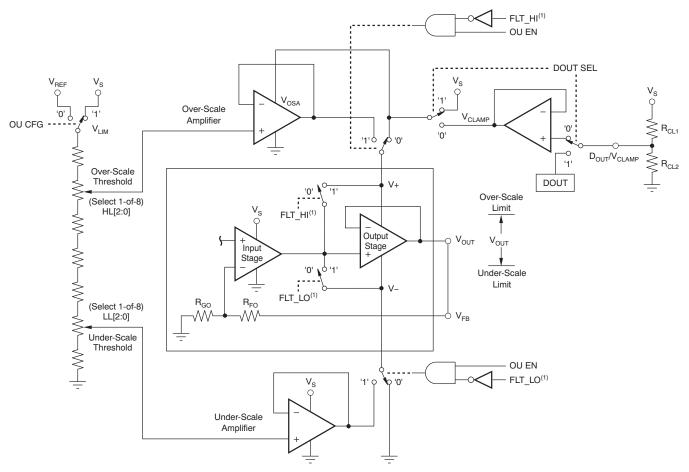

| 3-13.       Bridge Sensor Configuration with Temperature Sense       40         3-14.       Bridge Sensor Configuration with Temperature Sense       41         3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense       42         3-16.       Fault Monitor Logic and Fault Level Selection       43         3-17.       D <sub>QUV</sub> /C <sub>LAWE</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 Module       56         5-5.       One-Wire Triminal PGA308 Module       58         5-2.       Four-Terminal PGA308 Module       59         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance.       61         5-5.       Pin 1W Circuit Protection Logic Levels       62         5-6.       Pin 1W Circuit EMI/RFI Filtering       63         5-7.       One-Wire Read Mod                                                                                                                                                                              | 3-11. | Over-Scale and Under-Scale Limit Circuit                                                                               | 37              |

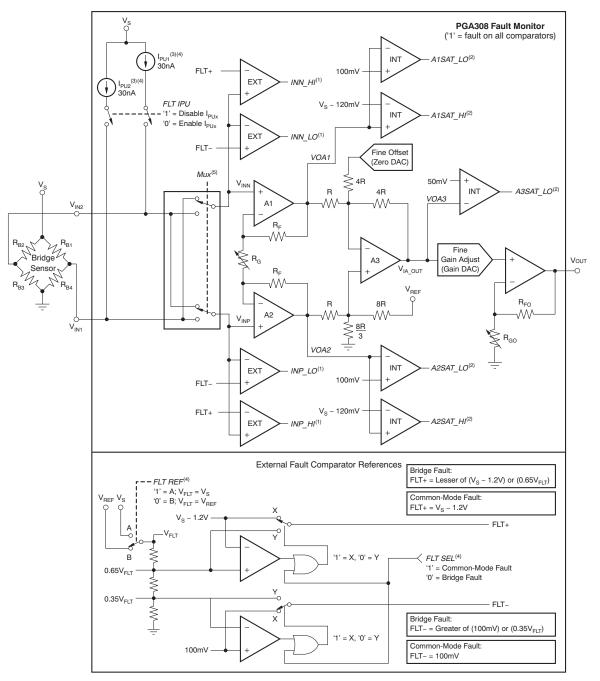

| 3-14.       Bridge Sensor Configuration with Temperature Sense.       41         3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense.       42         3-16.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       D <sub>OUT</sub> /V <sub>CLMP</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 Module       55         4-5.       One-Wire Timing Diagram       56         5-6.       Three-Terminal PGA308 Module       59         5-7.       One-Wire Timing Diagram       60         5-8.       SCR ESD Cell       60         5-9.       Flour Terminal PGA308 Module       59         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance.       61         5-7.       One-Wire Wite Mode       62         5-7. <td>3-12.</td> <td>Fault Monitor Comparators</td> <td>39</td>                                                                                                                                                       | 3-12. | Fault Monitor Comparators                                                                                              | 39              |

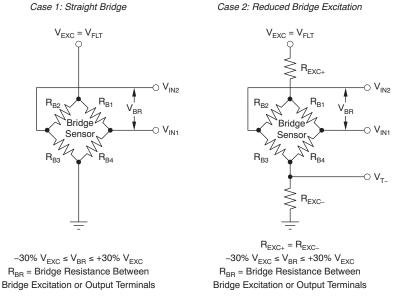

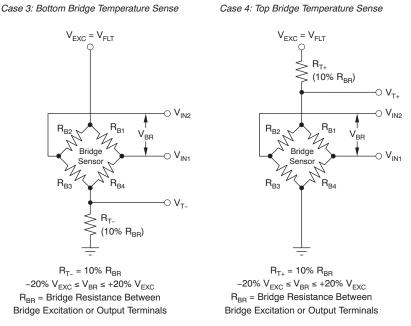

| 3-15.       Bridge Fault Example: Bottom Bridge Temperature Sense.       42         3-16.       Fault Monitor Logic and Fault Level Selection.       43         3-17.       D <sub>QUT</sub> /V <sub>CLAME</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       52         4-4.       Typical PGA308 IW Pin to External Controller Connection       55         4-5.       One-Wire Timing Diagram       56         5-6.       Four-Terminal PGA308 Module       59         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance       61         5-7.       One-Wire Write Mode       62         5-8.       One-Wire Write Mode       63         5-7.       One-Wire Read Mode       62         5-8.       Pin 1W Circuit Protection Logic Levels       64         5-9.       OTP Program Mode       65         <                                                                                                                                                                                                              | 3-13. | Bridge Sensor Configuration without Temperature Sense                                                                  | 40              |

| 3-16.       Fault Monitor Logic and Fault Level Selection       43         3-17.       D <sub>OUT</sub> /V <sub>CLAMP</sub> Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         3-11.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 1W Pin to External Controller Connection       55         4-5.       One-Wire Triming Diagram       56         5-6.       Four-Terminal PGA308 Module       58         5-7.       Four-Terminal PGA308 Module       58         5-8.       Scr ESD Cell       60         5-4.       Severe EMI/RFI Disturbance       61         5-5.       Pin 1W Circuit Protection Logic Levels       62         5-6.       Pin 1W Circuit EMI/RFI Filtering       63         5-7.       One-Wire Read Mode       64         5-8.       Ore-Wire Read Mode       66         5-9.       OTP Program Mode       66         5-10.                                                                                                                                                                                                                         | 3-14. | Bridge Sensor Configuration with Temperature Sense                                                                     | 41              |

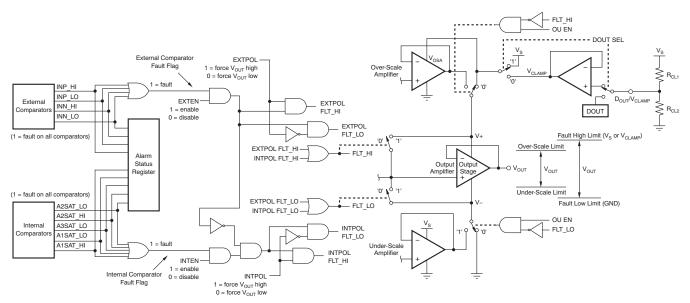

| 3-17. $D_{OUT}/V_{CLAMP}$ Function       44         3-18.       System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.       47         3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 1W Pin to External Controller Connection       55         4-5.       One-Wire Timing Diagram       56         5-1.       Three-Terminal PGA308 Module       58         5-2.       Four-Terminal PGA308 Module       58         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance.       61         5-5.       Pin 1W Circuit Protection Logic Levels       62         5-6.       Pin 1W Circuit EMI/RFI Filtering.       63         5-7.       One-Wire Read Mode.       64         5-8.       OTP Program Mode.       66         5-9.       OTP Program Mode.       66         5-10.       Standalone Mode Operation       68         5-11.       Repro                                                                                                                                                                                                                                                      | 3-15. | Bridge Fault Example: Bottom Bridge Temperature Sense                                                                  | 42              |

| 3-18.System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect.473-19.PGA308 Application Schematic: AC Considerations483-20.PGA308 Memory Structure524-1.PGA308 Memory Structure524-2.One-Wire Protocol Timing Diagram554-3.PGA308 Command Byte554-4.Typical PGA308 IW Pin to External Controller Connection554-5.One-Wire Timing Diagram565-1.Three-Terminal PGA308 Module595-2.Four-Terminal PGA308 Module595-3.SCR ESD Cell605-4.Severe EM/RFI Disturbance615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EM/RFI Filtering635-7.One-Wire Read Mode645-8.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{our}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode715-15. $V_{our}$ Enabled to Shutdown Delay ( $V_{is}$ = +5V, $V_{our}$ = 4.9V, $C_{is}$ = 0nF)745-17.V <sub>our</sub> Enabled to Shutdown Delay ( $V_{is}$ = +5V, $V_{our}$ = 4.9V, $C_{is}$ = 10nF)745-17.V <sub>our</sub> Enabled to Shutdown Delay ( $V_{is}$ = +5V, $V_{our}$ = 4.9V, $C_{is}$ = 10nF)745-18.Shutdown to $V_{our}$ Enabled Delay ( $V_{is}$ = +5V, $V_{our}$ = 4.9V, $C_{is}$ = 10nF)74 <td>3-16.</td> <td>•</td> <td></td>                                                                                                                                                                                                                        | 3-16. | •                                                                                                                      |                 |

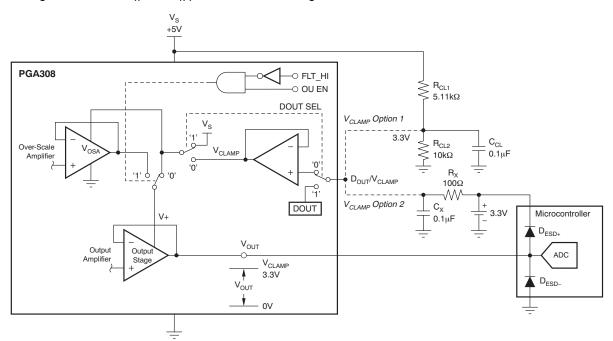

| 3-19.       PGA308 Application Schematic: AC Considerations       48         3-20.       PGA308 Application PCB Layout: AC Considerations       49         4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 1W Pin to External Controller Connection       55         4-5.       One-Wire Timing Diagram       56         5-1.       Three-Terminal PGA308 Module       58         5-2.       Four-Terminal PGA308 Module       59         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance       61         5-5.       Pin 1W Circuit Protection Logic Levels       62         5-6.       Pin 1W Circuit Protection Logic Levels       63         5-7.       One-Wire Write Mode       64         6-8.       One-Wire Read Mode       65         5-9.       OTP Program Mode       66         5-10.       Standalone Mode Operation       68         5-11.       Reprogram with NOW = 1 Mode       70         5-12.       1W Connected to $V_{outr}$ Program Mode       70         5-13.       Virtual Software Lock Mode <td< td=""><td>3-17.</td><td>D<sub>OUT</sub>/V<sub>CLAMP</sub> Function</td><td>44</td></td<>                                                                                                                                                                 | 3-17. | D <sub>OUT</sub> /V <sub>CLAMP</sub> Function                                                                          | 44              |

| $  \begin{array}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-18. | System ADC Range Budget: Over-Scale, Under-Scale, Linear Output, Fault Detect                                          | 47              |

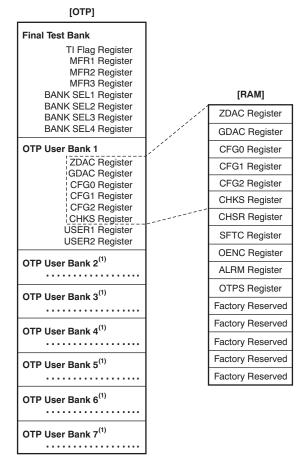

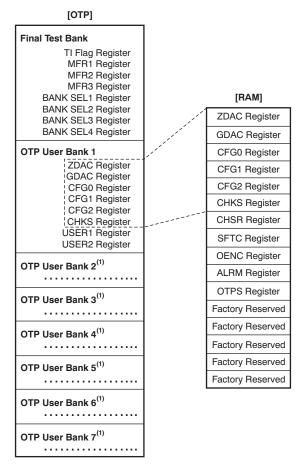

| 4-1.       PGA308 Memory Structure       52         4-2.       One-Wire Protocol Timing Diagram       55         4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 1W Pin to External Controller Connection       55         4-4.       Typical PGA308 1W Pin to External Controller Connection       55         4-5.       One-Wire Timing Diagram       56         5-1.       Three-Terminal PGA308 Module       58         5-2.       Four-Terminal PGA308 Module       59         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance       61         5-5.       Pin 1W Circuit Protection Logic Levels       62         5-6.       Pin 1W Circuit EMI/RFI Filtering.       63         5-7.       One-Wire Mode       63         5-7.       One-Wire Read Mode       64         5-8.       One-Wire Read Mode       65         5-9.       OTP Program Mode       65         5-10.       Standalone Mode Operation       68         5-11.       Reprogram with NOW = 1 Mode       69         5-12.       1W Connected to V <sub>out</sub> Program Mode       70         5-13.       Virtual Software Lock Mode       71         5                                                                                                                                                                                                                                                                         | 3-19. | PGA308 Application Schematic: AC Considerations                                                                        | 48              |

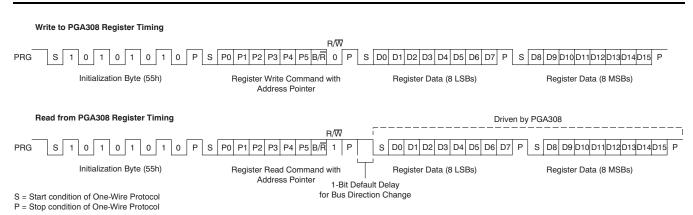

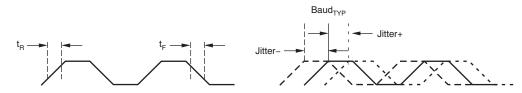

| 4-2.One-Wire Protocol Timing Diagram554-3.PGA308 Command Byte554-4.Typical PGA308 1W Pin to External Controller Connection554-5.One-Wire Timing Diagram565-1.Three-Terminal PGA308 Module585-2.Four-Terminal PGA308 Module595-3.SCR ESD Cell605-4.Severe EMI/RFI Disturbance615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering635-7.One-Wire Read Mode645-8.One-Wire Read Mode665-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{outr}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode715-15.V <sub>outr</sub> Enabled to Shutdown Delay (V <sub>S</sub> = +5V, V <sub>outr</sub> = 4.9V, C <sub>L</sub> = 0nF)745-18.Shutdown to V <sub>outr</sub> Enabled Delay (V <sub>S</sub> = +5V, V <sub>outr</sub> = 4.9V, C <sub>L</sub> = 10nF)74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-20. | PGA308 Application PCB Layout: AC Considerations                                                                       | 49              |

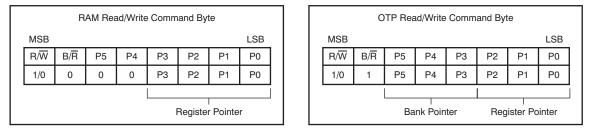

| 4-3.       PGA308 Command Byte       55         4-4.       Typical PGA308 1W Pin to External Controller Connection       55         4-5.       One-Wire Timing Diagram.       56         5-1.       Three-Terminal PGA308 Module       58         5-2.       Four-Terminal PGA308 Module       59         5-3.       SCR ESD Cell       60         5-4.       Severe EMI/RFI Disturbance       61         5-5.       Pin 1W Circuit Protection Logic Levels       62         5-6.       Pin 1W Circuit EMI/RFI Filtering       63         5-7.       One-Wire Read Mode       64         5-8.       One-Wire Read Mode       64         5-9.       OTP Program Mode       66         5-10.       Standalone Mode Operation       68         5-11.       Reprogram with NOW = 1 Mode       69         5-12.       1W Connected to V <sub>out</sub> Program Mode.       70         5-13.       Software Lock Mode       73         5-14.       Software Lock Mode       73         5-15.       V <sub>out</sub> Enabled to Shutdown Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 0nF).       74         5-16.       Shutdown to V <sub>out</sub> Enabled Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 0nF).       74         5-17.       V <sub>out</sub> Enabled t                                                                                                                                            | 4-1.  | PGA308 Memory Structure                                                                                                | 52              |

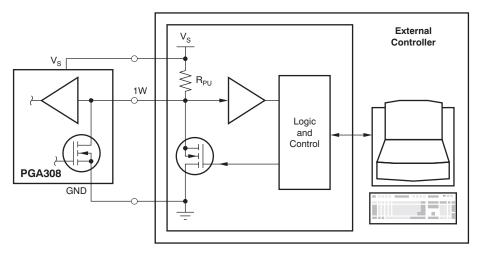

| 4-4.Typical PGA308 1W Pin to External Controller Connection554-5.One-Wire Timing Diagram.565-1.Three-Terminal PGA308 Module585-2.Four-Terminal PGA308 Module595-3.SCR ESD Cell605-4.Severe EMI/RFI Disturbance615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering635-7.One-Wire Write Mode645-8.One-Wire Read Mode655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{out}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{out}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )745-17.V <sub>out</sub> Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-2.  | One-Wire Protocol Timing Diagram                                                                                       | 55              |

| 4-5.One-Wire Timing Diagram.565-1.Three-Terminal PGA308 Module585-2.Four-Terminal PGA308 Module595-3.SCR ESD Cell605-4.Severe EMI/RFI Disturbance.615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering.635-7.One-Wire Write Mode.645-8.One-Wire Read Mode.655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to V <sub>out</sub> Program Mode.705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15.V <sub>out</sub> Enabled to Shutdown Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 0nF).745-16.Shutdown to V <sub>out</sub> Enabled Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 10nF)745-17.V <sub>out</sub> Enabled Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 10nF)74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-3.  | PGA308 Command Byte                                                                                                    | 55              |

| 5-1.Three-Terminal PGA308 Module585-2.Four-Terminal PGA308 Module595-3.SCR ESD Cell605-4.Severe EMI/RFI Disturbance615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering635-7.One-Wire Write Mode645-8.One-Wire Read Mode655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to V <sub>out</sub> Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15.V <sub>out</sub> Enabled to Shutdown Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 0nF).745-17.V <sub>out</sub> Enabled to Shutdown Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 10nF)745-18.Shutdown to V <sub>out</sub> Enabled Delay (V <sub>s</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 10nF)74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-4.  | Typical PGA308 1W Pin to External Controller Connection                                                                | 55              |

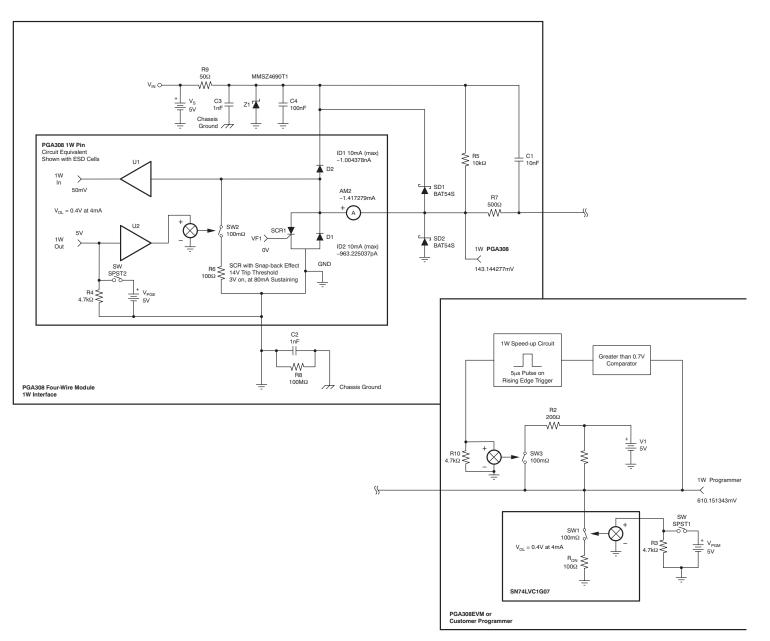

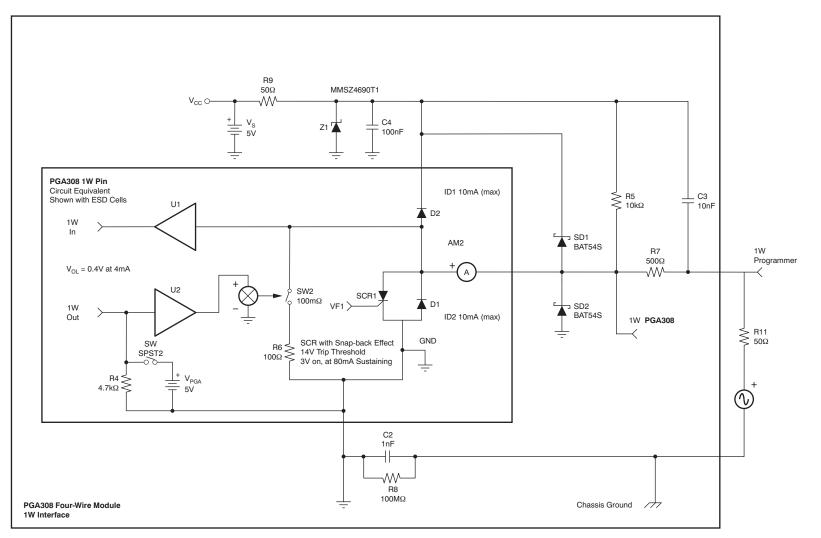

| 5-2.Four-Terminal PGA308 Module595-3.SCR ESD Cell605-4.Severe EMI/RFI Disturbance615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering635-7.One-Wire Write Mode645-8.One-Wire Read Mode655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{out}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{out}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-5.  | One-Wire Timing Diagram                                                                                                | 56              |

| 5-3.SCR ESD Cell605-4.Severe EMI/RFI Disturbance.615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering.635-7.One-Wire Write Mode.645-8.One-Wire Read Mode.655-9.OTP Program Mode.665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode.695-12.1W Connected to V <sub>out</sub> Program Mode.705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15.V <sub>out</sub> Enabled to Shutdown Delay (V <sub>S</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 0nF).745-16.Shutdown to V <sub>out</sub> Enabled Delay (V <sub>S</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 10nF)745-18.Shutdown to V <sub>out</sub> Enabled Delay (V <sub>S</sub> = +5V, V <sub>out</sub> = 4.9V, C <sub>L</sub> = 10nF)74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-1.  | Three-Terminal PGA308 Module                                                                                           | 58              |

| 5-4.Severe EMI/RFI Disturbance.615-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering635-7.One-Wire Write Mode645-8.One-Wire Read Mode655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{out}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{out}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 0nF$ )745-17. $V_{out}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 0nF$ )745-18.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2.  | Four-Terminal PGA308 Module                                                                                            | 59              |

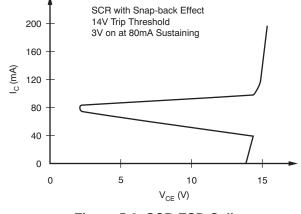

| 5-5.Pin 1W Circuit Protection Logic Levels625-6.Pin 1W Circuit EMI/RFI Filtering635-7.One-Wire Write Mode645-8.One-Wire Read Mode655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{out}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{out}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{out}$ Enabled Delay ( $V_s = +5V$ , $V_{out} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-3.  | SCR ESD Cell                                                                                                           | <b>60</b>       |

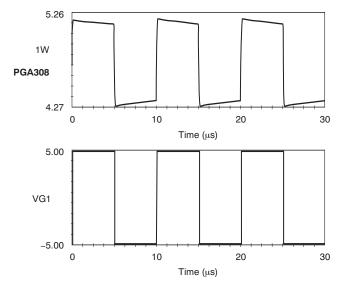

| 5-6.Pin 1W Circuit EMI/RFI Filtering.635-7.One-Wire Write Mode.645-8.One-Wire Read Mode.655-9.OTP Program Mode.665-10.Standalone Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-4.  | Severe EMI/RFI Disturbance                                                                                             | 61              |

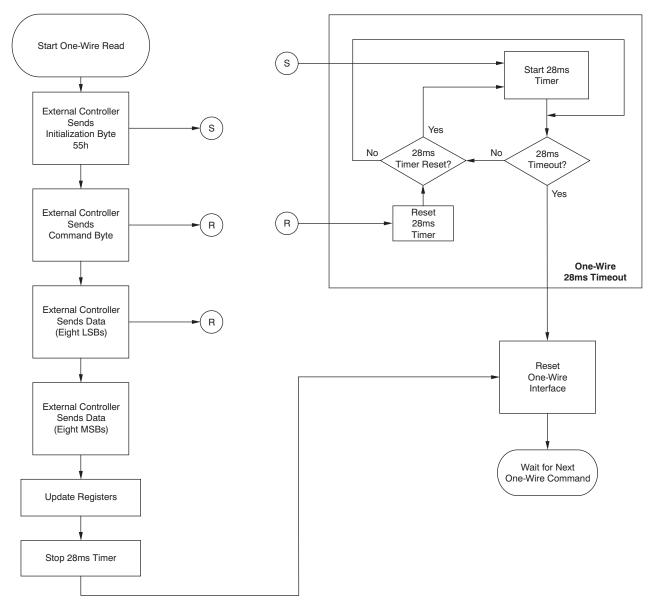

| 5-7.One-Wire Write Mode645-8.One-Wire Read Mode655-9.OTP Program Mode665-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{OUT}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-5.  | Pin 1W Circuit Protection Logic Levels                                                                                 | 62              |

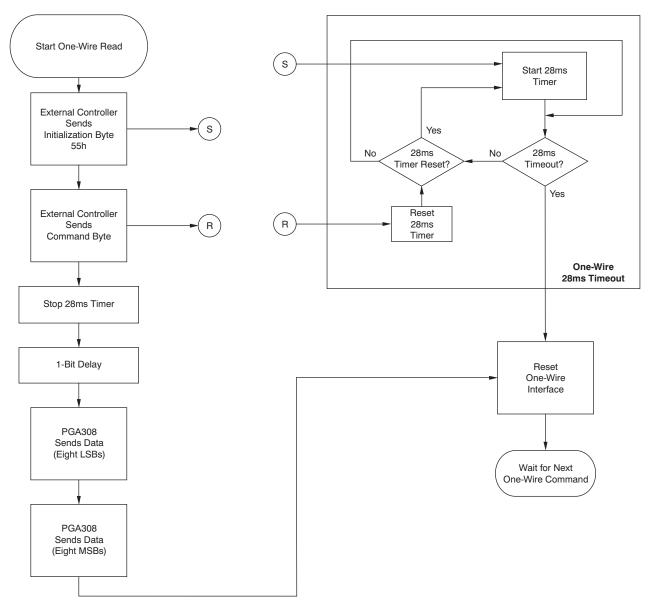

| 5-8.One-Wire Read Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-6.  | Pin 1W Circuit EMI/RFI Filtering                                                                                       | 63              |

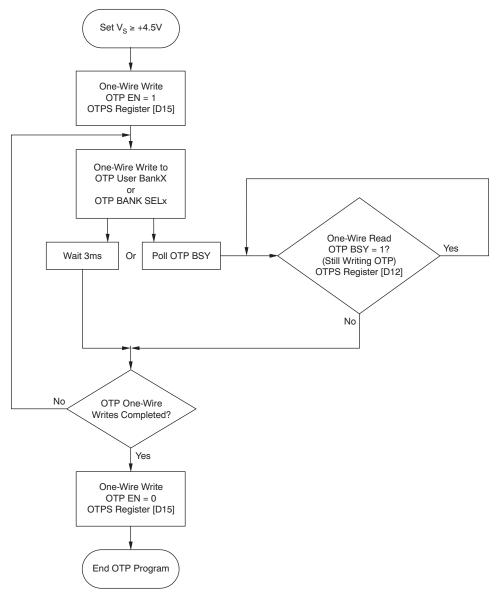

| 5-9.OTP Program Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-7.  | One-Wire Write Mode                                                                                                    | 64              |

| 5-10.Standalone Mode Operation685-11.Reprogram with NOW = 1 Mode695-12.1W Connected to $V_{OUT}$ Program Mode705-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-8.  | One-Wire Read Mode                                                                                                     | 65              |

| 5-11. Reprogram with NOW = 1 Mode695-12. 1W Connected to $V_{OUT}$ Program Mode705-13. Virtual Software Lock Mode715-14. Software Lock Mode735-15. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-16. Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18. Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-9.  | OTP Program Mode                                                                                                       | 66              |

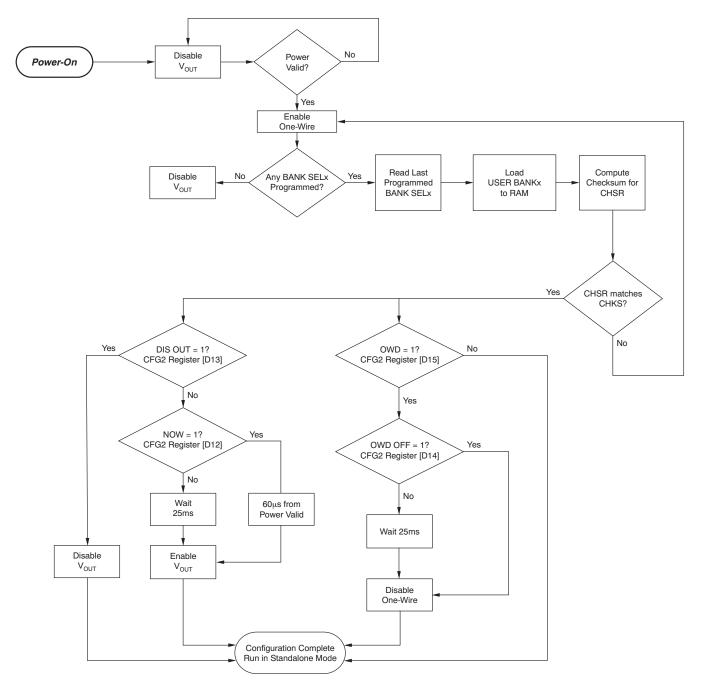

| 5-12.1W Connected to $V_{OUT}$ Program Mode.705-13.Virtual Software Lock Mode.715-14.Software Lock Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-10. | Standalone Mode Operation                                                                                              | <mark>68</mark> |

| 5-13.Virtual Software Lock Mode715-14.Software Lock Mode735-15. $V_{OUT}$ Enabled to Shutdown Delay ( $V_S = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{OUT}$ Enabled Delay ( $V_S = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_S = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_S = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_S = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-11. | Reprogram with NOW = 1 Mode                                                                                            | <b>69</b>       |

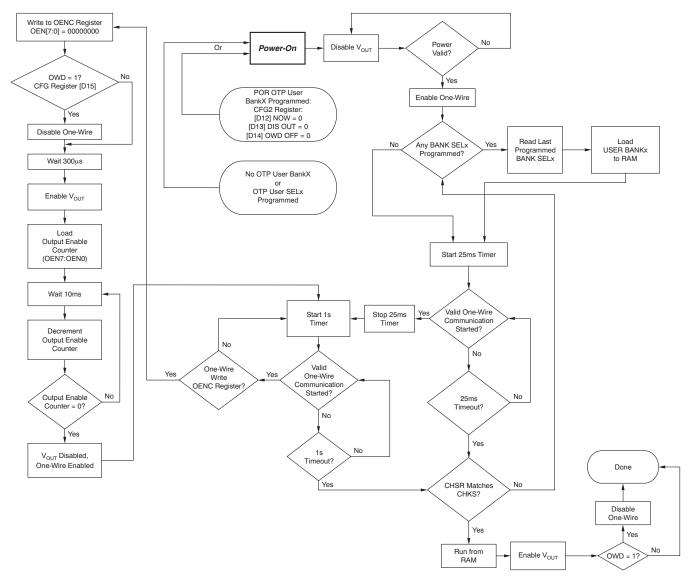

| 5-14.Software Lock Mode735-15. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-12. | 1W Connected to $V_{out}$ Program Mode                                                                                 | 70              |

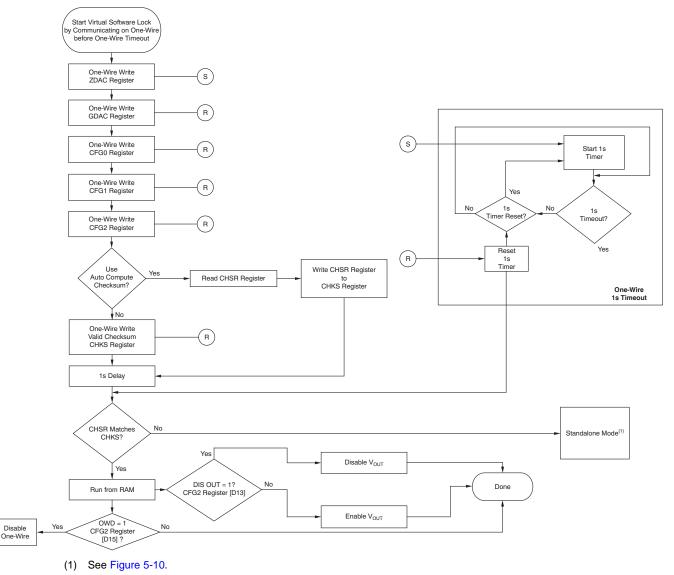

| 5-15. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-16.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 0nF$ )745-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-13. | Virtual Software Lock Mode                                                                                             | 71              |

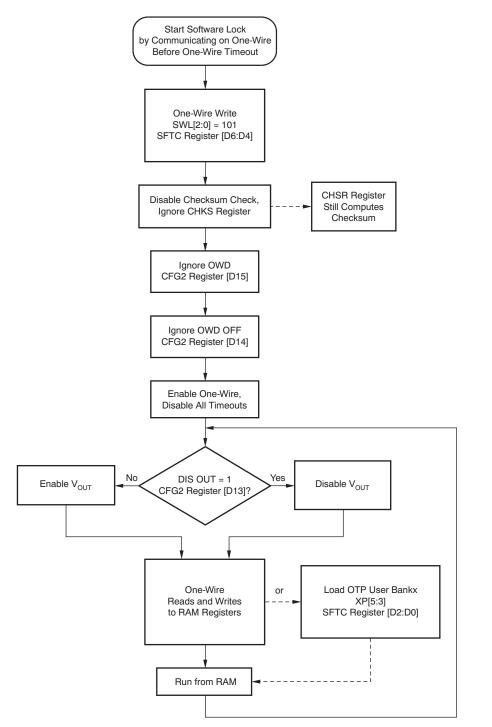

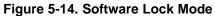

| 5-16.Shutdown to V_{OUT} Enabled Delay (V_s = +5V, V_{OUT} = 4.9V, C_L = 0nF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-14. | Software Lock Mode                                                                                                     | 73              |

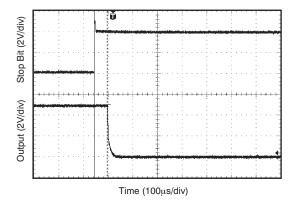

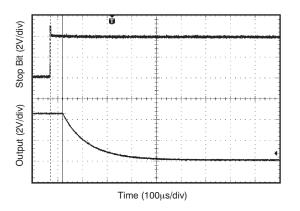

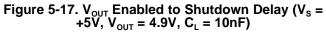

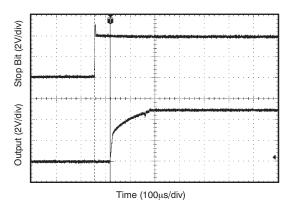

| 5-17. $V_{OUT}$ Enabled to Shutdown Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )745-18.Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-15. | $V_{\text{OUT}}$ Enabled to Shutdown Delay (V_s = +5V, V_{\text{OUT}} = 4.9V, $C_{\text{L}}$ = 0nF)                    | 74              |

| 5-18. Shutdown to $V_{OUT}$ Enabled Delay ( $V_s = +5V$ , $V_{OUT} = 4.9V$ , $C_L = 10nF$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-16. | Shutdown to V <sub>OUT</sub> Enabled Delay (V <sub>S</sub> = +5V, V <sub>OUT</sub> = 4.9V, C <sub>L</sub> = 0nF)       | 74              |

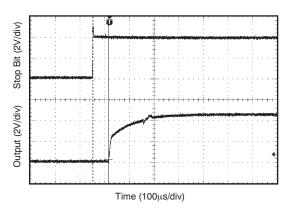

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-17. |                                                                                                                        |                 |