# Logic Solutions for IEEE Std 1284

SCEA013 June 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

| Contents                                                                                                                                            |                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Title                                                                                                                                               | Page               |

| Abstract                                                                                                                                            | 1                  |

| Introduction                                                                                                                                        | 1                  |

| Brief Overview of IEEE Std 1284                                                                                                                     | 1                  |

| Purpose and Benefits of IEEE Std 1284IEEE Std 1284 Data Transfer ModesIEEE Std 1284 Driver SpecificationIEEE Std 1284 Connectors                    | · · · 2<br>· · · 2 |

| Device Information                                                                                                                                  | 8                  |

| Application Information         Why the IEEE Std 1284 Driver is Needed         IEEE Std 1284 Parallel-Port Solutions Using TI Bus-Interface Devices | 13                 |

| Conclusion                                                                                                                                          | 17                 |

| Acknowledgment                                                                                                                                      | 18                 |

| Commonly Asked Questions                                                                                                                            | 18                 |

| Glossary                                                                                                                                            | 18                 |

## **List of Illustrations**

## Title

| Figure | Title                                                                                                         | Page |

|--------|---------------------------------------------------------------------------------------------------------------|------|

| 1.     | IEEE Std 1284-A (Host) to IEEE Std 1284-B (Peripheral) Wiring Diagram                                         | 3    |

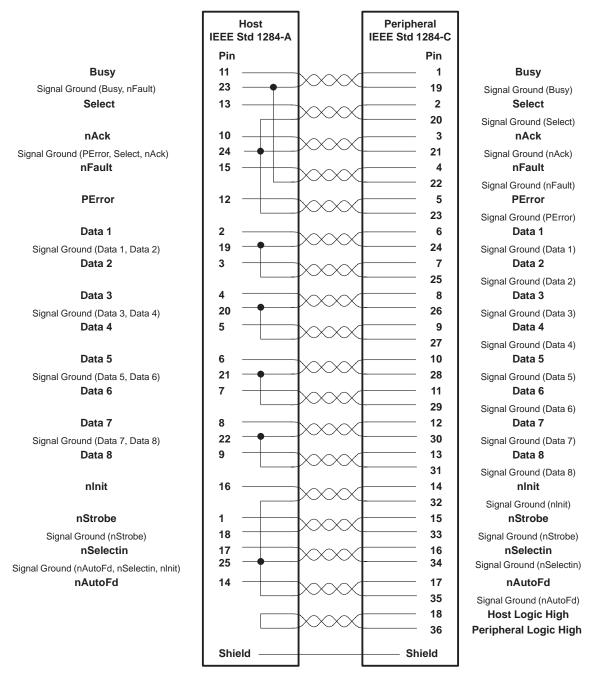

| 2.     | IEEE Std 1284-A (Host) to IEEE Std 1284-C (Peripheral) Wiring Diagram                                         | 4    |

| 3.     | IEEE Std 1284-C (Host) to IEEE Std 1284-C (Peripheral) Wiring Diagram                                         | 5    |

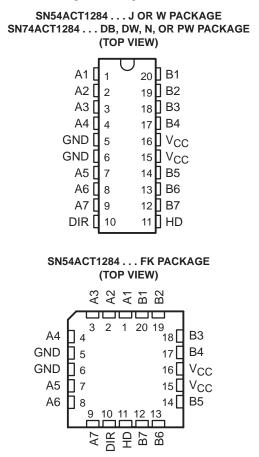

| 4.     | Pinout of SN54/SN74ACT1284                                                                                    | 6    |

| 5.     | Pinout of SN74LV161284 and SN74LVC161284                                                                      | 7    |

| 6.     | Test Setup for Back-Driving Current                                                                           | 9    |

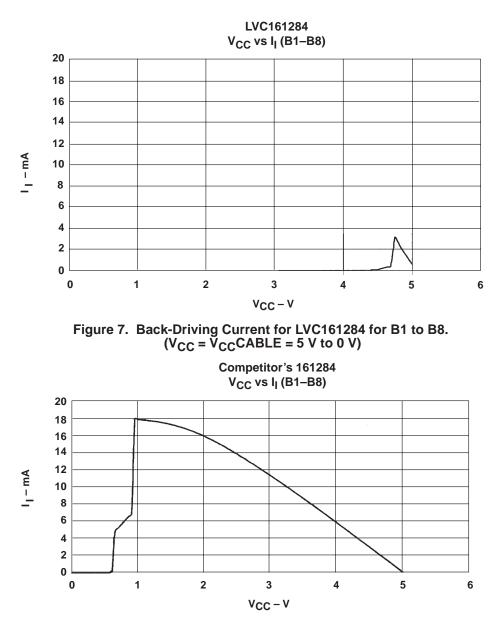

| 7.     | Back-Driving Current for LVC161284 for B1 to B8. ( $V_{CC} = V_{CC}CABLE = 5 V \text{ to } 0 V$ )             | 10   |

| 8.     | Back-Driving Current for Competitor's 161284 for B1 to B8. ( $V_{CC} = V_{CC}CABLE = 5 V \text{ to } 0 V$ )   | 10   |

| 9.     | Back-Driving Current for LVC161284 for C14 to C17. ( $V_{CC} = V_{CC}CABLE = 5 V \text{ to } 0 V$ )           | 11   |

| 10.    | Back-Driving Current for Competitor's 161284 for C14 to C17. ( $V_{CC} = V_{CC}CABLE = 5 V \text{ to } 0 V$ ) | 11   |

| 11.    | Pre-IEEE Std 1284 Parallel-Port Host Solution                                                                 | 13   |

| 12.    | Block Diagram of Parallel Interface Port Between the PC and Peripheral                                        | 14   |

| 13.    | IEEE Std 1284 Host Solution Using Two SN74ACT1284 Devices                                                     | 14   |

| 14.    | IEEE Std 1284 Peripheral Solution Using Two SN74ACT1284 Devices                                               | 15   |

| 15.    | IEEE Std 1284 Host Solution Using the SN74LV161284 or SN74LVC161284                                           | 16   |

| 16.    | IEEE Std 1284 Peripheral Solution Using the SN74LV161284 or SN74LV161284                                      | 17   |

# List of Tables

# Title

| Table | Title                                                       | Pa | ige |

|-------|-------------------------------------------------------------|----|-----|

| 1.    | Function Table for SN74ACT1284                              |    | 7   |

| 2.    | Function Table for SN74LV161284 and SN74LVC161284           |    | 7   |

| 3.    | Features and Benefits of the SN74ACT1284                    |    | 8   |

| 4.    | Features and Benefits of the SN74LV161284 and SN74LVC161284 |    | 8   |

| 5.    | Comparisons of Device Characteristics                       |    | 12  |

## Abstract

Since the creation of IEEE Std 1284, designers have been using this signaling method to interface between the personal computer and peripheral devices. Bulky discrete components, such as termination and pullup resistors and capacitors, were used extensively. To integrate into single-chip solutions that comply with IEEE Std 1284, Texas Instruments (TI<sup>™</sup>) offers three bus-interface devices that provide board-area savings and flexible level-type selection.

### Introduction

This application report presents a brief overview of IEEE Std 1284-1994, provides information on each device available from TI that is a bus-interface solution for this standard, and discusses how to use the devices in applications. TI offers the SN74ACT1284, which is a 7-bit bus-interface transceiver, and the SN74LVC161284 and SN74LV161284, which are 19-bit bus-interface transceivers, as discrete IEEE Std 1284 bus-interface solutions.

## **Brief Overview of IEEE Std 1284**

IEEE Std 1284, "Standard Signaling Method for a Bidirectional Parallel Peripheral Interface for Personal Computers," is a high-speed, high-integrity parallel-port method for a bidirectional peripheral interface for personal computers. This standard was developed to provide an open path for communications between computers and peripherals. Furthermore, it recommends new electrical interfaces, cabling, and interface hardware that provides improved performance, while retaining backward compatibility.

#### Purpose and Benefits of IEEE Std 1284

With increased technology development in the personal computer (PC), a need for improved parallel-port performance has emerged. Pre-existing methods used a wide variety of hardware and software products, each with unique and incompatible signaling schemes. Using existing parallel-port architecture, the maximum data transfer rate is about 150 kbyte/s, and external cables are limited to 6 feet.

IEEE Std 1284 was created because of the need for an existing defined standard for bidirectional parallel communication between the PC and printing peripherals. Being backward compatible with the old Centronics specifications, this standard offers more functionality and performance for new PC and peripheral products. Data rates are increased to greater than 1Mbyte/s and maximum cable length is increased to 32 feet for the defined cable type.

## IEEE Std 1284 Data Transfer Modes

IEEE Std 1284 defines five modes of data transfer. Not all modes are required in all peripherals; forward is defined as data transfer from host to peripheral, and reverse is defined as data transfer from peripheral to host. The bidirectional mode provides both forward and reverse transfer mode within the same operational mode. The modes are:

- Compatibility Mode: This is the basic mode of operation for all parallel communications. It is asynchronous, byte wide, forward direction, and offers 50-kbyte/s to 150-kbyte/s data-transfer rate.

- Nibble Mode: This asynchronous, reverse-channel mode provides two sequential, 4-bit nibbles to the host. It is used with the compatibility mode to implement a bidirectional channel. The data transfer rate is the same as in the compatibility mode.

- Byte Mode: This mode allows the transfer of data in the reverse direction if the data lines are bidirectional. The data transfer rate is the same as in the compatibility and nibble modes.

- Enhanced Parallel Port (EPP): This mode allows high-speed transfers of bytes in either direction. EPP is ideal for real-time-controlled peripherals, such as network adapters, data acquisition, portable hard drives, and other devices.

- Extended Capabilities Port (ECP): The ECP protocol was proposed as an advanced mode for communication with printer and scanner peripherals. Like the EPP protocol, ECP provides a high-performance, bidirectional communication path between the host and peripheral. ECP and EPP modes are ten times faster than the compatibility, nibble, and byte modes.

## **IEEE Std 1284 Driver Specification**

IEEE Std 1284 specifies characteristics of parallel-port drivers and receivers, and describes two types of interfaces:

- Level I (open drain): Level I devices are designed to be consistent with the pre-existing installed devices. Applications using Level I should not be operated in the high-speed advanced modes, but should take advantage of reverse-channel capabilities of the standard.

- Level II (totem pole): Level II devices have stronger drivers and inputs with hysteresis. They are designed to operate in the advanced mode where a longer cable and higher data rates prevail. Level II offers better performance, while remaining compatible with the original interface.

## **IEEE Std 1284 Connectors**

Three interface connectors defined in IEEE Std 1284 are:

- IEEE Std 1284-A: This is the existing DB25 connector, used primarily on the host side.

- IEEE Std 1284-B: This is the existing 36-pin, 0.085-inch centerline connector, used only on the peripheral side.

- IEEE Std 1284-C: This connector is a new 36-pin, 0.050-inch centerline connector recommended by IEEE Std 1284 that is used on both host and peripheral sides.

Since A- and B-type connectors do not have the same number of pins, Figures 1 and 2 detail pin connections for communication between the PC and peripheral. These connections (A host and B peripheral; A host and C peripheral) are the most commonly accepted in the industry.

As recommended in IEEE Std 1284, using the C-type connector on both host and peripheral sides provides a high-speed, high-integrity parallel port for reliable bidirectional communication. Figure 3 shows the straightforward connection between the two ports.

Figure 1. IEEE Std 1284-A (Host) to IEEE Std 1284-B (Peripheral) Wiring Diagram

Figure 2. IEEE Std 1284-A (Host) to IEEE Std 1284-C (Peripheral) Wiring Diagram

|                                          | Host<br>IEEE Std 1284-C |                    | Peripheral<br>IEEE Std 1284-C |                                          |

|------------------------------------------|-------------------------|--------------------|-------------------------------|------------------------------------------|

|                                          | Pin                     |                    | Pin                           |                                          |

| Busy                                     | 1                       | $\sim$             | 1                             | Busy                                     |

| Signal Ground (Busy)                     | 19                      | $\sim\sim\sim\sim$ | 19                            | Signal Ground (Busy)                     |

| Select                                   | 2                       | $\sim$             | 2                             | Select                                   |

| Signal Ground (Select)                   | 20                      |                    | 20                            | Signal Ground (Select)                   |

| nAck                                     | 3                       | $\times$           | 3                             | nAck                                     |

| Signal Ground (nAck)                     | 21                      |                    | 21                            | Signal Ground (nAck)                     |

| nFault                                   | 4                       | $\times$           | 4                             | nFault                                   |

| Signal Ground (nFault)                   | 22                      |                    | 22                            | Signal Ground (nFault)                   |

| PError                                   | 5                       | $\times$           | 5                             | PError                                   |

| Signal Ground (PError)                   | 23                      |                    | 23                            | Signal Ground (PError)<br>Data 1         |

| Data 1                                   | 6<br>24                 | $\times$           | 6<br>24                       |                                          |

| Signal Ground (Data 1)<br>Data 2         | 7                       |                    | 7                             | Signal Ground (Data 1)<br>Data 2         |

|                                          | 25                      | $\times$           | 25                            |                                          |

| Signal Ground (Data 2)<br>Data 3         | 8                       |                    | 8                             | Signal Ground (Data 2)<br>Data 3         |

| Signal Ground (Data 3)                   | 26                      | XXXX               | 26                            | Signal Ground (Data 3)                   |

| Data 4                                   | 9                       |                    | 9                             | Data 4                                   |

| Signal Ground (Data 4)                   | 27                      |                    | 27                            | Signal Ground (Data 4)                   |

| Data 5                                   | 10                      |                    | 10                            | Data 5                                   |

| Signal Ground (Data 5)                   | 28                      | XXXX               | 28                            | Signal Ground (Data 5)                   |

| Data 6                                   | 11                      |                    | 11                            | Data 6                                   |

| Signal Ground (Data 6)                   | 29                      |                    | 29                            | Signal Ground (Data 6)                   |

| Data 7                                   | 12                      | $\sim$             | 12                            | Data 7                                   |

| Signal Ground (Data 7)                   | 30                      |                    | 30                            | Signal Ground (Data 7)                   |

| Data 8                                   | 13                      | $\times$           | 13                            | Data 8                                   |

| Signal Ground (Data 8)                   | 31                      |                    | 31                            | Signal Ground (Data 8)                   |

| nlnit                                    | 14                      | $\times$           | 14                            | nInit                                    |

| Signal Ground (nInit)                    | 32                      |                    | 32                            | Signal Ground (nInit)                    |

| nStrobe                                  | 15                      | $\times$           | 15                            | nStrobe                                  |

| Signal Ground (nStrobe)                  | 33                      |                    | 33                            | Signal Ground (nStrobe)                  |

| nSelectin                                | 16<br>34                | $\times$           | 16<br>34                      | nSelectin                                |

| Signal Ground (nSelectin)                | -                       |                    | -                             | Signal Ground (nSelectin)                |

| nAutoFd                                  | 17                      | $\times$           | 17                            | nAutoFd                                  |

| Signal Ground (nAutoFd)                  | 35                      |                    | 35<br>                        | Signal Ground (nAutoFd)                  |

| Host Logic High<br>Peripheral Logic High | 36                      | $\times$           | 18<br>36                      | Host Logic High<br>Peripheral Logic High |

| renpheral Logic righ                     | 30                      |                    | 30                            |                                          |

|                                          | Shield                  |                    | Shield                        |                                          |

Figure 3. IEEE Std 1284-C (Host) to IEEE Std 1284-C (Peripheral) Wiring Diagram

## **Device Information**

TI offers three bus-driver solutions that comply with the IEEE Std 1284 specification: SN74ACT1284, SN74LVC161284, and SN74LV161284. These devices can be used in the ECP mode to provide an asynchronous, bidirectional, parallel peripheral interface for personal computers. These devices allow data transmission in the A-to-B direction or B-to-A direction, depending on the logic level of the direction-control (DIR) pin. The output drive mode is determined by the high-drive (HD) control pin. HD enables the outputs (B and Y side only) to switch from open collector to totem pole. The A side outputs have totem-pole outputs only. This meets the drive requirements as specified in the IEEE Std 1284-I (level-1 type) and IEEE Std 1284-II (level-2 type) parallel peripheral-interface specifications. All these devices have two supply voltages, one for the cable side, and the other for the logic side. To reduce the chance of faulty signals being transferred over the system's parallel port, all these devices feature a finely tuned Output Edge-Rate Control (OEC<sup>TM</sup>) circuit and an enhanced input hysteresis circuit.

The pinouts and function tables of these devices are given in Figures 4 and 5 and in Tables 1 and 2, respectively.

Figure 4. Pinout of SN54/SN74ACT1284

OEC is a trademark of Texas Instruments Incorporated.

| DGG OR DL PACKAGE<br>(TOP VIEW)                                                                                                                                         |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HD<br>A9<br>A10<br>A11<br>A12<br>A13<br>V <sub>CC</sub><br>A1<br>A2<br>GND<br>A3<br>A4<br>A5<br>A6<br>GND<br>A7<br>A8<br>V <sub>CC</sub><br>PERI LOGIC IN<br>A14<br>A15 | 1<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21 | 48       DIR         47       Y9         46       Y10         45       Y11         44       Y12         43       Y13         42       V <sub>CC</sub> CABLE         41       B1         40       B2         39       GND         38       B3         37       B4         36       B5         35       B6         34       GND         33       B7         32       B8         31       V <sub>CC</sub> CABLE         30       PERI LOGIC OUT         29       C14         28       C15 |  |  |

| A16 L<br>A17 [<br>HOST LOGIC OUT [                                                                                                                                      | 23                                                                                                                     | 27 C16<br>26 C17<br>25 HOST LOGIC IN                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

# Figure 5. Pinout of SN74LV161284 and SN74LVC161284

| INPUTS |    | OUTPUT     | MODE                                             |  |

|--------|----|------------|--------------------------------------------------|--|

| DIR    | HD | OUTPUT     | MODE                                             |  |

|        |    | Open drain | A to B: Bits 5, 6, 7                             |  |

|        | L  | Totem pole | B to A: Bits 1, 2, 3, 4                          |  |

| L      | Н  | Totem pole | B to A: Bits 1, 2, 3, 4 and A to B: Bits 5, 6, 7 |  |

| Н      | L  | Open drain | A to B: Bits 1, 2, 3, 4, 5, 6, 7                 |  |

| Н      | Н  | Totem pole | A to B: Bits 1, 2, 3, 4, 5, 6, 7                 |  |

## Table 1. Function Table for SN74ACT1284

| INP                                                                              | INPUTS |                                                                       | NODE                                                                                      |

|----------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| DIR                                                                              | HD     | OUTPUT                                                                | MODE                                                                                      |

|                                                                                  |        | Open drain                                                            | A9–A13 to Y9–Y13 and PERI LOGIC IN to PERI LOGIC OUT                                      |

| Totem pole B1–B8 to A1–A8 and C14–C17 to A14–A17                                 |        | B1–B8 to A1–A8 and C14–C17 to A14–A17                                 |                                                                                           |

| L                                                                                | Н      | Totem pole                                                            | B1-B8 to A1-A8, A9-A13 to Y9-Y13, PERI LOGIC IN to PERI LOGIC OUT, and C14-C17 to A14-A17 |

| Open drain A1–A8 to B1–B8, A9–A13 to Y9–Y13, and PERI LOGIC IN to PERI LOGIC OUT |        | A1-A8 to B1-B8, A9-A13 to Y9-Y13, and PERI LOGIC IN to PERI LOGIC OUT |                                                                                           |

| Н                                                                                | L      | Totem pole                                                            | C14-C17 to A14-A17                                                                        |

| Н                                                                                | Н      | Totem pole                                                            | A1-A8 to B1-B8, A9-A13 to Y9-Y13, C14-C17 to A14-A17, and PERI LOGIC IN to PERI LOGIC OUT |

## **Features and Benefits**

Tables 3 and 4 summarize the features and corresponding benefits for three TI devices that are IEEE Std 1284 compliant.

| Table 3. Features and Benefits of the SN74ACT1284 |

|---------------------------------------------------|

|---------------------------------------------------|

| FEATURES                                                                                                              | BENEFITS                               |  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Flow-through architecture                                                                                             | Optimizes printed circuit board layout |  |

| Center-pin V <sub>CC</sub> and GND configuration                                                                      | Minimizes high-speed switching noise   |  |

| Software configurable to IEEE Std 1284-I (level-1 type) and IEEE Std 1284-II (level-2 type) electrical specifications | Easy level-type selection              |  |

| A-to-B and B-to-A transmission for bits 1, 2, 3, and 4                                                                | Configurable data flow                 |  |

## Table 4. Features and Benefits of the SN74LV161284 AND SN74LVC161284

| FEATURES                                                                                                              | BENEFITS                                   |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Integrated 1.4-k $\Omega$ pullup resistors on all open-drain cable-side outputs $^{\dagger}$                          | Eliminates the need for discrete resistors |

| Software-configurable to IEEE Std 1284-I (level-1 type) and IEEE Std 1284-II (level-2 type) electrical specifications | Easy level-type selection                  |

| Flow-through architecture                                                                                             | Optimizes printed circuit board layout     |

| V <sub>CC</sub> CABLE from 3 V to 5.5 V, V <sub>CC</sub> from 3 V to 3.6 V (SN74LVC161284 only)                       | Wide voltage range                         |

| 4.5-V to 5.5-V V <sub>CC</sub> and V <sub>CC</sub> CABLE (SN74LV161284 only)                                          | Single supply                              |

| Eight bidirectional data bits, five cable drivers and four receivers                                                  | Complete peripheral solution               |

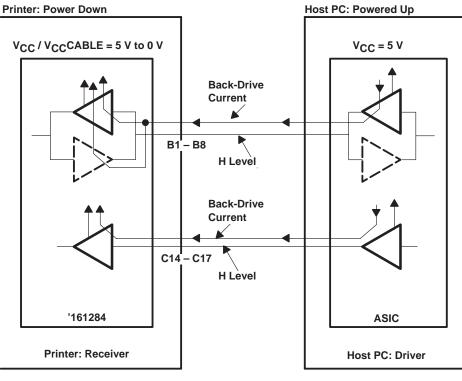

| Integrated PMOS transistors between $V_{CC}$ and cable-side data and receiver outputs $\ddagger$                      | Avoids back-drive current                  |

| Integrated 33- $\Omega$ termination resistors to all cable-side outputs                                               | Eliminates the need for discrete resistors |

| Dedicated buffers for Peripheral Logic High and Host Logic High signals $\S$                                          | Complete peripheral solution               |

<sup>†</sup> Pullup resistors ensure operation with a Level I compatible device and provide sufficient voltage and timing margins as specified by IEEE Std 1284. In addition, the pullup resistors add margin for noisy cable environments.

‡ Avoiding back-drive current keeps the peripheral from being powered up by the host when the peripheral is off and allows for a 5-V system to be connected to the cable side. Laboratory experiments using TI's SN74LVC161284 and a competitor's 1284 transceiver show how the two devices compare, while simulating a typical PC-to-peripheral application. In this situation, a '161284 is used on the peripheral.

S Hosts and peripherals indicate their readiness to communicate by asserting Host Logic High and Peripheral Logic High, respectively. All hosts and peripherals with IEEE Std 1284-C connectors shall provide Host Logic High and Peripheral Logic High. Because devices with IEEE Std 1284-A or IEEE Std 1284-B connectors may or may not support Host Logic High or Peripheral Logic High, there are no reliable means of initiating a transfer.

## **Performance Comparison**

As the Super I/O transmits a high level to the peripheral via the cable, the '161284 on the printer side receives the signal because it is configured as a receiver. In TI's laboratory, the host PC side is simulated by driving +5 V to the '161284 receiver. Any back-drive current is measured and plotted as the peripheral device is being powered down and is receiving a high-level input (H level). The experiment is repeated for the competitor's part. Figure 6 shows the test setup. Results, plotted on Figures 7, 8, 9, and 10, show the superior performance of the TI SN74LVC161284 vs a competitor's equivalent device.

DIR: L Level HD: H to L (Connect V<sub>CC</sub>)

Figure 8. Back-Driving Current for Competitor's 161284 for B1 to B8. ( $V_{CC} = V_{CC}CABLE = 5 V to 0 V$ )

Figure 10. Back-Driving Current for Competitor's 161284 for C14 to C17.  $(V_{CC} = V_{CC}CABLE = 5 V \text{ to } 0 V)$

Table 5 provides a comparison of characteristics of the SN74ACT184, SN74LVC161284, and SN74LV161284 devices.

| DEVICE<br>CHARACTERISTICS         | SN74ACT1284 SN74LVC161284                                                                                 |                                                                                                                                         | SN74LV161284                                                                                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Number of pins                    | 20                                                                                                        | 48                                                                                                                                      | 48                                                                                                                                      |

| Number of data bits               | Four bidirectional bits                                                                                   | Eight bidirectional bits                                                                                                                | Eight bidirectional bits                                                                                                                |

| Number of control and status bits | Three unidirectional<br>bits for control or<br>status                                                     | Five driver and four receiver<br>for status and control bits,<br>one receiver for host logic,<br>and one driver for peripheral<br>logic | Five driver and four receiver<br>for status and control bits,<br>one receiver for host logic,<br>and one driver for peripheral<br>logic |

| Supply voltage                    | 4.7 V ≤ V <sub>CC</sub> ≤ 5.5 V                                                                           | $\begin{array}{l} 3 \ V \leq V_{CC} \leq 3.6 \ V \\ 3 \ V \leq V_{CC} CABLE \leq 5.5 \ V \\ V_{CC} CABLE \geq V_{CC} \end{array}$       | $\begin{array}{l} 4.5 \ V \leq V_{CC} \leq 5.5 \ V \\ 4.5 \ V \leq V_{CC} CABLE \leq 5.5 \ V \\ V_{CC} CABLE \geq V_{CC} \end{array}$   |

| Temperature range                 | 0°C to 70°C                                                                                               |                                                                                                                                         | –40°C to 85°C                                                                                                                           |

| Available package<br>types        | SOIC (DW)Plastic 300-mil ShrinkSSOP (DB)Small-Outline (DL)TSSOP (DW)Thin Shrink Small-OutlineDIP (N)(DGG) |                                                                                                                                         | Plastic 300-mil Shrink<br>Small-Outline (DL)<br>Thin Shrink Small-Outline<br>(DGG)                                                      |

| Input hysteresis                  | All inputs have hysteresis to provide noise margin                                                        |                                                                                                                                         |                                                                                                                                         |

| Pullup resistors                  | No pullup resistor is included                                                                            | 1.4-kΩ pullup resistor is<br>included in all cable-side<br>pins, except for Host Logic<br>and Peripheral Logic                          | 1.4 k-Ω pullup resistor is<br>included in all cable-side<br>pins, except for Host Logic<br>and Peripheral Logic                         |

| Termination resistors             | No internal series<br>termination resistor<br>included                                                    | 33-Ω series resistor<br>integrated into cable-side<br>data output                                                                       | 33-Ω series resistor<br>integrated into cable-side<br>data output                                                                       |

Table 5. Comparisons of Device Characteristics

## **Application Information**

### Why the IEEE Std 1284 Driver is Needed

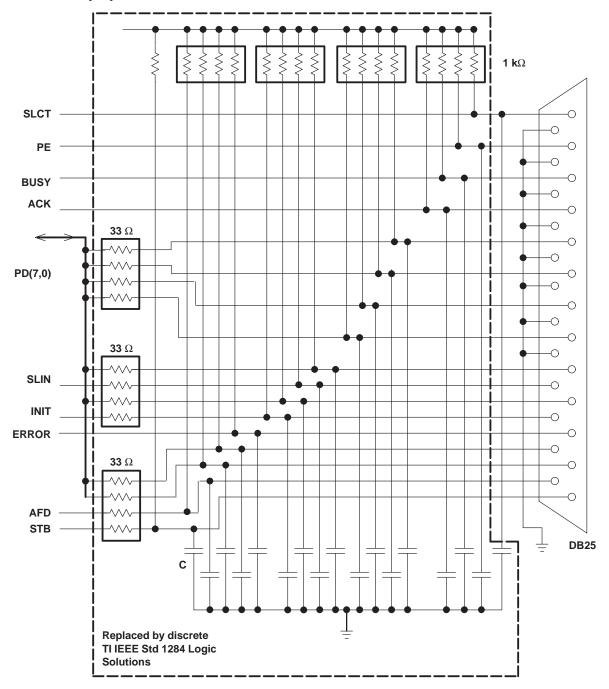

Before IEEE Std 1284, there was no defined electrical specification for driver, receiver, termination, and capacitance requirements that required compatibility between devices. Host adapters and peripherals were built with different pullup values on the control lines, open-collectors or open-drains, and totem-pole drivers for the data and control lines. Often, up to 10,000-pF capacitors on the data and strobe lines were used. Figure 11 shows a typical pre-IEEE Std 1284 application host solution. All capacitors and pullup and termination resistors are replaced by TI's discrete integrated bus-interface solution (dashed box around components in Figure 11) that provides efficient designs of parallel-port communication between the PC and peripheral.

Figure 11. Pre-IEEE Std 1284 Parallel-Port Host Solution

## IEEE Std 1284 Parallel-Port Solutions Using TI Bus-Interface Devices

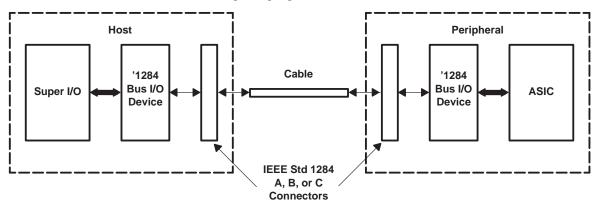

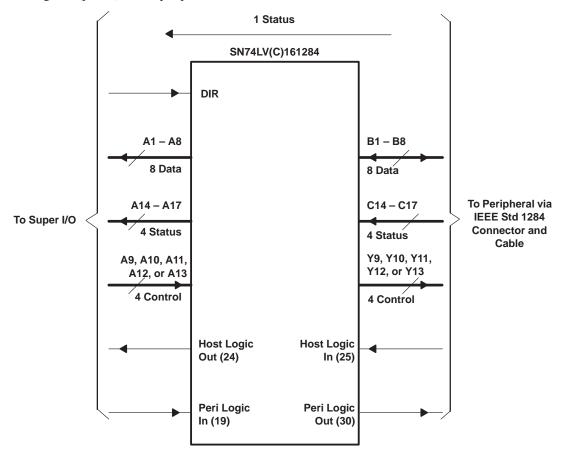

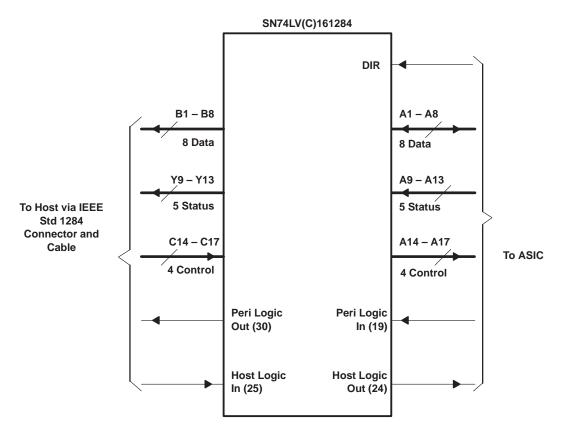

Figure 12 is a basic block diagram of an IEEE Std 1284 parallel port. Only one SN74LV161284 or SN74LVC161284 is used per side, but two SN74ACT1284 devices are required per port.

Figure 12. Block Diagram of Parallel Interface Port Between the PC and Peripheral

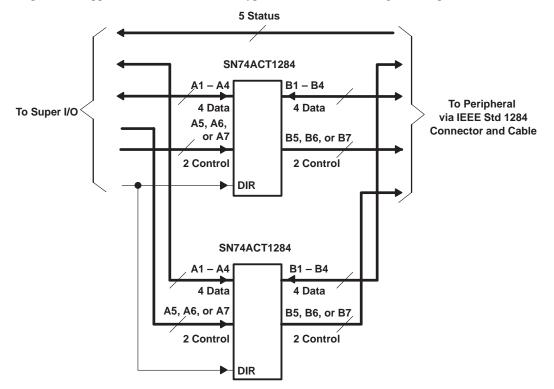

To illustrate how to apply the SN74ACT1284 as shown in Figure 12, Figures 13 and 14 explicitly show all data, control, and status lines from the Super I/O on the host side to the ASIC on the peripheral. The designer must decide which connector is suitable for a particular application and to what level type to set the devices using the HD pin.

Figure 13. IEEE Std 1284 Host Solution Using Two SN74ACT1284 Devices

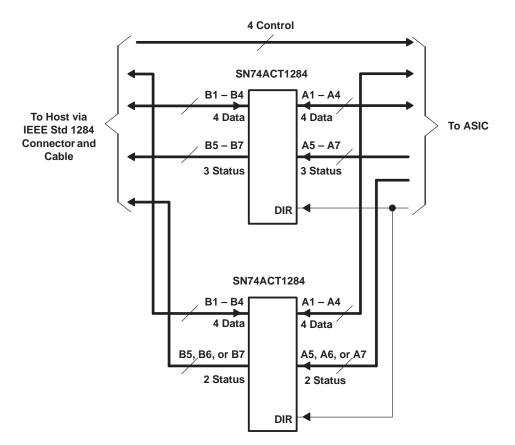

Figure 14. IEEE Std 1284 Peripheral Solution Using Two SN74ACT1284 Devices

While the SN74ACT1284 provides an acceptable two-chip solution, the SN74LV161284 and SN74LVC161284 devices provide optimum applicability—specifically, on the peripheral side. Figures 15 and 16 show all data, control, and status lines from the Super I/O on the host to the ASIC on the peripheral using these 19-bit bus interface devices.

Note that Host Logic In (pin 25) on the host side is connected via the IEEE Std 1284 connector and cable to Peri Logic Out (pin 30) on the peripheral. Likewise, Peri Logic Out (pin 30) on the host is connected the IEEE Std 1284 connector and cable to Host Logic In (pin 25) on the peripheral.

Figure 15. IEEE Std 1284 Host Solution Using the SN74LV161284 or SN74LVC161284

Figure 16. IEEE Std 1284 Peripheral Solution Using the SN74LV161284 or SN74LV161284

## Conclusion

This report gives a brief description of IEEE Std 1284-1994 and TI's logic solutions that conform to this standard. TI offers the bus interface SN74ACT1284, SN74LVC161284, and SN74LV161284 devices as complete solutions for a high-performance parallel port, and, as shown by laboratory data, the '161284 devices offer superior performance in back-drive current generation when compared to the competition. Furthermore, this report guides designers in choosing the correct bus interface device in their IEEE Std 1284 applications.

## Acknowledgment

The authors of this report are Nadira Sultana and Manny Soltero.

## **Commonly Asked Questions**

1. How is the SN74LVC161284 used with a parallel port?

The *Application Information* section of this application report, in conjunction with Figures 15 and 16, explains how to use the 'LVC161284 with the parallel port, whether it is on the host side or on the peripheral side.

2. If somebody wants an IEEE Std 1284 compliant design, is an IEEE Std 1284 transceiver required? What is so special about the SN74ACT1284, SN74LV161284, and SN74LVC161284?

To comply fully with IEEE Std 1284, one of TI's IEEE Std 1284 transceiver solutions should be used. Separate device descriptions are discussed in full, and one can see that these devices are the optimum choice.

3. How does the back-drive current of these devices compare to our competition?

The *Features and Benefits* section of this application report shows the excellent performance of the back-driving current of the SN74LVC161284. The SN74LV61284 has similar performance.

4. IEEE Std 1284 calls for series termination resistors on the driver lines before the pullup resistors. What is TI's recommendation for those termination resistors? Are they already included in the device (SN74ACT1284, SN74LVC161284, SN74LV161284)?

The SN74ACT1284 does not have any series termination resistors, but the other two parts have  $33-\Omega$  series termination resistors included in the part to conform to IEEE Std 1284. An external  $33-\Omega$  series resistor must be connected if the SN74ACT1284 is used.

5. What is the driver configuration for an IEEE Std 1284 level-1 driver?

The driver configuration for an IEEE Std 1284 level-1 driver is open drain.

6. Can the SN74LVC161284 be used on the host as well as on the peripheral side?

Yes, the SN74LVC161284 can be used on the host side, but it is optimized for use on the peripheral side. However, on the host side, one status line cannot be buffered through the device. Figures 15 and 16 show this in detail.

7. If someone does not want to use Host Logic and Peri Logic, what should be done with those terminals—tie them high, or low, or leave them open?

If the signal from the transmitting side is not to be used on their end, leave it open on the receiving side. However, the other signal should be driven true so that the other end of the cable sees it and can use it for better signal reliability.

# Glossary

| ASIC              | Application-Specific Integrated Circuit |

|-------------------|-----------------------------------------|

| Е                 |                                         |

| ECP               | Extended-Capabilities Port              |

| EPP               | Enhanced Parallel Port                  |

| Η                 |                                         |

| HD                | High Drive                              |

| 0                 |                                         |

| OEC <sup>TM</sup> | Output Edge-Rate Control                |

| Ρ                 |                                         |

| PC                | Personal Computer                       |

Α