20 2002

# PC-1600/2100 Stacked Registered DIMM Module

### **PLL Clock Driver**

| NAME<br>CDCV857B | CDCV857B<br>+/- 50 ps static     | R-DIMM<br>DDR-333 |  |

|------------------|----------------------------------|-------------------|--|

|                  | phase offset                     | )                 |  |

| CDCV857/A        | +/- 75 ps static<br>phase offset | DDR<br>200/266    |  |

## SN74SSTV32852 24:48 Bit Registered Buffer

- · Designed for 2.5-V operation

- SSTL\_2 compatible I/O's

- Differential Clock Inputs(CLK&/CLK)

- · LVCMOS switching levels on /RESET input

- /RESET input disables differential input receivers, resets all registers, and forces all outputs low.

- · Pinout optimizes DIMM PCB layout

- · Only one device per DIMM is required

- Designed specifically for 1U low-profile DIMM applications

- · Samples available

- Production Released

## **Registered Memory Buffers**

| NAME           | Device Description                             | R-DIMM            |

|----------------|------------------------------------------------|-------------------|

| SN74SSTV16857  | 14-Bit Registered Buffer With SSTL_2           | PC-1600/2100/2700 |

| SN74SSTVF16857 | Inputs and Outputs                             |                   |

| SN74SSTV16859  | 13-Bit to 26-Bit Registered Buffer with SSTL_2 | PC-1600/2100/2700 |

|                | Inputs and Outputs                             | Stacked R-DIMM    |

| SN74SSTV32852  | 24-Bit to 48-Bit Registered Buffer with SSTL_2 | PC-2400/2700      |

|                | Inputs and Outputs                             | Stacked R-DIMM    |

| SN74SSTV32867  | 26-Bit Registered Buffer with SSTL_2           | PC-2400/2700      |

|                | Inputs and LVCMOS Outputs                      |                   |

| SN74SSTV32877  | 26-Bit Registered Buffer with SSTL_2           | PC-2400/2700      |

|                | Inputs and Outputs                             |                   |

# **Recommended Registered Buffers**

| DIMM Configuration                                | 133 MHz<br>PC1600/2100JEDEC<br>1.7"TSOP DRAMs                  | 133 MHz PC1600/2100<br>1U Low ProfileTSOP<br>DRAMs               | 167 MHz PC2700<br>1U Low Profile BGA<br>DRAMs                 |

|---------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|

| 1 Bank x8<br>9 SDRAMs                             | Raw Card A<br>2 x SSTV16857<br>48-pin TSSOP<br>9 Loads/Output  | Raw Card L<br>2 x SSTV16857<br>48-pin TSSOP<br>9 Loads/Output    | Raw Card A<br>2 x SSTV16857<br>48-pin TSSOP<br>9 Loads/Output |

| 2 Banks x 8 (18 SDRAMs)<br>1 Bank x 4 (18 SDRAMs) | Raw Card A/B 2 x SSTV1685748-pin TSSOP 18 Loads/Output         | Raw Card L/M 2 x SSTV1685748-pin TSSOP 18 Loads/Output           | Raw Card B/C 2 x SSTV16859 64-pin TSSOP 9 Loads/Output        |

| 2 Banks x 4 (36 SDRAMs)                           | Raw Card C<br>2 x SSTV16859<br>64-pin TSSOP<br>18 Loads/Output | Raw Card N<br>1 x SSTV32852<br>114-ball LFBGA<br>18 Loads/Output | Raw Card D In<br>Development                                  |

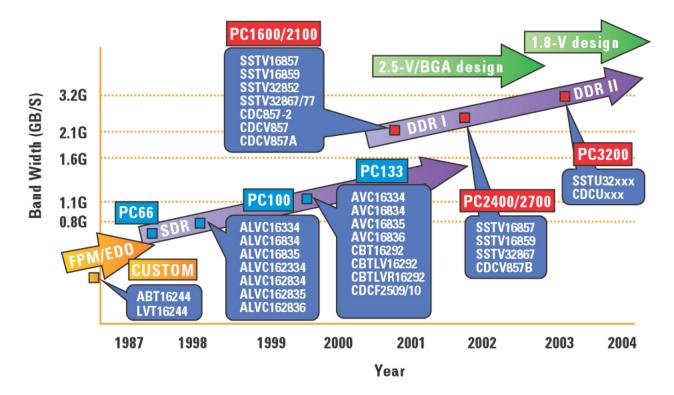

# Logic Roadmap for High-Speed Memory Interface

For more information about logic, go to: www.ti.com/sc/logic

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated