# Interfacing the ADS8332 to TMS320F28335 DSP

Dale Li

High Performance Analog

## ABSTRACT

This application report presents a solution for interfacing the 8-channel, 16-bit successive approximation register (SAR), analog-to-digital converter (ADC) ADS8332, to the serial peripheral interface (SPI) port of the TMS320F28335 DSP. The main focus of this report is the TMS320F28335 SPI port's configuration and initialization and the ADS8332's software control. The software demonstrates how to achieve exact conversion control by using the DSP timer and configure an external interrupt receiver on the DSP to collect the conversion result. The sample code described in this application report can be downloaded from http://www.ti.com/lit/zjp/SLAA551.

#### CONTENTS

### Introduction

| 1 | Introduction                    | 2 |

|---|---------------------------------|---|

| 2 | ADS8332 interface               | 3 |

| 3 | TMS320F28335 SPI interface      | 4 |

| 4 | ADC Configuration and Operation | 6 |

| 5 | Conclusion                      | 7 |

| 6 | Reference                       | 7 |

#### FIGURES

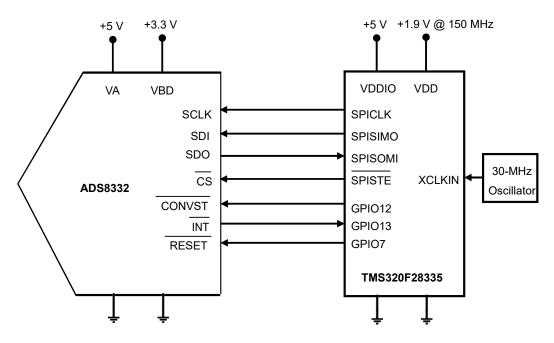

| Figure 1. | Hardware Connection2          |

|-----------|-------------------------------|

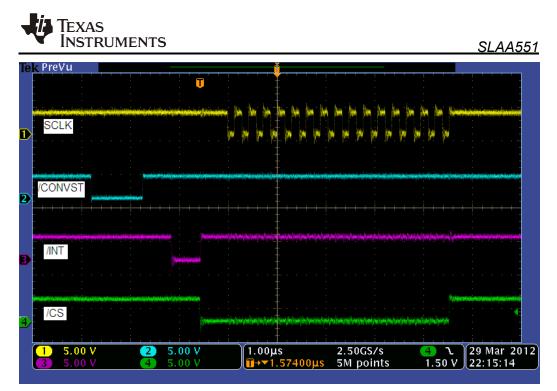

| Figure 2. | Screenshot of General Timing7 |

#### **TABLES**

| Table 1. | Different Types of Conversion Modes          | 3 |

|----------|----------------------------------------------|---|

| Table 2. | ADS8332 to TMS320F28335 Interface Definition | 4 |

| Table 3. | SPI Clocking Scheme                          | 4 |

## 1. Introduction

The ADS8332 is an 8-channel, 16-bit, 500 Kilosamples-per-second (KSPS), SAR, ADC with SPI interface and non-simultaneous sampling ADC with internal unipolar 8-to-1 input multiplexer. The ADS8331 offers the same core with a 4-channel option. This application report presents a hardware and software solution for interfacing and using the ADS8332 with the popular TMS320F28335 Digital Signal Processor (DSP™). The software for this report was developed with *Code Composer Studio*<sup>™</sup> V3.3 based on the eZdsp<sup>™</sup> F28335 from Spectrum Digital Incorporated and the ADS8332EVM from Texas Instruments. This sample code uses Timer0 of the TMS320F28335 DSP to create exact sampling control by general purpose I/O (GPIO) and uses external interrupt to collect 8192 samples from the ADS8332 data converter. Search "Interfacing the ADS8332 to the TMS320F28335" on the <u>www.ti.com</u> website for the associated software in zip format.

Figure 1. Hardware Connection

# 2. ADS8332 Interface

An internal oscillator in the ADS8332 can be used as the conversion clock (CCLK) source and also can be programmed to run the conversions using the external CPU's serial clock (SCLK). For simplicity, this report uses the internal oscillator.

The ADS8332 requires 18 conversion clock (CCLK) cycles to complete a conversion, and the minimum acquisition and sampling time is 3 CCLKs. The minimum time between two consecutive CONVST signals for the ADS8332 is 21 CCLKs (1826 ns with an 11.5-MHz typical internal CCLK).

The ADS8332 is programmable for Manual Channel Select mode, enabled through the configuration register (CFR) by setting the CFR\_D11 bit to 0, and then the desired channel is selected by writing to the command register (CMR). Auto Channel Select mode is enabled by setting the CFR\_D11 bit to 1, the first conversion is always from the channel of the last conversion completed before this mode is enabled.

The ADS8332 is configured for Manual-Trigger Mode by setting the CFR\_D9 bit to 1, the conversion can be initiated on the falling of the CONVST signal. Auto-Trigger Mode can also be selected by setting the CFR\_D9 bit to 0, automatically start conversion without CONVST signal.

Table 1 summarizes the different conversion modes.

| Mode      | Select Channel                     | Start Conversion                     |

|-----------|------------------------------------|--------------------------------------|

|           | Auto Channel Select                | Auto-Trigger Mode                    |

| Automatic | No need to write channel number.   | Start conversion based on conversion |

|           | Use internal sequence for ADS8332. | clock CCLK                           |

| Manual    | Manual Channel Select              | Manual-Trigger Mode                  |

| Manual    | Write channel number to CMR        | Start conversion with CONVST         |

#### Table 1. Different Types of Conversion Modes

### Tips:

- 1. The conversion result can be read while converting or sampling; read while sampling, the data is the current conversion result, read while converting, the data is the previous conversion result.

- 2. The output data should be read during one conversion period, it depends on the sampling rate and SCLK frequency of DSP SPI port.

- 3. Select Auto Channel Select mode to reduce the DSP's resource allocation. To implement the desired sampling rate, Manual-Trigger is often used. Both are used in this report.

- 4. The ADS8332 also supports three power-down modes to reduce power dissipation; Nap, Deep, and Auto-Nap. For most industrial applications, it's not necessary, so this report does not use these power-down modes.

3

### <u>SLAA551</u>

Table 2 shows the connections required for interfacing the ADS8332 to the TMS320F28335 DSP.

| DSP Pin No.<br>(PGF package) | DSP Pin<br>function | ADC Pin No.<br>(TSSOP | Signal Description                            |

|------------------------------|---------------------|-----------------------|-----------------------------------------------|

|                              |                     | package)              |                                               |

| 62                           | SPICLK              | 10                    | SPI clock for serial interface (SCLK)         |

| 27                           | SPISIMO             | 12                    | SPI serial data in (SDI)                      |

| 28                           | SPISOMI             | 13                    | SPI serial data out (SDO)                     |

| 63                           | SPISTE              | 11                    | Chip select input for SPI ( $\overline{CS}$ ) |

| 21                           | GPIO12              | 15                    | Conversion start ( CONVST )                   |

| 24                           | GPIO13              | 9                     | Status output (EOC/ INT /CDI)                 |

| 16                           | GPIO7               | 8                     | External reset ( RESET )                      |

### Table 2. ADS8332 to TMS320F28335 Interface Definition

## 3. TMS320F28335 SPI Interface

Configure the SPI port of TMS320F28335 as the master by setting the MASTER/SLAVE bit to *1* (SPICTL.2) in spi\_init() of mail.c.

## 3.1 SPI Clocking Schemes and Setting

The SPI's CLOCK POLARITY bit (SPICCR.6) and the CLOCK PHASE bit (SPICTL.3) control four different clocking schemes on the SPICLK pin as following: the CLOCK POLARITY bit selects the active edge, either rising or falling of the clock, the CLOCK PHASE bit controls the phase of the SPICLK signal. These two bits can be set in spi\_init() of mail.c.

| Clock Polarity<br>(SPICCR.6) | Clock Phase<br>(SPICTL.3) | Clocking Scheme Description                                          |

|------------------------------|---------------------------|----------------------------------------------------------------------|

| 0                            | 0                         | Transmits data on the rising edge and receives data on the falling   |

| 0                            | 5                         | edge of SPICLK                                                       |

| 0                            | 1                         | Transmits data one half-cycle ahead of the rising edge and receives  |

| 0                            | I                         | data on the rising edge of the SPICLK                                |

| 1                            | 0                         | Transmits data on the falling edge and receives data on the rising   |

| I                            | 0                         | edge of the SPICLK                                                   |

| 1                            | 1                         | Transmits data one half-cycle ahead of the falling edge and receives |

| I                            | Ι                         | data on the falling edge of the SPICLK                               |

Table 3. SPI Clocking Scheme

Because the ADS8332's output data bits are valid on the falling edge of SCLK with the  $t_{D2}$  delay (Figure 3 in the ADS8332's datasheet) and the data input is read on the falling edge of SCLK, so the SPI Clocking Scheme of TMS320F28335 can be configured to 00 or 11 (Clock Polarity : Clock Phase).

The SPI baud rate is decided by SPI SPIBRR register and LSPCLK. LSPCLK is decided by LOSPCP register and SYSCLKOUT. SYSCLKOUT is determined by OSCCLK (XCLKIN), PLLCR[DIV] and PLLSTS[DIVSEL] registers. LOSPCP can be found in DSP2833x\_SysCtrl.c, PLLCR and PLLSTS[DIVSEL] in DSP2833x\_Examples.h.

SPI Baud Rate =

$$\frac{\text{LSPCLK}}{(\text{SPIBRR + 1})} = \frac{\text{SYSCLKOUT}}{(\text{SPIBRR + 1}) * (\text{LOSPCP * 2})}$$

Where:

LSPCLK = Low-speed peripheral clock

SPIBRR = SPI baud-rate register

LOSPCP = Low-speed peripheral clock prescaler register

SYSCLKOUT = System clock

OSCCLK = CLKIN = External oscillator clock

PLLCR = PLL control register

PLLSTS = PLL status register

In the software code for this report, the default values: PLLCR = 10, PLLSTS = 2,

SYSCLKOUT=

$$\frac{OSCCLK^* \ 10}{2} = \frac{XCLKIN^* \ 10}{2} = \frac{30MHz^*}{2} \ 10 = 150MHz$$

The default value for LOSPCP is 2(0x0002) in InitPeripheralClocks() of DSP2833x\_SysCtrl.c, SPIBRR is set to 10 (0x000A) in spi\_init() of main.c, so

SPI Baud Rate =

$$\frac{\text{SYSCLKOUT}}{(\text{SPIBRR + 1}) * (\text{LOSPCP * 2})} = \frac{150\text{MHz}}{11 * 4} = 3.4\text{MHz}$$

The maximum SPI clock frequency the ADS8332 can accept is 40 MHz.

## 3.2 GPIO Pin Functions Setting

GPIO12, 13 and 7 pins are selected as a connection to ADS8332. DSP's GPAMUX1 register can configure these pins as GPIO function. When GPIO12 is configured as an output, it is assigned to the CONVST function. When GPIO13 is configured as an input, it is assigned to the INT function as an interrupt input from ADS8332. GPIO7 is configured as an output and assigned to RESET to ADC. The GPADIR register determines these GPIO's direction (input or output), the GPASET or GPACLEAR register decides the initialization status of these pins.

### 3.3 Timer Initialization and Configuration

In DSP2833x\_CpuTimers.c, InitCpuTimers(void) is used to initialize CPU timers to a known state, ConfigCpuTimer(struct CPUTIMER\_VARS \*Timer, float Freq, float Period) is used to configure the selected timer (Timer0) to the specified period, here the *Freq* should be entered as *MHz* and the Period in *µSeconds*.

The Timer0 can be used to create an exact sampling control with GPIO12 pin as CONVST signal to ADS8332 ADC in Timer0 interrupt service subroutine of the main.c file. One CONVST pulse is created for one interrupt. The Sampling\_Period in main.c is used to set the Timer0 interrupt interval. When the Sampling\_Period is set to 1000, Timer0 creates one Timer interrupt per 1000 µs, this means that the sampling rate of the ADS8332 is 1 KSPS. If the Sampling\_Period is set to 10, the sampling rate of the ADS8332 is 100 KSPS.

## 3.4 External Interrupt Setting

GPIO13 of the DSP is selected by GPIOXINT1SEL register as XINT1 external interrupt input in main.c file. XINT1CR external interrupt control register in main.c determines whether the interrupts are triggered on the rising edge, the falling edge of a signal or both the rising and falling edges on the GPIO13 pin. The falling edge is default for this application report.

5

# 4. ADC Configuration and Operation

# 4.1 RESET

Except internal power-on reset (POR) and software reset, an external reset signal can be used to RESET pin of ADS8332 from GPIO7 of DSP, this pin must be held at low pulse for a minimum of 25 ns to reset the device and return to default mode.

## 4.2 INT

The status output pin can be programmed as an EOC or  $\overline{\text{INT}}$  output, it is set as interrupt output,  $\overline{\text{INT}}$  in this report. The pin is low (default) after the end of conversion and returns high after  $\overline{\text{CS}}$  goes low. The polarity of this pin can be programmed through the D7 bit of ADS8332's CFR register.

# 4.3 CS

6

The SPISTE signal from the DSP can be connected to the CS pin of ADS8332 as Chip Select function. This pin is automatically driven low by the DSP before transmitting data to the ADS8332 and is taken high after the transmission is complete.

## 4.4 Writing and Reading Register/Data

There are two different types of writes to the register of the ADS8332: a 4-bit write to the CMR register and a full 16-bit write to the CMR plus CFR registers. A simple write for Manual Channel Selection, Wake up and Default mode only needs four SCLKs. A 16-bit writing CFR or reading CFR/Data takes at least 16 SCLKs. Only writing to the CFR register requires a 4-bit CMR command followed by 12 bits of valid data to the CFR register.

The conversion result can be read through the SDO pin of the ADS8332 in DSP's interrupt service subroutine of main.c. Data output from the SDO is left-adjusted MSB first. The output data bits are valid on the falling edge of SCLK. Generally 16 SCLKs are necessary, depending on read mode.

## 4.5 Starting Conversion

ADS8332's conversion for Manual-Trigger mode can be initiated by bringing the CONVST pin (GPIO12 from DSP) low for a minimum of 40 ns and then brought high, at the same time the acquisition and sampling phase is ended. The ADS8332 switches from conversion to acquisition and sampling mode on the falling edge of the INT signal.

Channel selection can also be done automatically if Auto Channel Select mode is selected (default status in the software code for this application report). The signals from all channels are converted in a fixed order. The channels are scanned sequentially and automatically.

Figure 2. Screenshot of General Timing

# 5. Conclusion

This application report introduces a solution for interfacing the ADS8332 converter to the TMS320F28335 DSP, including hardware connection, software configuration and control. The software from this report can be used as sample code when developing specific application software. This application report is also suitable for ADS8331 ADC from Texas Instruments.

# 6. Reference

- 1. ADS8332, ADS8331 datasheet (SBAS363C)

- 2. TMS320x2833x, 2823x Data Manual (SPRS439M)

- 3. TMS320x2833x, 2823x System Control and Interrupts Reference Guide (SPRUFB0D)

- 4. TMS320x2833x, 2823x Serial Peripheral Interface (SPI) Reference Guide (SPRUEU3A)

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated