# An Introduction to the ADS7863A

Tom Hendrick

Precision Analog – Energy Solutions Products

### ABSTRACT

This application note presents an introduction to the ADS7863A; a dual, 12-bit, 2x2 or 3x3 channel, simultaneous sampling analog-to-digital converter (ADC). The ADS7863A is an updated version of the ADS7863 with a higher degree of flexibility in the digital interface to the chip. This application note compares and contrasts the changes to the ADS7863 and provides some application tips and tricks to successfully implement the ADS7863A in new or existing designs.

### Contents

| 1 | Introduction                                          | .1 |

|---|-------------------------------------------------------|----|

| 2 | ADS7863 versus ADS7863A                               | .2 |

| _ | 2.1 ADS7863 RD Width                                  |    |

|   | 2.2 ADS7863 RD Timing                                 |    |

| 3 | Application Tips and Tricks with the revised ADS7863A |    |

### Figures

| Figure 1.   | Required Timing of the RD Pulse |

|-------------|---------------------------------|

| i igai e i. |                                 |

### Tables

| Table 1. | Pin State and Channel Selection Method | .2 |

|----------|----------------------------------------|----|

|          | Serial Data Ouput Format               |    |

|          | RD Signal Anomalies                    |    |

## 1 Introduction

The ADS7863A is configurable as a 2x2 channel (four fully-differential inputs) or 3x3 channel (six pseudo-differential inputs), simultaneously sampling 12–bit ADC, capable of sampling at rates up to 2MSPS. The inputs are grouped in two pairs, A and B, with independent sample and holds followed by two independent ADC channels. The conversion results are then presented via two serial data output lines for operation at full speed. For applications utilizing one serial bus, the ADS7863A can be configured to use a single serial output for both A and B channel conversion results. To ease the identification of conversion data, channel ID bits are inserted into the conversion results starting with the first two serial clocks applied to the ADS7863A.

As with the original ADS7863, control of the serial outputs and sampling scheme are accomplished by using dedicated MODE pins, M0 and M1. The Table 1 shows the pin state with the resultant channel selection method and serial output(s) used.

| Mode | M0 Pin | M1 Pin | Channel Selection                       | SDOx Used     |

|------|--------|--------|-----------------------------------------|---------------|

| I    | 0      | 0      | Manual (via serial data input commands) | SDOA and SDOB |

| II   | 0      | 1      | Manual (via serial data input commands) | SDOA only     |

| III  | 1      | 0      | Automatic sequencing                    | SDOA and SDOB |

| IV   | 1      | 1      | Automatic sequencing                    | SDOA Only     |

There are also two special modes associated with Mode II and Mode IV (SMII and SMIV). These special operating modes allow both channel conversion results to be read out of the ADS7863A with a single RD impulse.

As with the ADS7863, the ADS7863A also helps simplify the identification of channel conversion data by outputting two bits ahead of the conversion results. The following table represents the serial data output format.

Table 2.

Serial Data Output Format

| Clock<br>Cycle | 1     | 2     | 3    | 4    | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15 | 16 |

|----------------|-------|-------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|

| SDO            | CH0/1 | CHA/B | DB11 | BD10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | BD0 | 0  | 0  |

# 2 ADS7863 versus ADS7863A

Depending on the mode setting of the original ADS7863, the width and timing of the RD signal could cause unexpected behavior in the serial output data. Corrupted data, repeated data, or the swapping of channel number and pair bits were observed. The following sections describe this in more detail.

# 2.1 ADS7863 RD Width

Table 3 describes the observed anomalies depending on the width of the RD signal of the original ADS7863.

| Mode | Maximum Length of RD | What happens if RD is longer?                                                                                                                                          |

|------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I    | Max 16 clocks        | A second transfer is initiated                                                                                                                                         |

| II   | Max 2 clock periods  | ADC bit is inverted if RD falls before EOC. Data is corrupt when RD falls within data output, that is, after 4 clocks. No data comes out when RD is falling after EOC. |

|      | Max 1 clock period   | If RD is falling after 2 clocks, the channel info bits are swapped. If RD is                                                                                           |

Table 3.RD Signal Anomalies

|      |                    | falling after LSB, data is corrupt.                                                                                                                                                                                                                                                                                   |

|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IV   | Max 1 clock period | If RD is falling after 2 clocks, only the channel bit of A is inverted. If RD is falling after 3 clocks, the A channel bit and the ADC bits are inverted. The channel bit of B is correct. Data is corrupt when RD falls within data output, that is, after 4 clocks. No data comes out when RD is falling after EOC. |

| SMII | Max 32 clocks      | A second transfer is initiated                                                                                                                                                                                                                                                                                        |

| SMIV | Max 1 clock period | If RD is falling after 2 or 3 clocks, only the channel bit of A is inverted. If RD is falling after 18 clocks (during channel bit of B), both channel bits are inverted.                                                                                                                                              |

# 2.2 ADS7863 RD Timing

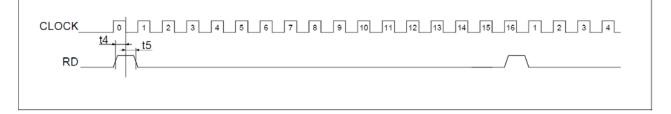

The timing of the RD signal is described relative to the falling clock edge with 10 ns (t4) setup time and 5 ns (t5) hold time. In synchronous serial systems, such as the multi-channel buffered serial port (McBSP) of the TMS320 series processors, meeting the setup and hold requirement minimums are possible. After the introduction of the ADS7863, however, it was discovered that an additional 4 ns delay before the next rising serial clock was necessary. The information in Figure 1 describes the required timing of the RD pulse.

|                |                                          |                  | ADS |                         |      |

|----------------|------------------------------------------|------------------|-----|-------------------------|------|

| SYMBOL         | PARAMETER                                | COMMENTS         | MIN | MAX                     | UNIT |

| t <sub>4</sub> | RD high setup time to CLOCK falling edge | See figure above | 10  |                         | ns   |

| t <sub>5</sub> | RD high hold time to CLOCK falling edge  | See figure above | 5   | t <sub>сьоск</sub> /2-4 | ns   |

## Figure 1. Required Timing of the RD Pulse

# 3 Application Tips and Tricks with the revised ADS7863A

With the release of the ADS7863A, the issues noted above have been addressed and the original ADS7863 has been placed on the Not Recommended for New Designs (NRND) list. Existing applications using the ADS7863, with the timing restrictions noted in section 2.2 above, will not be impacted by using the ADS7863A. Designs which use the ADS7861 will find it easier to upgrade to the ADS7863A as well.

Applications that remapped any swap in channel ID bits must revise the codes associated with the ADS7863A to correctly store the channel data. For additional support on the ADS7863 or the ADS7863A, please contact us through the <u>Precision Data Converter Forum</u>.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated