# **DAVREF633**

Design Guidelines for the TAS5086 Six-Channel Digital Audio PWM Processor and TAS5111/TAS5112A Digital Amplifier Power Output Stage—Single-Ended Configuration

# Design Guide

December 2004

**Digital Audio Group**

SLEU059

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Applications

Wireless

www.ti.com/wireless

#### Products

| amplifier.ti.com       | Audio                                                                                  | www.ti.com/audio                                                                                                                                                          |

|------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dataconverter.ti.com   | Automotive                                                                             | www.ti.com/automotive                                                                                                                                                     |

| dsp.ti.com             | Broadband                                                                              | www.ti.com/broadband                                                                                                                                                      |

| interface.ti.com       | Digital Control                                                                        | www.ti.com/digitalcontrol                                                                                                                                                 |

| logic.ti.com           | Military                                                                               | www.ti.com/military                                                                                                                                                       |

| power.ti.com           | Optical Networking                                                                     | www.ti.com/opticalnetwork                                                                                                                                                 |

| microcontroller.ti.com | Security                                                                               | www.ti.com/security                                                                                                                                                       |

|                        | Telephony                                                                              | www.ti.com/telephony                                                                                                                                                      |

|                        | Video & Imaging                                                                        | www.ti.com/video                                                                                                                                                          |

|                        | dataconverter.ti.com<br>dsp.ti.com<br>interface.ti.com<br>logic.ti.com<br>power.ti.com | dataconverter.ti.comAutomotivedsp.ti.comBroadbandinterface.ti.comDigital Controllogic.ti.comMilitarypower.ti.comOptical Networkingmicrocontroller.ti.comSecurityTelephony |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas. Texas 75265

Copyright © 2005, Texas Instruments Incorporated

#### Preface

### **Read This First**

#### About This Manual

1

This manual describes design guidelines for the DAVREF633 reference design from Texas Instruments.

#### How to Use This Manual

This document contains the following chapters:

- □ Chapter 1 Introduction

- Chapter 2 System Interfaces

- □ Chapter 3 Protection

- □ Chapter 4 Performance Graphs

- □ Chapter 5 System Setup and Debugging

- Chapter 6 Bill of Materials, Layout, and Schematics

#### Information About Cautions and Warnings

This book may contain cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to <u>you</u>.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

#### **Related Documentation From Texas Instruments**

The following table contains a list of data sheets that have detailed descriptions of the integrated circuits used in the design of the DAVREF633 board. These items can be obtained at the URL http://www.ti.com.

| Document Title                                                          | Literature<br>Number |

|-------------------------------------------------------------------------|----------------------|

| TAS5086 data sheet                                                      | N/A                  |

| TAS5111 Digital Amplifier Power Stage data sheet                        | SLES049              |

| TAS5112A Digital Amplifier Power Stage data sheet                       | SLES094              |

| System Design Considerations for True Digital Audio Power<br>Amplifiers | SLAA117              |

#### FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### Trademarks

Equibit and PurePath Digital are trademarks of Texas Instruments.

Windows is trademark of Microsoft Corporation.

Other trademarks are the property of their respective owners.

# Contents

| 1 | Intro  | luction                                                | 1-1 |

|---|--------|--------------------------------------------------------|-----|

|   | 1.1    | DAVREF633 Features                                     | 1-3 |

|   | 1.2    | Reference Layout                                       |     |

| 2 | Syster | n Interfaces                                           | 2-1 |

|   | 2.1    | Power Stage-to-PSU Interface                           | 2-2 |

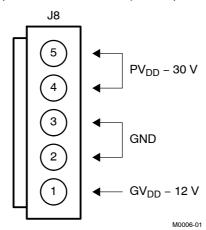

|   | 2.2    | PSU Connector (J8)                                     | 2-3 |

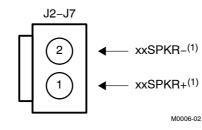

|   | 2.3    | Loudspeaker Connectors (J2–J7)                         | 2-3 |

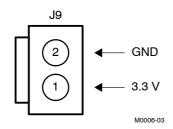

|   | 2.4    | Digital Power-Supply Connector (J9)                    |     |

|   | 2.5    | Digital Audio and Control Interface (J1)               |     |

| 3 | Prote  | ction                                                  | 3-1 |

|   | 3.1    | Short-Circuit Protection and Fault-Reporting Circuitry | 3-2 |

|   | 3.2    | Device Fault Reporting                                 | 3-2 |

| 4 | Perfor | mance Graphs                                           | 4-1 |

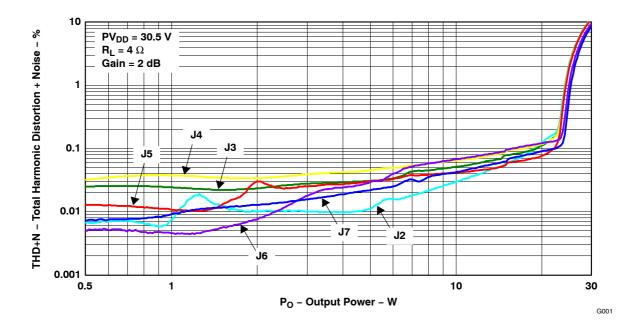

|   | 4.1    | THD+N vs Power                                         | 4-2 |

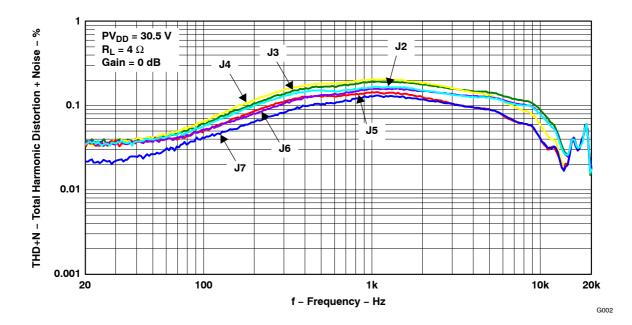

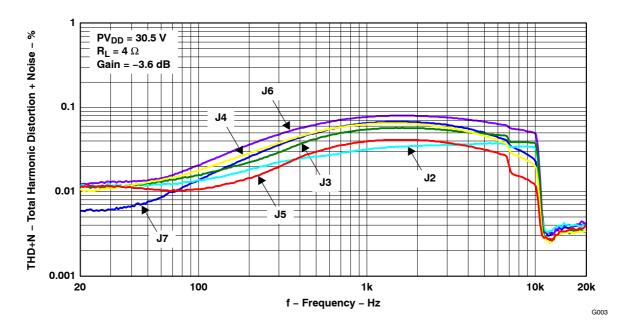

|   | 4.2    | THD+N vs Frequency                                     | 4-2 |

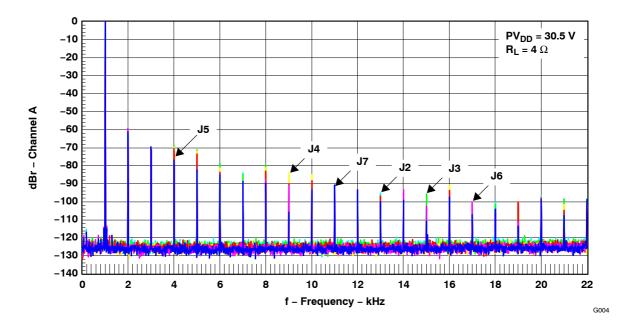

|   | 4.3    | FFT                                                    | 4-3 |

|   | 4.4    | FFT at -60 dB (Dynamic Range and Integrated Noise)     | 4-4 |

|   | 4.5    | Frequency Response                                     | 4-4 |

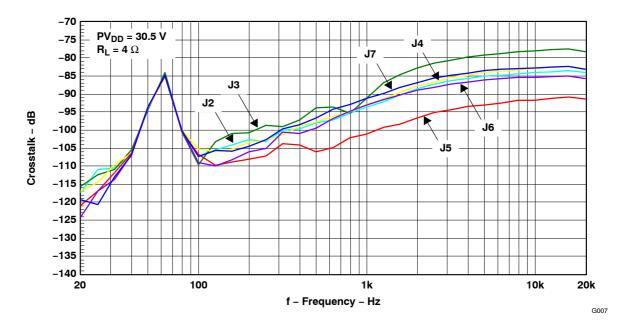

|   | 4.6    | Crosstalk vs Frequency                                 | 4-5 |

| 5 | Syster | n Setup and Debugging                                  | 5-1 |

|   | 5.1    | Hardware Setup                                         | 5-2 |

|   | 5.2    | Software Setup                                         | 5-2 |

|   | 5.3    | Debugging                                              | 5-3 |

# Figures

|     |                                             | _ |

|-----|---------------------------------------------|---|

| 1–1 | PurePath Digital System                     | 2 |

| 1–2 | Layout for the DAVREF633 (Rough Outline)1-  | 3 |

| 2–1 | Recommended Power–Up Sequence               | 2 |

| 2–2 | J8 Pin Numbers (PCB Connector, Top View)    | 3 |

| 2–3 | J2–J7 Pin Numbers (PCB Connector, Top View) |   |

| 2–4 | J9 Pin Numbers                              | 1 |

| 4–1 | THD+N vs Power                              | 2 |

| 4–2 | THD+N vs Frequency at 0 dB 4-2              | 2 |

| 4–3 | THD+N vs Frequency at 10 W 4-3              | 3 |

| 4–4 | FFT, 1-kHz Sine Wave at 0 dB 4-3            | 3 |

| 4–5 | FFT, i-kHz Sine Wave at –60 dB 4-4          | 1 |

| 4–6 | Frequency Response 4-4                      | 1 |

| 4–7 | Crosstalk vs Frequency 4-5                  | 5 |

|     |                                             |   |

# **Tables**

| 2–1 | Recommended Power Supplies                | . 2-2 |

|-----|-------------------------------------------|-------|

|     | J8 Pin Description                        |       |

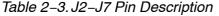

| 2–3 | J2–J7 Pin Description                     | . 2-3 |

| 2–4 | J9 Pin Description                        | . 2-4 |

| 2–5 | J1 Pin Description                        | . 2-5 |

| 5–1 | Debugging the DAVREF633 Digital Interface | . 5-3 |

| 5–2 | Debugging the TAS5086                     | . 5-4 |

| 5–3 | Debugging the Power Stage                 | . 5-6 |

### Introduction

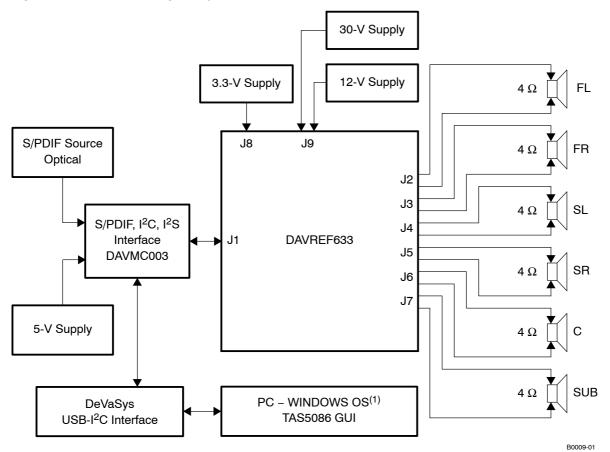

The DAVREF633 PurePath Digital<sup>™</sup> reference design demonstrates three integrated circuits, TAS5086DBT, TAS5112ADFD, and TAS5111DAD from Texas Instruments (TI).

The TAS5086 is a high-performance 32-bit (24-bit input) multichannel PurePath Digital pulse-width modulator (PWM) based on Equibit<sup>™</sup> technology with a fully symmetrical AD modulation scheme. The device also has integrated bass management and downmixing capabilities.

The power stages are high-performance digital amplifiers. In this reference design, they are designed to drive four 4- $\Omega$  loudspeakers up to 20 W at 10%THD+N (TAS5112ADFD) in the single-ended (SE) configuration, and two 4- $\Omega$  loudspeakers up to 25 W at 10% THD+N (TAS5111DAD) in the SE configuration. Each power stage has integrated gate drivers, matched and electrically isolated enhancement-mode N-channel power DMOS transistors, and protection/fault-reporting circuitry.

The DAVREF633 reference design is configured with six SE channels. This reference design, together with a TI input design DAVMC003 and DeVaSys USB-I<sup>2</sup>C interface, is a complete 6-channel digital audio amplifier system which includes digital input (S/PDIF). This reference is intended for home theater applications such as DVD mini-component systems, home theater in a box (HTIB), DVD receivers, or plasma display panels (PDP).

#### Topic

#### Page

| 1.1 | DAVREF633 Features | 1-3 |

|-----|--------------------|-----|

| 1.2 | Reference Layout   | 1-3 |

Figure 1–1. PurePath Digital System

<sup>(1)</sup> TAS5086 GUI can run on any Windows<sup>™</sup> OS that supports USB.

#### 1.1 DAVREF633 Features

- 6-channel PurePath Digital reference design

- Self-contained protection system (short-circuit and thermal)

- □ Standard I<sup>2</sup>S/I<sup>2</sup>C control connector for TI input board

- Designed for double-sided, plated-through, two-layer PCB

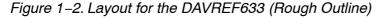

#### 1.2 Reference Layout

Layout for the DAVREF633 is illustrated in Figure 1–2.

# System Interfaces

This chapter describes the DAVREF633 reference design relative to the power supply unit (PSU) and system interfaces.

#### Topic

#### Page

| 2.1 | Power Stage-to-PSU Interface 2-2         |

|-----|------------------------------------------|

| 2.2 | PSU Connector (J8) 2-3                   |

| 2.3 | Loudspeaker Connectors (J2–J7) 2-3       |

| 2.4 | Digital Power-Supply Connector (J9) 2-4  |

| 2.5 | Digital Audio and Control Interface (J1) |

|     |                                          |

#### 2.1 Power Stage-to-PSU Interface

The DAVREF633 reference design must be powered from three external regulated power supplies. High audio performance requires a stabilized output-stage power supply with low ripple voltage and low output impedance.

Note: The length of the power supply cable must be minimized. Increasing the length of the PSU cable increases the distortion for the amplifier at high output levels and low frequencies.

Maximum output-stage supply voltage depends on the speaker load resistance. Check the recommended maximum supply voltage in the TAS5111 and TAS5112A data sheets.

Table 2–1. Recommended Power Supplies

| Description               | Voltage Limitations (4– $\Omega$ to 8– $\Omega$ Load) | Current<br>Recommendations |

|---------------------------|-------------------------------------------------------|----------------------------|

| System power supply       | 3.3 V                                                 | 0.25 A                     |

| Gate-drive supply         | 12 V                                                  | 0.25 A                     |

| Output power-stage supply | 0–30.5 V                                              | 5 A <sup>(1)</sup>         |

<sup>(1)</sup> The rated current corresponds to six channels full scale (25 W/4  $\Omega$  each), which is most likely adequate for a standard 6-channel amplifier design.

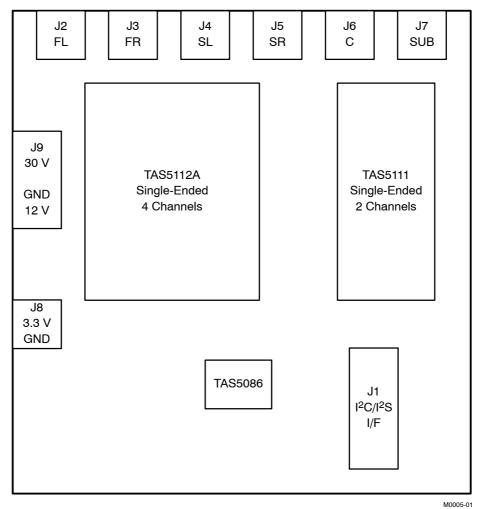

The recommended power-up sequence for both TAS5111 and TAS5112A is shown in Figure 2–1. For proper TAS5111/5112A operation, the RESET signal should be kept low during power up. RESET is pulled low for 200 ms during power up by the DAVMC003 S/PDIF–I<sup>2</sup>S–I<sup>2</sup>C interface board.

Figure 2–1. Recommended Power-Up Sequence

#### 2.2 PSU Connector (J8)

Figure 2–2. J8 Pin Numbers (PCB Connector, Top View)

Table 2–2. J8 Pin Description

| Pin | Net–Name in Schematics | Description                    |

|-----|------------------------|--------------------------------|

| 1   | GVDD                   | Gate-drive power supply (12 V) |

| 2   | GND                    | Ground                         |

| 3   | GND                    | Ground                         |

| 4   | PVDD                   | Power-stage supply (30 V)      |

| 5   | PVDD                   | Power-stage supply (30 V)      |

#### 2.3 Loudspeaker Connectors (J2–J7)

Both positive and negative speaker outputs are floating and must not be connected to ground (e.g., through an oscilloscope).

Figure 2–3. J2–J7 Pin Numbers (PCB Connector, Top View)

<sup>(1)</sup> xx = FL, FR, SL, SR, C, or SUB

| Pin | Net–Name in Schematics | Description             |

|-----|------------------------|-------------------------|

| 1   | xxSPKR+                | Speaker positive output |

| 2   | xxSPKR-                | Speaker negative output |

#### 2.4 Digital Power-Supply Connector (J9)

Figure 2–4. J9 Pin Numbers

#### Table 2-4. J9 Pin Description

| Pin | Net-Name in Schematics | Description          |

|-----|------------------------|----------------------|

| 1   | 3.3 V                  | Digital power supply |

| 2   | GND                    | Ground               |

#### 2.5 Digital Audio and Control Interface (J1)

The digital audio interface contains digital audio signal data (I<sup>2</sup>S), clocks, serial control data, serial clock (I<sup>2</sup>C), etc. See the preliminary TAS5086 data manual on the supplied CD for signal timing and details not explained in this document.

#### Table 2–5. J1 Pin Description

| Pin | Net-Name in Schematics | Description                                                                                                                                                             |

|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LRCLK                  | I <sup>2</sup> S left-right clock                                                                                                                                       |

| 2   | SHUTDOWN               | Power-stage shutdown when asserted                                                                                                                                      |

| 3   | SCLK                   | I <sup>2</sup> S bit clock                                                                                                                                              |

| 4   | GND                    | Ground                                                                                                                                                                  |

| 5   | SDIN2                  | I <sup>2</sup> S data 2, channels 3 and 4                                                                                                                               |

| 6   | GND                    | Ground                                                                                                                                                                  |

| 7   | SDIN3                  | I <sup>2</sup> S data 2, channels 5 and 6                                                                                                                               |

| 8   | GND                    | Ground                                                                                                                                                                  |

| 9   | SDIN1                  | I <sup>2</sup> S data 2, channels 1 and 2                                                                                                                               |

| 10  | GND                    | Ground                                                                                                                                                                  |

| 11  | MCLK                   | Master clock input. Low-jitter system clock<br>for PWM generation and reclocking.<br>Ground connection from source to<br>TAS5086 must be a low-impedance<br>connection. |

| 12  | GND                    | Ground                                                                                                                                                                  |

| 13  | SCL                    | Serial clock – I <sup>2</sup> C                                                                                                                                         |

| 14  | GND                    | Ground                                                                                                                                                                  |

| 15  | SDA                    | Serial data – I <sup>2</sup> C                                                                                                                                          |

| 16  | GND                    | Ground                                                                                                                                                                  |

| 17  | MUTE                   | Input mute signal. Mute when asserted                                                                                                                                   |

| 18  | GND                    | Ground                                                                                                                                                                  |

| 19  | RESET-IN               | Reset signal. Reset when asserted                                                                                                                                       |

| 20  | 3.3 V                  | 3.3-V power supply input from DAVMC003                                                                                                                                  |

# Protection

This chapter provides a brief overview of the DAVREF633 fault-protection capabilities.

| Торіс |                                                        |   |  |  |

|-------|--------------------------------------------------------|---|--|--|

| 3.1   | Short-Circuit Protection and Fault-Reporting Circuitry | ? |  |  |

| 3.2   | Device Fault Reporting 3-2                             | 2 |  |  |

#### 3.1 Short-Circuit Protection and Fault-Reporting Circuitry

The TAS5111 and TAS5112A have a self-protecting circuit that provides device fault reporting (including high-temperature protection and short-circuit protection). The TAS5111 and TAS5112A are configured in power-stage autorecovery mode and therefore reset automatically after all errors (M1 and M2 are set low). This means that the device both restarts itself after an error occurs and reports through the SD error signal.

#### 3.2 Device Fault Reporting

The  $\overline{\text{OTW}}$  and  $\overline{\text{SD}}_XX$  outputs from TAS5111 and TAS5112A indicate fault conditions. See the TAS5111 and TAS5112A data sheets for a detailed description of these pins.

# **Performance Graphs**

This chapter contains graphs showing various performance characteristics of the DAVREF633 reference design.

#### Topic

#### Page

| 4.1 | THD+N vs Power                                         |

|-----|--------------------------------------------------------|

| 4.2 | THD+N vs Frequency 4-2                                 |

| 4.3 | FFT                                                    |

| 4.4 | FFT at -60 dB (Dynamic Range and Integrated Noise) 4-4 |

| 4.5 | Frequency Response 4-4                                 |

| 4.6 | Crosstalk vs Frequency 4-5                             |

|     |                                                        |

#### 4.1 THD+N vs Power

Figure 4–1. THD+N vs Power

#### 4.2 THD+N vs Frequency

Figure 4–2. THD+N vs Frequency at 0 dB

#### 4.3 FFT

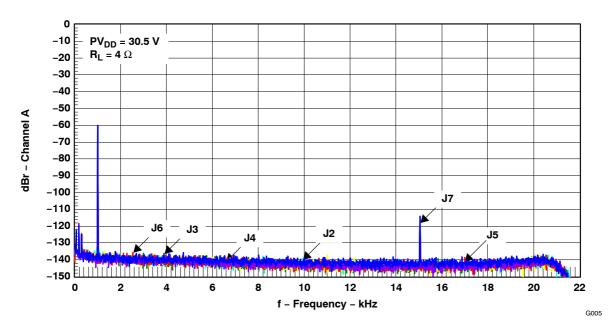

Figure 4-4. FFT, 1-kHz Sine Wave at 0 dB

#### 4.4 FFT at -60 dB (Dynamic Range and Integrated Noise)

Figure 4–5. FFT, i-kHz Sine Wave at –60 dB

The 15-kHz tone will be significantly reduced in systems using the improved TAS5086.

#### 4.5 Frequency Response

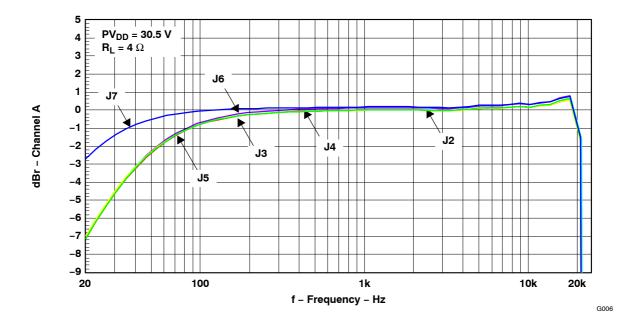

Figure 4–6. Frequency Response

#### 4.6 Crosstalk vs Frequency

# System Setup and Debugging

This chapter provides information on setting up the DAVREF633 hardware for operation and on loading and configuring the PC software to run the board. There is also troubleshooting information for use in the event of a hardware malfunction.

| Торіс |                   |    |

|-------|-------------------|----|

| 5.1   | Hardware Setup    | ·2 |

| 5.2   | Software Setup 5- | ·2 |

| 5.3   | Debugging5-       | .3 |

#### 5.1 Hardware Setup

- 1) Make sure all power supplies are in the off position.

- Insert flat flex cable from DAVREF633 to DAVMC003 (S/PDIF-I<sup>2</sup>S-I<sup>2</sup>C) board.

- 3) Connect J2–J7 to appropriate speakers.

- 4) Connect S/PDIF optical source to DAVMC003 S/PDIF optical input.

- 5) Connect 5-V power supply to DAVMC003.

- 6) Connect J8 to 30-V and 12-V power supplies.

- Connect J9 to 3.3-V power supply (optional, because 3.3 V is provided via DAVMC003).

- 8) Perform software setup (see Section 5.2).

#### 5.2 Software Setup

- 1) Copy the TAS5086 GUI zip file from the CD supplied with this reference design to a temporary directory on the PC hard drive and unzip it.

- 2) Double-click on the setup executable file and follow instructions. Using the default settings is suggested.

- Copy the TAS5086\_DAVREF633\_48KHz.cfg and TAS5086\_ DAVREF633\_44.1KHz.cfg files (located on the included CD) to the TAS5086 GUI directory (C:\Program Files\Texas Instruments Inc\ TAS5086 GUI 1.0).

- Plug in a USB cable from a PC with Windows operating system to the DeVaSys USB-I<sup>2</sup>C board.

- 5) When the USB driver is prompted by the Windows OS, direct the OS to the C:\Program Files\Texas Instruments Inc\TAS5086 GUI 1.0 directory. The USB driver for the DeVaSys board was loaded in this directory by GUI setup (Step 2).

- 6) By now, the USB interface board should be communicating with the Windows OS. Connect the 8-pin DIN (I<sup>2</sup>C) connector from the USB interface board (DeVaSys) to DAVMC003.

- 7) Turn on the power supplies in the following sequence: 3.3-V (optional), 5-V, 12-V and 30-V.

- 8) Run the TAS5086 GUI.

- 9) When the GUI is loaded, select the file pulldown menu and then select File→Load→Config File. Select the appropriate configuration file (48 KHz and 44.1 KHz refer to sampling frequency). The TAS5086 must be receiving the appropriate clocks (SCLK, LRCLK, and MCLK) and the input sample frequency must match the configuration file, i.e., if you use 48-kHz Fs, you must select TAS5086\_DAVREF633\_48KHz.cfg. IMPORTANT NOTE: To prevent possible system failure, the configuration file should not be loaded a second time without first resetting both hardware and software.

- 10) On the GUI, adjust to desirable volume.

- 11) On the S/PDIF source, start streaming audio.

- 12) If the audio does not get to the speaker, push the RESET button on the DAVMC003.

- 13) On the TAS5086 GUI, click on RESET. Then follow Step 9 above.

#### 5.3 Debugging

For troubleshooting purposes, the tables of this section provide information on the proper voltage/signal at specific locations and suggestions as to the possible cause if the observed condition is incorrect.

Check the J1 interface using Table 5–1.

Table 5–1. Debugging the DAVREF633 Digital Interface

| Pin | Name     | Check For                         | Possible Cause                                                                                                                                                               |

|-----|----------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LRCLK    | 44.1– or 48–kHz<br>clock at 3.3 V | There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board. |

| 2   | SHUTDOWN | 3.3 V                             | Ensure there are no faults, i.e., OTE or OC.                                                                                                                                 |

| 3   | SCLK     | ≈3-MHz clock at<br>3.3 V          | There should be a clean 3.3-V, $\approx$ 3-MHz clock. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                              |

| 4   | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 5   | SDIN2    | 3.3-V data                        | There should be I <sup>2</sup> S data at 3.3 V. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                                    |

| 6   | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 7   | SDIN3    | 3.3-V data                        | There should be I <sup>2</sup> S data at 3.3 V. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                                    |

| 8   | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 9   | SDIN1    | 3.3-V data                        | There should be I <sup>2</sup> S data at 3.3 V. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                                    |

| 10  | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 11  | MCLK     | 12.288 MHz at 3.3 V               | MCLK is a 3.3-V master clock input. There should be a clock of 12.288 MHz at 48-kHz Fs. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.            |

| 12  | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 13  | SCL      | 3.3-V clock                       | Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.                                                                               |

| 14  | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 15  | SDA      | 3.3-V data                        | Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.                                                                               |

| 16  | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 17  | MUTE     | 3.3 V                             | Make sure that this signal is not asserted. Make sure the pin is<br>not shorted. There should be a pullup resistor to the 3.3-V<br>supply.                                   |

| 18  | GND      | 0 V                               | If it is not at 0 V, power and ground may be shorted.                                                                                                                        |

| 19  | RESET-IN | 3.3 V                             | Make sure that this signal is not asserted. Make sure the pin is<br>not shorted. There should be a pullup resistor to the 3.3-V<br>supply.                                   |

| 20  | 3.3V     | 3.3 V                             | If 3.3-V level is not present, ensure power supply is on and check for voltage regulator malfunction on DAVMC003.                                                            |

#### Check the TAS5086 pins using Table 5–2.

#### Table 5–2. Debugging the TAS5086

| 1     VR_ANA     1.8 V     If 1.8 V is not present, ensure power supply is on and check for voltage regulator malfunction on DAVMC003.       2     AVDD     3.3 V     If 3.3 V is not present, ensure power supply is on and check for voltage regulator malfunction on DAVMC003.       3     AVSS     0 V     If it is not at 0 V, power and ground may be shorted.       4     AVSS_GR     0 V     If it is not at 0 V, power and ground may be shorted.       5     PLL_FLTM     0 V     If it is not at 0 V, power and ground may be shorted.       6     PLL_FLTP     -0.9 V     If this voltage is not present, device may be damaged.       7     AVSS     0 V     If it is not at 0 V, power and ground may be shorted.       8     MCLK     12.288 MHz at 3.3 V     MCLK is a 3.3-V clock master clock input. There should be a clock of 12.288 MHz at 48.4HZ Fs. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.       9     RESET     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       10     PDN     3.3 V     If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shots between power and ground.       11     DVDD                                                                                                                                 | Pin | Name     | Check For           | Possible Cause                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|---------------------|------------------------------------------------------------------|

| voltage regulator malfunction on DAVMC003.       3     AVSS     0 V     If it is not at 0 V, power and ground may be shorted.       4     AVSS_GR     0 V     If it is not at 0 V, power and ground may be shorted.       5     PLL_FLTM     0 V     If it is not at 0 V, power and ground may be shorted.       6     PLL_FLTP     -0.9 V     If this voltage is not present, device may be damaged.       7     AVSS     0 V     If it is not at 0 V, power and ground may be shorted.       8     MCLK     12.288 MHz at 3.3 V     GLCK is a 3.3-V clock master clock input. There should be a clock of 12.288 MHz at 48-kHz Fs. If not, check for shorts or possible damage to DIR1703 on DAVMC000 board.       9     RESET     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       10     PDN     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       11     DVDD     3.3 V     If is not at 0 V, power and ground may be shorted.       12     DVSS     0 V     If it is not at 0 V, power and ground may be shorted.       13     DVSS_OSC     0 V     If it is not at 0 V, power and ground may be sho                                                                                                                                                                       | 1   | VR_ANA   | 1.8 V               | If 1.8 V is not present, device may be damaged.                  |

| 4   AVSS_GR   0 V   If it is not at 0 V, power and ground may be shorted.     5   PLL_FLTM   0 V   If it is not at 0 V, power and ground may be shorted.     6   PLL_FLTP   ~0.9 V   If this voltage is not present, device may be damaged.     7   AVSS   0 V   If it is not at 0 V, power and ground may be shorted.     8   MCLK   12.288 MHz at 3.3 V   MCLK is a 3.3 V clock master clock input. Three should be a clock of 12.286 MHz at 48-kHz FS. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     9   RESET   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     10   PDN   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     11   DVDD   3.3 V   If it is not at 0 V, power and ground may be shorted.     12   DVSS   0 V   If it is not at 0 V, power and ground may be shorted.     13   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     14   OSC_RES   ~1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is n                                                                                                                                                                                                                       | 2   | AVDD     | 3.3 V               |                                                                  |

| 5     PLL_FLTM     0 V     If it is not at 0 V, power and ground may be shorted.       6     PLL_FLTP     =0.9 V     If this voltage is not present, device may be damaged.       7     AVSS     0 V     If it is not at 0 V, power and ground may be shorted.       8     MCLK     12.288 MHz at 3.3 V     MCLK is a 3.3-V clock master clock input. There should be a clock of 12.288 MHz at 48-KHz Fs. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.       9     RESET     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       10     PDN     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       11     DVDD     3.3 V     If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shorts between power and ground may be shorted.       12     DVSS     0 V     If it is not at 0 V, power and ground may be shorted.       14     OSC_RES     =1 V     Oscillator trim resistor. If 1 V is not present, device may be damaged.       16     MUTE     3.3 V     If 1.8 V is not present on this pin.       17     SDA     3.3-V cloc                                                                                                                            | 3   | AVSS     | 0 V                 | If it is not at 0 V, power and ground may be shorted.            |

| 6     PLL_FLTP     =0.9 V     If this voltage is not present, device may be damaged.       7     AVSS     0 V     If it is not at 0 V, power and ground may be shorted.       8     MCLK     12.288 MHz at 3.3 V     MCLK is a 3.3-V clock master clock input. There should be a clock of 12.288 MHz at 48-kHz Fs. If not, check for shorts or possible damage to DIR1703 on DAVMCO03 board.       9     RESET     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       10     PDN     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.       11     DVDD     3.3 V     If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shorts between power and ground.       12     DVSS     0 V     If it is not at 0 V, power and ground may be shorted.       13     DVSS_OSC     0 V     If it is not at 0 V, power and ground may be shorted.       14     OSC_RES     =1 V     Oscillator tim resistor. If 1 V is not present, device may be damaged.       16     MUTE     3.3 V     Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.                                                                           | 4   | AVSS_GR  | 0 V                 | If it is not at 0 V, power and ground may be shorted.            |

| 7   AVSS   0 V   If it is not at 0 V, power and ground may be shorted.     8   MCLK   12.288 MHz at 3.3 V   MCLK is a 3.3-V clock master clock input. There should be a clock of 12.288 MHz at 48-kHz Fs. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     9   RESET   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     10   PDN   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     11   DVDD   3.3 V   If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shorts between power and ground.     12   DVSS   0 V   If it is not at 0 V, power and ground may be shorted.     13   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     14   OSC_RES   =1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V                                                                                                                                              | 5   | PLL_FLTM | 0 V                 | If it is not at 0 V, power and ground may be shorted.            |

| 8   MCLK   12.288 MHz at 3.3 V   MCLK is a 3.3 V clock master clock input. There should be a clock of 12.288 MHz at 48-KHz Fs. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     9   RESET   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     10   PDN   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     11   DVDD   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     11   DVDD   3.3 V   If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shorts between power and ground.     12   DVSS   0 V   If it is not at 0 V, power and ground may be shorted.     14   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     15   VR_OSC   1.8 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3 V   If 1.8 V is not present, device may be damaged.                                                                                                          | 6   | PLL_FLTP | ≈0.9 V              | If this voltage is not present, device may be damaged.           |

| clock of 12.288 MHz at 48-kHz Fs. If not, check for shorts or<br>possible damage to DIR1703 on DAVMC003 board.       9     RESET     3.3 V     Make sure that this signal is not asserted. Make sure the pin is<br>not shorted. There should be a pullup resistor to the 3.3-V<br>supply.       10     PDN     3.3 V     Make sure that this signal is not asserted. Make sure the pin is<br>not shorted. There should be a pullup resistor to the 3.3-V<br>supply.       11     DVDD     3.3 V     If 3.3 V is not present, check to see if power supply is on or if<br>voltage regulator on DAVMC003 is not functioning. Also check<br>for possible shorts between power and ground.       12     DVSS     0 V     If it is not at 0 V, power and ground may be shorted.       13     DVSS_OSC     0 V     If it is not at 0 V, power and ground may be shorted.       14     OSC_RES     =1 V     Oscillator trim resistor. If 1 V is not present, device may be<br>damaged.       16     MUTE     3.3 V     If 1.8 V is not present, device may be damaged.       17     SDA     3.3-V data     Move the volume control on the TAS5086 GUI. The serial data<br>should be present on this pin.       18     SCL     3.3-V clock     Move the volume control on the TAS5086 GUI. The serial<br>waveform should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz<br>clock (DVD), or other clock rate (MP3). If not, check for shorts<br>or possible damage to DIR1703 on DAVMC003 board. | 7   | AVSS     | 0 V                 | If it is not at 0 V, power and ground may be shorted.            |

| not shorted. There should be a pullup resistor to the 3.3-V supply.     10   PDN   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     11   DVDD   3.3 V   If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shorts between power and ground.     12   DVSS   0 V   If it is not at 0 V, power and ground may be shorted.     13   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     14   OSC_RES   ~1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     19   LRCLK   44.1- or 48-KHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ~3-MHz clock at 3.3 V                                                                                                    | 8   | MCLK     | 12.288 MHz at 3.3 V | clock of 12.288 MHz at 48-kHz Fs. If not, check for shorts or    |

| not shorted. There should be a pullup resistor to the 3.3-V supply.     11   DVDD   3.3 V   If 3.3 V is not present, check to see if power supply is on or if voltage regulator on DAVMC003 is not functioning. Also check for possible shorts between power and ground.     12   DVSS   0 V   If it is not at 0 V, power and ground may be shorted.     13   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     14   OSC_RES   ~1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     16   MUTE   3.3 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ~3-MHz clock at 3.3 V   There should be a clean 3.3-V, ~3-MHz clock (depending on Fs). If not,                                                                                                           | 9   | RESET    | 3.3 V               | not shorted. There should be a pullup resistor to the 3.3-V      |

| 12   DVSS   0 V   If it is not at 0 V, power and ground may be shorted.     13   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     14   OSC_RES   ~1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     15   VR_OSC   1.8 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ~3-MHz clock at 3.3 V   There should be a clean 3.3-V, =3-MHz clock (depending on Fs). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                  | 10  | PDN      | 3.3 V               | not shorted. There should be a pullup resistor to the 3.3-V      |

| 13   DVSS_OSC   0 V   If it is not at 0 V, power and ground may be shorted.     14   OSC_RES   ≈1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     15   VR_OSC   1.8 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ≈3-MHz clock at 3.3 V   There should be a clean 3.3-V, ≈3-MHz clock (depending on Fs). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                              | 11  | DVDD     | 3.3 V               | voltage regulator on DAVMC003 is not functioning. Also check     |

| 14   OSC_RES   ≈1 V   Oscillator trim resistor. If 1 V is not present, device may be damaged.     15   VR_OSC   1.8 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ≈3-MHz clock at 3.3 V   There should be a clean 3.3-V, ≈3-MHz clock (depending on 5.3 V     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12  | DVSS     | 0 V                 | If it is not at 0 V, power and ground may be shorted.            |

| 15   VR_OSC   1.8 V   If 1.8 V is not present, device may be damaged.     16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ≈3-MHz clock at 3.3 V   There should be a clean 3.3-V, ≈3-MHz clock (depending on Fs). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13  | DVSS_OSC | 0 V                 | If it is not at 0 V, power and ground may be shorted.            |

| 16   MUTE   3.3 V   Make sure that this signal is not asserted. Make sure the pin is not shorted. There should be a pullup resistor to the 3.3-V supply.     17   SDA   3.3-V data   Move the volume control on the TAS5086 GUI. The serial data should be present on this pin.     18   SCL   3.3-V clock   Move the volume control on the TAS5086 GUI. The serial waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ≈3-MHz clock at 3.3 V   There should be a clean 3.3-V, ≈3-MHz clock (depending on Fs). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14  | OSC_RES  | ≈1 V                |                                                                  |

| not shorted. There should be a pullup resistor to the 3.3-V<br>supply.17SDA3.3-V dataMove the volume control on the TAS5086 GUI. The serial data<br>should be present on this pin.18SCL3.3-V clockMove the volume control on the TAS5086 GUI. The serial<br>waveform should be present on this pin.19LRCLK44.1- or 48-kHz clock<br>at 3.3 VThere should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz<br>clock (DVD), or other clock rate (MP3). If not, check for shorts<br>or possible damage to DIR1703 on DAVMC003 board.20SCLK~3-MHz clock at<br>3.3 VThere should be a clean 3.3-V, ~3-MHz clock (depending on<br>Fs). If not, check for shorts or possible damage to DIR1703 on<br>DAVMC003 board.21N/AN/AReserved pin22SDOUTN/AIt is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15  | VR_OSC   | 1.8 V               | If 1.8 V is not present, device may be damaged.                  |

| should be present on this pin.18SCL3.3-V clockMove the volume control on the TAS5086 GUI. The serial<br>waveform should be present on this pin.19LRCLK44.1- or 48-kHz clock<br>at 3.3 VThere should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz<br>clock (DVD), or other clock rate (MP3). If not, check for shorts<br>or possible damage to DIR1703 on DAVMC003 board.20SCLK~3-MHz clock at<br>3.3 VThere should be a clean 3.3-V, ~3-MHz clock (depending on<br>Fs). If not, check for shorts or possible damage to DIR1703 on<br>DAVMC003 board.21N/AN/AReserved pin22SDOUTN/AIt is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16  | MUTE     | 3.3 V               | not shorted. There should be a pullup resistor to the 3.3-V      |

| waveform should be present on this pin.     19   LRCLK   44.1- or 48-kHz clock<br>at 3.3 V   There should be a clean 3.3-V, 44.1-kHz clock (CD), 48-kHz<br>clock (DVD), or other clock rate (MP3). If not, check for shorts<br>or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ≈3-MHz clock at<br>3.3 V   There should be a clean 3.3-V, ≈3-MHz clock (depending on<br>Fs). If not, check for shorts or possible damage to DIR1703 on<br>DAVMC003 board.     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17  | SDA      | 3.3-V data          |                                                                  |

| at 3.3 V   clock (DVD), or other clock rate (MP3). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     20   SCLK   ≈3-MHz clock at 3.3 V   There should be a clean 3.3-V, ≈3-MHz clock (depending on Fs). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.     21   N/A   N/A   Reserved pin     22   SDOUT   N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18  | SCL      | 3.3-V clock         |                                                                  |

| 3.3 V Fs). If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.   21 N/A N/A   22 SDOUT N/A   It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19  | LRCLK    |                     | clock (DVD), or other clock rate (MP3). If not, check for shorts |

| 22 SDOUT N/A It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20  | SCLK     |                     | Fs). If not, check for shorts or possible damage to DIR1703 on   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21  | N/A      | N/A                 | Reserved pin                                                     |

| 23 SDIN4 N/A It is not used on this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22  | SDOUT    | N/A                 | It is not used on this reference design.                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23  | SDIN4    | N/A                 | It is not used on this reference design.                         |

| Pin | Name     | Check For  | Possible Cause                                                                                                                                                                      |

|-----|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24  | SDIN3    | 3.3-V data | There should be I <sup>2</sup> S data at 3.3 V. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                                           |

| 25  | SDIN2    | 3.3-V data | There should be I <sup>2</sup> S data at 3.3 V. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                                           |

| 26  | SDIN1    | 3.3-V data | There should be I <sup>2</sup> S data at 3.3 V. If not, check for shorts or possible damage to DIR1703 on DAVMC003 board.                                                           |

| 27  | BKND_ERR | 3.3 V      | Make sure this signal is not asserted. If it is asserted, check for a power-stage error. See power-stage debugging, Table 5–3.                                                      |

| 28  | VREG_EN  | 0 V        | If it is not at 0 V, power and ground may be shorted.                                                                                                                               |

| 29  | DVSS_ESD | 0 V        | If it is not at 0 V, power and ground may be shorted.                                                                                                                               |

| 30  | VR_DIG   | 1.8 V      | If 1.8 V is not present, device may be damaged.                                                                                                                                     |

| 31  | VALID2   | 3.3 V      | Make sure this signal is high (3.3 V). If not, check for possible power-stage errors or the system is in RESET or PDN.                                                              |

| 32  | VALID1   | 3.3 V      | Make sure this signal is high (3.3 V). If not, check for possible power-stage errors or the system is in RESET or PDN.                                                              |

| 33  | PWM_6    | 3.3-V PWM  | There should be PWM signal switching at 3.3 V. If not, check<br>for power-stage errors, system in reset, power down, or mute.<br>When mute, the PWM is switching at 50% duty cycle. |

| 34  | PWM_5    | 3.3-V PWM  | There should be PWM signal switching at 3.3 V. If not, check<br>for power-stage errors, system in reset, power down, or mute.<br>When mute, the PWM is switching at 50% duty cycle. |

| 35  | PWM_4    | 3.3-V PWM  | There should be PWM signal switching at 3.3 V. If not, check<br>for power-stage errors, system in reset, power down, or mute.<br>When mute, the PWM is switching at 50% duty cycle. |

| 36  | PWM_3    | 3.3-V PWM  | There should be PWM signal switching at 3.3 V. If not, check<br>for power-stage errors, system in reset, power down, or mute.<br>When mute, the PWM is switching at 50% duty cycle. |

| 37  | PWM_2    | 3.3-V PWM  | There should be PWM signal switching at 3.3 V. If not, check<br>for power-stage errors, system in reset, power down, or mute.<br>When mute, the PWM is switching at 50% duty cycle. |

| 38  | PWM_1    | 3.3-V PWM  | There should be PWM signal switching at 3.3 V. If not, check<br>for power-tage errors, system in reset, power down, or mute.<br>When mute, the PWM is switching at 50% duty cycle.  |

Table 5–2. Debugging the TAS5086 (continued)

#### Check the TAS5111 pins using Table 5–3 (TAS5112A is similar to TAS5111).

| Pin | Name     | Check For       | Possible Cause                                                                                                                                                                           |

|-----|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PWM_BP   | 3.3-V PWM       | PWM switching input from TAS5086 at 3.3-V swing. On TAS5086: check for mute signal if it is 50% duty cycle; check for reset, power-down signals if it is 0 V.                            |

| 2   | GND      | 0 V             | If it is not at 0 V, power and ground may be shorted.                                                                                                                                    |

| 3   | RESET    | 3.3 V           | Make sure that this signal is not asserted. Make sure the pin is not shorted.                                                                                                            |

| 4   | DREG_RTN | 0 V             | If it is not at 0 V, power and ground may be shorted.                                                                                                                                    |

| 5   | GREG     | 12 V            | If it is not at 12 V, check power-supply connection. Also check to see if power and ground are shorted.                                                                                  |

| 6   | МЗ       | 3.3 V           | SE configuration. If the voltage is not there, this pin may be grounded by mistake. This pin should be pulled up to 3.3 V.                                                               |

| 7   | DREG     | ≈3.3 V          | If it is not at 3.3 V, device may be damaged.                                                                                                                                            |

| 8   | DGND     | 0 V             | If it is not at 0 V, power and ground may be shorted.                                                                                                                                    |